# CDP1852/3, CDP1852C/3

March 1997

# High-Reliability Byte-Wide Input/Output Port

### Features

- · Static Silicon-Gate CMOS Circuitry

- Parallel 8-Bit Data Register and Buffer

- Handshaking Via Service Request Flip-Flop

- · Low Quiescent and Operating Power

- · Interfaces Directly with CDP1800-Series Microprocessors

- Single Voltage Supply

- · Full Military Temperature Range (-55°C to +125°C)

# Ordering Information

| PACKAGE | TEMP.<br>RANGE  | 5V         | 10V       | PKG.<br>NO |

|---------|-----------------|------------|-----------|------------|

| SBDIP   | -55°C to +125°C | CDP1852CD3 | CDP1852D3 | D24.6      |

#### Pinout

CDP1852/3, CDP1852C/3 (SBDIP) TOP VIEW

# Description

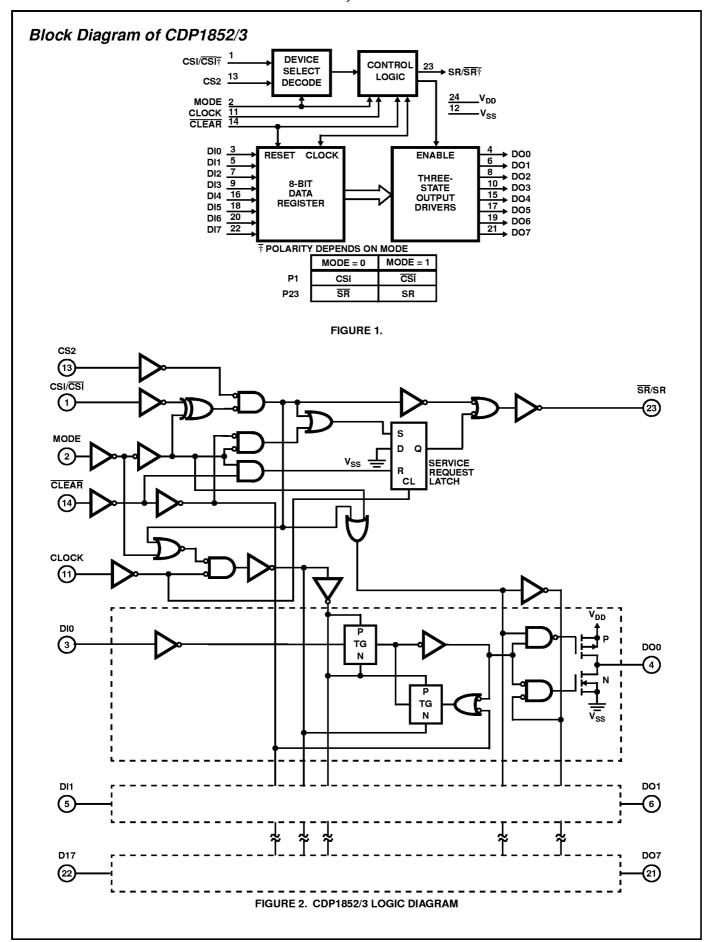

The CDP1852/3 and CDP1852C/3 are parallel, 8-bit, modeprogrammable input/output ports. They are compatible and will interface directly with CDP1800-Series microprocessors. They are also useful as 8-bit address latches when used with the CDP1800 multiplexed address bus and as I/O ports in general-purpose applications.

The mode control is used to program the device as an input port (mode = 0) or as an output port (mode = 1). The  $\overline{SR}/SR$ output can be used as a signal to indicate when data is ready to be transferred. In the input mode, a peripheral device can strobe data into the CDP1852/3, and microprocessor can read that data by device selection. In the output mode, a microprocessor strobes data into the CDP1852/3, and handshaking is established with a peripheral device when the CDP1852/3 is deselected.

In the input mode, data at the data-in terminals (DI0-DI7) is strobed into the port's 8-bit register by a high (1) level on the clock line. The negative high-to-low transition of the clock latches the data in the register and sets the service request output low (SR/SR = 0). When  $CS1/\overline{CS1}$  and CS2 are high  $(CS1/\overline{CS1})$  and CS2 = 1, the three-state output drivers are enabled and data in the 8-bit register appear at the data-out terminals (DO0-DO7). When either CS1/CS1 or CS2 goes low (CS1/ $\overline{CS1}$  or CS2 = 0), the data-out terminals are tristated and the service request output returns high  $(\overline{SR}/SR = 1)$ .

In the output mode, the output drivers are enabled at all times. Data at the data-in terminals (DI0-DI7) is strobed into the 8-bit register when  $CS1/\overline{CS1}$  is low  $(CS1/\overline{CS1} = 0)$  and CS2 and the clock are high (1), and are present at the dataout terminals (DO0-DO7). The negative high-to-low transition of the clock latches the data in the register. The SR/SR output goes high  $(\overline{SR}/SR = 1)$  when the device is deselected  $(CS1/\overline{CS1} = 1 \text{ or } CS2 = 0)$  and returns low  $(\overline{SR}/SR = 0)$  on the following trailing edge of the clock.

A CLEAR control is provided for resetting the port's register (DO0-DO7 = 0) and service request flip-flop (input mode:  $\overline{SR}/SR = 1$  and output mode:  $\overline{SR}/SR = 0$ ).

The CDP1852/3 is functionally identical to the CDP1852C/3. The CDP1852/3 has a recommended operating voltage range of 4V to 10.5V, and the CDP1852C/3 has a recommended operating voltage range of 4V to 6.5V.

The CDP1852/3 and CDP1852C/3 are supplied in 24-lead, dual-in-line side-brazed ceramic packages (D suffix).

# CDP1852/3, CDP1852C/3

# **Absolute Maximum Ratings**

####

# **Thermal Information**

| θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------|------------------------|

| 65                     | 20                     |

|                        |                        |

|                        |                        |

|                        | 100mW                  |

|                        |                        |

| 55 <sup>c</sup>        | °C to +125°C           |

| 65 <sup>c</sup>        | °C to +150°C           |

|                        |                        |

| ım)                    |                        |

|                        | +265°C                 |

|                        | 65<br>                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

**Recommended Operating Conditions** T<sub>A</sub> = Full-Package Temperature Range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges.

|                            | CPP1     | 852/3    | CDP18    |          |       |

|----------------------------|----------|----------|----------|----------|-------|

| PARAMETER                  | MIN      | MAX      | MIN      | MAX      | UNITS |

| DC Operating Voltage Range | 4        | 10.5     | 4        | 6.5      | V     |

| Input Voltage Range        | $V_{SS}$ | $V_{DD}$ | $V_{SS}$ | $V_{DD}$ | V     |

# Static Electrical Specifications $V_{IN} = 0$ or $V_{DD}$ , Except as Noted

|                                    |                 |                                              | LIMITS |       |      |      |          |

|------------------------------------|-----------------|----------------------------------------------|--------|-------|------|------|----------|

|                                    |                 |                                              | -55°C, | +25°C | +12  | 25°C | <b>1</b> |

| PARAMETER                          | SYMBOL          | TEST CONDITIONS                              | MIN    | MAX   | MIN  | MAX  | UNITS    |

| Quiescent Device Current (Note 1)  | l <sub>DD</sub> | V <sub>DD</sub> = 5V                         | -      | 10    | -    | 100  | μΑ       |

|                                    |                 | V <sub>DD</sub> = 10V                        | -      | 20    | -    | 300  | μΑ       |

| Output Low Drive (Sink) Current    | l <sub>OL</sub> | $V_{DD} = 5V, V_{O} = 0.4V$                  | 2.6    | -     | 1.9  | -    | mA       |

|                                    |                 | $V_{DD} = 10V, V_{O} = 0.5V$                 | 6.1    | -     | 4.1  | -    | mA       |

| Output High Drive (Source) Current | I <sub>OH</sub> | $V_{DD} = 5V, V_{O} = 4.6V$                  | -1.8   | -     | -1.3 | -    | mA       |

|                                    |                 | $V_{DD} = 10V, V_{O} = 9.5V$                 | -4.4   | -     | -2.9 | -    | mA       |

| Output Voltage Low Level           | V <sub>OL</sub> | $V_{DD} = 5V$ , $I_{OL} = 0\mu A$            | -      | 0.1   | -    | 0.2  | ٧        |

|                                    |                 | $V_{DD} = 10V, I_{OL} = 0\mu A$              | -      | 0.1   | -    | 0.2  | ٧        |

| Output Voltage High Level          | V <sub>OH</sub> | $V_{DD} = 5V$ , $I_{OL} = 0\mu A$            | 4.9    | -     | 4.8  | -    | ٧        |

|                                    |                 | $V_{DD} = 10V, I_{OL} = 0\mu A$              | 9.9    | -     | 9.8  | -    | ٧        |

| Input Low Voltage                  | V <sub>IL</sub> | $V_{DD} = 5V, V_{O} = 0.2, 4.8V$             | -      | 1.5   | -    | 1.5  | ٧        |

|                                    |                 | $V_{DD} = 10V, V_{O} = 0.2, 9.8V$            | -      | 3     | -    | 3    | ٧        |

| Input High Voltage                 | V <sub>IH</sub> | $V_{DD} = 5V, V_{O} = 0.2, 4.8V$             | 3.5    | -     | 3.5  | -    | ٧        |

|                                    |                 | $V_{DD} = 10V, V_{O} = 0.2, 9.8V$            | 7      | -     | 7    | -    | ٧        |

| Input Leakage Low                  | I <sub>IL</sub> | V <sub>DD</sub> = 5V, V <sub>IN</sub> = 0V   | -      | -1    | -    | -5   | μΑ       |

|                                    |                 | V <sub>DD</sub> = 10V, V <sub>IN</sub> = 0V  | -      | -1    | -    | -5   | μΑ       |

| Input Leakage High                 | I <sub>IH</sub> | V <sub>DD</sub> = 5V, V <sub>IN</sub> = 5V   | -      | 1     | -    | 5    | μΑ       |

|                                    |                 | V <sub>DD</sub> = 10V, V <sub>IN</sub> = 10V | -      | 1     | -    | 5    | μΑ       |

# Static Electrical Specifications $V_{IN} = 0$ or $V_{DD}$ , Except as Noted (Continued)

|                                 |                  |                             | LIMITS |       |     |     |       |

|---------------------------------|------------------|-----------------------------|--------|-------|-----|-----|-------|

|                                 |                  |                             | -55°C, | +25°C | +12 | 5°C |       |

| PARAMETER                       | SYMBOL           | TEST CONDITIONS             | MIN    | MAX   | MIN | MAX | UNITS |

| Three-State Output Leakage Low  | I <sub>OZL</sub> | $V_{DD} = 5V, V_{O} = 0V$   | -      | -1    | -   | -5  | μΑ    |

|                                 |                  | $V_{DD} = 10V, V_{O} = 0V$  | -      | -1    | -   | -5  | μΑ    |

| Three-State Output Leakage High | l <sub>ozh</sub> | $V_{DD} = 5V, V_{O} = 5V$   | -      | 1     | -   | 5   | μΑ    |

|                                 |                  | $V_{DD} = 10V, V_{O} = 10V$ | -      | 1     | -   | 5   | μΑ    |

| Input Capacitance               | C <sub>IN</sub>  | Note 2                      | -      | 10    | -   | 10  | pF    |

| Output Capacitance              | C <sub>OUT</sub> | Note 2                      | -      | 15    | -   | 15  | pF    |

#### NOTES:

- 1. The CDP1852C/3 meets all 5V static electrical specifications of the CDP1852/3 except +125 $^{\circ}$ C quiescent device current for which the limit is  $I_{DD}$  = 300 $\mu$ A.

- 2. Input and output capacitance are guaranteed but not tested.

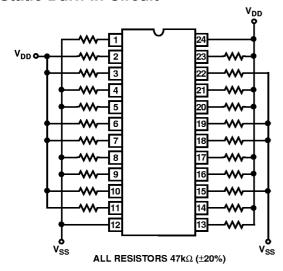

# Static Burn-In Circuit

| TYPE NO.   | V <sub>DD</sub> | TEMPERATURE | TIME          |

|------------|-----------------|-------------|---------------|

| CDP1852/3  | 11V             | +125°C      | 160 Hrs. Min. |

| CDP1852C/3 | 7V              | +125°C      | 160 Hrs. Min. |

#

|                                  |                  |                          | LIMITS (NOTE 1) |       |                 |     |       |

|----------------------------------|------------------|--------------------------|-----------------|-------|-----------------|-----|-------|

|                                  |                  |                          | -55°C,          | +25°C | +12             | 5°C |       |

| PARAMETER                        | SYMBOL           | V <sub>DD</sub><br>VOLTS | (NOTE 1)<br>MIN | MAX   | (NOTE 1)<br>MIN | MAX | UNITS |

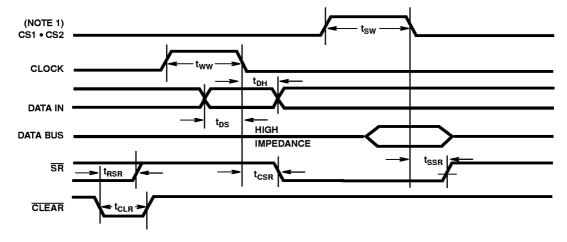

| Select Duration                  | t <sub>SW</sub>  | 5                        | 250             | -     | 360             | -   | ns    |

|                                  |                  | 10                       | 150             | -     | 180             | -   | ns    |

| Clock Pulse Width                | t <sub>ww</sub>  | 5                        | 150             | -     | 200             | -   | ns    |

|                                  |                  | 10                       | 90              | -     | 110             | -   | ns    |

| Clear Pulse Width                | t <sub>CLR</sub> | 5                        | 110             | -     | 160             | -   | ns    |

|                                  |                  | 10                       | 50              | -     | 80              | -   | ns    |

| Data-In to Clock Fall Setup Time | t <sub>DS</sub>  | 5                        | -10             | -     | -10             | -   | ns    |

|                                  |                  | 10                       | -5              | -     | -5              | -   | ns    |

$\textbf{Dynamic Electrical Specifications} \quad \text{Mode = 0 Input Port, See Figure 3, Input $t_r$, $t_f \leq 15 ns$; $C_L = 50 pF$ } \quad \textbf{(Continued)}$

|                                         |                  |                          | LIMITS (NOTE 1) |       |                 |     |       |

|-----------------------------------------|------------------|--------------------------|-----------------|-------|-----------------|-----|-------|

|                                         |                  |                          | -55°C,          | +25°C | +125°C          |     |       |

| PARAMETER                               | SYMBOL           | V <sub>DD</sub><br>VOLTS | (NOTE 1)<br>MIN | MAX   | (NOTE 1)<br>MIN | MAX | UNITS |

| Data-In After Clock Fall Hold Time      | t <sub>DH</sub>  | 5                        | 150             | -     | 170             | -   | ns    |

|                                         |                  | 10                       | 70              | -     | 100             | -   | ns    |

| Propagation Delay Times:<br>Clear to SR | t <sub>RSR</sub> | 5                        | -               | 200   | -               | 340 | ns    |

|                                         |                  | 10                       | -               | 110   | -               | 170 | ns    |

| Clock to SR                             | t <sub>CSR</sub> | 5                        | -               | 175   | -               | 220 | ns    |

|                                         |                  | 10                       | -               | 110   | -               | 130 | ns    |

| Deselect to SR                          | t <sub>SSR</sub> | 5                        | -               | 175   | -               | 240 | ns    |

|                                         |                  | 10                       | -               | 110   | -               | 120 | ns    |

# NOTE:

1. Time required by a device to allow for the indicated function.

# NOTE:

1. CS1 • CS2 is the overlap of CS1 = 1 and CS2 = 1.

| MODE = 0 TRUTH TABLE |                    |       |                 |  |  |  |  |  |

|----------------------|--------------------|-------|-----------------|--|--|--|--|--|

| CLOCK                | CS1 • CS2 (Note 1) | CLEAR | DATA OUT EQUALS |  |  |  |  |  |

| Х                    | 0                  | Х     | High Impedance  |  |  |  |  |  |

| 0                    | 1                  | 0     | 0               |  |  |  |  |  |

| 0                    | 1                  | 1     | Data Latch      |  |  |  |  |  |

| 1                    | 1                  | Х     | Data In         |  |  |  |  |  |

| SERVICE REQUEST<br>TRUTH TABLE |                           |  |  |  |  |

|--------------------------------|---------------------------|--|--|--|--|

| Clock =                        | CS1 or CS2 = or CLEAR = 0 |  |  |  |  |

| <del>SR</del> = 0              | SR = 1                    |  |  |  |  |

# NOTE:

1. CS1 • CS2 = CS1 = 1, CS2 = 1.

FIGURE 3. MODE = 0 INPUT PORT TIMING WAVEFORMS AND TRUTH TABLES

# CDP1852/3, CDP1852C/3

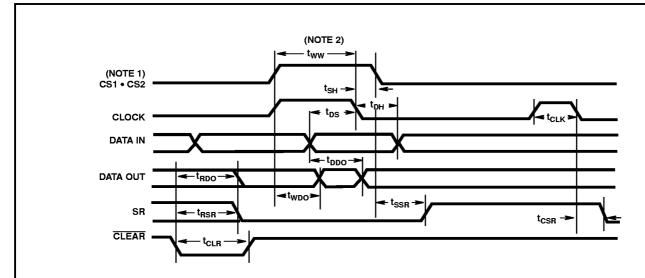

$\textbf{Dynamic Electrical Specification} \qquad \text{Mode} = 1 \text{ Output Port, See Figure 4, Input } tr, tf \leq 15 ns; C_L = 50 pF$

|                                           |                  |                          |                 | LIMITS | (NOTE 1)        |     |       |

|-------------------------------------------|------------------|--------------------------|-----------------|--------|-----------------|-----|-------|

|                                           |                  |                          | -55°C,          | +25°C  | +12             | 5°C | 1     |

| PARAMETER                                 | SYMBOL           | V <sub>DD</sub><br>VOLTS | (NOTE 1)<br>MIN | MAX    | (NOTE 1)<br>MIN | MAX | UNITS |

| Clock Pulse Width                         | t <sub>CLK</sub> | 5                        | 170             | -      | 260             | -   | ns    |

|                                           |                  | 10                       | 90              | -      | 130             | -   | ns    |

| Write Width Duration                      | t <sub>WW</sub>  | 5                        | 200             | -      | 260             | -   | ns    |

|                                           |                  | 10                       | 110             | -      | 130             | -   | ns    |

| Clear Pulse Width                         | t <sub>CLR</sub> | 5                        | 110             | -      | 135             | -   | ns    |

|                                           |                  | 10                       | 60              | -      | 75              | -   | ns    |

| Data-In to Clock Fall Setup Time          | t <sub>DS</sub>  | 5                        | -10             | -      | -10             | -   | ns    |

|                                           |                  | 10                       | -5              | -      | -5              | -   | ns    |

| Data Hold from Write Termination          | t <sub>DH</sub>  | 5                        | 130             | -      | 170             | -   | ns    |

|                                           |                  | 10                       | 70              | -      | 90              | -   | ns    |

| Select-After Clock-Fall Hold Time         | t <sub>sн</sub>  | 5                        | 0               | -      | 0               | -   | ns    |

|                                           |                  | 10                       | 0               | -      | 0               | -   | ns    |

| Propagation Delay Times:<br>Clear to Data | <sup>t</sup> RDO | 5                        | -               | 215    | -               | 290 | ns    |

|                                           |                  | 10                       | -               | 140    | -               | 190 | ns    |

| Write to Data Out                         | t <sub>WDO</sub> | 5                        | -               | 250    | -               | 350 | ns    |

|                                           |                  | 10                       | -               | 130    | -               | 190 | ns    |

| Data In to Data Out                       | t <sub>DDO</sub> | 5                        | -               | 150    | -               | 200 | ns    |

|                                           |                  | 10                       | -               | 80     | -               | 100 | ns    |

| Clear to SR                               | t <sub>RSR</sub> | 5                        | -               | 175    | -               | 240 | ns    |

|                                           |                  | 10                       | -               | 120    | -               | 160 | ns    |

| Clock to SR                               | t <sub>CSR</sub> | 5                        | -               | 170    | -               | 240 | ns    |

|                                           |                  | 10                       | -               | 90     | -               | 120 | ns    |

| Deselect to SR                            | t <sub>SSR</sub> | 5                        | -               | 170    | -               | 240 | ns    |

|                                           |                  | 10                       | -               | 90     | -               | 120 | ns    |

#### NOTE:

<sup>1.</sup> Time required by a device to allow for the indicated function.

#### NOTES:

- 1. CS1 CS2 is the overlap of the  $\overline{CS1}$  = 0 and CS2 = 1.

- 2. Write is the overlap of CS1 CS2 and clock.

| MODE = 1 TRUTH TABLE |                           |       |                 |  |  |  |  |

|----------------------|---------------------------|-------|-----------------|--|--|--|--|

| CLOCK                | <u>CS1</u> • CS2 (NOTE 1) | CLEAR | DATA OUT EQUALS |  |  |  |  |

| 0                    | Х                         | 0     | 0               |  |  |  |  |

| 0                    | Х                         | 1     | Data Latch      |  |  |  |  |

| Х                    | 0                         | 1     | Data Latch      |  |  |  |  |

| 1                    | 1                         | Х     | Data In         |  |  |  |  |

| SERVICE REQUEST<br>TRUTH TABLE |                       |

|--------------------------------|-----------------------|

| CS1 _ <b>√</b>                 | Clock • (CS1 • CS2) → |

| or                             | or                    |

| CS2                            | CLEAR = 0             |

| SR = 1                         | SR = 0                |

# NOTE:

1. <del>CS1</del> • CS2 = <del>CS1</del> = 0, CS2 = 1

FIGURE 4. MODE = 1 OUTPUT PORT TIMING WAVEFORMS AND TRUTH TABLES