# FM1105

### Nonvolatile 5V Dual State Saver

# Features

### Nonvolatile State Saver

- Logic States Retained in Absence of Power

- Outputs Automatically Restored at Power-up

- Number of State Changes: 10<sup>12</sup>

- Max t<sub>PD</sub> 50ns at 4.5V

- Max Frequency 1 MHz

### Low Power Operation

- Supply voltage of 4.5V to 5.5V

- 15 µA Standby Current (+85°C)

### **Industry Standard Configuration**

- Automotive Temperature -40° C to +125° C

Qualified to AEC Q100 Specification

- 8-pin "Green"/RoHS SOIC Package

### Overview

The FM1105 is an innovative FRAM-based device that stores inputs like conventional logic and retains the stored state in the absence of power. This product solves three basic problems in an elegant fashion. First, it provides continuous access to nonvolatile system settings without performing a memory read operation or using dedicated processor I/O pins. Second, it allows the storage of signals that may change frequently and possibly without notice. Third, it allows the nonvolatile storage of a system setting without the system overhead and extra pins of a serial memory.

Functionally, the inputs are stored and passed to the output on the rising edge of the clock CLK. This unique product serves a variety of applications. Here are a few applications:

Control relays or valves with automatic setting on power-up without processor intervention

- Interface to soft/momentary front-panel switch and indicator lamp. Capture switch settings and drive LEDs without processor intervention

- Replaces jumpers & control signal routing

- Initialize state of I/O card signals

- Eliminate the overhead of serial memory for systems needing only a bit of data

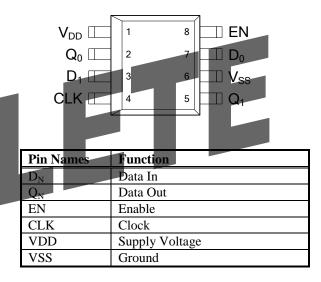

# **Pin Configuration**

| Ordering Information |                               |  |  |

|----------------------|-------------------------------|--|--|

| FM1105-GA            | Dual State Saver,             |  |  |

|                      | 8-pin "Green"/RoHS SOIC,      |  |  |

|                      | Automotive Grade 1            |  |  |

| FM1105-GATR          | Dual State Saver,             |  |  |

|                      | 8-pin "Green"/RoHS SOIC,      |  |  |

|                      | Automotive Grade 1, Tape&Reel |  |  |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

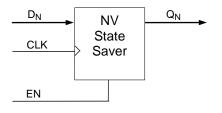

# **Block Diagram and Truth Table**

| INPUTS |        |    | OUTPUT |

|--------|--------|----|--------|

| EN     | CLK    | Dn | Qn     |

| Н      | 1      | L  | L      |

| Н      | 1      | Н  | Н      |

| Н      | H or L | Х  | $Q_0$  |

| L      | Х      | Χ  | Hi-Z   |

L Low voltage level

H High voltage level

X Don't Care

↑ CLK rising edge

$Q_0$  Previous output state before CLK  $\uparrow$

# **Pin Descriptions**

| Pin Name   | I/O    | Description                                                                                                                                                                                                   |

|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $D_0, D_1$ | Input  | Data inputs                                                                                                                                                                                                   |

| $Q_0, Q_1$ | Output | Data outputs                                                                                                                                                                                                  |

| CLK        | Input  | Clock: On a rising edge of CLK, the $D_N$ inputs are transferred to the $Q_N$ outputs. While CLK is high or low, the $Q_N$ outputs do not change regardless of the state of the data inputs. See truth table. |

| EN         | Input  | Enable. This active-high input enables the device. When low, inputs are ignored and updates to the nonvolatile cells are prevented. When high, the device operates normally.                                  |

| VDD        | Supply | Power Supply (4.5V to 5.5V)                                                                                                                                                                                   |

| VSS        | Supply | Ground                                                                                                                                                                                                        |

|            |        |                                                                                                                                                                                                               |

# Description

Nonvolatile storage applied to logic is a revolutionary concept. The FM1105 simplifies the design of system control functions. This product is unique because it remembers the stored output values in the absence of power. Any change in the latched state is automatically written to a nonvolatile ferroelectric latch. This function is possible due to the fast write time and extremely high write endurance of the underlying ferroelectric memory technology.

# **Use of Enable Pin**

The FM1105 has an enable pin that is intended to be used in conjunction with a system reset. An activelow reset may be tied directly to the EN pin. At power-up, /RESET will be held low for some time during which the data input and CLK pins will be ignored. Once the system comes out of reset and EN goes high, the outputs  $Q_N$  drive to the state that were previously latched and the device operates normally. When the EN pin is low, the outputs  $Q_N$  are tristated.

The enable pin may be tied to  $V_{DD}$  since the device integrates a power management circuit that monitors the  $V_{DD}$  level during power cycles.

# OBSOLETE

### **Electrical Specifications** Absolute Maximum Ratings

| Symbol            | Description                                               | Ratings                      |

|-------------------|-----------------------------------------------------------|------------------------------|

| V <sub>DD</sub>   | Power Supply Voltage with respect to V <sub>SS</sub>      | -1.0V to +7.0V               |

| $V_{IN}$          | Voltage on any signal pin with respect to V <sub>SS</sub> | -1.0V to +7.0V               |

|                   |                                                           | and $V_{IN} < V_{DD} + 1.0V$ |

| T <sub>STG</sub>  | Storage temperature                                       | -55°C to + 125°C             |

| T <sub>LEAD</sub> | Lead temperature (Soldering, 10 seconds)                  | 300° C                       |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage                           |                              |

|                   | - Human Body Model (JEDEC Std JESD22-A114-B)              | 4kV                          |

|                   | - Charged Device Model (JEDEC Std JESD22-C101-A)          | 1kV                          |

|                   | - Machine Model (JEDEC Std JESD22-A115-A)                 | 200V                         |

|                   | Package Moisture Sensitivity Level                        | MSL-1                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and the functional operation of the device at these or any other conditions above those listed in the operational section of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

| <b>DC Operating</b> | <b>Conditions</b> ( $T_A = -40^\circ \text{ C te}$ | $+125^{\circ}$ C, $V_{DD} = 4.5$ V to | 5.5V unless otherwise | specified) |

|---------------------|----------------------------------------------------|---------------------------------------|-----------------------|------------|

|---------------------|----------------------------------------------------|---------------------------------------|-----------------------|------------|

| Symbol           | Parameter                                           | Min            | Тур | Max            | Units    | Notes |

|------------------|-----------------------------------------------------|----------------|-----|----------------|----------|-------|

| V <sub>DD</sub>  | Power Supply Voltage                                | 4.5            | 5.0 | 5.5            | V        |       |

| I <sub>SB</sub>  | Standby Current                                     |                |     |                |          | 1     |

|                  | @ +85℃<br>@ +125℃                                   |                |     | 15<br>20       | μA<br>μA |       |

| C <sub>PD</sub>  | Power Dissipation Capacitance                       |                |     | 165            | pF       | 2     |

| ILI              | Input Leakage Current                               |                |     | ±1             | μΑ       | 3     |

| I <sub>LO</sub>  | Output Leakage Current                              |                |     | ±1             | μΑ       | 3     |

| V <sub>IL</sub>  | Input Low Voltage                                   | -0.3           |     | $0.3 V_{DD}$   | V        |       |

| V <sub>IH</sub>  | Input High Voltage                                  | $0.7 V_{DD}$   |     | $V_{DD} + 0.3$ | V        |       |

| V <sub>OH</sub>  | Output High Voltage                                 |                |     |                |          |       |

|                  | @ I <sub>OH</sub> = -1 mA                           | $V_{DD} - 0.5$ |     | -              | V        |       |

| V <sub>OL</sub>  | Output Low Voltage                                  |                |     |                |          |       |

|                  | @ $I_{OL} = 1 \text{ mA} (V_{DD} = 4.5 \text{V})$   | -              |     | 0.4            | V        |       |

|                  | @ $I_{OL} = 10 \text{ mA} (V_{DD} = 4.5 \text{ V})$ | -              |     | 0.8            | V        |       |

| V <sub>HYS</sub> | Input Hysteresis (CLK, EN)                          | 150            |     |                | mV       | 4     |

Notes

1.  $CLK = V_{SS}$ , all other inputs at  $V_{DD}$  or  $V_{SS}$ .

2. To calculate device power dissipation,  $P_D = C_{PD} * V_{DD}^2 * f_i + C_L * V_{DD}^2 * f_o$ , where  $f_i$  is the input clk freq,  $f_o$  is the output freq, and  $C_L$  is the output load capacitance. Active current  $I_{DD}$  may be calculated as  $I_{DD} = C_{PD} * V_{DD} * f_i$ , assuming outputs are floating.

3.  $V_{IN}$  or  $V_{OUT} = V_{SS}$  to  $V_{DD}$ .

4. This parameter is characterized but not tested.

### **Capacitance** ( $T_A = 25^{\circ} \text{ C}$ , f=1.0 MHz, $V_{DD} = 5.0 \text{ V}$ )

| Symbol | Parameter         | Min | Max | Units | Notes |

|--------|-------------------|-----|-----|-------|-------|

| CI     | Input Capacitance | -   | 8   | pF    | 1     |

Notes

1. This parameter is characterized but not tested.

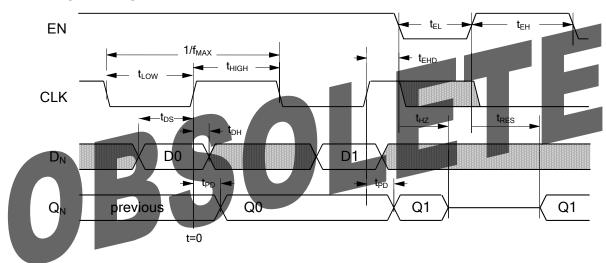

| <b>AC Parameters</b> | $(T_A = -40^\circ \text{ C to } +125^\circ \text{ C})$ | C, $V_{DD} = 4.5V$ to 5.5V, $C_L = 3$ | 0 pF unless otherwise specified) |

|----------------------|--------------------------------------------------------|---------------------------------------|----------------------------------|

|----------------------|--------------------------------------------------------|---------------------------------------|----------------------------------|

| Symbol            | Parameter                                     | Min | Max | Units | Notes |

|-------------------|-----------------------------------------------|-----|-----|-------|-------|

| f <sub>MAX</sub>  | Maximum Clock Frequency                       | -   | 1   | MHz   |       |

| t <sub>LOW</sub>  | CLK Low Period                                | 0.3 | -   | μs    |       |

| t <sub>HIGH</sub> | CLK High Period                               | 0.3 | -   | μs    |       |

| t <sub>PD</sub>   | Propagation delay CLK to Q <sub>N</sub>       | -   | 50  | ns    |       |

| t <sub>HZ</sub>   | EN Low to Q <sub>N</sub> Hi-Z                 | -   | 25  | ns    | 1     |

| t <sub>R</sub>    | Input Rise Time                               | -   | 100 | ns    | 1     |

| t <sub>F</sub>    | Input Fall Time                               | -   | 100 | ns    | 1     |

| t <sub>DS</sub>   | Data ( $D_N$ ) Setup Time to CLK $\uparrow$   | 5   | -   | ns    |       |

| t <sub>DH</sub>   | Data ( $D_N$ ) Hold Time after CLK $\uparrow$ | 10  | -   | ns    |       |

| t <sub>EHD</sub>  | EN Hold Time (EN High after CLK $\uparrow$ )  | 50  | -   | ns    |       |

| t <sub>EH</sub>   | EN High Time                                  | 5   | -   | μs    |       |

| t <sub>EL</sub>   | EN Low Time                                   | 2   | -   | μs    |       |

Notes

1. This parameter is characterized but not tested.

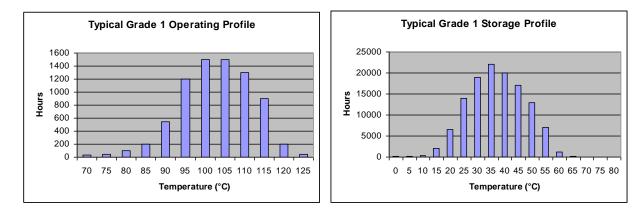

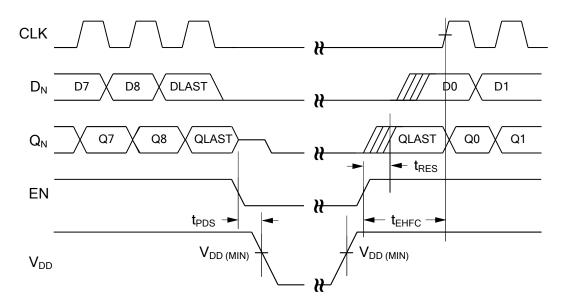

### **Power Cycling and Data Retention** ( $T_A = -40^{\circ}$ C to $+125^{\circ}$ C, $V_{DD} = 4.5$ V to 5.5V, unless otherwise specified)

| Symbol            | Parameter                                     | Min | Max | Units | Notes |

|-------------------|-----------------------------------------------|-----|-----|-------|-------|

|                   | Nonvolatile Data Retention Time               | 45  | -   | years |       |

| t <sub>VDR</sub>  | V <sub>DD</sub> Rise Time                     | 25  |     | μs/V  | 1     |

| t <sub>VDF</sub>  | V <sub>DD</sub> FallTime                      | 50  | -   | μs/V  | 1     |

| t <sub>RES</sub>  | EN High to Q <sub>N</sub> Restore Time        | -   | 0.5 | μs    | 2     |

| t <sub>PDS</sub>  | EN Low to Power Down Time                     | 1   | -   | μs    |       |

| t <sub>EHFC</sub> | EN High to First Clock (CLK ↑) after Power Up | 4   | -   | μs    | 3     |

| Teder             |                                               |     |     |       |       |

### Notes

1. Slope measured at any point on  $V_{DD}$  waveform.

2. After power up, when EN goes high the nonvolatile latches are read and the values restored to the outputs  $Q_N$ .

3. After power up, this is the minimum time required before a state change operation may occur. EN and  $V_{DD}$  may be coincident at power up, and in this case  $t_{EHFC}$  time is referenced to  $V_{DD}$  (min) and CLK  $\uparrow$ .

### **Data Retention** $(V_{DD} = 4.5V \text{ to } 5.5V)$

| Parameter              | Min  | Max | Units | Notes |

|------------------------|------|-----|-------|-------|

| Data Retention         |      |     |       |       |

| @ $T_A = 85^{\circ}C$  | 45   | -   | Years |       |

| @ $T_A = 125^{\circ}C$ | 9000 | -   | Hours |       |

Note: The device is guaranteed to retain data after both conditions have been applied: (1) 45 yrs at a temperature of 85°C and (2) 9000 hours at 125°C.

### **AC Test Conditions**

| Input Pulse Levels             | $0.1~V_{\text{DD}}$ to $0.9~V_{\text{DD}}$ |

|--------------------------------|--------------------------------------------|

| Input Rise and Fall Times      | 10 ns                                      |

| Input and Output Timing Levels | 0.5 V <sub>DD</sub>                        |

| Output Load Capacitance        | 30pF                                       |

### FM1105 Signal Timing

# **Power Cycle Timing**

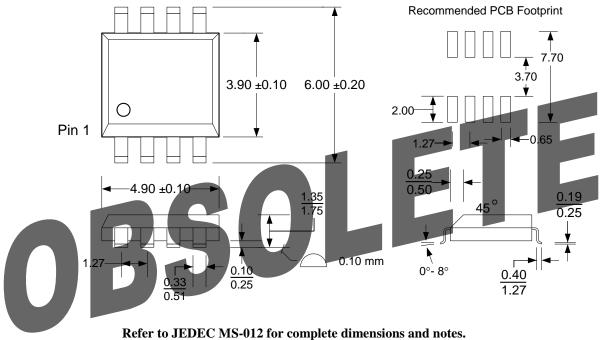

# **Mechanical Drawing**

8-pin SOIC (JEDEC Standard MS-012 variation AA)

All dimensions in <u>millimeters</u>.

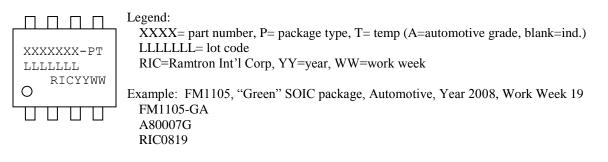

# **SOIC Package Marking Scheme**

# **Revision History**

| Revision | Date                     | Summary                                                                      |

|----------|--------------------------|------------------------------------------------------------------------------|

| 1.0      | 11/26/2008               | Created automotive temperature spec.                                         |

| 1.1      | 2/3/2009                 | Updated I <sub>SB</sub> @ +85C and added tape and reel ordering information. |

| 3.0      | 4/15/2009                | Changed to Production status. Changed 125C retention time.                   |

| 4.0      | 4 <sup>th</sup> Oct 2012 | Added obsolete text                                                          |

# OBSOLETE