# Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 Series

Datasheet, Volume 2

April 2009

Order Number: 321322-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Xeon® Processor 5500 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details. Over time processor numbers will increment based on changes in clock, speed, cache, FSB, or other features, and increments are not intended to represent proportional or quantitative increases in any particular feature. Current roadmap processor number progression is not necessarily representative of future roadmaps. See www.intel.com/products/processor\_number for details.

Hyper-Threading Technology requires a computer system with a processor supporting HT Technology and an HT Technologyenabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. For more information including details on which processors support HT Technology, see http://www.intel.com/products/ht/hyperthreading\_more.htm

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting operating system. Check with your PC manufacturer on whether your system delivers Execute Disable Bit functionality.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel® 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

Intel® Turbo Boost Technology requires a PC with a processor with Intel Turbo Boost Technology capability. Intel Turbo Boost Technology performance varies depending on hardware, software and overall system configuration. Check with your PC manufacturer on whether your system delivers Intel Turbo Boost Technology. For more information, see www.intel.com.

Enhanced Intel SpeedStep® Technology. See the http://processorfinder.intel.com or contact your Intel representative for more information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Xeon, Enhanced Intel SpeedStep Technology, and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

\*Other brands and names are the property of their respective owners.

Copyright © 2009, Intel Corporation.

## Contents

| 1 | Intro | duction  |                                                | . 15 |

|---|-------|----------|------------------------------------------------|------|

|   | 1.1   | Termino  | blogy                                          | . 15 |

|   |       | 1.1.1    | Processor Terminology                          | . 15 |

|   | 1.2   | Referen  | ces                                            |      |

| 2 | Regis | ster Des | cription                                       | . 19 |

|   | 2.1   |          | r Terminology                                  |      |

|   | 2.2   |          | n Configuration Structure                      |      |

|   | 2.3   |          | Mapping                                        |      |

|   | 2.4   |          | I Configuration Space Maps                     |      |

|   | 2.5   |          | ndard Registers                                |      |

|   |       | 2.5.1    | VID - Vendor Identification Register           |      |

|   |       | 2.5.2    | DID - Device Identification Register           |      |

|   |       | 2.5.3    | RID - Revision Identification Register         |      |

|   |       | 2.5.4    | CCR - Class Code Register                      |      |

|   |       | 2.5.5    | HDR - Header Type Register                     |      |

|   |       | 2.5.6    | SID/SVID - Subsystem Identity/Subsystem Vendor |      |

|   |       | 2.0.0    | Identification Register                        | . 47 |

|   |       | 2.5.7    | PCICMD - Command Register                      |      |

|   |       | 2.5.8    | PCISTS - PCI Status Register                   |      |

|   | 2.6   | Generic  | Non-core Registers                             |      |

|   |       | 2.6.1    | MAXREQUEST_LC                                  |      |

|   |       | 2.6.2    | MAXREQUEST_LS                                  |      |

|   |       | 2.6.3    | MAXREQUEST_LL                                  | . 51 |

|   |       | 2.6.4    | MAX_RTIDS                                      |      |

|   |       | 2.6.5    | DESIRED_CORES                                  |      |

|   |       | 2.6.6    | MEMLOCK_STATUS                                 | . 52 |

|   |       | 2.6.7    | MC_CFG_CONTROL                                 |      |

|   |       | 2.6.8    | POWER_CNTRL_ERR_STATUS                         |      |

|   |       | 2.6.9    | CURRENT_UCLK_RATIO                             |      |

|   |       | 2.6.10   | MIRROR_PORT_CTL                                |      |

|   |       | 2.6.11   | MIP_PH_CTR_LO                                  |      |

|   |       |          | MIP_PH_CTR_L1                                  | . 55 |

|   |       | 2.6.12   | MIP_PH_PRT_LO                                  |      |

|   |       |          | MIP_PH_PRT_L1                                  | . 56 |

|   | 2.7   | SAD - S  | ystem Address Decoder Registers                | . 56 |

|   |       | 2.7.1    | SAD_PAM0123                                    | . 56 |

|   |       | 2.7.2    | SAD_PAM456                                     | . 58 |

|   |       | 2.7.3    | SAD_HEN                                        | . 59 |

|   |       | 2.7.4    | SAD_SMRAM                                      | . 59 |

|   |       | 2.7.5    | SAD_PCIEXBAR                                   | . 60 |

|   |       | 2.7.6    | SAD_DRAM_RULE_0                                |      |

|   |       |          | SAD_DRAM_RULE_1                                |      |

|   |       |          | SAD_DRAM_RULE_2                                |      |

|   |       |          | SAD_DRAM_RULE_3                                |      |

|   |       |          | SAD_DRAM_RULE_4                                |      |

|   |       |          | SAD_DRAM_RULE_5                                |      |

|   |       |          | SAD_DRAM_RULE_6<br>SAD_DRAM_RULE_7             | 60   |

|   |       |          |                                                |      |

|      | 2.7.7     | SAD_INTERLEAVE_LIST_0                            |

|------|-----------|--------------------------------------------------|

|      |           | SAD_INTERLEAVE_LIST_1                            |

|      |           | SAD_INTERLEAVE_LIST_2                            |

|      |           | SAD_INTERLEAVE_LIST_3                            |

|      |           | SAD_INTERLEAVE_LIST_4                            |

|      |           | SAD_INTERLEAVE_LIST_5<br>SAD_INTERLEAVE_LIST_6   |

|      |           | SAD_INTERLEAVE_LIST_0<br>SAD_INTERLEAVE_LIST_761 |

| 2.8  | Intol OP  | I Link Registers                                 |

| 2.0  | 2.8.1     | QPI_QPILCP_L0                                    |

|      | 2.0.1     | QPI_QPILCP_L1                                    |

|      | 2.8.2     | QPI QPILCL LO                                    |

|      | 2.0.2     | QPI_QPILCL_L1                                    |

|      | 2.8.3     | QPI QPILS LO                                     |

|      |           | QPI_QPILS_L1                                     |

|      | 2.8.4     | QPI_DEF_RMT_VN_CREDITS_L0                        |

|      |           | QPI_DEF_RMT_VN_CREDITS_L163                      |

|      | 2.8.5     | QPI_RMT_QPILPO_STAT_LO                           |

|      |           | QPI_RMT_QPILPO_STAT_L1                           |

|      | 2.8.6     | QPI_RMT_QPILP1_STAT_L0                           |

|      | 0 0 7     | QPI_RMT_QPILP1_STAT_L1                           |

|      | 2.8.7     | QPI_RMT_QPILP2_STAT_L0<br>QPI_RMT_QPILP2_STAT_L1 |

|      | 2.8.8     | QPI_RMT_QPILP2_STAT_L1                           |

|      | 2.0.0     | QPI_RMT_QPILP3_STAT_L0<br>QPI_RMT_QPILP3_STAT_L1 |

| 2.9  |           | I Physical Layer Registers                       |

| 2.7  | 2.9.1     | QPI_0_PH_CPR                                     |

|      | 2.7.1     | QPI_1_PH_CPR                                     |

|      | 2.9.2     | QPI 0 PH CTR                                     |

|      |           | QPI_1_PH_CTR                                     |

|      | 2.9.3     | QPI_0_PH_PIS                                     |

|      |           | QPI_1_PH_PIS                                     |

|      | 2.9.4     | QPI_0_PH_PTV                                     |

|      |           | QPI_1_PH_PTV                                     |

|      | 2.9.5     | QPI_0_PH_LDC                                     |

|      | <i>(</i>  | QPI_1_PH_LDC                                     |

|      | 2.9.6     | QPI_0_PH_PRT                                     |

|      | 207       | QPI_1_PH_PRT                                     |

|      | 2.9.7     | QPI_0_PH_PMR0<br>QPI_1_PH_PMR070                 |

|      | 2.9.8     | QPI_0_EP_SR                                      |

|      | 2.7.0     | QPI_1_EP_SR                                      |

|      | 2.9.9     | QPI_0_EP_MCTR                                    |

|      | ,,,       | QPI_1_EP_MCTR                                    |

| 2.10 | Intel QP  | I Miscellaneous Registers                        |

|      | 2.10.1    | QPI_0_PLL_STATŬS                                 |

|      |           | QPI_1_PLL_STATUS                                 |

|      | 2.10.2    | QPI_0_PLL_RATIO                                  |

|      |           | QPI_1_PLL_RATIO72                                |

| 2.11 | Integrate | ed Memory Controller Control Registers73         |

|      | 2.11.1    | MC_CONTROL73                                     |

|      | 2.11.2    | MC_STATUS74                                      |

|      | 2.11.3    | MC_SMI_DIMM_ERROR_STATUS                         |

|      | 2.11.4    | MC_SMI_CNTRL                                     |

|      | 2.11.5    | MC_RESET_CONTROL                                 |

|      | 2.11.6    | MC_CHANNEL_MAPPER                                |

|      | 2.11.7    | MC_MAX_DOD                                       |

|      | 2.11.8    | MC_RD_CRDT_INIT                                  |

|      | 2.11.9    | MC_CRDT_WR_THLD                                  |

| 2.12  | 2.11.11          | MC_SCRUBADDR_LO                                                                                                                                                                                      |

|-------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 2.12.2           | TAD_INTERLEAVE_LIST_0<br>TAD_INTERLEAVE_LIST_1<br>TAD_INTERLEAVE_LIST_2<br>TAD_INTERLEAVE_LIST_3<br>TAD_INTERLEAVE_LIST_4<br>TAD_INTERLEAVE_LIST_5<br>TAD_INTERLEAVE_LIST_6<br>TAD_INTERLEAVE_LIST_7 |

| 2.13  | -                | ed Memory Controller RAS Registers82                                                                                                                                                                 |

|       | 2.13.1           | MC_SSRCONTROL                                                                                                                                                                                        |

|       | 2.13.2           | MC_SCRUB_CONTROL                                                                                                                                                                                     |

|       | 2.13.3           | MC_RAS_ENABLES                                                                                                                                                                                       |

|       | 2.13.4<br>2.13.5 | MC_RAS_STATUS                                                                                                                                                                                        |

|       | 2.13.5           | MC_SSRSTATUS                                                                                                                                                                                         |

|       | 2.13.0           | MC_COR_ECC_CNT_1<br>MC_COR_ECC_CNT_2<br>MC_COR_ECC_CNT_3<br>MC_COR_ECC_CNT_4                                                                                                                         |

| 2 1 4 | Intograt         | MC_COR_ECC_CNT_5                                                                                                                                                                                     |

| 2.14  | 2.14.1           | ed Memory Controller Test Registers                                                                                                                                                                  |

|       | 2.14.1           | MC_TEST_ERR_RCV1                                                                                                                                                                                     |

|       | 2.14.2           | MC_TEST_ERK_RCV0                                                                                                                                                                                     |

|       | 2.14.3           | MC_TEST_PH_PIS                                                                                                                                                                                       |

|       | 2.14.4           | MC_TEST_PAT_GCTR                                                                                                                                                                                     |

|       | 2.14.5           | MC_TEST_PAT_GOTK                                                                                                                                                                                     |

|       | 2.14.7           | MC_TEST_PAT_IS                                                                                                                                                                                       |

|       | 2.14.7           | MC_TEST_PAT_DCD                                                                                                                                                                                      |

| 2.15  |                  | ed Memory Controller Channel Control Registers                                                                                                                                                       |

| 2.10  | 2.15.1           | MC_CHANNEL_0_DIMM_RESET_CMD                                                                                                                                                                          |

|       |                  | MC_CHANNEL_1_DIMM_RESET_CMD                                                                                                                                                                          |

|       |                  | MC_CHANNEL_2_DIMM_RESET_CMD                                                                                                                                                                          |

|       | 2.15.2           | MC_CHANNEL_0_DIMM_INIT_CMD                                                                                                                                                                           |

|       |                  | MC_CHANNEL_1_DIMM_INIT_CMD                                                                                                                                                                           |

|       |                  | MC_CHANNEL_2_DIMM_INIT_CMD                                                                                                                                                                           |

|       | 2.15.3           | MC_CHANNEL_0_DIMM_INIT_PARAMS<br>MC_CHANNEL_1_DIMM_INIT_PARAMS                                                                                                                                       |

|       | 0154             | MC_CHANNEL_2_DIMM_INIT_PARAMS                                                                                                                                                                        |

|       | 2.15.4           | MC_CHANNEL_0_DIMM_INIT_STATUS<br>MC_CHANNEL_1_DIMM_INIT_STATUS                                                                                                                                       |

|       |                  | MC_CHANNEL_1_DIMM_INIT_STATUS<br>MC_CHANNEL_2_DIMM_INIT_STATUS                                                                                                                                       |

|       | 2.15.5           | MC_CHANNEL_0_DDR3CMD                                                                                                                                                                                 |

|       |                  | MC_CHANNEL_1_DDR3CMD                                                                                                                                                                                 |

|       |                  | MC_CHANNEL_2_DDR3CMD                                                                                                                                                                                 |

|       | 2.15.6           | MC_CHANNEL_0_REFRESH_THROTTLE_SUPPORT                                                                                                                                                                |

|       |                  | MC_CHANNEL_1_REFRESH_THROTTLE_SUPPORT                                                                                                                                                                |

|       |                  | MC_CHANNEL_2_REFRESH_THROTTLE_SUPPORT                                                                                                                                                                |

| 2.15.7    | MC_CHANNEL_0_MRS_VALUE_0_1                                                 |

|-----------|----------------------------------------------------------------------------|

|           | MC_CHANNEL_1_MRS_VALUE_0_1<br>MC_CHANNEL_2_MRS_VALUE_0_1                   |

| 2.15.8    | MC_CHANNEL_2_MRS_VALUE_0_1                                                 |

| 2.13.0    | MC_CHANNEL_1_MRS_VALUE_2                                                   |

|           | MC_CHANNEL_2_MRS_VALUE_2                                                   |

| 2.15.9    | MC_CHANNEL_O_RANK_PRESENT                                                  |

|           | MC_CHANNEL_1_RANK_PRESENT                                                  |

|           | MC_CHANNEL_2_RANK_PRESENT                                                  |

| 2.15.10   | MC_CHANNEL_O_RANK_TIMING_A                                                 |

|           | MC_CHANNEL_1_RANK_TIMING_A<br>MC_CHANNEL_2_RANK_TIMING_A95                 |

| 2 15 11   | MC_CHANNEL_0_RANK_TIMING_B                                                 |

| 2.10.11   | MC_CHANNEL_1_RANK_TIMING_B                                                 |

|           | MC_CHANNEL_2_RANK_TIMING_B                                                 |

| 2.15.12   | MC_CHANNEL_0_BANK_TIMING                                                   |

|           | MC_CHANNEL_1_BANK_TIMING                                                   |

| 0 1 - 10  | MC_CHANNEL_2_BANK_TIMING                                                   |

| 2.15.13   | MC_CHANNEL_0_REFRESH_TIMING<br>MC_CHANNEL_1_REFRESH_TIMING                 |

|           | MC_CHANNEL_2_REFRESH_TIMING                                                |

| 2.15.14   | MC_CHANNEL_0_CKE_TIMING                                                    |

|           | MC_CHANNEL_1_CKE_TIMING                                                    |

|           | MC_CHANNEL_2_CKE_TIMING                                                    |

| 2.15.15   | MC_CHANNEL_0_ZQ_TIMING                                                     |

|           | MC_CHANNEL_1_ZQ_TIMING<br>MC_CHANNEL_2_ZQ_TIMING100                        |

| 2 15 16   | MC_CHANNEL_2_2Q_TIMING                                                     |

| 2.15.10   | MC_CHANNEL_1_RCOMP_PARAMS                                                  |

|           | MC_CHANNEL_2_RCOMP_PARAMS101                                               |

| 2.15.17   | MC_CHANNEL_0_ODT_PARAMS1                                                   |

|           | MC_CHANNEL_1_ODT_PARAMS1                                                   |

| 0 1 5 1 0 | MC_CHANNEL_2_ODT_PARAMS1                                                   |

| 2.15.18   | MC_CHANNEL_0_ODT_PARAMS2<br>MC_CHANNEL_1_ODT_PARAMS2                       |

|           | MC_CHANNEL_2_ODT_PARAMS2 102                                               |

| 2.15.19   | MC_CHANNEL_0_ODT_MATRIX_RANK_0_3_RD                                        |

|           | MC_CHANNEL_1_ODT_MATRIX_RANK_0_3_RD                                        |

|           | MC_CHANNEL_2_ODT_MATRIX_RANK_0_3_RD102                                     |

| 2.15.20   | MC_CHANNEL_0_ODT_MATRIX_RANK_4_7_RD                                        |

|           | MC_CHANNEL_1_ODT_MATRIX_RANK_4_7_RD<br>MC_CHANNEL_2_ODT_MATRIX_RANK_4_7_RD |

| 2 15 21   | MC_CHANNEL_0_ODT_MATRIX_RANK_0_3_WR                                        |

|           | MC_CHANNEL_1_ODT_MATRIX_RANK_0_3_WR                                        |

|           | MC_CHANNEL_2_ODT_MATRIX_RANK_0_3_WR103                                     |

| 2.15.22   | MC_CHANNEL_0_ODT_MATRIX_RANK_4_7_WR                                        |

|           | MC_CHANNEL_1_ODT_MATRIX_RANK_4_7_WR                                        |

| 2 15 22   | MC_CHANNEL_2_ODT_MATRIX_RANK_4_7_WR                                        |

| 2.15.23   | MC_CHANNEL_0_WAQ_PARAMS<br>MC_CHANNEL_1_WAQ_PARAMS                         |

|           | MC_CHANNEL_2_WAQ_PARAMS                                                    |

| 2.15.24   | MC_CHANNEL_0_SCHEDULER_PARAMS                                              |

|           | MC_CHANNEL_1_SCHEDULER_PARAMS                                              |

|           | MC_CHANNEL_2_SCHEDULER_PARAMS104                                           |

| 2.15.25   | MC_CHANNEL_0_MAINTENANCE_OPS<br>MC_CHANNEL_1_MAINTENANCE_OPS               |

|           | MC_CHANNEL_1_MAINTENANCE_OPS<br>MC_CHANNEL_2_MAINTENANCE_OPS               |

| 2.15.26   | MC_CHANNEL_2_MAINTENANCE_OFS                                               |

|           | MC_CHANNEL_1_TX_BG_SETTINGS                                                |

|           | MC_CHANNEL_2_TX_BG_SETTINGS                                                |

|      | 2.15.27   | MC_CHANNEL_0_RX_BGF_SETTINGS                                                 |

|------|-----------|------------------------------------------------------------------------------|

|      |           | MC_CHANNEL_1_RX_BGF_SETTINGS                                                 |

|      |           | MC_CHANNEL_2_RX_BGF_SETTINGS 106                                             |

|      | 2.15.28   | MC_CHANNEL_0_EW_BGF_SETTINGS                                                 |

|      |           | MC_CHANNEL_1_EW_BGF_SETTINGS                                                 |

|      |           | MC_CHANNEL_2_EW_BGF_SETTINGS                                                 |

|      | 2.15.29   | MC_CHANNEL_0_EW_BGF_OFFSET_SETTINGS                                          |

|      |           | MC_CHANNEL_1_EW_BGF_OFFSET_SETTINGS                                          |

|      | 0 4 5 0 0 | MC_CHANNEL_2_EW_BGF_OFFSET_SETTINGS                                          |

|      | 2.15.30   | MC_CHANNEL_O_ROUND_TRIP_LATENCY                                              |

|      |           | MC_CHANNEL_1_ROUND_TRIP_LATENCY                                              |

|      | 0 45 04   | MC_CHANNEL_2_ROUND_TRIP_LATENCY                                              |

|      | 2.15.31   | MC_CHANNEL_O_PAGETABLE_PARAMS1                                               |

|      |           | MC_CHANNEL_1_PAGETABLE_PARAMS1<br>MC_CHANNEL_2_PAGETABLE_PARAMS1             |

|      | 2 15 22   |                                                                              |

|      | 2.15.32   | MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH0<br>MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH1 |

|      |           | MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH1<br>MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH2 |

|      | 2 15 22   | MC_TX_BG_CMD_OFFSET_SETTINGS_CH0                                             |

|      | 2.10.33   | MC_TX_BG_CMD_OFFSET_SETTINGS_CH0                                             |

|      |           | MC_TX_BG_CMD_OFFSET_SETTINGS_CH2                                             |

|      | 2 15 3/   | MC_TX_BG_DATA_OFFSET_SETTINGS_CH0                                            |

|      | 2.10.04   | MC_TX_BG_DATA_OFFSET_SETTINGS_CH1                                            |

|      |           | MC_TX_BG_DATA_OFFSET_SETTINGS_CH2                                            |

| 2.16 | Integrate | ed Memory Controller Channel Address Registers                               |

| 2.10 | 2.16.1    | MC DOD CHO 0                                                                 |

|      | 2.10.1    | MC DOD CH0 1                                                                 |

|      |           | MC_DOD_CH0_2                                                                 |

|      | 2.16.2    | MC_DOD_CH1_0                                                                 |

|      | 20.2      | MC DOD CH1 1                                                                 |

|      |           | MC_DOD_CH1_2                                                                 |

|      | 2.16.3    | MC_DOD_CH2_0                                                                 |

|      |           | MC_DOD_CH2_1                                                                 |

|      |           | MC_DOD_CH2_2                                                                 |

|      | 2.16.4    | MC_SAG_CH0_0                                                                 |

|      |           | MC_SAG_CH0_1                                                                 |

|      |           | MC_SAG_CH0_2                                                                 |

|      |           | MC_SAG_CH0_3                                                                 |

|      |           | MC_SAG_CH0_4                                                                 |

|      |           | MC_SAG_CH0_5                                                                 |

|      |           | MC_SAG_CH0_6                                                                 |

|      |           | MC_SAG_CH0_7                                                                 |

|      |           | MC_SAG_CH1_0                                                                 |

|      |           | MC_SAG_CH1_1                                                                 |

|      |           | MC_SAG_CH1_2                                                                 |

|      |           | MC_SAG_CH1_3                                                                 |

|      |           | MC_SAG_CH1_4<br>MC_SAG_CH1_5                                                 |

|      |           | MC_SAG_CH1_6                                                                 |

|      |           | MC_SAG_CH1_7                                                                 |

|      |           | MC_SAG_CH2_0                                                                 |

|      |           | MC_SAG_CH2_1                                                                 |

|      |           | MC_SAG_CH2_2                                                                 |

|      |           | MC_SAG_CH2_3                                                                 |

|      |           | MC_SAG_CH2_4                                                                 |

|      |           | MC_SAG_CH2_5                                                                 |

|      |           | MC_SAG_CH2_6                                                                 |

|      |           | MC_SAG_CH2_7 112                                                             |

| 2.17 | Integrate | ed Memory Controller Channel Rank Registers 113                              |

| 2.17.1  | MC RIR LIMIT CHO O   |

|---------|----------------------|

|         | MC_RIR_LIMIT_CH0_1   |

|         | MC_RIR_LIMIT_CH0_2   |

|         | MC_RIR_LIMIT_CH0_3   |

|         | MC_RIR_LIMIT_CH0_4   |

|         | MC_RIR_LIMIT_CH0_5   |

|         |                      |

|         | MC_RIR_LIMIT_CH0_6   |

|         | MC_RIR_LIMIT_CH0_7   |

|         | MC_RIR_LIMIT_CH1_0   |

|         | MC_RIR_LIMIT_CH1_1   |

|         | MC_RIR_LIMIT_CH1_2   |

|         | MC_RIR_LIMIT_CH1_3   |

|         | MC_RIR_LIMIT_CH1_4   |

|         | MC_RIR_LIMIT_CH1_5   |

|         | MC_RIR_LIMIT_CH1_6   |

|         | MC_RIR_LIMIT_CH1_7   |

|         | MC_RIR_LIMIT_CH2_0   |

|         | MC_RIR_LIMIT_CH2_1   |

|         | MC_RIR_LIMIT_CH2_2   |

|         | MC_RIR_LIMIT_CH2_3   |

|         | MC_RIR_LIMIT_CH2_4   |

|         | MC_RIR_LIMIT_CH2_5   |

|         | MC_RIR_LIMIT_CH2_6   |

|         | MC_RIR_LIMIT_CH2_7   |

| 0 1 7 0 |                      |

| 2.17.2  | MC_RIR_WAY_CHO_0     |

|         | MC_RIR_WAY_CHO_1     |

|         | MC_RIR_WAY_CHO_2     |

|         | MC_RIR_WAY_CH0_3     |

|         | MC_RIR_WAY_CH0_4     |

|         | MC_RIR_WAY_CH0_5     |

|         | MC_RIR_WAY_CHO_6     |

|         | MC_RIR_WAY_CH0_7     |

|         | MC_RIR_WAY_CH0_8     |

|         | MC_RIR_WAY_CH0_9     |

|         | MC_RIR_WAY_CH0_10    |

|         | MC_RIR_WAY_CH0_11    |

|         | MC_RIR_WAY_CH0_12    |

|         | MC_RIR_WAY_CH0_13    |

|         | MC_RIR_WAY_CH0_14    |

|         | MC_RIR_WAY_CH0_15    |

|         | MC_RIR_WAY_CH0_16    |

|         | MC_RIR_WAY_CH0_17    |

|         | MC_RIR_WAY_CH0_18    |

|         | MC_RIR_WAY_CH0_19    |

|         | MC_RIR_WAY_CHO_20    |

|         | MC_RIR_WAY_CH0_21    |

|         | MC_RIR_WAY_CH0_22    |

|         |                      |

|         | MC_RIR_WAY_CH0_23    |

|         | MC_RIR_WAY_CHO_24    |

|         | MC_RIR_WAY_CHO_25    |

|         | MC_RIR_WAY_CHO_26    |

|         | MC_RIR_WAY_CH0_27    |

|         | MC_RIR_WAY_CH0_28    |

|         | MC_RIR_WAY_CH0_29    |

|         | MC_RIR_WAY_CH0_30    |

|         | MC_RIR_WAY_CH0_31114 |

| 2.17.3 | MC_RIR_WAY_CH1_0      |

|--------|-----------------------|

|        | MC_RIR_WAY_CH1_1      |

|        | MC_RIR_WAY_CH1_2      |

|        | MC_RIR_WAY_CH1_3      |

|        | MC_RIR_WAY_CH1_4      |

|        | MC_RIR_WAY_CH1_5      |

|        | MC_RIR_WAY_CH1_6      |

|        | MC_RIR_WAY_CH1_7      |

|        | MC_RIR_WAY_CH1_8      |

|        | MC_RIR_WAY_CH1_9      |

|        | MC_RIR_WAY_CH1_10     |

|        | MC_RIR_WAY_CH1_11     |

|        | MC_RIR_WAY_CH1_12     |

|        | MC_RIR_WAY_CH1_13     |

|        | MC_RIR_WAY_CH1_14     |

|        | MC_RIR_WAY_CH1_15     |

|        | MC_RIR_WAY_CH1_16     |

|        | MC_RIR_WAY_CH1_17     |

|        | MC_RIR_WAY_CH1_18     |

|        | MC_RIR_WAY_CH1_19     |

|        | MC_RIR_WAY_CH1_20     |

|        | MC_RIR_WAY_CH1_21     |

|        | MC_RIR_WAY_CH1_22     |

|        | MC_RIR_WAY_CH1_23     |

|        | MC_RIR_WAY_CH1_24     |

|        | MC_RIR_WAY_CH1_25     |

|        | MC_RIR_WAY_CH1_26     |

|        | MC_RIR_WAY_CH1_27     |

|        | MC_RIR_WAY_CH1_28     |

|        | MC_RIR_WAY_CH1_29     |

|        | MC_RIR_WAY_CH1_30     |

|        | MC_RIR_WAY_CH1_31 115 |

9

|      | 2.17.4 | MC_RIR_WAY_CH2_0                                  |

|------|--------|---------------------------------------------------|

|      |        | MC_RIR_WAY_CH2_1                                  |

|      |        | MC_RIR_WAY_CH2_2                                  |

|      |        | MC_RIR_WAY_CH2_3<br>MC_RIR_WAY_CH2_4              |

|      |        | MC_RIR_WAY_CH2_5                                  |

|      |        | MC_RIR_WAY_CH2_6                                  |

|      |        | MC_RIR_WAY_CH2_7                                  |

|      |        | MC_RIR_WAY_CH2_8                                  |

|      |        | MC_RIR_WAY_CH2_9                                  |

|      |        | MC_RIR_WAY_CH2_10                                 |

|      |        | MC_RIR_WAY_CH2_11                                 |

|      |        | MC_RIR_WAY_CH2_12                                 |

|      |        | MC_RIR_WAY_CH2_13<br>MC_RIR_WAY_CH2_14            |

|      |        | MC_RIR_WAY_CH2_14<br>MC_RIR_WAY_CH2_15            |

|      |        | MC_RIR_WAY_CH2_16                                 |

|      |        | MC_RIR_WAY_CH2_17                                 |

|      |        | MC_RIR_WAY_CH2_18                                 |

|      |        | MC_RIR_WAY_CH2_19                                 |

|      |        | MC_RIR_WAY_CH2_20                                 |

|      |        | MC_RIR_WAY_CH2_21                                 |

|      |        | MC_RIR_WAY_CH2_22<br>MC_RIR_WAY_CH2_23            |

|      |        | MC_RIR_WAY_CH2_24                                 |

|      |        | MC_RIR_WAY_CH2_25                                 |

|      |        | MC_RIR_WAY_CH2_26                                 |

|      |        | MC_RIR_WAY_CH2_27                                 |

|      |        | MC_RIR_WAY_CH2_28                                 |

|      |        | MC_RIR_WAY_CH2_29                                 |

|      |        | MC_RIR_WAY_CH2_30<br>MC_RIR_WAY_CH2_31117         |

| 2.18 | Memory | Thermal Control                                   |

| 2.10 | 2.18.1 | MC THERMAL CONTROLO                               |

|      | 2.10.1 | MC_THERMAL_CONTROL1                               |

|      |        | MC_THERMAL_CONTROL2                               |

|      | 2.18.2 | MC_THERMAL_STATUS0                                |

|      |        | MC_THERMAL_STATUS1                                |

|      |        | MC_THERMAL_STATUS2                                |

|      | 2.18.3 | MC_THERMAL_DEFEATURE0                             |

|      |        | MC_THERMAL_DEFEATURE1<br>MC_THERMAL_DEFEATURE2    |

|      | 2.18.4 | MC_THERMAL_PARAMS_A0                              |

|      | 2      | MC_THERMAL_PARAMS_A1                              |

|      |        | MC_THERMAL_PARAMS_A2119                           |

|      | 2.18.5 | MC_THERMAL_PARAMS_B0                              |

|      |        | MC_THERMAL_PARAMS_B1                              |

|      | 0.40.4 | MC_THERMAL_PARAMS_B2                              |

|      | 2.18.6 | MC_COOLING_COEF0<br>MC_COOLING_COEF1              |

|      |        | MC_COOLING_COEF2                                  |

|      | 2.18.7 | MC_CLOSED_LOOP0                                   |

|      | 2.10.7 | MC_CLOSED_LOOP1                                   |

|      |        | MC_CLOSED_LOOP2121                                |

|      | 2.18.8 | MC_THROTTLE_OFFSET0                               |

|      |        | MC_THROTTLE_OFFSET1                               |

|      | 0.46.5 | MC_THROTTLE_OFFSET2                               |

|      | 2.18.9 | MC_RANK_VIRTUAL_TEMP0                             |

|      |        | MC_RANK_VIRTUAL_TEMP1<br>MC_RANK_VIRTUAL_TEMP2122 |

|      |        |                                                   |

|   |      | 2.18.10   | MC_DDR_THERM_COMMAND0<br>MC_DDR_THERM_COMMAND1<br>MC_DDR_THERM_COMMAND2 | 122 |

|---|------|-----------|-------------------------------------------------------------------------|-----|

|   |      | 2.18.11   | MC_DDR_THERM_STATUS0<br>MC_DDR_THERM_STATUS1<br>MC_DDR_THERM_STATUS2    | 123 |

|   | 2.19 | Integrat  | ted Memory Controller Miscellaneous Registers                           | 123 |

|   |      | 2.19.1    | MC_DIMM_CLK_RATIO_STATUS                                                | 123 |

|   |      | 2.19.2    | MC_DIMM_CLK_RATIO                                                       | 124 |

| 3 | DIM  | /I Popula | ition Requirements                                                      | 125 |

|   | 3.1  | General   | Population Requirements                                                 | 125 |

|   | 3.2  | Populati  | ing DIMMs Within a Channel                                              | 126 |

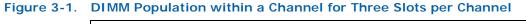

|   |      |           | DIMM Population for Three Slots per Channel                             |     |

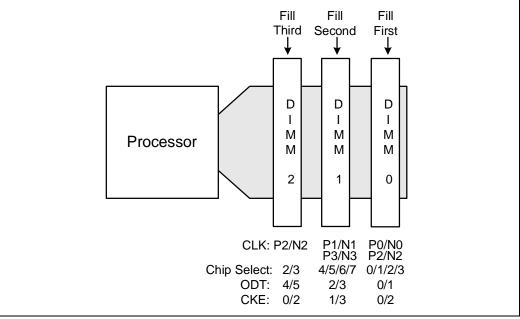

|   |      | 3.2.2     | DIMM Population for Two Slots per Channel                               | 128 |

## **Tables**

| 1-1  | References                                                                                | . 17 |

|------|-------------------------------------------------------------------------------------------|------|

| 2-1  | Functions Specifically Handled by the Processor                                           | . 22 |

| 2-2  | Device 0, Function 0: Generic Non-core Registers                                          | . 23 |

| 2-3  | Device 0, Function 1: System Address Decoder Registers                                    | . 24 |

| 2-4  | Device 2, Function 0: Intel QPI Link 0 Registers                                          | . 25 |

| 2-5  | Device 2, Function 1: Intel QPI Physical 0 Registers                                      | . 26 |

| 2-6  | Device 2, Function 4: Intel QPI Link 1 Registers1                                         | . 27 |

| 2-7  | Device 2, Function 5: Intel QPI Physical 1 Registers                                      | . 28 |

| 2-8  | Device 3, Function 0: Integrated Memory Controller Registers                              | . 29 |

| 2-9  | Device 3, Function 1: Target Address Decoder Registers                                    | . 30 |

| 2-10 | Device 3, Function 2: Integrated Memory Controller RAS Registers                          | . 31 |

| 2-11 | Device 3, Function 4: Integrated Memory Controller Test Registers                         | . 32 |

| 2-12 | Device 4, Function 0: Integrated Memory Controller Channel 0                              |      |

|      | Control Registers                                                                         | . 33 |

| 2-13 | Device 4, Function 1: Integrated Memory Controller Channel 0                              |      |

|      | Address Registers                                                                         | . 34 |

| 2-14 | Device 4, Function 2: Integrated Memory Controller Channel 0                              |      |

| 0.45 | Rank Registers                                                                            | . 35 |

| 2-15 | Device 4, Function 3: Integrated Memory Controller Channel 0<br>Thermal Control Registers | 24   |

| 2-16 | Device 5, Function 0: Integrated Memory Controller Channel 1                              | . 30 |

| 2-10 | Control Registers                                                                         | 27   |

| 2-17 | Device 5, Function 1: Integrated Memory Controller Channel 1                              | . 57 |

| 2-17 | Address Registers                                                                         | 38   |

| 2-18 | Device 5, Function 2: Integrated Memory Controller Channel 1                              |      |

| 2.0  | Rank Registers                                                                            | . 39 |

| 2-19 | Device 5, Function 3: Integrated Memory Controller Channel 1                              |      |

|      | Thermal Control Registers                                                                 | . 40 |

| 2-20 | Device 6, Function 0: Integrated Memory Controller Channel 2                              |      |

|      | Control Registers                                                                         | . 41 |

| 2-21 | Device 6, Function 1: Integrated Memory Controller Channel 2                              |      |

|      | Address Registers                                                                         | . 42 |

| 2-22 | Device 6, Function 2: Integrated Memory Controller Channel 2                              |      |

|      | Rank Registers                                                                            | . 43 |

| 2-23 | Device 6, Function 3: Integrated Memory Controller Channel 2                              |      |

|      | Thermal Control Registers                                                                 | . 44 |

| 3-1 | Key Parameters for DIMM Configurations                                        |

|-----|-------------------------------------------------------------------------------|

| 3-2 | RDIMM Population Configurations within a Channel for Three Slots              |

|     | per Channel                                                                   |

| 3-3 | UDIMM Population Configurations within a Channel for Three Slots              |

|     | per Channel                                                                   |

| 3-4 | MetaSDRAM* R-DIMM Population Configurations within a Channel for              |

|     | Three Slots per Channel                                                       |

| 3-5 | RDIMM Population Configurations Within a Channel for                          |

|     | Two Slots per Channel129                                                      |

| 3-6 | UDIMM Population Configurations within a Channel for Two Slots per Channel129 |

| 3-7 | MetaSDRAM R-DIMM Population Configurations within a Channel for               |

|     | Two Slots per Channel                                                         |

|     |                                                                               |

## Figures

| 3-1 | DIMM Population within a Channel for Three Slots per Channel1 | 26 |

|-----|---------------------------------------------------------------|----|

| 3-2 | DIMM Population Within a Channel for Two Slots per Channel1   | 28 |

## **Revision History**

| Reference<br>Number | Revision<br>Number | Description                                    | Date       |

|---------------------|--------------------|------------------------------------------------|------------|

| 321322              | 001                | Public release                                 | March 2009 |

| 321322              | 002                | Added Chapter 3 "DIMM Population Requirements" | April 2009 |

| 1 | - |

|---|---|

| ( |   |

| • | - |

# **1** Introduction

The Intel® Xeon® Processor 5500 Series is the first generation DP server/workstation processor to implement key new technologies:

- Integrated Memory Controller

- Point-to-point link interface based on Intel® QuickPath Interconnect (Intel® QPI). Reference to this interface may sometimes be abbreviated with Intel QPI throughout this document.

The processor is optimized for performance with the power efficiencies of a low-power microarchitecture to enable smaller, quieter systems.

This document provides register documentation and functional description of major functional areas of the processor non-core design such as the memory controller and Intel QPI logic, and additional features pertinent to implementation and operation of the processor.

The Intel Xeon Processor 5500 Series are multi-core processors, based on 45 nm process technology. Processor features vary by SKU and include up to two Intel QuickPath Interconnect point to point links capable of up to 6.4 GT/s, up to 8 MB of shared cache, and an integrated memory controller. The processors support all the existing Streaming SIMD Extensions 2 (SSE2), Streaming SIMD Extensions 3 (SSE3) and Streaming SIMD Extensions 4 (SSE4). The processor supports several Advanced Technologies: Execute Disable Bit, Intel<sup>®</sup> 64 Technology, Enhanced Intel<sup>®</sup> SpeedStep Technology, Intel<sup>®</sup> Virtualization Technology (Intel<sup>®</sup> VT), and Intel<sup>®</sup> Hyper-Threading Technology.

## 1.1 Terminology

A '#' symbol after a signal name refers to an active low signal, indicating a signal is in the active state when driven to a low level. For example, when RESET# is low, a reset has been requested.

#### 1.1.1 Processor Terminology

Commonly used terms are explained here for clarification:

- **DDR3** Double Data Rate 3 synchronous dynamic random access memory (SDRAM) is the name of the new DDR memory standard that is being developed as the successor to DDR2 SDRAM.

- Enhanced Intel SpeedStep<sup>®</sup> Technology Enhanced Intel SpeedStep Technology allows trade-offs to be made between performance and power consumption.

- Execute Disable Bit Execute Disable allows memory to be marked as executable or non-executable, when combined with a supporting operating system. If code attempts to run in non-executable memory the processor raises an error to the operating system. This feature can prevent some classes of viruses or worms that exploit buffer over run vulnerabilities and can thus help improve the overall security of the system. See the *Intel® 64 and IA-32 Architectures Software Developer's Manual* for more detailed information. Refer to http://developer.intel.com/ for future reference on up to date nomenclatures.

- **Eye Definitions** The eye at any point along the data channel is defined to be the creation of overlapping of a large number of Unit Interval of the data signal and timing width measured with respect to the edges of a separate clock signal at any other point. Each differential signal pair by combining the D+ and D- signals produces a signal eye.

- 1366-land LGA package The processor is available in a Land Grid Array (LGA) package, consisting of the processor die mounted on a land grid array substrate with an integrated heat spreader (IHS).

- Functional Operation Refers to the normal operating conditions in which all processor specifications, including DC, AC, system bus, signal quality, mechanical, and thermal, are satisfied.

- Integrated Memory Controller (IMC) A memory controller that is integrated in the processor silicon.

- Integrated Heat Spreader (IHS) A component of the processor package used to enhance the thermal performance of the package. Component thermal solutions interface with the processor at the IHS surface.

- Intel<sup>®</sup> 64 Architecture An enhancement to Intel's IA-32 architecture, allowing the processor to execute operating systems and applications written to take advantage of Intel 64. Further details on Intel 64 architecture and programming model can be found at http://developer.intel.com/technology/intel64/.

- Intel<sup>®</sup> QuickPath Interconnect A cache-coherent, link-based interconnect specification for Intel processor, chipset, and I/O bridge components. Sometimes abbreviated as Intel QPI.

- Intel® QPI Abbreviation for Intel® QuickPath Interconnect.

- Intel<sup>®</sup> Virtualization Technology (Intel<sup>®</sup> VT) A set of hardware enhancements to Intel server and client platforms that can improve virtualization solutions. Intel VT provides a foundation for widely-deployed virtualization solutions and enables more robust hardware assisted virtualization solutions. More information can be found at: http://www.intel.com/technology/virtualization/

- **Jitter** Any timing variation of a transition edge or edges from the defined Unit Interval.

- LGA1366 Socket The processor (in the LGA-1366 package) mates with the system board through this surface mount, 1366-contact socket.

- **Mirror Port** Pads located on the top side of the processor package used to provide logic analyzer probing access for Intel QPI signal analysis.

- **Non-core** The portion of the processor comprising the shared cache, IMC and Intel QPI Link interface.

- **OEM** Original Equipment Manufacturer.

- Storage Conditions Refers to a non-operational state. The processor may be installed in a platform, in a tray, or loose. Processors may be sealed in packaging or exposed to free air. Under these conditions, processor lands should not be connected to any supply voltages, have any I/Os biased, or receive any clocks.

- Intel Xeon Processor 5500 Series The 2S server/workstation product, including processor substrate and integrated heat spreader (IHS).

• Unit Interval (UI) — Signaling convention that is binary and unidirectional. In this binary signaling, one bit is sent for every edge of the forwarded clock, whether it be a rising edge or a falling edge. If a number of edges are collected at instances t<sub>1</sub>, t<sub>2</sub>, t<sub>n</sub>,..., t<sub>k</sub> then the UI at instance "n" is defined as:

$$UI_{n} = t_{n} - t_{n-1}$$

### 1.2 References

Material and concepts available in the following documents may be beneficial when reading this document:

#### Table 1-1. References

| Document                                                                                                                                                                                                    | Reference #                          | Notes |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|

| Intel® 64 and IA-32 Architectures Software Developer's Manual                                                                                                                                               |                                      | 1     |

| <ul> <li>Volume 1: Basic Architecture</li> <li>Volume 2A: Instruction Set Reference, A-M</li> <li>Volume 2B: Instruction Set Reference, N-Z</li> <li>Volume 3A: System Programming Guide, Part 1</li> </ul> | 253665<br>253666<br>253667<br>253668 |       |

| Volume 3B: Systems Programming Guide, Part 2                                                                                                                                                                | 253669                               |       |

| Intel® 64 and IA-32 Architectures Optimization Reference Manual                                                                                                                                             | 248966                               | 1     |

| Intel® Xeon® Processor 5500 Series Specification Update                                                                                                                                                     | 321324                               | 1     |

| Intel® Xeon® Processor 5500 Series Datasheet, Volume 1                                                                                                                                                      | 321321                               | 1     |

Notes:

1. Document is available publicly at http://www.intel.com.

§

# **2** Register Description

The processor supports PCI configuration space accesses using the mechanism denoted as Configuration Mechanism in the PCI specification as defined in the *PCI Local Bus Specification*, as well as the PCI Express enhanced configuration mechanism as specified in the *PCI Express Base Specification*. All the registers are organized by bus, device, function, etc. as defined in the *PCI Express Base Specification*. All processor registers appear on the PCI bus assigned for the processor socket. Bus number is derived by the max bus range setting and processor socket number. All multi-byte numeric fields use "little-endian" ordering (i.e., lower addresses contain the least significant parts of the field).

As processor features vary by SKU, not all of the register descriptions in this document apply to all processors. This document highlights registers which do not apply to all processor SKUs. Refer to the particular processor's Specification Update for a list of features supported.

## 2.1 Register Terminology

Registers and register bits are assigned one or more of the following attributes. These attributes define the behavior of register and the bit(s) that are contained with in. All bits are set to default values by hard reset. Sticky bits retain their states between hard resets.

| Term | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO   | <b>Read Only</b> . If a register bit is read only, the hardware sets its state. The bit may be read by software. Writes to this bit have no effect.                                                                                                                                                                                                                                                                                                     |

| WO   | Write Only. The register bit is not implemented as a bit. The write causes some hardware event to take place.                                                                                                                                                                                                                                                                                                                                           |

| RW   | Read/Write. A register bit with this attribute can be read and written by software.                                                                                                                                                                                                                                                                                                                                                                     |

| RC   | Read Clear: The bit or bits can be read by software, but the act of reading causes the value to be cleared.                                                                                                                                                                                                                                                                                                                                             |

| RCW  | <b>Read Clear/Write:</b> A register bit with this attribute will get cleared after the read. The register bit can be written.                                                                                                                                                                                                                                                                                                                           |

| RW1C | Read/Write 1 Clear. A register bit with this attribute can be read or cleared by software.<br>In order to clear this bit, a one must be written to it. Writing a zero will have no effect.                                                                                                                                                                                                                                                              |

| RWOC | Read/Write O Clear. A register bit with this attribute can be read or cleared by software.<br>In order to clear this bit, a zero must be written to it. Writing a one will have no effect.                                                                                                                                                                                                                                                              |

| RW1S | <b>Read/Write 1 Set:</b> A register bit can be either read or set by software. In order to set this bit, a one must be written to it. Writing a zero to this bit has no effect. Hardware will clear this bit.                                                                                                                                                                                                                                           |

| RWOS | <b>Read/Write 0 Set:</b> A register bit can be either read or set by software. In order to set this bit, a zero must be written to it. Writing a one to this bit has no effect. Hardware will clear this bit.                                                                                                                                                                                                                                           |

| RWL  | <b>Read/Write/Lock</b> . A register bit with this attribute can be read or written by software.<br>Hardware or a configuration bit can lock the bit and prevent it from being updated.                                                                                                                                                                                                                                                                  |

| RWO  | <b>Read/Write Once.</b> A register bit with this attribute can be written to only once after power up. After the first write, the bit becomes read only. This attribute is applied on a bit by bit basis. For example, if the RWO attribute is applied to a 2 bit field, and only one bit is written, then the written bit cannot be rewritten (unless reset). The unwritten bit, of the field, may still be written once. This is special case of RWL. |

| RRW  | <b>Read/Restricted Write.</b> This bit can be read and written by software. However, only supported values will be written. Writes of non supported values will have no effect.                                                                                                                                                                                                                                                                         |

| L    | Lock. A register bit with this attribute becomes Read Only after a lock bit is set.                                                                                                                                                                                                                                                                                                                                                                     |

| Term                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSVD                                         | <b>Reserved Bit.</b> This bit is reserved for future expansion and must not be written. The <i>PCI Local Bus Specification</i> requires that reserved bits must be preserved. Any software that modifies a register that contains a reserved bit is responsible for reading the register, modifying the desired bits, and writing back the result.                                                                                                                                                                                                                                                                                                                                                 |

| Reserved Bits                                | Some of the processor registers described in this section contain reserved bits. These bits are labeled "Reserved". Software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back. Note that software does not need to perform a read-merge-write operation for the Configuration Address (CONFIG_ADDRESS) register.         |

| Reserved<br>Registers                        | In addition to reserved bits within a register, the processor contains address locations in the configuration space that are marked either "Reserved" or "Intel Reserved". The processor responds to accesses to "Reserved" address locations by completing the host cycle. When a "Reserved" register location is read, a zero value is returned. ("Reserved" registers can be 8, 16, or 32 bits in size). Writes to "Reserved" registers have no effect on the processor. Registers that are marked as "Intel Reserved" must not be modified by system software. Writes to "Intel Reserved" registers may cause system failure. Reads to "Intel Reserved" registers may return a non-zero value. |

| Default Value<br>upon a Reset                | Upon a reset, the processor sets all of its internal configuration registers to predetermined default states. Some register values at reset are determined by external strapping options. The default state represents the minimum functionality feature set required to successfully bring up the system. Hence, it does not represent the optimal system configuration. It is the responsibility of the system initialization software (usually BIOS) to properly determine the DRAM configurations, operating parameters and optional system features that are applicable, and to program the processor registers accordingly.                                                                  |

| "ST" appended to<br>the end of a bit<br>name | The bit is "sticky" or unchanged by a hard reset. These bits can only be cleared by a PWRGOOD reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## 2.2 Platform Configuration Structure

The processor contains 6 PCI devices within a single physical component. The configuration registers for these devices are mapped as devices residing on the PCI bus assigned for the processor socket. Bus number is derived by the max bus range setting and processor socket number.

- Device 0: Generic processor non-core. Device 0, Function 0 contains the generic non-core configuration registers for the processor and resides at DID (Device ID) of 2C40h. Device 0, Function 1 contains the System Address Decode registers and resides at DID of 2C01h.

- Device 2: Intel QPI. Device 2, Function 0 contains the Intel® QuickPath Interconnect configuration registers for Intel QPI Link 0 and resides at DID of 2C10h. Device 2, Function 1 contains the physical layer registers for Intel QPI Link 0 and resides at DID of 2C11h. Device 2, Function 4 contains the Intel® QuickPath configuration registers for Intel® QuickPath Interconnect Link 1 and resides at DID of 2C14h. Device 2, Function 5 contains the physical layer registers for Intel QPI Link 1 and resides at DID of 2C15h. Functions 4 and 5 only apply to processors with two Intel QPI links.

- **Device 3:** Integrated Memory Controller. Device 3, Function 0 contains the general registers for the Integrated Memory Controller and resides at DID of 2C18h. Device 3, Function 1 contains the Target Address Decode registers for the Integrated Memory Controller and resides at DID of 2C19h. Device 3, Function 2 contains the RAS registers for the Integrated Memory Controller and resides at DID of 2C19h. Device 3, Function 2 contains the Device 3, Function 4 contains the test registers for the Integrated Memory Controller and resides at DID of 2C1Ch. Function 2 only applies to processors supporting registered DIMMs.

- **Device 4:** Integrated Memory Controller Channel 0. Device 4, Function 0 contains the control registers for Integrated Memory Controller Channel 0 and resides at

DID of 2C20h. Device 4, Function 1 contains the address registers for Integrated Memory Controller Channel 0 and resides at DID of 2C21h. Device 4, Function 2 contains the rank registers for Integrated Memory Controller Channel 0 and resides at DID of 2C22h. Device 4, Function 3 contains the thermal control registers for Integrated Memory Controller Channel 0 and resides at DID of 2C23h.

- Device 5: Integrated Memory Controller Channel 1. Device 5, Function 0 contains the control registers for Integrated Memory Controller Channel 1 and resides at DID of 2C28h. Device 5, Function 1 contains the address registers for Integrated Memory Controller Channel 1 and resides at DID of 2C29h. Device 5, Function 2 contains the rank registers for Integrated Memory Controller Channel 1 and resides at DID of 2C2Ah. Device 5, Function 3 contains the thermal control registers for Integrated Memory Controller Channel 1 and resides at DID of 2C2Bh.

- Device 6: Integrated Memory Controller Channel 2. Device 6, Function 0 contains the control registers for Integrated Memory Controller Channel 2 and resides at DID of 2C30h. Device 6, Function 1 contains the address registers for Integrated Memory Controller Channel 2 and resides at DID of 2C31h. Device 6, Function 2 contains the rank registers for Integrated Memory Controller Channel 2 and resides at DID of 2C32h. Device 6, Function 3 contains the thermal control registers for Integrated Memory Controller Channel 2 and resides at DID of 2C33h.

## 2.3 Device Mapping

Each component in the processor is uniquely identified by a PCI bus address consisting of Bus Number, Device Number and Function Number. Device configuration is based on the PCI Type 0 configuration conventions. All processor registers appear on the PCI bus assigned for the processor socket. Bus number is derived by the max bus range setting and processor socket number.

| Component | Register Group                                           | DID   | Device | Function       |

|-----------|----------------------------------------------------------|-------|--------|----------------|

| Processor | Intel® QuickPath Architecture Generic Non-core Registers | 2C40h | 0      | 0              |

|           | Intel® QuickPath Architecture System Address Decoder     | 2C01h | 1      | 1              |

|           | Intel QPI Link 0                                         | 2C10h | 2      | 0              |

|           | Intel QPI Physical 0                                     | 2C11  | 1      | 1              |

|           | Intel QPI Link 1                                         | 2C14h | 1      | 4 <sup>1</sup> |

|           | Intel QPI Physical 1                                     | 2C15h | 1      | 5 <sup>1</sup> |

|           | Integrated Memory Controller Registers                   | 2C18h | 3      | 0              |

|           | Integrated Memory Controller Target Address Decoder      | 2C19h | 1      | 1              |

|           | Integrated Memory Controller RAS Registers               | 2C1Ah | 1      | 2 <sup>2</sup> |

|           | Integrated Memory Controller Test Registers              | 2C1Ch | 1      | 4              |

|           | Integrated Memory Controller Channel 0 Control           | 2C20h | 4      | 0              |

|           | Integrated Memory Controller Channel 0 Address           | 2C21h | 1      | 1              |

|           | Integrated Memory Controller Channel 0 Rank              | 2C22h | T      | 2              |

|           | Integrated Memory Controller Channel 0 Thermal Control   | 2C23h | Ī      | 3              |

|           | Integrated Memory Controller Channel 1 Control           | 2C28h | 5      | 0              |

|           | Integrated Memory Controller Channel 1 Address           | 2C29h | T      | 1              |

|           | Integrated Memory Controller Channel 1 Rank              | 2C2Ah | T      | 2              |

|           | Integrated Memory Controller Channel 1 Thermal Control   | 2C2Bh | 1      | 3              |

|           | Integrated Memory Controller Channel 2 Control           | 2C30h | 6      | 0              |

|           | Integrated Memory Controller Channel 2 Address           | 2C31h | Ţ      | 1              |

|           | Integrated Memory Controller Channel 2 Rank              | 2C32h | Ţ      | 2              |

|           | Integrated Memory Controller Channel 2 Thermal Control   | 2C33h | Ţ      | 3              |

#### Table 2-1. Functions Specifically Handled by the Processor

Notes:

Applies only to processors with two Intel QPI links.

Applies only to processors supporting mirroring and scrubbing RAS features.

## 2.4 Detailed Configuration Space Maps

| DID    | VID    | 00h         | DESIRED_CORES          | 80h         |

|--------|--------|-------------|------------------------|-------------|

| PCISTS | PCICMD | 04h         |                        | 84h         |

| CCR    | RID    | 08h         | MEMLOCK_STATUS         | 88h         |

| HDR    |        | 0Ch         |                        | 8Ch         |

|        |        | 10h         | MC_CFG_CONTROL         | 90h         |

|        |        | 14h         |                        | 94h         |

|        |        | 18h         |                        | 98h         |

|        |        | 1Ch         |                        | 9Ch         |

|        |        | 20h         |                        | A0h         |

|        |        | 24h         |                        | A4h         |

|        |        | 28h         |                        | A8h         |

| SID    | SVID   | 2Ch         |                        | ACh         |

|        |        | 30h         | POWER_CNTRL_ERR_STATUS | B0h         |

|        |        | 34h         |                        | B4h         |

|        |        | 38h         |                        | B8h         |

|        |        | 3Ch         |                        | BCh         |

| MAXREQ |        | 40h<br>44h  | CURRENT_UCLK_RATIO     | C0h<br>C4h  |

| MAXREQ |        | 4411<br>48h |                        | C4II<br>C8h |

| MAREO  |        | 4011<br>4Ch |                        | CCh         |

|        |        | 50h         | MIRROR_PORT_CTL        | D0h         |

|        |        | 54h         |                        | D4h         |

|        |        | 58h         |                        | D8h         |

|        |        | 5Ch         |                        | DCh         |

| MAX_I  | RTIDS  | 60h         | MIP_PH_CTR_L0          | EOh         |

|        |        | 64h         | MIP_PH_PRT_L0          | E4h         |

|        |        | 68h         |                        | E8h         |

|        |        | 6Ch         |                        | ECh         |

|        |        | 70h         | MIP_PH_CTR_L1          | F0h         |

|        |        | 74h         | MIP_PH_PRT_L1          | F4h         |

|        |        | 78h         |                        | F8h         |