# Wide Bandwidth, Fast-Settling Operational Amplifier

AD9611

**FEATURES**

Unity Gain Stable

Small-Signal Bandwidth 280MHz

Full Power Bandwidth 210MHz

Settling – 13ns to 0.1%

Rise/Fall Times 1.3ns/1.5ns

Offset Voltage ±0.5mV

Bias Current ±1µA

Power Dissipation Independent of Load

APPLICATIONS

Driving Flash Converters

High-Speed DACs

Radar, IF Processors

Baseband and Video Communications

Photodiode Preamps

ATE/Pulse Generators

### GENERAL DESCRIPTION

Imaging/Display Applications

The AD9611 is an ultrafast-settling, wide-bandwidth, dc-coupled operational amplifier that combines exceptional ac and dc specifications to establish a new standard of excellence in dc-coupled amplifiers.

Rise and fall times are 1.3ns and 1.5ns, respectively. The -3dB bandwidth is 280MHz (G=-5); the full-power bandwidth is 210MHz. The AD9611 settles to 0.1% in 13ns, and dc performance is also exceptional. Offset voltage is  $\pm 0.5$ mV and drifts only  $5\mu$ V/°C. The inverting and noninverting bias currents are  $1\mu$ A.

The AD9611 requires  $\pm$  5V power supplies and employs an innovative current-steering output stage that keeps the total circuit power dissipation essentially constant regardless of output drive (for loads  $\leq$ 100 $\Omega$ ). Circuit power dissipation does not increase as the load is increased; the unit can be operated up to  $+110^{\circ}$ C in still air without heat sinking.

# AD9611 FUNCTIONAL BLOCK DIAGRAM

Current feedback is used instead of voltage feedback to provide dynamic performance that is relatively independent of gain settings. Flat gain and phase response combine with excellent noise and distortion performance to provide a unity-gain-stable amplifier especially well suited for use in digital communication systems. The AD9611 is an excellent choice for driving the newest generation of ultrahigh-speed flash converters when system SNR and effective number of bits are important.

The AD9611 is constructed with discrete transistors on a precision thin-film substrate. The AD9611BH is rated for case temperatures from -25°C to +85°C; the AD9611TH is guaranteed from -55°C to +125°C. Contact the factory for information about 883 grade parts. All units are built and tested in a MIL-STD-1772-certified facility.

# **SPECIFICATIONS**

# $\begin{tabular}{ll} \textbf{DC ELECTRICAL CHARACTERISTICS} ( \pm v_s = \pm 5 v; A_v = -5; R_M = 200 \Omega; R_{FB} = 1 k \Omega; R_{LDAD} = 100 \Omega) \\ \end{tabular}$

|                                                                              | Sub-    | AD9611BH/TH<br>Typical |              | AD9611BI<br>Min/Max( |                |            | AD%11'<br>Min/Ma |                |              |

|------------------------------------------------------------------------------|---------|------------------------|--------------|----------------------|----------------|------------|------------------|----------------|--------------|

| Parameter (Conditions)                                                       | Group   | @+25°C                 | −25°C        | + 25°C               | + 85℃          | −55°C      | + 25°C           | + 125℃         | Units        |

| / Offset Voltage                                                             | 1,2,3   | ±0.5                   | ±5.0         | ± 3.0                | ±4.3           | ± 5.0      | ± 3.0            | ± 4.3          | mV           |

| # Offset Voltage T <sub>C</sub> <sup>3</sup>                                 | ' '     | ±5                     |              |                      |                | ± 20       |                  | ± 20           | μV/°C        |

| / Input Bias Current                                                         |         |                        | l            |                      |                |            |                  |                | ] '          |

| Inverting                                                                    | 1,2,3   | ±1                     | ± 40         | ± 5                  | ± 19           | ± 40       | ± 5              | ±19            | μA           |

| Noninverting                                                                 | 1,2,3   | ±1                     | ± 25         | ± 5                  | ± 15           | ± 25       | ± 5              | ± 15           | μА           |

| Input Bias Current T <sub>C</sub> <sup>3</sup>                               | ļ       | ľ                      | 1            |                      |                |            |                  |                | ·            |

| # Inverting                                                                  |         | ± 140                  | 1            |                      |                | ± 275      |                  | ± 275          | nA/°C        |

| # Noninverting                                                               |         | ± 75                   | l            |                      |                | ± 175      |                  | ± 175          | nA/℃         |

| Noninverting                                                                 |         |                        | 1            |                      |                | 1          |                  |                |              |

| Impedance                                                                    |         | 150                    | l            |                      |                | l          |                  |                | kΩ           |

| Capacitance                                                                  |         | 3                      |              |                      |                | l          |                  |                | pF           |

| √ Common-Mode Input Range                                                    | 1,2,3   | ±1.5                   | ±1.4         | ± 1.4                | ±1.25          | ±1.4       | ± 1.4            | ±1.25          | v            |

| √ Internal Feedback Resistor (R <sub>FB</sub> )                              |         | 1000                   | 987/         | 990/                 | 987/           | 987/       | 990/             | 987/           | ]            |

|                                                                              |         |                        | 1013         | 1010                 | 1013           | 1013       | 1010             | 1013           | Ω            |

| # R <sub>FB</sub> Temperature Coefficient                                    |         |                        | ± 25         |                      | ± 25           | ± 25       |                  | ± 25           | ppm/℃        |

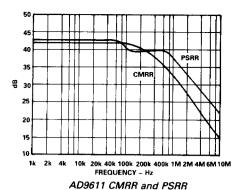

| $\sqrt{\text{Common-Mode Rejection Ratio}} (\Delta V_{CM} = 0.5 \text{V})^4$ | 4,5,6   | 42                     | ≥32          | ≥34                  | ≥32            | ≥32        | ≥34              | ≥32            | dB           |

| √ Common-Mode Sensitivity (CMS) <sup>5</sup>                                 |         |                        |              |                      |                |            |                  |                | İ            |

| Referred to Input                                                            |         |                        |              |                      |                |            |                  |                |              |

| -CMS                                                                         | 4,5,6   | 5                      | ≤24          | ≤20                  | ≤24            | ≤24        | ≤20              | ≤24            | μA/V         |

| +.CMS                                                                        | 4,5,6   | 5                      | ≤24          | ≤20                  | ≤24            | ≤24        | ≤20              | ≤24            | μA/V         |

| Output Impedance (dc to 1MHz)                                                |         | 0.03                   |              |                      |                |            |                  |                | Ω            |

| Output Impedance @ 100MHz                                                    |         | 0.4/18                 |              |                      |                | l          |                  |                | Ω/nH         |

| √ Output Voltage Swing                                                       | 1,2,3   | ±3                     | ≥ ± 2.8      | $\geq \pm 2.8$       | $\geq \pm 2.5$ | ≥ ± 2.8    | $\geq \pm 2.8$   | $\geq \pm 2.5$ | v            |

| # Output Current (continuous)                                                |         | ± 50                   | ≥ ± 40       | $\geq \pm 40$        | ≥ ± 40         | ≥ ± 40     | $\geq \pm 40$    | ≥ ± 40         | mA           |

| # Open-Loop Transimpedance Gain (100Ω Load)                                  |         | >0.35                  | ≥0.1         | ≥0.2                 | ≥0.2           | ≥0.1       | ≥0.2             | ≥0.2           | MΩ           |

| / + Supply Current(5V) <sup>6</sup>                                          | 1,2,3   | 70                     | ≤85          | ≤77                  | ≤77            | ≤85        | ≤77              | ≤77            | mA           |

| √ — Supply Current( — 5V) <sup>6</sup>                                       | 1,2,3   | 74                     | ≤88          | ≤80                  | ≲80            | ≤88        | ≤80              | ≤80            | mA           |

| Power Consumption <sup>6</sup>                                               | l       | 720                    | ≤865         | ≤785                 | ≤785           | ≤865       | ≤785             | ≤785           | mW           |

| / Power Supply Rejection Ratio $(\Delta V_S = 0.5V)^4$                       | 4,5,6   | 46                     | ≥35          | ≥37                  | ≥35            | ≥35        | ≥37              | ≥35            | dB           |

| / Power Supply Sensitivity (PSS) <sup>7</sup>                                | ' '     |                        | 1            |                      |                |            | - '              |                |              |

| Referred to Input                                                            |         |                        |              |                      |                |            |                  |                |              |

| - PSS                                                                        | 4,5,6   | 4                      | ≤17          | ≤14                  | ≤17            | ≤17        | ≤14              | ≤17            | μA/V         |

| + PSS                                                                        | 4,5,6   | 1 4                    | ≤17<br>≤17   | ≤14<br>≤14           | ≤17<br>≤17     | ≤17<br>≤17 | ≥14<br>≤14       | ≤17<br>≤17     | μΑ/V<br>μΑ/V |

| 1100                                                                         | 7, 2, 0 | L -                    | <u> </u> -1/ | ->14                 | ⇒1/            | ≥1/        | ≃14              | ⇒1/            | μην ν        |

# AC ELECTRICAL CHARACTERISTICS ( $\pm$ V<sub>S</sub> = $\pm$ 5V; A<sub>V</sub> = - 5; R<sub>MV</sub> = 200 $\Omega$ ; R<sub>EB</sub> = 1k $\Omega$ ; R<sub>LOAD</sub> = 100 $\Omega$ unless otherwise specified)

| $ \begin{tabular}{ll} \hline $V$ & Bandwidth ($-3dB$) ($V_{OUT}=1Vp$-p) \\ & Full Power Bandwidth ($V_{OUT}=3Vp$-p) \\ & Slew Rate \\ \end{tabular} $ | 4,5,6 | >280<br>>210<br>1900 | ≥250   | ≥250   | ≥220   | ≥250   | ≥250   | ≥220   | MHz<br>MHz<br>V/μs |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|--------|--------|--------|--------|--------|--------|--------------------|

| Amplitude of Peaking:                                                                                                                                 |       |                      | 1      |        |        | ١      |        |        |                    |

| $\sqrt{\text{dc to 70MHz}(V_{OUT} = 1V p-p)}$                                                                                                         | 4,5,6 | 0                    | 0.2    | 0.2    | 0.2    | 0.2    | 0.2    | 0.2    | dB                 |

| $\sqrt{} > 70 \text{MHz} \left( V_{\text{OUT}} = 1 \text{V p-p} \right)$                                                                              | 4,5,6 | 0                    | ≤0.8   | ≤0.8   | ≤1.6   | ≤0.8   | ≤0.8   | ≤1.6   | dB                 |

| Phase Nonlinearity (dc to 120MHz)                                                                                                                     |       | 1                    |        |        |        |        |        |        | 0                  |

| # Rise Time (V <sub>OUT</sub> = 1V Step)                                                                                                              | 1     | 1.3                  | ≤1.5   | ≤1.5   | ≤1.7   | ≤1.5   | ≤1.5   | ≤1.7   | ns                 |

| # Fall Time (V <sub>OUT</sub> = 1V Step)                                                                                                              | 1     | 1.5                  | ≤1.7   | ≤1.7   | ≤1.9   | ≤1.7   | ≤1.7   | ≤1.9   | ns                 |

| # Rise Time ( $V_{OUT} = 3V \text{ Step}$ )                                                                                                           |       | 1.4                  | ≤1.6   | ≤1.8   | ≤2.1   | ≤1.6   | ≤1.8   | ≤2.1   | ns                 |

| # Fall Time (V <sub>OUT</sub> = 3V Step)                                                                                                              |       | 1.6                  | ≤2.0   | ≤2.0   | ≤2.1   | ≤2.0   | ≤2.0   | ≤2.1   | ns                 |

| # Settling Time to 1%                                                                                                                                 |       | 7                    | ≤12    | ≤12    | ≤13    | ≤12    | ≤12    | ≤13    | ns                 |

| $(V_{OUT} = 1.5V \text{ Step})$                                                                                                                       | 1     |                      |        |        |        |        |        |        |                    |

| # Settling Time to 0.1%                                                                                                                               | 1 1   | 13                   | ≤19    | ≤19    | ≤22    | ≤19    | ≤19    | ≤22    | ns                 |

| $(V_{OUT} = 3V \text{ Step; } R_L = 50\Omega)$                                                                                                        | 1 1   |                      | 1      |        |        | ]      |        |        |                    |

| Settling Time to 0.05%                                                                                                                                | 1 1   | 16                   | 1      |        |        |        |        |        | ns                 |

| $(V_{OUT} = 3V \text{ Step}; R_{I.} = 50\Omega)$                                                                                                      |       |                      | 1      |        |        |        |        |        |                    |

| # Overshoot Amplitude (V <sub>OUT</sub> = 2V Step)                                                                                                    |       | 4                    | ≤14    | ≤14    | ≤18    | ≤14    | ≤14    | ≤18    | %                  |

| Overdrive Recovery to 1%(2X; 50ns)                                                                                                                    |       |                      | 1      |        |        |        |        |        |                    |

| Positive Rail to Linear Region                                                                                                                        | 1 1   | 20                   |        |        |        |        |        |        | ns                 |

| Negative Rail to Linear Region                                                                                                                        | 1 1   | 40                   |        |        |        |        |        |        | ns                 |

| Propagation Delay                                                                                                                                     |       | 2.1                  |        |        |        | 1      |        |        | ns                 |

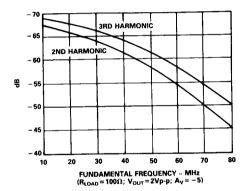

| / 2nd Harmonic Distortion                                                                                                                             | 4,5,6 | - 54                 | < - 50 | ≤ - 50 | ≤ – 42 | ≤ ~ 50 | ≤ - 50 | ≤ - 42 | dB                 |

| $(f = 60MHz; V_{OUT} = 2V p-p)$                                                                                                                       | ',',' | 5.                   | - 30   | _ >0   |        | 1 1    |        |        | ]                  |

| / 3rd Harmonic Distortion                                                                                                                             | 4,5,6 | - 58                 | ≤ - 51 | ≤ – 51 | ≤ - 44 | ≤-51   | ≤ 51   | ≤ – 44 | dВ                 |

| •                                                                                                                                                     | 7,5,0 | 56                   | 1 51   |        |        | l - '' |        |        | ""                 |

| $(f = 60MHz; V_{OUT} = 2V p-p)$                                                                                                                       | 1     |                      | 1      |        |        | ]      |        |        | 1                  |

11\_11

| Parameter                                                                                                                                                                                                                                            | Sub-<br>Group | AD%11BH/TH<br>Typical<br>@+25°C     |                    | AD9611BI<br>Min/Max(<br>+ 25°C | (a)                 | −55°C              | AD9611'<br>Min/Mar<br>+ 25°C |                     | Units                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------|--------------------|--------------------------------|---------------------|--------------------|------------------------------|---------------------|--------------------------------------------|

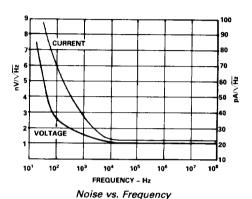

| Noise  Voltage (5MHz to 280MHz)  Current (5MHz to 280MHz)  Equivalent Integrated Input (5MHz to 280MHz)                                                                                                                                              |               | 1.0<br>21<br>75                     | ≤1.4<br>≤25<br><92 | ≤1.4<br>≤25<br>≤92             | ≤1.7<br>≤28<br>≤106 | ≤1.4<br>≤25<br>≤92 | ≤1.4<br>≤25<br>≤92           | ≤1.7<br>≤28<br>≤106 | nV/√ <u>Hz</u><br>pA/√ <del>Hz</del><br>μV |

| Other Information  Case to Ambient, $\theta_{CA}^{8,9}$ (Still Air; No Heat Sink)  Case to Ambient, $\theta_{CA}^{8,9}$ (500 LFPM Air; No Heat Sink)  MTBF (Mean Time Betwen Failures) ( $T_{CASE} = 70^{\circ}$ C; Ground Fixed; per MIL-HDBK-217D) |               | 50<br>30<br>⇒1.96 × 10 <sup>6</sup> | *                  | * *                            | * *                 | *                  | *                            | *                   | °C/W °C/W hours                            |

| PACKAGE OPTION <sup>10</sup><br>TO-8 (H-12A)                                                                                                                                                                                                         |               |                                     |                    | AD9611B                        | н                   |                    | AD9611                       | тн                  |                                            |

For applications assistance, call Computer Labs Division (at (919) 668-9511

- 100% tested (See Notes 1 and 2).

- # Specifications guaranteed by design; not tested.

- \*Specification same as AD9611BH/TH typical specification.

- <sup>1</sup>AD9611BH parameters preceded by a check (,·) are tested at +25°C ambient temperature; performance is guaranteed over the

- industrial temperature range (-25°C to +85°C) case temperature.

- <sup>2</sup>AD9611TH parameters preceded by a check (,/) are tested at -55°C case, +25°C ambient, and + 125°C case temperatures.

- <sup>3</sup>Offset voltage T<sub>C</sub> and bias current T<sub>C</sub> are guaranteed over the respective temperature ranges.

- <sup>4</sup>CMRR and PSRR apply only for stated conditions.

- <sup>5</sup>CMS values can be used to determine the CMRR for specific gain settings according to the following worst case relationships:

$$\Delta V_{OUT} = [-CMS] \{R_F] \{\Delta V_{CM}\} - [+CMS] \{R2\} \left[1 + \frac{R_F}{R1}\right] [\Delta V_{CM}]$$

$$CMRR = -20 LOG \left[\frac{\Delta V_{OUT}}{(\Delta V_{CM})}\right]$$

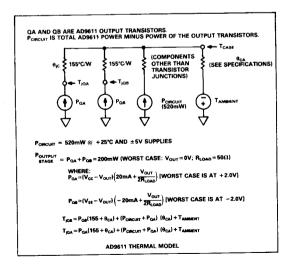

<sup>6</sup>Supply current and power dissipation numbers are for quiescent operation (V<sub>IN</sub> = 0V). A proprietary output stage assures total circuit power dissipation

does not increase as a function of output current and R<sub>1,0,0,0</sub>. (See Text)

PSS values can be used to determine the PSRR for specific gain settings according to the following worst case relationships (See diagram in 5 above):

$$\begin{split} \Delta V_{OUT} &= [-PSS] \left[ R_f \right] \left[ \Delta V_{SUPPLY} \right] - \left[ + PSS \right] \left[ R2 \right] \left[ 1 + \frac{R_f}{R1} \right] \left[ \Delta V_{SUPPLY} \right] \\ WHERE \ \Delta V_{SUPPLY} &= \Delta - V_{SUPPLY} \ OR \ \Delta + V_{SUPPLY} \\ PSRR &= -20 \ LOG \left[ \frac{\Delta V_{OUT}}{(\Delta V_{PURD NOV})} \right] \end{split}$$

<sup>8</sup>Recommended maximum junction temperature is + 165°C.

Bottom of unit raised approximately 0.125" (3.2mm) above surface of copper-clad board.

<sup>10</sup>See Section 16 for package outline information.

Specifications subject to change without notice.

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltages $(\pm V_S)$ $\pm 6V$          |

|-----------------------------------------------|

| Analog Input ≤V <sub>S</sub>                  |

| Inverting Input Sink Current                  |

| Continuous Output Current ± 50mA              |

| Operating Temperature Range (Case)            |

| AD9611BH 25°C to + 85°C                       |

| AD9611TH55°C to +125°C                        |

| Power Dissipation See Thermal Model           |

| Junction Temperature + 165°C                  |

| Storage Temperature Range65°C to +150°C       |

| Lead Temperature (soldering, 10 sec.) + 300°C |

# EXPLANATION OF GROUP A MILITARY SUBGROUPS

Subgroup 1 - Static tests at +25°C.

(10% PDA calculated against Subgroup 1 for high-rel versions)

Subgroup 2 - Static tests at maximum rated temperature. Subgroup 3 - Static tests at minimum rated temperature.

Subgroup 4 - Dynamic tests at +25°C.

Subgroup 5 - Dynamic tests at maximum rated temperature. Subgroup 6 - Dynamic tests at minimum rated temperature.

Subgroup 7 - Functional tests at +25°C.

Subgroup 8 - Functional tests at maximum and minimum

rated temperatures.

Subgroup 9 - Switching tests at +25°C.

Subgroup 10 - Switching tests at maximum rated temperatures. Subgroup 11 - Switching tests at minimum rated temperatures.

Subgroup 12 - Periodically sample tested.

### THEORY OF OPERATION

The advantages of using the transimpedance AD9611 operational amplifier instead of a conventional high-speed op amp are based on the difference in the way the two types of amplifiers operate.

The AD9611 operational amplifier uses current feedback, rather than the voltage feedback common to traditional amplifiers. Current feedback amplifiers provide significantly more bandwidth at given gain settings than traditional amplifiers do.

Both types are similar in terms of setting gain and calculating noise, but there is a major difference in the input stages when comparing current feedback (transimpedance) amplifiers and voltage feedback amplifiers.

Traditionally, conventional amplifiers have two high-impedance inputs. Within the AD9611, however, the inputs are connected across a unity gain buffer; this causes the noninverting input to be a high impedance and the inverting input to be low impedance.

Under normal operating conditions, the inverting input current is very small. The AD9611 operation is similar to a traditional amplifier in that the voltage between the input terminals and the bias currents are, ideally, zero.

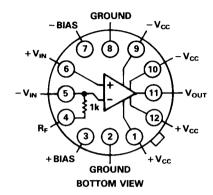

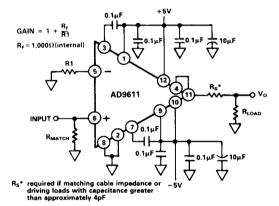

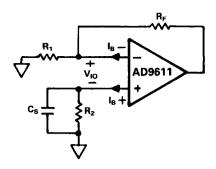

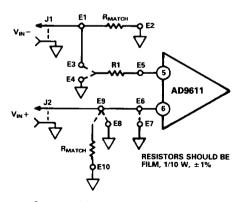

Figure 1.

Closed-loop bandwidth (CLBW) of the AD9611 is first-order independent of its closed-loop gain (G). Its transfer function can be expressed as:

$$1. \qquad \frac{V_O}{V_S} \cong \quad \frac{G}{\frac{R_F}{T(s)} \left(1 + \frac{R_N}{R1}\right) + \, 1} \label{eq:VoS}$$

where:

$R_F$  is the internal feedback resistor;  $R_F = 1k\Omega$

R1 is the gain-setting input resistor

T(s) is the transimpedance gain as a function of frequency (s) and is independent of gain-setting resistors; T(s) =  $V_O(s)I_{IN}(s)$

$G = R_F/R1$  (closed-loop gain)

$R_N$  is the open-loop input impedance (typically  $22\Omega$  in the 200MHz-300MHz band)

When closed-loop gain is greatly increased, CLBW is only slightly diminished because of the low input impedance of  $R_N$ . The ratio of CLBW for any gain to CLBW at G=-0 can be determined using the following relationship:

2.

$$\frac{\text{CLBW } (G = x)}{\text{CLBW } (G = 0)} \cong \frac{1}{\left[1 - \frac{R_N}{R_F} G\right]} = \frac{1}{(1 - 0.022G)}$$

As an example, when G=-20, the CLBW will be 70% of the CLBW when G=0 (typically 310MHz).

In the AD9611,  $R_{\rm F}$  is internal and has a value of  $1k\Omega$ ; this design helps reduce the effect of stray capacitances and makes it easier to apply the amplifier. The low input impedance at the inverting input means all of the input signal voltage is impressed across R1; this causes a direct voltage-to-current conversion to take place.

Using only the feedback resistor within the unit means the gain of the AD9611 can be set by varying only R1.

### APPLYING THE AD9611 OP AMP

In applying the AD9611 op amp, there are certain precautions which must be observed to protect the unit from damage:

- 1. Shorting either power supply input pin (Pins 9/10 or Pins 1/12) to the output (Pin 11) will destroy the device.

- 2. Shorting the output (Pin 11) to ground will destroy the device; no internal protection is included.

As noted earlier, the noninverting input of the AD9611 operational amplifier is a high impedance. This requires that it be driven from a low-impedance source, or connected to a low impedance when used in the inverting mode. Driving this input from a high impedance will reduce bandwidth. Feedback resistor  $R_F$  is internal to the AD9611 and has been precisely adjusted to allow a wide range of operating conditions. In some instances, the user may want to obtain higher closed-loop gains than those which can be achieved with only the internal feedback resistor. It is possible to use an external feedback resistor in series with the internal  $1k\Omega$   $R_F$  to achieve relatively higher gains, but bandwidth will be reduced. Table I lists typical bandwidths at G = -5 with varying amounts of feedback resistance. In this listing, the  $R_F$  which is shown is the total resistance, including the internal  $1k\Omega$ .

| Value of R <sub>F</sub> | - 3dB Bandwidth |

|-------------------------|-----------------|

| lkΩ                     | 280MHz          |

| $1.5$ k $\Omega$        | 175MHz          |

| $2k\Omega$              | 135MHz          |

| $2.5k\Omega$            | 125MHz          |

Table I

Good layout practices are always crucial to realize the full potential of the AD9611. A massive ground plane is strongly recommended. The ground plane provides a low impedance path for all power supply and signal currents, and suppresses EMI.

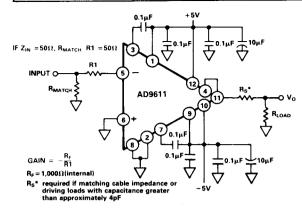

Ceramic  $0.1\mu F$  decoupling capacitors should be placed as close to the specified pins shown in Figures 2 and 3 as possible; preferably, the distance should be less than 0.1 inch. The  $(10\mu F)$  tantalum capacitors for additional decoupling of each power supply should be placed within one inch of their specified pins.

Run lengths must be kept as short as possible; if the signal path must be longer than two or three inches, use terminated coaxial cable and/or microstrip techniques. Impedance mismatches will cause signal reflections and system distortion.

Output impedance of the driving source should equal  $R_{MATCH} ||R1|$  (inverting mode) or  $R_{MATCH}$  (noninverting mode). A suggested layout is shown on the last page of this data sheet.

Parasitic capacitance associated with ZIF (and other) device sockets will severely degrade the performance of the AD9611; if sockets must be used, individual pin sockets for each lead are strongly encouraged.

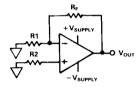

Figure 2. AD9611 Inverting Operation

Figure 3. AD9611 Noninverting Operation

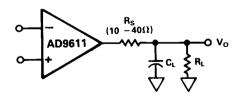

The best high-frequency performance of the AD9611 is achieved when total output capacitance  $(C_L)$  is at a minimum. Realistically, this is not always possible; but performance can be improved if a series resistor is used at the output of the amplifier, as shown in Figure 4.

Figure 4. Isolating Capacitive Loads

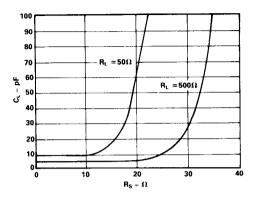

The unit will drive capacitive loads without appreciable degradation in either settling time or pulse fidelity. For driving capacitive

loads >8pF (if  $R_L=50\Omega$ ) and >4pF (if  $R_L=500\Omega$ ), isolation resistor  $R_S$  should be connected in series with the AD9611 output.

Figure 5. Output Capacitance vs. Compensation

Isolating the capacitive load from the amplifier's output is particularly useful when driving flash A/D converters.

### REDUCING OUTPUT VOLTAGE DRIFT

The expected dc error at the output of the AD9611 is a function of input offset voltage  $(V_{\rm IO})$ , and inverting and noninverting bias currents  $(I_{\rm B-}$  and  $I_{\rm B+})$ . The calculation is the same as it would be for conventional amplifiers.

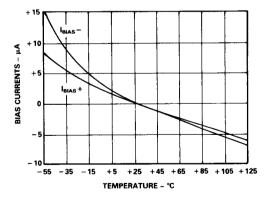

Bias currents vary inversely with temperature and typically track to within 10% of each other at high temperatures ( $+25^{\circ}$ C to  $+125^{\circ}$ C); and within 30% at low temperatures ( $-55^{\circ}$ C to  $+25^{\circ}$ C).

Figure 6. Bias Currents vs. Temperature

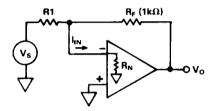

Output offset voltage drift  $(V_{OD})$  in the inverting mode can be markedly reduced, especially at high temperatures, by inserting a resistor (R2) between the noninverting input (Pin 6) and ground. This connection is shown in Figure 7.

For this configuration, output offset voltage can be determined as follows:

$$V_{O}\!=\!V_{IO}\left(1\ +\ \frac{R_{F}}{R1}\right)\ +\ I_{B+}\ (R2)\left(1\ +\ \frac{R_{F}}{R1}\right)\ -\ I_{B-}\ (R_{F})$$

where

R1 = gain-setting resistor

$R_F$  = internal feedback resistor (1k $\Omega$ )

$R2 = R1|R_F$

$C_S \ge (16,200/R2)pF$

A shunt capacitor (C<sub>S</sub>) must be connected in parallel with R2 when using this technique to maintain the amplifier's maximum bandwidth, stability, and low-noise performance. The value of the shunt is shown above.

As an example, assume the AD9611 is set up for a gain of -5; R1 should be 200 $\Omega$ ; R2 should be 167; and  $C_S$  should be 97pF. Resistor R2 reduces  $V_{\rm OD}$  by indirectly nulling the bias current drifts. The reduction in  $V_{\rm OD}$  is dramatically reduced from what

Figure 7. Reducing Offset Drift

it would be by simply grounding Pin 6. At high gain settings, the reduction in  $V_{\rm OD}$  becomes relatively less because  $V_{\rm IO}$  starts to dominate.

### **AD9611 PERFORMANCE**

The following graphs and drawings provide additional information on the performance of the AD9611 transimpedance operational amplifier. The data which are shown are based on typical characteristics.

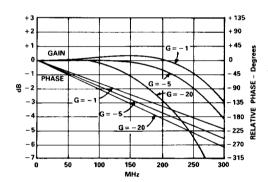

Gain and Phase vs. Frequency - Inverting

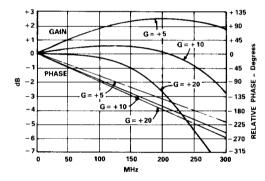

Gain and Phase vs. Frequency - Noninverting

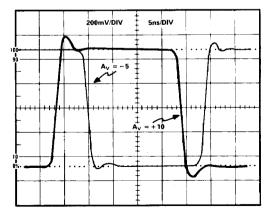

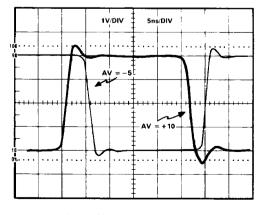

Small-Signal Pulse Response

Large-Signal Pulse Response

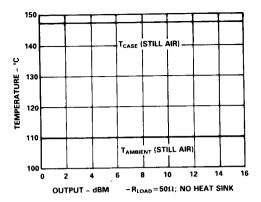

Maximum Temperatures vs. Output Power

# TEMPERATURE vs. OUTPUT POWER

The chart above illustrates an important characteristic of the AD9611 amplifier. A proprietary design feature of the output stage assures a constant case temperature regardless of the amount of output power. This is in marked contrast to most conventional amplifiers, in which increasing amounts of power raise the case temperature of the device as junction temperature increases.

This unique feature of the unit means that no heat sinking is required in still air at ambient temperatures as high as  $+110^{\circ}$ C; with air flow of 500 LFPM, the device can be operated to  $+125^{\circ}$ C before heat sinking is necessary.

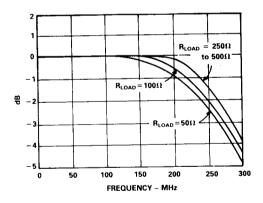

Bandwidth vs.  $R_{LOAD}$  ( $A_V = -5$ )

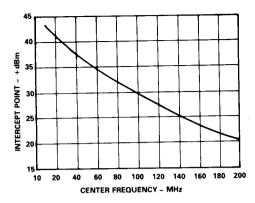

3rd Order Two-Tone Intermod Intercept (Gain = -5;  $R_{LOAD} = 50\Omega$ )

Harmonics vs. Frequency

AD9611 Thermal Model

# **AD%11 LAYOUT INFORMATION**

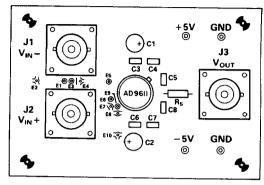

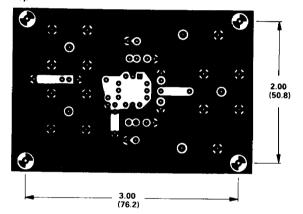

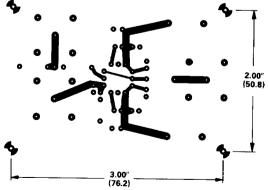

The suggested layout of the AD9611 shown below is based on the proven performance of the AD9611 Evaluation Board. The user is urged to use a similar layout when incorporating the amplifier into the system in which it will operate.

In the layout, resistors are film; 0.1W;  $\pm 1\%$ ; 50ppm. Capacitors C1 and C2 are tantalum;  $10\mu F$ ; 20%; 35V. C3 – C8 are ceramic;  $0.1\mu F$ ; 20%; 50V. Connectors J1 – J3 are Amphenol BNC type; pin sockets are available from Amp as part number 6-330808-0 (closed end) or part number 6-330808-3 (open end).

The input connections shown below are based on the layout of the evaluation board. Refer to Figure 2 (inverting operation) and Figure 3 (noninverting operation) for schematic details.

Suggested Layout Input Connections

| Operating Mode | Connect                           | Between                             |

|----------------|-----------------------------------|-------------------------------------|

| Inverting      | R <sub>MATCH</sub><br>R1<br>Strap | E1 and E2<br>E3 and E5<br>E6 and E7 |

|                | Strap                             | E8 and E9                           |

| Noninverting   | R1<br>R <sub>match</sub>          | E4 and E5<br>E9 and E10             |

Table II.

AD9611 Suggested Layout Component Side, Viewed from Top

AD9611 Suggested Layout Component Side (Top) Viewed from Top

AD9611 Suggested Layout Solder Side (Bottom) Viewed from Top