## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# BIPOLAR ANALOG INTEGRATED CIRCUIT $\mu PC1909$

### SWITCHING REGULATOR CONTROL IC

#### DESCRIPTION

The  $\mu$ PC1909 is a switching regulator control IC ideal for primary side control of active-clamp type<sup>Note</sup> DC/DC converters. This IC has 2 outputs employing a totem-pole circuit with peak output current 1.2 A, and is capable of directly driving a power MOS FET. As a result, it has been possible to realize primary side control of an active-clamp type converter on a single chip.

**Note** It is necessary to obtain license from Vicor Corporation before using the  $\mu$ PC1909 in an active-clamp type circuit.

#### **FEATURES**

- 2 on-chip outputs; for Q and Q

- · Capable of directly driving a power MOS FET

- Drive supply voltage range: 7 to 24 V

- · On-chip remote control circuit

- On-chip pulse-by-pulse overcurrent protection circuit

- · On-chip overvoltage latch circuit

#### **ORDERING INFORMATION**

| Part Number Package |                                    |  |

|---------------------|------------------------------------|--|

| μPC1909CX           | 16-pin plastic DIP (7.62 mm (300)) |  |

| μPC1909GS           | 16-pin plastic SOP (7.62 mm (300)) |  |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

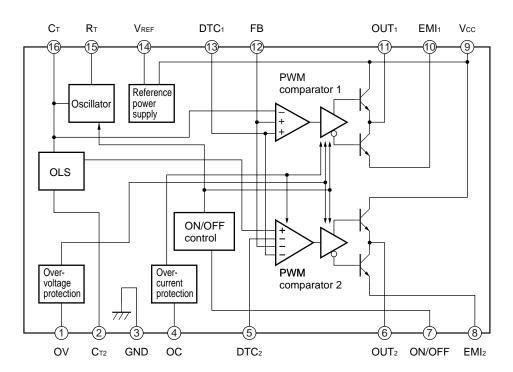

#### **★ BLOCK DIAGRAM**

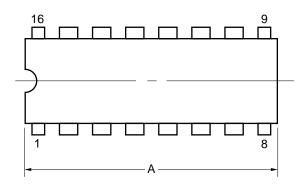

#### PIN CONFIGURATION (Top View)

16-pin plastic DIP (7.62 mm (300))  $\mu$ PC1909CX

16-pin plastic SOP (7.62 mm (300))  $\mu$ PC1909GS

#### **★** Pin Name

C<sub>T</sub> : Timing Capacitance C<sub>T2</sub> : OLS Shift Control

DTC<sub>1</sub> : OUT<sub>1</sub> Dead Time Control

DTC<sub>2</sub> : OUT<sub>2</sub> Dead Time Control

EMI1 : OUT1 EmitterEMI2 : OUT2 EmitterFB : Feedback Input

GND : Ground

OC : Over Current Protection

ON/OFF : ON/OFF Control

OUT1 : OUT1 Output

OUT2 : OUT2 Output

OV : Over Voltage Protection

R<sub>T</sub> : Timing Resistance

Vcc : Power Supply

VREF : Reference Voltage

3

### **CONTENTS**

| 1. PIN FUNCTION LIST                                                     | 5           |

|--------------------------------------------------------------------------|-------------|

| 2. ELECTRICAL SPECIFICATIONS                                             | 6           |

| ★ 3. OPERATION OVERVIEW                                                  | 11          |

| 3.1 Startup                                                              | 11          |

| 3.2 Steady Operation                                                     | 13          |

| 3.3 Overcurrent Limitation Operation                                     | 15          |

| 3.4 On/Off Operation                                                     | 16          |

| 3.5 Overvoltage Protection Operation                                     | 17          |

| ★ 4. SETTINGS                                                            | 18          |

| 4.1 Controller Settings                                                  | 18          |

| 4.2 Startup Circuit, Low Voltage Malfunction Prevention Circuit Settings | 18          |

| 4.3 Oscillator Settings                                                  | 21          |

| 4.4 Dead Time Setting                                                    | 22          |

| 4.4.1 Level shift setting                                                | 22          |

| 4.4.2 Dead time adjustment                                               | 24          |

| 4.5 Duty Settings                                                        | 25          |

| 4.5.1 Maximum duty setting                                               | 25          |

| 4.5.2 Minimum duty limit                                                 | 25          |

| 4.5.3 Soft start                                                         | 25          |

| 4.6 Remote Control                                                       | 26          |

| 4.7 Overcurrent Limiter Settings                                         | 27          |

| 4.8 Overvoltage Protection Circuit Setting                               | 28          |

| 4.9 Output Circuit                                                       | 29          |

| 4.7 Overcurrent Limiter Settings                                         | 2<br>2<br>2 |

### **★ 1. PIN FUNCTION LIST**

| Pin No. | Symbol           | Function                                                                                                                                                                                             |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OV               | Overvoltage protection  This is the input pin of the overvoltage detection comparator. Directly connect this pin to GND when not used.                                                               |

| 2       | Ст2              | OLS shift setting  The resistor that determines the amount of level shift for $dC_T$ (an internal triangle wave that is a level-shifted $C_T$ ) is connected between this pin and the $V_{REF}$ pin. |

| 3       | GND              | Ground This is the signal ground pin.                                                                                                                                                                |

| 4       | ос               | Overcurrent protection  This is the input pin of the overcurrent detection comparator. Directly connect this pin to GND when not used.                                                               |

| 5       | DTC <sub>2</sub> | OUT <sub>2</sub> dead time setting This pins sets the dead time of the OUT <sub>2</sub> output.                                                                                                      |

| 6       | OUT <sub>2</sub> | OUT <sub>2</sub> output  This is the subswitch drive output pin.                                                                                                                                     |

| 7       | ON/OFF           | ON/OFF control  The output circuit can be switched on or off by inputting an external signal.  Directly connect this pin to V <sub>REF</sub> when not used.                                          |

| 8       | EMI <sub>2</sub> | OUT <sub>2</sub> emitter  This is a power supply ground pin. This pin must be isolated from the signal ground pin (GND).                                                                             |

| 9       | Vcc              | Power supply                                                                                                                                                                                         |

| 10      | EMI <sub>1</sub> | OUT <sub>1</sub> emitter  This is a power supply ground pin. This pin must be isolated from the signal ground pin (GND).                                                                             |

| 11      | OUT <sub>1</sub> | OUT₁ output  This is the main switch drive output pin.                                                                                                                                               |

| 12      | FB               | Feedback input This is the feedback input pin of PWM comparators 1 and 2.                                                                                                                            |

| 13      | DTC <sub>1</sub> | OUT <sub>1</sub> dead time setting  This pin sets the maximum duty of the OUT <sub>1</sub> output and determines the minimum duty of the OUT <sub>2</sub> output.                                    |

| 14      | VREF             | Reference voltage This pin outputs a 4.9-V TYP. reference voltage.                                                                                                                                   |

| 15      | Rт               | Timing resistance  The resistor that determines the oscillation frequency is connected between this pin and GND.                                                                                     |

| 16      | Ст               | Timing capacitance  The capacitor that determines the oscillation frequency is connected between this pin and GND.  This pin outputs a triangle wave.                                                |

5

#### 2. ELECTRICAL SPECIFICATIONS

Absolute Maximum Ratings (Unless otherwise specified, T<sub>A</sub> = 25°C)

| Parameter                         | Symbol           | μPC1909CX   | μPC1909GS | Unit |  |

|-----------------------------------|------------------|-------------|-----------|------|--|

| Power Supply Voltage              | Vcc              | 2           | 26        |      |  |

| Output Current (DC, per output)   | Ic (DC)          | 10          | 100       |      |  |

| Output Current (peak, per output) | IC (peak)        | 1.2         |           | Α    |  |

| Total Power Dissipation           | Рт               | 1000 694    |           | mW   |  |

| Operating Ambient Temperature     | TA               | -20 to +85  |           | °C   |  |

| Operating Junction Temperature    | TJ               | −20 to +150 |           | °C   |  |

| Storage Temperature               | T <sub>stg</sub> | –55 to      | +150      | °C   |  |

#### Caution

Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

#### **Recommended Operating Conditions**

|   | Parameter                      | Symbol | MIN. | TYP. | MAX. | Unit |

|---|--------------------------------|--------|------|------|------|------|

|   | Power Supply Voltage           | Vcc    | 7    | 10   | 24   | V    |

|   | Oscillation Frequency          | fosc   | 50   | 200  | 500  | kHz  |

|   | Output Load Capacitance        | CL     |      | 2200 | 3000 | pF   |

| * | Timing Resistance              | R⊤     | 10   |      |      | kΩ   |

|   | Operating Junction Temperature | Тл     | -20  |      | +100 | °C   |

**★** Caution The recommended operating range may be exceeded without causing any problems provided that the absolute maximum ratings are not exceeded. However, if the device is operated in a way that exceeds the recommended operating conditions, the margin between the actual conditions of use and the absolute maximum ratings is small, and therefore thorough evaluation is necessary. The recommended operating conditions do not imply that the device can be used with all values at their maximum values.

### Electrical Characteristics (Unless otherwise specified, $T_A = 25$ °C, $V_{CC} = 10$ V, $R_T = 10$ k $\Omega$ , fosc = 200 kHz)

| Block                         | Parameter                                 | Symbol                    | Conditions                                         | MIN. | TYP.      | MAX.  | Unit  |

|-------------------------------|-------------------------------------------|---------------------------|----------------------------------------------------|------|-----------|-------|-------|

| Total                         | Standby Current                           | Icc (SB)                  | Vcc = 7 V                                          |      | 0.1       |       | mA    |

|                               | Circuit Current                           | Icc                       | Without load                                       | 6    | 12        | 18    | mA    |

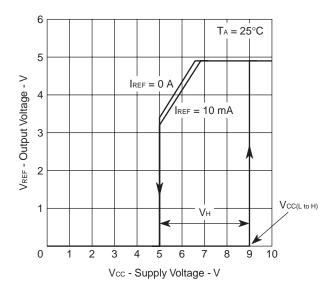

| Under-                        | Startup Threshold Voltage                 | VCC (L to H)              |                                                    | 8    | 9         | 10    | V     |

| Voltage<br>Lockout<br>Circuit | Operating Voltage Hysteresis<br>Width     | Vн                        |                                                    | 3    | 4         | 5     | V     |

| Reference                     | Output Voltage                            | VREF                      | IREF = 0 A                                         | 4.7  | 4.9       | 5.1   | V     |

| Voltage                       | Line Regulation                           | REGIN                     | 8 V ≤ Vcc ≤ 15 V,<br>IREF = 0 A                    |      | 1         | 10    | mV    |

|                               | Load Regulation                           | REG∟                      | 1 mA ≤ I <sub>REF</sub> ≤ 4 mA                     |      | 6         | 12    | mV    |

|                               | Output Voltage Temperature<br>Coefficient | $\Delta V_{REF}/\Delta T$ | $-10$ °C $\leq$ Ta $\leq$ +85°C,<br>IREF = 0 A     |      | 400       | (700) | μV/°C |

|                               | Short Circuit Current                     | IO short                  | IREF = 0 A                                         |      | 15        |       | mA    |

| Oscillation                   | Oscillation Frequency                     | fosc                      |                                                    | 180  | 200       | 220   | kHz   |

|                               | Frequency Line Regulation                 | $\Delta f/\Delta V$       | 8 V ≤ Vcc ≤ 15 V                                   |      | 1         |       | %     |

|                               | Frequency Temperature Coefficient         | $\Delta f/\Delta T$       | -10°C ≤ T <sub>A</sub> ≤ +85°C                     |      | 2         | (5)   | %     |

| PWM                           | Input Bias Current                        | B (COMP1)                 | Vcomp1 = Vref                                      |      |           | 10    | μΑ    |

| Comparator                    |                                           | B (COMP2)                 | VCOMP2 = VREF                                      |      |           | 10    | μΑ    |

|                               | Low-level Threshold Voltage               | V <sub>TH (L)</sub>       |                                                    |      | 1.5       |       | V     |

|                               | High-level Threshold Voltage              | Vтн (н)                   |                                                    |      | 3.5       |       | V     |

|                               | Dead time Temperature<br>Coeficient       | ΔDT/ΔΤ                    | $-10$ °C $\leq$ Ta $\leq$ +85°C,<br>Vd = 0.46 Vref |      | 3         |       | %     |

| Output                        | Low-level Output Voltage                  | Vol                       | Isink = 3 mA                                       |      |           | 0.5   | V     |

|                               | High-level Output Voltage                 | Vон                       | Isource = 30 mA                                    |      | Vcc - 1.6 |       | V     |

|                               | Rise Time                                 | tr                        | $R_L = 15 \Omega$ , $C_L = 2200 pF$                |      | 60        |       | ns    |

|                               | Fall Time                                 | tf                        | $R_L = 15 \Omega$ , $C_L = 2200 pF$                |      | 40        |       | ns    |

| Remote                        | Input Voltage at Output ON                | VIN (ON)                  |                                                    | 2.4  | 2.6       | 2.8   | V     |

| Control                       | Input Voltage at Output OFF               | VIN (OFF)                 |                                                    | 2.2  | 2.4       | 2.6   | V     |

|                               | Hysteresis Width                          | Vн                        |                                                    | 0.1  | 0.2       | 0.3   | V     |

| Overcurrent                   | Overcurrent Threshold Voltage             | V <sub>TH</sub> (OC)      |                                                    | 190  | 210       | 230   | mV    |

| Latch                         | Input Bias Current                        | B (OC)                    | Vcc = 0 V                                          |      | 200       |       | μΑ    |

|                               | Delay to Output                           | t <sub>d</sub> (OC)       |                                                    |      | 150       |       | ns    |

| Overvoltage                   | Overvoltage Threshold Voltage             | V <sub>TH</sub> (OV)      |                                                    | 2    | 2.4       | 2.8   | V     |

| Latch                         | Input Bias Current                        | IB (OV)                   | Vov = Vref                                         |      |           | 4     | μΑ    |

|                               | OVL Reset Voltage                         | V <sub>R</sub> (OV)       |                                                    |      | 2         |       | V     |

|                               | Delay to Output                           | t <sub>d</sub> (OV)       |                                                    |      | 750       |       | ns    |

Remark Values in parentheses ( ) represent reference values.

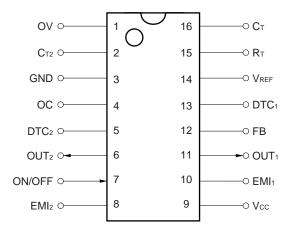

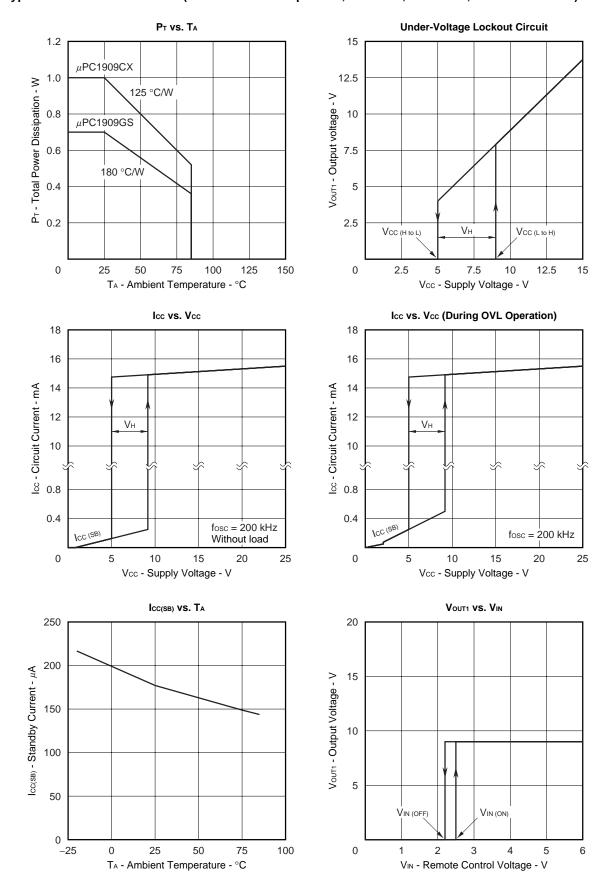

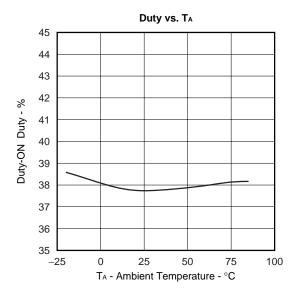

#### Typical Characteristics Curves (Unless otherwise specified, TA = 25°C, Vcc = 10 V, Reference Values)

#### **★ 3. OPERATION OVERVIEW**

#### 3.1 Startup

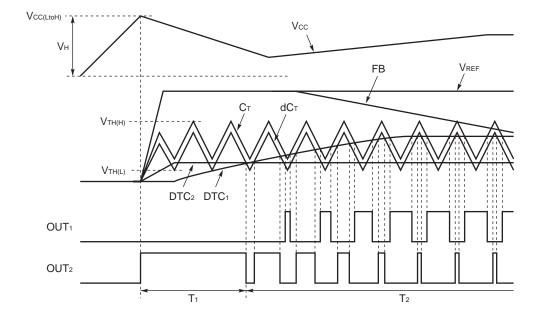

The operating waveforms at startup are shown in Figure 3-1 below. The operations at startup are as follows.

- <1> When the power supply voltage (Vcc) rises and exceeds the starting voltage (Vcc(L to H)), the reference voltage (VREF) rises.

- <2> The DTC1 voltage is boosted as the soft start capacitor is charged (refer to 4.5.3 Soft start).

- <3> Because the DTC<sub>1</sub> voltage is at a lower potential than other voltages, OUT<sub>1</sub> and OUT<sub>2</sub> become low and high level respectively during the T<sub>1</sub> period.

- <4> If the DTC<sub>1</sub> voltage is further boosted so that there is a period in which it is higher than the dC<sub>T</sub> voltage in the T<sub>2</sub> period, OUT<sub>2</sub> becomes low level. In the period in which the DTC<sub>1</sub> voltage exceeds C<sub>T</sub>, OUT<sub>1</sub> and OUT<sub>2</sub> are high and low level respectively. The duty of OUT<sub>1</sub> increases and that of OUT<sub>2</sub> decreases as DTC<sub>1</sub> is boosted.

Figure 3-1. Waveforms at Startup

11

| Signal Name      | Function                                                                    | Signal Name      | Function                                       |

|------------------|-----------------------------------------------------------------------------|------------------|------------------------------------------------|

| OUT <sub>1</sub> | Output for main switch                                                      | OUT <sub>2</sub> | Output for subswitch                           |

| DTC <sub>1</sub> | Voltage for setting maximum duty limit of OUT1                              | DTC <sub>2</sub> | Voltage for setting maximum duty limit of OUT2 |

| FB               | Feedback voltage of converter output                                        | Ст               | Triangle wave generated by oscillator          |

| dСт              | Triangle wave that is $C_T$ level-shifted via the level shift circuit (OLS) |                  |                                                |

- Remarks 1. The oscillation frequency of C<sub>T</sub> is determined by the external capacitor connected to the C<sub>T</sub> pin and the external resistor connected to the R<sub>T</sub> pin (refer to 3.3 Overcurrent Limitation Operation). C<sub>T</sub> is a symmetrical triangle wave with a trough voltage (low-level threshold voltage V<sub>TH(L)</sub>) of 1.5 V and a crest voltage (high-level threshold voltage V<sub>TH(H)</sub>) of 3.5 V. Note that the dC<sub>T</sub> voltage cannot be viewed externally.

- 2. In the T<sub>1</sub> and T<sub>2</sub> periods in Figure 3-1, the FB voltage level rises as the converter output voltage is boosted, with the result that the converter voltage cannot be controlled by FB.

#### 3.2 Steady Operation

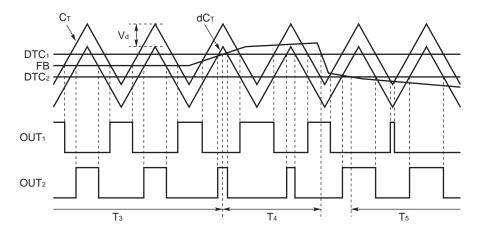

The operating waveforms during steady operation are shown in Figure 3-2 below. Steady operation as used here refers to the state in which the overcurrent and overvoltage latches are not working. The operations that occur during steady operation are as follows.

- <1> When the converter is operating at the rated input and output, the FB voltage is between DTC<sub>1</sub> and DTC<sub>2</sub> (in the T<sub>3</sub> period in Figure 3-2).

- •The FB voltage and  $C_T$  triangle wave are compared by PWM comparator 1. OUT<sub>1</sub> is high level when the FB voltage is higher than the  $C_T$  voltage.

- •The FB voltage and level-shifted dC<sub>T</sub> triangle wave are compared by PWM comparator 2. OUT<sub>2</sub> is high level when the FB voltage is lower than the dC<sub>T</sub> voltage.

- <2> Because the input voltage becomes lower as the load of the converter is increased, there is a period when the FB voltage rises and the OUT¹ duty increases (the T⁴ period in Figure 3-2).

When the FB voltage is greater than the DTC¹ voltage, OUT¹ operates at the maximum duty determined by

DTC<sub>1</sub>. At this time also, OUT<sub>2</sub> operates at the minimum duty determined by DTC<sub>1</sub>.

<3> Because the input voltage becomes higher as the load of the converter is decreased, there is a period when the FB voltage falls and the OUT¹ duty decreases (the T⁵ period in Figure 3-2).

When the FB voltage is less than the DTC² voltage, OUT² operates at the maximum duty determined by DTC².

Figure 3-2. Waveforms During Steady Operation

For the dC<sub>T</sub> level shift amount and the OUT<sub>1</sub> and OUT<sub>2</sub> dead time settings, refer to **4.4 Dead Time Setting**.

The relationship between the FB, DTC<sub>1</sub>, and DTC<sub>2</sub> voltages in each operating state and the pins that determine the duty of OUT<sub>1</sub> and OUT<sub>2</sub> are shown in Table 3-1 below. For the duty settings, refer to **4.5 Duty Settings**.

Table 3-1. Relationship Between Pins That Determine Duty During Steady Operation

| Operating Status                            |                | Voltage Relationship                     | Pin That Determines OUT <sub>1</sub> Duty | Pin That Determines OUT <sub>2</sub> Duty |

|---------------------------------------------|----------------|------------------------------------------|-------------------------------------------|-------------------------------------------|

| Steady operation 1 (rated status)           | Тз             | DTC <sub>2</sub> < FB < DTC <sub>1</sub> | FB                                        | FB                                        |

| Steady operation 2 (heavy load, low input)  | T <sub>4</sub> | DTC <sub>2</sub> < DTC <sub>1</sub> < FB | DTC <sub>1</sub>                          | DTC <sub>1</sub>                          |

| Steady operation 3 (light load, high input) | <b>T</b> 5     | FB < DTC <sub>2</sub> < DTC <sub>1</sub> | FB                                        | DTC <sub>2</sub>                          |

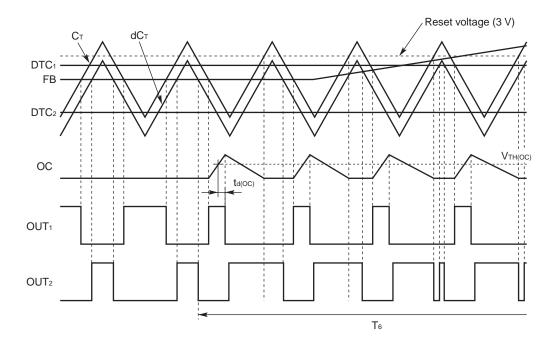

#### 3.3 Overcurrent Limitation Operation

The internal configuration of the overcurrent latch circuit is shown in Figure 3-3 below.

Overcurrent detection comparator OC 4 Flip-flop S  $\overline{\mathbb{Q}}$  To output circuit of OUT<sub>1</sub> R To PWM comparator 2

Figure 3-3. μPC1909 Overcurrent Latch Circuit

If a voltage that exceeds the overcurrent detection voltage ( $V_{TH(OC)} = 210$  mV TYP.) is input to the OC pin, OUT<sub>1</sub> is latched to low level, and then OUT<sub>2</sub> is latched to high level. The time between the detection of overcurrent and when OUT<sub>1</sub> becomes low level is the overcurrent detection delay time. Moreover, if the voltage of the C<sub>T</sub> pin exceeds 3.0 V, the reset signal will be input to the flip-flop, and the latch status of OUT<sub>1</sub> and OUT<sub>2</sub> will be reset. When the OC pin voltage reaches the overcurrent detection voltage, even in the cycle in which the latch status was reset, the latch and reset operations will be repeated. In other words, the pulse width is limited every cycle (pulse-by-pulse current limitation).

The waveforms when overcurrent limitation is operating are shown in Figure 3-4 below.

Figure 3-4. Waveforms When Overcurrent Limitation Is Operating

15

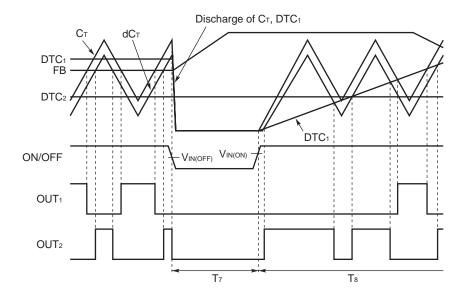

#### 3.4 On/Off Operation

The output of OUT<sub>1</sub> and OUT<sub>2</sub> can be made low level (off) by making the voltage of the ON/OFF pin low level. This also causes discharge of the soft start capacitor externally connected to the DTC<sub>1</sub> pin and the timing capacitor externally connected to the C<sub>T</sub> pin.

To prevent chattering when turning on and off slowly, the threshold voltage of the ON/OFF pin has a 0.2-V hysteresis. The waveforms during the on/off operation are shown in Figure 3-5 below.

Figure 3-5. Waveforms During On/Off Operation

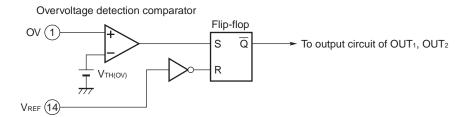

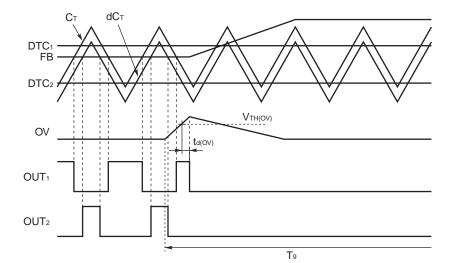

#### 3.5 Overvoltage Protection Operation

The overvoltage latch circuit is a protection circuit that stops the power supply to prevent damage to the load after detection of overvoltage caused by abnormal boosting of the output of the converter.

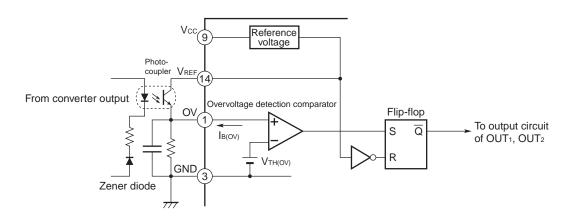

The internal configuration of the overvoltage latch circuit is shown in Figure 3-6 below.

Figure 3-6. μPC1909 Overvoltage Latch Circuit

The threshold voltage (V<sub>TH(OV)</sub>) connected to the overvoltage detection comparator is 2.0 to 2.8 V (2.4 V TYP.). If the voltage of the OV pin exceeds V<sub>TH(OV)</sub>, OUT<sub>1</sub> and OUT<sub>2</sub> are latched to low level. The waveforms when OV (overvoltage) occurs are shown in Figure 3-7 below.

To reset the status of the overvoltage latch, drop the voltage of the Vcc pin to below the OVL release voltage (VR(OV) = 2 V TYP.), and drop the voltage of the VREF pin to a sufficiently low level.

Figure 3-7. Waveforms When Overvoltage Latch Is Operating

17

#### \* 4. SETTINGS

#### 4.1 Controller Settings

The feedback circuit for when the converter output voltage is detected on the secondary side is configured as shown in Figure 4-1 below. The feedback gain is primarily determined by the R<sub>1</sub> resistor.

Figure 4-1. Feedback Circuit Configuration

The voltage of the FB pin is input to PWM comparators 1 and 2.

During steady operation ( $DTC_2 < FB < DTC_1$ ), the duty of  $OUT_1$  and  $OUT_2$  is determined by the slice level of the triangle wave based on the FB pin voltage.

Caution When using a shunt regulator such as the  $\mu$ PC1093 for the secondary-side detector,  $l_k$  must be set bearing in mind the variation of the  $C_{TR}$  in the photocoupler. Also, be sure to use the photocoupler grounded at the emitter ground.

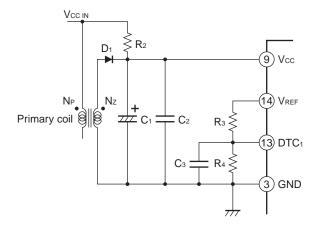

#### 4.2 Startup Circuit, Low Voltage Malfunction Prevention Circuit Settings

The startup circuit is configured as shown in Figure 4-2 below.

Figure 4-2. Startup Circuit

In the  $\mu$ PC1909, when the power supply voltage (Vcc) rises but is less than the operation start voltage (Vcc<sub>(L to H))</sub>, a current of about 100  $\mu$ A flows as a standby current.

When Vcc reaches or exceeds Vcc(L to H), the internal reference voltage (VREF) rises and operating current is supplied to the internal circuits, increasing the circuit current (Icc) to a level of about 12 mA.

In the startup circuit in Figure 4-2, Icc(SB) is supplied via a startup resistor (R<sub>2</sub>), and when the power MOS FET is turned on after the  $\mu$ PC1909 is started up, Icc is supplied from a capacitor (C<sub>1</sub>) until voltage reaches the auxiliary coil. R<sub>2</sub> is determined using Icc(SB) as follows.

$$R_2 \leq \left\{ \frac{V_{\text{IN(MIN.)}} - V_{\text{CC(LtoH)(MAX.)}}}{I_{\text{CC(SB)(MAX.)}} + I_{\text{REF}}} \right\}$$

If  $R_2$  is too small, the loss via  $R_2$  during steady operation will be large. The loss via  $R_2$  during steady operation ( $P_{L(MAX,)}$ ) is shown below. In this equation,  $N_Z$  is the number of turns in the power supply auxiliary coil,  $N_P$  is the number of turns in the primary coil, and  $V_{F(D1)}$  is the forward direction voltage drop in the diode ( $D_1$ ).

$$P_{L(MAX.)} = \frac{\left\{ \left(1 - Nz/N_P\right) \cdot V_{IN(MAX.)} + V_{F(D1)} \right\}^2}{R_2}$$

Note that a film or other capacitor (C2) with good high-frequency characteristics should be connected to prevent a high-frequency current flowing through the Vcc line when the power MOS FET is driven.

To apply a soft start, connect a soft start capacitor (C<sub>3</sub>) between the DTC<sub>1</sub> pin and GND. Using the overcurrent limitation function of the OC pin allows the duty to be limited on a pulse-by-pulse basis, enabling a more secure soft start.

The time between the startup of the  $\mu$ PC1909 and the first output of OUT<sub>1</sub> (t<sub>1</sub>) is expressed as follows.

$$t_1 = -\frac{C_3 \cdot R_3}{1 + R_3 / R_4} \ln \left\{ 1 - (1 + R_3 / R_4) \cdot (V_{TH(L)} / V_{REF}) \right\}$$

Although Vcc drops in the t<sub>1</sub> period, C<sub>1</sub> is determined so that OUT<sub>1</sub> is output while the drop voltage has not fallen to the operating voltage hysteresis width V<sub>H</sub>. At this time, because OUT<sub>2</sub> is output before OUT<sub>1</sub> (refer to **3.1 Startup**), C<sub>1</sub> must be set to compensate for the increase in current caused by the output of OUT<sub>2</sub>. Refer to Figure 3-1. Waveforms at Startup for the operating waveforms.

$$C_1 > \frac{I_{CC} + I_{REF} + I_{OUT} - I_{CC(R)}}{V_H} \cdot t_1$$

Here, IREF is the current that flows through the resistor with the maximum duty setting connected to the VREF pin, IOUT is the power MOS FET drive current, and ICC(R) is the current that is supplied from the startup resistor (R2).

Note that when the rising of VREF is later than the rising of Vcc at startup, OUT<sub>1</sub> and OUT<sub>2</sub> become high level simultaneously when VREF is in a range of about 0.45 to 0.5 V, which may result in the external power MOS FET being inadvertently turned on. To prevent this, speed up the rising of VREF by pulling it up to Vcc with a resistor. Note, however, that the standby current (Icc(SB)) will increase by only the current that flows through the connected resistor.

The pull-up resistance value (R) can be calculated from the following equation.

$$R [k\Omega] = \frac{V_{CC(MAX.)}[V] - 0.5}{0.1 [mA]}$$

Remark Vcc(MAX.): The highest power supply voltage that can be applied at startup without causing malfunction.

For the same reason, if Vcc drops below the operation stopped voltage (Vcc(L to H) - VH), VREF and the constant current circuit will be cut-off, which weakens the drive capacity of the OUT1 and OUT2 outputs when the power supply is cut-off. If this drive capacity is weakened, the charge that has accumulated at the power MOS FET gates may not be sufficiently discharged, blunting the falling section of the power MOS FET gate drive waveform. In this case, connecting a capacitor of at least 0.47  $\mu$ F between the VREF pin and GND allows sufficient time and output block drive capacity to discharge the charge accumulated at the gates of the power MOS FET.

Because the operation start and stop voltages in the  $\mu$ PC1909 are 9 V TYP. and 5 V TYP. respectively, VREF is output while operation is stopped until Vcc is 5 V or lower. However, when Vcc reaches about 6.5 V, VREF falls together with Vcc, as can be seen in Figure 4-3. When VREF falls, the constant current value of the triangle wave oscillator decreases, causing the oscillation frequency to drop.

Figure 4-3. VREF vs. Vcc Characteristics

In standard applications, VREF is resistance-divided to create the DTC<sub>1</sub>, DTC<sub>2</sub>, and FB voltages. In addition, because the levels of the triangle wave (C<sub>T</sub>) and internally level-shifted triangle wave (dC<sub>T</sub>) are also generated internally by dividing the resistance of VREF, if VREF drops, each of the above will drop in proportion to VREF. As a result, even if the oscillation frequency drops, standard applications are not affected. Further study will be required, however, including for transient states.

#### 4.3 Oscillator Settings

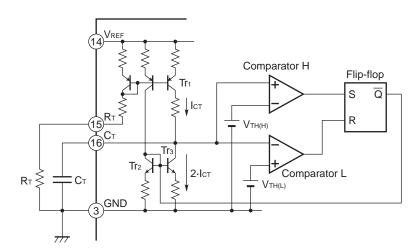

The oscillator circuit is shown in Figure 4-4 below.

Figure 4-4. µPC1909 Oscillator Circuit

A timing resistor ( $R_T$ ) is connected between the  $R_T$  pin and GND, and a timing capacitor ( $C_T$ ) is connected between the  $C_T$  pin and GND. The charge/discharge current of  $C_T$  is determined by  $R_T$ . The oscillator operates as follows.

- <1> If  $Ic\tau$  is taken as the current that flows through  $T_{r1}$ , the current the flows through  $T_{r3}$  is set as 2 x  $Ic\tau$ . Because the flip-flop  $(\overline{Q})$  outputs a high level at startup,  $T_{r2}$  is off, and  $C\tau$  is charged with  $Ic\tau$ .

- Vhen the CT voltage reaches VTH(H) = 3.5 V TYP., the output of comparator H is inverted, and Tr2 is turned on. Due to the discharging of the current set by 2 x lcT, the current flowing through CT is (lcT 2 x lcT) = lcT, so CT is discharged by lcT.

- <3> If the C<sub>T</sub> voltage drops to  $V_{TH(L)} = 1.5 \text{ V TYP.}$ , the output of comparator L is inverted, the flip-flop is reset, and C<sub>T</sub> is recharged because T<sub>r2</sub> is off.

- <4> <2> and <3> are repeated, generating a triangle wave with an amplitude of 1.5 to 3.5 V.

The oscillation frequency can be approximated from the following equation.

$$\text{fosc} \cong \frac{1 \times 10^6}{0.8251 \times \text{CT} \left[ \text{pF} \right] \times \left( \text{RT} \left[ \text{k}\Omega \right] + 0.8 \right) + 320} \left[ \text{kHz} \right]$$

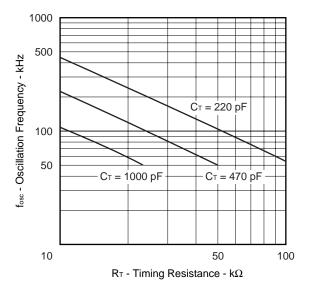

The results of measuring fosc vs. R⊤ are shown in Figure 4-5 below, with C⊤ as the parameter.

Figure 4-5. Relationship Between Oscillation Frequency (fosc), Timing Capacitor (Cτ) and Timing Resistor (Rτ)

#### 4.4 Dead Time Setting

The period in which OUT<sub>1</sub> and OUT<sub>2</sub> are simultaneously off is called dead time. This is an important parameter to realize a zero-cross switch when active-clamping. To set the dead time, it is necessary to adjust both the oscillation frequency and level shift parameters (for details of the oscillation frequency setting, refer to **4.3 Oscillator Settings**).

#### 4.4.1 Level shift setting

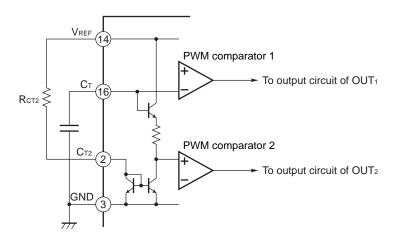

Whichever is higher of the DTC<sub>2</sub> pin and FB pin voltages is compared with the triangle wave that is the internally level-shifted wave of the  $C_T$  pin ( $dC_T$ ). OUT<sub>2</sub> is high level while  $dC_T$  is higher than the DTC<sub>2</sub> and FB voltages.

The triangle wave  $dC_T$ , which controls  $OUT_2$ , is generated by internally level-shifting the  $C_T$  wave on the low potential side. The amount of shift  $(V_d)$  is determined using the resistor  $(R_{CT2})$  connected between the  $C_{T2}$  and  $V_{REF}$  pins.

V<sub>d</sub> can be calculated from the following equation.

$$V_{d} \cong \frac{2 \times 4.2}{R_{CT2} \left[ k\Omega \right] + 10} \left[ V \right]$$

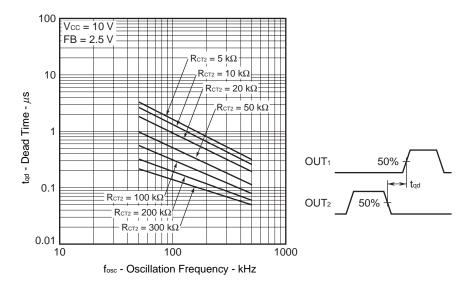

A general diagram of the level shift circuit (OLS) is shown in Figure 4-6, and the relationship between the oscillation frequency (fosc), the dead time (tqd), and resistor RcT2 is shown in Figure 4-7.

Figure 4-6. μPC1909 Level Shift Circuit (OLS)

Figure 4-7. Relationship Between fosc,  $t_{qd}$  and  $R_{CT2}$

23

#### 4.4.2 Dead time adjustment

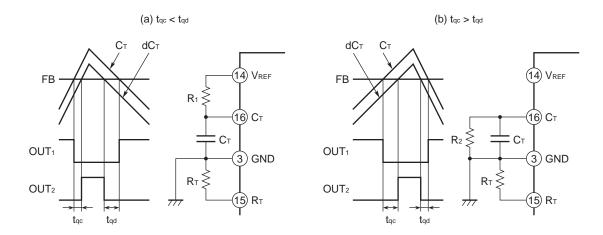

The dead time between the fall of OUT<sub>1</sub> and the rise of OUT<sub>2</sub> (t<sub>qc</sub>) and the dead time between the fall of OUT<sub>2</sub> and the rise of OUT<sub>1</sub> (t<sub>qd</sub>) is determined by the oscillation frequency and the amount of level shift of the triangle wave.

Although usually  $t_{qc} = t_{qd}$ , if these values differ, connect a suitable resistor between the  $C_T$  pin and the  $V_{REF}$  pin, as well as between the  $C_T$  pin and GND, and adjust the dead time by making the oscillation waveform asymmetrical, as shown in Figure 4-8.

Figure 4-8. Dead Time Adjustment

The charge current (IcT) of the timing capacitor (CT) is expressed as follows.

$$Ict [A] = \frac{4.2}{800 + Rt [\Omega]}$$

If R<sub>T</sub> is taken as 20 k $\Omega$ , IcT will be approximately 200  $\mu$ A.

To reduce  $t_{qc}$ , connect a resistor (R<sub>1</sub>) between the V<sub>REF</sub> and C<sub>T</sub> pins. If the value of the resistor is set so that the current charged in C<sub>T</sub> is about 10% more than I<sub>CT</sub>, t<sub>qc</sub> can be reduced and t<sub>qd</sub> increased by about 10% compared to when R<sub>1</sub> is not connected.

R<sub>1</sub> here can be calculated from the following equation.

$$R_1 [\Omega] = \frac{V_{REF} [V] - V_{OSC} [V]}{\Delta I_{CT} [A]}$$

Remark Vosc: Central voltage value of triangle wave

Δlcτ: Value of lcτ current increased (decreased) by R₁ (R₂)

Note also that connecting a resistor ( $R_2$ ) between  $C_T$  and GND makes it possible to reduce the current charged to  $C_T$ . If a resistor is selected that allows about 10% current to flow,  $t_{qc}$  can be increased and  $t_{qd}$  reduced by about 10% compared to when  $R_2$  is not connected.

R<sub>2</sub> here can be calculated from the following equation.

$$R_2 [\Omega] = \frac{\text{Vosc [V]}}{\Delta \text{Ict [A]}}$$

#### 4.5 Duty Settings

#### 4.5.1 Maximum duty setting

In the steady operation state (DTC<sub>2</sub> < FB < DTC<sub>1</sub>), the duty during operation at the FB voltage is determined by OUT<sub>1</sub> and OUT<sub>2</sub>. To set the duty as an independent FB input at times such as at startup, during low voltage input, and when the current is limited, the OUT<sub>1</sub> and OUT<sub>2</sub> outputs must be set to their maximum duty values. Set the maximum duty for OUT<sub>1</sub> and OUT<sub>2</sub> via the DTC<sub>1</sub> and DTC<sub>2</sub> pins, respectively, as shown in Figure 4-9.

14) V<sub>REF</sub>

13 DTC<sub>1</sub>

5 DTC<sub>2</sub>

Figure 4-9. Maximum Duty Settings in  $\mu$ PC1909

Note that when pulse-by-pulse current limitation is being applied using the OC pin, the maximum duty of OUT<sub>1</sub> should be set to between 60 and 65%. This is because the duty conversion of OUT<sub>1</sub> sets the reset level of the internal OC circuit to about 75%. For details, refer to **4.7 Overcurrent Limiter Settings**.

There is no limit to the maximum duty of OUT<sub>2</sub>.

#### 4.5.2 Minimum duty limit

When OUT<sub>1</sub> is operating at maximum duty, if OUT<sub>2</sub> is not output, it may inadvertently be set to a duty of 0%, depending on the value of "OUT<sub>1</sub> ON time + t<sub>qc</sub> + t<sub>qd</sub>". If OUT<sub>2</sub> has 0% duty when active clamping, the transformer will not be able to be reset, and a minimum duty limit will have to be set for OUT<sub>2</sub> at the same time the maximum duty of OUT<sub>1</sub> is determined. Because the DTC<sub>1</sub> pin is also the input of PWM comparator 2 on the OUT<sub>2</sub> side, if the FB voltage is higher than the DTC<sub>1</sub> voltage, the DTC<sub>1</sub> voltage is compared with dC<sub>T</sub> and the minimum duty of OUT<sub>2</sub> is limited.

#### 4.5.3 Soft start

This IC incorporates a transistor for discharging the soft start capacitor connected between the DCT<sub>1</sub> pin and GND. If Vcc falls below the operation stopped voltage (5 V TYP.) or if the ON/OFF pin becomes low level (off), the DTC<sub>1</sub> pin becomes low level and the soft start capacitor is initialized.

There is no such transistor incorporated on the DTC2 side.

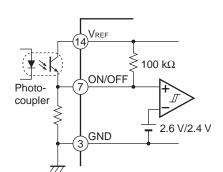

#### 4.6 Remote Control

In the  $\mu$ PC1909, starting up and stopping a converter can be controlled by turning on and off the output circuit using an external signal. When the ON/OFF pin is made low level, the low voltage malfunction protection circuit operates and cuts off OUT<sub>1</sub> and OUT<sub>2</sub>, causing the timing capacitor connected between the C<sub>T</sub> pin and GND (C<sub>T</sub>) and the soft start capacitor connected between the DTC<sub>1</sub> pin and GND to discharge. Because the on/off threshold voltage has 0.2-V hysteresis, the occurrence of chattering can be suppressed, even in slow on/off operations.

The ON/OFF pin is internally pulled up to  $V_{REF}$  via a 100  $k\Omega$  resistor. When the on/off function is not used, however, be sure to connect the ON/OFF pin directly to the  $V_{REF}$  pin in order to prevent the occurrence of noise.

A configuration whereby on/off control is controlled from the primary side by a photocoupler is shown in Figure 4-10 below. Be sure to set the pull-down resistor connected to the ON/OFF pin so that the leakage current between C and E when the photocoupler is off does not cause the ON/OFF pin voltage to be boosted to a level whereby the  $\mu$ PC1909 is turned on.

Figure 4-10. ON/OFF Pin Connection

#### 4.7 Overcurrent Limiter Settings

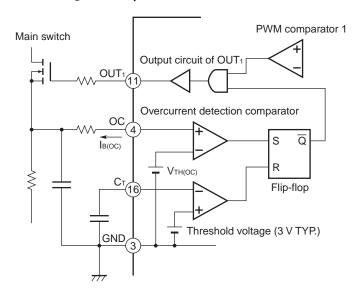

The OC pin in the  $\mu$ PC1909 allows the realization of a pulse-by-pulse overcurrent limiter, whose configuration is shown in Figure 4-11 below.

Figure 4-11. μPC1909 Overcurrent Limiter

If overcurrent is detected by the overcurrent detection comparator, OUT<sub>1</sub> is latched to low level by the flip-flop. Moreover, if the triangle wave generated by the oscillator and a voltage with a threshold value that causes the output latch to be reset are input to the other comparator the flip-flop will be reset at each cycle.

Because the reset threshold voltage is internally set to 3 V TYP. (about 75% VREF), if a maximum duty of 75% or over is set by the DTC<sub>1</sub> pin thus activating overcurrent limitation by the OC pin, two pulses will be inadvertently output in one cycle. To allow for differences in ICs, do not set the maximum duty of DTC<sub>1</sub> (60% or over) to more than 65% when applying overcurrent limitation using the OC pin. Alternatively, do not use OC pin overcurrent limitation if setting the maximum duty (60% or over) to more than 65%. In this case (overcurrent limitation current not used), connect the OC pin directly to GND.

Discharge current flows through the OC pin. This discharge current is expressed as the input bias current of the overcurrent latch block ( $I_{B(OC)}$ ). Although a filter is attached to the OC pin to prevent the overcurrent latch circuit from malfunctioning due to the surge current that flows when the power MOS FET is turned on, be sure to set the resistor to no more than 100  $\Omega$  to stop  $I_{B(OC)}$  causing a shift in the overcurrent detection point.

When overcurrent is being limited by the OC pin, OUT<sub>1</sub> operates at the minimum pulse width limitable by the overcurrent latch circuit. The minimum pulse width is the sum of the  $\mu$ PC1909's overcurrent detection delay time (td(OC)), the delay of the filter attached to the OC pin, and the turn-on time of the power MOS FET.

During steady operation (DTC<sub>2</sub> < FB < DTC<sub>1</sub>), OUT<sub>2</sub> operates at the duty determined by the FB voltage. Because the FB voltage rises when the output of the converter drops, the duty of the OUT<sub>2</sub> output drops in line with the converter output, until it reaches the minimum duty set by the DTC<sub>1</sub> voltage.

#### 4.8 Overvoltage Protection Circuit Setting

The overvoltage protection circuit based on the overvoltage latch in the  $\mu$ PC1909 is configured as shown in Figure 4-12 below. The threshold voltage connected to the overvoltage detection comparator (VTH(OV)) is 2.0 to 2.8 V (2.4 V TYP.). If the input at the OV pin exceeds VTH(OV), the flip-flop in the IC latches OUT<sub>1</sub> and OUT<sub>2</sub> to low level. Once the overvoltage latch circuit is latched, it is not released until the power supply voltage of the IC (Vcc) falls below the OVL release voltage (2 V TYP.) (because Icc is higher than Icc(SB) when the circuit is latched, the operation status will not be restored in the steady input state).

Figure 4-12. μPC1909 Overvoltage Protection Circuit

Discharge current flows through the OV pin. This is the input bias current of the overvoltage latch block in the electrical specifications ( $I_{B(OV)} = 4 \mu A$  MAX.). To prevent the detection level fluctuating due to  $I_{B(OV)}$ , and to allow for the effect of the leakage current between C and E in the photocoupler, be sure to set the overvoltage detection resistor connected to the OV pin to no more than  $100 \text{ k}\Omega$ .

Because the OVL (overvoltage latch) detection delay time is about 750 ns, a capacitor with good frequency characteristics should be connected between the OV pin and GND to prevent malfunction due to noise. However, if the overvoltage latch circuit does malfunction due to electrostatic discharge or other such external noise, an effective countermeasure is to connect a capacitor with good frequency characteristics such as a film capacitor between Vcc and GND.

Caution If the power is reapplied immediately after being stopped (VREF drop) while there is charge remaining in the filter's capacitor (such as when Vcc (auxiliary coil voltage) is being monitored from VREF without configuring an overvoltage protection circuit such as is shown in Figure 4-12), the overvoltage latch threshold value will be boosted in proportion with the boosting of VREF, possibly causing the overvoltage latch to latch too easily.

#### 4.9 Output Circuit

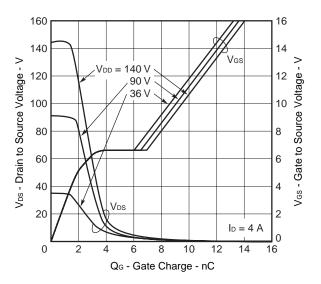

The output circuit is a totem-pole output with a peak output current rating ( $Ic_{(peak)}$ ) of 1.2 A. Although a power MOS FET can be driven directly, be careful not to exceed the allowable loss of the  $\mu$ PC1909 when the input capacitance of the power MOS FET is large or the operating frequency is high. The switching speed of the power MOS FET is determined by the charge/discharge current of the gates and the charge of the power MOS FET's gates. Be sure, however, to insert a series resistor at the gates of the power MOS FET to avoid exceeding the peak output current rating of the  $\mu$ PC1909.

Note that the heat generated in the  $\mu$ PC1909 by the output current is determined by the charge at the gates of the power MOS FET, and is not related to the switching speed.

When the 2SK1954 is used, for example, the loss of the  $\mu$ PC1909 (P<sub>d</sub>) can be determined as follows, when the gate drive voltage V<sub>GS</sub>  $\cong$  VOUT<sub>1</sub> = 10 V and the oscillation frequency fosc = 200 kHz, as shown in the gate charge graph on the right (Figure 4-13):

$$P_d = Q_G \cdot V_{GS} \cdot f_{OSC}$$

=10 [nC] x 10 [V] x 200 [kHz]

=0.02 [W]

Moreover, when the  $\mu$ PC1909 and the power MOS FET are separated, the wiring from the OUT<sub>1</sub> and OUT<sub>2</sub> output pins is lengthened, which combined with the parasitic inductance and floating capacitance elements of the power MOS FET causes

Figure 4-13. 2SK1954 Gate Change Characteristics

the voltage of the OUT<sub>1</sub> and OUT<sub>2</sub> pins to fall below that of the GND pin (undershoot). In this case, clamp the undershoot by connecting a Schottky barrier diode as shown in Figure 4-14 to prevent the possibility of malfunction in the  $\mu$ PC1909.

PC1909

OUT₁ (Pin No.11),

OUT₂ (Pin No.6)

GND 3

EMI₁ (Pin No.10),

EMI₂ (Pin No.8)

Figure 4-14. Power MOS FET Drive Circuit Block

Note that when active clamping, if the C-cut drive transistor is driven by  $OUT_2$ , the voltage of the  $OUT_2$  pin may become higher than Vcc. It is therefore vital to observe  $VOUT_2 \le Vcc + 5$  V by taking action such as connecting a diode between  $OUT_2$  and Vcc.

#### **★ 5. PACKAGE DRAWINGS**

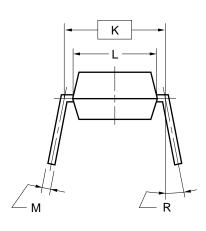

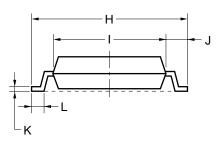

## 16-PIN PLASTIC DIP (7.62mm(300))

#### NOTES

- 1. Each lead centerline is located within 0.25 mm of its true position (T.P.) at maximum material condition.

- 2. Item "K" to center of leads when formed parallel.

| MILLIMETERS            |

|------------------------|

| 20.32 MAX.             |

| 1.27 MAX.              |

| 2.54 (T.P.)            |

| 0.50±0.10              |

| 1.1 MIN.               |

| 3.5±0.3                |

| 0.51 MIN.              |

| 4.31 MAX.              |

| 5.08 MAX.              |

| 7.62 (T.P.)            |

| 6.5                    |

| $0.25^{+0.10}_{-0.05}$ |

| 0.25                   |

| 1.1 MIN.               |

| 0~15°                  |

|                        |

P16C-100-300B-2

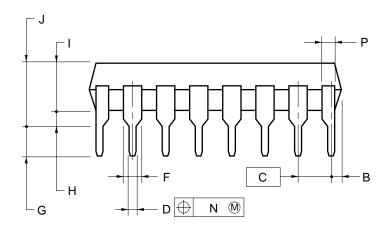

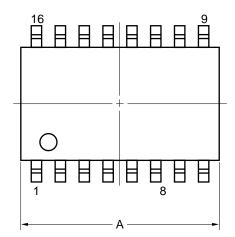

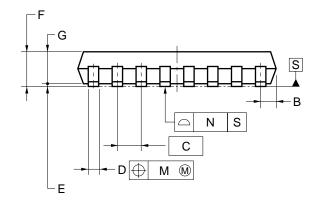

## 16-PIN PLASTIC SOP (7.62 mm (300))

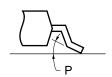

detail of lead end

#### NOTE

Each lead centerline is located within 0.12 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            |

|------|------------------------|

| Α    | 10.2±0.2               |

| В    | 0.78 MAX.              |

| С    | 1.27 (T.P.)            |

| D    | $0.42^{+0.08}_{-0.07}$ |

| Е    | 0.1±0.1                |

| F    | 1.65±0.15              |

| G    | 1.55                   |

| Н    | 7.7±0.3                |

| I    | 5.6±0.2                |

| J    | 1.1±0.2                |

| K    | $0.22^{+0.08}_{-0.07}$ |

| L    | 0.6±0.2                |

| М    | 0.12                   |

| N    | 0.10                   |

| Р    | 3°+7°                  |

|      |                        |

P16GM-50-300B-6

#### 6. RECOMMENDED SOLDERING CONDITIONS

When soldering this product, it is highly recommended to observe the conditions as shown below. If other soldering processes are used, or if the soldering is performed under different conditions, please make sure to consult with our sales offices.

For more details, refer to our document "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL" (C10535E).

#### **Type of Through-hole Device**

μPC1909CX: 16-pin plastic DIP (7.62 mm (300))

| Soldering Method           | Soldering Conditions                                          |

|----------------------------|---------------------------------------------------------------|

| Wave soldering (pins only) | Solder bath temperature : 260°C MAX., Time : 10 seconds MAX.  |

| Partial heating            | Pin temperature : 300°C MAX., Time : 3 seconds MAX. (per pin) |

Caution For through-hole device, the wave soldering process must be applied only to leads, and make sure that the package body does not get jet soldered.

#### **Type of Surface Mount Device**

μPC1909GS: 16-pin plastic SOP (7.62 mm (300))

| Soldering Method | Soldering Conditions                                                                                                                                | Recommended<br>Condition symbol |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Infrared reflow  | Package peak temperature : 235°C, Time : 30 seconds MAX. (at 210°C or higher), Count : Twice or less                                                | IR35-00-2                       |

| VPS              | Package peak temperature : 215°C, Time : 40 seconds MAX. (at 200°C or higher), Count : Twice or less                                                | VP15-00-2                       |

| Wave soldering   | Soldering bath temperature : 260°C or less, Time : 10 seconds MAX., Count : Once, Preheating temperature : 120°C MAX. (package surface temperature) | WS60-00-1                       |

Caution Do not use different soldering methods together.

[MEMO]

[MEMO]

[MEMO]

- The information in this document is current as of November, 2000. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4