www.ti.com

# Tablet PC and Netbook 2-Series Cell Li-Ion Battery Gas Gauge and Protection

Check for Samples: bq28400

#### **FEATURES**

- Fully Integrated Gas Gauge and Analog Monitoring with Protection in a Single Package

- 2-Series Cell Li-Ion or Li-Polymer Battery Packs

- Flexible Memory Architecture with Integrated Flash Memory

- Zero-Volt and Pre-Charge Mode

- Full Array of Programmable Protection:

- OV (Overvoltage)

- UV (Undervoltage)

- SC (Short Circuit)

- OT (Overtemperature)

- CIM (Cell Imbalance)

- Accurate CEDV Gauging Algorithm with Self Discharge Compensation

- High Accuracy Analog Interface with Two Independent ADCs:

- High Resolution 16-Bit Integrator for Coulomb Counting

- 16-Bit Delta-Sigma ADC with a 16-Channel Multiplexer for Voltage, Current, and Temperature

- High Side Protection FET Drive

- Fully Integrated Internal Clock Synthesizer with No External Components Required

- Two-Wire SMBus v1.1 Compliant Communications

- Reduced Power Modes (Typical Battery Pack Operating Range Conditions)

- Low Power

- Shutdown

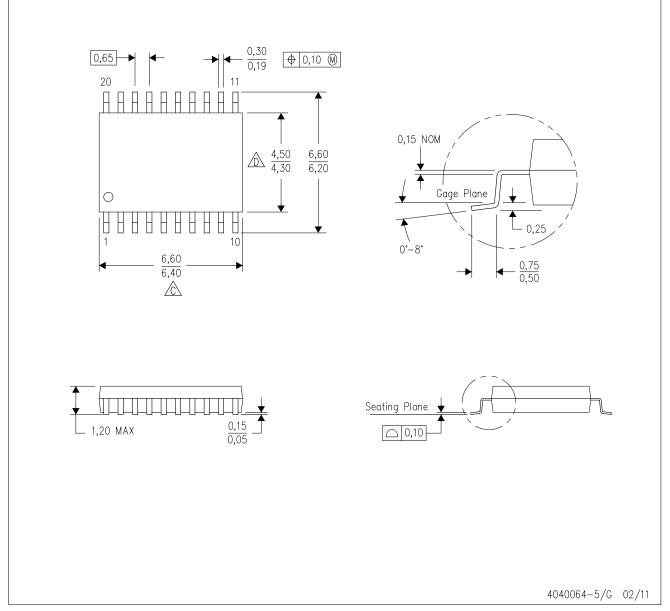

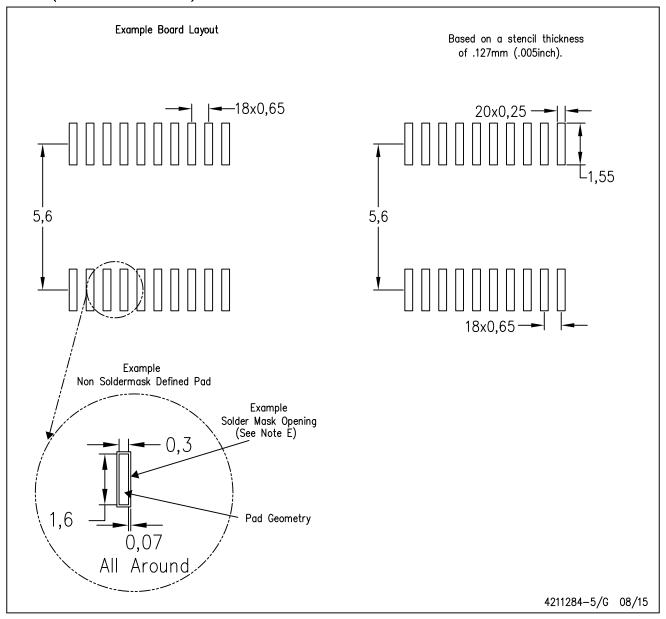

- 20-Pin TSSOP Package (RoHS-Compliant)

- JEITA/Enhanced Charging

- Supports SHA-1 Authentication Responder

#### **APPLICATIONS**

- Tablet PCs

- Slate PCs

- Netbooks/Notebooks

- Smartbooks

#### DESCRIPTION

The bq28400 device is a fully integrated gas gauge and analog monitoring management solution that provides protection and control for 2-series cell Li-lon battery packs in a single TSSOP package.

Implementing the optimum balance of quick response analog hardware-based monitoring and control along with an integrated fast CPU provides the ideal pack-based or in-system Li-lon battery solution. The bq28400 also provides flexible user programmable settings stored in flash memory for control of critical system parameters such as overcurrent, short circuit, under/overvoltage, and over/undertemperature conditions.

The bq28400 communicates with the system host via a two-wire SMBus 1.1 compatible interface, providing high-accuracy reporting and control of battery pack operation. The FET drive and TSSOP package enable a lower cost and small footprint solution along with a simple layout and routing on narrow pack PCBs.

## **AVAILABLE OPTIONS**

| т              | PACK                     | (AGE <sup>(1)</sup>             |

|----------------|--------------------------|---------------------------------|

| T <sub>A</sub> | 20-PIN TSSOP (PW) Tube   | 20-PIN TSSOP (PW) Tape and Reel |

| -40°C to 85°C  | bq28400PW <sup>(2)</sup> | bq28400PWR <sup>(3)</sup>       |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (2) A single tube quantity is 50 units.

- (3) A single reel quantity is 2000 units.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

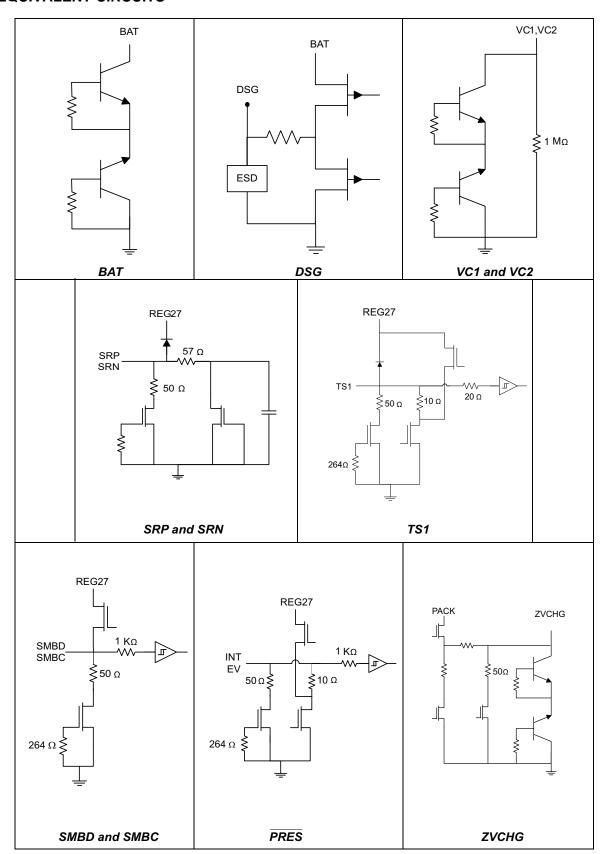

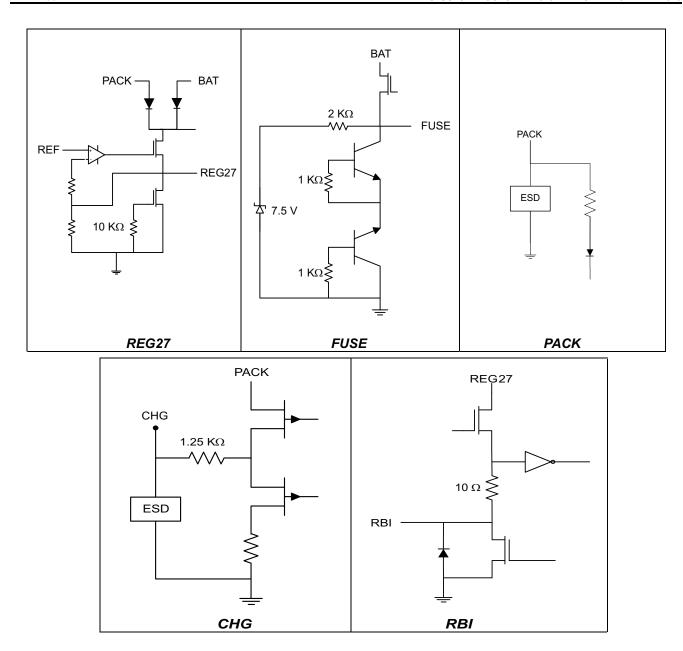

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

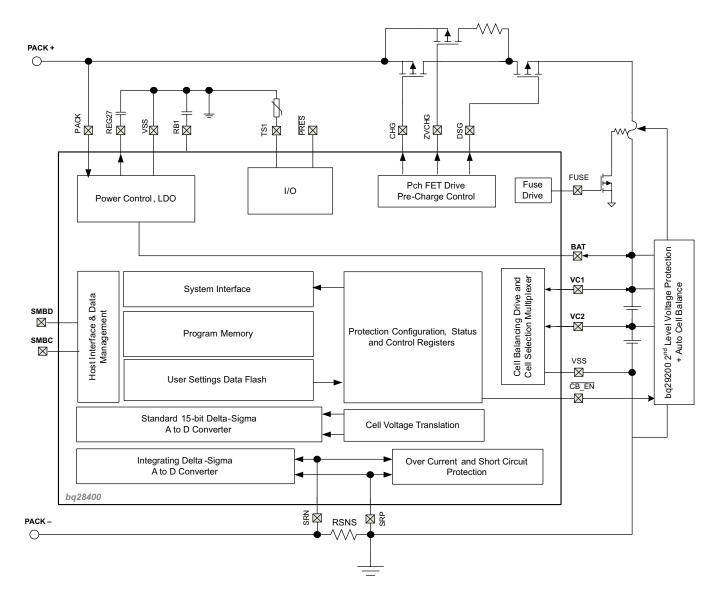

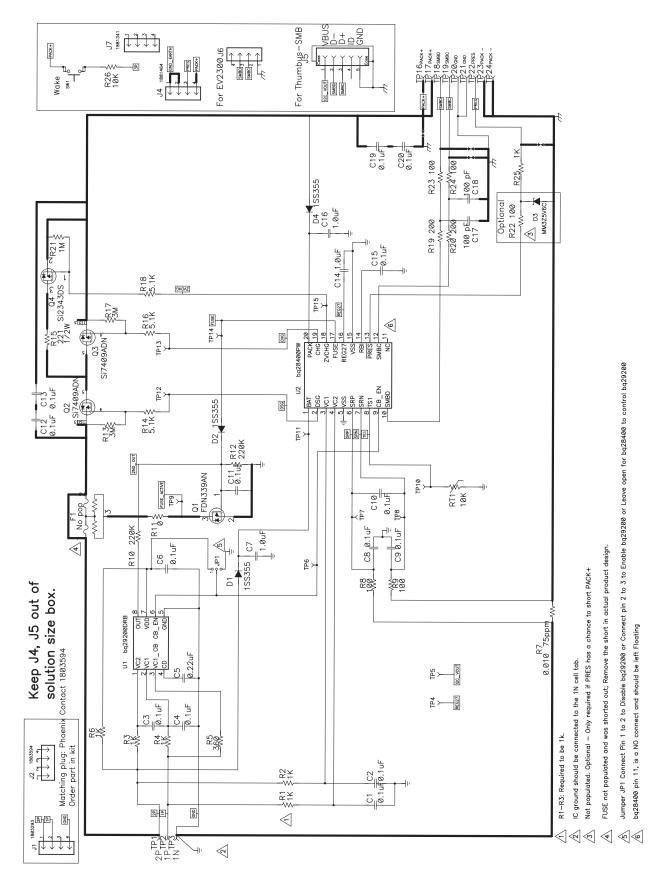

## **BLOCK DIAGRAM and TYPICAL IMPLEMENTATION**

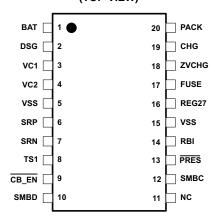

#### bq28400 PW PACKAGE (TOP VIEW)

## **PIN FUNCTIONS**

| PIN NAME | PIN NUMBER | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                         |

|----------|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| BAT      | 1          | Р                   | Alternate supply input                                                                                                                              |

| DSG      | 2          | 0                   | P-channel discharge FET gate drive                                                                                                                  |

| VC1      | 3          | AI                  | Sense input for the most positive cell. Also external cell balancing drive output for the most positive cell                                        |

| VC2      | 4          | AI                  | Sense input for the lowest cell. Also external cell balancing drive output for the lowest cell                                                      |

| VSS      | 5          | Р                   | Device ground                                                                                                                                       |

| SRP      | 6          | Al                  | Differential Coulomb Counter input or SRP oversampled ADC input                                                                                     |

| SRN      | 7          | Al                  | Differential Coulomb Counter input or SRN oversampled ADC input                                                                                     |

| TS1      | 8          | 1                   | Thermistor 1 input. Connect NTC from this pin to VSS pin                                                                                            |

| CB_EN    | 9          | 0                   | Output signal to control cell balancing                                                                                                             |

| SMBD     | 10         | I/OD                | SBS data                                                                                                                                            |

| NC       | 11         | _                   | No connection, leave floating                                                                                                                       |

| SMBC     | 12         | I/OD                | SBS clock                                                                                                                                           |

| PRES     | 13         | 1                   | System present                                                                                                                                      |

| RBI      | 14         | Р                   | RAM backup pin to provide backup potential to the internal DATA RAM if power is momentarily lost, by using a capacitor attached between RBI and VSS |

| VSS      | 15         | Р                   | Device ground                                                                                                                                       |

| REG27    | 16         | Р                   | 2.7-V regulator. Connect a capacitor between REG27 and VSS                                                                                          |

| FUSE     | 17         | 0                   | Push-pull fuse circuit drive                                                                                                                        |

| ZVCHG    | 18         | 0                   | P-channel precharge FET gate drive                                                                                                                  |

| CHG      | 19         | 0                   | P-channel charge FET gate drive                                                                                                                     |

| PACK     | 20         | Р                   | Alternate supply input                                                                                                                              |

$<sup>(1) \</sup>quad P = Power \ Connection, \ O = Digital \ Output, \ AI = Analog \ Input, \ I = Digital \ Input, \ I/OD = Digital \ Input/Output$

#### THERMAL INFORMATION

|                           |                                                  | bq28400 |       |

|---------------------------|--------------------------------------------------|---------|-------|

|                           | THERMAL METRIC <sup>(1)</sup>                    | PW      | UNITS |

|                           |                                                  | 20 PINS |       |

| $\theta_{JA}$             | Junction-to-ambient thermal resistance (2)       | 91.7    |       |

| $\theta_{\text{JC(top)}}$ | Junction-to-case(top) thermal resistance (3)     | 20.4    |       |

| $\theta_{\sf JB}$         | Junction-to-board thermal resistance (4)         | 45.6    | 0000  |

| ΨЈТ                       | Junction-to-top characterization parameter (5)   | 0.5     | °C/W  |

| ΨЈВ                       | Junction-to-board characterization parameter (6) | 43.3    |       |

| $\theta_{JC(bottom)}$     | Junction-to-case(bottom) thermal resistance (7)  | n/a     |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature (unless otherwise noted) (1)

|                                                  |                                                                                    | Value/Unit                                                                     |

|--------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Supply voltage range, V <sub>MAX</sub>           | PACK w.r.t. V <sub>SS</sub>                                                        | –0.3 to 34 V                                                                   |

|                                                  | VC1, BAT                                                                           | V <sub>VC2</sub> –0.3 to V <sub>VC2</sub> + 8.5 or 34 V,<br>whichever is lower |

|                                                  | VC2                                                                                | $V_{VSRP}$ –0.3 to $V_{VSRP}$ + 8.5 V                                          |

|                                                  | SRP, SRN                                                                           | –0.3 to V <sub>REG27</sub>                                                     |

|                                                  | General Purpose open-drain I/O pins: SMBD, SMBC                                    | V <sub>SS</sub> -0.3 V to 6 V                                                  |

| Input voltage range, V <sub>IN</sub>             | General Purpose push-pull I/O pins: TS1, PRES, CB_EN                               | -0.3 V to V <sub>REG27</sub> + 0.3 V                                           |

|                                                  | Input voltage range to all other pins, V <sub>IN</sub> relative to V <sub>SS</sub> | -0.3 V to V <sub>REG27</sub> + 0.3 V                                           |

|                                                  | DSG, CHG, ZVCHG                                                                    | -0.3 to BAT                                                                    |

|                                                  | FUSE                                                                               | -0.3 to [BAT or PACK] (whichever is lower)                                     |

|                                                  | RBI, REG27                                                                         | –0.3 to 2.75 V                                                                 |

| Maximum Operational VSS current, I <sub>SS</sub> |                                                                                    | 50 mA                                                                          |

| Ambient Temperature, T <sub>A</sub>              |                                                                                    | −20 to 110°C                                                                   |

| Storage temperature range, T <sub>STG</sub>      |                                                                                    | −65 to 150°C                                                                   |

| ECD Human Bady Madal(2)                          | All pins except VC1 and VC2                                                        | 2 kV                                                                           |

| ESD Human Body Model (2)                         | VC1 and VC2                                                                        | 1 kV                                                                           |

| ESD Machine Model                                | All pins                                                                           | 200 V                                                                          |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                        |                              | PIN                      | MIN              | NOM | MAX                   | UNIT |

|------------------------|------------------------------|--------------------------|------------------|-----|-----------------------|------|

|                        | Cupply voltage               | PACK                     |                  |     | V <sub>BAT</sub> + 5  | V    |

|                        | Supply voltage               | BAT                      | 3.8              |     | V <sub>VC2</sub> + 5  | V    |

| V <sub>(STARTUP)</sub> | Minimum startup voltage      | Start up voltage at PACK |                  | 5.2 | 5.5                   | V    |

|                        |                              | VC1, BAT                 | V <sub>VC2</sub> |     | V <sub>VC2</sub> + 5  | V    |

|                        |                              | VC2                      | $V_{VSRP}$       |     | V <sub>VSRP</sub> + 5 | ٧    |

| V <sub>IN</sub>        | Input Voltage Range          | VC1 – VC2                | 0                |     | 5                     | V    |

|                        |                              | PACK                     |                  |     | 18.75                 | ٧    |

|                        |                              | SRP to SRN               | -0.3             |     | 1                     | V    |

| C <sub>(REG27)</sub>   | External 2.7 V REG capacitor |                          | 1                |     |                       | μF   |

| T <sub>OPR</sub>       | Operating temperature        |                          | -20              |     | 85                    | °C   |

## **ELECTRICAL CHARACTERISTICS**

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}\text{C}$  to 85°C and  $V_{BAT} = V_{PACK} = 3.8 \text{ V}$  to 18.75 V over operating free-air temperature range (unless otherwise noted)

| ı                      | PARAMETER                         | TEST CONDITION <sup>(1)</sup>                                               | MIN                      | TYP             | MAX  | UNIT  |

|------------------------|-----------------------------------|-----------------------------------------------------------------------------|--------------------------|-----------------|------|-------|

| General Pu             | rpose I/O                         |                                                                             | ·                        |                 |      |       |

| $V_{IH}$               | High-level input voltage          | SMBD, SMBC, PRES                                                            | 2                        |                 |      | V     |

| $V_{IL}$               | Low-level input voltage           | SMBD, SMBC, PRES                                                            |                          |                 | 0.8  | V     |

| V <sub>OH</sub>        | Output voltage high               | $\overline{\text{PRES}}$ , $I_L = -0.5 \text{ mA}$                          | V <sub>REG27</sub> - 0.5 |                 |      | V     |

| M                      | High level Free entert            | $V_{BAT} = 3.8 \text{ V to 9 V, C}_{L} = 1 \text{ nF}$                      | 3                        | $V_{BAT} - 0.3$ | 8.6  | V     |

| $V_{OH(FUSE)}$         | High level Fuse output            | $V_{BAT} = 9 \text{ V to } 10 \text{ V, } C_L = 1 \text{ nF}$               | 7.5                      | 8               | 9    |       |

| t <sub>R(FUSE)</sub>   | FUSE output rise time             | C <sub>L</sub> = 1 nF, V <sub>OH(FUSE)</sub> = 0 V to 5 V                   |                          |                 | 10   | μs    |

| I <sub>O(FUSE)</sub>   | FUSE output current               | FUSE active                                                                 | -3                       |                 |      | mA    |

| Z <sub>O(FUSE)</sub>   | FUSE output impedance             |                                                                             |                          | 2               | 6    | kΩ    |

| V <sub>FUSE_DET</sub>  | FUSE Detect Input<br>Voltage      |                                                                             | 0.8                      | 2               | 3.2  | V     |

| V <sub>OL</sub>        | Low-level output voltage          | SMBD, SMBC, TS1, I <sub>L</sub> = 7 mA                                      |                          |                 | 0.4  | V     |

| C <sub>IN</sub>        | Input capacitance                 |                                                                             |                          | 5               |      | pF    |

| I <sub>(VOUT)</sub>    | VOUT source currents              | $V_O$ active, $V_O = V_{REG27} - 0.6 \text{ V}$                             | -3                       |                 |      | mA    |

| I <sub>LKG(VOUT)</sub> | VOUT leakage current              | V <sub>O</sub> inactive                                                     | -0.2                     |                 | 0.2  | μA    |

| I <sub>LKG</sub>       | Input leakage current             | SMBD, SMBC, PRES, TS1                                                       |                          |                 | 1    | μA    |

| $R_{\text{PD(SMBx)}}$  | SMBD and SMBC, pull-down resistor | $T_A = -20$ °C to 100°C                                                     | 600                      | 950             | 1300 | kΩ    |

| R <sub>PAD</sub>       | Pad resistance                    | TS1                                                                         |                          | 87              | 110  | Ω     |

| Supply Cur             | rent                              |                                                                             |                          |                 |      | •     |

| I <sub>CC</sub>        | Normal Mode                       | No flash memory write, No I/O activity                                      |                          | 400             |      | μA    |

| I <sub>LPM</sub>       | Low-Power Mode                    | CPU=HALT CHG=DSG=PCHG=OFF LDO ON but no load, no communication, BAT = 7.2 V |                          | 55              |      | μA    |

| I <sub>SHUTDOWN</sub>  | Shutdown Mode                     | $T_A = -20$ °C to 110°C                                                     |                          | 0.5             | 1    | μA    |

| REG27 Pow              | ver On Reset                      |                                                                             | 1                        |                 |      | 1     |

| V <sub>REG27IT</sub> - | Negative-going voltage            | input, at REG27                                                             | 2.22                     | 2.29            | 2.34 | V     |

| V <sub>REG27IT+</sub>  | Positive-going voltage i          | nput, at REG27                                                              | 2.25                     | 2.5             | 2.6  | V     |

| Flash                  | •                                 |                                                                             |                          |                 |      | •     |

|                        | Data retention                    |                                                                             | 10                       |                 |      | Years |

<sup>(1)</sup> By default: SMBus has internal pull-down.

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}\text{C}$  to 85°C and  $V_{BAT} = V_{PACK} = 3.8 \text{ V}$  to 18.75 V over operating free-air temperature range (unless otherwise noted)

| P                      | ARAMETER                                                                                                                                                            | TEST CONDITION <sup>(1)</sup>                                                                              | MIN | TYP    | MAX  | UNIT   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                        | Flash programming write-cycles                                                                                                                                      |                                                                                                            | 20k |        |      | Cycles |

| t <sub>ROWPROG</sub>   | Row programming time                                                                                                                                                |                                                                                                            |     |        | 2    | ms     |

| t <sub>MASSERASE</sub> | Mass-erase time                                                                                                                                                     |                                                                                                            |     |        | 250  |        |

| t <sub>PAGEERASE</sub> | Page-erase time                                                                                                                                                     |                                                                                                            |     |        | 25   |        |

| I <sub>CC(PROG)</sub>  | Flash-write supply current                                                                                                                                          |                                                                                                            |     | 4      | 6    | mA     |

| I <sub>CC(ERASE)</sub> | Flash-erase supply                                                                                                                                                  | $T_A = -40$ °C to 0°C                                                                                      |     | 8      | 22   |        |

|                        | current                                                                                                                                                             | T <sub>A</sub> = 0°C to 85°C                                                                               |     | 3      | 15   |        |

| RAM Backu              | p                                                                                                                                                                   |                                                                                                            |     |        |      |        |

|                        | RBI data-retention                                                                                                                                                  | $V_{RBI} > V_{(RBI)MIN}$ , $V_{REG27} < V_{REG27IT}$ , $T_A = 70^{\circ}\text{C}$ to 110°C                 |     | 20     | 1500 | nA     |

| I <sub>(RBI)</sub>     | input current                                                                                                                                                       | $V_{RBI} > V_{(RBI)MIN}$ , $V_{REG27} < V_{REG27IT}$ , $T_A = -20^{\circ}\text{C}$ to $70^{\circ}\text{C}$ |     |        | 500  | IIA    |

| V <sub>(RBI)</sub>     | RBI data-retention vol                                                                                                                                              | tage <sup>(2)</sup>                                                                                        | 1   |        |      | V      |

| Internal LDC           | )                                                                                                                                                                   |                                                                                                            | ·   |        |      |        |

| V <sub>REG</sub>       | Regulator output voltage                                                                                                                                            | I <sub>REG27</sub> = 10 mA, T <sub>A</sub> = -20°C to 85°C                                                 | 2.5 | 2.7    | 2.75 | V      |

|                        |                                                                                                                                                                     | PACK and BAT $\leq$ 4.5 V, T <sub>A</sub> = $-20^{\circ}$ C to 110°C                                       | 3   |        |      |        |

| $I_{REG}$              | Regulator Output                                                                                                                                                    | 4.5 V < PACK and BAT ≤ 6.8 V                                                                               | 10  |        |      | mA     |

| IREG                   | Current $ \begin{aligned} 6.8 \text{ V} < \text{PACK and BAT} &\leq 18.7 \text{ 5 V}, \\ T_{\text{A}} &= -20^{\circ}\text{C to } 70^{\circ}\text{C} \end{aligned} $ |                                                                                                            |     |        |      |        |

| $\Delta V_{(REGTEMP)}$ | Regulator output change with temperature                                                                                                                            | $I_{REG}$ = 10 mA, $T_A$ = -20°C to 85°C                                                                   |     | ±0. 5% |      |        |

| $\Delta V_{(REGLINE)}$ | Line regulation                                                                                                                                                     | I <sub>REG</sub> = 10 mA                                                                                   |     | ±2     | ±4   | mV     |

| $\Delta V_{(REGLOAD)}$ | Load regulation                                                                                                                                                     | I <sub>REG</sub> = 0.2 to 10 mA                                                                            |     | ±20    | ±40  | mV     |

| I <sub>(REGMAX)</sub>  | Current limit                                                                                                                                                       |                                                                                                            | 25  |        | 50   | mA     |

|                        |                                                                                                                                                                     |                                                                                                            |     |        |      |        |

<sup>(2)</sup> Specified by design. Not production tested.

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}\text{C}$  to 85°C and  $V_{BAT} = V_{PACK} = 3.8 \text{ V}$  to 18.75 V over operating free-air temperature range (unless otherwise noted)

| F                      | PARAMETER                                  | TEST CONDITION <sup>(1)</sup>                              | MIN      | TYP    | MAX                         | UNIT   |

|------------------------|--------------------------------------------|------------------------------------------------------------|----------|--------|-----------------------------|--------|

| SRx Wake f             | rom Sleep                                  |                                                            | <u> </u> |        |                             | 1      |

|                        |                                            | V <sub>WAKE</sub> = 1.2 mV                                 | 0.2      | 1.2    | 2                           |        |

| .,                     |                                            | V <sub>WAKE</sub> = 2.4 mV                                 | 0.4      | 2.4    | 3.6                         | 1 ,,   |

| V <sub>WAKE_ACR</sub>  | Accuracy of V <sub>WAKE</sub>              | V <sub>WAKE</sub> = 5 mV                                   | 2        | 5      | 6.8                         | mV     |

|                        |                                            | V <sub>WAKE</sub> = 10 mV                                  | 5.3      | 10     | 13                          |        |

| V <sub>WAKE_TCO</sub>  | Temperature drift of V <sub>V</sub>        | WAKE accuracy                                              |          | 0.5    |                             | %/°C   |

| t <sub>WAKE</sub>      | Time from application of                   | of current and wake of bq28400                             |          | 0.2    | 1                           | ms     |

| Coulomb C              | ounter                                     |                                                            |          |        |                             |        |

|                        | Input voltage range                        |                                                            | -0.20    |        | 0.25                        | V      |

|                        | Conversion time                            | Single conversion                                          |          | 250    |                             | ms     |

|                        | Effective resolution                       | Single conversion                                          | 15       |        |                             | Bits   |

|                        | Integral nonlinearity                      | $T_A = -20 \text{ to } 85^{\circ}\text{C}$                 |          | ±0.007 | ±0.034                      | %FSR   |

|                        | Offset error (3)                           | $T_A = -20 \text{ to } 85^{\circ}\text{C}$                 |          | 10     |                             | μV     |

|                        | Offset error drift                         |                                                            |          | 0.3    | 0.5                         | μV/°C  |

|                        | Full-scale error (4)                       |                                                            | -0.8%    | 0.2%   | 0.8%                        |        |

|                        | Full-scale error drift                     |                                                            |          |        | 150                         | PPM/°C |

|                        | Effective input resistance                 | ADC enabled                                                | 2.5      |        |                             | ΜΩ     |

| ADC                    |                                            |                                                            |          |        |                             |        |

|                        | Input voltage range for                    | TS1                                                        | -0.2     |        | 0.8 x<br>V <sub>REG27</sub> | V      |

|                        | Conversion time                            |                                                            |          | 31.5   |                             | ms     |

|                        | Resolution (no missing                     | codes)                                                     | 16       |        |                             | Bits   |

|                        | Effective resolution                       |                                                            |          | 15     |                             | Bits   |

|                        | Integral nonlinearity                      | -0.1 V to 0.8 x V <sub>ref</sub>                           |          |        | ±0.020                      | %FSR   |

|                        | Offset error (5)                           |                                                            |          | 70     | 160                         | μV     |

|                        | Offset error drift                         |                                                            |          | 25     |                             | μV/°C  |

|                        | Full-scale error                           | V <sub>IN</sub> = 1 V                                      | -0.8%    | ±0.2%  | 0.4%                        |        |

|                        | Full –scale error drift                    |                                                            |          |        | 150                         | PPM/°C |

|                        | Effective input resistan                   | ce                                                         | 8        |        |                             | ΜΩ     |

| External Ce            | II Balance Drive                           |                                                            |          |        |                             |        |

| D                      | Internal pull-down resistance for external | Cell balance ON for VC1, VCx – VCx + 4 V, where x = 1 to 2 |          | 3.7    |                             | kΩ     |

| R <sub>BAL_drive</sub> | cell balance                               | Cell balance ON for VC2, VCx – VCx + 4 V, where x = 1 to 2 |          | 1.75   |                             | K\$2   |

| Cell Voltage           | Monitor                                    |                                                            |          |        |                             |        |

|                        | CELL Voltage                               | $T_A = -10^{\circ}\text{C to } 60^{\circ}\text{C}$         |          | ±10    | ±20                         |        |

|                        | Measurement<br>Accuracy                    | $T_A = -20^{\circ}\text{C to } 85^{\circ}\text{C}$         |          | ±10    | ±35                         | mV     |

|                        |                                            |                                                            |          |        |                             |        |

<sup>(3)</sup> Post-Calibration Performance

Uncalibrated performance. This gain error can be eliminated with external calibration.

Channel to Channel Offset

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}$ C to 85°C and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}$ C to 85°C and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}$ C to 85°C and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}$ C to 85°C and  $V_{BAT} = V_{PACK} = 7.2 \text{ V}$ , Min/Max values stated where  $T_A = -20^{\circ}$ C to 85°C and  $V_{BAT} = 0.20^{\circ}$ C to 85°C and  $V_{BAT} = 0$

| ı                        | PARAMETER                                               | TEST CONDITION                                                                                                                                                                           | (1)              | MIN  | TYP  | MAX  | UNIT   |

|--------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|--------|

| Internal Ter             | nperature Sensor                                        |                                                                                                                                                                                          |                  |      |      |      |        |

| T <sub>INT</sub>         | Temperature sensor ad                                   | ccuracy                                                                                                                                                                                  |                  |      | ±3%  |      | °C     |

| Thermistor               | Measurement Support                                     |                                                                                                                                                                                          |                  |      |      |      |        |

| R <sub>ERR</sub>         | Internal resistor drift                                 |                                                                                                                                                                                          |                  |      | ±230 |      | PPM/°C |

| R                        | Internal resistor                                       |                                                                                                                                                                                          |                  |      | 18   | 20   | kΩ     |

| Internal The             | ermal Shutdown                                          |                                                                                                                                                                                          |                  |      |      |      |        |

| T <sub>MAX</sub>         | Maximum REG27 temp                                      | perature (6)                                                                                                                                                                             |                  | 125  |      | 175  | °C     |

| T <sub>RECOVER</sub>     | Recovery hysteresis te                                  | mperature (6)                                                                                                                                                                            |                  |      | 10   |      |        |

| Current Pro              | tection Thresholds                                      |                                                                                                                                                                                          |                  |      |      |      | •      |

| V <sub>(OCD)</sub>       | OCD detection thresho                                   | ld voltage range, typical                                                                                                                                                                |                  | 50   |      | 200  | mV     |

| $\Delta V_{(OCDT)}$      | OCD detection thresho                                   | ld voltage program step                                                                                                                                                                  |                  |      | 10   |      | mV     |

| V <sub>(SCCT)</sub>      | SCC detection thresho                                   | ld voltage range, typical                                                                                                                                                                |                  | -100 |      | -300 | mV     |

| $\Delta V_{(SCCT)}$      | SCC detection thresho                                   | ld voltage program step                                                                                                                                                                  |                  |      | -50  |      | mV     |

| V <sub>(SCDT)</sub>      | SCD detection thresho                                   | ld voltage range, typical                                                                                                                                                                |                  | 100  |      | 450  | mV     |

| $\Delta V_{(SCDT)}$      | SCD detection thresho                                   | ld voltage program step                                                                                                                                                                  |                  |      | 50   |      | mV     |

| V <sub>(OFFSET)</sub>    | SCD, SCC, and OCD of                                    | offset                                                                                                                                                                                   |                  | -10  |      | 10   | mV     |

| V <sub>(Scale_Err)</sub> | SCD, SCC, and OCD s                                     | scale error                                                                                                                                                                              |                  | -10% |      | 10%  |        |

|                          | tection Timing                                          |                                                                                                                                                                                          |                  | 1    |      |      |        |

| t <sub>(OCDD)</sub>      | Overcurrent in discharge                                | ne delav                                                                                                                                                                                 |                  | 1    |      | 31   | ms     |

| t <sub>(OCDD_STEP)</sub> | OCDD Step options                                       | ,,                                                                                                                                                                                       |                  |      | 2    |      | ms     |

| t <sub>(SCDD)</sub>      | Short circuit in discharg                               | ne delav                                                                                                                                                                                 |                  | 0    |      | 1830 | μs     |

| t <sub>(SCDD_STEP)</sub> | SCDD Step options                                       | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                  |                  |      | 122  |      | μs     |

|                          | Short circuit in charge                                 | delav                                                                                                                                                                                    |                  | 0    | 122  | 915  | μs     |

| t(SCCD)                  | SCCD Step options                                       | uciay                                                                                                                                                                                    |                  |      | 61   | 313  | μs     |

| t(SCCD_STEP)             | Current fault detect                                    | V <sub>SRP-SRN</sub> = V <sub>THRESH</sub> + 12.5 mV,                                                                                                                                    |                  |      | 01   |      | μο     |

| t <sub>(DETECT)</sub>    | time                                                    | $T_A = -20^{\circ}\text{C to } 85^{\circ}\text{C}$                                                                                                                                       |                  |      | 35   | 160  | μs     |

| t <sub>ACC</sub>         | Overcurrent and short<br>circuit delay time<br>accuracy | Accuracy of typical delay time with no WDI                                                                                                                                               | input            | -50% |      | 50%  |        |

| P-CH FET D               | rive                                                    | •                                                                                                                                                                                        |                  | •    |      |      |        |

| .,                       | Output voltage,                                         | $ \begin{vmatrix} V_{O(\text{FETONDSG})} = V_{(BAT)} - V_{(DSG)}, \\ R_{GS} = 1 \text{ MO}, T_{A} = -20 \text{ to } 110^{\circ}\text{C}, \\ BAT = 7.2 \text{ V}^{(7)} \\ \end{vmatrix} $ |                  | 6    | 6.5  | BAT  | V      |

| V <sub>O(FETON)</sub>    | charge and discharge<br>FETs on                         | V <sub>O(FETONCHG)</sub> = V <sub>(PACK)</sub> - V <sub>(CHG)</sub> ,<br>R <sub>GS</sub> = 1 MΩ, T <sub>A</sub> = -20 to 110°C,<br>PACK = 7.2 V <sup>(7)</sup>                           |                  | 6    | 6.5  | PACK | V      |

| V                        | Output voltage, charge and discharge                    | $V_{O(FETOFFDSG)} = V_{(BAT)} - V_{(DSG)},$<br>$T_A = -20^{\circ}C$ to 110°C, BAT = 7.2 V                                                                                                |                  |      |      | 0.2  | V      |

| V <sub>O(FETOFF)</sub>   | FETs off                                                | $V_{O(FETOFFCHG)} = V_{(PACK)} - V_{(CHG)},$<br>$T_A = -20^{\circ}C$ to 110°C, PACK = 7.2 V                                                                                              |                  |      |      | 0.2  | V      |

| +                        | Rise time                                               | C <sub>L</sub> = 4700 pF                                                                                                                                                                 | VDSG: 10% to 90% |      | 40   | 200  |        |

| t <sub>r</sub>           | Mac mile                                                | OL - 4100 PI                                                                                                                                                                             | VCHG: 10% to 90% |      | 40   | 200  | - µs   |

| t,                       | Fall time $C_1 = 4700 \text{ pF}$                       |                                                                                                                                                                                          | VDSG: 90% to 10% |      | 40   | 200  | μο     |

| t <sub>f</sub>           | . an unio                                               | о <sub>г</sub> 1100 bi                                                                                                                                                                   | VCHG: 90% to 10% |      | 40   | 200  |        |

<sup>(6)</sup> Specified by design. Not production tested. (7) For a  $V_{BAT}$  or  $V_{PACK}$  input range of 3.8 V to 18.75 V, MIN  $V_{O(FETON)}$  voltage is 9 V or  $V_{(BAT)} - 1$  V, whichever is less.

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = V_{PACK} = 7.2$  V, Min/Max values stated where  $T_A = -20^{\circ}$ C to 85°C and  $V_{BAT} = V_{PACK} = 3.8$  V to 18.75 V over operating free-air temperature range (unless otherwise noted)

| F                        | ARAMETER                                                                                | TEST CONDITION                                                                      | <b>J</b> <sup>(1)</sup>                | MIN | TYP  | MAX                       | UNIT |

|--------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------|-----|------|---------------------------|------|

| Pre-Charge/              | ZVCHG FET Drive                                                                         |                                                                                     |                                        | '   |      |                           | ,    |

| V <sub>(PreCHGON)</sub>  | $V_{O(PreCHGON)} = V_{(PACK)}$<br>- $V_{(ZVCHG)}$ , pre-charge<br>FET on <sup>(8)</sup> | R <sub>GS</sub> = 1 MΩ, V <sub>PACK</sub> = 10 V                                    |                                        | 9   | 9.5  | 10                        | V    |

| V <sub>(PreCHGOFF)</sub> | Output voltage,<br>pre-charge FET off <sup>(8)</sup>                                    | $R_{GS} = 1 \text{ M}\Omega$ , $T_A = -20^{\circ}\text{C}$ to $110^{\circ}\text{C}$ |                                        |     |      | V <sub>BAT</sub> –<br>0.5 | V    |

| t <sub>r</sub>           | Rise time                                                                               | $C_L = 4700 \text{ pF},$<br>$R_G = 5.1 \text{ k}\Omega$                             | V <sub>ZVCHG</sub> : 10% to 90%        |     | 80   | 200                       | μs   |

| t <sub>f</sub>           | Fall time                                                                               | $C_L = 4700 \text{ pF},$<br>$R_G = 5.1 \text{ k}\Omega$                             | $V_{ZVCHG:}$ 90% to 10%                |     | 1.7  |                           | ms   |

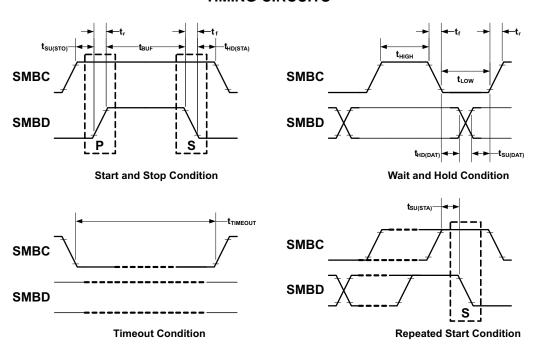

| SMBus                    |                                                                                         |                                                                                     |                                        |     |      |                           |      |

| f <sub>SMB</sub>         | SMBus operating frequency                                                               | Slave mode, SMBC 50% duty cycle                                                     |                                        | 10  |      | 100                       | kHz  |

| f <sub>MAS</sub>         | SMBus master clock frequency                                                            | Master mode, no clock low slave extend                                              | Master mode, no clock low slave extend |     | 51.2 |                           | kHz  |

| t <sub>BUF</sub>         | Bus free time between                                                                   | start and stop                                                                      |                                        | 4.7 |      |                           | μs   |

| t <sub>HD:STA</sub>      | Hold time after (repeate                                                                | ed) start                                                                           |                                        | 4   |      |                           | μs   |

| t <sub>SU:STA</sub>      | Repeated start setup ti                                                                 | me                                                                                  |                                        | 4.7 |      |                           | μs   |

| t <sub>SU:STO</sub>      | Stop setup time                                                                         |                                                                                     |                                        | 4   |      |                           | μs   |

| t <sub>HD:DAT</sub>      | Data hold time                                                                          | Receive mode Transmit mode                                                          |                                        | 300 |      |                           | ns   |

| t <sub>SU:DAT</sub>      | Data setup time                                                                         |                                                                                     |                                        | 250 |      |                           | ns   |

| t <sub>TIMEOUT</sub>     | Error signal/detect                                                                     | See <sup>(9)</sup>                                                                  |                                        | 25  |      | 35                        | ms   |

| t <sub>LOW</sub>         | Clock low period                                                                        |                                                                                     |                                        | 4.7 |      |                           | μs   |

| t <sub>HIGH</sub>        | Clock high period                                                                       | See (10)                                                                            |                                        | 4   |      | 50                        | μs   |

| t <sub>LOW:SEXT</sub>    | Cumulative clock low slave extend time                                                  | See (11)                                                                            |                                        |     |      | 25                        | ms   |

| t <sub>LOW:MEXT</sub>    | Cumulative clock low master extend time                                                 | See <sup>(12)</sup>                                                                 |                                        |     |      | 10                        | ms   |

| t <sub>f</sub>           | Clock/data fall time                                                                    | See (13)                                                                            |                                        |     |      | 300                       | ns   |

| t <sub>r</sub>           | Clock/data rise time                                                                    | See (14)                                                                            |                                        |     |      | 1000                      | ns   |

<sup>(8)</sup> For a V<sub>BAT</sub> or V<sub>PACK</sub> input range of 3.8 V to 18.75 V, MIN V<sub>O(FETON)</sub> voltage is 9 V or V<sub>(BAT)</sub> – 1 V, whichever is less.

<sup>(9)</sup> The bq28400 times out when any clock low exceeds t<sub>TIMEOUT</sub>.

(10) t<sub>HIGH:MAX</sub> is the minimum bus idle time. SMBC = SMBD = 1 for t > 50 μs causes reset of any transaction involving bq28400 that is in

<sup>(11)</sup> t<sub>LOW:SEXT</sub> is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

<sup>(12)</sup> tLOW:MEXT is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop.

<sup>(13)</sup> Rise time  $t_r = V_{ILMAX} - 0.15$ ) to  $(V_{IHMIN} + 0.15)$ . (14) Fall time  $t_f = 0.9V_{DD}$  to  $(V_{ILMAX} - 0.15)$ .

## PIN EQUIVALENT CIRCUITS

#### **TIMING CIRCUITS**

Figure 1. Timing Conditions

#### **GENERAL OVERVIEW**

The bq28400 has a flexible architecture that enables development of numerous battery-management solutions. The device is a fully integrated battery manager, as shown in the functional block diagram, and performs necessary calculations and control for a fully functional 2-series cell battery management system. The device provides flexible user settings that are stored in flash memory.

The bq28400 determines battery capacity by monitoring the amount of charge input or removal from 2-series cell Li-lon rechargeable batteries via a small value series sense resistor. The device then controls and reports the battery status using corrections for environmental and operating conditions. Additional control and monitoring is implemented for individual cell voltages, temperature, and current.

#### **FEATURE SET**

## **Safety Features**

The bq28400 supports a wide range of battery and system protection features that can be configured. The primary safety features include:

- Cell over/undervoltage protection

- · Overcurrent during charge and discharge

- Short circuit

- Overtemperature during charge and discharge

- Device watchdog timer

The secondary safety features used to indicate more serious faults which can be used to control FET state or blow an in-line fuse to permanently disable the battery pack include:

- Safety overvoltage

- · Safety undervoltage

- Safety overcurrent in charge and discharge

- Safety overtemperature in charge and discharge

- Charge, pre-charge, and discharge FET fault

- · Cell imbalance detection

## **Charge Control**

The bq28400 charge control features include:

- Reporting charging current needed for constant current charging and charging voltage needed for constant voltage charging to a smart charger using SMBus communications

- · Supports pre-charging/zero-volt charging

- Supports fast charging

- Supports charge inhibit and charge suspend if battery pack temperature is out of temperature range

- · Reports charging fault and also indicate charge status via charge and discharge alarms

## **Gas Gauging**

The device uses advanced Compensated End-of-Discharge Voltage (CEDV) technology to measure and calculate the available charge capacity in battery cells under system use and environmental conditions. The device accumulates a measure of charge and discharge currents, then compensates the charge current measurement for temperature and the state-of-charge of the battery. The bq28400 further estimates battery self-discharge, adjusts the self-discharge estimation for temperature, and then updates internal status registers. These internal registers are made available to the system host via the two-wire SMBus.

The internal general-purpose SRAM can be powered by the RBI pin of the bq28400 if power is lost. Typically, a 0.1-µF capacitor provides the necessary voltage to the SRAM array during inadvertent momentary power loss.

See the bq28400 technical reference guide for further details.

#### Lifetime Data Logging

The bq28400 maintains the highest temperature value from the last device reset.

#### **Power Modes**

The bq28400 supports three power modes to reduce power consumption:

- In Normal Mode, the device performs measurements, calculations, protection decisions, and data updates in 1-second intervals. Between these intervals, the device is in a reduced power stage.

- In Sleep Mode, the bq28400 performs measurements, calculations, protection decisions and data updates in longer intervals. Between these intervals, the device is in a reduced power stage.

- A wake function operates so that an exit from Sleep mode occurs when current flow, detection of failure,

or SMBus activity detected.

In Shutdown Mode, the bq28400 is completely disabled by turning off all FETs and powering down the bq28400.

#### CONFIGURATION

#### **Oscillator Function**

The bq28400 fully integrates the system oscillator; therefore, no external components are required for this feature.

#### **System Present Operation**

The device checks the PRES pin periodically. If the PRES pin input is pulled to ground by the external system, the bq28400 detects this event as the presence of the system.

#### 2-Series Cell Configuration

The bq28400 supports 2-series cell battery pack configurations.

#### **Cell Balancing Configuration**

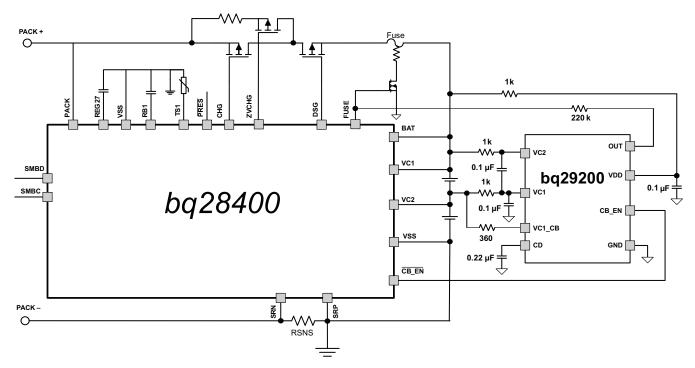

If cell balancing is required, the bq28400 cell balance control enables a weak, internal pull-down for each VCx pin. The purpose of this weak pull-down is to enable an external FET for current bypass. Series resistors placed between the input VCx pins and the positive battery cell terminals control the VGS of the external FET. Alternatively, CB\_EN output can be used with the bq29200 device to control the auto cell-balancing feature for the system (see Figure 5). Further details are provided in the APPLICATION INFORMATION section of this document.

#### **BATTERY PARAMETER MEASUREMENTS**

The bq28400 uses an integrating delta-sigma analog-to-digital converter (ADC) for current measurement, and a second delta-sigma ADC for individual cell voltage, battery voltage, and temperature measurements. The individual cell voltages, *Voltage*, *Current*, *AverageCurrent*, and *Temperature* are updated in 1-second intervals during normal operation.

#### **Charge and Discharge Counting**

The integrating ADC measures the charge and discharge flow of the battery by monitoring a small-value sense resistor between the SRP and SRN pins. The bq28400 integrating ADC measures bipolar signals across the SRP and SRN pins from -0.20~V to 0.25~V induced by current through the sense resistor (typically 5 m $\Omega$  to 20 m $\Omega$ ). Charge activity is detected when  $V_{SR} = V_{SRP} - V_{SRN}$  is positive and discharge activity when  $V_{SR} = V_{SRP} - V_{SRN}$  is negative. The bq28400 continuously integrates the signal over time, using an internal counter and updates *RemainingCapacity* with the charge or discharge amount every second.

#### Voltage

While monitoring the SRP and SRN pins for charge and discharge currents, the bq28400 monitors the individual series cell voltages. The internal bq28400 ADC then measures the voltage, scales, applies offsets, and calibrates it appropriately.

#### NOTE

For accurate differential voltage sensing, the VSS ground should be connected directly to the most negative terminal of the battery stack, not to the positive side of the sense resistor. This minimizes the voltage drop across the PCB trace.

#### **Voltage Calibration and Accuracy**

The bq28400 is calibrated for voltage prior to shipping from TI. The bq28400 voltage measurement signal chain (ADC, high voltage translation, circuit interconnect) is calibrated for each cell. The external filter resistors, connected from each cell to the VCx input of the bq28400, are required to be 1 k $\Omega$ . If different voltage accuracy is desired, customer voltage calibration is required.

www.ti.com

#### Current

The bq28400 uses the SRP and SRN inputs to measure and calculate the battery charge and discharge current using a 5-m $\Omega$  to 20-m $\Omega$  typical sense resistor.

#### **Temperature**

The bq28400 has an internal temperature sensor and input pin for an external temperature sensor. The bq28400 can be configured to use either the internal or external temperature sensor. The default setting for the bq28400 is for a Semitec 103AT thermistor as input to the TS1 pin. Reporting of measured temperature is available by way of the SBS Temperature command.

## **COMMUNICATIONS**

The bq28400 uses SMBus v1.1 in Slave Mode per the SBS specification.

## **SBS Commands**

**Table 1. SBS COMMANDS**

| SBS<br>Command | Mode | Name                  | Format | Min Value | Max Value | Default<br>Value | Unit             |

|----------------|------|-----------------------|--------|-----------|-----------|------------------|------------------|

| 0x00           | R/W  | ManufacturerAccess    | H2     | 0x0000    | 0xffff    | _                |                  |

| 0x03           | R/W  | BatteryMode           | H2     | 0x0000    | 0xe383    | _                |                  |

| 0x08           | R    | Temperature           | U2     | 0         | 65535     | _                | 0.1°K            |

| 0x09           | R    | Voltage               | U2     | 0         | 65535     | _                | mV               |

| 0x0a           | R    | Current               | 12     | -32768    | 32767     | _                | mA               |

| 0x0b           | R    | AverageCurrent        | 12     | -32768    | 32767     | _                | mA               |

| 0x0c           | R    | MaxError              | U1     | 0         | 100       | _                | %                |

| 0x0d           | R    | RelativeStateOfCharge | U1     | 0         | 100       | _                | %                |

| 0x0f           | R/W  | RemainingCapacity     | U2     | 0         | 65535     | _                | mAh or 10<br>mWh |

| 0x10           | R    | FullChargeCapacity    | U2     | 0         | 65535     | 7200             | mAh              |

| 0x14           | R    | ChargingCurrent       | U2     | 0         | 65534     | 2500             | mA               |

| 0x15           | R    | ChargingVoltage       | U2     | 0         | 65534     | 12600            | mV               |

| 0x16           | R    | BatteryStatus         | U2     | 0x0000    | 0xdbff    | _                |                  |

| 0x17           | R/W  | CycleCount            | U2     | 0         | 65535     | 0                |                  |

| 0x18           | R/W  | DesignCapacity        | U2     | 0         | 65535     | 7200             | mAh              |

| 0x19           | R/W  | DesignVoltage         | U2     | 0         | 65535     | 10800            | mV               |

| 0x1a           | R/W  | SpecificationInfo     | H2     | 0x0000    | 0xffff    | 0x0031           |                  |

| 0x1b           | R/W  | ManufactureDate       | U2     | _         | _         | 0                | ASCII            |

| 0x1c           | R/W  | SerialNumber          | H2     | 0x0000    | 0xffff    | 0x0001           |                  |

| 0x20           | R/W  | ManufacturerName      | S12    | _         | _         | Texas Inst.      | ASCII            |

| 0x21           | R/W  | DeviceName            | S8     | _         | _         | bq28400          | ASCII            |

| 0x22           | R/W  | DeviceChemistry       | S5     | _         | _         | LION             | ASCII            |

| 0x23           | R/W  | ManufacturerData      | S9     | _         | _         | _                | ASCII            |

| 0x2f           | R/W  | Authenticate          | S21    | _         | _         | _                | ASCII            |

| 0x3e           | R    | CellVoltage2          | U2     | 0         | 65535     | _                | mV               |

| 0x3f           | R    | CellVoltage1          | U2     | 0         | 65535     | _                | mV               |

## **Extended SBS Commands**

Table 2 shows the extended SBS commands for the device.

**Table 2. Extended SBS Commands**

| SBS<br>Cmd | Mode | Name          | Format | Size in<br>Bytes | Min Value  | Max Value | Default<br>Value | Unit |

|------------|------|---------------|--------|------------------|------------|-----------|------------------|------|

| 0x61       | R/W  | FullAccessKey | hex    | 4                | 0x00000000 | 0xfffffff |                  |      |

| 0x63       | R/W  | AuthenKey3    | hex    | 4                | 0x00000000 | 0xfffffff |                  |      |

| 0x64       | R/W  | AuthenKey2    | hex    | 4                | 0x00000000 | 0xfffffff | _                |      |

| 0x65       | R/W  | AuthenKey1    | hex    | 4                | 0x00000000 | 0xfffffff | _                |      |

| 0x66       | R/W  | AuthenKey0    | hex    | 4                | 0x00000000 | 0xfffffff |                  |      |

16

#### APPLICATION INFORMATION

## **Run Time to Empty**

To predict how much run time the battery pack can supply to the host system, a "Run Time To Empty" value can be calculated.

The SBS host system needs to read, store, and update the following values during a discharging period and average them over a user-determined period of time:

- DSG bit of the BatteryStatus register (ensure that it is in discharge mode)

- AverageCurrent (mA)

- Positive value = charge current

- Negative value = discharge current

- One minute rolling average of current (the user can accumulate this time for improved granularity)

- RemainingCapacity (mAh)

#### Then calculating:

RunTimeToEmpty = RemainingCapacity(avg mAh) ÷ AverageCurrent(avg mA) (The result will be in hours. For minutes, the user can take the above results and divide by 60.)

## **Charging Time to Full**

To predict how much charging time before the battery pack is fully charged, a "Run Time To Full" value can be calculated.

The SBS host system needs to read, store, and update the following values during a charging period and average them over a user-determined period of time:

- DSG bit of the BatteryStatus register (specify in charge mode)

- AverageCurrent (mA)

- Positive value = charge current

- Negative value = discharge current

- One minute rolling average of current (the user can accumulate this time for improved granularity)

- RemainingCapacity (mAh)

## Then calculating:

RunTimeToFull = [FullChargeCapacity(avg mAh) - RemainingCapacity(avg mAh)] ÷ AverageCurrent(avg mA)

#### **Remaining Capacity Alert**

To provide enough time for action to be taken when the battery is below a pre-determined capacity, the user may implement a remaining capacity alarm alert in the SMBus host system. To do this, an SMBus read of the *RemainingCapacity* value should be completed then compared by the SMBus host to a user-selected value. If the read *RemainingCapacity* value is < the user's Remaining Capacity, then the host system should instruct the user of what action is needed.

## **Remaining Time Alert**

Similar to the Remaining Capacity notification, the system operation may need an alarm notification based on time rather than remaining capacity. To do this, a determination of the *EndTimeToEmpty* (as discussed below) and compared by SMBus host to a user-selected remaining time limit value. If the *RemainingTimeLimit* value is < *EndTimeToEmpty*, then the host system should instruct the user of the action to be taken.

#### **Cell Balancing**

Cell balancing increases the useful life of battery packs. Cell-to-cell differences in self-discharge, capacity, and impedance can lead to different charge states among the cells; however, the charger terminates the charge based on the summed voltage only, which may leave some cells undercharged and others overcharged. To remedy this imbalance and to achieve the goal of having all cells reach 100% state-of-charge at charge termination, it is necessary to reduce the charge added to the overcharged cells by creating a current bypass during charging.

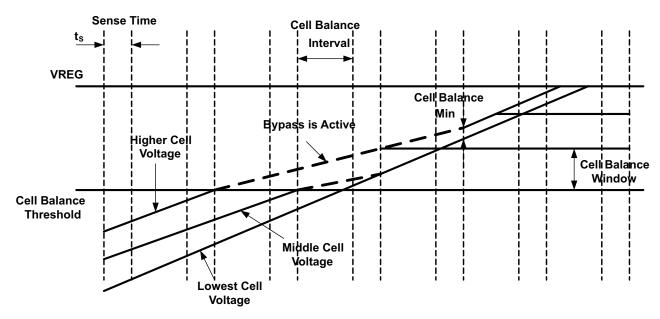

Cell balancing in the bq28400 is accomplished by connecting an external parallel bypass load to each cell and enabling the bypass load depending on each individual cell's charge state. The bypass load is typically formed by a P-CH MOSFET and a resistor. The series resistors that connect the cell tabs to VC1~VC2 pins of the bq28400 are required to be 1 k $\Omega$ . The bq28400 balances the cells during charge by discharging those cells above the threshold set in *Cell Balance Threshold*, if the maximum difference in cell voltages exceeds the value programmed in *Cell Balance Min*. During cell balancing, the bq28400 measures the cell voltages at an interval set in *Cell Balance Interval*. On the basis of the cell voltages, the bq28400 either selects the appropriate cell to discharge or adjusts the cell balance threshold up by the value programmed in *Cell Balance Window* when all cells exceed the cell balance threshold or the highest cell exceeds the cell balance threshold by the cell balance window.

Cell balancing only occurs when charging current is detected and the cell balance threshold is reset to the value in *Cell Balance Threshold* at the start of every charge cycle. The threshold is only adjusted once during any balance interval.

Figure 2. Cell Balance

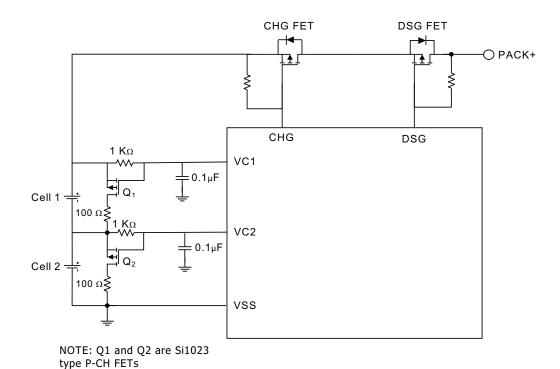

The bq28400 supports cell balancing using an external MOSFET, as illustrated in Figure 3.

Figure 3 shows an example of a cell-balancing circuit for a 2-series cell application. In this circuit, Q1 and Q2 are the external MOSFETs—specifically, Si1023 P-channel MOSFETs. These FETs were chosen because of its low gate-to-source threshold voltage.

Figure 3. Internal Cell Balancing Control Circuit

Figure 4. External Auto Cell Balancing Circuit

## **Layout Recommendations**

For an accurate differential voltage sensing, the VSS ground should be connected directly to the most negative terminal of the battery stack, not to the positive side of the sense resistor. This minimizes the voltage drop across the PCB trace.

Figure 5. Application Schematic

## PACKAGE OPTION ADDENDUM

6-Feb-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | _    |                            | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|--------------------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing            |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| BQ28400PW        | ACTIVE | TSSOP        | PW                 | 20   | 70   | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-2-260C-1 YEAR | -40 to 85    | BQ28400        | Samples |

| BQ28400PWR       | ACTIVE | TSSOP        | PW                 | 20   | 2000 | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-2-260C-1 YEAR | -40 to 85    | BQ28400        | Samples |