# PART NUMBER TMS9900JDL-ROCV

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

#### 1. INTRODUCTION

#### 1.1 DESCRIPTION

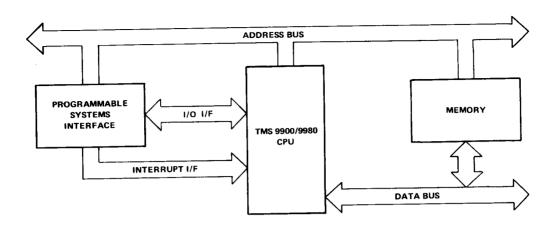

The TMS 9901 Programmable Systems Interface is a multifunctioned component designed to provide low cost interrupts and I/O ports in a 9900/9980 microprocessor system. It is fabricated with N-channel silicon-gate technology and is completely TTL compatible on all inputs and outputs including the power supply (+ 5 V) and single-phase clock. The Programmable Systems Interface provides a 9900/9980 system with interrupt control, I/O ports, and a real-time clock as shown in Figure 1.

#### 1.2 KEY FEATURES

- N-channel Silicon-Gate Process

- 9900 Series CRU Peripheral

- Performs Interrupt and I/O Interface Functions

- 6 Dedicated Interrupt Input Lines

- 7 Dedicated I/O Ports

- 9 Ports Programmable as Interrupts or I/O

- Easily Stacked for Interrupt and I/O Expansion

- Interval and Event Timer

- Single 5 V Supply

#### 2. FUNCTIONAL DESCRIPTION

#### 2.1 CPU INTERFACE

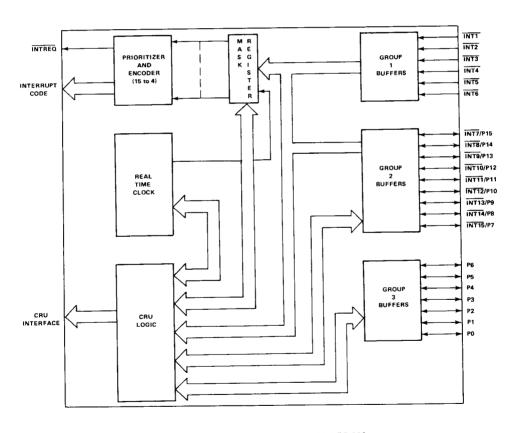

The TMS 9901 interfaces to the CPU through the Communications Register Unit (CRU) and the interrupt control lines as shown in Figure 2. The CRU interface consists of 5 address select lines (S0-S4), chip enable (CE), and 3 CRU lines (CRUIN, CRUOUT, CRUCLK). When CE becomes active (Iow), the 5 select lines point to the CRU bit being accessed (see Table 1). In the case of a write, the datum is strobed off the CRUOUT line by the CRUCLK signal. For a read, the datum is sent to the CPU on the CRUIN line. The interrupt control lines consist of an interrupt request line (INTREQ) and 4 code lines (ICO-IC3). The interrupt section of the TMS 9901 prioritizes and encodes the highest priority active interrupt into the proper code to present to the CPU, and outputs this code on the ICO-IC3 code lines along with an active INTREQ. Several TMS 9901's can be used with the CPU by connecting all CRU and address lines in parallel and providing a unique chip select to each device.

#### 2.2 SYSTEM INTERFACE

The system interface consists of 22 pins divided into 3 groups. The 6 pins in Group 1 ( $\overline{INTI} - \overline{INT6}$ ) are normally dedicated to interrupt inputs (active low), but may also be used as input ports (true data in). Group 2 ( $\overline{INT7/P15} - \overline{INT15/P7}$ ) consists of 9 pins which can be individually programmed as interrupt inputs (active low), input ports (true data in), or output ports (true data out). The remaining 7 pins which comprise Group 3 (P0–P6) are dedicated as individually programmable I/O ports (true data).

#### 2.3 INTERRUPT CONTROL

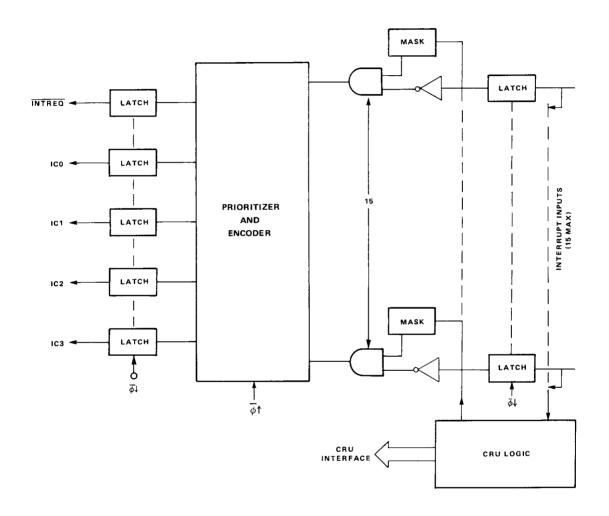

A block diagram of the interrupt control section is shown in Figure 3. The interrupt inputs (6 dedicated, 9 programmable) are sampled by  $\overline{\phi}$  (active low) and are ANDED with their respective mask bits. If an interrupt input is active (low) and enabled (MASK=1), the signal is passed through to the priority encoder where the highest priority signal is encoded into a 4 bit binary code as shown in Table 2. The code along with interrupt request is then output via the CPU interface on the leading edge of the next  $\overline{\phi}$  to ensure proper synchronization to the processor.

FIGURE 1 - 9900/9980 SYSTEM

FIGURE 2 - TMS 9901 BLOCK DIAGRAM

TABLE 1

CRU BIT ASSIGNMENTS

| CRU Bit | S <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> | CRU Read Data            | CRU Write Data  |

|---------|----------------------------------------------------------------------------|--------------------------|-----------------|

| 0       | 0 0 0 0                                                                    | CONTROL BIT(1)           | CONTROL BIT(1)  |

| 1       | 0 0 0 0 1                                                                  | INT1/CLK1 <sup>(2)</sup> | Mask 1/CLK1(3)  |

| 2       | 0 0 0 1 0                                                                  | INT2/CLK2                | Mask 2/CLK2     |

| 3       | 0 0 0 1 1                                                                  | . INT3/CLK3              | Mask 3/CLK3     |

| 4       | 0 0 1 0 0                                                                  | INT4/CLK4                | Mask 4/CLK4     |

| 5       | 0 0 1 0 1                                                                  | INT5/CLK5                | Mask 5/CLK5     |

| 6       | 0 0 1 1 0                                                                  | INT6/CLK6                | Mask 6/CLK6     |

| 7       | 0 0 1 1 1                                                                  | INT7/CLK7                | Mask 7/CLK7     |

| 8       | 0 1 0 0 0                                                                  | INT8/CLK8                | Mask 8/CLK8     |

| 9       | 0 1 0 0 1                                                                  | INT9/CLK9                | Mask 9/CLK9     |

| 10      | 0 1 0 1 0                                                                  | INT10/CLK10              | Mask 10/CLK10   |

| 11      | 0 1 0 1 1                                                                  | INT11/CLK11              | Mask 11/CLK11   |

| 12      | 0 1 1 0 0                                                                  | INT12/CLK12              | Mask 12/CLK12   |

| 13      | 0 1 1 0 1                                                                  | INT13/CLK13              | Mask 13/CLK13   |

| 14      | 0 1 1 1 0                                                                  | INT14/CLK14              | Mask 14/CLK14   |

| 15      | 0 1 1 1 1                                                                  | INT15/INTREQ             | Mask 15/RST2(4) |

| 16      | 1 0 0 0 0                                                                  | PO Input(5)              | PO Output(6)    |

| 17      | 1 0 0 0 1                                                                  | P1 Input                 | P1 Output       |

| 18      | 10010                                                                      | P2 Input                 | P2 Output       |

| 19      | 1 0 0 1 1                                                                  | P3 Input                 | P3 Output       |

| 20      | 10100                                                                      | P4 Input                 | P4 Output       |

| 21      | 1 0 1 0 1                                                                  | P5 Input                 | P5 Output       |

| 22      | 1 0 1 1 0                                                                  | P6 Input                 | P6 Output       |

| 23      | 1 0 1 1 1                                                                  | P7 Input                 | P7 Output       |

| 24      | 1 1 0 0 0                                                                  | P8 Input                 | P8 Output       |

| 25      | 1 1 0 0 1                                                                  | P9 Input                 | P9 Output       |

| 26      | 1 1 0 1 0                                                                  | P10 Input                | P10 Output      |

| 27      | 1 1 0 1 1                                                                  | P11 Input                | P11 Output      |

| 28      | 1 1 1 0 0                                                                  | P12 Input                | P12 Output      |

| 29      | 1 1 1 0 1                                                                  | P13 Input                | P13 Output      |

| 30      | 1 1 1 1 0                                                                  | P14 Input                | P14 Output      |

| 31      | 1 1 1 1 1                                                                  | P15 Input                | P15 Output      |

NOTES: (1) 0 = Interrupt Mode 1 = Clock Mode

- (2) Data present on INT input pin (or clock value) will be read regardless of mask value.

- (3) While in the Interrupt Mode (Control Bit = 0) writing a "1" into mask will enable interrupt; a "0" will disable.

- (4) Writing a zero to bit 15 while in the clock mode (control bit = 1) executes a software reset of the I/O pins.

- (5) Data present on the pin will be read. Output data can be read without affecting the data.

- (6) Writing data to the port will program the port to the output mode and output the data.

FIGURE 3 - INTERRUPT CONTROL LOGIC

TABLE 2

INTERRUPT CODE GENERATION

| NTERRUPT/STATE | PRIORITY    | ICO | l <sub>C1</sub> | I <sub>C2</sub> | IC3 | INTREQ |

|----------------|-------------|-----|-----------------|-----------------|-----|--------|

|                |             |     |                 |                 |     |        |

| INT 1          | 1 (HIGHEST) | 0   | 0               | 0               | 1   | 0      |

| ĪNT 2          | 2           | 0   | 0               | 1               | 0   | 0      |

| INT 3/CLOCK    | 3           | 0   | 0               | 1               | 1   | 0      |

| ĪNT 4          | 4           | 0   | 1               | 0               | 0   | 0      |

| INT 5          | 5           | 0   | 1               | 0               | 1   | 0      |

| INT 6          | 6           | 0   | 1               | 1               | 0   | 0      |

| ĪNT 7          | 7           | 0   | 1               | 1               | 1   | 0      |

| INT 8          | 8           | 1   | O               | 0               | 0   | 0      |

| INT 9          | 9           | 1   | 0               | 0               | 1   | 0      |

| INT 10         | 10          | 1   | 0               | 1               | 0   | 0      |

| INT 11         | 11          | 1   | 0               | 1               | 1   | 0      |

| INT 12         | 12          | 1   | 1               | 0               | 0   | 0      |

| INT 13         | 13          | 1   | 1               | 0               | 1   | 0      |

| INT 14         | 14          | 1   | 1               | 1               | 0   | 0      |

| INT 15         | 15 (LOWEST) | 1   | 1               | 1               | 1   | 0      |

| NO INTERRUPT   | _           | 1   | 1               | 1               | 1   | 1      |

The output signals will remain valid until the corresponding interrupt input is removed, the interrupt is disabled (MASK=0), or a higher priority enabled interrupt becomes active. When the highest priority enabled interrupt is removed, the code corresponding to the next highest priority enabled interrupt is output. If no enabled interrupt is active, all CPU interface lines (INTREQ, ICO-IC3) are held high. RSTI (power-up-reset) will force the output code to (0,0,0,0) with INTREQ held high and will reset all mask bits low (interrupts disabled). Individual interrupts can be subsequently enabled (disabled) by programming the appropriate command bits. Unused interrupt inputs may be used as datum inputs by disabling the interrupt (MASK=0).

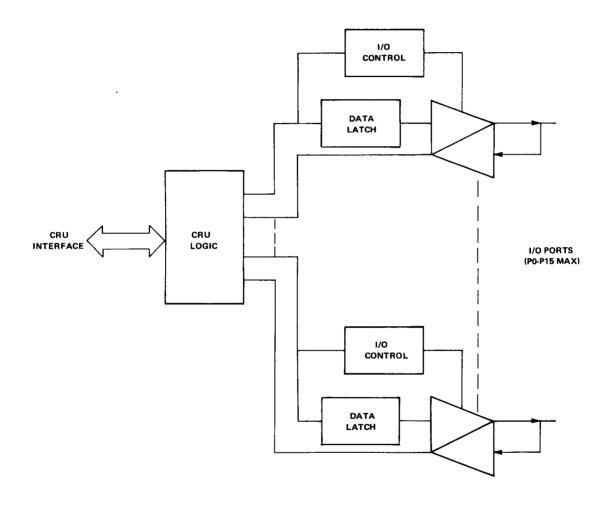

#### 2.4 INPUT/OUTPUT

A block diagram of the I/O section is shown in Figure 4. Up to 16 individually controlled I/O ports are available (7 dedicated, 9 programmable). RST1 or RST2 (a command bit) will program all ports to the input mode. Writing a datum to any port will program that port to the output mode and latch out the datum. The port will then remain in the output mode until either RST1 or RST2 are executed. Data present on the Group 2 pins can be read by either the Read Interrupt Commands or the Read Input Commands. Group 2 pins being used as input ports should have their respective Interrupt Mask values reset (low) to prevent false interrupts from occurring. In applications where Group 1 pins are not required as interrupt inputs, they may be used as input ports and read using the Read Input commands. As with Group 2 ports, any pins being used as input ports should have their respective Interrupt Masks disabled.

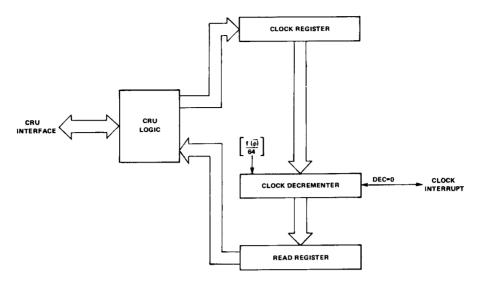

#### 2.5 PROGRAMMABLE REAL TIME CLOCK

A block diagram of the programmable real time clock section is shown in Figure 5. The clock consists of a 14 bit counter that decrements at a rate of  $F(\phi)/64$  (at 3 MHz this results in a maximum interval of 349 ms with a resolution of 21.3  $\mu$ s) and can be used as either an interval timer or as an event timer.

The clock is accessed by writing a one into the control bit (address 0) to force CRU bits 1-15 to clock mode. (See Table 1.) Writing a nonzero value into the clock register then enables the clock and sets its frequency. During system set up this entire operation can be accomplished with one additional I/O instruction (LDCR) as shown in Table 3. The clock functions as an interval timer by decrementing to zero, issuing an interrupt, and restarting at the programmed start

FIGURE 4 - I/O INTERFACE

FIGURE 5 - REAL TIME CLOCK

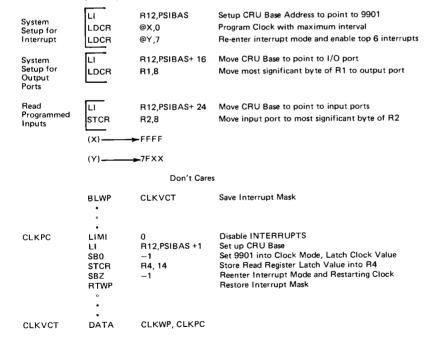

# TABLE 3 SOFTWARE EXAMPLES

#### ASSUMPTIONS

- System uses clock at maximum interval

- Total of 6 interrupts are used

- 8 bits are used as output port

- 8 bits are used as input port

- RSTI (power up reset) has already been applied.

value. When the clock interrupt is active, the clock mask (mask bit 3) must be written into (with either a "1" or a "0") to clear the interrupt.

If a value other than that initially programmed is required, a new 14-bit clock start value is similarly programmed by executing a CRU write operation to the same locations. During programming the decrementer is restarted with the current start value after each start value bit is written. A timer restart can be easily implemented by writing a single bit to any of the clock bits.

The clock is disabled by RSTI (power-up-clear) or by writing a zero value into the clock register. Enabling the clock programs the third priority interrupt (INT3) as the clock interrupt and disables generation of interrupts from the INT3 input pin. When accessing the clock all interrupts should be disabled to ensure that system integrity is maintained.

The clock can also function as an event timer since whenever the device is switched to the clock mode, by writing a one to the control bit, the current value of the clock is stored in the clock read register. Reading this value, and thus the elapsed event time, is accomplished by executing a 14 bit CRU read operation (addresses 1-14). The software example (Table 3) shows a read of the event timer.

The current status of the machine can always be obtained by reading the control (address zero) bit. A "0" indicates the machine is in an interrupt mode. Bits 1 thru 15 would normally be the interrupt input lines in this mode, but if any are not needed for interrupts they may also be read with a CRU input command and interpreted as normal data inputs. A "1" read on the control bit indicates that the 9901 is in the clock mode. Reading bits 1 thru 14 completes the event timer operation as described above. Reading bit 15 indicates whether the interrupt request line is active.

A software reset RST2 can be performed by writing a "1" to the control bit followed by writing a "1" to bit 15, which forces all I/O ports to the input mode.

#### 2.6 SYSTEM OPERATION

During power up RSTI must be activated (low) for a minimum of 2 clock cycles to force the TMS 9901 into a known state. RST1 will disable all interrupts, disable the clock, program all I/O ports to the input mode, and force ICO-IC3 to (0,0,0,0) with INTREQ held high. System software must then enable the proper interrupts, program the clock (if used), and configure the I/O ports as required (See Table 3 for an example). After initial power up, the TMS 9901 will be accessed only as needed to service the clock, enable (disable) interrupts, or read (write) data to the I/O ports. The I/O ports can be reconfigured by use of the RST2 command bit.

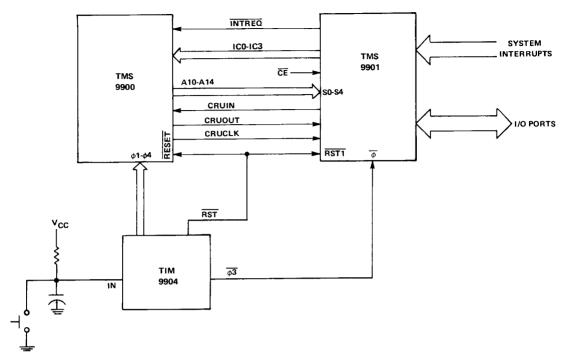

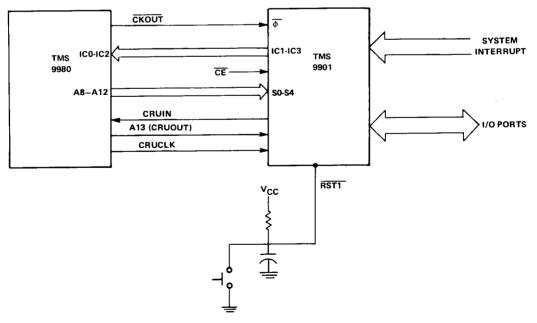

Figure 6 illustrates the use of a TMS 9901 with a TMS 9900. The TIM 9904 is used to generate RST to reset the 9900 and the 9901 (connected to RST1). Figure 7 shows a TMS 9980 system using the TMS 9901. The reset function, load interrupt, and 4 maskable interrupts allowed in a 9980 are encoded as shown in Table 4. Connecting the system as shown ensures that the proper reset will be applied to the 9980.

TABLE 4

9980 INTERRUPT LEVEL DATA

| INTERRUPT<br>CODE<br>(ICO-IC2) | FUNCTION | VECTOR LOCATION<br>(MEMORY ADDRESS<br>IN HEX) | DEVICE ASSIGNMENT | INTERRUPT MASK VALUES<br>TO ENABLE<br>(ST12 THROUGH ST15) |

|--------------------------------|----------|-----------------------------------------------|-------------------|-----------------------------------------------------------|

| 1 1 0                          | Level 4  | 0 0 1 0                                       | External Device   | 4 Through F                                               |

| 1 0 1                          | Level 3  | 0 0 0 C                                       | External Device   | 3 Through F                                               |

| 1 0 0                          | Level 2  | 0 0 0 8                                       | External Device   | 2 Through F                                               |

| 0 1 1                          | Level 1  | 0 0 0 4                                       | External Device   | 1 Through F                                               |

| 0 0 1                          | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                                |

| 0 1 0                          | Load     | 3 F F C                                       | Load Stimulus     | Don't Care                                                |

| 0 0 0                          | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                                |

| 1 1 1                          | No-Op    | ******                                        |                   |                                                           |

FIGURE 6 - TMS 9900-TMS 9901 INTERFACE

FIGURE 7 - TMS 9980-TMS 9901 INTERFACE

## 2.7 PIN DEFINITIONS

Table 5 defines the TMS 9901 pin assignments and describes the function of each pin.

TABLE 5

TMS 9901 PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE                                                                                     | PIN                                                            | 1/0                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |                                           |                                            |               |                                              |                                                                                            |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|---------------|----------------------------------------------|--------------------------------------------------------------------------------------------|

| INTREQ                                                                                        | . 11                                                           | OUT                                                                | INTERRUPT Request. When active (low) INTREQ indicates that an enabled interrupt has been received. INTREQ will stay active until all enabled interrupt inputs are re-                                                                                                                                                           | RST1<br>CRUOUT<br>CRUCLK<br>CRUIN         | 1 [] 2 [] 3 [] 4 []                        |               | 40<br>39<br>38<br>37                         | VCC<br>SO<br>PO<br>P1                                                                      |

| ICO (MSB) IC1 IC2 IC3 (LSB) CE                                                                | 15<br>14<br>13<br>12<br>5                                      | OUT<br>OUT<br>OUT<br>OUT<br>IN                                     | moved.  Interrupt Code lines, ICO-IC3 output the binary code corresponding to the highest priority enabled interrupt. If no enabled interrupts are active ICO-IC3 = (1,1,1,1).  Chip Enable. When active (Iow) data may be transferred through the CRU interface to the CPU. CE has no effect on the interrupt control section. | CE INT6 INT5 INT4 INT3    INTRO INTRO IC3 | 5                                          |               | 36<br>35<br>34<br>33<br>32<br>31<br>30<br>29 | \$1<br>\$2<br> NT7/P15<br> INT8/P14<br> INT9/P13<br> INT10/P12<br> INT11/P11<br> INT12/P10 |

| \$0<br>\$1<br>\$2<br>\$3<br>\$4                                                               | 39<br>36<br>35<br>25<br>24                                     | IN<br>IN<br>IN<br>IN                                               | Address select lines. The data bit being accessed by the CRU interface is specified by the 5-bit code appearing on S0-S4.                                                                                                                                                                                                       | IC1                                       | 13  <br>14  <br>15  <br>16  <br>17  <br>18 |               | 28<br>27<br>26<br>25<br>24<br>23             | NT13/P9<br>NT14/P8<br>P2<br>S3<br>S4<br>NT15/P7                                            |

| CRUIN                                                                                         | 4                                                              | оит                                                                | CRU data in (to CPU). Data specified by S0-S4 is transmitted to the CPU by CRUIN. When $\overline{CE}$ is not active CRUIN is in a high-impedance state.                                                                                                                                                                        |                                           | 19  <br>20                                 | <del></del>   | 22 21                                        | P3<br>P4                                                                                   |

| CRUOUT                                                                                        | 2                                                              | IN                                                                 | CRU data out (from CPU). When $\overline{CE}$ is active, discretely calculated and written into the command bit specific                                                                                                                                                                                                        | -                                         | the Cl                                     | RUOUT in      | put will                                     | be sampled during                                                                          |

| CRUCLK<br>RST1                                                                                | 3                                                              | IN<br>IN                                                           | CRU Clock (from CPU), CRUCLK specifies that val<br>Power Up Reset. When active (low) RST1 resets a<br>I/O ports to inputs. RST1 has a Schmitt-Trigger in<br>Figure 6.                                                                                                                                                           | II interrupt mas                          | ks to "                                    | 0", disable   | s the cloc                                   |                                                                                            |

| VCC<br>VSS<br>Φ<br>INT1<br>INT2<br>INT3                                                       | 40<br>16<br>10<br>17<br>18<br>9                                | IN<br>IN<br>IN                                                     | Supply Voltage. +5 V nominal. Ground Reference System clock ( $\overline{\phi}3$ in TMS 9900 system, CKOUT in Group 1, interrupt inputs. When active. (Low) the signal is ANDed with its corresponding INT1 has highest priority.                                                                                               | •                                         |                                            | ed sent to t  | he interri                                   | upt control section.                                                                       |

| INT4<br>INT5<br>INT6<br>INT7/ P15<br>INT8/ P14<br>INT9/ P13<br>INT10/P12<br>INT11/P11         | 7<br>6<br>34<br>33<br>32<br>31<br>30                           | IN<br>IN<br>I/O<br>I/O<br>I/O<br>I/O                               | Group 2, programmable interrupt (active low) or I an interrupt, an input port, or an output port.                                                                                                                                                                                                                               | /O pins (true lo                          | gic). Ea                                   | ach pin is ii | ndividual                                    | ly programmable as                                                                         |

| INT12/P10<br>INT13/P9<br>INT14/P8<br>INT15/P7<br>P0<br>P1<br>P2<br>P3<br>P3<br>P4<br>P5<br>P6 | 29<br>28<br>27<br>23<br>38<br>37<br>26<br>22<br>21<br>20<br>19 | 1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0 | Group 3, I/O ports (true logic). Each pin is individu                                                                                                                                                                                                                                                                           | ally programma                            | able as a                                  | in input po   | irt or an o                                  | output port.                                                                               |

## 3. TMS 9901 ELECTRICAL SPECIFICATIONS

# 3.1 ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)\*

| Supply voltages, VCC and VSS       |    |    |   |  |  |  |  |  |  |  |  |  | −0.3 V to 10 V   |

|------------------------------------|----|----|---|--|--|--|--|--|--|--|--|--|------------------|

| All input and output voltages .    |    | •  |   |  |  |  |  |  |  |  |  |  | -0.3~V to $10~V$ |

| Continuous power dissipation       |    | -  |   |  |  |  |  |  |  |  |  |  | 0.75 W           |

| Operating free-air temperature rai | na | e. | - |  |  |  |  |  |  |  |  |  | . 0°C to /0 C    |

|                                    |    |    |   |  |  |  |  |  |  |  |  |  |                  |

<sup>\*</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute maximum rated conditions for extended period may affect device reliability.

# 3.2 RECOMMENDED OPERATING CONDITIONS

|                                                                 | MIN  | NOM | MAX             | UNIT |

|-----------------------------------------------------------------|------|-----|-----------------|------|

| Supply voltage, VCC                                             | 4.75 | 5   | 5.25            | V    |

|                                                                 |      | 0   |                 | V    |

| Supply voltage, VSS High-level input voltage, VIH               | 2.2  | 2.4 | V <sub>cc</sub> | V    |

|                                                                 |      | 0.8 | 0.8             | V    |

| Low-level input voltage, VIL Operating free-air temperature, TA | 0    | 25  | 70              | °C   |

# 3.3 ELECTRICAL CHARACTERISTICS OVER FULL RANGE OF RECOMMENDED OPERATING CONDITIONS (UNLESS OTHERWISE NOTED)

|                                               | PARAMETER                       | TEST CONDITIONS                                    | MIN | TYP | MAX  | UNIT |

|-----------------------------------------------|---------------------------------|----------------------------------------------------|-----|-----|------|------|

| 1.                                            | Input current (any input)       | V <sub>I</sub> = 0 V to V <sub>C</sub> C           |     | ±10 | ±100 | μΑ   |

| <u>''                                    </u> | input current (any input)       | ΙΟΗ = -100 μΑ                                      | 2.4 | 2.4 |      | >    |

| Vон                                           | High level output voltage       | ΙΟΗ = -400 μΑ                                      | 2.0 | 2   |      | V    |

| \/-·                                          | Low level output voltage        | I <sub>OL</sub> = 3.2 mA                           |     | 0.4 | 0.65 | V    |

| VOL                                           | Supply current from VCC         | 02                                                 |     | 100 |      | mA   |

|                                               | Supply current from VSS         |                                                    |     | 200 | 200  | mA   |

| ISS<br>CC(av)                                 | Average supply current from VCC | t <sub>C</sub> (φ) = 333 ns, T <sub>A</sub> = 25°C |     | 60  | 200  | mA   |

| Ci                                            | Capacitance, any input          | f = 1 MHz, All other                               |     | 10  | 15   | pF   |

| Co                                            | Capacitance, any output         | Pins at 0 V                                        |     | 20  | 25   | pF   |

# 3.4 TIMING REQUIREMENTS OVER FULL RANGE OF OPERATING CONDITIONS

| -                  | PARAMETER                                          | MIN | NOM | MAX  | UNIT |

|--------------------|----------------------------------------------------|-----|-----|------|------|

|                    | Clock cycle time                                   | 300 | 333 | 2000 | ns   |

| <sup>t</sup> c(φ)  | Clock rise time                                    | 10  | 10  |      | ns   |

| <sup>t</sup> r(φ)  | Clock fall time                                    | 10  | 10  |      | ns   |

| <sup>t</sup> f(φ)  | Clock pulse low width                              | 45  | 55  |      | ns   |

| tw(φL)             | Clock pulse high width                             | 200 | 240 |      | ns   |

| <sup>t</sup> w(φH) | Setup time for S0-S4, CE, or CRUOUT before CRUCLK  |     | 200 | 330  | ns   |

| t <sub>su</sub>    | Setup time, input before valid CRUIN               |     | 200 | 330  | ns   |

| t <sub>su</sub>    | Setup time, interrupt before $\overline{\phi}$ low |     | 40  | 65   | ns   |

| tw(CRUCLK)         | CRU clock pulse width                              | 90  | 100 | 300  | ns   |

| th                 | Address hold time                                  | 80  |     |      | ns   |

# 3.5 SWITCHING CHARACTERISTICS OVER FULL RANGE OF RECOMMENDED OPERATING CONDITIONS

|                 | PARAMETER                                                                                   | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| tPD             | Propagation delay, $\overline{\phi}$ low to valid INTREQ, $1_{\text{CO}}$ - $1_{\text{C3}}$ | C <sub>L</sub> = 100 pF,<br>2 TTL loads |     | 80  | 110 | ns   |

| <sup>t</sup> PD | Propagation delay, S0-S4 or CE<br>to valid CRUIN                                            | C <sub>L</sub> = 100 pF                 |     | 300 | 400 | ns   |

NOTE 1: ALL TIMING MEASUREMENTS ARE FROM 10% and 90% POINTS

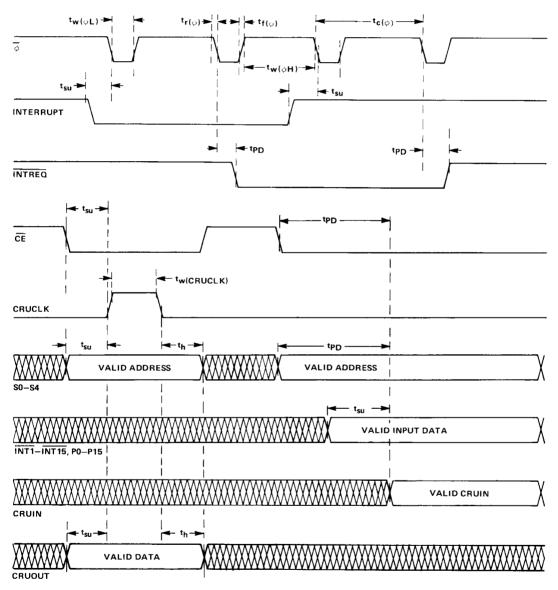

FIGURE 8 - SWITCHING CHARACTERISTICS

#### 4. MECHANICAL DATA

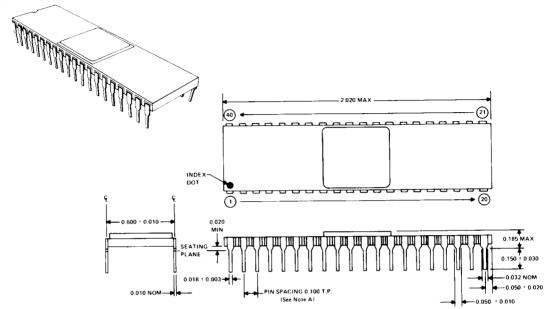

## 4.1 TMS 9901 - 40 PIN CERAMIC PACKAGE

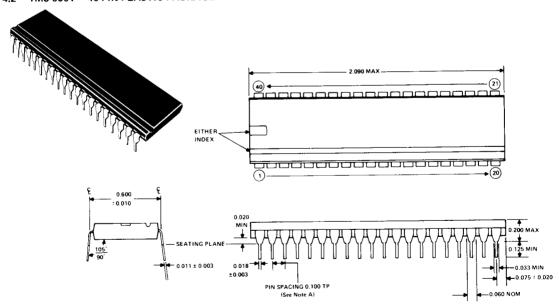

## 4.2 TMS 9901 - 40 PIN PLASTIC PACKAGE

NOTES: A. Each pin centerline is located within 0.010 of its true longitudinal position.

B. All linear dimensions are in inches