# MC9328MXS i.MX Integrated Portable System Processor

Reference Manual

Document Number: MC9328MXSRM

Rev. 1 12/2006

### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-521-6274 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. ARM and the ARM POWERED logo are the registered trademarks of ARM Limited. ARM9, ARM920T, ARM9TDMI, ARMv4T, ARM7, ARM7TDMI, Thumb, and StrongARM are trademarks of ARM Limited. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005, 2006. All rights reserved.

# **Contents**

| Chap<br>Intro                                  | ter 1<br>duction                                                                                           |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------|

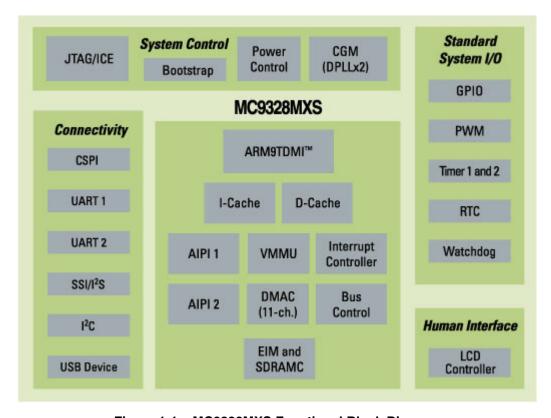

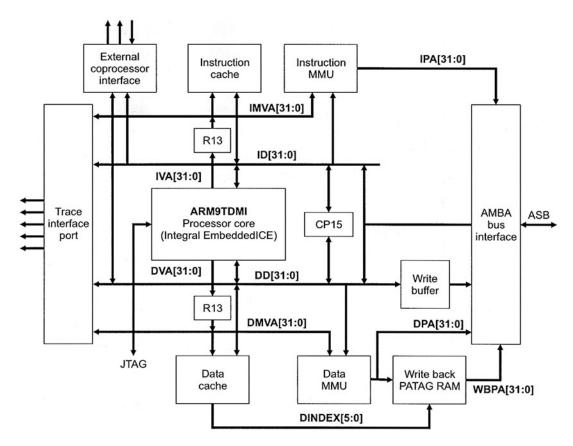

| 1.1                                            | ARM920T Microprocessor Core                                                                                |

| 1.2                                            | AHB to IP Bus Interfaces (AIPIs)1-                                                                         |

| 1.3                                            | External Interface Module (EIM)                                                                            |

| 1.4                                            | SDRAM Controller (SDRAMC)                                                                                  |

| 1.5                                            | Clock Generation Module (CGM) and Power Control Module                                                     |

| 1.6                                            | Two Universal Asynchronous Receiver/Transmitters (UART 1 and UART 2)                                       |

| 1.7                                            | Serial Peripheral Interface (SPI)1-                                                                        |

| 1.8                                            | Two General-Purpose 32-Bit Counters/Timers                                                                 |

| 1.9                                            | Watchdog Timer                                                                                             |

| 1.10                                           | Real-Time Clock/Sampling Timer (RTC)                                                                       |

| 1.11                                           | LCD Controller (LCDC)                                                                                      |

| 1.12                                           | Pulse-Width Modulation (PWM) Module                                                                        |

| 1.13                                           | Universal Serial Bus (USB) Device                                                                          |

| 1.14                                           | Direct Memory Access Controller (DMAC) 1-                                                                  |

| 1.15                                           | Synchronous Serial Interface and Inter-IC Sound (SSI/I <sup>2</sup> S) Module                              |

| 1.16                                           | Inter-IC (I <sup>2</sup> C) Bus Module                                                                     |

| 1.17                                           | General-Purpose I/O (GPIO) Ports                                                                           |

| 1.18                                           | Bootstrap Mode                                                                                             |

| 1.19                                           | Power Management Features                                                                                  |

| 1.20                                           | Operating Voltage Range                                                                                    |

| 1.21                                           | Packaging                                                                                                  |

| Chap<br>Signa                                  | ter 2<br>Il Descriptions and Pin Assignments                                                               |

| 2.1                                            | Signal and Pin Information                                                                                 |

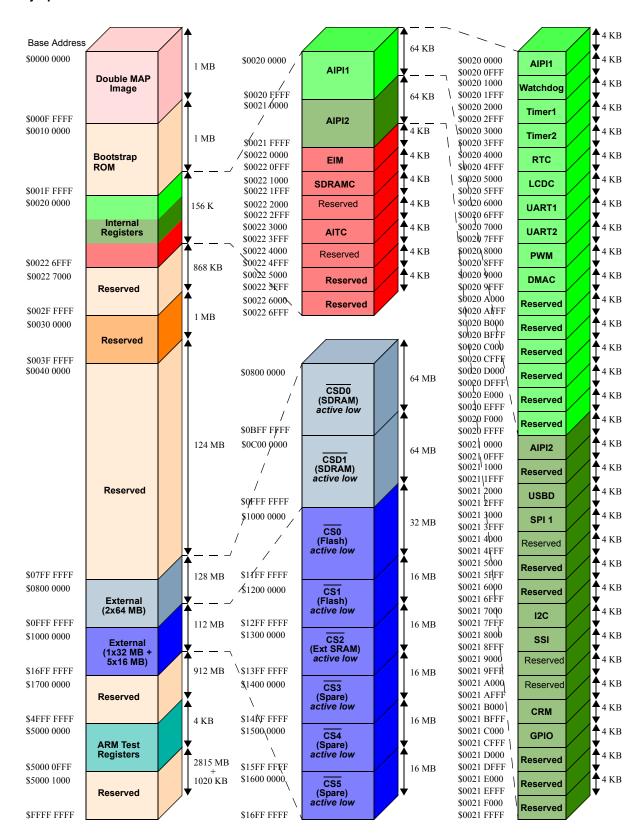

| Chap<br>Memo                                   | ter 3<br>ory Map                                                                                           |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 | Memory Space3-Memory Map3-Internal Register Space3-External Memory3-Double Map Image3-Internal Registers3- |

| Chap<br>ARM                                    | ter 4<br>920T Processor                                                                                    |

4.1 4.2

| 4-3                                    |

|----------------------------------------|

| 4-3                                    |

| 4-3                                    |

| 4-3                                    |

| 4-3                                    |

| 4-4                                    |

| 4-4                                    |

| 4-4                                    |

| 4-4                                    |

| 4-5                                    |

| 4-5                                    |

| 4-5                                    |

| 4-5                                    |

| 4-5                                    |

| 4-6                                    |

| 4-6                                    |

| 4-6                                    |

| 4-7                                    |

| 4-7                                    |

| 4-7                                    |

| <del>1</del> -/                        |

| 4-7                                    |

|                                        |

| 4-7                                    |

| 4-7                                    |

| 4-7                                    |

| 4-7                                    |

| 4-7<br>4-8<br>4-9                      |

| 4-7 4-8 4-9                            |

| 4-7 4-8 4-9 5-1 5-2                    |

| 4-7 4-8 4-9                            |

| 4-7 4-8 4-9 5-1 5-2                    |

| 4-7 4-8 4-9 5-1 5-2                    |

| 4-7 4-8 4-9 5-1 5-2                    |

| 4-7 4-8 4-9 5-1 5-2                    |

| 4-7 4-8 4-9 5-1 5-2 5-2                |

| 4-7<br>4-8<br>4-9<br>5-1<br>5-2<br>5-2 |

| 4-7 4-8 4-9 5-1 5-2 5-2                |

| 4-7 4-8 4-9 5-1 5-2 5-2 6-1 6-1 6-2    |

| 4-7 4-8 4-9 5-1 5-2 5-2 6-1 6-2 6-3    |

| 4-7 4-8 4-9 5-1 5-2 5-2 6-1 6-2 6-3    |

| 4-7 4-8 4-9 5-1 5-2 5-2 6-1 6-2 6-3    |

| 4-7 4-8 4-9 5-1 5-2 5-2 6-1 6-3 6-3    |

| 4-7 4-8 4-9 5-1 5-2 5-2 6-1 6-2 6-3    |

|                                        |

| 7-8                                                   |

|-------------------------------------------------------|

| 7-10                                                  |

| eral Size Register 0 7-10                             |

| eral Size Register 1 7-11                             |

| 7-12                                                  |

| 7-13                                                  |

| 7-14                                                  |

| 7-15                                                  |

| 7-15                                                  |

| 7-16                                                  |

| 7-17                                                  |

|                                                       |

| /-10                                                  |

|                                                       |

|                                                       |

|                                                       |

| 8-1                                                   |

| 8-2                                                   |

| 8-2                                                   |

| 8-4                                                   |

| 0.6                                                   |

| 8-6                                                   |

| 8-6<br>8-7                                            |

|                                                       |

|                                                       |

|                                                       |

|                                                       |

|                                                       |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3                       |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3<br>9-3                |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3                       |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3<br>9-3                |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3<br>9-3<br>9-3         |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3<br>9-3<br>9-3         |

| 9-1<br>9-1<br>9-2<br>9-2<br>9-3<br>9-3<br>9-3<br>9-3  |

| 8-7  9-1  9-1  9-2  9-2  9-3  9-3  9-3  9-3  9-3  9-3 |

| 9-1 9-1 9-2 9-2 9-3 9-3 9-3 9-3 9-5 9-7               |

| 9-1 9-1 9-2 9-2 9-2 9-3 9-3 9-3 9-3 9-3 9-5 9-7       |

| 9-1 9-1 9-2 9-2 9-3 9-3 9-3 9-3 9-3 9-5 9-7           |

| 9-1 9-1 9-2 9-2 9-2 9-3 9-3 9-3 9-3 9-3 9-5 9-7       |

|                                                       |

| 10.4.1              | Interrupt Control Register                                                       | 10-6    |

|---------------------|----------------------------------------------------------------------------------|---------|

| 10.4.2              | Normal Interrupt Mask Register                                                   | 10-8    |

| 10.4.3              | Interrupt Enable Number Register                                                 | 10-9    |

| 10.4.4              | Interrupt Disable Number Register                                                | . 10-10 |

| 10.4.5              | Interrupt Enable Register High and Interrupt Enable Register Low                 | . 10-11 |

| 10.4.5.1            | Interrupt Enable Register High                                                   | 10-11   |

| 10.4.5.2            | Interrupt Enable Register Low                                                    | . 10-12 |

| 10.4.6              | Interrupt Type Register High and Interrupt Type Register Low                     | . 10-13 |

| 10.4.6.1            | Interrupt Type Register High                                                     | . 10-13 |

| 10.4.6.2            | Interrupt Type Register Low                                                      | 10-14   |

| 10.4.7              | Normal Interrupt Priority Level Registers                                        | 10-14   |

| 10.4.7.1            | Normal Interrupt Priority Level Register 7                                       | . 10-15 |

| 10.4.7.2            | Normal Interrupt Priority Level Register 6                                       | 10-16   |

| 10.4.7.3            | Normal Interrupt Priority Level Register 5                                       | . 10-17 |

| 10.4.7.4            | Normal Interrupt Priority Level Register 4.                                      | 10-18   |

| 10.4.7.5            | Normal Interrupt Priority Level Register 3                                       | . 10-19 |

| 10.4.7.6            | Normal Interrupt Priority Level Register 2                                       |         |

| 10.4.7.7            | Normal Interrupt Priority Level Register 1                                       | 10-21   |

| 10.4.7.8            | Normal Interrupt Priority Level Register 0                                       |         |

| 10.4.8              | Normal Interrupt Vector and Status Register                                      |         |

| 10.4.9              | Fast Interrupt Vector and Status Register                                        |         |

| 10.4.10             | Interrupt Source Register High and Interrupt Source Register Low                 |         |

| 10.4.10.1           | Interrupt Source Register High                                                   |         |

| 10.4.10.2           | Interrupt Source Register Low                                                    |         |

| 10.4.11             | Interrupt Force Register High and Interrupt Force Register Low                   |         |

| 10.4.11.1           | Interrupt Force Register High                                                    |         |

| 10.4.11.2           | Interrupt Force Register Low                                                     |         |

| 10.4.12             | Normal Interrupt Pending Register High and Normal Interrupt Pending Register Low |         |

| 10.4.12.1           | Normal Interrupt Pending Register High                                           |         |

| 10.4.12.2           | Normal Interrupt Pending Register Low                                            |         |

| 10.4.13             | Fast Interrupt Pending Register High and Fast Interrupt Pending Register Low     |         |

| 10.4.13.1           | Fast Interrupt Pending Register High                                             |         |

| 10.4.13.2           | Fast Interrupt Pending Register Low                                              |         |

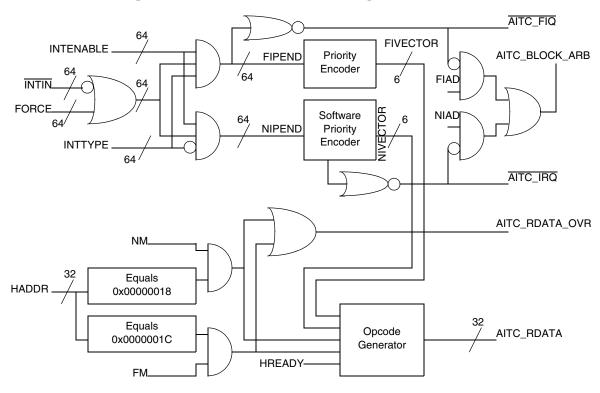

|                     | M920T Processor Interrupt Controller Operation                                   |         |

| 10.5.1              | ARM920T Processor Prioritization of Exception Sources                            |         |

| 10.5.2              | AITC Prioritization of Interrupt Sources                                         |         |

| 10.5.3              | Assigning and Enabling Interrupt Sources                                         |         |

| 10.5.4              | Enabling Interrupts Sources                                                      |         |

| 10.5.5              | Typical Interrupt Entry Sequences                                                |         |

| 10.5.6              | Writing Reentrant Normal Interrupt Routines                                      |         |

| 10.2.0              | Training Reconstruct Northan Interrupt Reduction                                 | . 10 55 |

| Chapter<br>External | 11<br>Interface Module (EIM)                                                     |         |

| 11.1 Ov             | erview                                                                           | . 11-1  |

vi Freescale Semiconductor

| 11.2     | EIM I/O Signals                                                     | 11-1 |

|----------|---------------------------------------------------------------------|------|

| 11.2.1   | Address Bus                                                         | 11-1 |

| 11.2.2   | Data Bus                                                            | 11-1 |

| 11.2.3   | Read/Write                                                          | 11-1 |

| 11.2.4   | Control Signals                                                     | 11-2 |

| 11.2.4.  | 1 OE—Output Enable                                                  | 11-2 |

| 11.2.4.2 | 2 EB [3:0]—Enable Bytes                                             | 11-2 |

| 11.2.4.3 | B DTACK—Data Transfer Acknowledge                                   | 11-2 |

| 11.2.5   | Chip Select Outputs                                                 |      |

| 11.2.5.  |                                                                     |      |

| 11.2.5.2 | Chip Select 1–Chip Select 5 ( $\overline{CS1}$ – $\overline{CS5}$ ) | 11-3 |

| 11.2.6   | Burst Mode Signals                                                  | 11-3 |

| 11.2.6.  | BCLK—Burst Clock                                                    | 11-3 |

| 11.2.6.2 | 2 <del>LBA</del> —Load Burst Address                                | 11-3 |

| 11.2.6.3 | B ECB—End Current Burst                                             | 11-3 |

| 11.3     | Pin Configuration for EIM                                           | 11-3 |

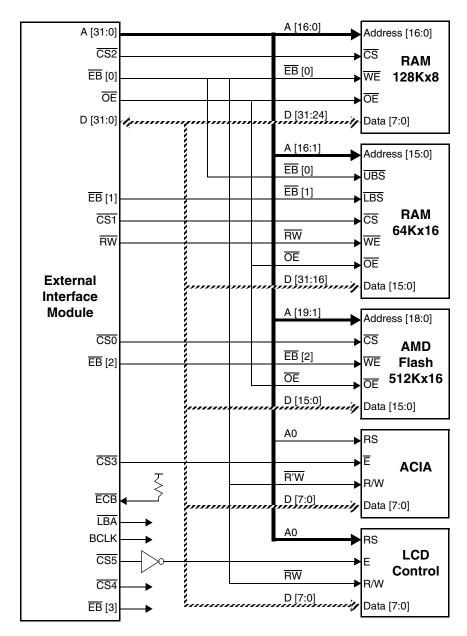

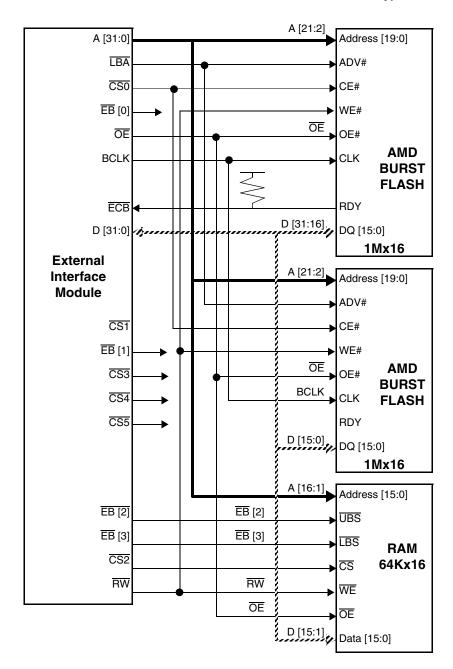

| 11.4     | Typical EIM System Connections                                      | 11-5 |

| 11.5     | EIM Functionality                                                   | 11-8 |

| 11.5.1   | Configurable Bus Sizing                                             | 11-8 |

| 11.5.2   | Programmable Output Generation                                      | 11-8 |

| 11.5.3   | Burst Mode Operation                                                |      |

| 11.5.4   | Burst Clock Divisor                                                 | 11-8 |

| 11.5.5   | Burst Clock Start                                                   | 11-9 |

| 11.5.6   | Page Mode Emulation                                                 | 11-9 |

| 11.5.7   | Error Conditions                                                    | 11-9 |

| 11.6     | Programming Model                                                   | 1-10 |

| 11.6.1   | Chip Select 0 Control Registers                                     | 1-11 |

| 11.6.1.  | Chip Select 0 Upper Control Register                                | 1-11 |

| 11.6.1.2 | Chip Select 0 Lower Control Register                                | 1-12 |

| 11.6.2   | Chip Select 1–Chip Select 5 Control Registers                       | 1-12 |

| 11.6.2.  | Chip Select 1–Chip Select 5 Upper Control Registers                 | 1-12 |

| 11.6.2.2 | Chip Select 1–Chip Select 5 Lower Control Registers                 | 1-13 |

| 11.6.3   | EIM Configuration Register                                          | 1-19 |

|          |                                                                     |      |

| Chapt    |                                                                     |      |

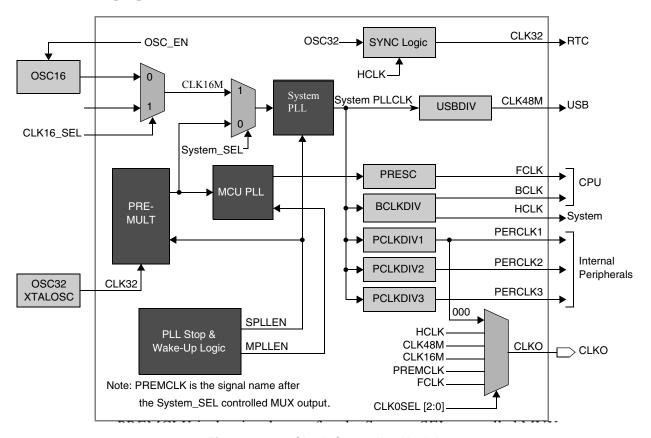

| Phase    | e-Locked Loop and Clock Controller                                  |      |

| 12.1     | Introduction                                                        | 12_1 |

|          | Clock Sources                                                       |      |

| 12.2.1   | Low Frequency Clock Source.                                         |      |

| 12.2.1   | High Frequency Clock Source                                         |      |

|          | DPLL Output Frequency Calculation                                   |      |

| 12.3.1   | DPLL Phase and Frequency Jitter                                     |      |

|          | MC9328MXS Power Management                                          |      |

| 12.4.1   | PLL Operation at Power-Up.                                          |      |

| 14.7.1   |                                                                     | 14-4 |

| 12.4.2            | PLL Operation at Wake-Up                    | 12-4  |

|-------------------|---------------------------------------------|-------|

| 12.4.3            | ARM920T Processor Low-Power Modes           | 12-4  |

| 12.4.4            | SDRAM Power Modes                           | 12-4  |

| 12.4.5            | Power Management in the Clock Controller    | 12-4  |

| 12.5 Pro          | ogramming Model                             |       |

| 12.5.1            | Clock Source Control Register               |       |

| 12.5.2            | Peripheral Clock Divider Register           |       |

| 12.5.3            | Programming Digital Phase Locked Loops      |       |

| 12.5.3.1          | MCU PLL Control Register 0.                 |       |

| 12.5.3.2          | MCU PLL and System Clock Control Register 1 |       |

| 12.5.4            | Generation of 48 MHz Clocks                 |       |

| 12.5.4.1          | System PLL Control Register 0               | 12-12 |

| 12.5.4.2          | System PLL Control Register 1               |       |

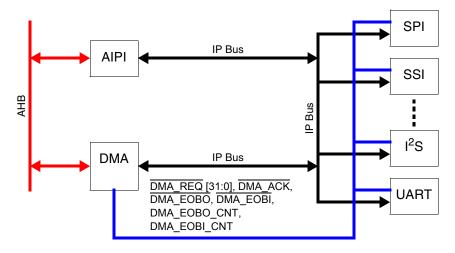

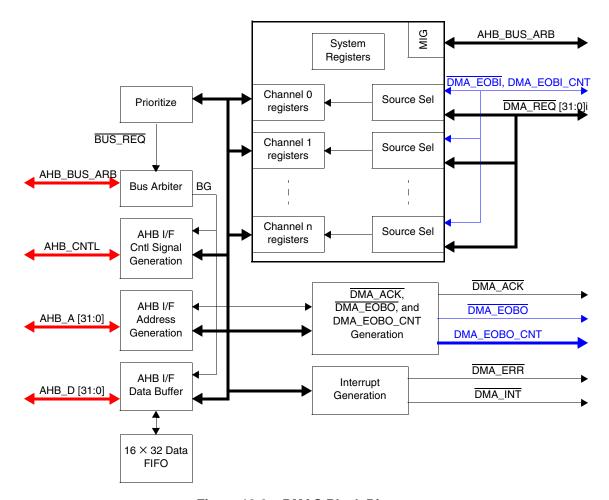

| Chapter<br>DMA Co |                                             |       |

|                   | ntures                                      |       |

| 13.2 Blo          | ock Diagram                                 | 13-2  |

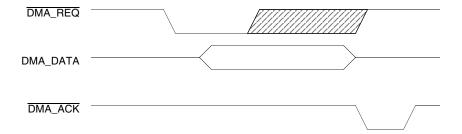

|                   | nal Description                             | 13-3  |

| 13.3.1            | Big Endian and Little Endian                |       |

| 13.4 Pro          | ogramming Model                             | 13-4  |

| 13.4.1            | General Registers                           |       |

| 13.4.1.1          | DMA Control Register                        | 13-8  |

| 13.4.1.2          | DMA Interrupt Status Register               | 13-9  |

| 13.4.1.3          | DMA Interrupt Mask Register                 | 13-10 |

| 13.4.1.4          | DMA Burst Time-Out Status Register          | 13-11 |

| 13.4.1.5          | DMA Request Time-Out Status Register        | 13-12 |

| 13.4.1.6          | DMA Transfer Error Status Register          |       |

| 13.4.1.7          | DMA Buffer Overflow Status Register         | 13-14 |

| 13.4.1.8          | DMA Burst Time-Out Control Register         | 13-15 |

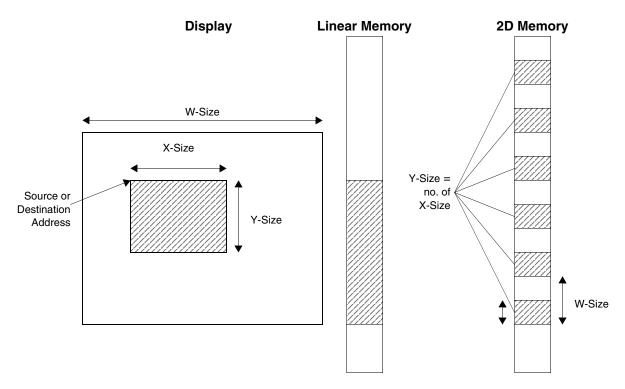

| 13.4.2            | 2D Memory Registers (A and B)               | 13-16 |

| 13.4.2.1          | W-Size Registers.                           | 13-16 |

| 13.4.2.2          | X-Size Registers                            | 13-17 |

| 13.4.2.3          | Y-Size Registers                            |       |

| 13.4.3            | Channel Registers                           | 13-18 |

| 13.4.3.1          | Channel Source Address Register             | 13-19 |

| 13.4.3.2          | Destination Address Registers               | 13-20 |

| 13.4.3.3          | Channel Count Registers                     | 13-21 |

| 13.4.3.4          | Channel Control Registers                   |       |

| 13.4.3.5          | Channel Request Source Select Registers     |       |

| 13.4.3.6          | Channel Burst Length Registers              |       |

| 13.4.3.7          | Channel Request Time-Out Registers          | 13-27 |

| 13.4.3.8          | Channel 0 Bus Utilization Control Register  |       |

| 13.5 DN           | AA Request Table                            | 13-30 |

|                   |                                             |       |

viii Freescale Semiconductor

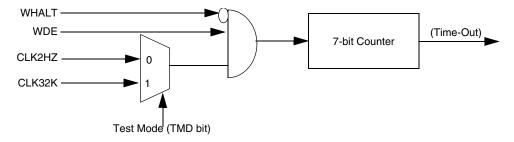

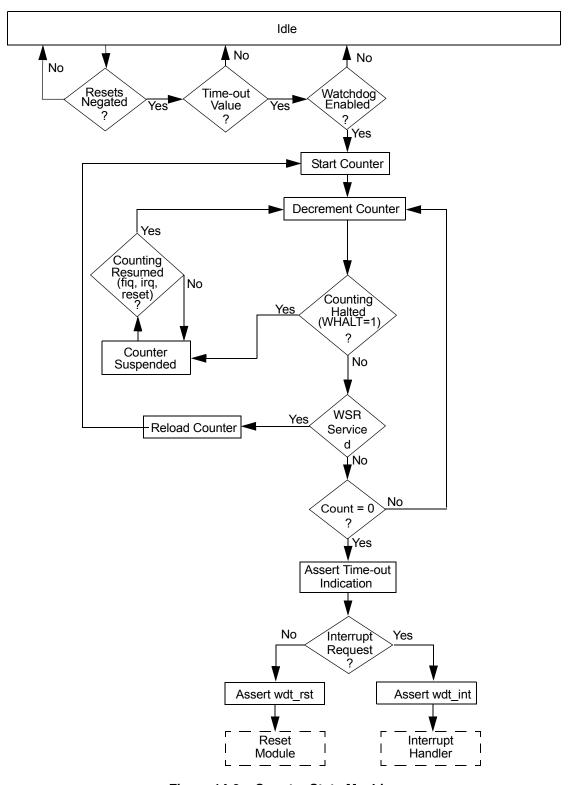

## Chapter 14 Watchdog Timer Module

| 14.1    | General Overview                      | 14-1  |

|---------|---------------------------------------|-------|

| 14.2    | Watchdog Timer Operation              | 14-1  |

| 14.2.1  | Timing Specifications                 |       |

| 14.2.2  | Watchdog During Reset                 | 14-2  |

| 14.2.2. | Power-On Reset                        | 14-2  |

| 14.2.2. |                                       |       |

| 14.3    | Watchdog After Reset                  | 14-2  |

| 14.3.1  | Initial Load                          | 14-2  |

| 14.3.2  | Countdown                             | 14-2  |

| 14.3.3  | Reload                                |       |

| 14.3.4  | Time-Out.                             | 14-3  |

| 14.3.5  | Halting the Counter                   | 14-3  |

| 14.4    | Watchdog Control                      |       |

| 14.4.1  | Interrupt Control                     | 14-3  |

| 14.4.2  | Reset Sources                         | 14-3  |

| 14.5    | State Machine                         | 14-4  |

| 14.6    | Watchdog Timer I/O Signals            | 14-5  |

| 14.7    | Programming Model                     |       |

| 14.7.1  | Watchdog Control Register             | 14-6  |

| 14.7.2  | Watchdog Service Register             |       |

| 14.7.3  | Watchdog Status Register              |       |

| Chan    | ter 15                                |       |

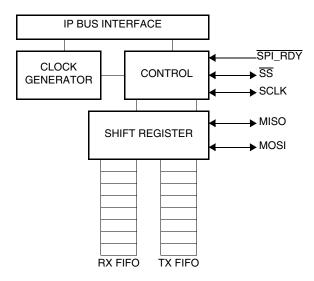

|         | l Peripheral Interface Module (SPI 1) |       |

|         | •                                     | 1.5.1 |

| 15.1    | SPI Block Diagram                     |       |

| 15.2    | Operation                             |       |

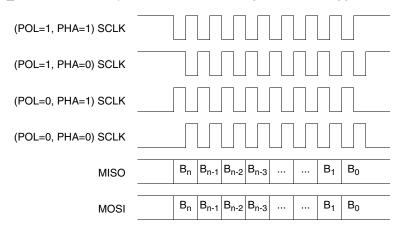

| 15.2.1  | Phase and Polarity Configurations     |       |

| 15.2.2  | Signals                               |       |

| 15.2.3  | Pin Configuration                     |       |

| 15.3    | Programming Model                     |       |

| 15.3.1  | Receive (RX) Data Register            |       |

| 15.3.2  | Transmit (TX) Data Register           |       |

| 15.3.3  | Control Register                      |       |

| 15.3.4  | Interrupt Control/Status Register     |       |

| 15.3.5  | Test Register                         |       |

| 15.3.6  | Sample Period Control Register        |       |

| 15.3.7  | DMA Control Register                  |       |

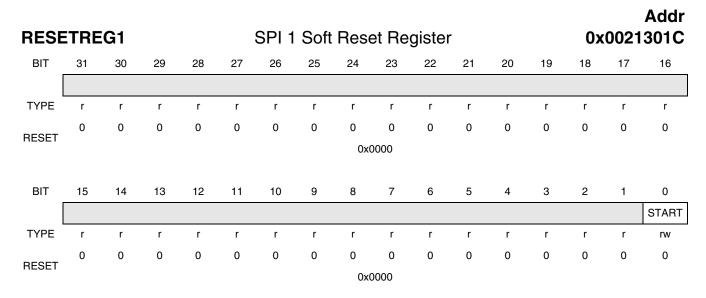

| 15.3.8  | Soft Reset Register                   | 5-14  |

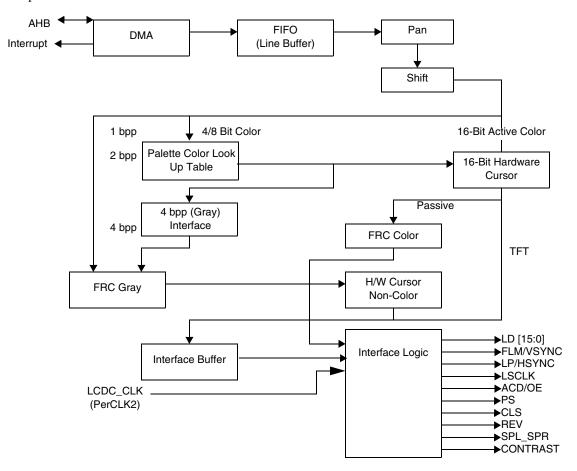

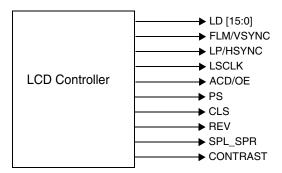

## Chapter 16 LCD Controller

| 16.1     | Introduction                                                          | 16-1  |

|----------|-----------------------------------------------------------------------|-------|

| 16.2     | Features                                                              | 16-1  |

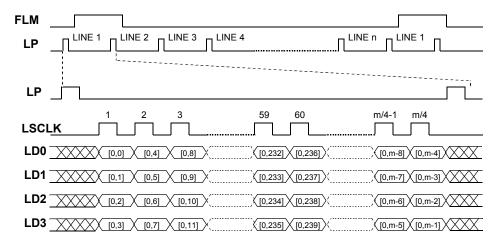

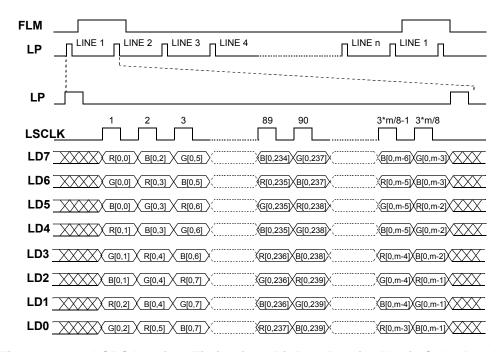

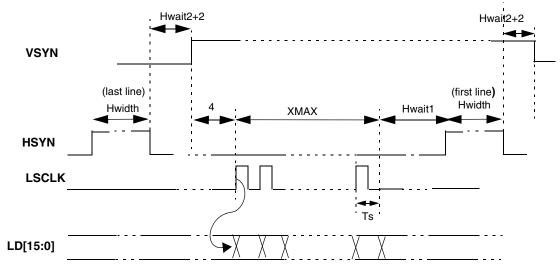

| 16.3     | LCDC Operation                                                        | 16-2  |

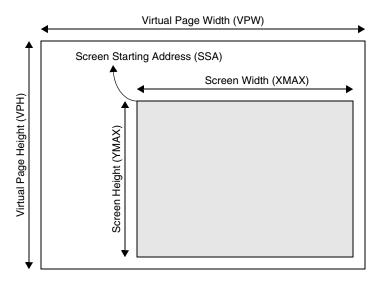

| 16.3.1   | LCD Screen Format                                                     | 16-2  |

| 16.3.2   | Panning                                                               | 16-3  |

| 16.3.3   | Display Data Mapping                                                  | 16-3  |

| 16.3.4   | Black-and-White Operation                                             |       |

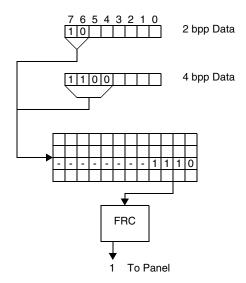

| 16.3.5   | Gray-Scale Operation                                                  | 16-7  |

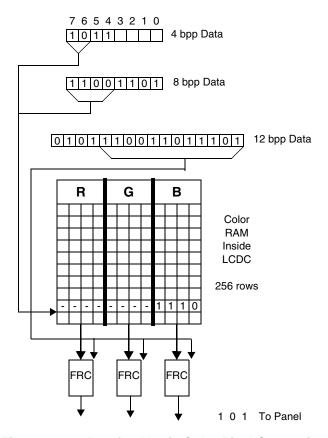

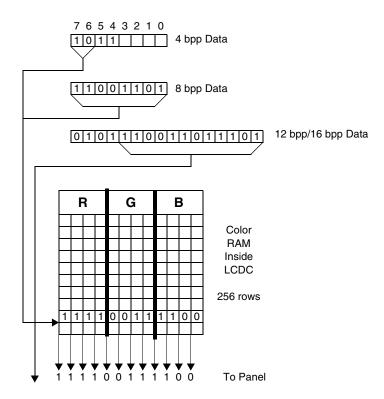

| 16.3.6   | Color Generation.                                                     | 16-8  |

| 16.3.7   | Frame Rate Modulation Control (FRC)                                   | 16-10 |

| 16.3.8   | Panel Interface Signals and Timing                                    | 16-11 |

| 16.3.8.  | Pin Configuration for LCDC                                            | 16-11 |

| 16.3.8.2 | Passive Matrix Panel Interface Signals                                | 16-12 |

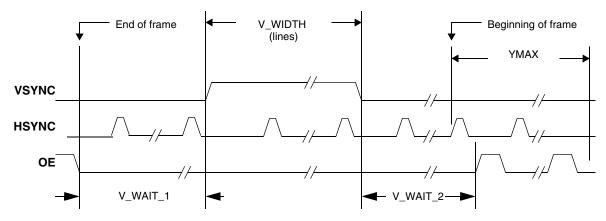

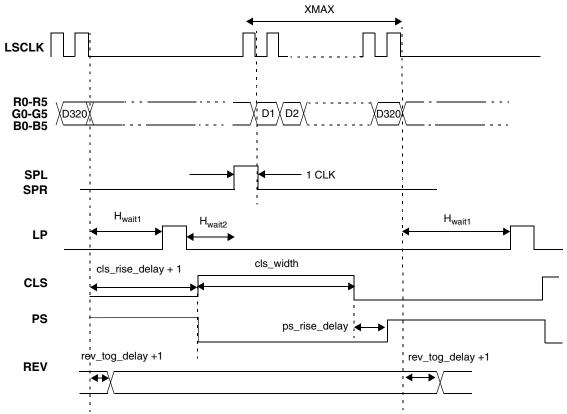

| 16.3.8.  | Passive Panel Interface Timing                                        | 16-13 |

| 16.3.9   | 8 bpp Mode Color STN Panel                                            | 16-14 |

| 16.3.9.  | Active Matrix Panel Interface Signals                                 | 16-14 |

| 16.3.9.2 | 2 Active Panel Interface Timing                                       | 16-16 |

| 16.4     | Programming Model                                                     | 16-18 |

| 16.4.1   | Screen Start Address Register                                         | 16-20 |

| 16.4.2   | Size Register                                                         | 16-21 |

| 16.4.3   | Virtual Page Width Register                                           | 16-22 |

| 16.4.4   | Panel Configuration Register                                          |       |

| 16.4.5   | Horizontal Configuration Register                                     | 16-26 |

| 16.4.6   | Vertical Configuration Register                                       |       |

| 16.4.7   | Panning Offset Register                                               | 16-28 |

| 16.4.8   | LCD Cursor Position Register                                          | 16-29 |

| 16.4.9   | LCD Cursor Width Height and Blink Register                            | 16-30 |

| 16.4.10  | LCD Color Cursor Mapping Register                                     | 16-31 |

| 16.4.11  | Sharp Configuration 1 Register                                        | 16-32 |

| 16.4.12  | PWM Contrast Control Register                                         | 16-34 |

| 16.4.13  | Refresh Mode Control Register                                         | 16-35 |

| 16.4.14  | DMA Control Register                                                  | 16-36 |

| 16.4.15  | Interrupt Configuration Register                                      | 16-37 |

| 16.4.16  | Interrupt Status Register                                             | 16-38 |

| 16.4.17  |                                                                       |       |

| 16.4.17  | One Bit/Pixel Monochrome Mode                                         | 16-39 |

| 16.4.17  | 7.2 Four Bits/Pixel Gray-Scale Mode                                   | 16-39 |

| 16.4.17  |                                                                       |       |

| 16.4.17  | Eight Bits/Pixel Passive Matrix Color Mode                            | 16-40 |

| 16.4.17  |                                                                       |       |

| 16.4.17  |                                                                       |       |

| 16.4.17  | 7.7 Twelve Bits/Pixel and Sixteen Bits/Pixel Active Matrix Color Mode | 16-42 |

x Freescale Semiconductor

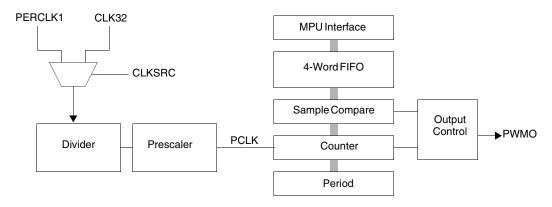

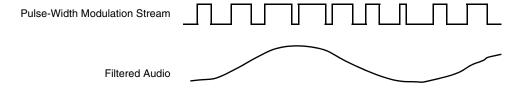

## Chapter 17 Pulse-Width Modulator (PWM)

| 17.1           | Introduction                           | 17-1 |

|----------------|----------------------------------------|------|

| 17.2           | PWM Signals                            | 17-1 |

| 17.2.1         | Clock Signals                          |      |

| 17.2.2         | Pin Configuration for PWM              |      |

| 17.3           | PWM Operation                          |      |

| 17.3.1         | Playback Mode                          |      |

| 17.3.2         | Tone Mode                              |      |

| 17.3.3         | Digital-to-Analog Converter (D/A) Mode | 17-3 |

| 17.4           | Programming Model                      |      |

| 17.4.1         | PWM Control Register                   |      |

| 17.4.1.        | 1 HCTR and BCTR Bit Description        | 17-6 |

| 17.4.2         | PWM Sample Register                    |      |

| 17.4.3         | PWM Period Register                    |      |

| 17.4.4         | PWM Counter Register                   |      |

| Chapt<br>Real- | ter 18<br>Time Clock (RTC)             |      |

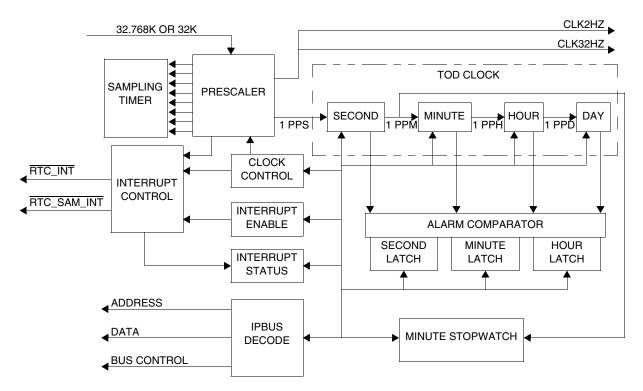

| 18.1           | Operation                              | 18-2 |

| 18.1.1         | Prescaler and Counter                  | 18-2 |

| 18.1.2         | Alarm                                  | 18-3 |

| 18.1.3         | Sampling Timer                         | 18-3 |

| 18.1.4         | Minute Stopwatch                       | 18-3 |

| 18.2           | Programming Model                      | 18-4 |

| 18.2.1         | RTC Days Counter Register              |      |

| 18.2.2         | RTC Hours and Minutes Counter Register | 18-5 |

| 18.2.3         | RTC Seconds Counter Register           |      |

| 18.2.4         | RTC Day Alarm Register                 |      |

| 18.2.5         | RTC Hours and Minutes Alarm Register   | 18-9 |

| 18.2.6         | RTC Seconds Alarm Register             |      |

| 18.2.7         | RTC Control Register                   |      |

| 18.2.8         | RTC Interrupt Status Register          |      |

| 18.2.9         | RTC Interrupt Enable Register          |      |

| 18.2.10        | Stopwatch Minutes Register             | 8-15 |

| Chapt<br>SDRA  | ter 19<br>IM Memory Controller         |      |

| 19.1           | Features                               | 19-1 |

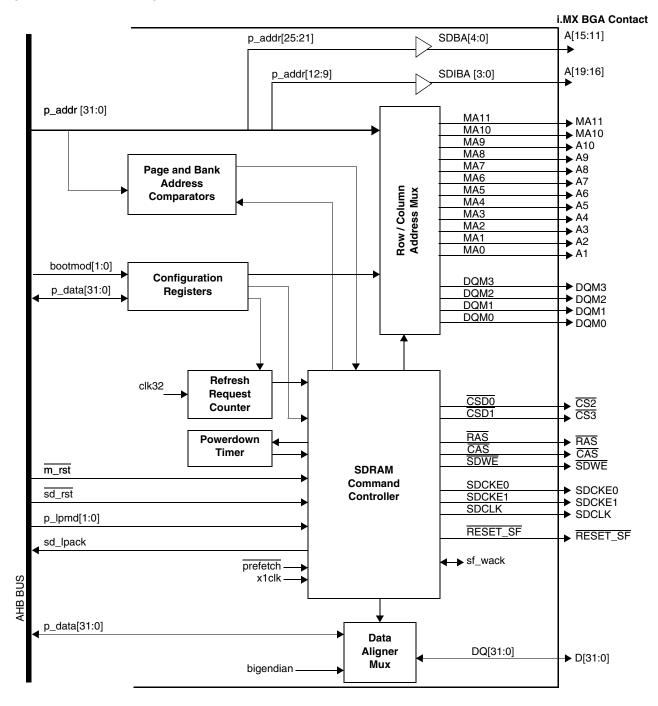

| 19.2           | Block Diagram                          | 19-2 |

| 19.3           | Functional Overview.                   |      |

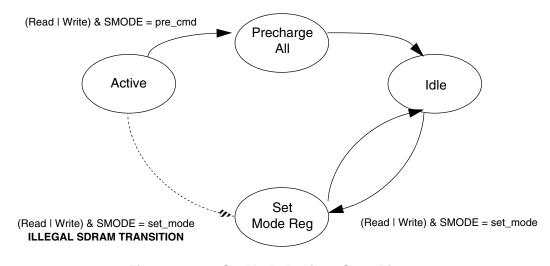

| 19.3.1         | SDRAM Command Controller               |      |

| 19.3.2         |                                        | 19-3 |

|                |                                        |      |

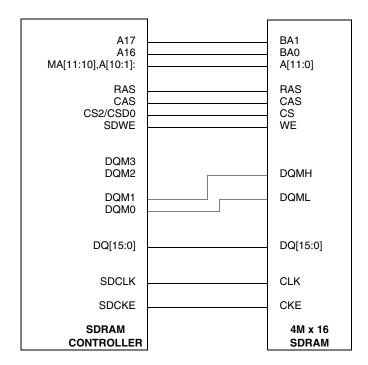

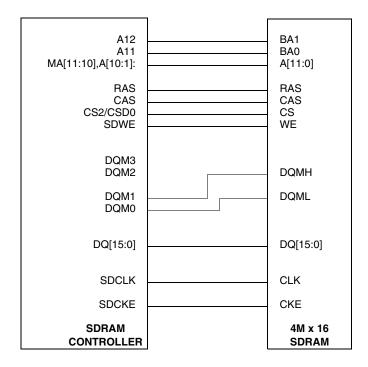

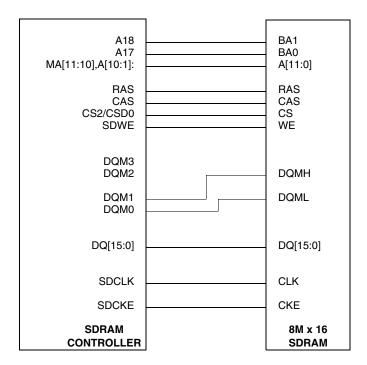

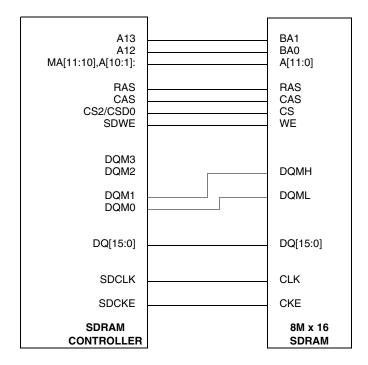

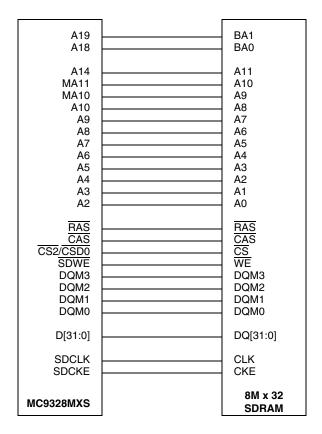

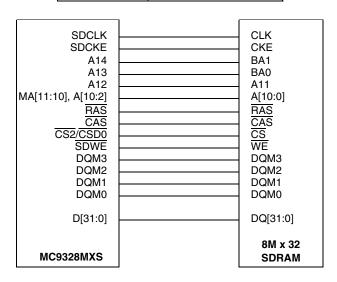

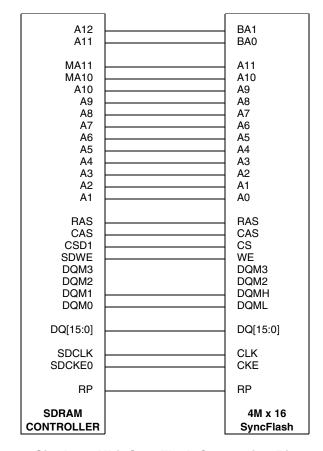

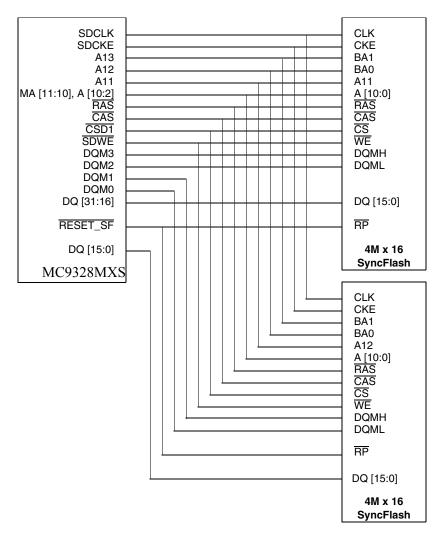

| 19.3.3   | Row and Column Address Multiplexer                   | . 19-3 |

|----------|------------------------------------------------------|--------|

| 19.3.4   | Data Aligner and Multiplexer                         |        |

| 19.3.5   | Configuration Registers                              | . 19-3 |

| 19.3.6   | Refresh Request Counter                              |        |

| 19.3.7   | Powerdown Timer                                      |        |

| 19.3.8   | DMA Operation with the SDRAM Controller              | . 19-4 |

| 19.3.9   | SDCLK—SDRAM Clock.                                   |        |

| 19.3.10  | SDCKE0, SDCKE1—SDRAM Clock Enables                   |        |

| 19.3.11  | CSD0, CSD1—SDRAM Chip-Select.                        | . 19-5 |

| 19.3.12  | DQ [31:0]—Data Bus (Internal)                        |        |

| 19.3.13  | MA [11:0]—Multiplexed Address Bus                    |        |

| 19.3.14  | SDBA [4:0], SDIBA [3:0]—Non-Multiplexed Address Bus  |        |

| 19.3.15  | DQM3, DQM2, DQM1, DQM0—Data Qualifier Mask           |        |

| 19.3.16  | SDWE—Write Enable                                    |        |

| 19.3.17  | RAS—Row Address Strobe                               |        |

| 19.3.18  | CAS—Column Address Strobe                            |        |

| 19.3.19  | RESET SF—Reset or Powerdown                          |        |

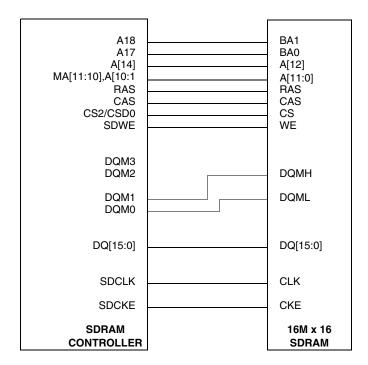

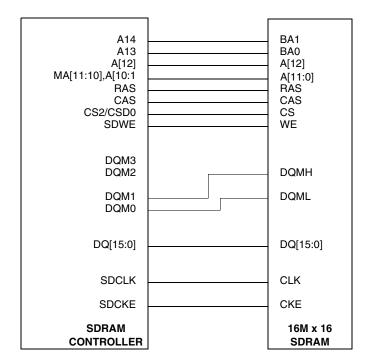

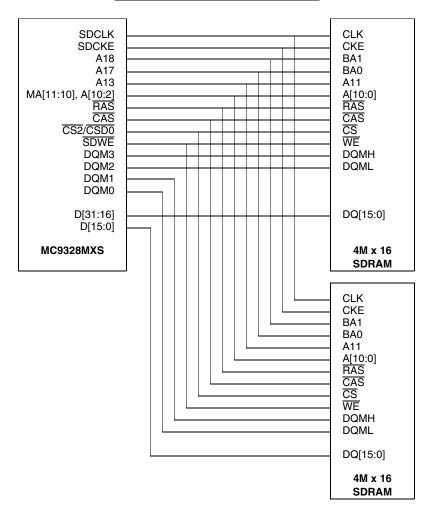

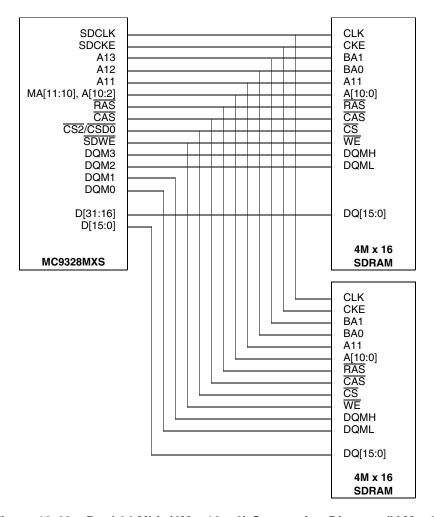

| 19.3.20  | Pin Configuration for SDRAMC                         |        |

| 19.4 Pro | ogramming Model                                      |        |

| 19.4.1   | SDRAM Control Registers                              |        |

| 19.4.2   | SDRAM Reset Register                                 |        |

| 19.4.3   | Miscellaneous Register                               |        |

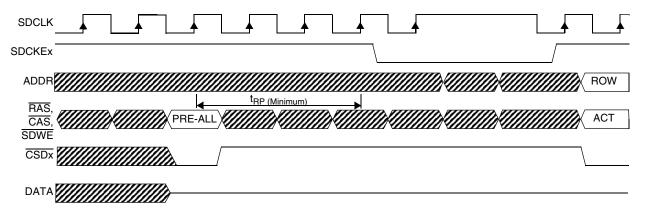

| 19.5 Op  | erating Modes                                        |        |

| 19.5.1   | SDRAM and SyncFlash Command Encoding                 |        |

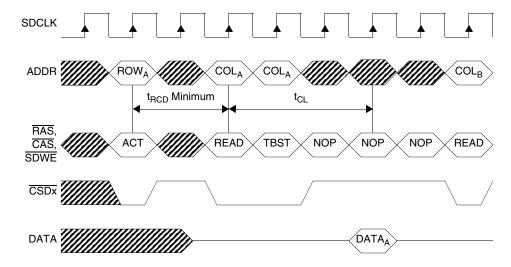

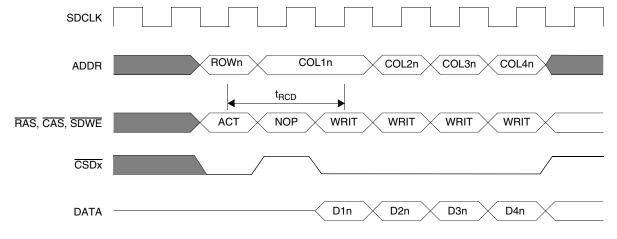

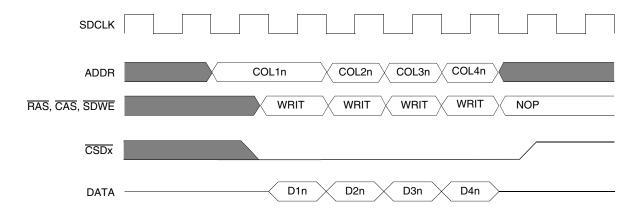

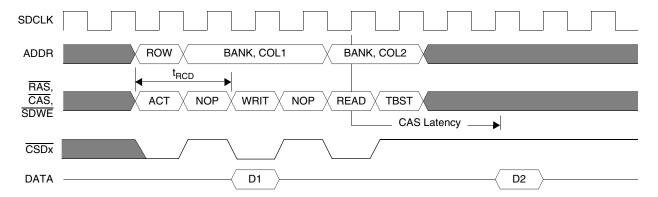

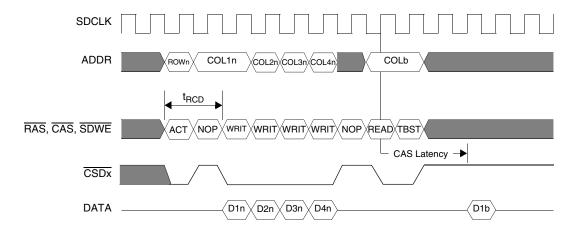

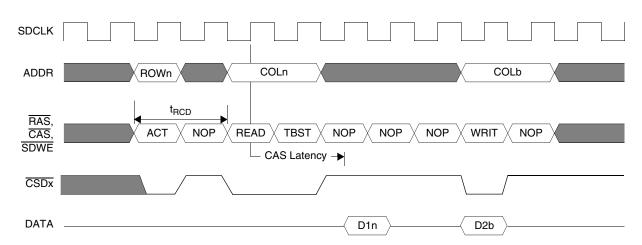

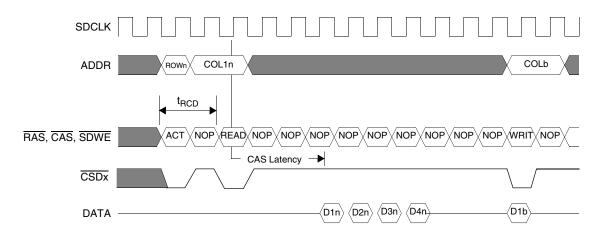

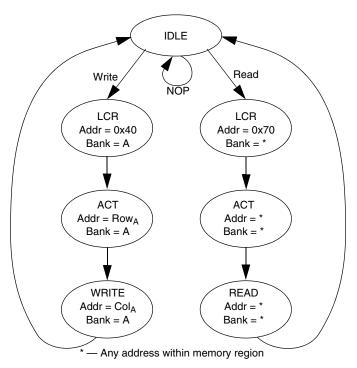

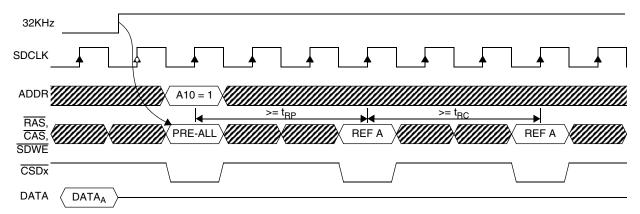

| 19.5.2   | Normal Read/Write Mode (SMODE = 000)                 |        |

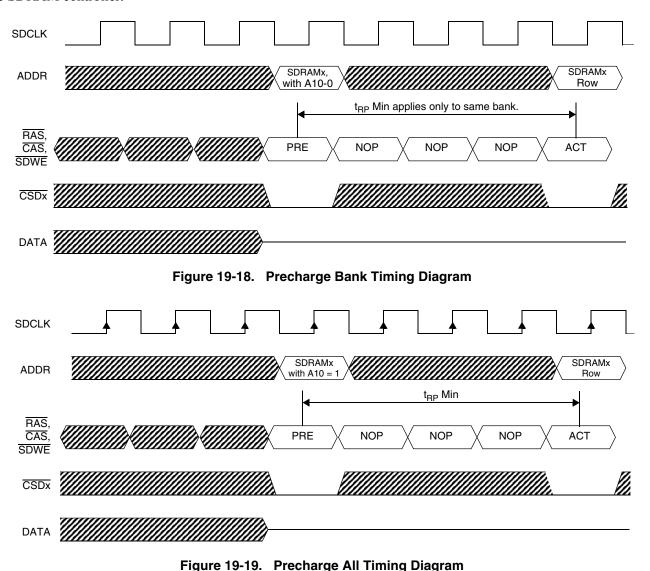

| 19.5.3   | Precharge Command Mode (SMODE = 001)                 |        |

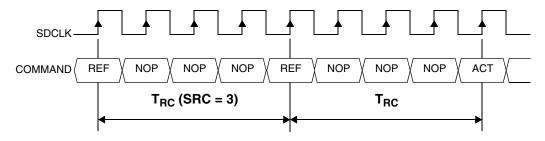

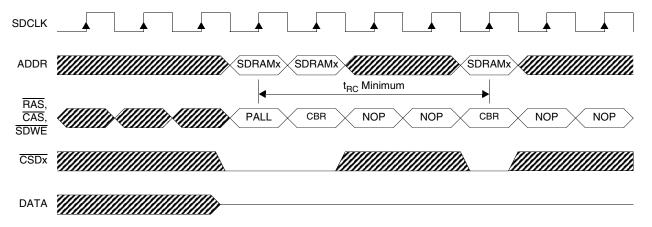

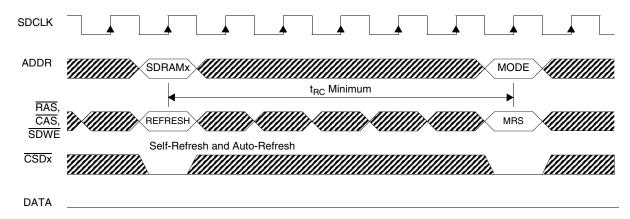

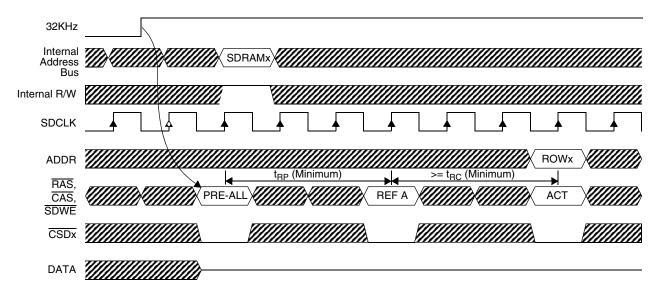

| 19.5.4   | Auto-Refresh Mode (SMODE = 010)                      | 19-25  |

| 19.5.5   | Set Mode Register Mode (SMODE = 011)                 |        |

| 19.5.6   | SyncFlash Load Command Mode                          |        |

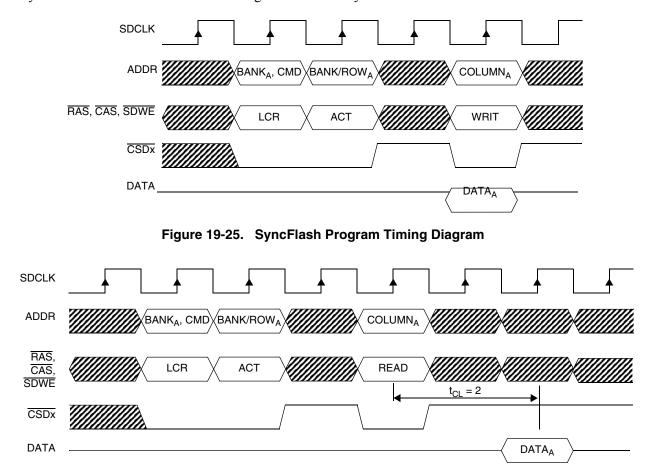

| 19.5.7   | SyncFlash Program Mode                               | 19-27  |

| 19.6 Ge  | neral Operation                                      | 19-28  |

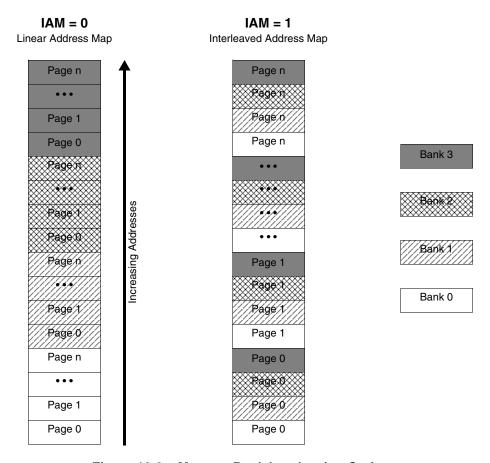

| 19.6.1   | Address Multiplexing                                 | 19-29  |

| 19.6.1.1 | Multiplexed Address Bus                              | 19-29  |

| 19.6.1.2 | Non-Multiplexed Address Bus                          | 19-31  |

| 19.6.1.3 | Bank Addresses                                       | 19-31  |

| 19.6.2   | Refresh                                              | 19-32  |

| 19.6.3   | Self-Refresh                                         | 19-33  |

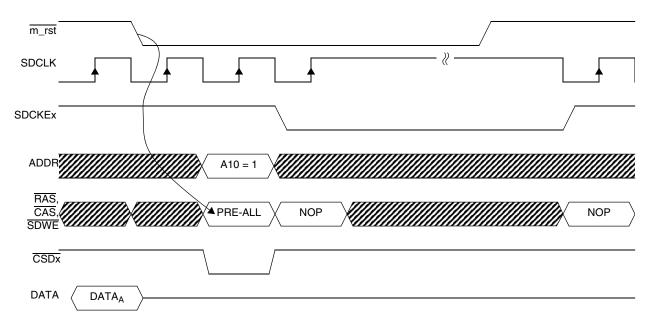

| 19.6.3.1 | Self-Refresh During RESET_IN                         | 19-33  |

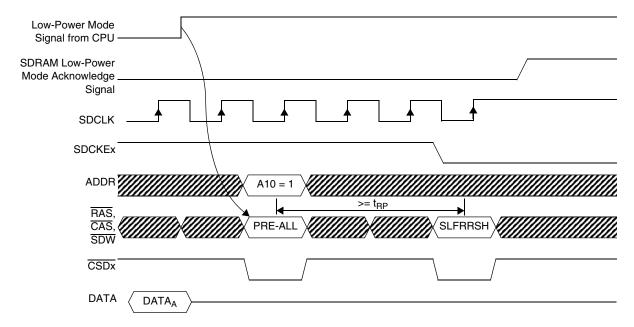

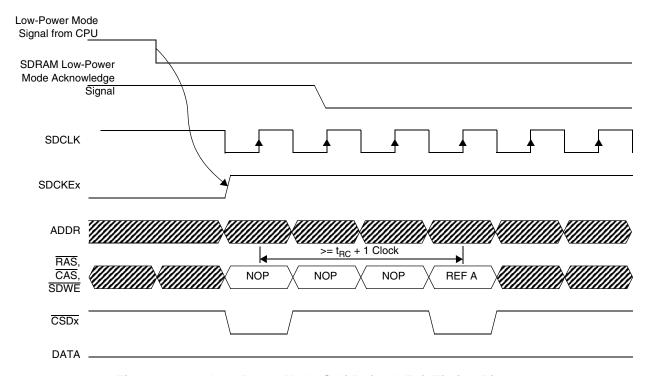

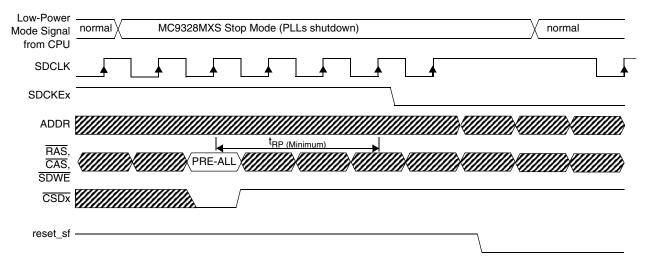

| 19.6.3.2 | Self-Refresh During Low-Power Mode                   | 19-33  |

| 19.6.3.3 | Powerdown Operation During Reset and Low-Power Modes |        |

| 19.6.4   | Clock Suspend Low-Power Mode                         |        |

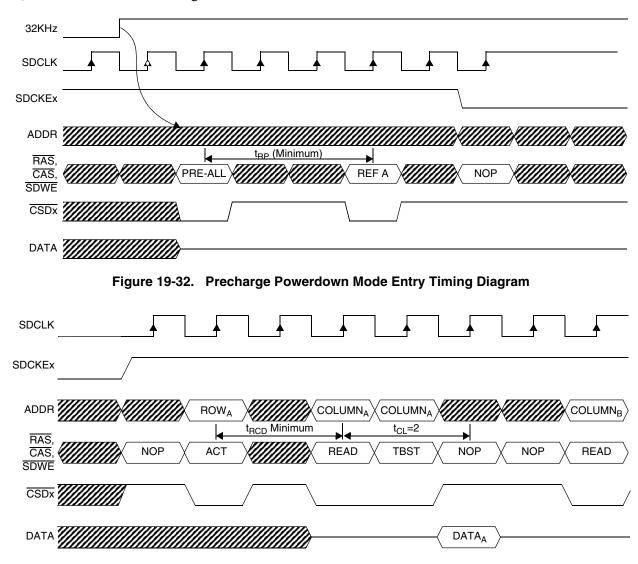

| 19.6.4.1 | Powerdown (Precharge Powerdown)                      | 19-35  |

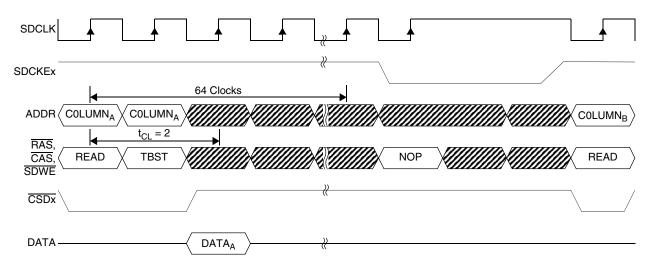

| 19.6.4.2 | Clock Suspend (Active Powerdown)                     |        |

| 19.6.4.3 | Refresh During Powerdown or Clock Suspend            |        |

| 19.7 SD  | RAM Operation                                        |        |

|          |                                                      |        |

xii Freescale Semiconductor

| 1070                                                                                                                                | SDRAM Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1) 51                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 19.7.2                                                                                                                              | Configuring Controller for SDRAM Memory Array                                                                                                                                                                                                                                                                                                                                                                                                                   | 19-38                                                  |

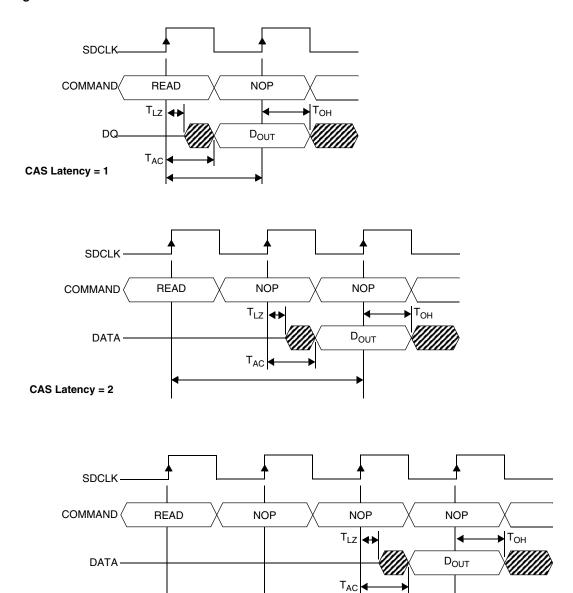

| 19.7.2.                                                                                                                             | 1 CAS Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19-38                                                  |

| 19.7.2.                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

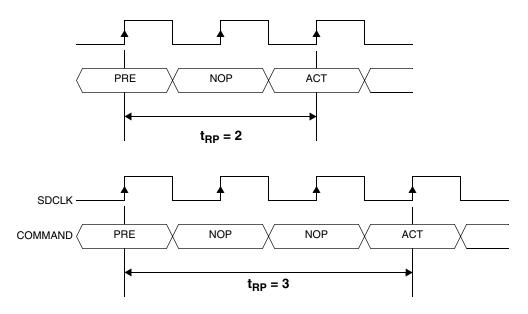

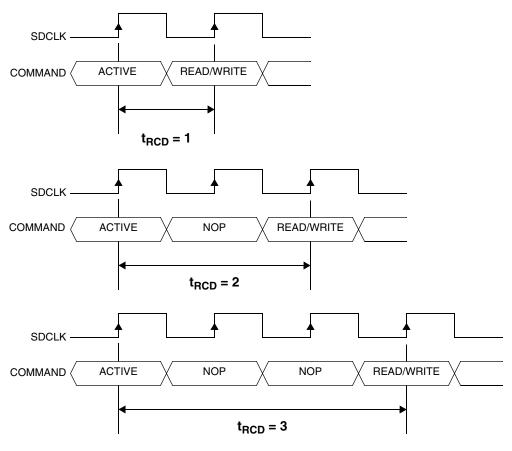

| 19.7.2.                                                                                                                             | Row-to-Column Delay                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-38                                                  |

| 19.7.2.                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

| 19.7.2.                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

| 19.7.2.                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

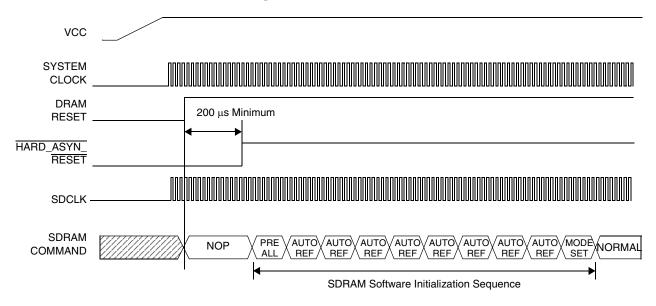

| 19.7.3                                                                                                                              | SDRAM Reset Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |

| 19.7.4                                                                                                                              | Mode Register Programming                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |

| 19.7.5                                                                                                                              | Mode Register Programming Examples                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                        |

| 19.7.5.                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

| 19.7.5.                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

| 19.7.6                                                                                                                              | SDRAM Memory Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |

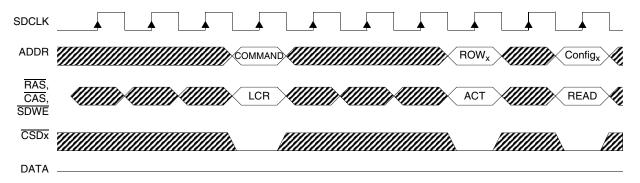

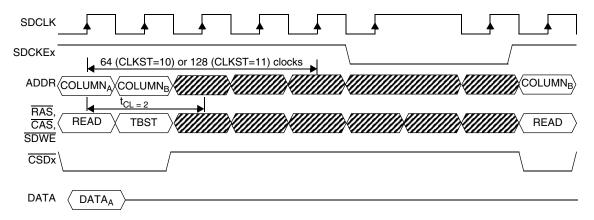

| 19.8                                                                                                                                | SyncFlash Operation                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                        |

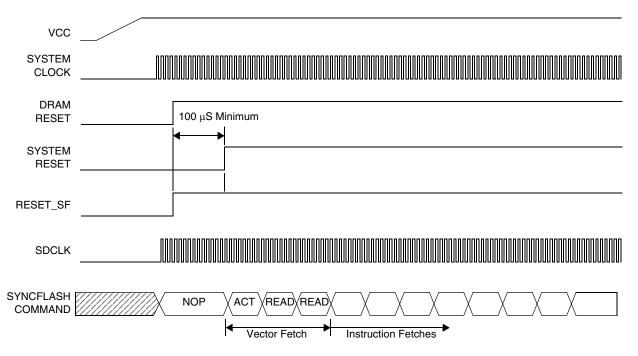

| 19.8.1                                                                                                                              | SyncFlash Reset Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |

| 19.8.2                                                                                                                              | SyncFlash Mode Register Programming                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                        |

| 19.8.3                                                                                                                              | Booting From SyncFlash                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |

| 19.8.4                                                                                                                              | SyncFlash Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                        |

| 19.8.5                                                                                                                              | SyncFlash Programming                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |

| 19.8.6                                                                                                                              | Clock Suspend Timer Use with SyncFlash                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |

| 19.8.7                                                                                                                              | Powerdown Operation with SyncFlash                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                        |

| 19.9                                                                                                                                | Deep Powerdown Operation with SyncFlash                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                        |

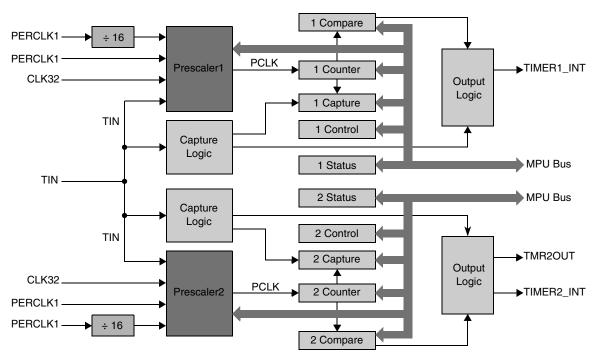

| Gene                                                                                                                                | ter 20 ral-Purpose Timers  Operation                                                                                                                                                                                                                                                                                                                                                                                                                            | 20.2                                                   |

| 20.1<br>20.1.1                                                                                                                      | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |

| ZU I I                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                        |

|                                                                                                                                     | Pin Configuration for General-Purpose Timers                                                                                                                                                                                                                                                                                                                                                                                                                    | 20-2                                                   |

| 20.2                                                                                                                                | Pin Configuration for General-Purpose Timers                                                                                                                                                                                                                                                                                                                                                                                                                    | 20-2                                                   |

| 20.2<br>20.2.1                                                                                                                      | Pin Configuration for General-Purpose Timers  Programming Model                                                                                                                                                                                                                                                                                                                                                                                                 | 20-2<br>20-3<br>20-3                                   |

| 20.2<br>20.2.1<br>20.2.2                                                                                                            | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.                                                                                                                                                                                                                                                                                                                          | 20-2<br>20-3<br>20-3                                   |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3                                                                                                  | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.                                                                                                                                                                                                                                                                                        | 20-2<br>20-3<br>20-5<br>20-6                           |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4                                                                                        | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.                                                                                                                                                                                                                                                      | 20-2 20-3 20-5 20-6 20-7                               |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5                                                                              | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.  Timer Counter Registers 1 and 2.                                                                                                                                                                                                                    | 20-2 20-3 20-3 20-5 20-6 20-7 20-8                     |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6                                                                    | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.                                                                                                                                                                                                                                                      | 20-2 20-3 20-3 20-5 20-6 20-7 20-8                     |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b>                                                     | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.  Timer Counter Registers 1 and 2.  Timer Status Registers 1 and 2.  Timer Status Registers 1 and 2.                                                                                                                                                  | 20-2 20-3 20-3 20-5 20-6 20-7 20-8                     |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b>                                                     | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.  Timer Counter Registers 1 and 2.  Timer Status Registers 1 and 2.                                                                                                                                                                                   | 20-2 20-3 20-3 20-5 20-6 20-7 20-8                     |

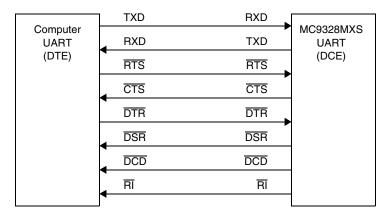

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br>Chap<br>Unive                                                   | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.  Timer Counter Registers 1 and 2.  Timer Status Registers 1 and 2.  Timer Status Registers 1 and 2.                                                                                                                                                  | 20-2 20-3 20-3 20-5 20-6 20-8 20-9                     |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b><br><b>Unive</b>                                     | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.  Timer Counter Registers 1 and 2.  Timer Status Registers 1 and 2.                                                                                | 20-2 20-3 20-3 20-5 20-6 20-7 20-8 20-9                |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b><br><b>Unive</b>                                     | Pin Configuration for General-Purpose Timers  Programming Model.  Timer Control Registers 1 and 2.  Timer Prescaler Registers 1 and 2.  Timer Compare Registers 1 and 2.  Timer Capture Registers 1 and 2.  Timer Counter Registers 1 and 2.  Timer Status Registers 1 and 2.  Tersal Asynchronous Receiver/Transmitters (UART) Modules  Introduction.                                                                                                          | 20-2 20-3 20-5 20-6 20-8 20-9                          |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b><br><b>Unive</b><br>21.1<br>21.2<br>21.2.1           | Pin Configuration for General-Purpose Timers  Programming Model  Timer Control Registers 1 and 2  Timer Prescaler Registers 1 and 2  Timer Compare Registers 1 and 2  Timer Capture Registers 1 and 2  Timer Counter Registers 1 and 2  Timer Status Registers 1 and 2  Timer Status Registers 1 and 2  Inter Status Registers 1 and 2  Introduction  Features  Module Interface                                                                                | 20-2 20-3 20-5 20-6 20-8 20-9                          |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b><br><b>Unive</b><br>21.1<br>21.2<br>21.2.1<br>21.2.2 | Pin Configuration for General-Purpose Timers  Programming Model  Timer Control Registers 1 and 2  Timer Prescaler Registers 1 and 2  Timer Compare Registers 1 and 2  Timer Capture Registers 1 and 2  Timer Counter Registers 1 and 2  Timer Status Registers 1 and 2  Timer Status Registers 1 and 2  Inter 21  Persal Asynchronous Receiver/Transmitters (UART) Modules  Introduction.  Features                                                             | 20-2 20-3 20-5 20-6 20-7 20-8 20-9                     |

| 20.2<br>20.2.1<br>20.2.2<br>20.2.3<br>20.2.4<br>20.2.5<br>20.2.6<br><b>Chap</b>                                                     | Pin Configuration for General-Purpose Timers Programming Model Timer Control Registers 1 and 2 Timer Prescaler Registers 1 and 2 Timer Compare Registers 1 and 2 Timer Capture Registers 1 and 2 Timer Counter Registers 1 and 2 Timer Status Registers 1 and 2 Timer Status Registers 1 and 2 Timer Status Registers 1 and 2  Inter 21 Persal Asynchronous Receiver/Transmitters (UART) Modules  Introduction Features Module Interface UART Pin Configuration | 20-2 20-3 20-5 20-6 20-7 20-8 21-1 21-1 21-2 21-3 21-4 |

| 21.4.1    | RTS—UART Request To Send                     | . 21-5 |

|-----------|----------------------------------------------|--------|

| 21.4.2    | RTS Edge Triggered Interrupt                 | . 21-6 |

| 21.4.3    | DTR—Data Terminal Ready                      | . 21-6 |

| 21.4.4    | DTR Edge Triggered Interrupt                 | . 21-7 |

| 21.4.5    | DSR—Data Set Ready                           | . 21-7 |

| 21.4.6    | DCD—Data Carrier Detect.                     | . 21-7 |

| 21.4.7    | RI—Ring Indicator                            | . 21-7 |

| 21.4.8    | CTS—Clear To Send                            |        |

| 21.4.9    | Programmable CTS Deassertion.                |        |

| 21.4.10   | TXD—UART Transmit                            |        |

| 21.4.11   | RXD—UART Receive                             |        |

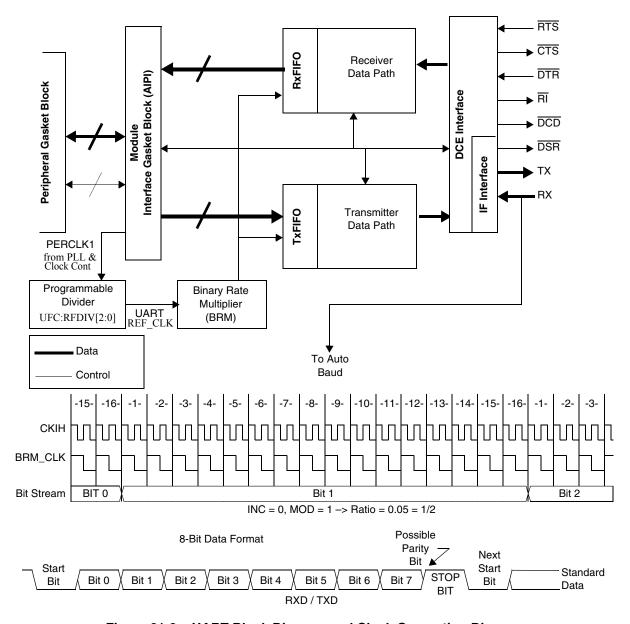

| 21.5 Sub  | p-Block Description                          | . 21-9 |

| 21.5.1    | Transmitter                                  |        |

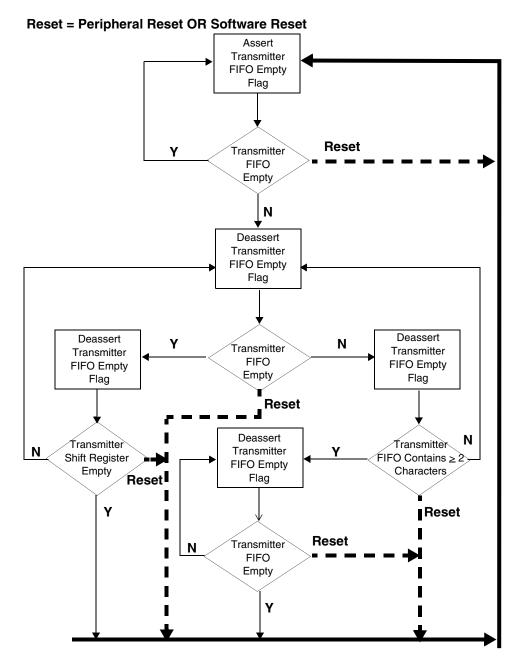

| 21.5.2    | Transmitter FIFO Empty Interrupt Suppression |        |

| 21.5.3    | Receiver                                     |        |

| 21.5.4    | Idle Line Detect                             |        |

| 21.5.4.1  | Idle Condition Detect Configuration          |        |

| 21.5.5    | Receiver Wake                                |        |

| 21.5.6    | Receiving a BREAK Condition                  |        |

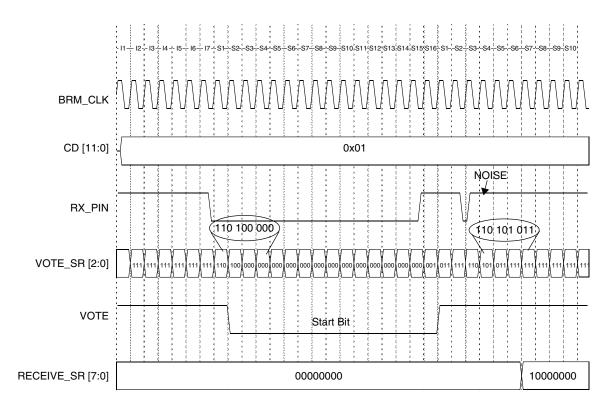

| 21.5.7    | Vote Logic                                   |        |

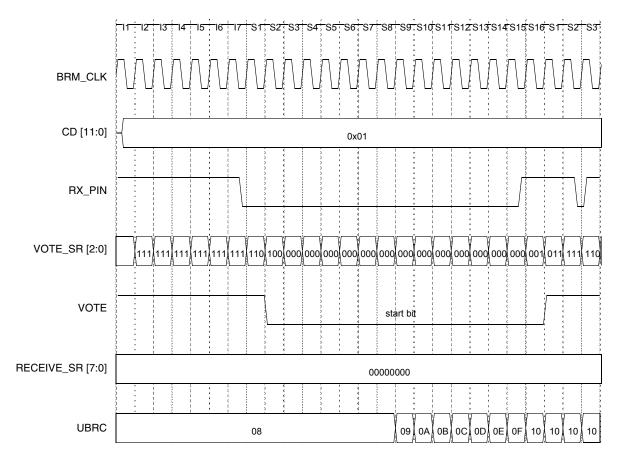

| 21.5.8    | Binary Rate Multiplier (BRM)                 |        |

| 21.5.9    | Baud Rate Automatic Detection Logic          |        |

| 21.5.9.1  | Baud Rate Automatic Detection Protocol.      |        |

| 21.5.10   | Escape Sequence Detection                    |        |

| 21.6 Infi | rared Interface                              |        |

|           | gramming Model                               |        |

| 21.7.1    | UART Receiver Registers                      |        |

| 21.7.2    | UART Transmitter Registers                   |        |

| 21.7.3    | UART Control Register 1                      |        |

| 21.7.4    | UART Control Register 2                      |        |

| 21.7.5    | UART Control Register 3                      |        |

| 21.7.5.1  | UART1 Control Register 3                     |        |

| 21.7.5.2  | UART2 Control Register 3                     |        |

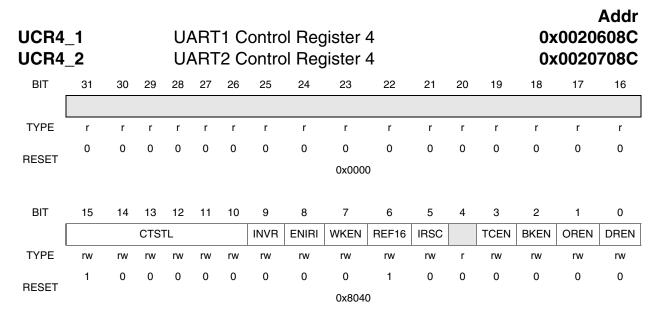

| 21.7.6    | UART Control Register 4                      |        |

| 21.7.7    | UART FIFO Control Registers                  |        |

| 21.7.8    | UART Status Register 1                       |        |

| 21.7.9    | UART Status Register 2                       |        |

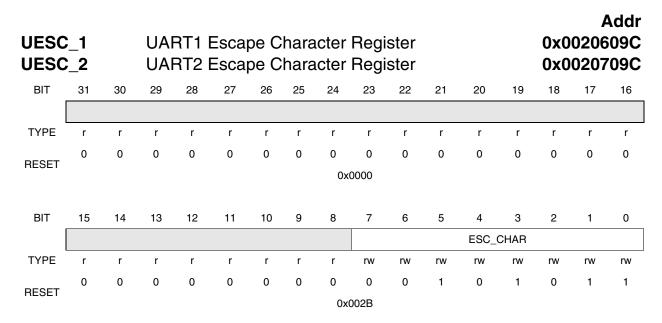

| 21.7.10   | UART Escape Character Registers              |        |

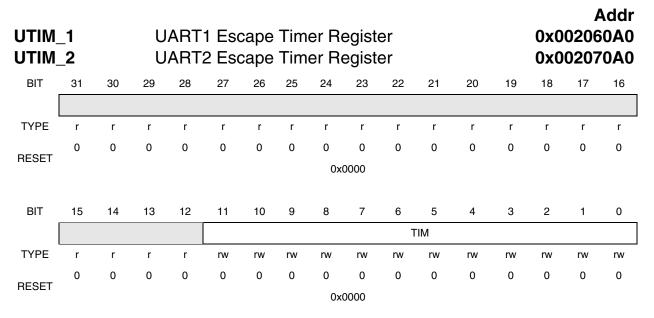

| 21.7.11   | UART Escape Timer Registers.                 |        |

| 21.7.12   | UART BRM Incremental Registers               |        |

| 21.7.13   | UART BRM Modulator Registers                 |        |

| 21.7.14   | UART Baud Rate Count Registers               |        |

| 21.7.15   | UART BRM Incremental Preset Registers 1–4    |        |

| 21.7.16   | UART BRM Modulator Preset Registers 1–4      |        |

| 21.7.17   | UART Test Register 1                         |        |

|           | 5                                            |        |

xiv Freescale Semiconductor

| 21.8        | UART Operation in Low-Power System States         | 21-52 |

|-------------|---------------------------------------------------|-------|

| Chap<br>USB | ter 22<br>Device Port                             |       |

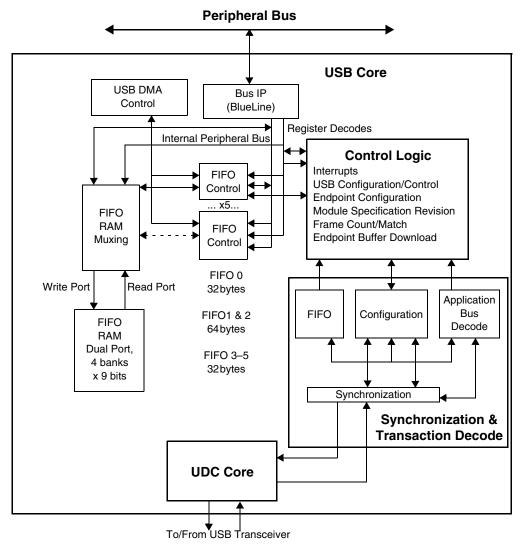

| 22.1        | Introduction                                      |       |

| 22.1.1      | Features                                          |       |

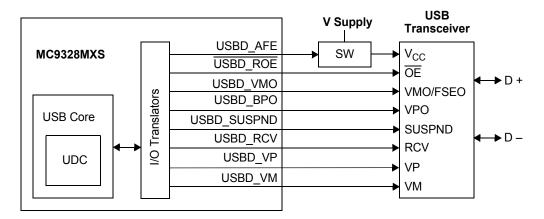

| 22.2        | Module Components                                 |       |

| 22.2.1      | Universal Serial Bus Device Controller            |       |

| 22.2.2      | Synchronization and Transaction Decode            |       |

| 22.2.3      | Endpoint FIFO Architecture                        |       |

| 22.2.4      | Control Logic                                     |       |

| 22.2.5      | USB Transceiver Interface                         |       |

| 22.2.6      | Signal Description                                |       |

| 22.2.7      | Pin Configuration for USB                         |       |

| 22.3        | Programming Model                                 |       |

| 22.3.1      | USB Frame Register                                |       |

| 22.3.2      | USB Specification Register                        |       |

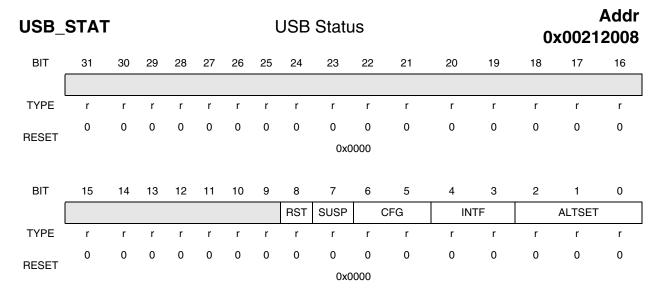

| 22.3.3      | USB Status Register                               |       |

| 22.3.4      | USB Control Register                              | 22-11 |

| 22.3.5      | USB Descriptor RAM Address Register               | 22-13 |

| 22.3.6      | USB Descriptor RAM/Endpoint Buffer Data Register  | 22-14 |

| 22.3.7      | USB Interrupt Register                            |       |

| 22.3.8      | USB Interrupt Mask Register                       | 22-17 |

| 22.3.9      | USB Enable Register                               |       |

| 22.3.10     | Endpoint n Status/Control Registers               | 22-19 |

| 22.3.11     | Endpoint n Interrupt Status Registers             | 22-20 |

| 22.3.12     | Endpoint n Interrupt Mask Register                | 22-23 |

| 22.3.13     | Endpoint n FIFO Data Registers                    | 22-25 |

| 22.3.14     | Endpoint n FIFO Status Registers                  | 22-26 |

| 22.3.15     | Endpoint n FIFO Control Registers                 | 22-28 |

| 22.3.16     | USB Endpoint n Last Read Frame Pointer Registers  | 22-30 |

| 22.3.17     | USB Endpoint n Last Write Frame Pointer Registers | 22-31 |

| 22.3.18     | B Endpoint n FIFO Alarm Registers                 | 22-32 |

| 22.3.19     | Endpoint n FIFO Read Pointer Registers            | 22-33 |

| 22.3.20     | Endpoint n FIFO Write Pointer Registers           | 22-34 |

| 22.4        | Programmer's Reference                            | 22-34 |

| 22.5        | Device Initialization                             | 22-35 |

| 22.5.1      | Configuration Download                            | 22-36 |

| 22.5.1.     |                                                   |       |

| 22.5.1.     |                                                   |       |

| 22.5.1.     | •                                                 |       |

| 22.5.1.     |                                                   |       |

| 22.6        | Exception Handling                                |       |

| 22.6.1      | Unable to Complete Device Request                 |       |

|             | •                                                 |       |

ΧV

Freescale Semiconductor

| 22.6.2   | Aborted Device Request                                | 22-38 |  |  |  |

|----------|-------------------------------------------------------|-------|--|--|--|

| 22.6.3   | Unable to Fill or Empty FIFO Due to Temporary Problem |       |  |  |  |

| 22.6.4   | Catastrophic Error                                    |       |  |  |  |

| 22.7 Da  | ata Transfer Operations                               | 22-39 |  |  |  |

| 22.7.1   | USB Packets                                           | 22-39 |  |  |  |

| 22.7.1.1 | Short Packets                                         | 22-39 |  |  |  |

| 22.7.1.2 | Sending Packets                                       | 22-40 |  |  |  |

| 22.7.1.3 | Receiving Packets                                     | 22-40 |  |  |  |

| 22.7.1.4 | Programming the FIFO Controller                       | 22-41 |  |  |  |

| 22.7.2   | USB Transfers                                         | 22-41 |  |  |  |

| 22.7.2.1 | Data Transfers to the Host                            | 22-41 |  |  |  |

| 22.7.2.2 | Data Transfers to the Device                          | 22-42 |  |  |  |

| 22.7.3   | Control Transfers                                     | 22-42 |  |  |  |

| 22.7.4   | Bulk Traffic                                          | 22-42 |  |  |  |

| 22.7.4.1 | Bulk OUT                                              | 22-42 |  |  |  |

| 22.7.4.2 | Bulk IN                                               | 22-43 |  |  |  |

| 22.7.5   | Interrupt Traffic                                     | 22-43 |  |  |  |

| 22.7.6   | Isochronous Operations                                | 22-43 |  |  |  |

| 22.7.6.1 | Isochronous Transfers in a Nutshell                   | 22-43 |  |  |  |

| 22.7.6.2 | The SYNCH_FRAME Standard Request                      | 22-44 |  |  |  |

| 22.8 Int | terrupt Services                                      | 22-44 |  |  |  |

| 22.8.1   | USB General Interrupts                                | 22-44 |  |  |  |

| 22.8.1.1 | MSOF—Missed Start-of-Frame                            | 22-44 |  |  |  |

| 22.8.1.2 | SOF—Start-of-Frame                                    | 22-44 |  |  |  |

| 22.8.1.3 | RESET_STOP—End of USB Reset Signaling                 | 22-44 |  |  |  |

| 22.8.1.4 | RESET_START—Start of USB Reset Signaling              | 22-45 |  |  |  |

| 22.8.1.5 | WAKEUP—Resume (Wakeup) Signaling Detected             |       |  |  |  |

| 22.8.1.6 | SUSP—USB Suspended                                    |       |  |  |  |

| 22.8.1.7 | FRAME_MATCH—Match Detected in USB_FRAME Register      | 22-45 |  |  |  |

| 22.8.1.8 | CFG_CHG—Host Changed USB Device Configuration         |       |  |  |  |

| 22.8.2   | Endpoint Interrupts                                   |       |  |  |  |

| 22.8.2.1 | FIFO_FULL                                             | 22-45 |  |  |  |

| 22.8.2.2 | FIFO_EMPTY                                            |       |  |  |  |

| 22.8.2.3 | FIFO_ERROR                                            |       |  |  |  |

| 22.8.2.4 | FIFO_HIGH                                             |       |  |  |  |

| 22.8.2.5 | FIFO_LOW                                              |       |  |  |  |

| 22.8.2.6 | EOT—End of Transfer                                   |       |  |  |  |

| 22.8.2.7 | DEVREQ—Device Request                                 |       |  |  |  |

| 22.8.2.8 | MDEVREQ—Multiple Device Request.                      |       |  |  |  |

| 22.8.2.9 | EOF—End of Frame.                                     |       |  |  |  |

| 22.8.3   | Interrupts, Missed Interrupts, and the USB            |       |  |  |  |

| 22.8.3.1 | SOF                                                   |       |  |  |  |

| 22.8.3.2 | CFG_CHG                                               |       |  |  |  |