# SEMICONDUCTOR, INC. BEYOND MEMORY

# Not Recommended for New Design CAT521

# Configured Digitally Programmable Potentiometer (DPP™): Programmable Voltage Applications

## FEATURES

- 8-bit DPP configured as a programmable voltage source in DAC-like applications

- Buffered wiper output

- Non-volatile NVRAM memory wiper storage

- Output voltage range includes both supply rails

- 1 LSB accuracy, high resolution

- Serial Microwire-like interface

- Single supply operation: 2.7V 5.5V

- Setting read-back without effecting outputs

For Ordering Information details, see page 12.

## **APPLICATIONS**

- Automated product calibration

- Remote control adjustment of equipment

- Offset, gain and zero adjustments in selfcalibrating and adaptive control systems

- Tamper-proof calibrations

- DAC (with memory) substitute

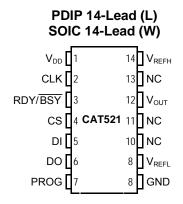

## **PIN CONFIGURATION**

## DESCRIPTION

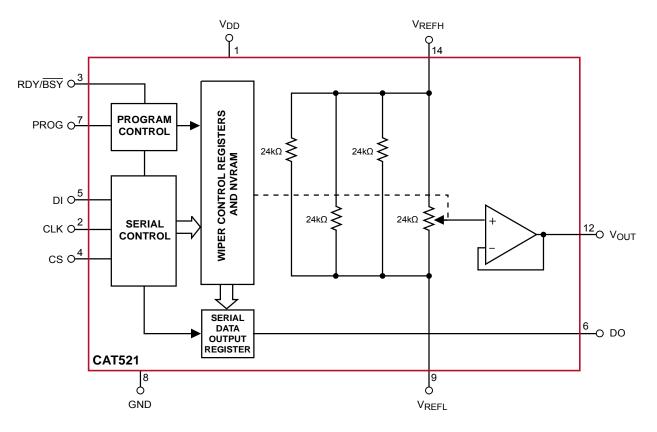

The CAT521 is a 8-bit digitally-programmable potentiometer (DPP<sup>™</sup>) configured for programmable voltage and DAC-like applications. Intended for final calibration of products such as camcorders, fax machines and cellular telephones on automated high volume production lines, it is also well suited for self-calibrating systems and for applications where equipment which requires periodic adjustment is either difficult to access or in a hazardous environment.

The programmable DPP has an output voltage range which includes both supply rails. The wiper is buffered by a rail to rail op amp. The wiper setting, stored in non-volatile NVRAM memory, is not lost when the device is powered down and is automatically reinstated when power is returned. The wiper can be dithered to test new output values without effecting the stored settings and stored settings can be read back without disturbing the DPP's output.

The CAT521 is controlled with a simple 3-wire, Microwire like serial interface. A Chip Select pin allows several devices to share a common serial interface. Communication back to the host controller is via a single serial data line thanks to the CAT521 Tri-Stated Data Output pin. A RDY/BSY output working in concert with an internal low voltage detector signals proper operation of the non-volatile NVRAM memory Erase/Write cycle.

The CAT521 is available in 0°C to 70°C commercial and -40°C to 85°C industrial operating temperature ranges. Both 14-pin plastic DIP and surface mount packages are available.

## FUNCTIONAL DIAGRAM

#### ABSOLUTE MAXIMUM RATINGS

| Parameters                | Ratings                      | Units |

|---------------------------|------------------------------|-------|

| Supply Voltage*           |                              | V     |

| V <sub>DD</sub> to GND    | -0.5 to +7                   | v     |

| Inputs                    |                              |       |

| CLK to GND                | -0.5 to $V_{\text{DD}}$ +0.5 | V     |

| CS to GND                 | -0.5 to $V_{\text{DD}}$ +0.5 | V     |

| DI to GND                 | -0.5 to $V_{\text{DD}}$ +0.5 | V     |

| RDY/BSY to GND            | -0.5 to $V_{\text{DD}}$ +0.5 | V     |

| PROG to GND               | -0.5 to V <sub>DD</sub> +0.5 | V     |

| V <sub>REF</sub> H to GND | -0.5 to V <sub>DD</sub> +0.5 | V     |

| V <sub>REF</sub> L to GND | -0.5 to $V_{\text{DD}}$ +0.5 | V     |

| Parameters                                                           | Ratings                      | Units |

|----------------------------------------------------------------------|------------------------------|-------|

| Outputs<br>D <sub>0</sub> to GND                                     | -0.5 to V <sub>DD</sub> +0.5 | V     |

| V <sub>OUT</sub> 1–4 to GND                                          | -0.5 to $V_{\text{DD}}$ +0.5 | V     |

| Operating Ambient Temperature<br>Commercial<br>('C' or Blank suffix) | 0 to +70                     | °C    |

| Industrial ('l' suffix)                                              | -40 to +85                   | °C    |

| Junction Temperature                                                 | +150                         | °C    |

| Storage Temperature                                                  | -65 to +150                  | °C    |

| Lead Soldering (10 sec max)                                          | +300                         | °C    |

#### **RELIABILITY CHARACTERISTICS**

| Symbol                             | Parameter          | Test Method                   | Min  | Max | Units |

|------------------------------------|--------------------|-------------------------------|------|-----|-------|

| V <sub>ZAP</sub> <sup>(2)</sup>    | ESD Susceptibility | MIL-STD-883, Test Method 3015 | 2000 |     | V     |

| I <sub>LTH</sub> <sup>(2)(3)</sup> | Latch-Up           | JEDEC Standard 17             | 100  |     | mA    |

#### **POWER SUPPLY**

| Symbol           | Parameter               | Conditions                 | Min | Тур  | Max  | Units |

|------------------|-------------------------|----------------------------|-----|------|------|-------|

| I <sub>DD1</sub> | Supply Current (Read)   | Normal Operating           | _   | 400  | 600  | μA    |

| I <sub>DD2</sub> | Supply Current (Write)  | Programming, $V_{DD}$ = 5V | _   | 1600 | 2500 | μA    |

|                  |                         | V <sub>DD</sub> = 3V       |     | 1000 | 1600 | μA    |

| V <sub>DD</sub>  | Operating Voltage Range |                            | 2.7 | _    | 5.5  | V     |

### LOGIC INPUTS

| Symbol          | Parameter                | Conditions           | Min | Тур | Max             | Units |

|-----------------|--------------------------|----------------------|-----|-----|-----------------|-------|

| I <sub>IH</sub> | Input Leakage Current    | $V_{IN} = V_{DD}$    | _   | —   | 10              | μA    |

| I <sub>IL</sub> | Input Leakage Current    | V <sub>IN</sub> = 0V | _   | —   | -10             | μA    |

| V <sub>IH</sub> | High Level Input Voltage |                      | 2   | —   | $V_{\text{DD}}$ | V     |

| V <sub>IL</sub> | Low Level Input Voltage  |                      | 0   | _   | 0.8             | V     |

### LOGIC OUTPUTS

| Symbol          | Parameter                 | Conditions                                      | Min                  | Тур | Max | Units |

|-----------------|---------------------------|-------------------------------------------------|----------------------|-----|-----|-------|

| V <sub>OH</sub> | High Level Output Voltage | Ι <sub>ΟΗ</sub> = -40μΑ                         | V <sub>DD</sub> -0.3 | —   | _   | V     |

| VIL             | Low Level Output Voltage  | I <sub>OL</sub> = 1 mA, V <sub>DD</sub> = +5V   | —                    | —   | 0.4 | V     |

|                 |                           | I <sub>OL</sub> = 0.4 mA, V <sub>DD</sub> = +3V | _                    |     | 0.4 | V     |

Notes:

(1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

(2) This parameter is tested initially and after a design or process change that affects the parameter.

(3) Latch-up protection is provided for stresses up to 100mA on address and data pins from -1V to  $V_{CC}$  + 1V.

#### POTENTIOMETER CHARACTERISTICS

$V_{DD}$  = +2.7V to +5.5V,  $V_{REFH}$  =  $V_{DD}$ ,  $V_{REFL}$  = 0V, unless otherwise specified

| Symbol             | Parameter                        | Conditions | Min | Тур  | Max                   | Units  |

|--------------------|----------------------------------|------------|-----|------|-----------------------|--------|

| R <sub>POT</sub>   | Potentiometer Resistance         | See note 3 |     | 24   |                       | kΩ     |

|                    | R <sub>POT</sub> to RPOT Match   |            | —   | ±0.5 | ±1                    | %      |

|                    | Pot Resistance Tolerance         |            |     |      | ±20                   | %      |

|                    | Voltage on V <sub>REFH</sub> pin |            | 2.7 |      | $V_{DD}$              | V      |

|                    | Voltage on V <sub>REFL</sub> pin |            | 0   |      | V <sub>DD</sub> - 2.7 | V      |

|                    | Resolution                       |            |     | 0.4  |                       | %      |

| INL                | Integral Linearity Error         |            |     | 0.5  | 1                     | LSB    |

| DNL                | Differential Linearity Error     |            |     | 0.25 | 0.5                   | LSB    |

| R <sub>OUT</sub>   | Buffer Output Resistance         |            |     |      | 10                    | Ω      |

| I <sub>OUT</sub>   | Buffer Output Current            |            |     |      | 3                     | mA     |

| TC <sub>RPOT</sub> | TC of Pot Resistance             |            |     | 300  |                       | ppm/ºC |

| $C_H/C_L$          | Potentiometer Capacitances       |            |     | 8/8  |                       | pF     |

#### **AC ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = +2.7V to +5.5V,  $V_{REFH}$  =  $V_{DD}$ ,  $V_{REFL}$  = 0V, unless otherwise specified

| Symbol             | Parameter                  | Conditions                        | Min | Тур | Max | Units |

|--------------------|----------------------------|-----------------------------------|-----|-----|-----|-------|

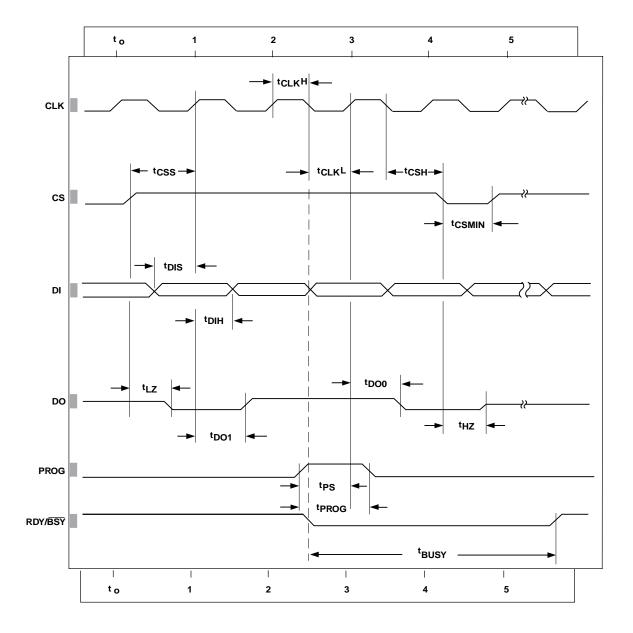

| Digital            |                            |                                   |     |     |     |       |

| t <sub>CSMIN</sub> | Minimum CS Low Time        |                                   | 150 | _   | —   | ns    |

| t <sub>CSS</sub>   | CS Setup Time              |                                   | 100 | —   | —   | ns    |

| t <sub>CSH</sub>   | CS Hold Time               |                                   | 0   | —   | —   | ns    |

| t <sub>DIS</sub>   | DI Setup Time              |                                   | 50  | —   | _   | ns    |

| t <sub>DIH</sub>   | DI Hold Time               | $C_{L} = 100 pF^{(1)}$            | 50  | —   | —   | ns    |

| t <sub>DO1</sub>   | Output Delay to 1          |                                   | _   | _   | 150 | ns    |

| t <sub>DO0</sub>   | Output Delay to 0          |                                   | _   | _   | 150 | ns    |

| t <sub>HZ</sub>    | Output Delay to High-Z     |                                   | _   | 400 | _   | ns    |

| t <sub>LZ</sub>    | Output Delay to Low-Z      |                                   | _   | 400 | _   | ns    |

| t <sub>BUSY</sub>  | Erase/Write Cycle Time     |                                   | _   | 4   | 5   | ms    |

| t <sub>PS</sub>    | PROG Setup Time            |                                   | 150 | —   | —   | ns    |

| t <sub>PROG</sub>  | Minimum Pulse Width        |                                   | 700 | _   | _   | ns    |

| t <sub>ськ</sub> Н | Minimum CLK High Time      |                                   | 500 | —   | _   | ns    |

| t <sub>CLK</sub> L | Minimum CLK Low Time       |                                   | 300 | —   | —   | ns    |

| f <sub>C</sub>     | Clock Frequency            |                                   | DC  | _   | 1   | MHz   |

| Analog             |                            |                                   |     |     |     |       |

| t <sub>DS</sub>    | DPP Settling Time to 1 LSB | $C_{LOAD}$ = 10pF, $V_{DD}$ = +5V |     | 3   | 10  | μs    |

|                    |                            | $C_{LOAD}$ = 10pF, $V_{DD}$ = +3V | _   | 6   | 10  | μs    |

Notes:

(1) All timing measurements are defined at the point of signal crossing  $V_{\mbox{\tiny DD}}$  / 2.

(2) These parameters are periodically sampled and are not 100% tested.

(3) The 24k $\Omega$  +20% resistors are configured as 4 resistors in parallel which would provide a measured value between V<sub>REFL</sub> and V<sub>REFL</sub> of 6k $\Omega$  +20%. The individual 24k $\Omega$  resistors are not measurable but guaranteed by design and verification of the 6k $\Omega$  +20% value.

## A.C. TIMING DIAGRAM

## PIN DESCRIPTION

| Pin | Name             | Function                           |

|-----|------------------|------------------------------------|

| 1   | $V_{DD}$         | Power supply positive              |

| 2   | CLK              | Clock input pin                    |

| 3   | RDY/BSY          | Ready/Busy output                  |

| 4   | CS               | Chip select                        |

| 5   | DI               | Serial data input pin              |

| 6   | DO               | Serial data output pin             |

| 7   | PROG             | EEPROM Programming Enable<br>Input |

| 8   | GND              | Power supply ground                |

| 9   | $V_{REFL}$       | Minimum DAC output voltage         |

| 10  | NC               | No Connect                         |

| 11  | NC               | No Connect                         |

| 12  | V <sub>OUT</sub> | DPP output                         |

| 13  | NC               | No Connect                         |

| 14  | $V_{REFH}$       | Maximum DPP 1 output voltage       |

DPP addressing is as follows:

| DPP OUTPUT       | A0 | A1 |

|------------------|----|----|

| V <sub>OUT</sub> | 1  | 0  |

## **DEVICE OPERATION**

The CAT521 is a single 8-bit configured digitally programmable potentiometer (DPP<sup>TM</sup>) whose output can be programmed to any one of 256 individual voltage steps. Once programmed, the output setting is retained in non-volatile memory and will not be lost when power is removed from the chip. Upon power up the DPP returns to the setting stored in non-volatile memory. The DPP can be written to and read from without effecting the output voltage during the read or write cycle. The output can also be adjusted without altering the stored output setting, which is useful for testing new output settings before storing them in memory.

#### DIGITAL INTERFACE

The CAT521 employs a 3 wire, Microwire-like serial control interface consisting of Clock (CLK), Chip Select (CS) and Data In (DI) inputs. For all operations, address and data are shifted in LSB first. In addition, all digital data must be preceded by a logic "1" as a start bit. The DPP address and data are clocked into the DI pin on the clock's rising edge. When sending multiple blocks of information a minimum of two clock cycles is required between the last block sent and the next start bit.

Multiple devices may share a common input data line by selectively activating the CS control of the desired IC. Data Outputs (DO) can also share a common line because the DO pin is Tri-Stated and returns to a high impedance when not in use.

#### CHIP SELECT

Chip Select (CS) enables and disables the CAT521's read and write operations. When CS is high data may be read to or from the chip, and the Data Output (DO) pin is active. Data loaded into the DPP control register will remain in effect until CS goes low. Bringing CS to a logic low returns all DPP outputs to the settings stored in nonvolatile memory and switches DO to its high impedance Tri-State mode.

Because CS functions like a reset the CS pin has been desensitized with a 30ns to 90ns filter circuit to prevent noise spikes from causing unwanted resets and the loss of volatile data.

#### CLOCK

The CAT521 clock controls both data flow in and out of the device and non-volatile memory cell programming. Serial data is shifted into the DI pin and out of the DO pin on the clock's rising edge. While it is not necessary for the clock to be running between data transfers, the clock must be operating in order to write to non-volatile memory, even though the data being saved may already be resident in the DPP wiper control register.

No clock is necessary upon system power-up. The CAT521 internal power-on reset circuitry loads data from non-volatile memory to the DPP without using the external clock.

As data transfers are edge triggered clean clock transitions are necessary to avoid falsely clocking data into the control register. Standard CMOS and TTL logic families work well in this regard and it is recommended that any mechanical switches used for breadboarding or device evaluation purposes be debounced by a flip-flop or other suitable debouncing circuit.

#### $V_{\text{REF}}$

$V_{REF}$ , the voltage applied between pins  $V_{REFH} \& V_{REFL}$ , sets the DPP's Zero to Full Scale output range where  $V_{REFL}$  = Zero and  $V_{REFH}$  = Full Scale.  $V_{REF}$  can span the full power supply range or just a fraction of it. In typical applications  $V_{REFH} \& V_{REFL}$  are connected across the power supply rails. When using less than the full supply voltage be mindfull of the limits placed on  $V_{REFH}$  and  $V_{REFL}$  as specified in the References section of DC Electrical Characteristics.

### READY/BUSY

When saving data to non-volatile memory, the Ready/Busy ouput (RDY/BSY) signals the start and duration of the erase/write cycle. Upon receiving a command to store data (PROG goes high) RDY/BSY goes low and remains low until the programming cycle is complete. During this time the CAT521 will ignore any data appearing at DI and no data will be output on DO.

$RDY/\overline{BSY}$  is internally ANDed with a low voltage detector circuit monitoring  $V_{DD}$ . If  $V_{DD}$  is below the minimum value required for EEPROM programming,

RDY/BSY will remain high following the program command indicating a failure to record the desired data in non-volatile memory.

### DATA OUTPUT

Data is output serially by the CAT521, LSB first, via the Data Out (DO) pin following the reception of a start bit and two address bits by the Data Input (DI). DO becomes active whenever CS goes high and resumes its high impedance Tri-State mode when CS returns low. Tri-Stating the DO pin allows several 521s to share a single serial data line and simplifies interfacing multiple 521s to a microprocessor.

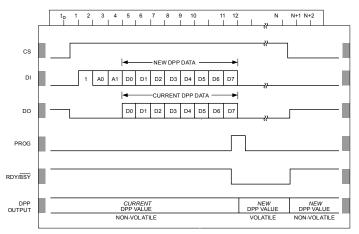

#### WRITING TO MEMORY

Programming the CAT521's non-volatile memory is accomplished through the control signals: Chip Select (CS) and Program (PROG). With CS high, a start bit followed by a two bit DPP address and eight data bits are clocked into the DPP wiper control register via the DI pin. Data enters on the clock's rising edge. The DPP output changes to its new setting on the clock cycle following D7, the last data bit.

Programming is accomplished by bringing PROG high sometime after the start bit and at least 150ns prior to the rising edge of the clock cycle immediately following the D7 bit. Two clock cycles after the D7 bit the DPP wiper control register will be ready to receive the next set of address and data bits. The clock must be kept running throughout the programming cycle. Internal control circuitry takes care of generating and ramping up the programming voltage for data transfer to the non-volatile memory cells. The CAT521 nonvolatile memory cells will endure over 1,000,000 write cycles and will retain data for a minimum of 100 years without being refreshed.

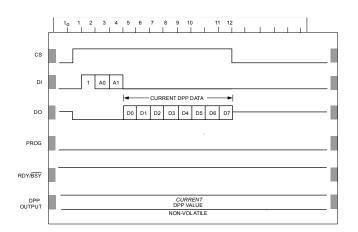

Figure 1. Writing to Memory

### **READING DATA**

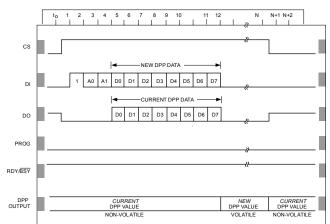

Each time data is transferred into the DPP wiper control register currently held data is shifted out via the D0 pin, thus in every data transaction a read cycle occurs. Note, however, that the reading process is destructive. Data must be removed from the register in order to be read. Figure 2 depicts a Read Only cycle in which no change occurs in the DPP's output. This feature allows µPs to poll DPPs for their current setting without disturbing the output voltage but it assumes that the setting being read is also stored in non-volatile memory so that it can be restored at the end of the read cycle. In Figure 2 CS returns low before the 13<sup>th</sup> clock cycle completes. In doing so the non-volatile memory's setting is reloaded into the DPP wiper control register. Since this value is the same as that which had been there previously no change in the DPP's output is noticed. Had the value held in the control register been different from that stored in nonvolatile memory then a change would occur at the read cycle's conclusion.

## TEMPORARILY CHANGE OUTPUT

The CAT521 allows temporary changes in the DPP's output to be made without disturbing the settings retained in non-volatile memory. This feature is particularly useful when testing for a new output setting and allows for user adjustment of preset or default values without losing the original factory settings.

Figure 3 shows the control and data signals needed to effect a temporary output change. DPP settings may be changed as many times as required. The temporary setting remains in effect long as CS remains high. When CS returns low the DPP will return to the output value stored in non-volatile memory.

When it is desired to save a new setting acquired using this feature, the new value must be reloaded into the DPP wiper control register prior to programming. This is because the CAT521's internal control circuitry discards from the programming register the new data two clock cycles after receiving it if no PROG signal is received.

Figure 2. Reading from Memory

#### Figure 3. Temporary Change in Output

## **APPLICATION CIRCUITS**

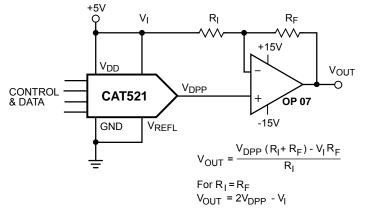

| DPP I | NPUT | DPP OUTPUT                                                                                | ANALOG OUTPUT                   |

|-------|------|-------------------------------------------------------------------------------------------|---------------------------------|

|       |      | $V_{DPP} = \frac{CODE}{255} \times (V_{FS} - V_{ZERO}) + V_{ZERO}$                        |                                 |

| MSB   | LSB  | V <sub>FS</sub> = 0.99V <sub>REF</sub>                                                    | V <sub>REF</sub> = 5V           |

|       |      | V <sub>ZERO</sub> = 0.01V <sub>REF</sub>                                                  | R <sub>I</sub> = R <sub>F</sub> |

| 1111  | 1111 | $\frac{255}{255} \times 0.98 V_{\text{REF}} + 0.01 V_{\text{REF}} = 0.990 V_{\text{REF}}$ | V <sub>OUT</sub> = +4.90V       |

| 1000  | 0000 | $\frac{128}{255} \times 0.98V_{\text{REF}} + 0.01V_{\text{REF}} = 0.502V_{\text{REF}}$    | V <sub>OUT</sub> = +0.02V       |

| 0111  | 1111 | $\frac{127}{255} \times 0.98V_{\text{REF}} + 0.01V_{\text{REF}} = 0.498V_{\text{REF}}$    | V <sub>OUT</sub> = -0.02V       |

| 0000  | 0001 | $\frac{1}{255}$ × 0.98V <sub>REF</sub> + 0.01V <sub>REF</sub> = 0.014V <sub>REF</sub>     | V <sub>OUT</sub> = -4.86V       |

| 0000  | 0000 | $\frac{0}{255}$ × 0.98V <sub>REF</sub> + 0.01V <sub>REF</sub> = 0.010V <sub>REF</sub>     | V <sub>OUT</sub> = -4.90V       |

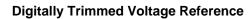

**Bipolar DPP Output**

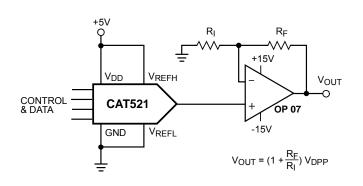

**Amplified DPP Output**

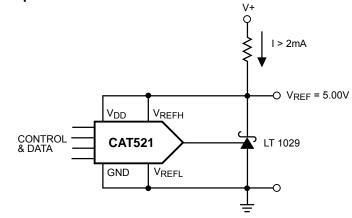

### **Digitally Controlled Voltage Reference**

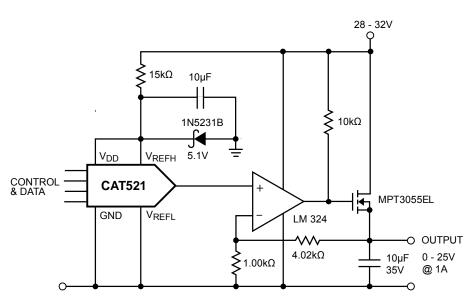

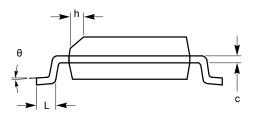

## PACKAGE OUTLINE DRAWINGS

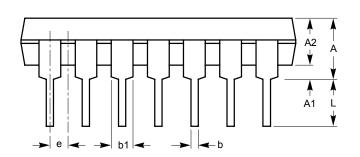

PDIP 14-Lead (L)<sup>(1)(2)</sup>

TOP VIEW

| SYMBOL | MIN   | NOM      | МАХ   |

|--------|-------|----------|-------|

| A      | 3.56  |          | 5.33  |

| A1     | 0.38  |          |       |

| A2     | 2.92  | 3.30     | 4.95  |

| b      | 0.36  | 0.45     | 0.55  |

| b1     | 1.15  | 1.52     | 1.77  |

| с      | 0.21  | 0.26     | 0.35  |

| D      | 18.67 | 19.05    | 19.68 |

| E      | 7.62  | 7.87     | 8.25  |

| E1     | 6.10  | 6.35     | 7.11  |

| е      |       | 2.54 BSC |       |

| eB     | 7.88  |          | 10.92 |

| L      | 2.99  | 3.30     | 3.81  |

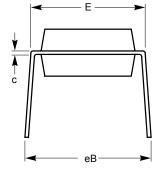

SIDE VIEW

END VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

#### Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MS-001.

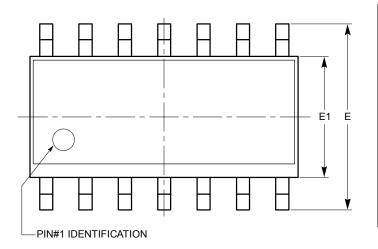

# SOIC 14-Lead (W)<sup>(1)(2)</sup>

| SYMBOL | MIN      | NOM  | MAX  |

|--------|----------|------|------|

| А      | 1.35     |      | 1.75 |

| A1     | 0.10     |      | 0.25 |

| b      | 0.33     |      | 0.51 |

| С      | 0.19     |      | 0.25 |

| D      | 8.55     | 8.65 | 8.75 |

| E      | 5.80     | 6.00 | 6.20 |

| E1     | 3.80     | 3.90 | 4.00 |

| е      | 1.27 BSC |      |      |

| h      | 0.25     |      | 0.50 |

| L      | 0.40     |      | 1.27 |

| θ      | 0°       |      | 8°   |

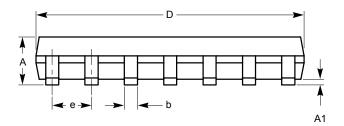

TOP VIEW

SIDE VIEW

END VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

#### Notes:

(1) All dimensions are in millimeters. Angles in degrees.

(2) Complies with JEDEC MS-012.

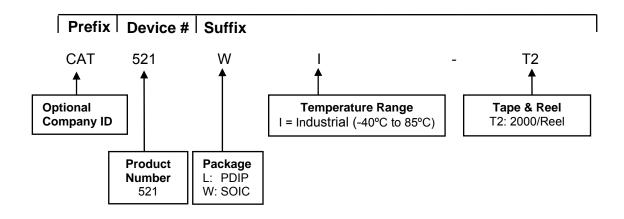

## EXAMPLE OF ORDERING INFORMATION

#### Notes:

- (1) All packages are RoHS compliant (Lead-free, Halogen-free).

- (2) Standard lead finish is Matte-Tin.

- (3) The device used in the above example is a CAT521WI-T2 (SOIC, Industrial Temperature, Tape & Reel).

| ORDERING INFORMATION |  |  |

|----------------------|--|--|

| CAT521WI             |  |  |

| CAT521LI             |  |  |

## **REVISION HISTORY**

| Date      | Revision | Description                                                                                                                       |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 16-Mar-04 | E        | Updated Potentiometer Characteristics                                                                                             |

| 12-Jul-04 | F        | Updated Functional Diagram<br>Updated Potentiometer Characteristics<br>Added Note 3 under Potentiometer/AC Characteristics tables |

| 26-Jul-07 | G        | Updated Ordering Information<br>Added MD- to document number<br>Add Package Outline Drawings                                      |

| 15-Jul-08 | Н        | Add "Not Recommended for New Design" to the top of all pages                                                                      |

#### Copyrights, Trademarks and Patents

© Catalyst Semiconductor, Inc.

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following: Adaptive Analog<sup>™</sup>, Beyond Memory<sup>™</sup>, DPP<sup>™</sup>, EZDim<sup>™</sup>, LDD<sup>™</sup>, MiniPot<sup>™</sup>, Quad-Mode<sup>™</sup> and Quantum Charge Programmable<sup>™</sup>

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000 Fax: 408.542.1200 OHwww.catsemi.com

Document No: MD-2003 Revision: H Issue date: 07/15/08