#### Data Sheet

## July 2003

# 3.2µs Sample and Hold Amplifiers

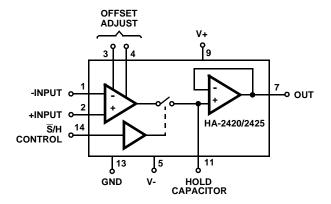

The HA-2420 and HA-2425 is a monolithic circuit consisting of a high performance operational amplifier with its output in series with an ultra-low leakage analog switch and JFET input unity gain amplifier.

With an external hold capacitor connected to the switch output, a versatile, high performance sample-and-hold or track-and-hold circuit is formed. When the switch is closed, the device behaves as an operational amplifier, and any of the standard op amp feedback networks may be connected around the device to control gain, frequency response, etc. When the switch is opened the output will remain at its last level.

Performance as a sample-and-hold compares very favorably with other monolithic, hybrid, modular, and discrete circuits. Accuracy to better than 0.01% is achievable over the temperature range. Fast acquisition is coupled with superior droop characteristics, even at high temperatures. High slew rate, wide bandwidth, and low acquisition time produce excellent dynamic characteristics. The ability to operate at gains greater than 1 frequently eliminates the need for external scaling amplifiers.

The device may also be used as a versatile operational amplifier with a gated output for applications such as analog switches, peak holding circuits, etc. For more information, please see Application Note AN517.

The MIL-STD-883 data sheet for this device is available on request.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE      | PKG.<br>DWG. # |

|-------------|----------------------------------|--------------|----------------|

| HA1-2420-2  | -55 to 125                       | 14 Ld CERDIP | F14.3          |

| HA1-2425-5  | 0 to 75                          | 14 Ld CERDIP | F14.3          |

| HA3-2425-5  | 0 to 75                          | 14 Ld PDIP   | E14.3          |

## Features

| • | Maximum | Acquisition | Time |

|---|---------|-------------|------|

|---|---------|-------------|------|

- 10V Step to 0.1% ...... 4μs (Max)

- 10V Step to 0.01% ..... 6μs (Max)

- Low Droop Rate (C<sub>H</sub> = 1000pF).....5μV/ms (Typ)

- Low Effective Aperture Delay Time ..... 30ns (Typ)

- TTL Compatible Control Input

- ±12V to ±15V Operation

## Applications

- 12-Bit Data Acquisition

- Digital to Analog Deglitcher

- Auto Zero Systems

- Peak Detector

- Gated Operational Amplifier

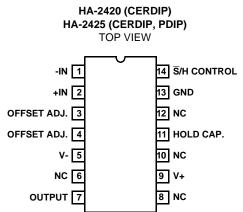

## Pinout

### **Absolute Maximum Ratings**

#### **Operating Conditions**

| Temperature Range                               |

|-------------------------------------------------|

| HA-2420-2                                       |

| HA-2425-5 0 <sup>o</sup> C to 75 <sup>o</sup> C |

| Supply Voltage Range (Typical) ±12V to ±15V     |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)    | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)    |

|-----------------------------------------|-------------------------------------|----------------------------------------|

| CERDIP Package                          | 75                                  | 20                                     |

| PDIP Package                            | 95                                  | N/A                                    |

| Maximum Junction Temperature (Ceramic   | Packages) .                         | 175 <sup>0</sup> C                     |

| Maximum Junction Temperature (Plastic F |                                     |                                        |

| Maximum Storage Temperature Range .     | 6                                   | 5 <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1   | 0s)                                 | 300 <sup>o</sup> C                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

# **Electrical Specifications** Test Conditions (Unless Otherwise Specified) V<sub>SUPPLY</sub> = ±15.0V; C<sub>H</sub> = 1000pF; Digital Input: V<sub>IL</sub> = +0.8V (Sample), V<sub>IH</sub> = +2.0V (Hold), Unity Gain Configuration (Output tied to Negative Input)

|                                            | TEST                                 | TEMP. | HA-2420-2 |      |     | HA-2425-5 |      |     |       |

|--------------------------------------------|--------------------------------------|-------|-----------|------|-----|-----------|------|-----|-------|

| PARAMETER                                  | CONDITIONS                           | (°C)  | MIN       | ТҮР  | MAX | MIN       | ТҮР  | MAX | UNITS |

| INPUT CHARACTERISTICS                      |                                      |       |           |      |     | 1         |      |     |       |

| Input Voltage Range                        |                                      | Full  | ±10       | -    | -   | ±10       | -    | -   | V     |

| Offset Voltage                             |                                      | 25    | -         | 2    | 4   | -         | 3    | 6   | mV    |

|                                            |                                      | Full  | -         | 3    | 6   | -         | 4    | 8   | mV    |

| Bias Current                               |                                      | 25    | -         | 40   | 200 | -         | 40   | 200 | nA    |

|                                            |                                      | Full  | -         | -    | 400 | -         | -    | 400 | nA    |

| Offset Current                             |                                      | 25    | -         | 10   | 50  | -         | 10   | 50  | nA    |

|                                            |                                      | Full  | -         | -    | 100 | -         | -    | 100 | nA    |

| Input Resistance                           |                                      | 25    | 5         | 10   | -   | 5         | 10   | -   | MΩ    |

| Common Mode Range                          |                                      | Full  | ±10       | -    | -   | ±10       | -    | -   | V     |

| TRANSFER CHARACTERISTICS                   | L                                    |       |           |      | J   |           |      |     |       |

| Large Signal Voltage Gain                  | $R_L = 2k\Omega$ , $V_O = 20V_{P-P}$ | Full  | 25        | 50   | -   | 25        | 50   | -   | kV/V  |

| Common Mode Rejection                      | $V_{CM} = \pm 10V$                   | Full  | 80        | 90   | -   | 74        | 90   | -   | dB    |

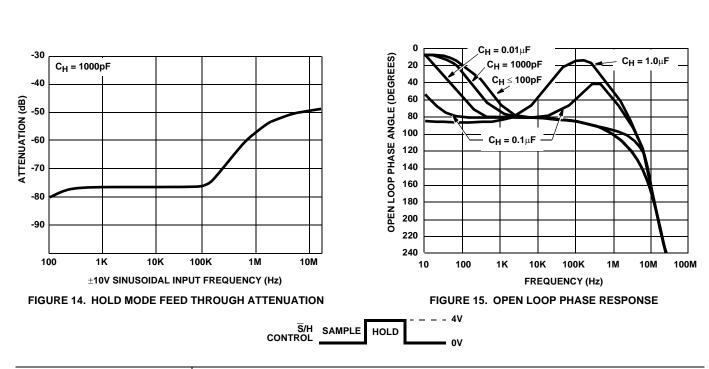

| Hold Mode Feedthrough Attenuation (Note 2) | $f_{IN} \leq 100 kHz$                | Full  | -         | -76  | -   | -         | -76  | -   | dB    |

| Gain Bandwidth Product (Note 2)            |                                      | 25    | -         | 2.5  | -   | -         | 2.5  | -   | MHz   |

| OUTPUT CHARACTERISTICS                     | 1                                    |       |           |      |     | 1         |      |     | 1     |

| Output Voltage Swing                       | $R_L = 2k\Omega$                     | Full  | ±10       | -    | -   | ±10       | -    | -   | V     |

| Output Current                             |                                      | 25    | ±15       | -    | -   | ±15       | -    | -   | mA    |

| Full Power Bandwidth (Note 2)              | $V_{O} = 20V_{P-P}$                  | 25    | -         | 100  | -   | -         | 100  | -   | kHz   |

| Output Resistance                          | DC                                   | 25    | -         | 0.15 | -   | -         | 0.15 | -   | Ω     |

| TRANSIENT RESPONSE                         | 1                                    |       |           | 1    | 1   | 1         | 1    | 1   | 1     |

| Rise Time (Note 2)                         | $V_{O} = 200 \text{mV}_{P-P}$        | 25    | -         | 75   | 100 | -         | 75   | 100 | ns    |

| Overshoot (Note 2)                         | $V_{O} = 200 \text{mV}_{P-P}$        | 25    | -         | 25   | 40  | -         | 25   | 40  | %     |

| Slew Rate (Note 2)                         | V <sub>O</sub> = 10V <sub>P-P</sub>  | 25    | 3.5       | 5    | -   | 3.5       | 5    | _   | V/µs  |

## **Electrical Specifications**

Test Conditions (Unless Otherwise Specified)  $V_{SUPPLY} = \pm 15.0V$ ;  $C_H = 1000pF$ ; Digital Input:  $V_{IL} = +0.8V$  (Sample),  $V_{IH} = +2.0V$  (Hold), Unity Gain Configuration (Output tied to Negative Input) (Continued)

|                                 | TEST                 | TEMP. | HA-2420-2 |     |      | HA-2425-5 |     |      |       |

|---------------------------------|----------------------|-------|-----------|-----|------|-----------|-----|------|-------|

| PARAMETER                       | CONDITIONS           | (°C)  | MIN       | ТҮР | MAX  | MIN       | TYP | MAX  | UNITS |

| DIGITAL INPUT CHARACTERIS       | TICS                 |       |           |     |      |           |     |      |       |

| Digital Input Current           | $V_{IN} = 0V$        | Full  | -         | -   | -0.8 | -         | -   | -0.8 | mA    |

|                                 | V <sub>IN</sub> = 5V | Full  | -         | -   | 20   | -         | -   | 20   | μΑ    |

| Digital Input Voltage           | Low                  | Full  | -         | -   | 0.8  | -         | -   | 0.8  | V     |

|                                 | High                 | Full  | 2.0       | -   | -    | 2.0       | -   | -    | V     |

| SAMPLE AND HOLD CHARACT         | ERISTICS             |       |           |     |      | •         | •   | •    |       |

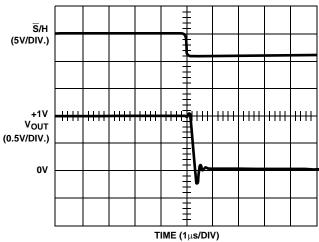

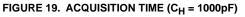

| Acquisition Time (Note 2)       | To 0.1% 10V Step     | 25    | -         | 2.3 | 4    | -         | 2.3 | 4    | μs    |

| Acquisition Time (Note 2)       | To 0.01% 10V Step    | 25    | -         | 3.2 | 6    | -         | 3.2 | 6    | μs    |

| Hold Step Error                 | V <sub>IN</sub> = 0V | 25    | -         | 10  | 20   | -         | 10  | 20   | mV    |

| Hold Mode Settling Time         | To ±1mV              | 25    | -         | 860 | -    | -         | 860 | -    | ns    |

| Aperture Time (Note 3)          |                      | 25    | -         | 30  | -    | -         | 30  | -    | ns    |

| Effective Aperture Delay Time   |                      | 25    | -         | 30  | -    | -         | 30  | -    | ns    |

| Aperture Uncertainty            |                      | 25    | -         | 5   | -    | -         | 5   | -    | ns    |

| Drift Current (Note 2)          | $V_{IN} = 0V$        | 25    | -         | 5   | -    | -         | 5   | -    | pА    |

| HA1-2420                        |                      | Full  | -         | 1.8 | 10   | -         | -   | -    | nA    |

| HA1-2425                        |                      | Full  | -         | -   | -    | -         | 0.1 | 1.0  | nA    |

| HA3-2425, HA4P2425,<br>HA9P2425 |                      | Full  | -         | -   | -    | -         | 7.5 | 10.0 | nA    |

| POWER SUPPLY CHARACTER          | ISTICS               |       |           |     |      |           |     |      | ·     |

| Supply Current (+)              |                      | 25    | -         | 3.5 | 5.5  | -         | 3.5 | 5.5  | mA    |

| Supply Current (-)              |                      | 25    | -         | 2.5 | 3.5  | -         | 2.5 | 3.5  | mA    |

| Power Supply Rejection          |                      | Full  | 80        | 90  | -    | 74        | 90  | -    | dB    |

Derived from computer simulation only; not tested.

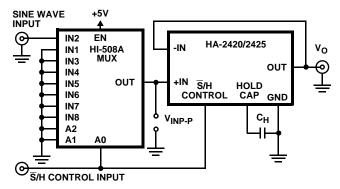

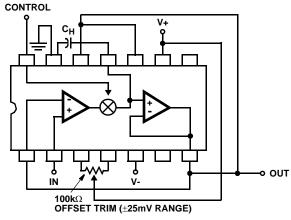

# Functional Diagram

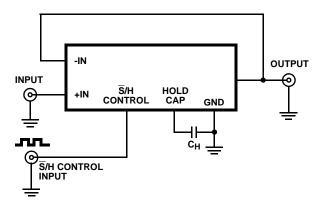

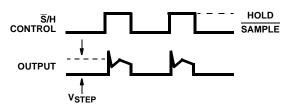

## Test Circuits and Waveforms

FIGURE 1. HOLD STEP ERROR AND DRIFT CURRENT

NOTE: Set rise/fall times of  $\overline{S}/H$  Control to approximately 20ns.

**FIGURE 2. HOLD STEP ERROR TEST**

NOTE: Compute hold mode feedthrough attenuation from the formula:

Feedthrough Attenuation =  $20 \log \frac{V_{OUT}HOLD}{V_{IN}HOLD}$

Where  $V_{OUT}HOLD$  = Peak-to-Peak value of output sinewave during the hold mode.

FIGURE 4. HOLD MODE FEEDTHROUGH ATTENUATION

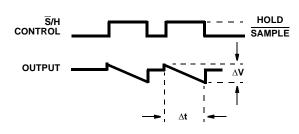

NOTE: Measure the slope of the output during hold,  $\Delta V / \Delta t$ , and compute drift current from:  $I_D = C_H \Delta V / \Delta t$ .

FIGURE 3. DRIFT CURRENT TEST

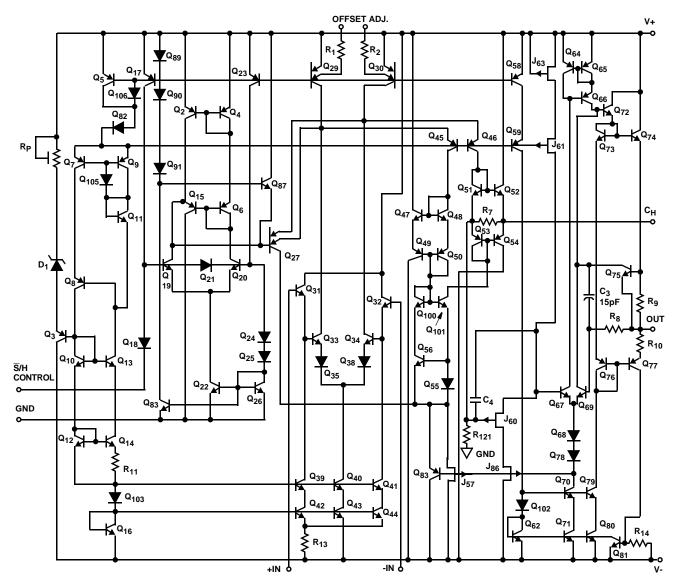

# Schematic Diagram

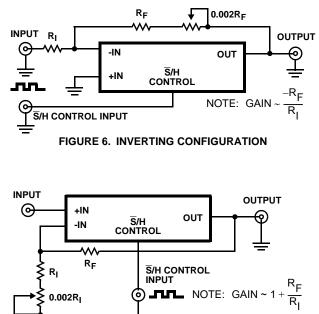

## Application Information

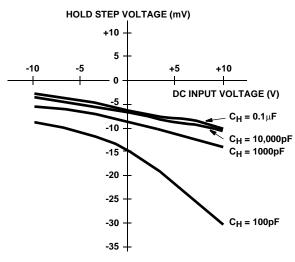

FIGURE 5. HOLD STEP vs INPUT VOLTAGE

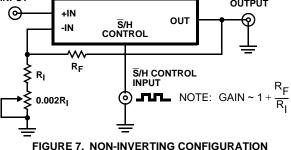

## Offset Adjustment

The offset voltage of the HA-2420 and HA-2425 may be adjusted using a  $100k\Omega$  trim pot, as shown in Figure 8. The recommended adjustment procedure is:

Apply 0V to the sample-and-hold input, and a square wave to the  $\overline{S}/H$  control.

Adjust the trim pot for 0V output in the hold mode.

## Gain Adjustment

The linear variation in pedestal voltage with sample-andhold input voltage causes a -0.06% gain error (C<sub>H</sub> = 1000pF). In some applications (D/A deglitcher, A/D converter) the gain error can be adjusted elsewhere in the system, while in other applications it must be adjusted at the sample-and-hold. The two circuits shown below demonstrate how to adjust gain error at the sample-and-hold.

The recommended procedure for adjusting gain error is:

- 1. Perform offset adjustment.

- 2. Apply the nominal input voltage that should produce a +10V output.

- 3. Adjust the trim pot for +10V output in the hold mode.

- 4. Apply the nominal input voltage that should produce a -10V output.

- 5. Measure the output hold voltage (V-10NOMINAL). Adjust the trim pot for an output hold voltage of

$$\frac{(V_{-10NOMINAL}) + (-10V)}{2}$$

Figure 8 shows a typical unity gain circuit, with Offset Zeroing. All of the other normal op amp feedback configurations may be used with the HA-2420, HA-2425. The input amplifier may be used as a gated amplifier by utilizing Pin 11 as the output. This amplifier has excellent drive capabilities along with exceptionally low switch leakage.

FIGURE 8. BASIC SAMPLE-AND-HOLD (TOP VIEW)

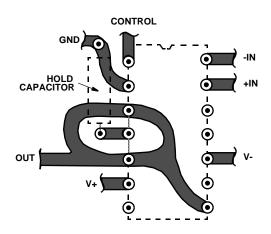

The method used to reduce leakage paths on the PC board and the device package is shown in Figure 9. This guard ring is recommended to minimize the drift during hold mode.

The hold capacitor should have extremely high insulation resistance and low dielectric absorption. Polystyrene (below 85<sup>o</sup>C), Teflon, or Parlene types are recommended.

For more applications, consult Intersil Application Note AN517, or the factory applications group.

FIGURE 9. GUARD RING LAYOUT (BOTTOM VIEW)

# Glossary of Terms

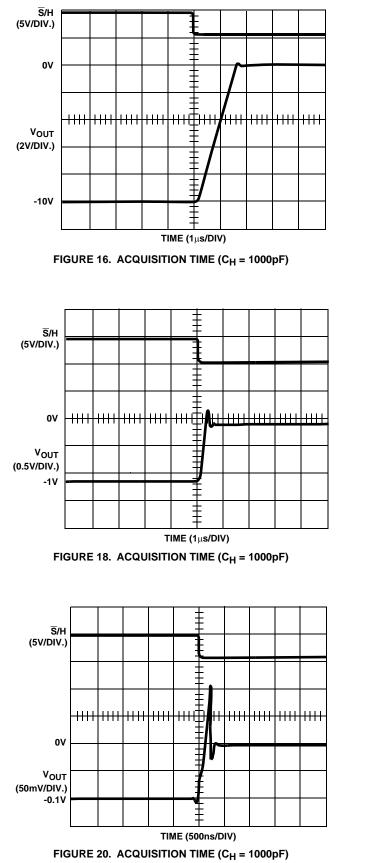

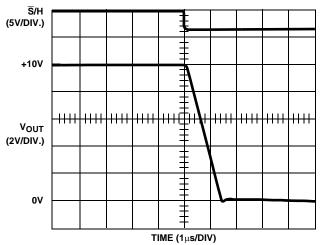

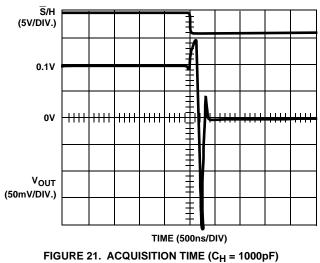

## Acquisition Time

The time required following a "sample" command, for the output to reach its final value within  $\pm 0.1\%$  or  $\pm 0.01\%$ . This is the minimum sample time required to obtain a given accuracy, and includes switch delay time, slewing time and settling time.

## Aperture Time

The time required for the sample-and-hold switch to open, independent of delays through the switch driver and input amplifier circuitry. The switch opening time is that interval between the conditions of 10% open and 90% open.

## Effective Aperture Delay Time (EADT)

The difference between the digital delay time from the Hold command to the opening of the S/H switch, and the propagation time from the analog input to the switch.

EADT may be positive, negative or zero. If zero, the S/H amplifier will output a voltage equal to  $V_{IN}$  at the instant the Hold command was received. For negative EADT, the output in Hold (exclusive of pedestal and droop errors) will correspond to a value of  $V_{IN}$  that occurred before the Hold command.

## Aperture Uncertainty

The range of variation in Effective Aperture Delay Time. Aperture Uncertainty (also called Aperture Delay Uncertainty, Aperture Time Jitter, etc.) sets a limit on the accuracy with which a waveform can be reconstructed from sample data.

## Drift Current

The net leakage current from the hold capacitor during the hold mode. Drift current can be calculated from the droop rate using the formula:

$$I_D (pA) = C_H (pF) \times \frac{\Delta V}{\Delta t} (V/s)$$

## Typical Performance Curves

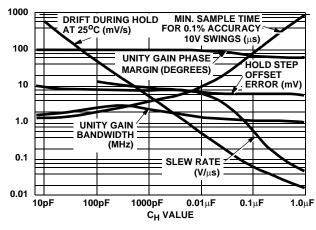

FIGURE 10. TYPICAL SAMPLE AND HOLD PERFORMANCE AS A FUNCTION OF HOLDING CAPACITOR

25

FIGURE 12. DRIFT CURRENT vs TEMPERATURE

0

50

TEMPERATURE (°C)

75

1000

100

10

1

-50

-25

(bd) dI

125

100

8

## Typical Performance Curves (Continued)

FIGURE 17. ACQUISITION TIME (C<sub>H</sub> = 1000pF)

## **Die Characteristics**

#### DIE DIMENSIONS:

102 mils x 61 mils x 19 mils 2590µm x 1550µm x 483µm

#### **METALLIZATION:**

Type: Al, 1% Cu Thickness: 16kÅ ±2kÅ

## SUBSTRATE POTENTIAL:

V-

## BACKSIDE FINISH:

Gold, Nickel, Silicon, etc.

## Metallization Mask Layout

#### **PASSIVATION:**

Type: Nitride (Si<sub>3</sub>N<sub>4</sub>) over Silox (SiO<sub>2</sub>, 5% Phos.) Silox Thickness:  $12k\dot{A} \pm 2k\dot{A}$ Nitride Thickness:  $3.5k\dot{A} \pm 1.5k\dot{A}$

## TRANSISTOR COUNT:

78

#### PROCESS:

**Bipolar Dielectric Isolation**

<text>

HA-2420, HA-2425

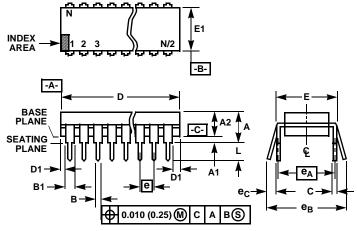

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 -1.14mm).

#### E14.3 (JEDEC MS-001-AA ISSUE D) 14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIM   |          |       |

|----------------|-------|-------|----------|----------|-------|

| SYMBOL         | MIN   | MAX   | MIN MAX  |          | NOTES |

| А              | -     | 0.210 | -        | 5.33     | 4     |

| A1             | 0.015 | -     | 0.39     | -        | 4     |

| A2             | 0.115 | 0.195 | 2.93     | 4.95     | -     |

| В              | 0.014 | 0.022 | 0.356    | 0.558    | -     |

| B1             | 0.045 | 0.070 | 1.15     | 1.77     | 8     |

| С              | 0.008 | 0.014 | 0.204    | 0.355    | -     |

| D              | 0.735 | 0.775 | 18.66    | 19.68    | 5     |

| D1             | 0.005 | -     | 0.13     | -        | 5     |

| E              | 0.300 | 0.325 | 7.62     | 8.25     | 6     |

| E1             | 0.240 | 0.280 | 6.10     | 7.11     | 5     |

| е              | 0.100 | BSC   | 2.54     | 2.54 BSC |       |

| e <sub>A</sub> | 0.300 | BSC   | 7.62 BSC |          | 6     |

| е <sub>В</sub> | -     | 0.430 | -        | 10.92    | 7     |

| L              | 0.115 | 0.150 | 2.93     | 3.81     | 4     |

| Ν              | 1     | 4     | 1        | 4        | 9     |

Rev. 0 12/93

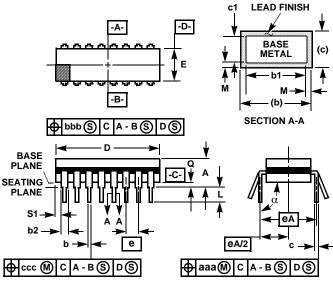

## Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

NOTES:

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- 2. The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 3. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

#### **F14.3** MIL-STD-1835 GDIP1-T14 (D-1, CONFIGURATION A) 14 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INC             | HES              | MILLIN          |                  |       |

|--------|-----------------|------------------|-----------------|------------------|-------|

| SYMBOL | MIN             | MAX              | MIN MAX         |                  | NOTES |

| А      | -               | 0.200            | -               | 5.08             | -     |

| b      | 0.014           | 0.026            | 0.36            | 0.66             | 2     |

| b1     | 0.014           | 0.023            | 0.36            | 0.58             | 3     |

| b2     | 0.045           | 0.065            | 1.14            | 1.65             | -     |

| b3     | 0.023           | 0.045            | 0.58            | 1.14             | 4     |

| С      | 0.008           | 0.018            | 0.20            | 0.46             | 2     |

| c1     | 0.008           | 0.015            | 0.20            | 0.38             | 3     |

| D      | -               | 0.785            | -               | 19.94            | 5     |

| Е      | 0.220           | 0.310            | 5.59            | 7.87             | 5     |

| е      | 0.100           | BSC              | 2.54 BSC        |                  | -     |

| eA     | 0.300           | BSC              | 7.62 BSC        |                  | -     |

| eA/2   | 0.150           | BSC              | 3.81            | BSC              | -     |

| L      | 0.125           | 0.200            | 3.18            | 5.08             | -     |

| Q      | 0.015           | 0.060            | 0.38            | 1.52             | 6     |

| S1     | 0.005           | -                | 0.13            | -                | 7     |

| α      | 90 <sup>0</sup> | 105 <sup>0</sup> | 90 <sup>0</sup> | 105 <sup>0</sup> | -     |

| aaa    | -               | 0.015            | -               | 0.38             | -     |

| bbb    | -               | 0.030            | -               | 0.76             | -     |

| ССС    | -               | 0.010            | -               | 0.25             | -     |

| М      | -               | 0.0015           | -               | 0.038            | 2, 3  |

| Ν      | 1               | 4                | 1               | 8                |       |

Rev. 0 4/94

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com