Sample &

Buy

LM10692 SNVSA53 – JULY 2014

# LM10692 Power Management Unit for SandForce SF3700 SSD Controllers

Technical

Documents

### 1 Features

- Six High-efficiency Programmable Buck Regulators:

- Integrated FETs with Low RDSon

- Bucks Operate Phase Shifted to Reduce the Input

- Current ripple And Capacitor Size

- Output Voltage Programmable via Serial interface

- Under and Over Voltage Lock-out

- Automatic Internal Soft Start

- Output Current Overload and Thermal Shutdown Protection

- Active Discharge for Fast Discharge of Output Voltage When Buck is Disabled

- I2C Compatible Serial Interface, up to 1 MHz

- Power-On-Reset Output with Delay and Input Voltage Trigger

- Independent Enable Input Pins and Power Good output Pins for Control of Always-On (AON) and Core Power (CPE) Rails

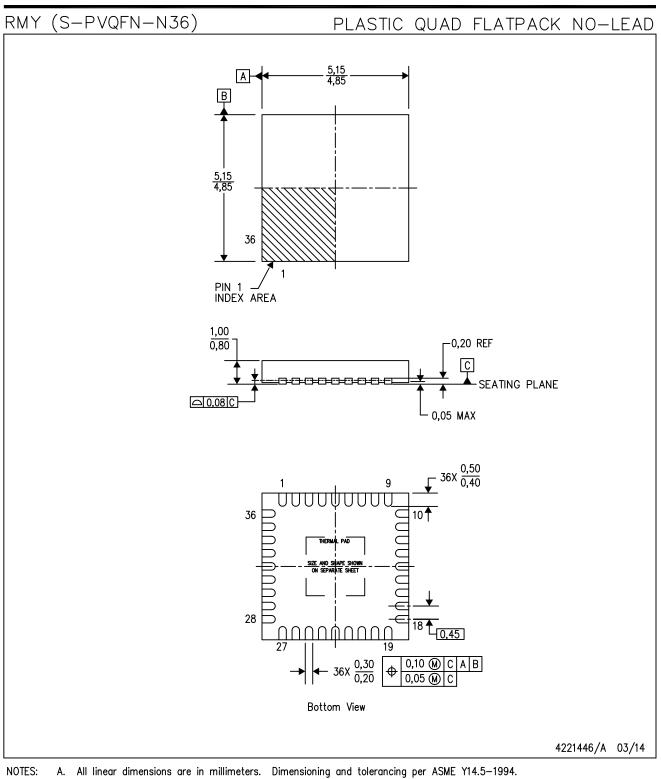

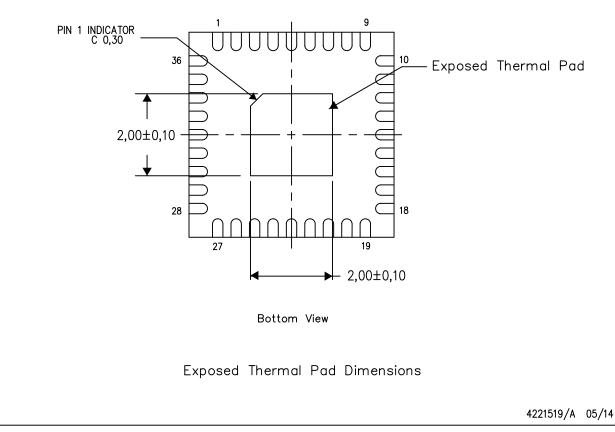

- RMY Package Size 5.00 mm x 5.00 mm x 0.9 mm (NOM)

- Key Specifications

- Single Input Rail with Wide Range: 2.5 V to 4.0 V

- Programmable Output Voltage:

- Buck1: 1.75 V to 3.3 V, 2.5 A

- Buck2: 1.0 V to 2.55 V, 200 mA

- Buck3: 0.8 V to 2.35 V, 200 mA

- Buck4: 0.8 V to 2.35 V, 2.5 A

- Buck5: 0.8 V to 1.575 V, 0.8 A

- Buck6: 0.8 V to 1.575 V, 2.5 A

- Buck1 Configurable as Bypass Switch (No Inductor)

- ±1% Feedback Voltage Accuracy

- Up to 95% Peak efficiency Buck Regulators

2 MHz Switching Frequency For Smaller Inductor Size

Support &

Community

20

### 2 Applications

Tools &

Software

- Optimized for Use in SSDs

- Embedded Systems: SoCs, ASICs, and Processors

### **3** Description

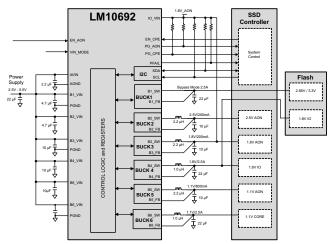

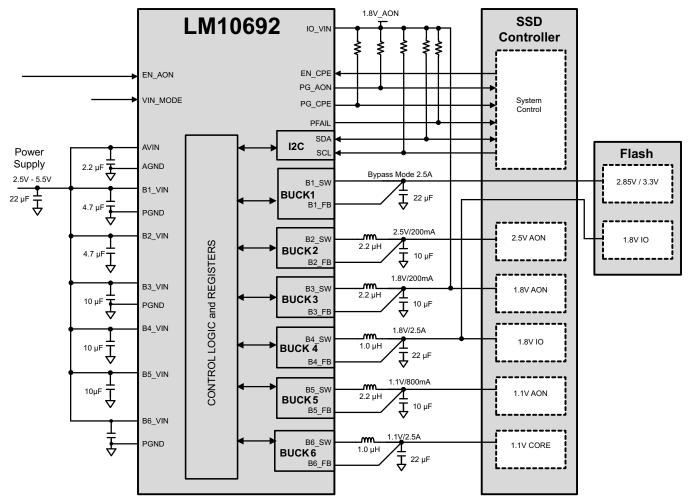

The LM10692 is an advanced PMU containing six configurable, buck regulators for supplying power to advanced Flash Controllers in solid-state drives (SSDs). The device is ideal for use in solid state drive designs. The LM10692 communicates with the SF3700 Flash Controller via an I2C compatible interface and digital I/O pins to optimize power consumption with power saving modes.

#### **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |  |  |  |

|-------------|----------|-------------------|--|--|--|--|

| LM10692     | QFN (36) | 5.00 mm × 5.00 mm |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

### **Typical Application**

TEXAS INSTRUMENTS

www.ti.com

# **Table of Contents**

| 1 | Features                                  | 1        |

|---|-------------------------------------------|----------|

| 2 | Applications                              | 1        |

| 3 | Description                               | 1        |

| 4 | Revision History                          | 2        |

| 5 | Device Comparison Table                   | 3        |

| 6 | Pin Configuration and Functions           | 4        |

| 7 | Specifications                            | 6        |

|   | 7.1 Absolute Maximum Ratings              | 6        |

|   | 7.2 Handling Ratings                      | 6        |

|   | 7.3 Recommended Operating Conditions      | 6        |

|   | 7.4 Thermal Information                   | 6        |

|   | 7.5 Electrical Characteristics            | 7        |

|   | 7.6 Buck 1 Electrical Characteristic      |          |

|   | 7.7 Buck 2 Electrical Characteristic      | 9        |

|   | 7.8 Buck 3 Electrical Characteristics     | 10       |

|   | 7.9 Buck 4 Electrical Characteristic      | 11       |

|   | 7.10 Buck 5 Electrical Characteristic     | 12       |

|   | 7.11 Buck 6 Electrical Characteristic     | 13       |

|   | 7.12 Typical Characteristics, Efficiency  | 14       |

|   | 7.13 Typical Characteristics, Load Regula | ation 15 |

|   | 7.14 Typical Characteristics, Load Transi | ients 16 |

|   |                                           |          |

| 8  | Deta | illed Description                 | . 18 |

|----|------|-----------------------------------|------|

|    | 8.1  | Overview                          | 18   |

|    | 8.2  | Functional Block Diagram          | 18   |

|    | 8.3  | Feature Description               | 19   |

|    | 8.4  | Device Functional Modes           | 25   |

|    | 8.5  | Programming                       |      |

|    | 8.6  | Register Maps                     | 29   |

| 9  | Арр  | lication and Implementation       | . 35 |

|    | 9.1  | Application Information           | 35   |

|    | 9.2  | Typical Application               | 35   |

| 10 | Pow  | ver Supply Recommendations        | . 38 |

|    | 10.1 | Supply Overview                   | 38   |

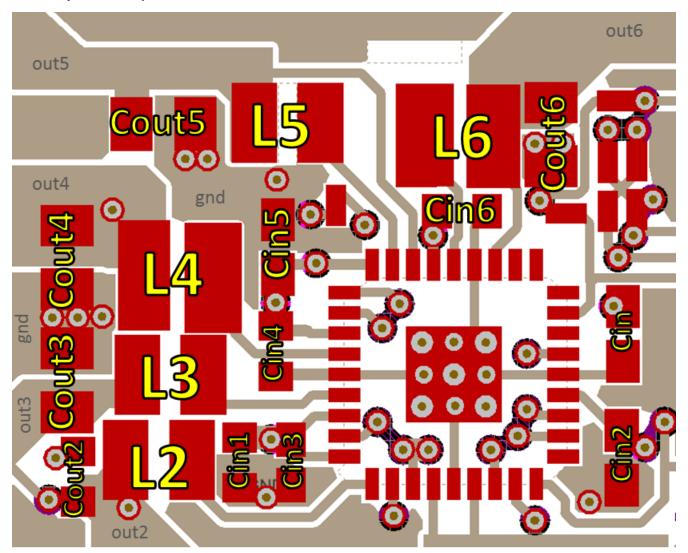

| 11 | Lay  | out                               | . 39 |

|    |      | Layout Guidelines                 |      |

|    | 11.2 | Layout Example                    | 40   |

| 12 |      | ice and Documentation Support     |      |

|    | 12.1 | Trademarks                        | 41   |

|    | 12.2 | Electrostatic Discharge Caution   | 41   |

|    |      | Glossary                          |      |

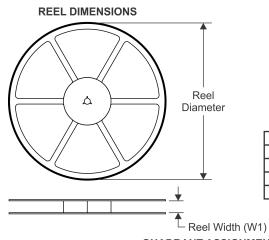

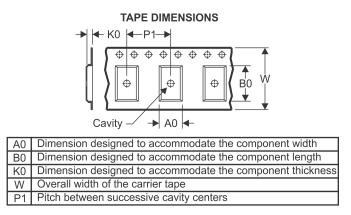

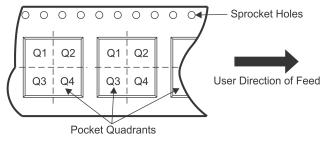

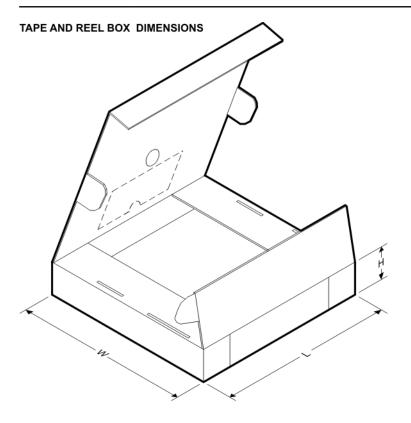

| 13 | Mec  | hanical, Packaging, and Orderable |      |

|    |      | rmation                           | . 41 |

|    |      |                                   |      |

# 4 Revision History

| DATE      | REVISION | NOTES            |

|-----------|----------|------------------|

| June 2014 | *        | Initial release. |

# 5 Device Comparison Table

|       | Variants         |            |  |  |  |

|-------|------------------|------------|--|--|--|

|       | 1.1V PCIe / SATA | 1.15V PCle |  |  |  |

|       | LM10692          | LM10692B   |  |  |  |

| Buck1 | 2.85V            | 2.85V      |  |  |  |

| Buck2 | 2.5V             | 2.5V       |  |  |  |

| Buck3 | 1.8V             | 1.8V       |  |  |  |

| Buck4 | 1.8V             | 1.8V       |  |  |  |

| Buck5 | 1.1V             | 1.15V      |  |  |  |

| Buck6 | 1.1V             | 1.15V      |  |  |  |

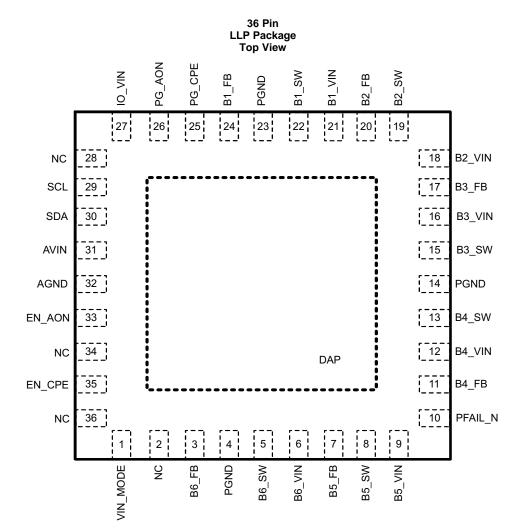

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN    |          | I/O | TYPE | DESCRIPTION                                                                      |  |  |

|--------|----------|-----|------|----------------------------------------------------------------------------------|--|--|

| NUMBER | NAME     | 1/0 | (1)  | DESCRIPTION                                                                      |  |  |

| 1      | VIN_MODE | I   | D    | Leave floating for the LM10692. Input pin defines Buck1 mode operation.          |  |  |

| 2      | NC       | -   | -    | Leave Floating                                                                   |  |  |

| 3      | B6_FB    | I   | А    | Buck Switcher Regulator 6 – Voltage output feedback for Buck Regulator 6         |  |  |

| 4      | PGND     | G   | Р    | ver ground for Buck Regulator –Return Input and Output Cap to this pin           |  |  |

| 5      | B6_SW    | 0   | Р    | ck Switcher Regulator 6 – Power Switching node, connect to inductor              |  |  |

| 6      | B6_VIN   | I   | Р    | ck Switcher Regulator 6 – Power supply voltage input for power stage PFET.       |  |  |

| 7      | B5_FB    | I   | А    | ck Switcher Regulator 5 – Voltage output feedback for Buck Regulator 5           |  |  |

| 8      | B5_SW    | 0   | Р    | Buck Switcher Regulator 5 – Power Switching node, connect to inductor            |  |  |

| 9      | B5_VIN   | I   | Р    | Buck Switcher Regulator 5-Power supply voltage input for power stage PFET.       |  |  |

| 10     | PFAIL_N  | 0   | D    | Provides reset function to controller. Monitors VIN. Digital Output. Open Drain. |  |  |

| 11     | B4_FB    | I   | А    | Buck Switcher Regulator 4 – Voltage output feedback for Buck Regulator 4         |  |  |

| 12     | B4_VIN   | I   | Р    | Buck Switcher Regulator 4 – Power supply voltage input for power stage PFET.     |  |  |

| 13     | B4_SW    | 0   | Р    | Buck Switcher Regulator 4 – Power Switching node, connect to inductor            |  |  |

| 14     | PGND     | G   | Р    | Power ground for Buck Regulator – Return Input and Output Cap to this pin        |  |  |

(1) A: Analog Pin; D: Digital Pin; G: Ground Pin; P: Power Pin; I: Input Pin; O: Output Pin

## Pin Functions (continued)

| Р      | IN     |     |     |                                                                                 |

|--------|--------|-----|-----|---------------------------------------------------------------------------------|

| NUMBER | NAME   | I/O | (1) | DESCRIPTION                                                                     |

| 15     | B3_SW  | 0   | Р   | Buck Switcher Regulator 3 – Power Switching node, connect to inductor           |

| 16     | B3_VIN | I   | Р   | Buck Switcher Regulator 3 – Power supply voltage input for power stage PFET     |

| 17     | B3_FB  | I   | А   | Buck Switcher Regulator 3 – Voltage output feedback for Buck Regulator 3        |

| 18     | B2_VIN | I   | Р   | Buck Switcher Regulator 2 – Power supply voltage input for power stage PFET     |

| 19     | B2_SW  | 0   | Р   | Buck Switcher Regulator 2 – Power Switching node, connect to inductor           |

| 20     | B2_FB  | I   | А   | Buck Switcher Regulator 2 – Voltage output feedback for Buck Regulator 2        |

| 21     | B1_VIN | I   | Р   | Buck Switcher Regulator 1 – Power supply voltage input for power stage PFET     |

| 22     | B1_SW  | 0   | Р   | Buck Switcher Regulator 1 – Power Switching node, connect to inductor           |

| 23     | PGND   | G   | Р   | Power ground for Buck Regulator – Return Input and Output Cap to this pin       |

| 24     | B1_FB  | Ι   | А   | Buck Switcher Regulator 1 – Voltage output feedback for Buck Regulator 1        |

| 25     | PG_CPE | 0   | D   | Power good output for core power rails - Buck 1, Buck 4, and Buck 6, open drain |

| 26     | PG_AON | 0   | D   | Power good pin for always on rails – Buck 2, Buck 3, and Buck 5, open drain     |

| 27     | IO_VIN | I   | Р   | Reference supply for digital interface to controller.                           |

| 28     | NC     | -   | -   | Leave Floating                                                                  |

| 29     | SCL    | I   | D   | Digital interface for I2C Clock signal. Open Drain.                             |

| 30     | SDA    | 10  | D   | Digital interface for I2C Data signal. Open Drain.                              |

| 31     | AVIN   | I   | Р   | Power Supply input Voltage. Must be present for device to work.                 |

| 32     | AGND   | G   | Р   | Power Supply Ground. Must be grounded for device to work.                       |

| 33     | EN_AON | I   | D   | Enable pin for always on rails – Buck 2, Buck 3, and Buck 5                     |

| 34     | NC     | -   | -   | Leave Floating                                                                  |

| 35     | EN_CPE | I   | D   | Enable for core power rails – Buck 1, Buck 4, and Buck 6                        |

| 36     | NC     | -   | -   | Leave Floating                                                                  |

| DAP    | PGND   | -   | -   | Thermally bonded. Needs low-impedance thermal connection to PCB                 |

### 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)(2)(3)(4)</sup>

over operating free-air temperature range (unless otherwise noted) <sup>(5)</sup>

|                            | MIN  | MAX                              | UNIT |

|----------------------------|------|----------------------------------|------|

| Any supply pin, VIN to GND | -0.3 | 6                                | V    |

| Any signal pin             | -0.3 | +(VIN+0.3)V but<br>not over 6.0V | V    |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are measured with respect to the potential at the GND pins.

(3) VIN refers to these power pins connected together: VIN\_B1 = VIN\_B2=VI\_B3 = VIN\_B4 = VIN\_B5 = VIN\_B6 = VIN

(4) GND Pins means all ground pins must be connected together.

(5) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 Handling Ratings

|                                |                                                                                          |     | MIN  | MAX | UNIT |

|--------------------------------|------------------------------------------------------------------------------------------|-----|------|-----|------|

| T <sub>stg</sub>               | Storage temperature rang                                                                 | -65 | 150  | °C  |      |

| V(rep) Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              |     | 2000 | V   |      |

|                                | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |     | 1000 | V   |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions<sup>(1)(2)(3)(4)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                      | MIN | MAX | UNIT |

|--------------------------------------|-----|-----|------|

| VIN, VIN_B2, VIN_B3, VIN_B4, VIN_B5  | 2.5 | 5.5 | V    |

| VIN_B1, VIN_B6                       | 2.5 | 4   | V    |

| Junction Temperature, T <sub>J</sub> | -40 | 125 | °C   |

| Ambient Temperature, T <sub>A</sub>  | -40 | 85  | °C   |

| Storage Temperature                  | -65 | 150 | °C   |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are measured with respect to the potential at the GND pins.

(3) VIN refers to these power pins connected together: VIN\_B1 = VIN\_B2=VI\_B3 = VIN\_B4 = VIN\_B5 = VIN\_B6 = VIN

(4) GND Pins means all ground pins must be connected together.

### 7.4 Thermal Information

|                       |                                              | LM10692 |      |

|-----------------------|----------------------------------------------|---------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RMY     | UNIT |

|                       |                                              | 36 PINS |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 39.2    |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 9.8     |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.2     | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.1     | C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 6.2     |      |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.6     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## over operating free-air temperature range (unless otherwise noted)

Unless otherwise noted, VIN = 3.3V, where: VIN =VIN B1=VIN B2= VIN B3=VIN B4=VIN B5= VIN B6.

|                             |                                                                                                           |                                                                       | –40°C ≤ 1 | $\Gamma_A \leq T_J \leq -$ | +85°C           | 1        | Γ <sub>A</sub> = 25°C |             |      |

|-----------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------|----------------------------|-----------------|----------|-----------------------|-------------|------|

|                             | PARAMETER                                                                                                 | TEST CONDITIONS                                                       | MIN       | <b>TYP</b><br>(3)          | МАХ             | MIN      | TYP <sup>(3)</sup>    | МАХ         | UNIT |

| I <sub>Q_OFF</sub>          | Quiescent supply current.                                                                                 | All Bucks OFF                                                         |           |                            |                 |          | 8                     |             | μA   |

| I <sub>Q_AON</sub>          | Quiescent supply current                                                                                  | All Bucks unloaded,<br>EN_CPE low                                     |           |                            |                 |          | 250                   |             | μA   |

| Ι <sub>Q</sub>              | Quiescent supply current.                                                                                 | All Bucks unloaded and<br>in PFM mode                                 |           |                            |                 |          | 320                   |             | μA   |

| I <sub>Q_ALLON</sub>        | Quiescent supply current                                                                                  | All Bucks unloaded,<br>Buck6 in FPWM mode<br>(default operating mode) |           |                            |                 |          | 6                     |             | mA   |

| UNDER/OVER                  | VOLTAGE LOCK OUT                                                                                          |                                                                       |           |                            |                 |          |                       |             |      |

| V <sub>UVLO_RISING</sub>    |                                                                                                           | Factory pre-set                                                       |           |                            | 2.50            |          | 2.4                   |             | V    |

| V <sub>UVLO_FALLING</sub>   |                                                                                                           | Factory pre-set                                                       |           |                            | 2.40            |          | 2.3                   |             | V    |

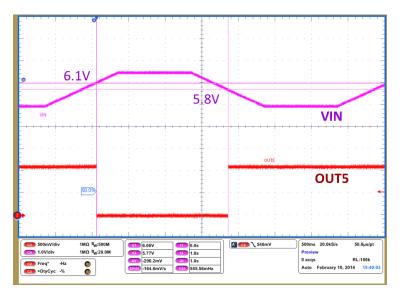

| V <sub>OVLO_RISING</sub>    |                                                                                                           | Factory pre-set                                                       |           |                            |                 |          | 6.1                   | 6.25        | V    |

| V <sub>OVLO_FALLING</sub>   |                                                                                                           | Factory pre-set                                                       |           |                            |                 |          | 5.8                   |             | V    |

| THERMAL SH                  | UTDOWN                                                                                                    |                                                                       | *         |                            |                 |          |                       |             |      |

| T <sub>SD</sub>             | Thermal Shutdown<br>Temperature                                                                           |                                                                       | 145       |                            | 160             |          |                       |             | °C   |

| DIGITAL INTER               | RFACE                                                                                                     |                                                                       |           |                            |                 |          |                       |             |      |

| V <sub>IL-IO</sub>          | Logic Input Low                                                                                           | SDA, SCL                                                              |           |                            | 0.4             |          |                       |             | V    |

| V <sub>IH-IO</sub>          | Logic Input High                                                                                          | SDA, SCL                                                              | 1.05      |                            |                 |          |                       |             | V    |

| V <sub>OL-IO</sub>          | Logic Output Low                                                                                          | SDA                                                                   |           |                            | 0.4             |          |                       |             | V    |

| V <sub>DDIO</sub> Range     | External Logic pullup voltage for IO_VIN                                                                  |                                                                       | 1.2       |                            | V <sub>IN</sub> |          |                       |             | V    |

| IIL                         | Input Current, pin driven<br>low                                                                          |                                                                       |           |                            |                 | -2<br>-5 |                       |             | μA   |

| I <sub>IH</sub>             | Input Current, pin driven high                                                                            | VIN_MODE                                                              |           |                            |                 |          |                       | 2           | μA   |

| f <sub>I2C_MAX</sub>        | I <sup>2</sup> C max frequency                                                                            | IO_VIN = 1.8 V Max<br>frequency is application<br>specific            |           |                            |                 |          |                       | 1000        | kHz  |

| V <sub>IL-VIN_MODE</sub>    | VIN_MODE input low                                                                                        | (See <sup>(3)</sup> )                                                 |           |                            |                 |          |                       | GND<br>+0.3 | V    |

| V <sub>IH-VIN_MODE</sub>    | VIN_MODE input high                                                                                       | (See <sup>(3)</sup> )                                                 |           |                            |                 | VIN-0.3  |                       |             | V    |

|                             | HOLD and BYPASS THRES                                                                                     | HOLD                                                                  |           |                            |                 |          |                       |             |      |

| V <sub>PFAIL</sub> -falling | PFAIL_N falling threshold voltage                                                                         | VIN_MODE = GND or<br>FLOATING                                         |           |                            |                 | 2.3      | 2.6                   | 3.3         | V    |

| V <sub>PFAIL</sub> -rising  | PFAIL_N rising threshold voltage                                                                          | VIN_MODE = GND or<br>FLOATING                                         |           |                            |                 | 2.3      | 2.7                   | 3.3         | V    |

| T <sub>PFAIL</sub>          | PFAIL_N rise delay time                                                                                   | Active High <sup>(3)</sup> , default<br>trim                          |           |                            |                 |          | 4                     |             | ms   |

| V <sub>BYPASS</sub>         | Bypass Mode threshold (transitions from PWM to Bypass mode when input voltage falls below $V_{BYPASS}$ ). | VIN_MODE = GND                                                        |           |                            |                 |          | 2.9                   |             | V    |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(3) Specification ensured by design. Not tested during production.

TEXAS INSTRUMENTS

www.ti.com

### 7.6 Buck 1 Electrical Characteristic<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

Unless otherwise noted, VIN = 3.3V, where: VIN =VIN\_B1=VIN\_B2, VIN\_B3=VIN\_B4=VIN\_B5= VIN\_B6.

The application circuit used is the one shown in "Typical Application Circuit"

|                        | DADAMETED                               | TEST CONDITIONS                                                                                                                | T <sub>A</sub> = 25°C |                    |      | LINUT |

|------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|-------|

|                        | PARAMETER                               | TEST CONDITIONS                                                                                                                | MIN                   | TYP <sup>(3)</sup> | MAX  | UNIT  |

| V <sub>OUT</sub>       | Output Voltage default value            |                                                                                                                                | 2.76                  | 2.85               | 2.93 | V     |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current         | Buck 1 enabled, (see <sup>(3)</sup> )                                                                                          |                       | 2.5                |      | А     |

| I <sub>PEAK</sub>      | Peak switching current limit            | Buck 1 enabled                                                                                                                 |                       | 4.2                |      | А     |

| η <sub>SW1-5V</sub>    | Efficiency, Buck 1 <sup>(3)</sup>       | $I_{OUT} = 5$ mA to 1A, $V_{IN} = 3.3$ V                                                                                       | 80%                   |                    | 95%  |       |

| F <sub>SW</sub>        | Switching Frequency                     | PWM operation                                                                                                                  |                       | 2                  |      | MHz   |

| C <sub>IN</sub>        | Input Capacitor <sup>(3)</sup>          |                                                                                                                                |                       | 22                 |      | μF    |

| 0                      | Output Filter Capacitor <sup>(3)</sup>  |                                                                                                                                |                       | 22                 |      | μF    |

| C <sub>OUT</sub>       | Output Capacitor ESR <sup>(3)</sup>     | $- 0 \text{ mA} \le I_{\text{OUT}} \le I_{\text{OUT-MAX}}$                                                                     |                       | 10                 |      | mΩ    |

| L                      | Output Filter Inductance <sup>(3)</sup> |                                                                                                                                |                       | 1                  |      | μH    |

| V <sub>FB1</sub>       | Feedback Voltage                        | V <sub>OUT</sub> = 2.85 V (default),<br>PWM Mode, No Load (%)                                                                  |                       | 2.85               |      | V     |

|                        | DC Line regulation <sup>(3)</sup>       | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5\text{V},$<br>$I_{\text{OUT}} = I_{\text{OUT-MAX}}$                               | -1%                   |                    | 1%   |       |

| ΔV <sub>OUT</sub>      | DC Load regulation <sup>(3)</sup>       | Vin = 3.3 V ,<br>$0.1 \times I_{OUT-MAX} \le I_{OUT-MAX}$                                                                      | -1%                   |                    | 1%   |       |

| I <sub>FB</sub>        | Feedback pin input bias current         | V <sub>FB</sub> = 2.85 V                                                                                                       |                       |                    | 7    | μA    |

| R <sub>DS-ON-HS</sub>  | High Side Switch On Resistance          | Measured pin-to-pin, Vin = 3.3 V                                                                                               |                       | 80                 |      | mΩ    |

| R <sub>DS-ON-LS</sub>  | Low Side Switch On Resistance           |                                                                                                                                |                       | 115                |      | mΩ    |

| R <sub>DISCHARGE</sub> | Active Discharge Resistance             | Measured from FB to GND                                                                                                        |                       | 20                 |      | Ω     |

|                        | Internal soft-start (turn on time)      | Start up from shutdown, $V_{OUT} = 0 V$ ,<br>no load, $V_{OUT} = 95\%$ of 3.3 V in<br>bypass mode <sup>(3)</sup> , Cout = 22µF |                       | 470                |      | μs    |

| T <sub>start</sub>     |                                         | Start up from shutdown, $V_{OUT} = 0 V$ ,<br>no load, VOUT = 95% of 3.3 V in<br>bypass mode <sup>(3)</sup> , Cout = 66µF       |                       | 530                |      | μs    |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(3) Specification ensured by design. Not tested during production.

#### Buck 2 Electrical Characteristic<sup>(1)(2)</sup> 7.7

over operating free-air temperature range (unless otherwise noted) Unless otherwise noted, VIN = 3.3V, where: VIN =VIN B1=VIN B2, VIN B3=VIN B4=VIN B5= VIN B6. The application circuit used is the one shown in "Typical Application Circuit"

|                        |                                         |                                                                                                  | T <sub>A</sub> = 25°C |                    |      |      |

|------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|------|

|                        | PARAMETER                               | CONDITIONS                                                                                       | MIN                   | TYP <sup>(3)</sup> | MAX  | UNIT |

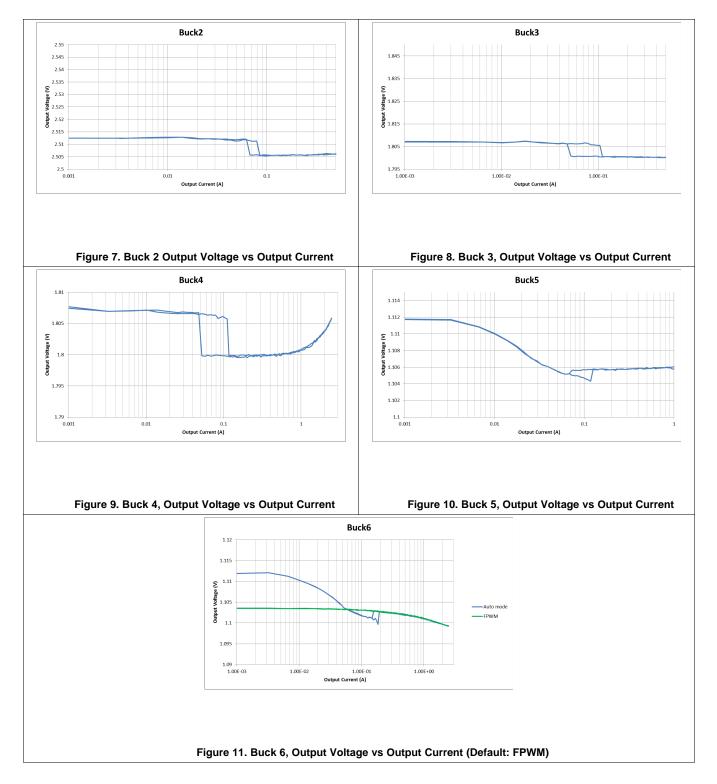

| V <sub>OUT</sub>       | Output Voltage default value            |                                                                                                  | 2.42                  | 2.5                | 2.57 | V    |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current         | Buck 2 enabled <sup>(3)</sup>                                                                    |                       | 0.2                |      | А    |

| I <sub>PEAK</sub>      | Peak switching current limit            | Buck 2 enabled                                                                                   |                       | 1.9                |      | А    |

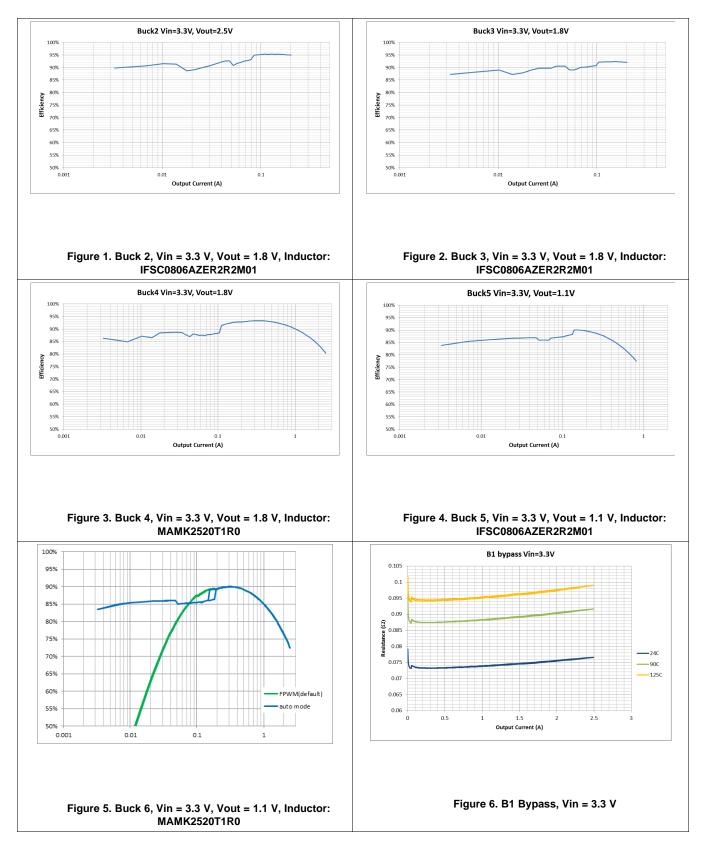

| η <sub>SW2-5V</sub>    | Efficiency, Buck 2 <sup>(3)</sup>       | $I_{OUT}$ = 100 $\mu A$ to 0.2 A, $V_{OUT}$ = 2.5 V, L= 2.2 $\mu H,$ ESRL = 220 m $\Omega$       | 80%                   |                    | 90%  |      |

| F <sub>SW</sub>        | Switching Frequency                     | PWM operation                                                                                    |                       | 2                  |      | MHz  |

| C <sub>IN</sub>        | Input Capacitor <sup>(3)</sup>          |                                                                                                  |                       | 4.7                |      | μF   |

| C <sub>OUT</sub>       | Output Filter Capacitor <sup>(3)</sup>  |                                                                                                  |                       | 10                 |      | μF   |

|                        | Output Capacitor ESR <sup>(3)</sup>     | − 0 mA ≤ $I_{OUT}$ ≤ $I_{OUT-MAX}$                                                               |                       | 10                 |      | mΩ   |

| L                      | Output Filter Inductance <sup>(3)</sup> |                                                                                                  |                       | 2.2                |      | μH   |

| V <sub>FB2</sub>       | Feedback Voltage                        | V <sub>OUT</sub> = 2.5 V (default),<br>PWM Mode, No Load                                         |                       | 2.5                |      | V    |

| ΔV <sub>OUT</sub>      | DC Line regulation <sup>(3)</sup>       | 2.9 V ≤ VIN ≤5.0V,<br>I <sub>OUT</sub> = I <sub>OUT-MAX</sub>                                    | -1%                   |                    | 1%   |      |

|                        | DC Load regulation <sup>(3)</sup>       | Vin = 3.3,<br>$0.1 \times I_{OUT-MAX} \le I_{out} \le I_{OUT-MAX}$                               | -1%                   |                    | 1%   |      |

| I <sub>FB</sub>        | Feedback pin input bias current         | V <sub>FB</sub> = 2.5 V                                                                          |                       |                    | 5    | μA   |

| R <sub>DS-ON-HS</sub>  | High Side Switch On Resistance          | Measured pin-to-pin, Vin = 3.3 V                                                                 |                       | 135                |      | mΩ   |

| R <sub>DS-ON-LS</sub>  | Low Side Switch On Resistance           |                                                                                                  |                       | 105                |      | mΩ   |

| R <sub>DISCHARGE</sub> | Active Discharge Resistance             | Measured from FB to GND                                                                          |                       | 18                 |      | Ω    |

| T <sub>start</sub>     | Internal soft-start (turn on time)      | Start up from shutdown, $V_{OUT}$ = 0 V, no load, VOUT = 95% of 2.5 V <sup>(3)</sup> , Cout=22µF |                       | 275                |      | μs   |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics. Specification ensured by design. Not tested during production. (2)

(3)

STRUMENTS www<u>.ti.com</u>

XAS

### 7.8 Buck 3 Electrical Characteristics<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

Unless otherwise noted, VIN = 3.3V, where: VIN =VIN B1=VIN B2, VIN B3=VIN B4=VIN B5= VIN B6.

The application circuit used is the one shown in "Typical Application Circuit".

|                        | DADAMETER                               | TEST CONDITIONS                                                                                                                | T <sub>A</sub> = 25°C |                    |      |      |

|------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|------|

|                        | PARAMETER                               | TEST CONDITIONS                                                                                                                | MIN                   | TYP <sup>(3)</sup> | MAX  | UNIT |

| V <sub>OUT</sub>       | Output Voltage default value            |                                                                                                                                | 1.75                  | 1.8                | 1.85 | V    |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current         | Buck 3 enabled, <sup>(3)</sup>                                                                                                 |                       | 0.2                |      | А    |

| I <sub>PEAK</sub>      | Peak switching current limit            | Buck 3 enabled                                                                                                                 |                       | 0.8                |      | А    |

| ηSW3-5V                | Efficiency, Buck 3 <sup>(3)</sup>       | $I_{OUT}$ = 5mA to 0.2 A, 1.8 $V_{out},$ L = 2.2 $\mu H,$ ESRL = 200 m $\Omega$                                                | 80%                   |                    | 90%  |      |

| F <sub>SW</sub>        | Switching Frequency                     | PWM operation                                                                                                                  |                       | 2                  |      | MHz  |

| C <sub>IN</sub>        | Input Capacitor <sup>(3)</sup>          |                                                                                                                                |                       | 4.7                |      | μF   |

| 2                      | Output Filter Capacitor <sup>(3)</sup>  |                                                                                                                                |                       | 10                 |      | μF   |

| C <sub>OUT</sub>       | Output Capacitor ESR <sup>(3)</sup>     | $0 \text{ mA} \le I_{OUT} \le I_{OUT-MAX}$                                                                                     |                       | 10                 |      | mΩ   |

| L                      | Output Filter Inductance <sup>(3)</sup> |                                                                                                                                |                       | 2.2                |      | μH   |

| VFB3                   | Feedback Voltage                        | V <sub>OUT</sub> = 1.8 V (default),<br>PWM Mode, No Load                                                                       |                       | 1.8                |      | V    |

|                        | DC Line regulation <sup>(3)</sup>       | $2.9V \le VIN \le 5.0 V$ ,<br>$I_{OUT} = I_{OUT-MAX}$                                                                          | -1%                   |                    | +1%  |      |

| ΔV <sub>OUT</sub>      | DC Load regulation <sup>(3)</sup>       | Vin = 3.3 V,<br>0.1 × $I_{OUT-MAX} \le I_{OUT-MAX}$                                                                            | -1%                   |                    | +1%  |      |

| I <sub>FB</sub>        | Feedback pin input bias current         | V <sub>FB</sub> = 1.8 V                                                                                                        |                       |                    | 3.5  | μA   |

| R <sub>DS-ON-HS</sub>  | High Side Switch On Resistance          | Measured pin-to-pin, Vin = 3.3 V                                                                                               |                       | 220                |      | mΩ   |

| R <sub>DS-ON-LS</sub>  | Low Side Switch On Resistance           |                                                                                                                                |                       | 105                |      | mΩ   |

| R <sub>DISCHARGE</sub> | Active Discharge Resistance             | Measured from FB to GND                                                                                                        |                       | 18                 |      | Ω    |

| T <sub>start</sub>     | Internal soft-start (turn on time)      | Start up from shutdown, $V_{OUT} = 0 V$ ,<br>no load, $V_{OUT} = 95\%$ of 1.8 V <sup>(3)</sup> , $C_{out} = 190$<br>22 $\mu$ F |                       |                    | μs   |      |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics. Specification ensured by design. Not tested during production. (2)

(3)

### 7.9 Buck 4 Electrical Characteristic<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted) Unless otherwise noted, VIN = 3.3V, where: VIN =VIN\_B1=VIN\_B2, VIN\_B3=VIN\_B4=VIN\_B5= VIN\_B6. The application circuit used is the one shown in "Typical Application Circuit".

|                        | DADAMETED                               | TEST CONDITIONS                                                                                  | T <sub>A</sub> = 25°C |                    |      |      |

|------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|------|

|                        | PARAMETER                               | TEST CONDITIONS                                                                                  | MIN                   | TYP <sup>(3)</sup> | MAX  | UNIT |

| V <sub>OUT</sub>       | Output Voltage default value            |                                                                                                  | 1.75                  | 1.8                | 1.85 | V    |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current         | Buck 4 enabled, <sup>(4)</sup>                                                                   |                       | 2.5                |      | А    |

| I <sub>PEAK</sub>      | Peak switching current limit            | Buck 4 enabled                                                                                   |                       | 3.6                |      | А    |

| ηSW4-5V                | Efficiency, Buck 4 <sup>(4)</sup>       | $I_{OUT}$ = 5mA to 1A, $V_{OUT}$ = 1.8 V, L = 1 $\mu H,$ ESRL = 50 m $\Omega$                    | 80%                   |                    | 90%  |      |

| F <sub>SW</sub>        | Switching Frequency                     | PWM operation                                                                                    |                       | 2                  |      | MHz  |

| C <sub>IN</sub>        | Input Capacitor <sup>(4)</sup>          | $0 \text{ mA} \le I_{\text{OUT}} \le I_{\text{OUT-MAX}}$                                         |                       | 22                 |      | μF   |

| C <sub>OUT</sub>       | Output Filter Capacitor <sup>(4)</sup>  |                                                                                                  |                       | 22                 |      | μF   |

|                        | Output Capacitor ESR <sup>(4)</sup>     |                                                                                                  |                       | 10                 |      | mΩ   |

| L                      | Output Filter Inductance <sup>(4)</sup> |                                                                                                  |                       | 1                  |      | μH   |

| V <sub>FB4</sub>       | Feedback Voltage                        | V <sub>OUT</sub> = 1.8V (default),<br>PWM Mode, No Load                                          |                       | 1.8                |      | V    |

| $\Delta_{\text{VOUT}}$ | DC Line regulation <sup>(4)</sup>       | $2.9 \le \text{VIN} \le 5.0 \text{ V},$<br>$I_{\text{OUT}} = I_{\text{OUT-MAX}}$                 | -1%                   |                    | +1%  |      |

|                        | DC Load regulation <sup>(4)</sup>       | Vin = 3.3 V,<br>0.1 × $I_{OUT-MAX} \le I_{out} \le I_{OUT-MAX}$                                  | -1%                   |                    | +1%  |      |

| I <sub>FB</sub>        | Feedback pin input bias current         | V <sub>FB</sub> = 1.8 V                                                                          |                       |                    | 3.5  | μA   |

| R <sub>DS-ON-HS</sub>  | High Side Switch On Resistance          | Measured pin-to-pin, Vin = 3.3 V                                                                 |                       | 85                 |      | mΩ   |

| R <sub>DS-ON-LS</sub>  | Low Side Switch On Resistance           |                                                                                                  |                       | 60                 |      | mΩ   |

| R <sub>DISCHARGE</sub> | Active Discharge Resistance             | Measured from FB to GND                                                                          |                       | 18                 |      | Ω    |

| T <sub>start</sub>     | Internal soft-start (turn on time)      | Start up from shutdown, $V_{OUT}$ = 0 V, no load, $V_{OUT}$ = 95% of 1.8 V, $^{(4)}$ Cout = 22µF |                       | 165                |      | μs   |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(3) Specification ensured by design. Not tested during production.

(4) Specification ensured by design. Not tested during production.

### 7.10 Buck 5 Electrical Characteristic<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted) Unless otherwise noted, VIN = 3.3V, where: VIN =VIN\_B1=VIN\_B2, VIN\_B3=VIN\_B4=VIN\_B5= VIN\_B6. The application circuit used is the one shown in "Typical Application Circuit".

|                        |                                         | TEAT CONDITIONS                                                                                                        | T <sub>A</sub> = 25°C |                    |      |      |

|------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|------|

|                        | PARAMETER                               | TEST CONDITIONS                                                                                                        | MIN                   | TYP <sup>(3)</sup> | MAX  | UNIT |

| V <sub>OUT</sub>       | Output Voltage default value            |                                                                                                                        | 1.07                  | 1.1                | 1.13 | V    |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current         | Buck 5 enabled, <sup>(4)</sup>                                                                                         |                       | 0.8                |      | А    |

| I <sub>PEAK</sub>      | Peak switching current limit            | Buck 5 enabled                                                                                                         |                       | 2                  |      | А    |

| ηSW5-5V                | Efficiency, Buck 5 <sup>(4)</sup>       | $I_{OUT}$ = 5mA to 600 mA, $V_{OUT}$ = 1.1V,<br>L = 2.2 µH, ESRL = 200 mΩ                                              | 80%                   |                    | 90%  |      |

| F <sub>SW</sub>        | Switching Frequency                     | PWM operation                                                                                                          |                       | 2                  |      | MHz  |

| C <sub>IN</sub>        | Input Capacitor <sup>(4)</sup>          |                                                                                                                        |                       | 4.7                |      | μF   |

| C <sub>OUT</sub>       | Output Filter Capacitor <sup>(4)</sup>  |                                                                                                                        |                       | 10                 |      | μF   |

|                        | Output Capacitor ESR <sup>(4)</sup>     | $= 0 \text{ mA} \le I_{\text{OUT}} \le I_{\text{OUT-MAX}}$                                                             |                       | 10                 |      | mΩ   |

| L                      | Output Filter Inductance <sup>(4)</sup> |                                                                                                                        |                       | 2.2                |      | uH   |

| VFB5                   | Feedback Voltage                        | V <sub>OUT</sub> = 1.1V (default),<br>PWM Mode, No Load                                                                |                       | 1.1                |      | V    |

| $\Delta_{\text{VOUT}}$ | DC Line regulation <sup>(4)</sup>       | $2.9 \text{ V} \le \text{VIN} \le 5 \text{ V},$<br>$I_{\text{OUT}} = I_{\text{OUT-MAX}}$                               | -1%                   |                    | +1%  |      |

|                        | DC Load regulation <sup>(4)</sup>       | Vin = 3.3 V ,<br>0.1 × $I_{OUT-MAX} \le I_{out} \le I_{OUT-MAX}$                                                       | -1%                   |                    | +1%  |      |

| I <sub>FB</sub>        | Feedback pin input bias current         | V <sub>FB</sub> =1.1V                                                                                                  |                       |                    | 2.5  | μA   |

| R <sub>DS-ON-HS</sub>  | High Side Switch On Resistance          | Measured pin-to-pin, Vin = 3.3 V                                                                                       |                       | 120                |      | mΩ   |

| R <sub>DS-ON-LS</sub>  | Low Side Switch On Resistance           |                                                                                                                        |                       | 85                 |      | mΩ   |

| R <sub>DISCHARGE</sub> | Active Discharge Resistance             | Measured from FB to GND 18                                                                                             |                       |                    | Ω    |      |

| T <sub>start</sub>     | Internal soft-start (turn on time)      | Start up from shutdown, $V_{OUT} = 0 V$ , no<br>load, $V_{OUT} = 95\%$ of 1.05 V <sup>(4)</sup> , Cout = 22<br>$\mu$ F |                       |                    | μs   |      |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(3) Specification ensured by design. Not tested during production.

(4) Specification ensured by design. Not tested during production.

### 7.11 Buck 6 Electrical Characteristic<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted) Unless otherwise noted, VIN = 3.3V, where: VIN =VIN\_B1=VIN\_B2, VIN\_B3=VIN\_B4=VIN\_B5= VIN\_B6. The application circuit used is the one shown in "Typical Application Circuit".

|                        | DADAMETED                               | TEST CONDITIONS                                                                                                           | T <sub>A</sub> = 25°C |                    |      |      |

|------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|------|

|                        | PARAMETER                               | TEST CONDITIONS                                                                                                           | MIN                   | TYP <sup>(3)</sup> | MAX  | UNIT |

| V <sub>OUT</sub>       | Output Voltage default value            |                                                                                                                           | 1.07                  | 1.1                | 1.07 | V    |

| l <sub>Q</sub>         | DC Bias Current in Vin                  | No Load, PFM Mode                                                                                                         |                       |                    |      | mA   |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current         | Buck 6 enabled, <sup>(3)</sup>                                                                                            |                       | 2.5                |      | А    |

| I <sub>PEAK</sub>      | Peak switching current limit            | Buck 6 enabled                                                                                                            |                       | 4.1                |      | А    |

| $\eta_{SW6\text{-}5V}$ | Efficiency, Buck 6 <sup>(3)</sup>       | $I_{OUT}$ = 100 mA $-$ 1 A , $V_{OUT}$ = 1.1 V, L = 1 $\mu H,$ ESRL = 50 m $\Omega$                                       | 80%                   |                    | 90%  |      |

| F <sub>SW</sub>        | Switching Frequency                     | PWM operation                                                                                                             |                       | 2                  |      | MHz  |

| C <sub>IN</sub>        | Input Capacitor <sup>(3)</sup>          |                                                                                                                           |                       | 22                 |      | μF   |

| C <sub>OUT</sub>       | Output Filter Capacitor <sup>(3)</sup>  |                                                                                                                           |                       | 22                 |      | μF   |

|                        | Output Capacitor ESR <sup>(3)</sup>     | $- 0 \text{ mA} \le I_{\text{OUT}} \le I_{\text{OUT-MAX}}$                                                                |                       | 10                 |      | mΩ   |

| L                      | Output Filter Inductance <sup>(3)</sup> |                                                                                                                           |                       | 1                  |      | μH   |

| V <sub>FB6</sub>       | Feedback Voltage Accuracy               | V <sub>OUT</sub> = 1.05 V (default),<br>PWM Mode, No Load (%)                                                             |                       | 1.1                |      | V    |

| $\Delta V_{OUT}$       | DC Line regulation <sup>(3)</sup>       | $2.9V \le V_{IN} \le 4.0 V$ ,<br>$I_{OUT} = I_{OUT-MAX}$                                                                  | -1%                   |                    | 1%   |      |

|                        | DC Load regulation <sup>(3)</sup>       | V in = 3.3V,<br>0.1 × $I_{OUT-MAX} \le I_{out} \le I_{OUT-MAX}$                                                           | -1%                   |                    | 1%   |      |

| I <sub>FB</sub>        | Feedback pin input bias current         | V <sub>FB</sub> =1.1V                                                                                                     |                       |                    | 2.5  | μA   |

| R <sub>DS-ON-HS</sub>  | High Side Switch On Resistance          | Vin = 3.3 V                                                                                                               |                       | 70                 |      | mΩ   |

| R <sub>DS-ON-LS</sub>  | Low Side Switch On Resistance           |                                                                                                                           |                       | 65                 |      | mΩ   |

| R <sub>DISCHARGE</sub> | Active Discharge Resistance             | Measured from FB to GND                                                                                                   |                       | 18                 |      | Ω    |

| T <sub>start</sub>     | Internal soft-start (turn on time)      | Start up from shutdown, V <sub>OUT</sub> = 0 V, no load, V <sub>OUT</sub> = 95% of 1.1 V <sup>(3)</sup> , Cout=22 $\mu$ F |                       | 145                |      | μs   |

(1) All limits are guaranteed by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with TA = 25M C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(3) Specification ensured by design. Not tested during production.

### 7.12 Typical Characteristics, Efficiency

## 7.13 Typical Characteristics, Load Regulation

TEXAS INSTRUMENTS

www.ti.com

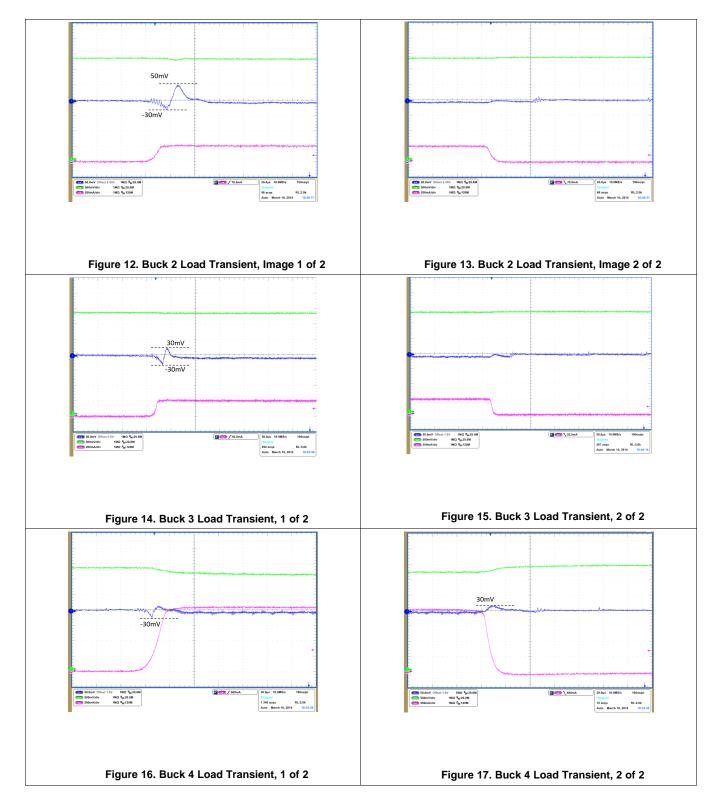

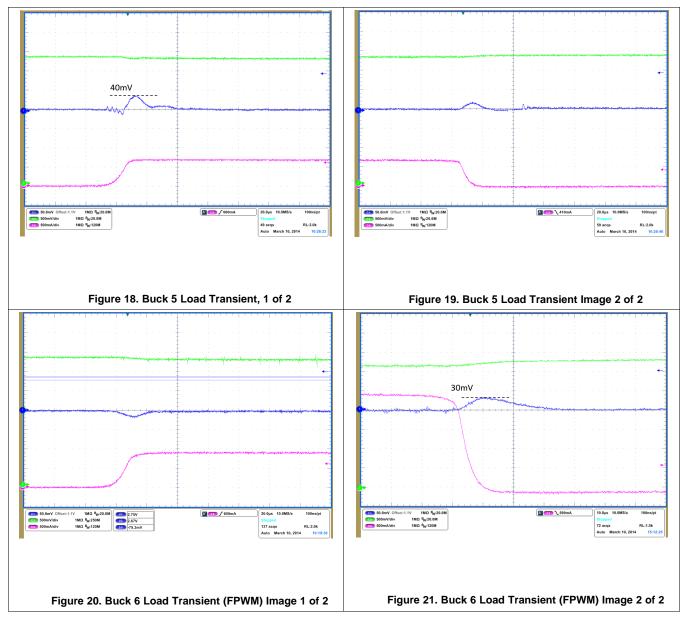

## 7.14 Typical Characteristics, Load Transients

### **Typical Characteristics, Load Transients (continued)**

### 8 Detailed Description

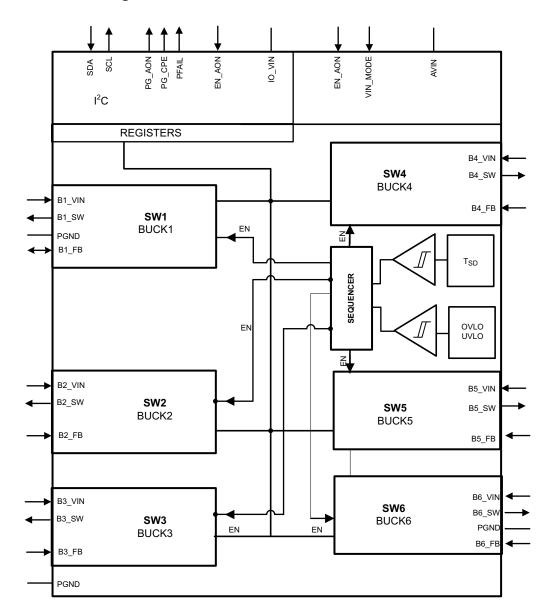

#### 8.1 Overview

LM10692 is a highly efficient and integrated Power Management Unit for Systems-on-a-Chip (SoCs), ASICs, and processors. It operates cooperatively and communicates with ASICs over an I2C compatible serial interface with programmable Regulator Vout, Dynamic Voltage Scaling (DVS), and individual Output Enable/Disable.

The device incorporates six high-efficiency synchronous buck regulators that deliver six output voltages from a single power source.

#### 8.2 Functional Block Diagram

### 8.3 Feature Description

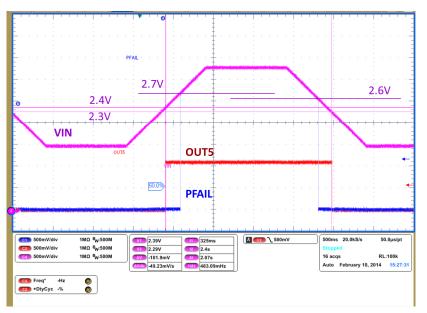

### 8.3.1 UVLO, PFAIL and OVLO

The IC has a default UVLO setting of 2.4V with a hysteresis of 100mV (2.3V when VIN is falling). When VIN rises above this threshold, start-up sequence is initialized and begins 3ms after. PFAIL\_N output comes up when VIN rises above 2.7V. There is a delay of 4ms between the time VIN rises above the PFAIL threshold and the PFAIL\_N output goes high. There is no delay when VIN falls below the PFAIL threshold.

When VIN rises over the OVLO threshold, the outputs are disabled. PFAIL\_N output will not come down during an OVLO event. The outputs are re-enabled in sequence when VIN falls below the OVLO threshold.

The PFAIL\_N output needs an IO\_VIN voltage of more than 1.0V to be operational. The value of the output is invalid for IO\_VIN voltages below 1.0V.

Figure 22. UVLO and PFAIL Thresholds. VIN is Slewed at 1V/s

Figure 23. OVLO Thresholds. VIN is Slewed at 1.5V/s

(1)

(2)

### Feature Description (continued)

#### 8.3.2 OCP

When one channel reaches the Over Current Protection threshold, the current will be limited and the output voltage will collapse as a result. The situation remains until the over current event is cleared and the system can resume regulation. The IC will not reset due to an OCP event and the other channels will remain operational. One exception is in the case of OCP on Buck6 or Buck1. Since Buck1 is enabled only when Buck6 is in a Power Good state (output voltage within 90% of set value) and Buck4 is enabled only when Buck1 is in a Power Good state as well, Buck1 and Buck4 will shut-down during OCP events on Buck6. Likewise, Buck4 will shut-down during OCP events on Buck1.

Buck1 OCP is not operational when Buck1 is used as a bypass switch.

Values given in the EC table refer to peak inductor current, not average output current. The average output current threshold will be lower due to the ripple in the inductor current.

The ripple can be estimated with the following formula:

$$\Delta I_{L} = \frac{V_{OUT} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{L \times 2 \times 10^{6}}$$

where

•  $\Delta I_{L}$  is the inductor ripple

L is the inductance

The threshold for the output current will then be:

$I_{OUT MAX} = I_{PEAK} - 0.5 \times \Delta I_{L}$

#### 8.3.3 **PFAIL\_N** Operation and Output Thresholds

PFAIL\_N is a digital output with open drain. It can be pulled-up up to Vin. When the input voltage drops below the threshold, PFAIL\_N turns low within 20us. When the Vin rises above the threshold. PFAIL\_N turns high after a delay that is programmable in EPROM (Default is 4ms). By default there is a 100mV hysteresis between the Vin threshold falling and the Vin threshold rising.

The PFAIL\_N output needs an IO\_VIN voltage of more than 1.0V to be operational. The value of the output is invalid for IO\_VIN voltages below 1.0V.

The PFAIL function is operational 2ms after power-up.

The rising and falling thresholds for the PFAIL\_N output comparator are independently programmable. This enables the setting of the hysteresis to any desired value within 50mV steps.

| Table 1. Reg | ister Settinas for H | HOSTMONITOR / | <b>PFAIL Rising and</b> | Falling Thresholds |

|--------------|----------------------|---------------|-------------------------|--------------------|

| Tuble II Keg | lotor oottingo ior i |               |                         |                    |

| 5  | •                            | 5 5           |

|----|------------------------------|---------------|

| Ν  | PFAILN UP_ PFAILN_DN SETTING | THRESHOLD (V) |

| 0  | 0                            | 3.2           |

| 1  | 1                            | 3.15          |

| 2  | 10                           | 3.1           |

| 3  | 11                           | 3.05          |

| 4  | 100                          | 3             |

| 5  | 101                          | 2.95          |

| 6  | 110                          | 2.9           |

| 7  | 111                          | 2.85          |

| 8  | 1000                         | 2.8           |

| 9  | 1001                         | 2.75          |

| 10 | 1010                         | 2.7           |

| 11 | 1011                         | 2.65          |

| 12 | 1100                         | 2.6           |

#### Feature Description (continued)

| N  | PFAILN UP_ PFAILN_DN SETTING | THRESHOLD (V) |

|----|------------------------------|---------------|

| 13 | 1101                         | 2.55          |

| 14 | 1110                         | 2.5           |

| 15 | 1111                         | 2.45          |

| 16 | 10000                        | 2.4           |

| 17 | 10001                        | 2.35          |

| 18 | 10010                        | 2.3           |

| 19 | 10011                        | 2.3           |

| 20 | 10100                        | 2.3           |

#### Table 1. Register Settings for HOSTMONITOR / PFAIL Rising and Falling Thresholds (continued)

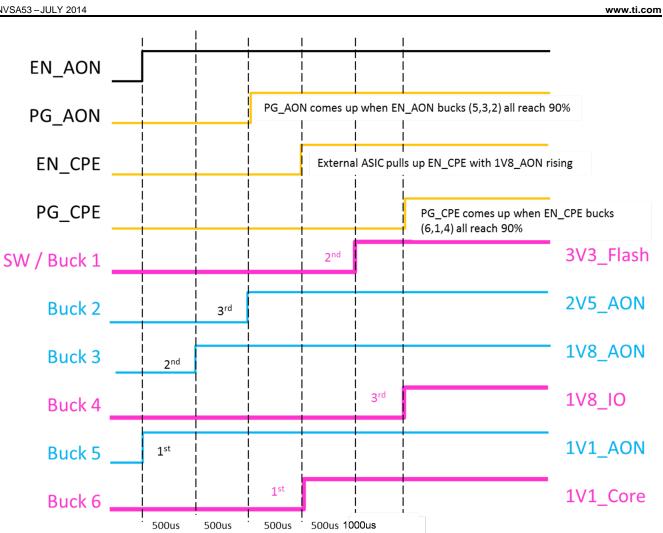

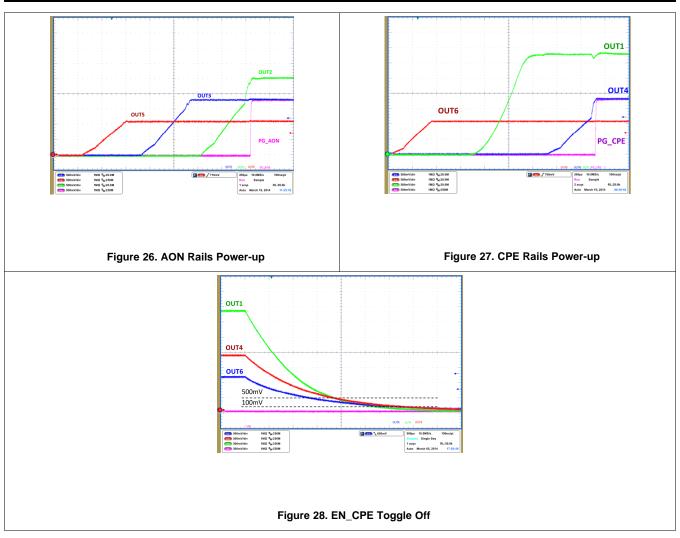

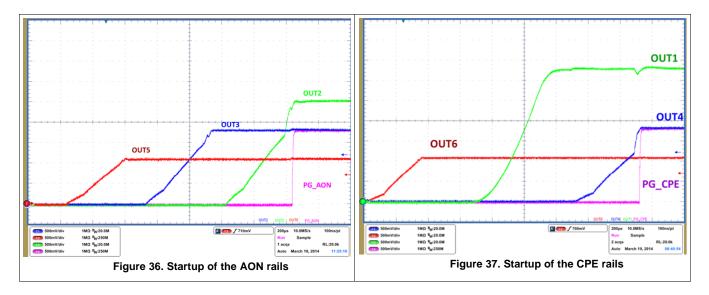

### 8.3.4 Power-Up Sequencing and EN\_AON and EN\_CPE

The EN\_AON pin controls the sequenced startup of Always-On rails Buck 5, Buck 3, and Buck 2, each separated by 0.5ms. The EN\_CPE pin controls the sequenced startup of core power rails Buck 6, Buck 1, and Buck 4. There is no logical dependency between EN\_CPE and EN\_AON, and it is expected that any required dependency (for example, EN\_CPE must be low when EN\_AON is low) between these signals will be enforced externally. Different startup sequences and timing are possible via factory trim. However, there is a fixed dependency for the CPE rails (Buck1, Buck4, Buck6): Buck6 must be up and running for Buck1 to start-up. Likewise, Buck1 needs to be up and running (in bypass mode or in buck mode) for Buck4 to start-up.

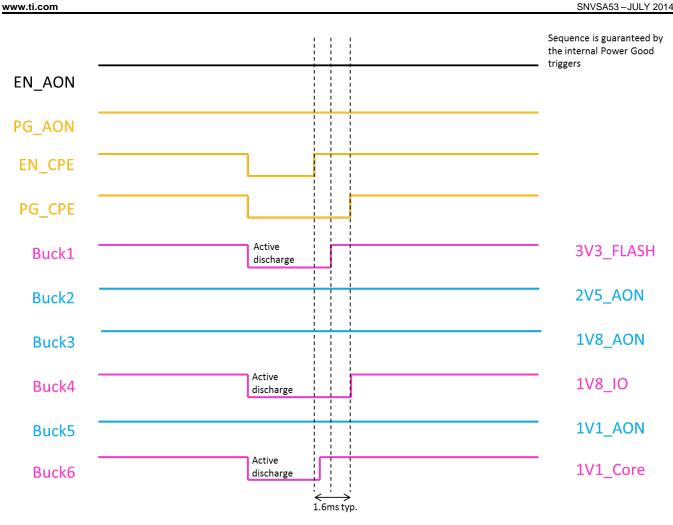

During the initial Power-up sequence, the controller checks all the internal Power Good flags. If all the PG flags (Buck1-Buck6) are not high 8ms after the last programmed buck has begun soft-start, the IC will power-down and wait 200ms before restarting. This means that EN\_CPE must be high during the power-up sequence. Once all the PGs have been asserted, EN\_CPE can be toggled low at will.

The startup timing of the rails controlled by EN\_CPE is different depending on whether EN\_CPE goes high during the initial startup sequence upon power-up, or during wake-up from a sleep mode. In the case where EN\_CPE goes high during the initial startup, the startup of Buck 6, Buck1, and Buck4 are delayed by 500us (or longer depending on the soft-start time of each buck). In the case where it is waking up from a sleep mode, the startups are only delayed by the PGOOD of the previous rail, so the timing is dependent on the soft-start time of the rails which may be 100us to 1000us.

EN\_AON controls Buck5, Buck3 and Buck2. When EN\_AON is toggled high, Buck5, Buck3 and Buck2 will power-up in sequence (5->3->2). When EN\_AON is toggled low, all six rails (Buck1-Buck6) will power-down at the same time regardless of the state of the EN\_CPE pin.

When EN\_AON is toggled back high, EN\_CPE needs to be set high too for the system to re-start properly as in the power-up sequence.

EN\_CPE controls Buck6,Buck1 and Buck4. When EN\_CPE is toggled high, Buck6, Buck1 and Buck4 will powerup in sequence (6->1->4). When EN\_CPE is toggled low, all three rails will shut-down at the same time.

Voltage at IO\_VIN pin is not necessary for the AON rails to power-up. However IO\_VIN needs to be supplied with a proper voltage for the CPE rails to power-up.

Each channel has an active discharge circuitry which will discharge the output into an  $18-20\Omega$  internal resistance when the channel is turned-off in order to quickly lower the output voltage as needed by the SSD circuits before being able to power up again. This will enable the user to toggle EN\_CPE off and back on within a few milliseconds. The discharge time of the output rails is dependent on the output capacitance used.

LM10692 SNVSA53 – JULY 2014

Figure 24. Power-up Sequence with EN\_AON and EN\_CPE, where EN\_CPE is Tied to 1V8\_AON.

Figure 25. Wake-up Sequence from EN\_CPE

TEXAS INSTRUMENTS

www.ti.com

When the output current is low, each converter operates in PFM with a hysteretic pattern to limit the amount of switching event to a minimum and keep the current consumption lower. Buck1 and Buck6 are programmed to operate in PWM mode all the time.

This mode can be overridden by the user with specific I2C commands (Specification ensured by design. Not tested during production). However, the default programmed mode will be reloaded upon reset.

### 8.4 Device Functional Modes

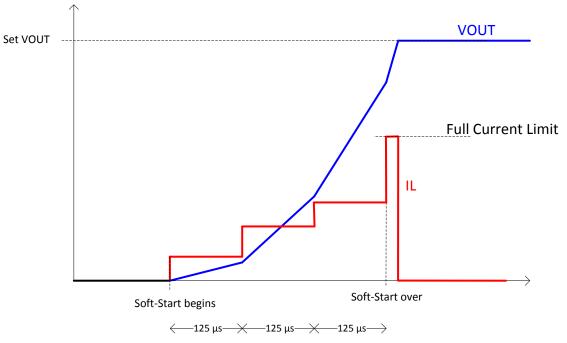

#### 8.4.1 Soft Start

#### 8.4.1.1 Buck Mode

During power-up or when EN\_AON or EN\_CPE is toggled high, the bucks will turn on following a three steps soft-start pattern. Each step lasts 125us and consist of a constant average inductor current. The output voltage rise in a set of ramps as the output capacitor is being charged. If the set output voltage is reached prior to all the steps being completed, the soft-start period will be over. After the 375us soft-start period has elapsed, the full current (limited by the OCP setting for that buck converter) is allowed into the inductor regardless of the state of the output voltage.

Figure 29. Typical Soft-Start Pattern

It is preferable to ensure that the output voltage will be reached before the Soft-Start period is over. If not, in-rush current spike might be observed on the input. That spike depends on input capacitor, output capacitor and output voltage but is typically 1A to 2A in magnitude.

For higher output capacitances, the output voltage will rise more slowly. Also, for higher output voltage settings, the desired output voltage will be reached less quickly. Hence depending on the output voltage, the output capacitance might have to be limited if in-rush current is a concern.

#### 8.4.1.2 Bypass Mode

If Buck1 is programmed as a bypass mode, the gate of the internal High Side switch will be gradually increased to ensure a soft-start pattern. After the HS switch has fully turned ON, the internal PG signal will come up and the additional bypass switch between the input and the FB1 pin will turn-ON to help reduce the resistance and voltage drop across the switch.

Copyright © 2014, Texas Instruments Incorporated

LM10692 SNVSA53 – JULY 2014

#### **Device Functional Modes (continued)**

#### 8.4.2 VIN\_MODE and Buck1 Bypass Operation

The VIN\_MODE input pin defines the behavior of Buck1 and the thresholds for the PFAIL comparator.

The VIN\_MODE pin function is sensed only when the converter powers-up.

#### Table 2. VIN\_MODE and Buck1 Bypass Operation

| VIN_MODE                                            | BUCK1 BEHAVIOR                                                                                                                                                    |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN_MODE floating                                   | Buck1 will always be in bypass mode when it is enabled. OUT1 is<br>not regulated. In this mode, it operates as a load switch and does<br>not require an inductor. |

| VIN_MODE tied to GND not recommended if Vout>0.8Vin | Buck1 regulates OUT1 to the VREF1 target. If VIN drops below a threshold, Buck1 will automatically enter bypass mode.                                             |

The state of this pin is defined at startup of PMIC and changes in state afterwards are ignored.

The LM10692 is mainly designed to interact with the SF3700 controller. For this purpose, it should operate with VIN\_MODE pin floating and Buck1 operating as a switch, with FB connected directly to the B1\_SW pin for reduced ON resistance.

Buck1 has a bypass FET integrated in the IC that connects B1\_VIN directly to B1\_FB. When VIN\_MODE is floating, Buck1 will always be in bypass mode when it is enabled, and OUT1 is not regulated. In this mode, Buck1 operates as a load switch with the bypass FET (on the FB node) and high-side PFET (on the buck switch node) both carrying current, and Buck1 does not require an inductor.

When the VIN\_MODE pin is set to GND, Buck1 will regulate the output to the reference set by the Buck1 voltage code.

If the input voltage drops and the output cannot be regulated anymore, the output will then switch into bypass mode and keep both the high-side PFET and bypass FET ON to minimize the resistance and reduce the drop on the output voltage. The bypass FET provides a low resistance path around the inductor, and will carry the majority of the current.

Since there may be potentially high currents being passed through the B1\_FB pin, the traces for this particular feedback path should be made thicker than for a conventional feedback pin.

When operating with VIN = 3.3V, it is recommended that VIN\_MODE be left floating and that Buck1 be operated as a load switch. This shrinks the solution size and cost by enabling the user to remove the inductor for this output. If VIN\_MODE is tied GND, care must be taken to ensure that the required output voltage (typically 2.85V for a Flash rail) can be met for the specified worst case VIN, which can be as low as 2.97V (-10% of 3.3V). Transient performance specs are also difficult to meet at these operating points due to the very high duty cycle operation. In order to meet performance specifications at worst case temperatures and max currents, a larger inductor with lower DC resistance (DCR) may be needed.

#### 8.5 **Programming**

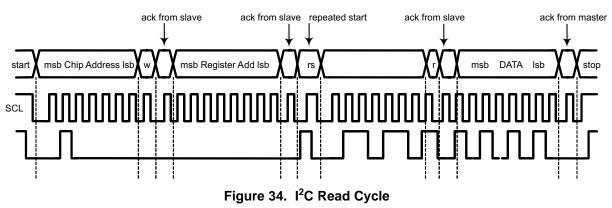

### 8.5.1 I<sup>2</sup>C Interface

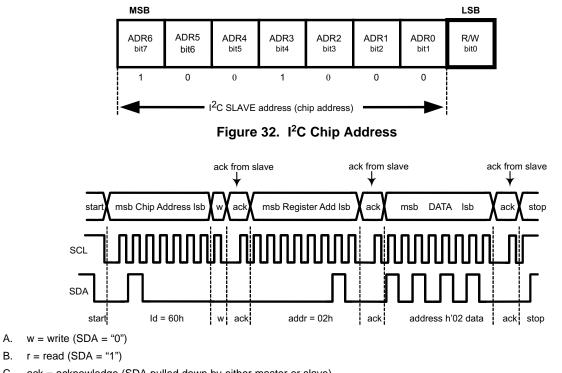

Control of LM10692 is done via I<sup>2</sup>C compatible interface.

### 8.5.1.1 PC Signals

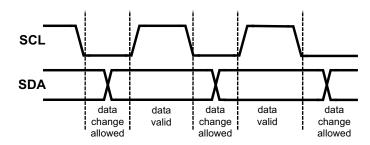

In I2C-compatible mode, the SCL pin is used for the I2C clock and the SDA pin is used for the I2C data. Both these signals need a pull-up resistor according to I2C specification. The values of the pull-up resistors are determined by the capacitance of the bus. See I2C specification from Philips for further details. Signal timing specifications are according to the I2C bus specification. Maximum frequency is 1MHz.

#### 8.5.1.2 $\hat{F}$ C Data Validity

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when CLK is LOW.

Figure 30. I<sup>2</sup>C Signals – Data Validity

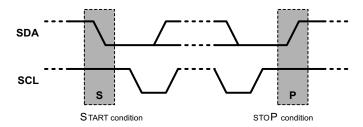

#### 8.5.1.3 I2C Start and Stop Conditions

START and STOP bits classify the beginning and the end of the I2C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I2C master always generates START and STOP bits. The I2C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I2C master can generate repeated START conditions. First START and repeated START conditions are functionally equivalent.

Figure 31. Start and Stop Conditions

#### 8.5.1.4 Transferring Data