National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

2.9 ns

0.6 ns

6.8 mA

2.7V to 12V

-40°C to 125°C

May 29, 2008

# LMH7220 High Speed Comparator with LVDS Output

## **General Description**

The LMH7220 is a high speed, low power comparator with an operating supply voltage range of 2.7V to 12V. The LMH7220 has a differential, LVDS output, driving 325 mV into a 100 $\Omega$  symmetrical transmission line. The LMH7220 has a 2.9 ns propagation delay and 0.6 ns rise and fall times while the supply current is only 6.8 mA at 5V (load current excluded).

The LMH7220 inputs have a voltage range that extends 200 mV below ground, allowing ground sensing applications. The LMH7220 is available in both the 6-Pin TSOT and SC-70 packages. These packages are ideal where space is a critical item.

#### Features

(V\_S = 5V T\_A = 25°C, Typical values unless otherwise specified)

- Propagation delay @ 100 mV overdrive

- Rise and fall times

- Supply voltage

- Supply current

- Temperature range

- LVDS output

### Applications

- Acquisition trigger

- Fast differential line receiver

- Pulse height analyzer

- Peak detector

- Pulse width modulator

- Remote threshold detection

- Oscilloscope triggering

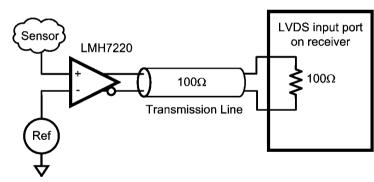

## **Typical Schematic**

20137603

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 2)                 |            |

|----------------------------------------|------------|

| Human Body Model                       | 2.5 kV     |

| Machine Model                          | 250V       |

| Supply Voltage (V <sub>CC</sub> - GND) | 13.5V      |

| Differential Input Voltage             | ±13V       |

| Output Shorted to GND (Note 4)         | Continuous |

| Output Shorted Together (Note 4)       | Continuous |

| Storage Temperature Range     | -65°C to +150°C                   |

|-------------------------------|-----------------------------------|

| Voltage on any I/O Pin        | GND-0.2V to V <sub>CC</sub> +0.2V |

| Junction Temperature (Note 3) | 150°C max                         |

|                               |                                   |

## Operating Ratings (Note 1)

| Temperature Range (Note 3)                   | -40°C to +125°C |

|----------------------------------------------|-----------------|

| Supply Voltage                               | 2.7V to 13V     |

| Package Thermal Resistance ( $\theta_{JA}$ ) |                 |

| 6-Pin TSOT                                   | 189°C/W         |

| 6-Pin SC-70                                  | 450°C/W         |

|                                              |                 |

## +12V DC Electrical Characteristics

Unless otherwise specified, all limits are guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 300 \text{ mV}$ ,  $-50 \text{ mV} < V_{ID} < +50 \text{ mV}$  and  $R_L = 100\Omega$ . Boldface limits apply at the temperature extremes. (Note 6)

| Symbol             | Parameter                                           | Conditions                                                    | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)     | Units |

|--------------------|-----------------------------------------------------|---------------------------------------------------------------|-----------------|-----------------|---------------------|-------|

| I <sub>B</sub>     | Input Bias Current                                  | V <sub>IN</sub> Differential = 0                              | -5<br>-7        | -2.1            | -0.5                | μA    |

| I <sub>os</sub>    | Input Offset Current                                | V <sub>IN</sub> Differential = 0                              | -500            |                 | +500                | nA    |

| TC I <sub>OS</sub> | Input Offset Current TC                             | V <sub>IN</sub> Differential = 0                              |                 | ±2              |                     | nA/°C |

| V <sub>OS</sub>    | Input Offset Voltage                                |                                                               | -9.5            |                 | +9.5                | mV    |

| TC V <sub>OS</sub> | Input Offset Voltage TC                             |                                                               |                 | ± 50            |                     | µV/°C |

| VRI                | Input Voltage Range                                 | CMRR > 50 dB                                                  | -0.2            |                 | V <sub>CC</sub> -2  | V     |

| CMRR               | Common-Mode Rejection Ratio                         | $V_{CM} = 0$ to $V_{CC}$ -2.2V                                | 60              | 70              |                     | dB    |

| PSRR               | Power Supply Rejection Ratio                        |                                                               | 63              | 74              |                     | dB    |

| A <sub>V</sub>     | Open Loop Gain                                      |                                                               |                 | 59              |                     | dB    |

| Vo                 | Output Offset Voltage                               | V <sub>IN</sub> Differential = 50 mV                          | 1125            | 1225            | 1325                | mV    |

| Δνο                | V <sub>O</sub> Change Between '0' and '1'           | V <sub>IN</sub> Differential = ±50 mV                         | -25             |                 | +25                 | mV    |

| V <sub>OH</sub>    | Output Voltage High                                 | V <sub>IN</sub> Differential = 50 mV                          |                 | 1390            | 1475                | mV    |

| V <sub>OL</sub>    | Output Voltage Low                                  | V <sub>IN</sub> Differential = 50 mV                          | 925             | 1060            |                     | mV    |

| V <sub>OD</sub>    | Output Voltage Differential                         | V <sub>IN</sub> Differential = 50 mV                          | 250             | 330             | 400                 | mV    |

| ΔV <sub>OD</sub>   | V <sub>OD</sub> Change between '0' to '1'           | V <sub>IN</sub> Differential = ±50 mV                         | -25             |                 | +25                 | mV    |

| I <sub>SC</sub>    | Short Circuit Current Output to GND<br>Pin (Note 4) | OUT Q to GND Pin<br>V <sub>IN</sub> Differential = 50 mV      |                 |                 | 5                   |       |

|                    |                                                     | OUT                                                           |                 |                 | 5                   | mA    |

|                    | Output Shorted Together (Note 4)                    | OUT Q to OUT Q<br>V <sub>IN</sub> Differential = 50 mV        |                 |                 | 5                   |       |

| I <sub>S</sub>     | Supply Current                                      | Load Current Excluded<br>V <sub>IN</sub> Differential = 50 mV |                 | 7.5             | 10.0<br><b>14.0</b> | mA    |

## +12V AC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 300 \text{ mV}$ ,  $-50 \text{ mV} < V_{ID} < +50 \text{ mV}$  and  $R_L = 100\Omega$ . Bold-face limits apply at the temperature extremes. (Note 6)

| Symbol                  | Parameter         | Conditions                                                | Min      | Тур      | Max      | Units |

|-------------------------|-------------------|-----------------------------------------------------------|----------|----------|----------|-------|

|                         |                   |                                                           | (Note 6) | (Note 5) | (Note 6) |       |

| TR                      | Toggle Rate       | Overdrive = $\pm 50 \text{ mV}$ ; C <sub>L</sub> = 2 pF @ | 860      | 1080     |          | Mb/s  |

|                         |                   | 50% Output Swing                                          |          |          |          |       |

| t <sub>jitter RMS</sub> | RMS-Random Jitter | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                 |          | 4.29     |          | ps    |

| ,                       |                   | Center Frequency = 70 MHz                                 |          |          |          |       |

|                         |                   | Bandwidth = 10 Hz – 20 MHz                                |          |          |          |       |

|                         | •                 | •                                                         |          |          |          |       |

| Symbol                | Parameter                                                            | Conditions                                           | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|-----------------------|----------------------------------------------------------------------|------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| t <sub>PDLH</sub>     | Propagation Delay                                                    | Overdrive 20 mV                                      |                 | 3.56            |                 |       |

|                       | $t_{PDLH} = (t_{PDH} + t_{PD\overline{L}}) / 2$                      | Overdrive 50 mV                                      |                 | 2.98            |                 |       |

|                       | (see figure 3 application note)                                      | Overdrive 100 mV                                     |                 | 2.7             | 7               | ns    |

|                       | Input SR = Constant<br>V <sub>ID</sub> start value = -100 mV         | Overdrive 1V                                         |                 | 2.24            |                 |       |

| t <sub>op</sub> -disp | Input Overdrive Dispersion                                           | @Overdrive 20 - 100 mV                               |                 | 0.86            |                 |       |

|                       |                                                                      | @Overdrive 100 mV - 1V                               |                 | 0.46            |                 | ns    |

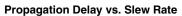

| t <sub>sR</sub> -disp | Input Slew Rate Dispersion                                           | 0.05 V/ns to 1 V/ns<br>Overdrive 100 mV              |                 | 0.24            |                 | ns    |

| t <sub>CM</sub> -disp | Input Common Mode dispersion                                         | SR = 4 V/ns; Overdrive 100 mV<br>$V_{CM}$ = 0 to 10V |                 | 0.55            |                 | ns    |

| ∆t <sub>PDLH</sub>    | Q to Q Time Skew<br>  t <sub>PDH</sub> - t <sub>PDE</sub>   (Note 8) | Overdrive = 100 mV; C <sub>L</sub> = 2 pF            |                 | 0               |                 | ns    |

| ∆t <sub>PDHL</sub>    | Q to Q Time Skew<br>  t <sub>PDL</sub> - t <sub>PDH</sub>   (Note 8) | Overdrive = 100 mV; C <sub>L</sub> = 2 pF            |                 | 0.06            |                 | ns    |

| t <sub>r</sub>        | Output Rise Time (20% - 80%) (Note<br>9)                             | Overdrive = 100 mV; $C_L = 2 pF$                     |                 | 0.56            |                 | ns    |

| f                     | Output Fall Time (20% - 80%) (Note<br>9)                             | Overdrive = 100 mV; C <sub>L</sub> = 2 pF            |                 | 0.49            |                 | ns    |

## +5V DC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 300 \text{ mV}$ ,  $-50 \text{ mV} < V_{ID} < +50 \text{ mV}$  and  $R_L = 100\Omega$ . Bold-face limits apply at the temperature extremes. (Note 6)

| Symbol             | Parameter                                           | Conditions                                                          | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)    | Units |

|--------------------|-----------------------------------------------------|---------------------------------------------------------------------|-----------------|-----------------|--------------------|-------|

| I <sub>B</sub>     | Input Bias Current                                  | V <sub>IN</sub> Differential = 0                                    | -5<br>-7        | -1.5            | -0.5               | μA    |

| I <sub>os</sub>    | Input Offset Current                                | V <sub>IN</sub> Differential = 0                                    | -500            |                 | +500               | nA    |

| TC I <sub>OS</sub> | Input Offset Current TC                             | V <sub>IN</sub> Differential = 0                                    |                 | ± 2             |                    | nA/°C |

| V <sub>os</sub>    | Input Offset Voltage                                |                                                                     | -9.5            |                 | +9.5               | mV    |

| TC V <sub>os</sub> | Input Offset Voltage TC                             |                                                                     |                 | ± 50            |                    | µV/°C |

| VRI                | Input Voltage Range                                 | CMRR > 50 dB                                                        | -0.2            |                 | V <sub>CC</sub> -2 | V     |

| CMRR               | Common-Mode Rejection Ratio                         | $V_{CM} = 0$ to $V_{CC} - 2.2V$                                     | 60              | 70              |                    | dB    |

| PSRR               | Power Supply Rejection Ratio                        |                                                                     | 63              | 74              |                    | dB    |

| A <sub>V</sub>     | Open Loop Gain                                      |                                                                     |                 | 59              |                    | dB    |

| Vo                 | Output Offset Voltage                               | V <sub>IN</sub> Differential = 50 mV                                | 1125            | 1217            | 1325               | mV    |

| ΔV <sub>O</sub>    | V <sub>O</sub> Change Between '0' and '1'           | $V_{IN}$ Differential = ±50 mV                                      | -25             |                 | +25                | mV    |

| V <sub>OH</sub>    | Output Voltage High                                 | V <sub>IN</sub> Differential = 50 mV                                |                 | 1380            | 1475               | mV    |

| V <sub>OL</sub>    | Output Voltage Low                                  | V <sub>IN</sub> Differential = 50 mV                                | 925             | 1060            |                    | mV    |

| V <sub>OD</sub>    | Output Voltage Differential                         | V <sub>IN</sub> Differential = 50 mV                                | 250             | 320             | 400                | mV    |

| ΔV <sub>OD</sub>   | V <sub>OD</sub> Change between '0' to '1'           | V <sub>IN</sub> Differential = ±50 mV                               | -25             |                 | +25                | mV    |

| I <sub>SC</sub>    | Short Circuit Current Output to GND<br>Pin (Note 4) | OUT Q to GND Pin<br>V <sub>IN</sub> Differential = 50 mV            |                 |                 | 5                  |       |

|                    |                                                     | OUT                                                                 |                 |                 | 5                  | mA    |

|                    | Output Shorted Together (Note 4)                    | OUT Q to OUT $\overline{Q}$<br>V <sub>IN</sub> Differential = 50 mV |                 |                 | 5                  |       |

| I <sub>S</sub>     | Supply Current                                      | Load Current Excluded<br>V <sub>IN</sub> Differential = 50 mV       |                 | 6.8             | 9<br><b>12.6</b>   | mA    |

www.national.com

LMH7220

## +5V AC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 300 \text{ mV}$ ,  $-50 \text{ mV} < V_{ID} < +50 \text{ mV}$  and  $R_L = 100\Omega$ . Bold-face limits apply at the temperature extremes. (Note 6)

| Symbol                  | Parameter                                                            | Conditions                                                                                          | Min<br>(Note 6) | <b>Typ</b><br>(Note 5) | Max<br>(Note 6) | Units |

|-------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|------------------------|-----------------|-------|

| TR                      | Toggle Rate                                                          | Overdrive = $\pm 50 \text{ mV}$ ; C <sub>L</sub> = 2 pF @<br>50% Output Swing                       | 750             | 940                    |                 | Mb/s  |

| t <sub>jitter_RMS</sub> | RMS-Random Jitter                                                    | Overdrive = 100 mV; $C_L = 2 \text{ pF}$<br>Center Frequency = 70 MHz<br>Bandwidth = 10 Hz - 20 MHz |                 | 4.44                   |                 | ps    |

| t <sub>PDLH</sub>       | Propagation Delay                                                    | Overdrive 20 mV                                                                                     |                 | 3.63                   |                 |       |

|                         | $t_{PDLH} = (t_{PDH} + t_{PD\overline{L}}) / 2$                      | Overdrive 50 mV                                                                                     |                 | 3.09                   |                 |       |

|                         | (see figure 3 application note)                                      | Overdrive 100 mV                                                                                    |                 | 2.9                    | 7               | ns    |

|                         | Input SR = Constant<br>V <sub>ID</sub> start value = -100mV          | Overdrive 1V                                                                                        |                 | 2.41                   |                 |       |

| t <sub>OD</sub> -disp   | Input Overdrive Dispersion                                           | @Overdrive 20 - 100 mV                                                                              |                 | 0.79                   |                 |       |

|                         |                                                                      | @Overdrive 100 mV - 1V                                                                              |                 | 0.43                   |                 | ns    |

| t <sub>SR</sub> -disp   | Input Slew Rate Dispersion                                           | 0.05 V/ns to 1 V/ns<br>Overdrive 100 mV                                                             |                 | 0.20                   |                 | ns    |

| t <sub>CM</sub> -disp   | Input Common Mode Dispersion                                         | SR = 4 V/ns; Overdrive 100 mV<br>V <sub>CM</sub> = 0 to 3V                                          |                 | 0.21                   |                 | ns    |

| ∆t <sub>PDLH</sub>      | Q to Q Time Skew<br>  t <sub>PDH</sub> - t <sub>PDE</sub>   (Note 8) | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |                 | 0.09                   |                 | ns    |

| ∆t <sub>PDHL</sub>      | Q to Q Time Skew<br>  t <sub>PDL</sub> - t <sub>PDH</sub>   (Note 8) | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |                 | 0.07                   |                 | ns    |

| t <sub>r</sub>          | Output Rise Time (20% - 80%) (Note<br>9)                             | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                                                           |                 | 0.59                   |                 | ns    |

| t <sub>f</sub>          | Output Fall Time (20% - 80%) (Note<br>9)                             | Overdrive = 100 mV; $C_L = 2 pF$                                                                    |                 | 0.55                   |                 | ns    |

## +2.7V DC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 300 \text{ mV}$ ,  $-50 \text{ mV} < V_{ID} < +50 \text{ mV}$  and  $R_L = 100\Omega$ . Bold-face limits apply at the temperature extremes. (Note 6)

| Symbol             | Parameter                                    | Conditions                           | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)    | Units |

|--------------------|----------------------------------------------|--------------------------------------|-----------------|-----------------|--------------------|-------|

| I <sub>B</sub>     | Input Bias Current                           | V <sub>IN</sub> Differential = 0     | -5<br><b>-7</b> | -1.3            | -0.5               | μA    |

| I <sub>OS</sub>    | Input Offset Current                         | V <sub>IN</sub> Differential = 0     | -500            |                 | +500               | nA    |

| TC I <sub>OS</sub> | Input Offset Current TC                      | V <sub>IN</sub> Differential = 0     |                 | ±2              |                    | nA/°C |

| V <sub>os</sub>    | Input Offset Voltage                         |                                      | -9.5            |                 | +9.5               | mV    |

| TC V <sub>OS</sub> | Input Offset Voltage TC                      |                                      |                 | ± 50            |                    | µV/°C |

| VRI                | Input Voltage Range                          | CMRR > 50 dB                         | -0.2            |                 | V <sub>CC</sub> -2 | V     |

| CMRR               | Common-Mode Rejection Ratio                  | $V_{CM} = 0$ to $V_{CC}$ -2.2V       | 56              | 70              |                    | dB    |

| PSRR               | Power Supply Rejection Ratio                 |                                      | 63              | 74              |                    | dB    |

| A <sub>V</sub>     | Open Loop Gain                               |                                      |                 | 59              |                    | dB    |

| Vo                 | Output Offset Voltage                        | V <sub>IN</sub> Differential = 50 mV | 1125            | 1213            | 1325               | mV    |

| ΔV <sub>O</sub>    | V <sub>O</sub> Change Between '0' and '1'    | $V_{IN}$ Differential = ± 50 mV      | -25             |                 | +25                | mV    |

| V <sub>OH</sub>    | Output Voltage High<br>Average of '0' to '1' | V <sub>IN</sub> Differential = 50 mV |                 | 1370            | 1475               | mV    |

| V <sub>OL</sub>    | Output Voltage Low<br>Average of '0' to '1'  | V <sub>IN</sub> Differential = 50 mV | 925             | 1060            |                    | mV    |

| V <sub>OD</sub>    | Output Voltage Differential                  | $V_{IN}$ Differential = 50 mV        | 250             | 315             | 400                | mV    |

LMH7220

| Symbol           | Parameter                                           | Conditions                                                    | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|------------------|-----------------------------------------------------|---------------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| ΔV <sub>OD</sub> | V <sub>OD</sub> Change between '0' to '1'           | $V_{IN}$ Differential = ±50 mV                                | -25             |                 | +25             | mV    |

| I <sub>SC</sub>  | Short Circuit Current Output to GND<br>Pin (Note 4) | OUT Q to GND Pin<br>V <sub>IN</sub> Differential = 50 mV      |                 |                 | 5               |       |

|                  |                                                     | OUT Q to GND Pin<br>V <sub>IN</sub> Differential = 50 mV      |                 |                 | 5               | mA    |

|                  | Output Shorted Together (Note 4)                    | OUT Q to OUT Q<br>V <sub>IN</sub> Differential = 50 mV        |                 |                 | 5               |       |

| I <sub>S</sub>   | Supply Current                                      | Load Current Excluded<br>V <sub>IN</sub> Differential = 50 mV |                 | 6.6             | 9<br>12.6       | mA    |

## +2.7V AC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 300 \text{ mV}$ ,  $-50 \text{ mV} < V_{ID} < +50 \text{ mV}$  and  $R_L = 100\Omega$ . Bold-face limits apply at the temperature extremes. (Note 6)

| Symbol                  | Parameter                                                   | Conditions                                                | Min<br>(Note 6) | <b>Typ</b><br>(Note 5) | Max<br>(Note 6) | Units |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------|------------------------|-----------------|-------|

| TR                      | Toggle Rate                                                 | Overdrive = $\pm 50 \text{ mV}$ ; C <sub>L</sub> = 2 pF @ | 700             | 880                    |                 | Mb/s  |

|                         |                                                             | 50% Output Swing                                          |                 |                        |                 |       |

| t <sub>jitter_RMS</sub> | RMS-Random Jitter                                           | Overdrive = 100 mV; $C_L = 2 pF$                          |                 | 4.82                   |                 | ps    |

|                         |                                                             | Center Frequency = 70 MHz                                 |                 |                        |                 |       |

|                         |                                                             | Bandwidth = 10 Hz – 20 MHz                                |                 |                        |                 |       |

| t <sub>PDLH</sub>       | Propagation Delay                                           | Overdrive 20 mV                                           |                 | 3.80                   |                 |       |

|                         | $t_{PDLH} = (t_{PDH} + t_{PD\overline{L}}) / 2$             | Overdrive 50 mV                                           |                 | 3.29                   |                 |       |

|                         | (see figure 3 application note)                             | Overdrive 100 mV                                          |                 | 3.0                    | 7               | ns    |

|                         | Input SR = Constant<br>V <sub>ID</sub> start value = -100mV | Overdrive 1V                                              |                 | 2.60                   |                 |       |

| t <sub>OD</sub> -disp   | Input Overdrive Dispersion                                  | @Overdrive 20 - 100 mV                                    |                 | 0.83                   |                 |       |

|                         |                                                             | @Overdrive 100 mV - 1V                                    |                 | 0.37                   |                 | ns    |

| t <sub>sR</sub> -disp   | Input Slew Rate Dispersion                                  | 0.05 V/ns to 1 V/ns                                       |                 | 0.23                   |                 | ns    |

|                         |                                                             | Overdrive 100 mV                                          |                 |                        |                 |       |

| t <sub>cM</sub> -disp   | Input Common Mode dispersion                                | SR = 4 V/ns; Overdrive 100 mV                             |                 | 0.16                   |                 | ns    |

|                         |                                                             | V <sub>CM</sub> = 0 to 1.5V                               |                 |                        |                 |       |

| ∆t <sub>PDLH</sub>      | Q to $\overline{Q}$ Time Skew                               | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                 |                 | 0.09                   |                 | ns    |

| I DEIT                  | ∣ t <sub>PDH</sub> - t <sub>PDL</sub> ∣ (Note 8)            | _                                                         |                 |                        |                 |       |

| ΔtPDHL                  | Q to $\overline{Q}$ Time Skew                               | Overdrive = 100 mV; $C_1 = 2 pF$                          |                 | 0.09                   |                 | ns    |

|                         | ∣ t <sub>PDL</sub> - t <sub>PDH</sub> ∣ (Note 8)            |                                                           |                 |                        |                 |       |

| t <sub>r</sub>          | Output Rise Time (20% - 80%) (Note                          | Overdrive = 100 mV; $C_L = 2 pF$                          |                 | 0.64                   |                 | ns    |

| -                       | 9)                                                          |                                                           |                 |                        |                 |       |

| t <sub>f</sub>          | Output Fall Time (20% - 80%) (Note<br>9)                    | Overdrive = 100 mV; C <sub>L</sub> = 2 pF                 |                 | 0.59                   |                 | ns    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Conditions indicate specifications for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC)

**Note 3:** The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/|\theta_{JA}|$ . All numbers apply for packages soldered directly onto a PC Board.

Note 4: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

Note 5: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 6: All limits are guaranteed by testing or statistical analysis.

**Note 7:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where  $T_J > T_A$ . See applications section for information on temperature de-rating of this device.

LMH7220

**Note 8:** Propagation Delay Skew,  $\Delta t_{PD}$ , is defined as the average of  $\Delta t_{PDLH}$  and  $\Delta t_{PDHL}$ . **Note 9:** The rise or fall time is the average of the Q and  $\overline{Q}$  rise or fall time.

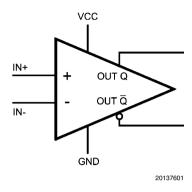

## Schematic Diagram

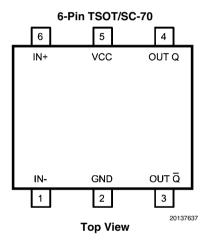

## **Connection Diagram**

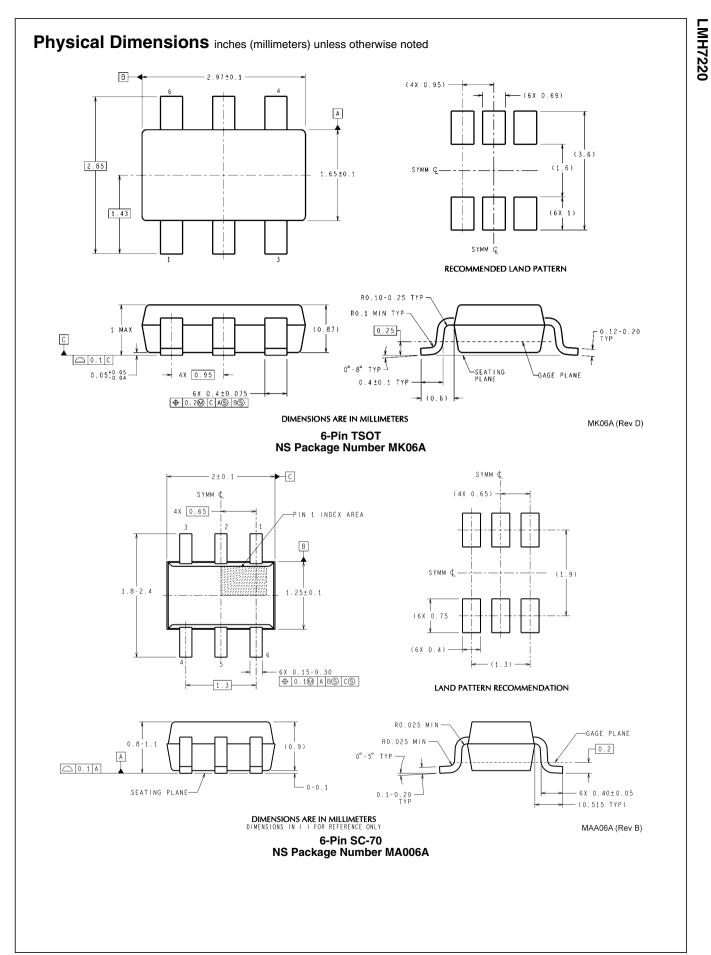

## **Ordering Information**

| Package Part Number<br>Temperature Range (T <sub>A</sub> )<br>-40°C to +85°C |            | Package Marking | Transport Media        | NSC Drawing |

|------------------------------------------------------------------------------|------------|-----------------|------------------------|-------------|

| 6-Pin TSOT                                                                   | LMH7220MK  | C29A            | 1k Units Tape and Reel | MK06A       |

| 0-FIII 1301                                                                  | LMH7220MKX | 029A            | 3k Units Tape and Reel | MINUOA      |

| 6-Pin SC-70                                                                  | LMH7220MG  | C38             | 1k Units Tape and Reel | MA006A      |

| 0-Fill SC-70                                                                 | LMH7220MGX | 038             | 3k Units Tape and Reel | IVIAUU6A    |

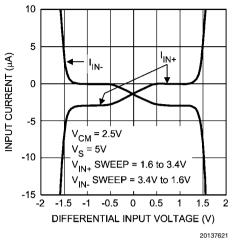

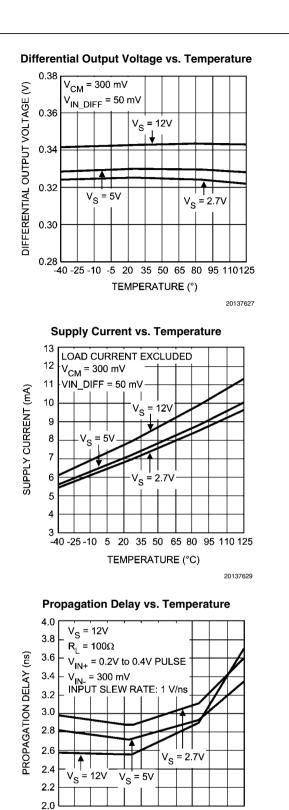

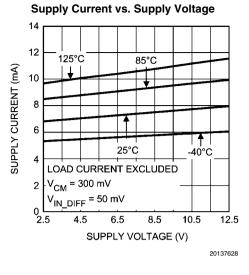

## **Typical Performance Characteristics**

At T<sub>J</sub> = 25°C; unless otherwise specified: V<sub>CM</sub> = 0.3V, V<sub>OVERDRIVE</sub> = 100 mV, R<sub>L</sub> = 100 $\Omega$ .

#### Input Current vs. Differential Input Voltage

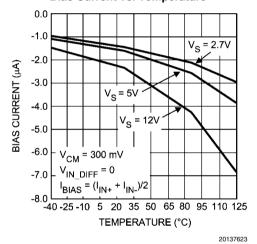

Bias Current vs. Temperature

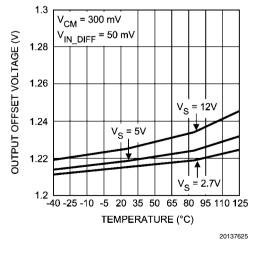

**Bias Current vs. Supply Voltage**

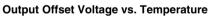

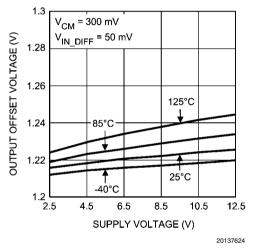

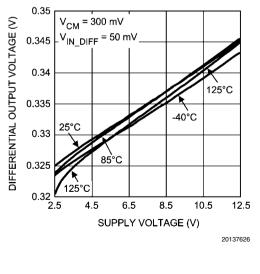

Output Offset Voltage vs. Supply Voltage

-40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

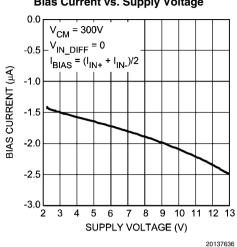

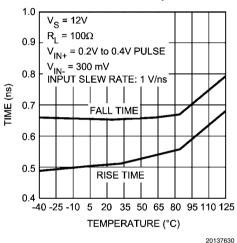

**Rise & Fall Time vs. Temperature**

i

20137631

## **Application Information**

#### INTRODUCTION

The LMH7220 is a high speed comparator with LVDS outputs. The LVDS (Low Voltage Differential Signaling) standard uses differential outputs with a voltage swing of approximately 325 mV on each output. The most widely used setup for LVDS outputs consists of a switched current source of 3.25 mA. The output pins need to be differentially terminated with an external 100 $\Omega$  resistor, producing the standardized output voltage swing of 325 mV. The common mode level of both outputs is about 1.2V, and is independent of the power supply voltage. The use of complementary outputs gives a high level of suppression for common mode noise. The very fast rise and fall times of the LMH7220 enable data transmission rates up to several hundreds of Megabits per second (Mbps). Due to the current-nature of the outputs the power consumption remains at a very low level even if the data transmission rate is rising. Power delivered to a load resistance of  $100\Omega$  is only 1.2 mW. More information about the LVDS standard can be found on the National site:

http://www.national.com/appinfo/lvds/0,1798,100,00.html

The LMH7220 inputs have a common mode voltage range that extends 200 mV below the negative supply voltage thus allowing ground sensing in case of single supply. The rise and fall times of the LMH7220 are about 0.6 ns, while the propagation delay time is about 2.7 ns. The LMH7220 can operate over the full supply voltage range of 2.7V to 12V, while using single or dual supply voltages. The LVDS outputs refer to the negative supply rail. The supply current is 6.8 mA at 5V (load current excluded). The LMH7220 is available in both the 6-Pin TSOT and SC-70 packages.

These packages are ideal where space is an important issue. In the next sections the following issues are discussed:

- In- and output topology

- Definition of terms of used specifications

- Propagation delay and dispersion

- Hysteresis and oscillations

- The output

- Applying transmission lines

- PCB layout

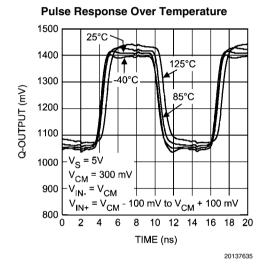

#### **INPUT & OUTPUT TOPOLOGY**

All input and output pins are protected against excessive voltages by ESD diodes. These diodes are connected from the negative supply to the positive supply. As can be seen in *Figure 1*, both inputs are connected to these diodes. Protection against excessive supply voltages is provided by a power clamp between V<sub>CC</sub> and GND. Both inputs are also connected to the bases of the input transistors of the differential pair via 1.5 k $\Omega$  resistors. The input transistors cannot withstand high reverse voltages between bases and emitter, due to their high frequency properties. To protect the input stage against damage, both bases are connected together by a string of antiparallel diodes. Be aware of situations in which differential input voltage level is such that these diodes are conducting. In this case the input current is raised far above the normal value stated in the datasheet tables.

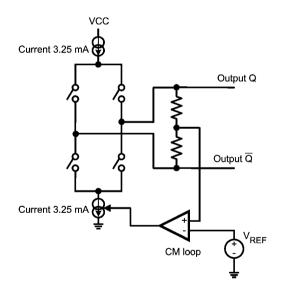

FIGURE 1. Equivalent Input Circuitry

The output can be seen as a bridge configuration in which switches are crosswise closed, producing the differential LVDS logic high and low levels (see *Figure 2*). The output switches are fed at top and bottom by two current sources. The top one is fixed and determines the differential voltage across the external load resistor. The other one is regulated and determines the common-mode voltage on the outputs. It is essential to keep the output common-mode voltage at the defined standardized LVDS level under all circumstances. To realize this, both outputs are internally connected together via two equal resistors. At the midpoint this produces the common mode output voltage, which is made equal to V<sub>REF</sub> (1.2V) by means of the CM feedback loop.

Equivalent Output Circuitry

20137611

#### FIGURE 2. Equivalent Output Circuitry

#### DEFINITIONS

For a good understanding of many parameters of the LMH7220 it is necessary to perform a lot of measurements. All of those parameters are listed in the data tables in the first part of the datasheet. There are different tables for several supply voltages containing a separate set of data per supply

voltage. In the table below is a list of abbreviations of the measured parameters and a short description of the conditions which are applied for measuring them . Following this table several parameters are highlighted to explain more clearly what it means exactly and what effects such a phenomena can have for any applied electronic circuit.

| Symbol                                 | Text                                             | Description                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I <sub>B</sub>                         | Input Bias Current                               | Current flowing in or out the input pins, when both biased at 0.3 Volt above GND                                                                                                                                                                                                                                                                                                                          |  |

| I <sub>OS</sub>                        | Input Offset Current                             | Difference between the positive- and the negative input currents needed to make the outputs change state, averaged for H to L and L to H transitions                                                                                                                                                                                                                                                      |  |

| TC I <sub>OS</sub>                     | Average Input Offset Current Drift               | Temperature Coefficient of I <sub>OS</sub>                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>OS</sub>                        | Input Offset Voltage                             | Voltage difference needed between $IN^+$ and $IN^-$ to make the outputs change state, averaged for H to L and L to H transitions                                                                                                                                                                                                                                                                          |  |

| TC V <sub>OS</sub>                     | Average Input Offset Voltage Drift               | Temperature Coefficient of V <sub>OS</sub>                                                                                                                                                                                                                                                                                                                                                                |  |

| CMRR                                   | Common Mode Rejection Ratio                      | Ratio of input offset voltage change and input common mode voltage change                                                                                                                                                                                                                                                                                                                                 |  |

| VRI                                    | Input Voltage Range                              | Upper and lower limits of the input voltage are defined as where CMRR drops below 50 dB.                                                                                                                                                                                                                                                                                                                  |  |

| PSRR                                   | Power Supply Rejection Ratio                     | Ratio of input offset voltage change and supply voltage change from $V_{\text{S-MIN}}$ to $V_{\text{S-MAX}}$                                                                                                                                                                                                                                                                                              |  |

| Vo                                     | Output Offset Voltage                            | Output Common Mode Voltage averaged for logic '0' and logic '1' levels (See <i>Figure 12</i> )                                                                                                                                                                                                                                                                                                            |  |

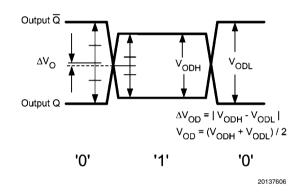

| ΔV <sub>O</sub>                        | Change in Output Offset Voltage                  | Difference in Output Common Mode Voltage between logic '0' and logic '1' levels (See <i>Figure 13</i> )                                                                                                                                                                                                                                                                                                   |  |

| V <sub>OH</sub>                        | Output Voltage High                              | High state single ended output voltage ( $\overline{Q}$ or Q) (See Figure 12)                                                                                                                                                                                                                                                                                                                             |  |

| V <sub>OL</sub>                        | Output Voltage Low                               | Low state single ended output voltage ( $\overline{Q}$ or Q) (See <i>Figure 12</i> )                                                                                                                                                                                                                                                                                                                      |  |

| V <sub>ODH</sub>                       | Output Differential Voltage logic '1'            | $V_{OH(Q)} - V_{OL(\overline{Q})}$ (logic level '1') (See <i>Figure 13</i> )                                                                                                                                                                                                                                                                                                                              |  |

| V <sub>ODL</sub>                       | Output Differential Voltage logic '0'            | $V_{OH(\overline{Q})} - V_{OL(Q)}$ (logic level '0') (See <i>Figure 13</i> )                                                                                                                                                                                                                                                                                                                              |  |

| V <sub>OD</sub>                        | Average of V <sub>ODH</sub> and V <sub>ODL</sub> | $(V_{ODH} + V_{ODL})/2$                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ΔV <sub>OD</sub>                       | Change in V <sub>OD</sub> between '0' and '1'    | IV <sub>ODH</sub> – V <sub>ODL</sub> I (See <i>Figure 13</i> )                                                                                                                                                                                                                                                                                                                                            |  |

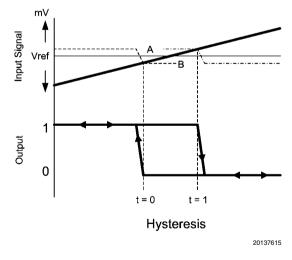

| Hyst                                   | Hysteresis                                       | Difference in input switching levels for L to H and H to L transitions.<br>(See <i>Figure 11</i> )                                                                                                                                                                                                                                                                                                        |  |

| $I_{SQG}, I_{S\overline{Q}G}$          | Short Circuit Current one output to GND          | Current that flows from one output to GND if shorted single ended                                                                                                                                                                                                                                                                                                                                         |  |

| I <sub>SQQ</sub>                       | Short Circuit Current outputs together           | Current flowing between output Q and output $\overline{Q}$ if shorted differentially                                                                                                                                                                                                                                                                                                                      |  |

| TR                                     | Maximum Toggle Rate                              | Maximum frequency at which the outputs can toggle before V <sub>OD</sub> drops under 50% of the nominal value.                                                                                                                                                                                                                                                                                            |  |

| PW                                     | Pulse Width                                      | Time from 50% of the rising edge of a signal to 50% of the falling edge                                                                                                                                                                                                                                                                                                                                   |  |

| t <sub>PDH</sub> resp t <sub>PDL</sub> | Propagation Delay                                | Delay time between the moment the input signal crosses the switching level L to H and the moment the output signal crosses 50% of the rising edge of Q output ( $t_{PDH}$ ), or delay time between the moment the input signal crosses the switching level H to L and the moment the output signal crosses 50% of the falling edge of Q output ( $t_{PDL}$ )                                              |  |

| t <sub>PDĒ</sub> resp t <sub>PDĦ</sub> |                                                  | Delay time between the moment the input signal crosses the switching level L to H and the moment the output signal crosses 50% of the falling edge of $\overline{Q}$ output $(t_{PD\overline{L}})$ , or delay time between the moment the input signal crosses the switching level H to L and the moment the output signal crosses 50% of the rising edge of $\overline{Q}$ output $(t_{PD\overline{H}})$ |  |

| t <sub>PDLH</sub>                      |                                                  | Average of $t_{PDH}$ and $t_{PD\overline{L}}$                                                                                                                                                                                                                                                                                                                                                             |  |

| t <sub>PDHL</sub>                      |                                                  | Average of $t_{PDL}$ and $t_{PD\overline{H}}$                                                                                                                                                                                                                                                                                                                                                             |  |

| t <sub>PD</sub>                        |                                                  | Average of t <sub>PDLH</sub> and t <sub>PDHL</sub>                                                                                                                                                                                                                                                                                                                                                        |  |

| Symbol                                                | Text                                  | Description                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| t <sub>PDHd</sub> resp t <sub>PDLd</sub>              |                                       | Delay time between the moment the input signal crosses the switching level L to H and the zero crossing of the rising edge of the differentia output signal ( $t_{PDHd}$ ), or delay time between the moment the input signal crosses the switching level H to L and the zero crossing of the falling edge of the differential output signal ( $t_{PDHd}$ ). |  |  |

| $\Delta t_{PDLH} \operatorname{resp} \Delta t_{PDHL}$ | Q to $\overline{Q}$ time skew         | Time skew between 50% levels of rising edge of Q output and falling edge of $\overline{Q}$ output ( $\Delta t_{PDLH}$ ), or time skew between 50% levels of falling edge of Q output and rising edge of $\overline{Q}$ output ( $\Delta t_{PDLH}$ )                                                                                                          |  |  |

| Δt <sub>PD</sub>                                      | Average Q to $\overline{Q}$ time skew | Average of t <sub>PDLH</sub> and t <sub>PDHL</sub> for L to H and H to L transients                                                                                                                                                                                                                                                                          |  |  |

| Δt <sub>PDd</sub>                                     | Average diff. time skew               | Average of t <sub>PDHd</sub> and t <sub>PDLd</sub> for L to H and H to L transients                                                                                                                                                                                                                                                                          |  |  |

| t <sub>OD-disp</sub>                                  | Input overdrive dispersion            | Change in t <sub>PD</sub> for different overdrive voltages at the input pins                                                                                                                                                                                                                                                                                 |  |  |

| t <sub>SR-disp</sub>                                  | Input slew rate dispersion            | Change in t <sub>PD</sub> for different slew rates at the input pins                                                                                                                                                                                                                                                                                         |  |  |

| t <sub>CM-disp</sub>                                  | Input Common Mode dispersion          | Change in t <sub>PD</sub> for different common mode voltages at the input pins                                                                                                                                                                                                                                                                               |  |  |

| t <sub>r</sub> / t <sub>rd</sub>                      | Output rise time (20% - 80%)          | Time needed for the (single ended or differential) output voltage to change from 20% of its nominal value to 80%                                                                                                                                                                                                                                             |  |  |

| t <sub>f</sub> / t <sub>fd</sub>                      | Output fall time (20% - 80%)          | Time needed for the (single ended or differential) output voltage to change from 80% of its nominal value to 20%                                                                                                                                                                                                                                             |  |  |

#### DELAY AND DISPERSION

Comparators are widely used to connect the analog world to the digital one. The accuracy of a comparator is dictated by its DC properties such as offset voltage and hysteresis and by its timing aspects such as rise and fall times and delay. For low frequency applications most comparators are much faster than the analog input signals they handle. The timing aspects are less important here than the accuracy of the input switching levels. The higher the frequency, the more important the timing properties of the comparator become, because the response of the comparator can give e.g. a noticeable change in time frame or duty cycle. A designer has to know these effects in order to deal with them. In order to predict what the output signal will do compared to the input signal, several parameters are defined which describe the behavior of the comparator. For a good understanding of the timing parameters discussed in the following section, a brief explanation is given and several timing diagrams are shown for clarification.

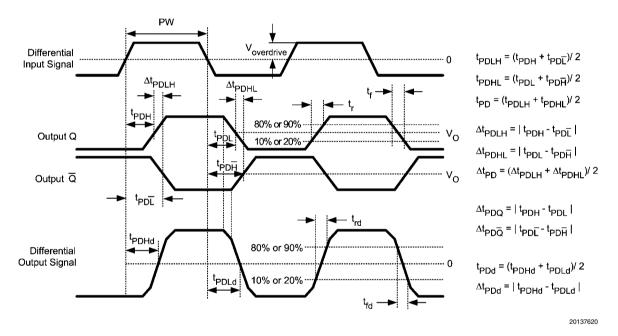

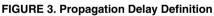

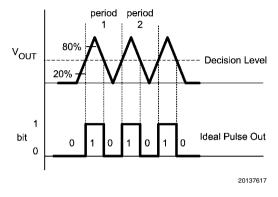

#### PROPAGATION DELAY

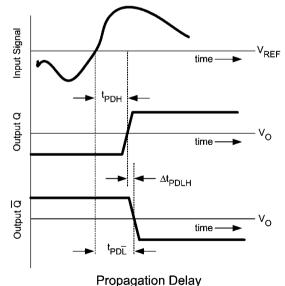

The propagation delay parameter is defined as the time it takes for the comparator to change the output level halfway in its transition from L to H or H to L, in reaction to the moment the input signal crosses the switching level. Due to this definition there are two parameters,  $t_{PDH}$  and  $t_{PDL}$  (*Figure 4*). Both parameters don't necessarily have the same value. It is possible that differences will occur due to a different response of the internal circuitry. As a result of this effect another parameter is defined:  $\Delta t_{PD}$ . This parameter is defined as the absolute value of the difference between  $t_{PDH}$  and  $t_{PDL}$ .

FIGURE 4. Pulse Parameter

If  $\Delta t_{PD}$  isn't zero, duty cycle distortion will occur. For example when applying a symmetrical waveform (e.g. a sinewave) at the input, it is expected that the comparator produces a symmetrical square wave at the output with a duty cycle of 50%. In case of different  $t_{\text{PDH}}$  and  $t_{\text{PDL}}$  the duty cycle of the output signal will not remain at 50%, but will be lower or higher. In addition to the propagation delay parameters for single ended outputs discussed before, there are other parameters in case of complementary outputs. These parameters describe the delay from input to each of the outputs and the difference between both delay times (see Figure 5). When the differential input signal crosses the reference level from L to H, both outputs will switch to their new state with some delay. This is defined as  $t_{PDH}$  for the Q output and  $t_{PDL}$  for the Q output, while the difference between both signals is defined as  $\Delta tP_{DLH}$ . similar definitions for the falling slope of the input signal can be seen in Figure 3.

Flopagation Delay

**FIGURE 5. Propagation Delay**

Both output circuits should be symmetrical. At the moment one output is switching 'on' the other is switching 'off' with ideally no skew between them. The design of the LMH7220 is optimized to minimize this timing difference. Propagation delay  $t_{PD}$  is defined as the average delay of both outputs at both slopes:  $(t_{PDLH} + t_{PDHL}) / 2$ .

#### DISPERSION

There are several circumstances that will produce a variation of the propagation delay time. This effect is called dispersion.

#### **Amplitude Overdrive Dispersion**

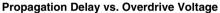

One of the parameters that causes dispersion is the amplitude variation of the input signal. *Figure 6* shows the dispersion due to a variation of the input overdrive voltage. The overdrive is defined as the 'goto' differential voltage applied to the inputs. *Figure 6* shows the impact it has on the propagation delay time if overdrive is varied from 10 millivolts to 100 millivolts. This parameter is measured with a constant slew rate of the input signal.

#### **FIGURE 6. Overdrive Dispersion**

The overdrive dispersion is caused by the fact that switching currents in the input stage depend on the level of the differential input signal.

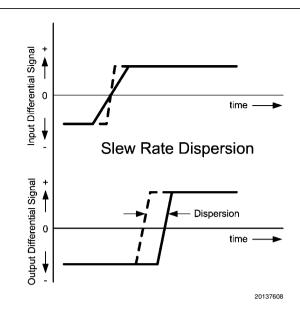

#### **Slew Rate Dispersion**

The slew rate is another parameter that affects propagation delay. The higher the input slew rate, the faster the input stage switches (*Figure 7*).

20137612

# LMH7220

**FIGURE 7. Slew Rate Dispersion**

A combination of overdrive- and slew rate dispersion occurs when applying signals with different amplitude at constant frequency. A small amplitude will produce a small voltage change per time unit (dV/dt) but also a small maximum switching current (overdrive) in the input transistors. High amplitudes produce a high dV/dt and a bigger overdrive.

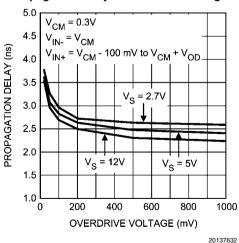

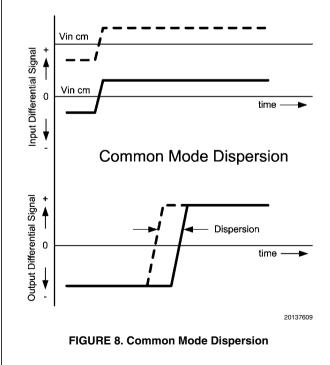

#### **Common Mode Dispersion**

Dispersion will also occur when changing the common mode level of the input signal (*Figure 8*). When  $V_{REF}$  is swept through the CMVR (Common Mode Voltage Range), this results in a variation of the propagation delay time. This variation is called Common Mode Dispersion.

All of the dispersion effects discussed before influence the propagation delay. In practice the dispersion is often caused by a combination of more than one varied parameter. It is good to realize this if there is the need to predict how much dispersion a circuit will show.

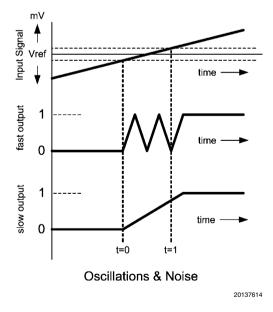

#### **HYSTERESIS & OSCILLATIONS**

In contrast to an op amp, the output of a comparator has only two defined states '0' or '1'. Due to finite comparator gain however, there will be a small band of input differential voltage where the output is in an undefined state. An input signal with fast slopes will pass this band very quickly without problems. During slow slopes however, passing the band of uncertainty can be relatively long. This enables the comparator outputs to switch back and forth several times between '0' and '1' on a single slope. The comparator will switch on its input noise, ground bounce (possible oscillations), ringing etc. Noise in the input signal will also contribute to these undesired switching effects.

In the next sections an explanation follows about these phenomena in situations where no hysteresis is applied, and the possible improvement hysteresis can give.

#### **Using No Hysteresis**

In *Figure 9* can be seen what happens when the input signal rises from just under the threshold  $V_{REF}$  to a level just above it. From the moment the input reaches the lowest dotted line around  $V_{REF}$  at t=0, the output toggles on noise etc. Toggling ends when the input signal leaves the undefined area at t=1. In this example the output was fast enough to toggle three times. Due to this behavior digital circuitry connected to the output will count a wrong number of pulses. One way to prevent this is to choose a very slow comparator with an output that is not able to switch more than once between '0' and '1' during the time the input state is undefined.

FIGURE 9. Oscillations & Noise

In most circumstances this is not an option because the slew rate of the input signal will vary.

#### **Using Hysteresis**

Cp

Rp

$V_{RFF}$

A good way to avoid oscillations and noise during slow slopes is the use of hysteresis. For this purpose a threshold is introduced that pushes the input switching level back at the moment the output switches (See *Figure 10*). In this simple setup, a comparator with a single output and a resistive divider to the positive input is drawn.

$c_{c}$

R,

V<sub>IN</sub>

## Simplified Schematic

#### **FIGURE 10. Simplified Schematic**

The divider  $R_F \cdot R_P$  feeds back a portion of the output voltage to the positive input. Only a small part of the output voltage is needed, just enough to avoid the area at which the input is in an undefined state. Assuming this is only a few millivolts, it is sufficient to add (plus or minus) 10 mV to the positive input to prevent the circuit from oscillations. If the output switches between 0V and 5V and the choice for one of the resistors is done the other can be calculated. Assume  $R_P$  is 50 $\Omega$  then  $R_F$  is 25 k $\Omega$  for 10 mV threshold on the positive input. The situation of *Figure 11* is now created.

FIGURE 11. Hysteresis

In this picture there are two dotted lines A and B, both indicating the resulting level at the positive input. When the signal at the negative input is low, the state of the input stage is well defined with the negative input much lower than the positive input. As a result the output will be in the high state. The positive input is at level A. With the input signal sloping up, this situation remains until V<sub>IN</sub> crosses level A at t=1. Now the output toggles, and the voltage at the positive input is lowered to level B. So before the output has the possibility to toggle again, the difference between both inputs is made sufficient to have a stable situation again. When the input signal comes down from high to low, the situation is stable until level B is reached at t=0. At this moment the output will toggle back, and the circuit is back in the start situation with the negative input at a much lower level than the positive one. In the situation without hysteresis, the output would toggle exactly at V<sub>REF</sub>. With hysteresis this happens at the introduced levels A and B, as can be seen in *Figure 11*. Varying the levels A and B will also vary the timing of t=0 and t=1. When designing a circuit be aware of this effect. Introducing hysteresis will cause some time shifts between output and input (e.g. duty cycle variations), but eliminates undesired switching of the output.

#### **Parasitic Capacitors**

In the simple schematic of Figure 10 some capacitors are drawn. The capacitors C<sub>P</sub>. represent the parasitic (board) capacitance at the input of the part. This capacity will slow down the change of the level of the positive input in reaction to the changing output voltage. As a result of this, the output may have the time to switch over more than once. Actually the parasitic capacity represented by C<sub>P</sub> makes the attenuation circuit of R<sub>F</sub> and R<sub>P</sub> frequency dependent. The only action to take is to create a frequency independent circuit. This is simply done by placing the compensation capacitor C<sub>C</sub> in parallel with  $R_{F}$ . The capacitor  $C_{C}$  can be calculated with the formula  $R_F * C_C = R_P * C_P$ , this means that both of the time constants must be the same to create a frequency independent network. A simple example gives the following assuming that  $C_{P}$  is in total 2.5 pF and as already calculated  $R_F = 25 \text{ k}\Omega$  in combination with  $R_P = 50\Omega$ . These input data gives:

$$C_{C} = R_{P} * C_{P}/R_{F}$$

$C_{C} = 50*2.5e-12/25e3$

$C_{C} = 5e-15 = 0.005 \text{ pF}$

This is not a practical value and different conclusions are possible:

- No capacitor C<sub>C</sub> needed

- Place a capacitor C<sub>C</sub> of 1 pF and accept a big overshoot at the positive input being sure that the input stage is in a secure new position

- Place an extra  $C_P$  of such a value that  $C_C$  has a realistic value of say 1 pF (extra  $C_P = \pm 500$  pF).

#### **Position of Feedback Resistors**

Another important issue while using positive feedback is the placement of the resistors  $R_p$  and  $R_F$ . These resistors must be placed as near as possible to the positive input, because this input is most sensitive for picking up spurious signals, noise etc. This connection must be very clean for the best performance of the overall circuit. With raising speeds the total PCB design becomes more and more critical, the LMH7220 comparator doesn't have built in hysteresis, so the input signal must meet minimum requirements to make the output switch over properly. In the following sections some aspects concerning the load connected to the outputs and transmission lines will be discussed.

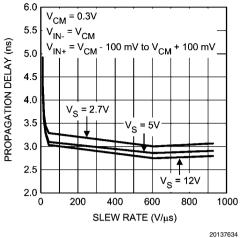

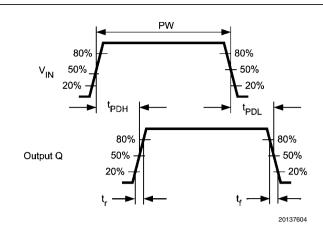

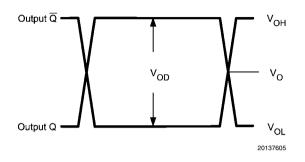

#### THE OUTPUT SWING PROPERTIES

LVDS has differential outputs which means that both outputs have the same swing but in opposite direction (*Figure 12*). Both outputs swing around a voltage called the common mode output voltage ( $V_O$ ). This voltage can be measured at the midpoint of two equal resistors connected to both outputs as discussed in the section 'Input and Output Topology'. The absolute value of the difference between both voltages is called V<sub>OD</sub>. LVDS outputs cannot be held at the V<sub>O</sub> level because of their digital nature. They only cross this level during a transition. Due to the symmetrical structure of the circuit, both output voltages cross at V<sub>O</sub> regardless if the output changes from '0' to '1' or vise versa.

FIGURE 12. LVDS Output Signals

In case the outputs aren't symmetrical or are a-symmetrically loaded, the output voltages differ from the situation of *Figure 12*. For this non-ideal situation there are two additional parameters defined,  $\Delta V_O$  and  $\Delta V_{OD}$ , as can be seen in *Figure 13*.

#### FIGURE 13. LVDS Output Signals with Different Amplitude

$\Delta V_O$  is the difference in  $V_O$  between the '1' state and the '0' state. This variation is acceptable if it is below 50 mV following the ANSI/TIA/EIA-644 LVDS standard. It is also possible that  $V_{OD}$  in the '1' state isn't the same as in the '0' state. This parameter is specified as  $\Delta V_{OD}$ , and is calculated as the absolute value of the difference of  $V_{ODH}$  and  $V_{ODL}$ .

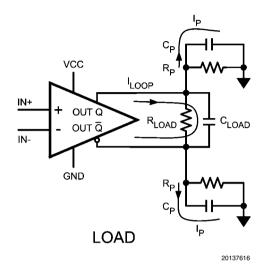

#### LOADING THE OUTPUT

The output structure creates a current ( $I_{LOOP}$  see *Figure 14*) through an external differential load resistor of 100 $\Omega$  nominal. This results in a differential output voltage of 325 mV. The outputs of the comparator are connected to tracks on a PCB. These tracks can be seen as a differential transmission line. The differential load resistor acts as a high frequency termination at the end of the transmission line. This means that for a proper signal behavior the PCB tracks have to be dimensioned for a characteristic impedance of 100 $\Omega$  as well. Changing the load resistor also implies a change of the transmission line and termination can be found in the next section. The signal across the 100 $\Omega$  termination resistor is fed into the inputs of subsequent circuitry that processes the data. Any connection to input circuitry of course draws current from the

comparator's outputs. In the case of a balanced input connected to the load resistance, current  $I_{\rm P}$  is drawn from both output connection points to ground. Keep in mind that the LMH7220's ability to source currents is much higher than to sink them. The connected input circuitry also forms a differential load to the outputs of the comparator (see *Figure 14*). This will cause the voltage across the termination resistor to differ from its nominal value.

#### FIGURE 14. Load

In general one single connection only draws a few µA's, and doesn't have much effect on the LVDS output voltage. For multiple inputs on one output pair, load currents must not exceed the specified limits, as described in the ANSI or IEEE LVDS standards. Below a specified value of V<sub>OD</sub>, the functioning of subsequent circuitry becomes uncertain. However under normal conditions there is no need to worry. Another point of practice is load capacitances. Capacitances are applied differentially ( $C_{LOAD}$ ) and also to ground ( $C_P$ ). All of these capacitors will disturb the pulse shape. The edges of the output pulse become slower, and in reaction the detection of the transition comes at a later moment. Be aware of this effect when measuring with probes. Both single ended and differential probes have these capacitances. A standard probe commonly has a load capacity of about 8 to 10 pF. This will cause some degradation of the pulse shape and will add some time delay.

#### TRANSMISSION LINES & TERMINATION TECHNOLOGIES

The LMH7220 uses LVDS technology. LVDS is a way to communicate data using low voltage swing and low power consumption. Nowadays data rates are growing, requiring increasing speed. Data isn't only connected to other IC's on a single PCB board but in many cases there are interconnections from board to board or from equipment to equipment. Distances can be short or long but it is always necessary to have a reliable connection, consume low power and to be able to handle high data rates. LVDS is a differential signal protocol. The advantage over single ended signal transmission is its higher immunity to common mode noise. Common mode signals are signals that are equally apparent on both lines and because the receiver only looks at the difference between both lines, this noise is canceled.

#### **Maximum Bitrates**

A very important specification in high speed circuits are the rise and fall times. In fact these determine the maximum toggle rate (TR) of the part. The LVDS standard specifies them at 0.26 ns to 1.5 ns. Rise and fall times are normally specified at 20% and 80% of the signal amplitude (60% difference). TR is defined as the bitrate at which the differential output voltage drops to 50% of its nominal value.

#### FIGURE 15. Bitrate

#### **Need for Terminated Transmission Lines**

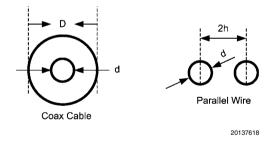

During the '80's and '90's National fabricated the 100k ECL logic family. The rise and fall time specification was 0.75 ns which was very fast and will easily introduce errors in digital circuits if insufficient care has been taken to the transmission lines and terminations used for these signals. To be helpful to designers that use ECL with "old" PCB-techniques, the 10k ECL family was introduced with a rise and fall time specification of 2 ns. This was much slower and more easy to use. LVDS signals have transition times that exceed the fastest ECL family. A careful PCB design is needed using RF techniques for transmission and termination. Transmission lines can be formed in several ways. The most commonly used types are the coaxial cable and the twisted pair telephony cable (*Figure 16*).

FIGURE 16. Cable Configuration

These cables have a characteristic impedance determined by their geometric parameters. Widely used impedances for the coaxial cable are  $50\Omega$  and  $75\Omega$ . Twisted pair cables have impedances of about  $120\Omega$  to  $150\Omega$ .

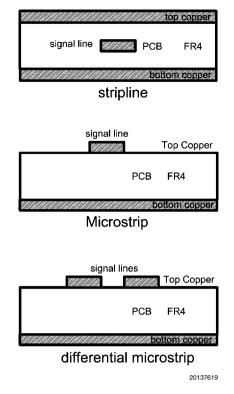

Other types of transmission lines are the strip line and the micro strip. These last types are used on PCB boards. They have the characteristic impedance dictated by the physical dimensions of a track placed over a metal ground plane (See *Figure 17*).

FIGURE 17. PCB Transmission Lines

#### **Differential Microstrip Line**