# 8274

# Multi-Protocol Serial Controller (MPSC)

The Intel 8274 Multi-Protocol Series Controller (MPSC) is designed to interface High Speed Communications Lines using Asynchronous, IBM Bisync, and SDLC/HDLC protocol to Intel microcomputer systems. It can be interfaced with Intel's MCS-48, -85, -51; iAPX-86, -88, -186 and -188 families, the 8237 DMA controller, or the 8089 I/O processor in polled, interrupt driven, or DMA driven modes of operation.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# 8274 MULTI-PROTOCOL SERIAL CONTROLLER (MPSC)

- Asynchronous, Byte Synchronous and Bit Synchronous Operation

- Two Independent Full Duplex Transmitters and Receivers

- Fully Compatible with 8048, 8051, 8085, 8088, 8086, 80188 and 80186 CPU's; 8257 and 8237 DMA Controllers; and 8089 I/O Proc.

- 4 Independent DMA Channels

- Baud Rate: DC to 880K Baud

- **■** Asynchronous:

- 5-8 Bit Character; Odd, Even, or No Parity; 1, 1.5 or 2 Stop Bits

- Error Detection: Framing, Overrun, and Parity

- **■** Byte Synchronous:

- Character Synchronization, Int. or Ext.

- One or Two Sync Characters

- Automatic CRC Generation and Checking (CRC-16)

- IBM Bisync Compatible

- **■** Bit Synchronous:

- SDLC/HDLC Flag Generation and Recognition

- 8 Bit Address Recognition

- Automatic Zero Bit Insertion and Deletion

- Automatic CRC Generation and Checking (CCITT-16)

- CCITT X.25 Compatible

- Available in EXPRESS and Military

The Intel 8274 Multi-Protocol Series Controller (MPSC) is designed to interface High Speed Communications Lines using Asynchronous, IBM Bisync, and SDLC/HDLC protocol to Intel microcomputer systems. It can be interfaced with Intel's MCS-48, -85, -51; iAPX-86, -88, -186 and -188 families, the 8237 DMA Controller, or the 8089 I/O Processor in polled, interrupt driven, or DMA driven modes of operation.

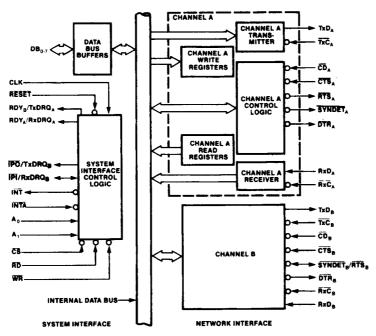

The MPSC is a 40 pin device fabricated using Intel's High Performance HMOS TeFnology.

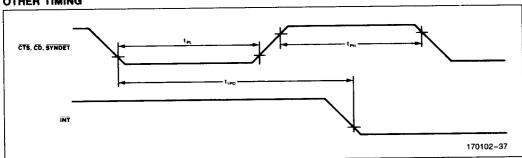

Figure 1. Block Diagram

September 1992 Order Number: 170102-003

170102-1

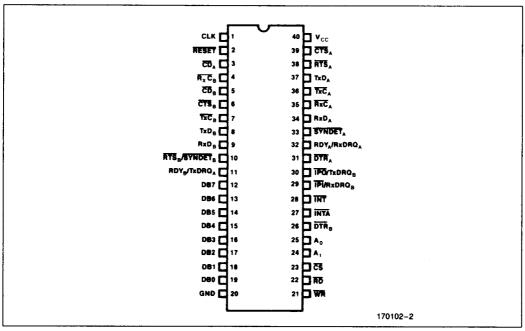

Figure 2. 8274 Pin Configuration (PDIP)

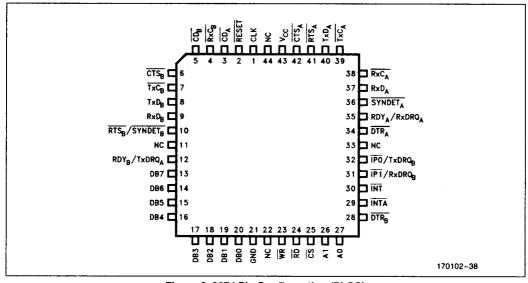

Figure 3. 8274 Pin Configuration (PLCC)

**Table 1. Pin Description**

|                                          | fable 1. Pin Description |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|------------------------------------------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol                                   | Pin<br>No.               | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| CLK                                      | 1                        |      | CLOCK: System clock, TTL compatible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| RESET                                    | 2                        | 1    | <b>RESET:</b> A low signal on this pin will force the MPSC to an idle state. $TxD_A$ and $TxD_B$ are forced high. The modem interface output signals are forced high. The MPSC will remain idle until the control registers are initialized. Reset must be true for one complete CLK cycle.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| CDA                                      | 3                        | l    | <b>CARRIER DETECT (CHANNEL A):</b> This interface signal is supplied by the modem to indicate that a data carrier signal has been detected and that a valid data signal is present on the $RxD_A$ line. If the auto enable control is set the 8274 will not enable the serial receiver until $\overline{CD}_A$ has been activated.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| RxC <sub>B</sub>                         | 4                        | 1    | RECEIVE CLOCK (CHANNEL B): The serial data are shifted into the Receive Data input (RxD <sub>B</sub> ) on the rising edge of the Receive Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| CD <sub>B</sub>                          | 5                        | l    | CARRIER DETECT (CHANNEL B): This interface signal is supplied by the modem to indicated that a data carrier signal has been detected and that a valid data signal is present on the RxD <sub>B</sub> line. If the auto enable control is set the 8274 will not enable the serial receiver until CD <sub>B</sub> has been activated.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| CTS <sub>B</sub>                         | 6                        | 1    | CLEAR TO SEND (CHANNEL B): This interface signal is supplied by the modern in response to an active RTS signal. CTS indicates that the data terminal/computer equipment is permitted to transmit data. In addition, if the auto enable control is set, the 8274 will not transmit data bytes until CTS has been activated.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| TxC <sub>B</sub>                         | 7                        | ı    | TRANSMIT CLOCK (CHANNEL B): The serial data are shifted out from the Transmit Data output (TxDB) on the falling edge of the Transmit Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| TxD <sub>B</sub>                         | 8                        | 0    | TRANSMIT DATA (CHANNEL B): This pin transmits serial data to the communications channel (Channel B).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| RxD <sub>B</sub>                         | 9                        | ı    | RECEIVE DATA (CHANNEL B): This pin receives serial data from the communications channel (Channel B).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| SYNDET <sub>B</sub><br>7RTS <sub>B</sub> |                          | 1/0  | SYNCHRONOUS DETECTION (CHANNEL B): This pin is used in byte synchronous mode as either an internal sync detect (output) or as a means to force external synchronization (input). In SDLC mode, this pin is an output indicating Flag detection. In asynchronous mode it is a general purpose input (Channel B).  REQUEST TO SEND (CHANNEL B): General purpose output, generally used to signal that Channel B is ready to send data. When the RTS bit is reset in asynchronous mode, the signal does not go inactive (High) until the transmitter is empty.  SYNDETB or RTSB selection is done by WR2; D7. (Channel A). |  |  |  |  |  |  |  |

Table 1. Pin Description (Continued)

| Symbol                                   | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                         |

|------------------------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY <sub>B</sub> /<br>TxDRQ <sub>A</sub> | 11         | 0    | READY (CHANNEL B)/TRANSMITTER DMA REQUEST (CHANNEL A): In mode 0 this pin is RDY <sub>B</sub> and is used to synchronize data transfers between the processor and the MPSC (Channel B). In modes 1 and 2 this pin is TxDRQ <sub>A</sub> and is used by the Channel A transmitter to request a DMA transfer.               |

| DB7                                      | 12         | 1/0  | DATA BUS: The Data Bus lines are bidirectional three state lines which interface with the system's Data Bus.                                                                                                                                                                                                              |

| DB6                                      | 13         |      |                                                                                                                                                                                                                                                                                                                           |

| DB5                                      | 14         |      |                                                                                                                                                                                                                                                                                                                           |

| DB4                                      | 15         |      |                                                                                                                                                                                                                                                                                                                           |

| DB3                                      | 16         |      |                                                                                                                                                                                                                                                                                                                           |

| DB2                                      | 17         |      |                                                                                                                                                                                                                                                                                                                           |

| DB1                                      | 18         |      |                                                                                                                                                                                                                                                                                                                           |

| DB0                                      | 19         |      |                                                                                                                                                                                                                                                                                                                           |

| GND                                      | 20         |      | GROUND.                                                                                                                                                                                                                                                                                                                   |

| V <sub>CC</sub>                          | 40         |      | POWER: +5V Supply                                                                                                                                                                                                                                                                                                         |

| CTSA                                     | 39         |      | CLEAR TO SEND (CHANNEL A): This interface signal is supplied by the Modem in response to an active RTS signal. CTS indicates that the data terminal/computer equipment is permitted to transmit data. In addition, if the auto enable control is set, the 8274 will not transmit data bytes until CTS has been activated. |

| RTSA                                     | 38         | 0    | REQUEST TO SEND (CHANNEL A): General purpose output commonly used to signal that Channel A is ready to send data. When the RTS bit is reset in asynchronous mode, the signal does not go inactive (High) until the transmitter is empty.                                                                                  |

| TxD <sub>A</sub>                         | 37         | 0    | TRANSMIT DATA (CHANNEL A): This pin transmits serial data to the commmunications channel (Channel A).                                                                                                                                                                                                                     |

| TxC <sub>A</sub>                         | 36         | I    | TRANSMIT CLOCK (CHANNEL A): The serial data are shifted out from the Transmit Data output (TxD <sub>A</sub> ) on the falling edge of the Transmit Clock.                                                                                                                                                                  |

| RxC <sub>A</sub>                         | 35         |      | RECEIVE CLOCK (CHANNEL A): The serial data are shifted into the Receive Data input (RxD <sub>A</sub> ) on the rising edge of the Receive Clock.                                                                                                                                                                           |

| RxD <sub>A</sub>                         | 34         | l .  | RECEIVE DATA (CHANNEL A): This pin receives serial data from the communications channel (Channel A).                                                                                                                                                                                                                      |

| SYNDETA                                  | 33         | 1/0  | SYNCHRONOUS DETECTION (CHANNEL A): This pin is used in byte synchronous mode as either an internal sync detect (output) or as a means to force external synchronization (input). In SDLC mode, this pin is an output indicating flag detection. In asynchronous mode it is a general purpose input (Channel A).           |

Table 1. Pin Description (Continued)

| Symbol                                   | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY <sub>A</sub> /<br>RxDRQ <sub>A</sub> | 32         | 0    | READY: In mode 0 this pin is RDY <sub>A</sub> and is used to synchronize data transfers between the processor and the MPSC (Channel A). In modes 1 and 2 this pin is RxDRQ <sub>A</sub> and is used by the channel A receiver to request a DMA transfer.                                                                                                                                          |

| DTR <sub>A</sub>                         | 31         | 0    | DATA TERMINAL READY (CHANNEL A): General purpose output.                                                                                                                                                                                                                                                                                                                                          |

| iPO/<br>TxDRQ <sub>B</sub>               | 30         | 0    | INTERRUPT PRIORITY OUT/TRANSMITTER DMA REQUEST (CHANNEL B): In modes 0 and 1, this pin is Interrupt Priority Out. It is used to establish a hardware interrupt priority scheme with IPI. It is low only if IPI is low and the controlling processor is not servicing an interrupt from this MPSC. In mode 2 it is TxDRQB and is used to request a DMA cycle for a transmit operation (Channel B). |

| īPī/<br>RxDRQ <sub>B</sub>               | 29         | 1/0  | INTERRUPT PRIORITY IN/RECEIVER DMA REQUEST (CHANNEL B): In modes 0 and 1,  P  is Interrupt Priority In. A low on  P  means that no higher priority device is being serviced by the controlling processor's interrupt service routine. In mode 2 this pin is RxDRQ <sub>B</sub> and is used to request a DMA cycle for a receive operation (Channel B).                                            |

| INT                                      | 28         | 0    | INTERRUPT: The interrupt signal indicates that the highest priority internal interrupt requires service (open collector). Priority can be resolved via an external interrupt controller or a daisy-chain scheme.                                                                                                                                                                                  |

| INTA                                     | 27         | ı    | INTERRUPT ACKNOWLEDGE: This Interrupt Acknowledge signal allows the highest priority interrupting device to generate an interrupt vector. This pin must be pulled high (inactive) in non-vector mode.                                                                                                                                                                                             |

| DTR <sub>B</sub>                         | 26         | 0    | DATA TERMINAL READY (CHANNEL B): This is a general purpose output.                                                                                                                                                                                                                                                                                                                                |

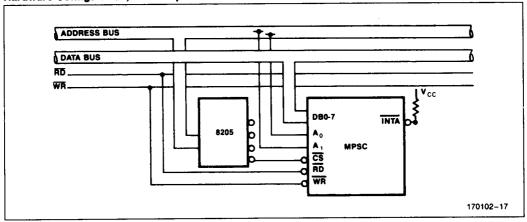

| A <sub>0</sub>                           | 25         | I    | ADDRESS: This line selects Channel A or B during data or command transfers. A low selects Channel A.                                                                                                                                                                                                                                                                                              |

| A <sub>1</sub>                           | 24         | I    | ADDRESS: This line selects between data or command information transfer. A low means data.                                                                                                                                                                                                                                                                                                        |

| CS                                       | 23         | l    | CHIP SELECT: This signal selects the MSPC and enables reading from or writing into registers.                                                                                                                                                                                                                                                                                                     |

| RD                                       | 22         | I    | READ: Read controls a data byte or status byte transfer from the MPSC to the CPU.                                                                                                                                                                                                                                                                                                                 |

| WR                                       | 21         | I    | WRITE: Write controls transfer of data or commands to the MPSC.                                                                                                                                                                                                                                                                                                                                   |

### RESET

When the 8274 RESET line is activitated, both MPSC channels enter the idle state. The serial output lines are forced to the marking state (high) and the modem interface signals (RTS, DTR) are forced high. In addition, the pointers registers are set to zero.

### **GENERAL DESCRIPTION**

The Intel 8274 Multi-Protocol Serial Controller is a microcomputer peripheral device which supports Asynchronous, Byte Synchronous (Monosync, IBM Bisync), and Bit Synchronous (ISO's HDLC, IBM's SDLC) protocols. This controller's flexible architecture allows easy implementation of many variations of these three protocols with low software and hardware overhead.

The Multi-Protocol Serial controller (MPSC) implements two independent serial receiver/transmitter channels.

The MPSC supports several microprocessor interface options: Polled, Wait, Interrupt driven and DMA driven. The MPSC is designed to support INTEL's MCS-85 and iAPX 86, 88, 186, 188 families.

### **FUNCTIONAL DESCRIPTION**

Additional information on Asynchronous and Synchronous Communications with the 8274 is available respectively in the Applications Notes AP 134 and AP 145.

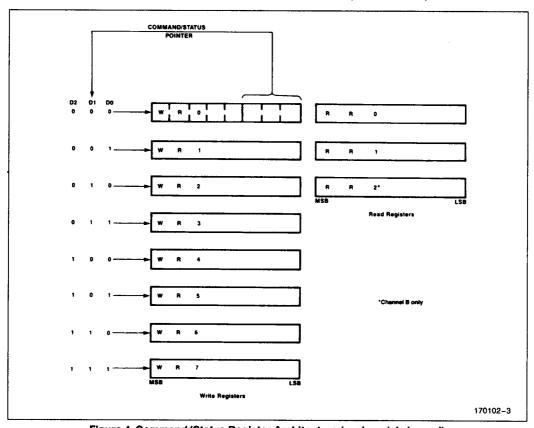

Command, parameter, and status information is stored in 21 registers within the MPSC (8 writable registers for each channel, 2 readable registers for Channel A and 3 readable registers for Channel B).

In the following discussion, the writable registers will be referred to as WRO through WR7 and the readable registers will be referred to as RRO through RR2.

This section of the data sheet describes how the Asynchronous and Synchronous protocols are implemented in the MPSC. It describes general considerations, transmit operation, and receive operation for Asynchronous, Byte Synchronous, and Bit Synchronous protocols.

### **ASYNCHRONOUS OPERATIONS**

### Transmitter/Receiver Initialization

(See Detailed Command Description Section for complete information)

In order to operate in asynchronous mode, each MPSC channel must be initialized with the following information:

- Transmit/Receive Clock Rate. This parameter is specified by bits 6 and 7 of WR4. The clock rate may be set to 1, 16, 32, or 64 times the data-link bit rate. If the X1 clock mode is selected, the bit synchronization must be accomplished externally.

- Number of Stop Bits. This parameter is specified by bits 2 and 3 of WR4. The number of stop bits may be set to 1, 1½, or 2.

- Parity Selection. Parity may be set for odd, even, or no parity by bits 0 and 1 of WR4.

- Receiver Character Length. This parameter sets the length of received characters to 5, 6, 7, or 8 bits. This parameter is specified by bits 6 and 7 of WR3.

- Receiver Enable. The serial-channel receiver operation may be enabled or disabled by setting or clearing bit 0 of WR3.

- 6. Transmitter Character Length. This parameter sets the length of transmitted characters to 5, 6, 7, or 8 bits. This parameter is specified by bits 5 and 6 of WR5. Characters of less than 5 bits in length may be transmitted by setting the transmitted length to five bits (set bits 5 and 6 of WR5 to 0).

The MPSC then determines the actual number of bits to be transmitted from the character data byte. The bits to be transmitted must be right justified in the data byte, the next three bits must be set to 0 and all remaining bits must be set to 1. The following table illustrates the data formats for transmission of 1 to 5 bits of data.

|    |    | Ву | te V | Number of<br>Bits Transmitted |    |    |    |                    |

|----|----|----|------|-------------------------------|----|----|----|--------------------|

| D7 | D6 | D5 | D4   | D3                            | D2 | D1 | D0 | (Character Length) |

| 1  | 1  | 1  | 1    | 0                             | 0  | 0  | С  | 1                  |

| 1  | 1  | 1  | 0    | 0                             | 0  | С  | С  | 2                  |

| 1  | 1  | 0  | 0    | 0                             | С  | С  | С  | 3                  |

| 1  | 0  | 0  | 0    | С                             | С  | С  | С  | 4                  |

| 0  | 0  | 0  | С    | С                             | С  | С  | С  | 5                  |

- Transmitter Enable. The serial channel transmitter operation may be enabled or disabled by setting or clearing bit 3 of WR5.

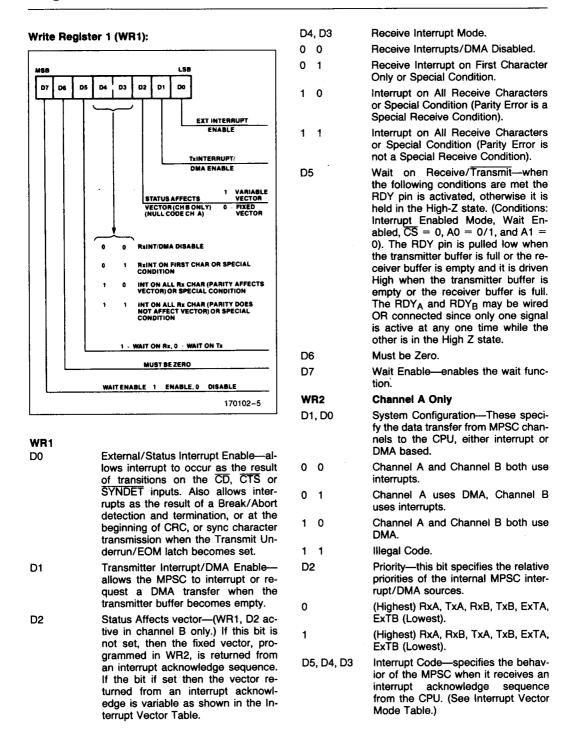

- 8. Interrupt Mode. Specified by bits 3 and 4 of WR1.

For data transmission via a modem or RS-232-C interface, the following information must also be specified:

- The Request To Send (RTS) (WR5; D1) and Data Terminal Ready (DTR) (WR5; D7) bits must be set along with the Transmit Enable bit (WR5; D3).

- 2. Auto Enable may be set to allow the MPSC to automatically enable the channel transmitter when the clear-to-send signal is active and to automatically enable the receiver when the carrierdetect signal is active. However, the Transmit Enable bit (WR3; D3) and Receive Enable bit (WR3; D1) must be set in order to use the Auto Enable mode. Auto Enable is controlled by bit 5 of WR3.

When loading Initialization parameters into the MPSC, WR4 information must be written before the WR1, WR3, WR5 parameters commands.

During initialization, it is desirable to guarantee that the external/status latches reflect the latest interface information. Since up to two state changes are internally stored by the MPSC, at least two Reset External/Status Interrupt commands must be issued. This procedure is most easily accomplished by simply issuing this reset command whenever the pointer register is set during initialization.

An MPSC initialization procedure (MPSC\$RX\$INIT) for asynchronous communication is listed in Intel Application Note AP 134.

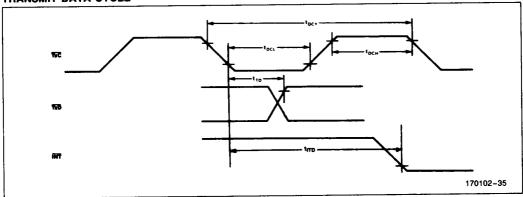

### TRANSMIT

The transmit function begins when the Transmit Enable bit (WR5; D3) is set. The MPSC automatically adds the start bit, the programmed parity bit (odd, even or no parity) and the programmed number of stop bits (1, 1.5 or 2 bits) to the data character being transmitted. 1.5 stop bits option must be used with X16, X32 or X64 clock options only. The data character is transmitted least significant bit first.

The serial data are shifted out from the Transmit Data (TxD) output on the falling edge of the Transmit Clock (TxC) input at a rate programmable to 1, 1/16th, 1/32nd, or 1/64th of the clock rate supplied to the TxC input.

The TxD output is held high when the transmitter has no data to send, unless, under program control, the Send Break (WR5; D4) command is issued to hold the TxD low.

If the External/Status Interrupt bit (WR1; D0) is set, the status of CD, CTS and SYNDET are monitored and, if any changes occur for a period of time greater than the minimum specified pulse width, an interrupt is generated. CTS is usually monitored using this interrupt feature (e.g., Auto Enable option).

The Transmit Buffer Empty bit (RRO; D2) is set by the MPSC when the data byte from the buffer is loaded in the transmit shift register. Data should be written to the MPSC only when the Tx buffer becomes empty to prevent overwriting.

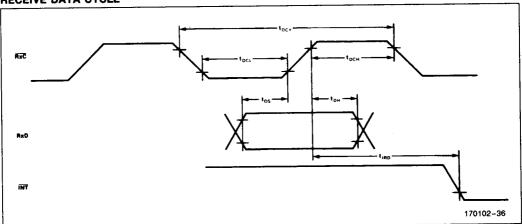

### Receive

The receive function begins when the Receive Enable (WR3; D0) bit is set. If the Auto Enable (WR3; D5) option is selected, then Carrier Detect (CD) must also be low. A valid start bit is detected if a low persists for at least ½ bit time on the Receive Data (RxD) input.

The data is sampled at mid-bit time, on the rising edge of RxC, until the entire character is assembled. The receiver inserts 1's when a character is less than 8 bits. If parity (WR4; D0) is enabled and the character is less than 8 bits the parity bit is not stripped from the character.

### **Error Reporting**

The receiver also stores error status for each of the 3 data characters in the data buffer. Three error conditions may be encountered during data reception in the asynchronous mode:

- Parity. If parity bits are computed and transmitted with each character and the MPSC is set to check parity (bit 0 in WR4 is set), a parity error will occur whenever the number of "1" bits within the character (including the parity bit) does not match the odd/even setting of the parity check flag (bit 1 in WR4). When a parity error is detected, the parity error flag (RR1; D4) is set and remains set until it is reset by the Error Reset command (WR0; D5, D4, D3).

- 2. Framing. A framing error will occur if a stop bit is not detected immediately following the parity bit (if parity checking is enabled) or immediately following the most-significant data bit (if parity checking is not enabled). When a Framing Error is detected, the Framing Error bit (RR1; D6) is set and remains set until reset by the Error Reset Command (WR0; D5, D4, D3). The detection of a Framing Error adds an additional ½ bit time to the character time so the Framing Error is not interpreted as a new start bit.

- 3. Overrun. If the CPU fails to read a data character while more than three characters have been received, the Receive Overrun bit (RR1; D5) is set. When this occurs, the fourth character assembled replaces the third character in the receive buffers. Only the overwritten character is flagged with the Receive Overrun bit. The Receive Overrun bit (RR1; D5) is reset by the Error Reset command (WR0; D5, D4, D3).

### **External/Status Latches**

The MPSC continuously monitors the state of five external/status conditions:

- CTS—clear-to-send input pin.

- CD—carrier-detect input pin.

- SYNDET—sync-detect input pin. This pin may be used as a general-purpose input in the asynchronous communication mode.

- BREAK—a break condition (series of space bits on the receiver input pin).

- TxUNDERRUN/EOM—Transmitter Underrun/ End of Message.

A change of state in any of these monitored conditions will cause the associated status bit in RR0 to be latched (and optionally cause an interrupt).

If the External/Status Interrupt bit (WR1; D0) is enabled, Break Detect (RR0; D7) and Carrier Detect (RR0; D3) will cause an interrupt. Reset Ex-

ternal/Status interrupts (WR0; D5, D4, D3) will clear Break Detect and Carrier Detect bits if they are set.

Command, parameter, and status information is stored in 21 registers within the MPSC (8 writable registers for each channel, 2 readable registers for Channel A and 3 readable registers for Channel B). They are all accessed via the command ports.

An internal pointer register selects which of the command or status registers will be read or written during a commmand/status access of an MPSC channel.

After reset, the contents of the pointer registers are zero. The first write to a command register causes the data to be loaded into Write Register 0 (WR0). The three least significant bits of WR0 are loaded into the Command/Status Pointer. The next read or write operation accesses the read or write register selected by the pointer. The pointer is reset after the read or write operation is completed.

Figure 4. Command/Status Register Architecture (each serial channel)

### Asynchronous Mode Register Setup

|     | D7 D6                                                       |                                                                        | D5             | D4 | D3                                                 | D2 | D1                     | D0               |

|-----|-------------------------------------------------------------|------------------------------------------------------------------------|----------------|----|----------------------------------------------------|----|------------------------|------------------|

| WR3 | 01 Rx 7<br>10 Tx 6                                          | b/char<br>b/char<br>b/char<br>b/char                                   | AUTO<br>ENABLE | 0  | 0                                                  | 0  | 0                      | Rx<br>ENABLE     |

| WR4 | 00 X1 Clock<br>01 X16 Clock<br>10 X32 Clock<br>11 X64 Clock |                                                                        | 0              | 0  | 01 1 STOP BIT<br>10 1½ STOP BITS<br>11 2 STOP BITS |    | EVEN/<br>ODD<br>PARITY | PARITY<br>ENABLE |

| WR5 | DTR                                                         | 00 Tx ≤ 5 b/char<br>01 Tx 7 b/char<br>10 Tx 6 b/char<br>11 Tx 8 b/char |                |    | Tx<br>ENABLE                                       | 0  | RTS                    | 0                |

# SYNCHRONOUS OPERATION—MONOSYNC, BISYNC

### General

The MPSC must be initialized with the following parameters: odd or even parity (WR4; D1, D0), X1 clock mode (WR4; D7, D6), 8- or 16-bit sync character (WR4; D5, D4), CRC polynomial (WR5; D2), Transmitter Enable (WR5; D3), interrupt modes (WR1, WR2), transmit character length (WR5; D6, D5) and receive character length (WR3; D7, D6). WR4 parameters must be written before WR1, WR3, WR5, WR6 and WR7.

The data is transmitted on the falling edge of the Transmit Clock, (TxC) and is received on the rising edge of Receive Clock (RxC). The X1 clock is used for both transmit and receive operations for all three sync modes: Mono, Bi and External.

### Transmit Set-Up-Monosync, Bisync

Transmit data is held high after channel reset, or if the transmitter is not enabled. A break may be programmed to generate a spacing line that begins as soon as the Send Break (WR5; D4) bit is set. With the transmitter fully initialized and enabled, the default condition is continuous transmission of the 8- or 16-bit sync character.

Using interrupts for data transfer requires that the Transmit Interrupt/DMA Enable bit (WR1; D1) be set. An interrupt is generated each time the transmit buffer becomes empty. The interrupt can be satisfied either by writing another character into the transmitter or by resetting the Transmitter Interrupt/DMA Pending latch with a Reset Transmitter Interventy.

### Synchronous Mode Register Setup-Monosync, Bisync

|     | D7                                                                   | D6 | D5                                             | D4                                      | D3 | D2                       | D1                              | D0               |

|-----|----------------------------------------------------------------------|----|------------------------------------------------|-----------------------------------------|----|--------------------------|---------------------------------|------------------|

| WR3 | 00 Rx 5 b/char<br>01 Rx 7 b/char<br>10 Tx 6 b/char<br>11 Rx 8 b/char |    | AUTO<br>ENABLE                                 | THINI I                                 |    | 0                        | SYNC<br>CHAR<br>LOAD<br>INHIBIT | Rx<br>ENABLE     |

| WR4 | 0                                                                    | 0  | 00 8 bit S<br>01 16 bit<br>11 Ext Sy           | Sync                                    | 0  | 0                        | EVEN/<br>ODD<br>PARITY          | PARITY<br>ENABLE |

| WR5 | DTR 01 Tx 7                                                          |    | ≤ 5 b/char<br>7 b/char<br>6 b/char<br>3 b/char | 5 b/char<br>o/char SEND<br>o/char BREAK |    | 1<br>(SELECTS<br>CRC-16) | RTS                             | Tx CRC<br>ENABLE |

rupt/DMA Pending Command (WR0; D5, D4, D3). If nothing more is written into the transmitter, there can be no further Transmit Buffer Empty interrupt, but this situation does cause a Transmit Underrun condition (RR0; D6).

Data Transfers using the RDY signal are for software controlled data transfers such as block moves. RDY tells the CPU that the MPSC is not ready to accept/provide data and that the CPU must extend the output/input cycle. DMA data transfers use the TxDRQ A/B signals which indicate that the transmit buffer is empty, and that the MPSC is ready to accept the next data character. If the data character is not loaded into the MPSC by the time the transmit shift register is empty, the MPSC enters the Transmit Underrun condition.

The MPSC has two programmable options for solving the transmit underrun condition: it can insert sync characters, or it can send the CRC characters generated so far, followed by sync characters. Folowing a chip or channel reset, the Transmit Underrun/EOM status bit (RR0; D6) is in a set condition allowing the insertion of sync characters when there is no data to send. The CRC is not calculated on these automatically inserted sync characters. When the CPU detects the end message, a Reset Transmit Underrun/EOM command can be issued. This allows CRC to be sent when the transmitter has no data to send.

In the case of sync insertion, an interrupt is generated only after the first automatically inserted sync character has been loaded in the Transmit Shift Register. The status register indicates the Transmit Underrun/EOM bit and the Transmit Buffer Empty bit are set.

In the case of CRC insertion, the Transmit Underrun/EOM bit is set and the Transmit Buffer Empty bit is reset while CRC is being sent. When CRC has been completely sent, the Transmit Buffer Empty status bit is set and an interrupt is generated to indicate to the CPU that another message can begin (this interrupt occurs because CRC has been sent and sync has been loaded into the Tx Shift Register). If no more messages are to be sent, the program can terminate transmission by resetting RTS, and disabling the transmitter (WR5; D3).

Bisync CRC Generation. Setting the Transmit CRC enable bit (WR5; D0) indicates CRC accumulation when the program sends the first data character to the MPSC. Although the MPSC automatically transmits up to two sync characters (16 bit sync), it is wise to send a few more sync characters ahead of the message (before enabling Transmit CRC) to ensure synchronization at the receiving end.

The Transmit CRC Enable bit can be changed on the fly any time in the message to include or exclude a particular data character from CRC accumulation. The Transmit CRC Enable bit should be in the desired state when the data character is loaded into the transmit shift register. To ensure this bit in the proper state, the Transmit CRC Enable bit must be issued before sending the data character to the MPSC.

Transmit Transparent Mode. Transparent mode (Bisync protocol) operation is made possible by the ability to change Transmit CRC Enable on the fly and by the additional capability of inserting 16 bit sync characters. Exclusion of DLE characters from CRC calculation can be achieved by disabling CRC calculation immediately preceding the DLE character transfer to the MPSC.

In the transmit mode, the transmitter always sends the programmed number of sync bits (8 or 16) (WR4; D5, D4). When in the Monosync mode, the transmitter sends from WR6 and the receiver compares against WR7. One or two CRC polynomials, CRC 16 or SDLC, may be used with synchronous modes. In the transmit initialization process, the CRC generator is initialized by setting the Reset Transmit CRC Generator command (WR0; D7, D6).

The External/Status interrupt (WR1; D0) mode can be used to monitor the status of the CTS input as well as the Transmit Underrun/EOM latch. Optionally, the Auto Enable (WR3; D5) feature can be used to enable the transmitter when CTS is active. The first data transfer to the MPSC can begin when the External/Status interrupt (CTS (RR0; D5) status bit set) occurs following the Transmit Enable command (WR5; D3).

### Receive

After a channel reset, the receiver is in the Hunt phase, during which the MPSC looks for character synchronization. The Hunt begins only when the receiver is enabled and data transfer begins only when character synchronization has been achieved. If character synchronization is lost, the hunt phase can be re-entered by writing the Enter Hunt Phase (WR3; D4) bit. The assembly of received data continues until the MPSC is reset or until the receiver is disabled (by command or by CD while in the Auto Enables mode) or until the CPU sets the Enter Hunt Phase bit. Under program control, all the leading sync characters of the message can be inhibited from loading the receive buffers by setting the Sync Character Load Inhibit (WR3; D1) bit. After character synchronization is achieved the assembled characters are transferred to the receive data FIFO. After receiving the first data character, the Sync Character Load Inhibit bit should be reset to zero so that all characters are received, including the sync characters. This is important because the received CRC may look like a sync character and not get received.

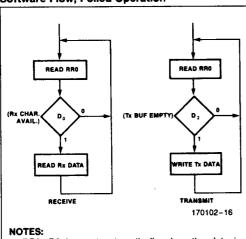

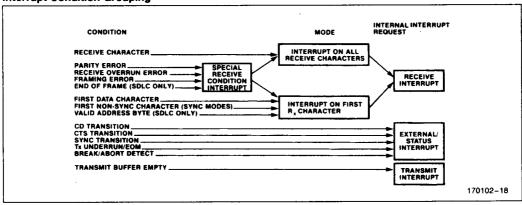

Data may be transferred with or without interrupts. Transferring data without interrupts is used for a purely polled operation or for off-line conditions. There are two interrupt modes available for data transfer: Interrupt on First Character Only and Interrupt on Every Character.

Interrupt on First Character Only mode is normally used to start a polling loop, a block transfer sequence using RDY to synchronize the CPU to the incoming data rate, or a DMA transfer using the RxDRQ signal. The MPSC interrupts on the first character and thereafter only interrupts after a Special Receive Condition is detected. This mode can be reinitialized using the Enable Interrupt On Next Receive Character (WR0; D5, D4, D3) command which allows the next character received to generate an interrupt. Parity Errors do not cause interrupts, but End of Frame (SDLC operation) and Receive Overrun do cause interrupts in this mode. If the external status interrupts (WR1; D0) are enabled an interrupt may be generated any time the CD changes state.

Interrupt On Every Character mode generates an interrupt whenever a character enters the receive buffer. Errors and Special Receive Conditions generate a special vector if the Status Affects Vector (WR1B; D2) is selected. Also the Parity Error may be programmed (WR1; D4, D3) not to generate the special vector while in the Interrupt On Every Character mode.

The Special Receive Condition interrupt can only occur while in the Receive Interrupt On First Character Only or the Interrupt On Every Receive Character modes. The Special Receive Condition interrupt is caused by the Receive Overrun (RR1; D5) error condition. The error status reflects an error in the current word in the receive buffer, in addition to any Parity or Overrun errors since the last Error Reset (WR0; D5, D4, D3). The Receive Overrun and Parity error status bits are latched and can only be reset by the Error Reset (WR0; D5, D4, D3) command.

The CRC check result may be obtained by checking for CRC bit (RR1; D6). This bit gives the valid CRC result 16 bit times after the second CRC byte has been read from the MPSC. After reading the second CRC byte, the user software must read two more characters (may be sync characters) before checking for CRC result in RR1. Also for proper CRC computation by the receiver, the user software must reset the Receive CRC Checker (WR0; D7, D6) after receiving the first valid data character. The receive CRC Enable bit (WR3; D3) may also be enabled at this time.

### SYNCHRONOUS OPERATION—SDLC

### General

Like the other synchronous operations the SDLC mode must be initialized with the following parameters: SDLC mode (WR4; D5, D4), SDLC polynomial (WR5; D2), Request to Send, Data Terminal Ready, transmit character length (WR5; D6, D5), interrupt modes (WR1; WR2), Transmit Enable (WR5; D3), Receive Enable (WR3; D0), Auto Enable (WR3; D5) and External/Status Interrupt (WR1; D0). WR4 parameters must be written before WR1, WR3, WR5, WR6 and WR7.

The Interrupt modes for SDLC operation are similar to those discussed previously in the synchronous operations section.

### Synchronous Mode Register Setup—SDLC/HDLC

|     | <b>D</b> 7                                                           | D6                                                                     | D5                                                            | D4                        | D3                  | D2                                 | D1  | D0                  |  |

|-----|----------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|---------------------|------------------------------------|-----|---------------------|--|

| WR3 | 00 Rx 5 b/char<br>01 Rx 7 b/char<br>10 Rx 6 b/char<br>11 Rx 8 b/char |                                                                        | 01 Rx 7 b/char AUTO HUNT CRC 10 Rx 6 b/char ENABLES MODE ENAB |                           | Rx<br>CRC<br>ENABLE | ADDRESS<br>SEARCH<br>MODE          | 0   | Rx                  |  |

| WR4 | 0                                                                    | 0                                                                      | ,                                                             | 0<br>CTS SDLC/<br>C MODE) | 0                   | 0                                  | 0   | 0                   |  |

| WR5 | DTR                                                                  | 00 Tx ≤ 5 b/char<br>01 Tx 7 b/char<br>10 Tx 6 b/char<br>11 Tx 8 b/char |                                                               | SEND<br>BREAK             | Tx<br>ENABLE        | 0<br>(SELECTS<br>SDLC/HDLC<br>CRC) | RTS | Tx<br>CRC<br>ENABLE |  |

### **Transmit**

After a channel reset, the MPSC begins sending SDLC flags.

Following the flags in an SDLC operation the 8-bit address field, control field and information field may be sent to the MPSC by the microprocessor. The MPSC transmits the Frame Check Sequence using the Transmit Underrun feature. The MPSC automatically inserts a zero after every sequence of 5 consecutive 1's except when transmitting Flags or Aborts.

SDLC—like protocols do not have provision for fill characters within a message. The MPSC therefore automatically terminates an SDLC frame when the transmit data buffer and output shift register have no more bits to send. It does this by sending the two bytes of CRC and then one or more flags. This allows very high-speed transmissions under DMA or CPU control without requiring the CPU to respond quickly to the end-of-message situation.

After a reset, the Transmit Underrun/EOM status bit is in the set state and prevents the insertion of CRC characters during the time there is no data to send. Flag characters are sent. The MPSC begins to send the frame when data is written into the transmit buffer. Between, the time the first data byte is written, and the end of the message, the Reset Transmit Underrun/EOM (WR0; D7, D6) command must be issued. The Transmit Underrun/EOM status bit (RR0; D6) is in the reset state at the end of the message which automatically sends the CRC characters.

The MPSC may be programmed to issue a Send Abort command (WR0; D5, D4, D3). This command causes at least eight 1's but less than fourteen 1's to be sent before the line reverts to continuous flags.

### Receive

After initialization, the MPSC enters the Hunt phase, and remains in the Hunt phase until the first Flag is received. The MPSC never again enters the Hunt phase unless the microprocessor writes the Enter Hunt command. The MPSC will also detect flags separated by a single zero. For example, the bit pattern 0111111011111110 will be detected as two flags.

The MPSC can be programmed to receive all frames or it can be programmed to the Address Search Mode. In the Address Search Mode, only frames with addresses that match the value in WR6 or the global address (0FFH) are received by the MPSC. Extended address recognition must be done by the microprocessor software.

The control and information fields are received as data.

SDLC/HDLC CRC calculation does not have an 8bit delay, since all characters are included in the calculation, unlike Byte Synchronous Protocols.

Reception of an abort sequence (7 or more 1's) will cause the Break/Abort bit (RR0; D7) to be set and will cause an External/Status interrupt, if enabled. After the Reset External/Status Interrupts Command has been issued, a second interrupt will occur at the end of the abort sequence.

### **MPSC**

### **Detailed Command/Status Description**

### **GENERAL**

The MPSC supports an extremely flexible set of serial and system interface modes.

The system interface to the CPU consists of 8 ports or buffers:

| cs | A <sub>1</sub> | A <sub>0</sub> | Read Operation    | Write Operation         |

|----|----------------|----------------|-------------------|-------------------------|

| 0  | 0              | 0              | Ch. A Data Read   | Ch. A Data Write        |

| 0  | 1              | 0              | Ch. A Status Read | Ch. A Command/Parameter |

| 0  | 0              | 1              | Ch. B Data Read   | Ch. B Data Write        |

| 0  | 1              |                |                   | Ch. B Command/Parameter |

| 1  | Х              | Х              | High Impedance    | High Impedance          |

Data buffers are addressed by  $A_1 = 0$ , and Command ports are addressed by  $A_1 = 1$ .

### **COMMAND/STATUS DESCRIPTION**

The following command and status bytes are used during initialization and execution phases of operation. All Command/Status operations on the two channels are identical, and independent, except where noted.

### **Detailed Register Description**

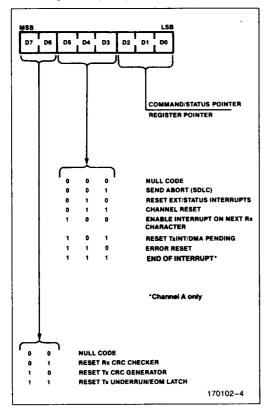

### Write Register 0 (WR0):

### WR0

D2, D1, D0—Command/Status Register Pointer bits determine which write-register the next byte is to be written into, or which read-register the next byte is to be read from. After reset, the first byte written into either channel goes into WR0. Following a read or write to any register (except WR0) the pointer will point to WR0.

D5, D4, D3—Command bits determine which of the basic seven commands are to be performed.

Command 0 Null—has no effect.

Command 1 Send Abort—causes the generation of eight to thirteen 1's when in the SDLC mode.

Command 2 Reset External/Status Interrupts—

resets the latched status bits of RR0

and re-enables them, allowing interrupts to occur again.

Command 3 Channel Reset—resets the Latched Status bits of RR0, the interrupt prioritization logic and all control registers for the channel. Four extra system clock cycles should be allowed for MPSC reset time before any additional commands or controls are written into the channel.

Command 4 Enable Interrupt on Next Receive Character—if the Interrupt on First Receive Character mode is selected, this command reactivates that mode after each complete message is received to prepare the MPSC for the next message.

Command 5 Reset Transmitter Interrupt/DMA

Pending—if The Transmit Interrupt/

DMA Enable mode is selected, the

MPSC automatically interrupts or requests DMA data transfer when the

transmit buffer becomes empty.

When there are no more characters

to be sent, issuing this command prevents further transmitter interrupts or

DMA requests until the next character has been completely sent.

Command 6 Error Reset—error latches, Parity and Overrun errors in RR1 are reset.

Command 7 End of Interrupt—resets the interrupt-in-service latch of the highestpriority internal device under service.

D7, D6 CRC Reset Code.

00 Null—has no effect.

01 Reset Receive CRC Checker—resets the CRC checker to 0's. If in SDLC mode the CRC checker is initialized to all 1's.

10 Reset Transmit CRC Generator—resets the CRC generator to 0's. If in SDLC mode the CRC generator's initialized to all 1's.

11 Reset Tx Underrun/End of Message

Latch.

Z

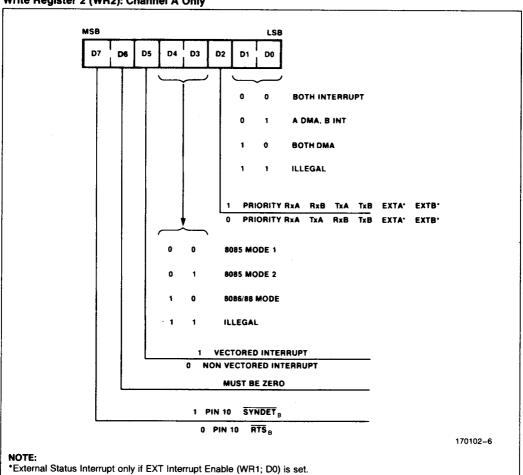

0 X X Non-vectored interrupts—intended for use with external DMA CONTROLLER. The Data Bus remains in a high impedance state during INTA sequences.

1 0 0 8085 Vector Mode 1—intended for use as the primary MPSC in a daisy chained priority structure. (See System Interface section).

1 0 1

8085 Vector Mode 2—intended for use as any secondary MPSC in a daisy chained priority structure. (See System Interface section).

1 1 0

8086/88 Vector Mode—intended for use as either a primary or secondary in a daisy chained priority structure. (See System Interface section).

D6

Must be zero.

D7

zero Pin 10 =  $\overline{RTS}_B$

one Pin 10 = SYNDETB

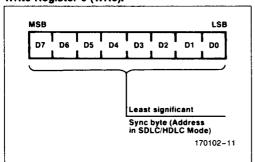

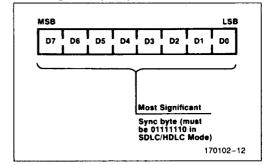

### Write Register 2 (WR2): Channel A Only

# intel.

The following table describes the MPSC's response to an interrupt acknowledge sequence:

| D5 | D4 | D3 | ĪPĪ | MODE         | INTA                             |                 | -               |                         | Da            | ta Bus        |               | ,            |              |

|----|----|----|-----|--------------|----------------------------------|-----------------|-----------------|-------------------------|---------------|---------------|---------------|--------------|--------------|

| 0  | х  | х  | х   | Non-vectored | Any INTA                         | D7<br>High      | Impe            | dance                   |               |               |               | C            | 00           |

| 1  | 0  | 0  | 0   | 85 Mode 1    | 1st INTA<br>2nd INTA<br>3rd INTA | 1<br>V7<br>0    | 1<br>V6<br>0    | 0<br>V5<br>0            | 0<br>V4*<br>0 | 1<br>V3*<br>0 | 1<br>V2*<br>0 | 0<br>V1<br>0 | 1<br>V0<br>0 |

| 1  | 0  | 0  | 1   | 85 Mode 1    | 1st INTA<br>2nd INTA<br>3rd INTA | _               | •               | 0<br>dance<br>dance     | 0             | 1             | 1             | 0            | 1            |

| 1  | 1  | 0  | 0   | 86 Mode      | 1st INTA<br>2nd INTA             | High<br>V7      | Impe<br>V6      | dance<br>V5             | V4            | V3            | V2*           | V1*          | V0*          |

| 1  | 0  | 1  | 0   | 85 Mode 2    | 1st INTA<br>2nd INTA<br>3rd INTA | High<br>V7<br>0 | Impe<br>V6<br>0 | dance<br>V5<br>0        | V4*<br>0      | 0<br>V3*      | V2*<br>0      | V1<br>0      | V0<br>0      |

| 1  | 0  | 1  | 1   | 85 Mode 2    | 1st INTA<br>2nd INTA<br>3rd INTA | High            | Impe            | dance<br>dance<br>dance |               | -             |               |              |              |

| 1  | 1  | 0  | 1   | 86 Mode      | 1st INTA<br>2nd INTA             |                 |                 | dance<br>dance          |               |               |               |              |              |

### NOTE:

### Interrupt/DMA Mode, Pin Functions, and Priority

|                |                          |                | 1-4/0144 |       |                    | Pin Fur | nctions |                    |                                                                                                                   |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

|----------------|--------------------------|----------------|----------|-------|--------------------|---------|---------|--------------------|-------------------------------------------------------------------------------------------------------------------|--|---|--|--|--|--|--|------------------------------------------|------------------------------------------|----------------------------|----------------------------|----------|--|

| Ch.            | h. A WR2 Int/DMA<br>Mode |                |          |       |                    |         |         |                    |                                                                                                                   |  | 1 |  |  |  |  |  | RDY <sub>A</sub> /<br>RxDRQ <sub>A</sub> | RDY <sub>B</sub> /<br>TxDRQ <sub>A</sub> | PIP/<br>RxDRQ <sub>B</sub> | ĪPŌ/<br>TxDRQ <sub>B</sub> | Priority |  |

| D <sub>2</sub> | D <sub>1</sub>           | D <sub>0</sub> | CH. A    | СН. В | Pin 32             | Pin 11  |         |                    | Highest Lowes                                                                                                     |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| 0              | 0                        | 0              | INT      | INT   | RDY₄               | RDYB    | ĪPĪ     | iPO                | RxA, TxA, RxB, TxB, EXTA, EXTB                                                                                    |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| 1              | 0                        | 0              | INT      | INT   | NDIA               | HOIB    |         |                    | RxA, RxB, TxA, TxB, EXTA, EXTB                                                                                    |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| 0              | 0                        | 1              | DMA      |       |                    | TxDRQA  | ĪΡĪ     | ĪPŌ                | RxA, TxA (DMA)                                                                                                    |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| ١              | U                        | '              |          | INT   | RXDRQ              |         |         |                    | RxA(1), RxB, TxB, EXTA, EXTB (INT                                                                                 |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| _              | 0                        | 1              | DMA      |       | HADRICA            |         |         |                    | RxA, TxA (DMA)                                                                                                    |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| '              | U                        | '              |          | INT   |                    |         |         |                    | RxA(1), RxB, TxB, EXTA, EXTB (INT                                                                                 |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| 0              | 1                        | 0              | DMA      | DMA   | RxDRQ <sub>A</sub> | TxDRQ₄  | RxDRQR  | TxDRQ <sub>B</sub> | RxA, TxA, RxB, TxB (DMA)<br>RxA <sup>(1)</sup> , RxB <sup>(1)</sup> , EXT <sub>A</sub> , EXT <sub>B</sub> , (INT) |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

| 1              | 1                        | 0              | DMA      | DMA   | HADRICA            | INDRUGA | LIVDUGB | INDIGE             | RxA, RxB, TxA, TxB, (DMA)<br>RxA(1), RxB(1), EXT <sub>A</sub> , EXT <sub>B</sub> (INT)                            |  |   |  |  |  |  |  |                                          |                                          |                            |                            |          |  |

### NOTE:

<sup>\*</sup>These bits are variable if the "status affects vector" mode has been programmed, (WR1B, D2).

<sup>1.</sup> Special Receive Condition

### 2

### Interrupt Vector Mode Table

| 8085 Modes<br>8086/88 Mode | V <sub>4</sub><br>V <sub>2</sub> | V <sub>3</sub><br>V <sub>1</sub> | V <sub>2</sub><br>V <sub>0</sub> | Channel | Condition                     |

|----------------------------|----------------------------------|----------------------------------|----------------------------------|---------|-------------------------------|

|                            | 0                                | 0                                | 0                                | В       | Tx Buffer Empty               |

|                            | 0                                | 0                                | 1                                |         | Ext/Status Change             |

|                            | 0                                | 1                                | 0                                |         | Rx Char. Available            |

|                            | 0                                | 1                                | 1                                |         | Special Rx Condition (Note 1) |

|                            | 1                                | 0                                | 0                                | Α       | Tx Buffer Empty               |

|                            | 1                                | 0                                | 1                                |         | Ext/Status Change             |

|                            | 1                                | 1                                | 0                                |         | Rx Char. Available            |

|                            | 1                                | 1                                | 1                                |         | Special Rx Condition (Note 1) |

### NOTE:

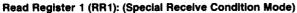

1. Special Receive Condition = Parity Error, Rx Overrun Error, Framing Error, End of Frame (SDLC).

### Write Register 2 (WR2): Channel B

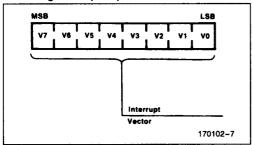

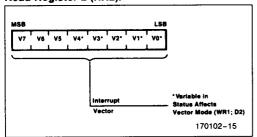

### WR2 CHANNEL B

D7-D0

Interrupt vector—This register contains the value of the interrupt vector placed on the data bus during interrupt acknowledge sequences.

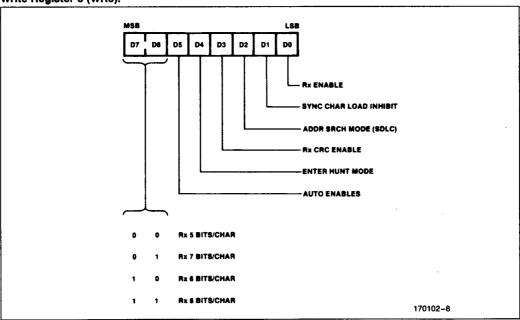

### Write Register 3 (WR3):

# intها.

| WR3    |                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0     | Receiver Enable—A one enables the receiver to begin. This bit should be set only after the receiver has been initialized.                                                                                                                                                                                                                                                                   |

| D1     | Sync Character Load Inhibit—A one prevents the receiver from loading sync characters into the receive buffers. In SDLC, this bit must be zero.                                                                                                                                                                                                                                              |

| D2     | Address Search Mode—If the SDLC mode has been selected, the MPSC will receive all frames unless this bit is a 1. If this bit is a 1, the MPSC will receive only frames with address (0FFH) or the value loaded into WR6. This bit must be zero in non-SDLC modes.                                                                                                                           |

| D3     | Receive CRC Enable—A one in this bit enables (or re-enables) CRC calculation. CRC calculation starts with the last character placed in the Receiver FIFO. A zero in this bit disables, but does not reset, the Receiver CRC generator.                                                                                                                                                      |

| D4     | Enter Hunt Phase—After initializa-<br>tion, the MPSC automatically enters<br>the Hunt mode. If synchronization is<br>lost, the Hunt phase can be re-en-<br>tered by writing a one to this bit.                                                                                                                                                                                              |

| D5     | Auto Enable—A one written to this bit causes $\overline{\text{CD}}$ to be automatic enable signal for the receiver and $\overline{\text{CTS}}$ to be an automatic enable signal for the transmitter. A zero written to this bit limits the effect of $\overline{\text{CD}}$ and $\overline{\text{CTS}}$ signals to setting/resetting their corresponding bits in the status register (RR0). |

| D7, D6 | Receive Character length                                                                                                                                                                                                                                                                                                                                                                    |

| 0 0    | Receive 5 Data bits/character                                                                                                                                                                                                                                                                                                                                                               |

| 0 1    | Receive 7 Data bits/character                                                                                                                                                                                                                                                                                                                                                               |

| 1 0    | Receive 6 Data bits/character                                                                                                                                                                                                                                                                                                                                                               |

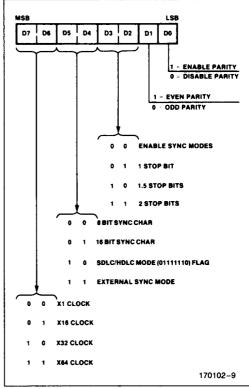

### WR4 D0

1 1

Parity—A one in this bit causes a parity bit to be added to the programmed number of data bits per character for both the transmitted and received character. If the MPSC is programmed to receive 8 bits per character, the parity bit is not transferred to the microprocessor. With other receiver character lengths, the parity bit is transferred to the microprocessor.

Receive 8 Data bits/character

### Write Register 4 (WR4):

| D1 | Even/Odd Parity—If parity is en-<br>abled, a one in this bit causes the<br>MPSC to transmit and expect even |

|----|-------------------------------------------------------------------------------------------------------------|

|    | parity, and a zero causes it to send and expect odd parity.                                                 |

Stop bits/sync mode

|    | •     | •                                    |

|----|-------|--------------------------------------|

| 0  | 0     | Selects synchronous modes            |

| 0  | 1     | Async mode, 1 stop bit/character     |

| 1  | 0     | Async mode, 11/2 stop bits/character |

| 1  | 1     | Async mode, 2 stop bits/character    |

| D! | 5, D4 | Sync mode select                     |

| 0  | 0     | 8-bit sync character                 |

| 0  | 1     | 16-bit sync character                |

| 1  | 0     | SDLC mode (Flag sync)                |

| 1  | 1     | External sync mode                   |

|    |       |                                      |

D7, D6

Clock Mode—Selects the clock/data rate multiplier for both the receiver and the transmitter. 1x mode must be selected for synchronous modes. If the 1x mode is selected, bit synchronization must be done externally.

D3, D2

D1

D2

D3

D4

| 0 | 0  | Clock rate = | Data rate | × | 1  |

|---|----|--------------|-----------|---|----|

| 0 | 1  | Clock rate = | Data rate | × | 16 |

| 1 | 0. | Clock rate = | Data rate | × | 32 |

| 1 | 1  | Clock rate = | Data rate | × | 64 |

Request to Send—A one in this bit forces the RTS pin active (low) and zero in this bit forces the RTS pin inactive (high).

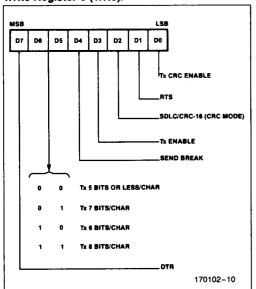

Write Register 5 (WR5):

CRC Select—A one in this bit selects the CRC – 16 polynomial ( $X^{16} + X^{15} + X^2 + 1$ ) and a zero in this bit selects the CCITT-CRC polynomial ( $X^{16} + X^{12} + X^5 + 1$ ). In SDLC mode, CCITT-CRC must be selected.

Transmitter Enable—A zero in this bit forces a marking state on the transmitter output. If this bit is set to zero during data or sync character transmission, the marking state is entered after the character has been sent. If this bit is set to zero during transmission of a CRC character, sync or flag bits are substituted for the remainder of the CRC bits.

Send Break—A one in this bit forces the transmit data low. A zero in this bit allows normal transmitter operation.

| Dŧ | S, D5 | Transmit Character length   |

|----|-------|-----------------------------|

| 0  | 0     | Transmit 1-5 bits/character |

| 0  | 1     | Transmit 7 bits/character   |

| 1  | 0     | Transmit 6 bits/character   |

| 1  | 1     | Transmit 8 bits/character   |

### WR5 D0

Bits to be sent must be right justified least significant bit first, e.g.:

Transmit CRC Enable—A one in this bit enables the transmitter CRC generator. The CRC calculation is done when a character is moved from the transmit buffer into the shift register. A zero in this bit disables CRC calculations. If this bit is not set when a transmitter underrun occurs, the CRC will not be sent.

D7 D6 D5 D4 D3 D2 D1 D0 0 0 B5 B4 B3 B2 B1 B0

D7 Data Terminal Ready—When set, this bit forces the DTR pin active (low). When reset, this bit forces the DTR pin inactive (high).

| 1  | Five or less mode allows transmission of one to five bits per character. The microprocessor must format the data in the following way: |     |    |    |    |    |    |                       |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------|-----|----|----|----|----|----|-----------------------|--|--|

| D7 | D6                                                                                                                                     | D5  | D4 | D3 | D2 | D1 | D0 |                       |  |  |

| 1  | 1                                                                                                                                      | 1   | 1  | 0  | 0  | 0  | B0 | Sends one data bit    |  |  |

| 1  | 1                                                                                                                                      | 1   | 0  | 0  | 0  | B1 | B0 | Sends two data bits   |  |  |

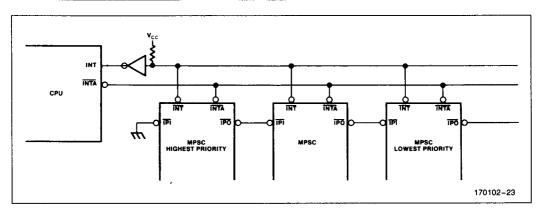

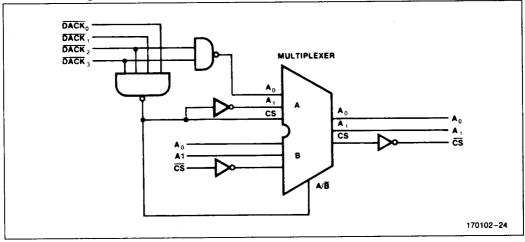

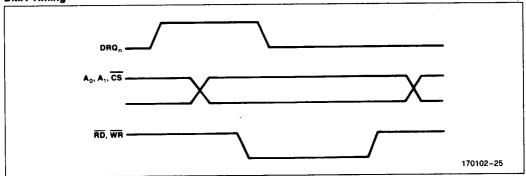

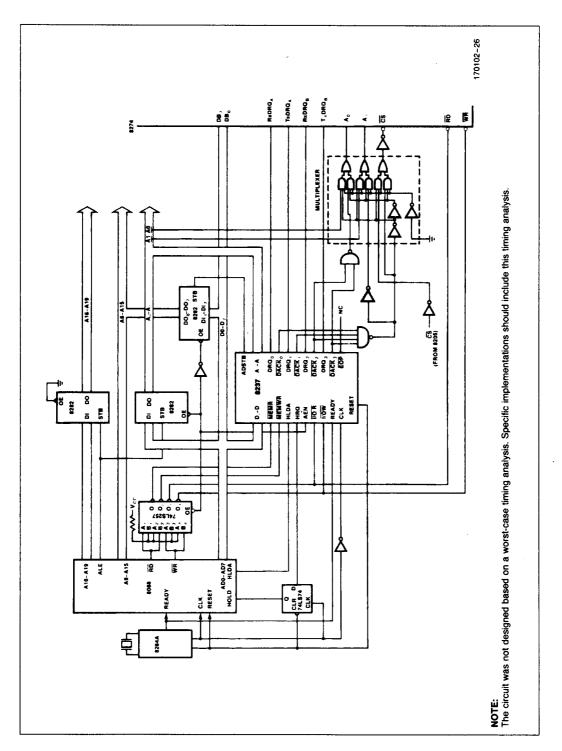

| 1  | 1 '                                                                                                                                    | . 0 | 0  | 0  | B2 | B1 | B0 | Sends three data bits |  |  |