# AM29C821A/BLA

# High-Performance CMOS Bus Interface Registers

The Am29C821A and Am29C82311 CMOS Bus Interface Registers are designed to eliminate the extra devices required to buffer stand alone registers and to provide extra data width for wider address/data paths or buses carrying parity.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Advanced Micro Devices

# Am29C821A/Am29C823A

# **High-Performance CMCS Bus Interface Registers**

#### DISTINCTIVE CHARACTERISTICS

- Proprietary edge-rate controlled outputs dramatically reduce undershoots, overshoots and ground bounce

- High-speed parallel positive edge-triggered registers with D-type flip-flops

- CP-Y propagation delay = 5 r s lypical

- Low standby power

- Very high output drive

- IoL = 48 mA Commercial, 32 nm. Military

- Extra-wide (9- and 10-bit) data paths

- Power-up/down disable circuit provides for glitch-free power supply sequencing

- Can be powered off while in 3-state, ideal for card edge interface applications

- Minimal speed degradation with multiple outputs switching

- JEDEC FCT-compatible specs

#### **GENERAL DESCRIPTION**

The Am29C821A and Am29C823A CMOS Bus Interface Registers are designed to eliminate the extra devices required to buffer stand alone registers and to provide extra data width for wider address/data paths or buses carrying parity. The Am29C800A registers are produced with AMD's exclusive CS115A CMOS process, and feature typical propagation delays of 5 ns, as well as an output current drive of 48 reA

The Am29C821A is a buffered, 10 bir version of the popular '374/'534 function. The Am29C823A is a 9-bit buffered register with Clock Enable EN) and Clear (CLR)—ideal for parity bus in emacing in high-performance microprogrammed systems

The Am29C821A and Am29C823A interpretate AMD's proprietary edge-controlled outputs interder to minimize simultaneous switching noise (ground bounce), undershoots and overshoots. By controlling the output transient currents, ground bounce and output ringing have

been greatly reduced. A modified AMD output provides a stable, usable voltage level in less time than a non-controlled output.

Additionally, speed degradation due to increasing number of outputs switching is reduced. Together, these benefits of edge-rate control result in significant increase in system performance despite a minor increase in device propagation delay.\*

A unique I/O circuitry, which utilizes n-channel pull-up transistors (eliminating the parasitic diode to Vcc), provides for high-impedance outputs during power-off and power-up/down sequencing, thus providing glitch-free operation for card-edge and other active bus applications.

The Am29C821A and Am29C823A are available in the standard package options: DIPs, PLCCs, and SOICs.

Publication# 11227 Rev. B Amendment/0

Issue Date: December 1990

<sup>\*</sup>For more details refer to a Minimization and Prounce Bounce Through Output Edge-Rate Control Application Note (See Chapter 3).

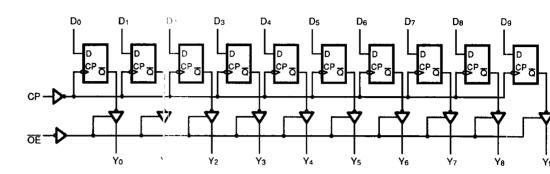

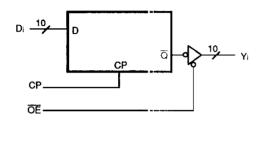

# BLOCK DIAGRAMS Am29C821A

11227-001A

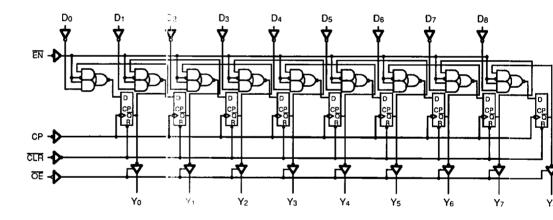

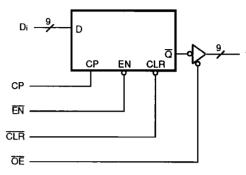

# Am29C823A

11227-002A

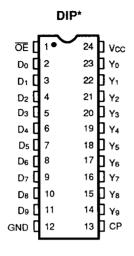

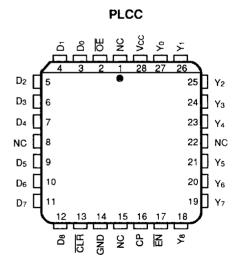

# CONNECTION DIAGRAMS (Top View) Am29C821A

11227-003A

11227-004A

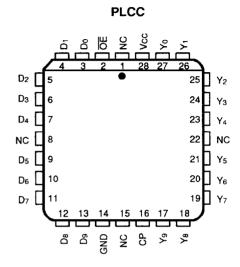

# Am29C823A

11227-005A

11227-006A

<sup>\*</sup>Also available in 24-Pin Small Outline package; pinout identical to DIPs.

# LOGIC SYMBOLS

## Am29C821A

# Am29C823A

11227-007A

11227-008

# **FUNCTION TABLES**

# Am29C821A

|    | Inputs | _        | Internal   | Outputs |          |

|----|--------|----------|------------|---------|----------|

| ŌĒ | D      | СР       | <b>Q</b> i | Yı      | Function |

| Н  | L      | 1        | н          | Z       |          |

| Н  | Н      | <b>↑</b> | L          | Z       | Hi-Z     |

| L  | L      | <u></u>  | Н          | L       |          |

| L  | H      | 1        | L          | Н       | Load     |

# Am29C823A

|    |     | Iriputs |    |          | Internal | Outputs |          |  |

|----|-----|---------|----|----------|----------|---------|----------|--|

| ŌĒ | CLR | EN      | Di | CP       | Qi       | Yi      | Function |  |

| Н  | Н   | l       | Ļ  | <u> </u> | Н        | Z       |          |  |

| Н  | Н   | L       | Н  | 1        | L        | Z       | Hi-Z     |  |

| Н  | L   | Х       | Х  | Х        | Н        | Z       |          |  |

| L  | L   | Х       | Х  | Х        | Н        | L       | Clear    |  |

| Н  | Н   | H       | Х  | Х        | NC       | Z       |          |  |

| L  | Н   | Н       | Х  | Х        | NC       | NC      | Hold     |  |

| H  | Н   | L       | L  | 1        | Н        | Z       |          |  |

| Н  | Н   | L       | H  | 1        | L        | Z       | l        |  |

| L  | Н   | L       | L  | _     ↑  | Н        | L       | Load     |  |

| L  | Н   | L_      | Н  |          | L        | Н       |          |  |

H = HIGH

NC = No Change

L= LOW

↑ = LOW-to-HIGH Transition

X = Don't Care

Z = High Impedance

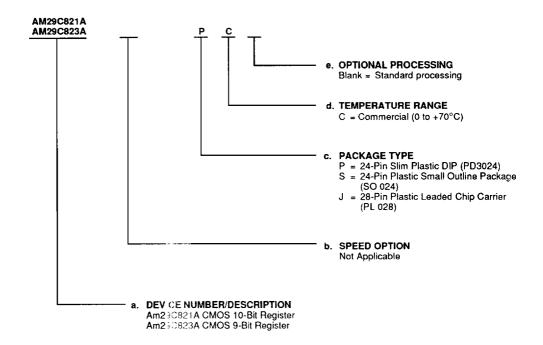

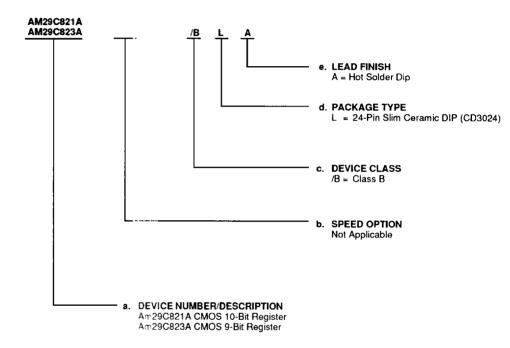

# ORDERING INFORMATION **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

d. Temperature Range

- e. Optional Processing

| Valid Combinations |                   |  |  |  |  |  |

|--------------------|-------------------|--|--|--|--|--|

| AM29C821A          | <b>DO</b> 600 100 |  |  |  |  |  |

| AM29C823A          | PC, SD, JC        |  |  |  |  |  |

## **Valid Combinations**

Valid Combinations fist configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific: valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# MILITARY ORDERING INFORMATION **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- Speed Option (if applicable)

Device Class

Package Type

Lead Finish

- c. d.

| Valid Combinations |       |  |  |  |  |  |

|--------------------|-------|--|--|--|--|--|

| AM29C821A          | .DV A |  |  |  |  |  |

| AM29C823A          | ∃BLA  |  |  |  |  |  |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, or to check on newly released combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

# PIN DESCRIPTION Am29C821A/Am29C823A

D

#### Data input (input)

Di are the register data inputs.

## CP

# Clock Pulse (Input, LOW-to-HIGH Transition)

Clock Pulse is the clock input for the registers. Data is entered into the registers on the LOW-to-HIGH transitions.

#### Yi

# **Data Outputs (Output)**

Yi are the three-state outputs.

#### **OE**

## Output Enable (Input, Active LO'N)

When the  $\overline{OE}$  input is HIGH, the  $V_i$  outputs are in the high-impedance state. When  $\overline{OE}$  is LOW, the register data is present at the  $Y_i$  outputs.

# Am29C823A only

#### EN

# Clock Enable (Input, Active LOW)

When  $\overline{EN}$  is LOW, data on the Di inputs are transferred to the  $\overline{Q_i}$  outputs on the LOW-to-HIGH clock transition. When  $\overline{EN}$  is HIGH, the  $\overline{Q_i}$  outputs do not change state, regardless of the data or clock input transitions.

## CLR

## Clear (input, Active LOW)

When  $\overline{\text{CLR}}$  is LOW, the internal register is cleared. When  $\overline{\text{CLR}}$  is LOW and  $\overline{\text{OE}}$  is LOW, the  $\overline{\text{Qi}}$  outputs are HIGH. When  $\overline{\text{CLR}}$  is HIGH, data can be entered into the register.

## **ABSOLUTE MAXIMUM RATINGS**

-65 to +150°C StorageTemperature Supply Voltage to Ground **Potential Continous** -0.5 V to +7.0 V DC Output Voltage -0.5 V to +6.0 V DC Input Voltage -0.5 V to +6.0 V DC Output Diode Current: Into Output +50 mA Out of Output -50 mA DC Input Diode Current: Into Input +20 mA Out of Input -20 mA

DC Output Current:

Into Output +100 mA Out of Output -100 mA

**Total DC Ground Current**

(n x lot + m x loct) mA (Note 1)

Total DC Vcc Current (n x lon + m x loct) mA (Note 1)

#### Note:

1. n = number of outputs, m = ncmber of inputs.

Stresses above those listed uncer Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

Commercial (C) Devices

Ambient Temperature (T<sub>A</sub>) 0 to +70°C Supply Voltage (Vcc) +4.5 to +5.5 V

Military (M) Devices

Ambient Temperature (T<sub>A</sub>) -55 to +125°C Supply Voltage (Vcc) +4.5 to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter Description        | Test Conditions                                                  |                       |                | Min. | Max. | Unit        |

|---------------------|------------------------------|------------------------------------------------------------------|-----------------------|----------------|------|------|-------------|

| Vон                 | Output HIGH Voltage          | Vcc = 4.5 V<br>Vin = Vihor Vil                                   |                       |                | 2.4  |      | V           |

| Vol                 | Output LOW Voltage           | Vcc = 4.5 V                                                      | MIL IOL = 3           | 2 mA           |      | 0.5  | >           |

|                     |                              | Vin = Vihor Vil                                                  | COM'L lou             | = 48 mA        |      | 0.5  | ٧           |

| ViH                 | Input HIGH Voltage           | Guaranteed Input Logical HIGH<br>Voltage for All Inputs (Note 1) |                       |                | 2.0  |      | ٧           |

| VIL                 | Input LOW Voltage            | Guaranteed Input Logical LOW<br>Voltage for All Inputs (Note 1)  |                       |                |      | 0.8  | >           |

| Vı                  | Input Clamp Voltage          | Vcc = 4.5 V, lin = -18 mA                                        |                       |                |      | -1.2 | >           |

| l <sub>IL</sub>     | Input LOW Current            | Vcc = 5.5 V, Vin = GND                                           |                       |                |      | -5   | μΑ          |

| lıн                 | Input HIGH Current           | Vcc = 5.5 V, Vin = 5.5 V                                         |                       |                |      | 5    | μΑ          |

| lozн                | Output Off-State Current     | Vcc = 5.5 V, Vo = 5.5 V                                          |                       |                |      | +10  | μA          |

| lozL                | (High Impedance)             | Vcc = 5.5 V, Vc                                                  | Vcc = 5.5 V, Vo = GND |                |      | -10  | μΑ          |

| Isc                 | Output Short-Circuit Surrent | Vcc = 5.5 V, Vo = 0 V (Note 2)                                   |                       |                | -60  |      | mA          |

| lcca                | 1,112,27452                  | -                                                                | VIN = Vcc or          | MIL            |      | 1.5  | mA          |

|                     |                              | Vcc = 5.5 V                                                      | GND                   | COM'L          |      | 1.2  | 1117        |

| ICCT                | Static Supply Currer t       | Outputs Open                                                     | $V_{IN} = 3.4 V$      | Data Input     |      | 1.5  | mA/         |

|                     |                              |                                                                  |                       |                |      | 3.0  | Bit         |

| lccpt               | Dynamic Supply Current       | Vcc = 5.5 V (Note 3) Outputs O                                   |                       | Outputs Open   |      | 275  | μA⁄         |

|                     |                              |                                                                  |                       | Outputs Loaded |      | 400  | MHz/<br>Bit |

#### Notes:

- 1. Input thresholds are tested in confibration with other DC parameters or by correlation.

- 2. Not more than one output shortec at a time. Duration should not exceed 100 milliseconds.

- 3. Measured at a frequency ≤ 10 MHz with 50% duty cycle.

- † Not included in Group A tests.

# SWITCHING CHARACTERISTICS for light capacitive loading over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|              | Parameter Description                 |      |                        | Commercial |          | Military |      |      |

|--------------|---------------------------------------|------|------------------------|------------|----------|----------|------|------|

| Symbol       |                                       |      | Test Conditions*       | Min.       | Max.     | Min.     | Max. | Unit |

| tры          | Propagation Delay Clock to Yi         |      |                        | 2          | 8.5      | 2        | 9.5  | ns   |

| tphL         | (OE = LOW) (Note                      |      |                        | 3          | 8.5      | 3        | 9.5  | ns   |

| ts           | Data to CP Setup Time                 |      |                        | 3          |          | 3        |      | ns   |

| tн           | Data to CP Hold Time                  |      |                        | 2          |          | 2        |      | ns   |

| ts           | Enable (EN 1) to GP Setup             | Time |                        | 4          | <u> </u> | 4        |      | ns   |

| ts           | Enable (EN_F) to GP Setup Time        |      |                        | 4          |          | 4        |      | ns   |

| tн           | Enable (EN) Hold T∉ne                 |      | C <sub>L</sub> = 50 pF | 0          |          | 0        |      | ns   |

| <b>t</b> PHL | Propagation Delay, Clear to Yi        |      | $R_1 = 500 \Omega$     | 3          | 10       | 3        | 10.5 | ns   |

| trec         | Clear (CLR_F) to CF Setup Time        |      | $R_2 = 500 \Omega$     | 6          |          | 6        |      | ns   |

| tрwн         | Clock Pulse Width                     | HIGH | ]                      | 6          |          | 6        |      | ns   |

| tpwL         | Clock Fulse Width                     | LOW  |                        | 6          |          | 6        |      | ns   |

| tpwL         | Clear Pulse Width                     | LOW  |                        | 6          |          | 6        |      | ns   |

| tzн          | Output Enable Time 진단 <b>TL</b> to Yi |      |                        | 1          | 8.5      | 1        | 9    | ns   |

| tzl          |                                       |      |                        | 3          | 12       | 3        | 13   | ns   |

| tHZ          | Output Disable Time ÖÉ 🥒 to Yi        |      |                        | 2          | 8        | 2        | 8.5  | ns   |

| tLZ          | Output Disable Time Or.               |      | l                      | 2          | 8        | 2        | 8.5  | ns   |

# SWITCHING CHARACTERISTICS for heavy capacitive loading over operating ranges unless otherwise specified (Note 2)

|              |                                 |                                                                    | Commercial |      | Mili |      |      |

|--------------|---------------------------------|--------------------------------------------------------------------|------------|------|------|------|------|

| Symbol       | Parameter Description           | Test Conditions*                                                   | Min.       | Max. | Min. | Max. | Unit |

| tpLH         | Propagation Delay Clicck to Yi  |                                                                    | 2          | 15.5 | 2    | 17.5 | ns   |

| <b>t</b> PHL | (OE = LOW) (Note                | $C_L = 300 \text{ pF}$<br>$R_1 = 500 \Omega$<br>$R_2 = 500 \Omega$ | 3          | 15.5 | 3    | 17.5 | ns   |

| tzн          | Output Enable Time Time to Yi   |                                                                    | 2          | 15   | 2    | 15.5 | ns   |

| tzı          |                                 |                                                                    | 3          | 18.5 | 3    | 19.5 | ns   |

| tHZ          | Output Disable Tim : OF _ to Ye | CL = 5 pF                                                          | 2          | 6.5  | 2    | 7    | ns   |

| tız          | Output Disable Tim : OF - to Yi | $R_1 = 500 \Omega$<br>$R_2 = 500 \Omega$                           | 2          | 6.5  | 2    | 7    | ns   |

<sup>\*</sup>See Test Circuit and Waveforms listen in Chapter 2.

#### Notes:

<sup>1.</sup> For more details refer to a Minim of thom of Ground Bounce Through Output Edge-Rate Control Application Note (See Chapter 3).

<sup>2.</sup> These parameters are guarantee: by characterization but not production tested.