### PLLatinum<sup>™</sup> Ultra Low Power Frequency Synthesizer for **RF** Personal Communications 2.5 GHz LMX2310U LMX2311U 2.0 GHz

# **General Description**

LMX2312U

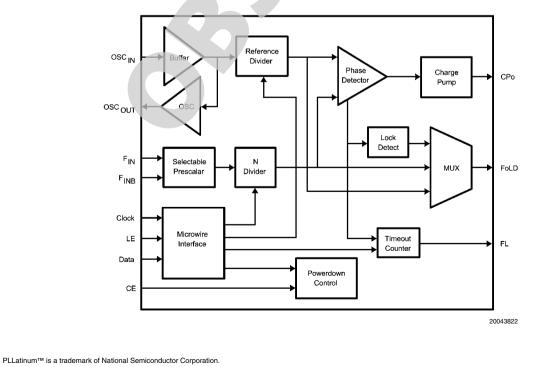

The LMX2310/1/2/3U are high performance frequency synthesizers. The LMX2310/1/2U use a selectable, dual modulus 32/33 and 16/17 prescaler. The LMX2313U uses a selectable, dual modulus 16/17 and 8/9 prescaler. The device, when combined with a high quality reference oscillator and a voltage controlled oscillator, generates very stable, low noise local oscillator signals for up and down conversion in wireless communication devices.

1.2 GHz

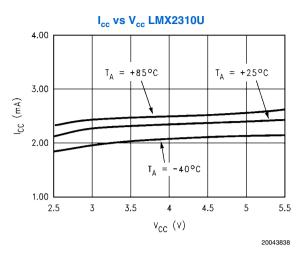

Serial data is transferred into LMX2310/1/2/3U via a threewire interface (Data, Enable, Clock) that can be directly interfaced with low voltage baseband processors. Supply voltage can range from 2.7V to 5.5V. LMX2310U features very low current consumption, typically 2.3 mA at 3.0V.

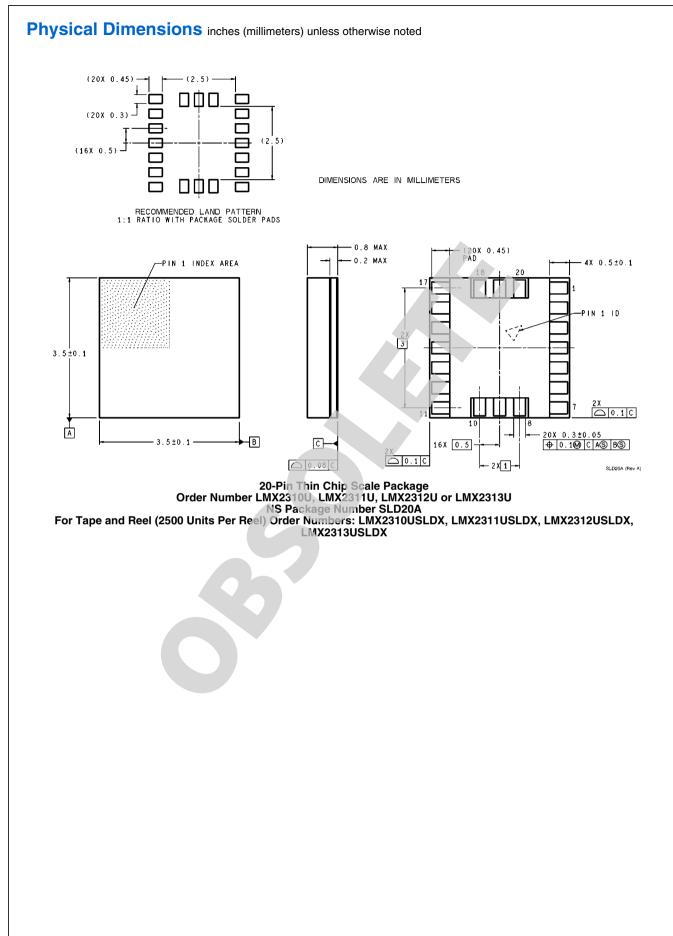

The LMX2310/1/2/3U are manufactured using National's 0.5µ ABiC V silicon BiCMOS process and is available in 20-pin CSP packages.

**Functional Block Diagram**

# **Features**

LMX2313U

- RF operation up to 2.5 GHz

- 2.7V to 5.5V operation

- -Ultra Low Current Consumption Low prescaler values LMX2310/1/2U 32/33 or 16/17

- LMX2313U 16/17 or 8/9

- **Excellent Phase Noise**

- Internal balanced, low leakage charge pump

- Selectable Charge Pump Current Levels

- Selectable Fastlock mode with Time-Out Counter

600 MHz

- Low Voltage MICROWIRE interface (1.72V to V<sub>CC</sub>)

- Digital and Analog Lock Detect

- Small 20-pad Thin Chip Scale Package .

# Applications

- Cellular DCS, PCS, WCDMA telephone systems

- Wireless Local Area Networks (WLAN)

- Global Positioning Systems (GPS) R.

- Other wireless communications systems

### © 2011 National Semiconductor Corporation 200438

www.national.com

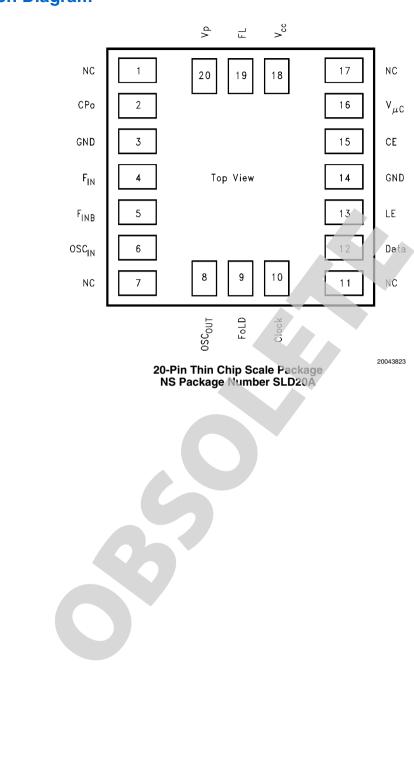

# **Connection Diagram**

| Pin Number | Pin Name           | I/O | Description                                                                                                                                                                                                                                                                        | I/O Circuit Configuration |

|------------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1          | NC                 | —   | No Connect.                                                                                                                                                                                                                                                                        |                           |

| 2          | CPo                | 0   | Charge Pump output. For connection to a<br>loop filter for driving the voltage control input<br>of an external VCO.                                                                                                                                                                |                           |

| 3          | GND                |     | Analog ground.                                                                                                                                                                                                                                                                     | •                         |

| 4          | F <sub>IN</sub>    | 1   | RF prescaler input. Small signal input from the VCO.                                                                                                                                                                                                                               | V <sub>cc</sub>           |

| 5          | F <sub>INB</sub>   | 1   | RF prescaler complementary input. For<br>single ended operation, this pin should be<br>AC grounded. The LMX2310/1/2/3U can be<br>driven differentially when a bypass<br>capacitor is omitted.                                                                                      |                           |

| 6          | OSC <sub>IN</sub>  | 1   | Oscillator input. An input to a CMOS low<br>noise inverting buffer. The input can be<br>driven from an external CMOS or TTL logic<br>gate.                                                                                                                                         |                           |

| 7          | NC                 | _   | No Connect.                                                                                                                                                                                                                                                                        |                           |

| 8          | OSC <sub>OUT</sub> | 0   | Oscillator output. The $OSC_{IN}$ low noise<br>buffer drives an independent oscillator<br>buffer. Its output is connected to the<br>$OSC_{OUT}$ pin. It can be used as a buffer to<br>provide the reference oscillator frequency to<br>other circuitry or as a crystal oscillator. |                           |

| 9          | FoLD               | 0   | Multi-function CMOS output pin that provides multiplexed access to digital lock detect, open drain analog lock detect, as well as the outputs of the R and N counters. The FoLD pin is internally referenced to $V_{\mu C}$ .                                                      |                           |

| Pin Number | Pin Name        | I/O | Description                                                                                                                                                                                                                                                                    | I/O Circuit Configuration |

|------------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 10         | Clock           | 1   | High impedance CMOS Clock input. Data for the counters is clocked in on the rising edge, into the 22-bit shift register. The Clock is internally referenced to $V_{\mu C}$ .                                                                                                   |                           |

| 11         | NC              | 1_  | No Connect.                                                                                                                                                                                                                                                                    |                           |

| 12         | Data            | 1   | High impedance CMOS Data input. Serial Data is entered MSB first. The last two bits are the address for the target registers. The Data is internally referenced to $V_{\mu C}$ .                                                                                               |                           |

| 13         | LE              | 1   | High impedance CMOS LE input. When Latch Enable goes HIGH, data stored in the 22-bit shift register is loaded into one the 3 control registers, based on the address field. The Latch Enable is internally referenced to $V_{\mu C}$ .                                         |                           |

| 14         | GND             | 1_  | Digital ground.                                                                                                                                                                                                                                                                |                           |

| 15         | CE              | I   | High impedance CMOS Chip Enable input. Provides logical power-down control of the device. Pull-up to $V_{\mu C}$ if unused. The Chip Enable is internally referenced to $V_{\mu C}$ .                                                                                          |                           |

| 16         | V <sub>µC</sub> |     | Power supply for MICROWIRE circuitry.<br>Must be $\leq V_{CC}$ . Typically connected to same<br>supply level as microprocessor or baseband<br>controller to enable programming at low<br>voltages.                                                                             |                           |

| 17         | NC              |     | No Connect.                                                                                                                                                                                                                                                                    |                           |

| 18         | V <sub>cc</sub> | -   | Power supply voltage input. Input may<br>range from 2.7V to 5.5V. Bypass capacitors<br>should be placed as close as possible to this<br>pin and be connected directly to the ground<br>plane.                                                                                  |                           |

| 19         | FL              | 0   | Fastlock mode output. In Fastlock mode this<br>pin is at logic low. When not in Fastlock<br>mode, this pin is in TRI-STATE mode. This<br>pin can also be forced to TRI-STATE, forced<br>low or forced high by the programming of the<br>first two-bits of the Timeout Counter. |                           |

| 20         | V <sub>P</sub>  | -   | Power supply for charge pump. Must be $\geq$ V <sub>CC</sub> .                                                                                                                                                                                                                 |                           |

www.national.com

# Absolute Maximum Ratings (Note 1, Note

<u>2</u>)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Power Supply Voltage,                                          |                                 |

|----------------------------------------------------------------|---------------------------------|

| $(V_{CC}, V_{P}, V_{\mu C})$                                   | -0.3V to +6.5V                  |

| Voltage on any pin with GND=0V                                 |                                 |

| $CP_{o}$ , FL, $F_{IN}$ , $OSC_{IN}$ , $OSC_{OUT}$ ( $V_{i}$ ) | –0.3V to V <sub>CC</sub> + 0.3V |

| Data, Clock, LE, CE, FoLD (V <sub>i</sub> )                    | –0.3V to $V_{\mu C}$ + 0.3V     |

Storage Temperature Range, (T<sub>S</sub>) Lead Temp. (solder 4 sec.), (T<sub>1</sub>) -65°C to +150°C +260°C

.. ..

# Recommended Operating Conditions (Note 1)

|                                          | Min      | Мах      | Unit |  |

|------------------------------------------|----------|----------|------|--|

| Power Supply Voltage                     |          |          |      |  |

| (V <sub>CC</sub> )                       | 2.7      | 5.5      | V    |  |

| (V <sub>P</sub> )                        | $V_{CC}$ | 5.5      | V    |  |

| (V <sub>µC</sub> )                       | 1.72     | $V_{CC}$ | V    |  |

| Operating Temperature, (T <sub>A</sub> ) | -40      | +85      | °C   |  |

# **Electrical Characteristics**

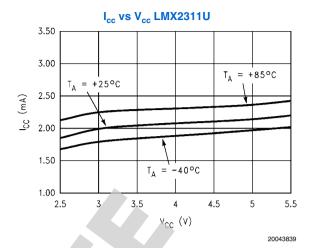

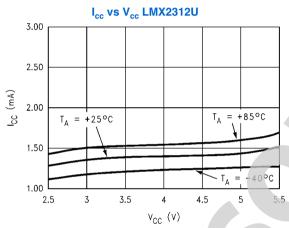

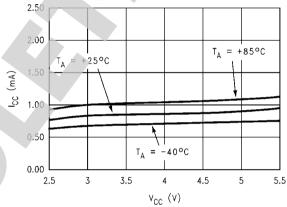

$V_{CC}$  =  $V_{P}$  =  $V_{\mu C}$  = 3.0V, -40°C <  $T_{A}$  < +85°C unless specified otherwise.

| Symbol                         | Parameter                                          |                                               | Conditions (Note 3)                                                                                  | Min  | Тур  | Max             | Units            |

|--------------------------------|----------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------|------|------|-----------------|------------------|

| сс                             |                                                    |                                               |                                                                                                      |      |      |                 |                  |

|                                |                                                    | LMX2310U                                      | (Note 4)                                                                                             |      | 2.3  | 3.0             | mA               |

|                                |                                                    |                                               | V <sub>CC</sub> = 5.5V ( <i>Note 4</i> )                                                             |      |      | 3.4             | mA               |

|                                |                                                    | LMX2311U                                      | (Note 4)                                                                                             |      | 2.0  | 2.7             | mA               |

|                                | Power Supply                                       |                                               | V <sub>CC</sub> = 5.5V ( <i>Note 4</i> )                                                             |      |      | 3.2             | mA               |

| сс                             | Current                                            | LMX2312U                                      | (Note 4)                                                                                             |      | 1.4  | 2.0             | mA               |

|                                |                                                    |                                               | V <sub>CC</sub> = 5.5V ( <i>Note 4</i> )                                                             |      |      | 2.4             | mA               |

|                                |                                                    | IMV0010U                                      | (Note 4)                                                                                             |      | 1.0  | 1.3             | mA               |

|                                |                                                    | LMX2313U                                      | V <sub>CC</sub> = 5.5V ( <i>Note</i> 4)                                                              |      |      | 1.6             | mA               |

| CC-PWDN                        | Power-Down C                                       | urrent                                        | Clock, Data and LE = GND<br>CE = GND                                                                 |      | 1    | 10              | μA               |

| RF PRESCAL                     | .ER                                                |                                               |                                                                                                      |      |      |                 |                  |

|                                |                                                    | LMX2310U                                      |                                                                                                      | 0.5  |      | 2.5             | GHz              |

| En I '                         | Operating                                          | LMX2311U                                      |                                                                                                      | 0.5  |      | 2.0             | GHz              |

|                                | Frequency                                          | LMX2312U                                      |                                                                                                      | 0.2  |      | 1.2             | GHz              |

|                                |                                                    | LMX2313U                                      |                                                                                                      | 45   |      | 600             | MHz              |

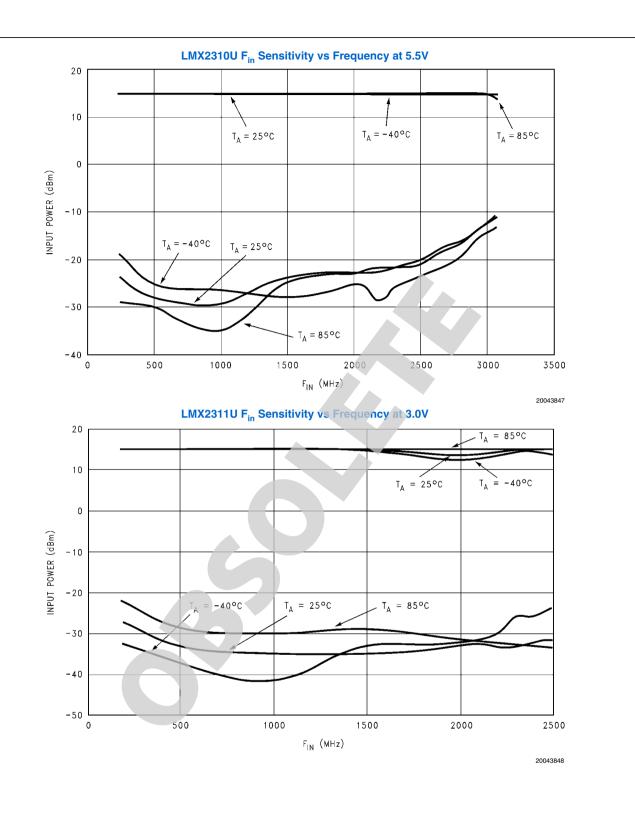

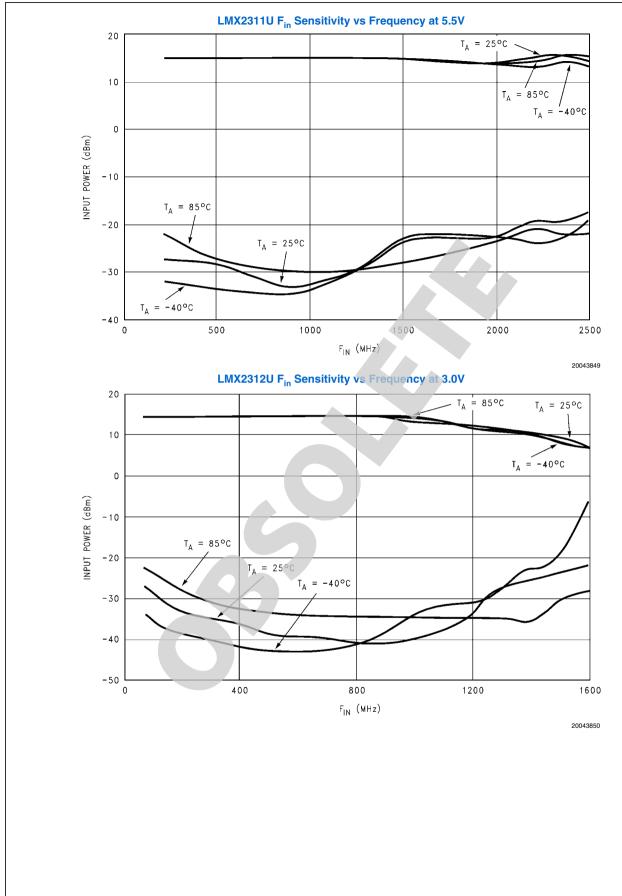

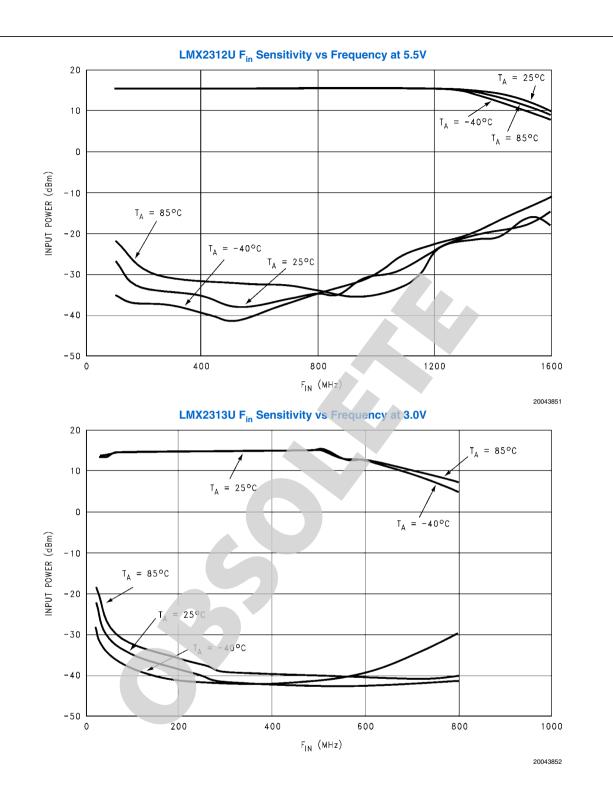

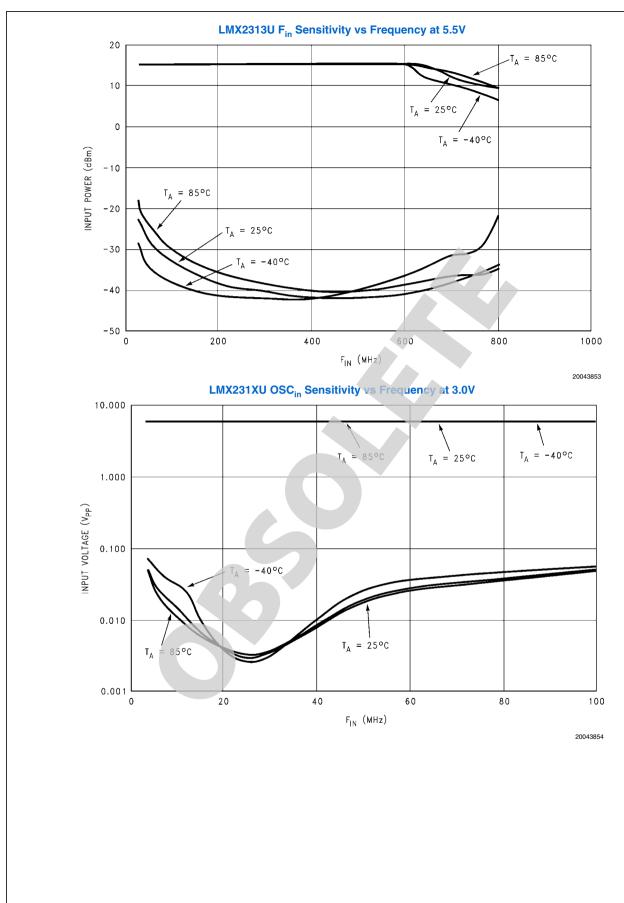

| Input Sensitivity              | /, RF                                              | 2.7 ≤ V <sub>CC</sub> ≤3.0V ( <i>Note 5</i> ) | -15                                                                                                  |      | 0    | dBm             |                  |

| PF <sub>IN</sub>               | Prescaler                                          |                                               | 3.0V < V <sub>CC</sub> ≤ 5.5V ( <i>Note 5</i> )                                                      | -10  |      | 0               | dBm              |

| PHASE DETE                     | CTOR                                               |                                               |                                                                                                      |      |      |                 |                  |

| Fφ                             | Phase Detector                                     | Frequency                                     |                                                                                                      |      |      | 10              | MHz              |

| REFERENCE                      | OSCILLATOR                                         |                                               |                                                                                                      |      |      |                 |                  |

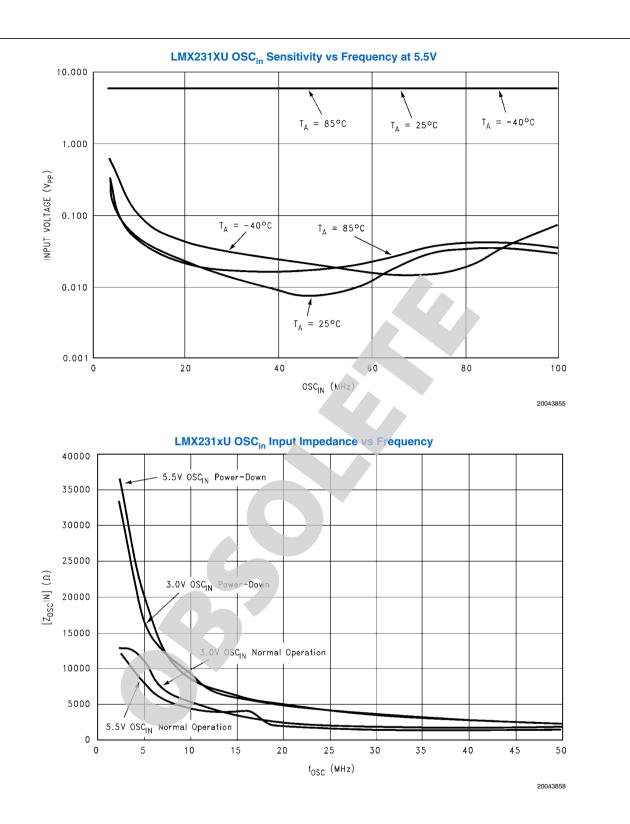

| Fosc                           | Operating Frequency,<br>Reference Oscillator Input |                                               |                                                                                                      | 2    |      | 50              | MHz              |

| V <sub>OSCIN</sub>             | Input Sensitivity<br>Oscillator Input              |                                               | (Note 6)                                                                                             | 0.5  |      | V <sub>cc</sub> | $V_{P-P}$        |

| IH                             | OSC <sub>IN</sub> Input Cu                         | irrent                                        | V <sub>IH</sub> = V <sub>CC</sub> = 5.5V                                                             |      |      | 100             | μA               |

| IL                             | OSC <sub>IN</sub> Input Cu                         | irrent                                        | $V_{IL} = 0, V_{CC} = 5.5V$                                                                          | -100 |      |                 | μA               |

| / <sub>OSC<sub>OUT</sub></sub> | OSC <sub>OUT</sub> Bias L                          | evel                                          | OSC <sub>IN</sub> Open                                                                               |      | 1.5  |                 | V                |

| D <sub>OSCout</sub>            | OSC <sub>OUT</sub> Duty Cycle                      |                                               | $OSC_{IN} = 20 \text{ MHz}, 0.5 \text{ V}_{P-P},$<br>$OSC_{IN} \text{ Duty Cycle} = 50\%$            |      | 50   |                 | %                |

| OSCOUT                         | OSC <sub>OUT</sub> Level                           |                                               | OSC <sub>IN</sub> = 20 MHz, 0.5 V <sub>P-P</sub> ,<br>OSC <sub>OUT</sub> Load = 10 pF II 10 k<br>Ohm |      | 2.6  |                 | V <sub>P-P</sub> |

| V <sub>он</sub>                | OSC <sub>OUT</sub> Output                          | t Voltage                                     | Ι <sub>OH</sub> = -500 μΑ                                                                            | 2.6  | 2.8  |                 | V                |

| V <sub>ol</sub>                | OSC <sub>OUT</sub> Output                          | t Voltage                                     | Ι <sub>ΟL</sub> = 500 μΑ                                                                             |      | 0.2  | 0.4             | V                |

| ОН                             | OSC <sub>OUT</sub> Output                          |                                               | V <sub>OH</sub> = 2.25 V                                                                             | 1    | -1.1 | i i             | mA               |

LMX2310U/LMX2311U/LMX2312U/LMX2313U

| Symbol                                               | Parameter                                   | Conditions ( <i>Note 3</i> )                                                                                                                      | Min                   | Тур  | Max                 | Units  |  |

|------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|---------------------|--------|--|

| I <sub>OL</sub>                                      | OSC <sub>OUT</sub> Output Current           | V <sub>OL</sub> = 0.75 V                                                                                                                          |                       | 1.1  |                     | mA     |  |

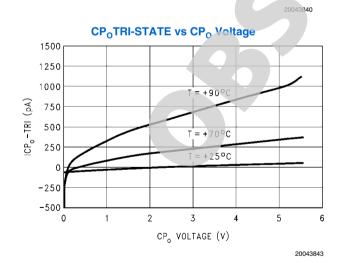

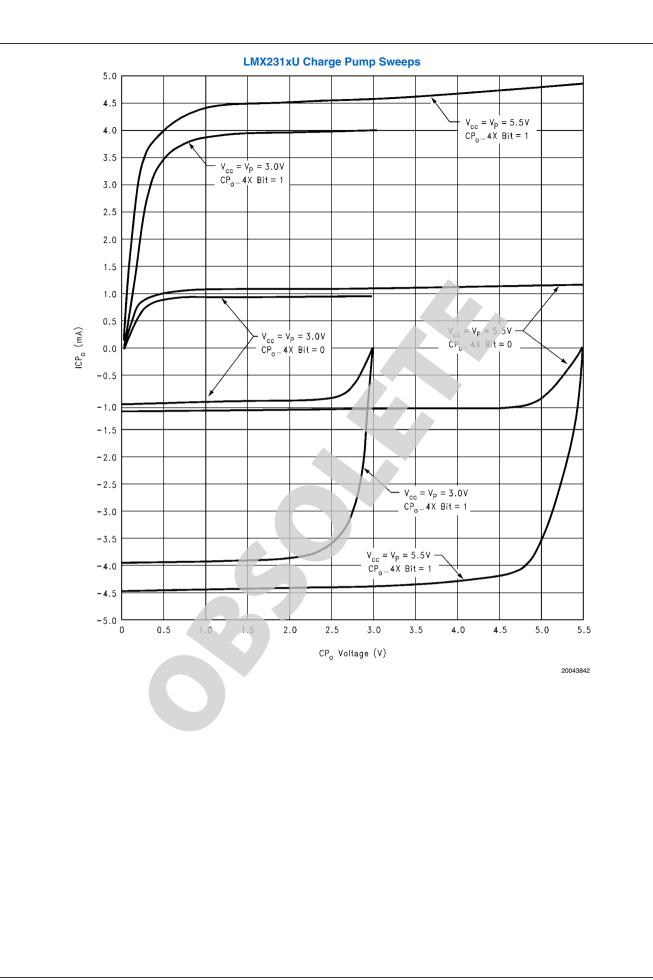

| CHARGE PUM                                           | P                                           |                                                                                                                                                   | •                     |      | •                   |        |  |

| ICPo- <sub>source</sub>                              |                                             | VCPo = Vp/2, <b>ICPo_4X</b> = 0                                                                                                                   | 0.8                   | 1.0  | 1.2                 | mA     |  |

| ICPo- <sub>sink</sub>                                | Charge Pump Output                          | VCPo = Vp/2, <b>ICPo_4X</b> = 0                                                                                                                   | -0.8                  | -1.0 | -1.2                | mA     |  |

| ICPo- <sub>source</sub>                              | Current (Note 7)                            | VCPo = Vp/2, <b>ICPo_4X</b> = 1                                                                                                                   | 3.2                   | 4.0  | 4.8                 | mA     |  |

| ICPo- <sub>sink</sub>                                |                                             | VCPo = Vp/2, <b>ICPo_4X</b> = 1                                                                                                                   | -3.2                  | -4.0 | -4.8                | mA     |  |

| ICPo- <sub>tri</sub>                                 | Charge Pump TRI-STATE<br>Current            | $0.5V \le VCP_0 \le V_P - 0.5V$                                                                                                                   | -2.5                  |      | 2.5                 | nA     |  |

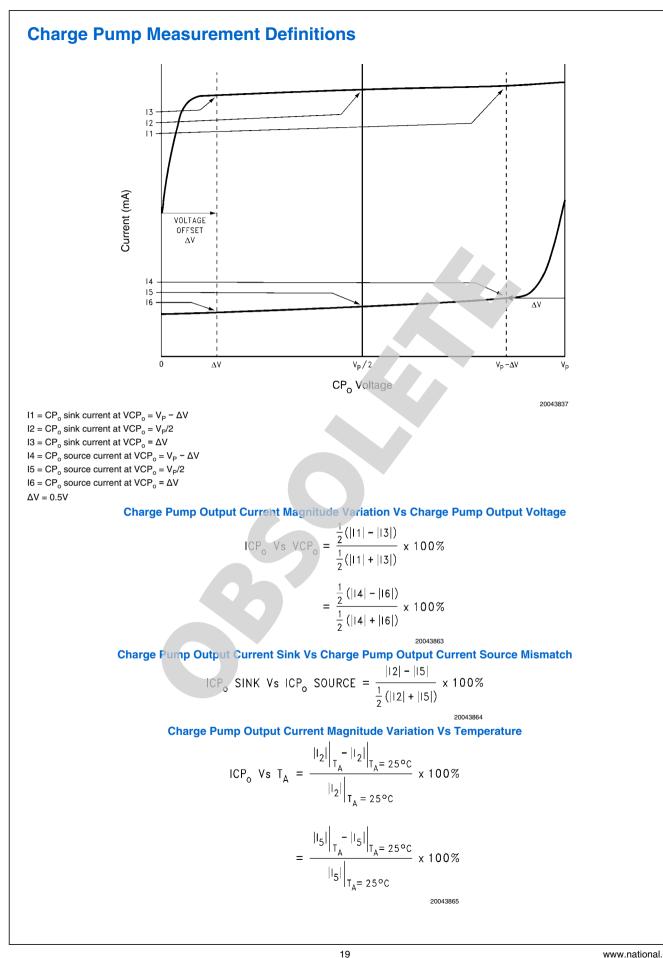

| ICPo- <sub>sink</sub> vs.<br>ICPo- <sub>source</sub> | CP Sink vs. Source<br>Mismatch              | VCPo = Vp/2<br>T <sub>A</sub> = 25°C<br>( <i>Note 8</i> )                                                                                         |                       | 3    | 10                  | %      |  |

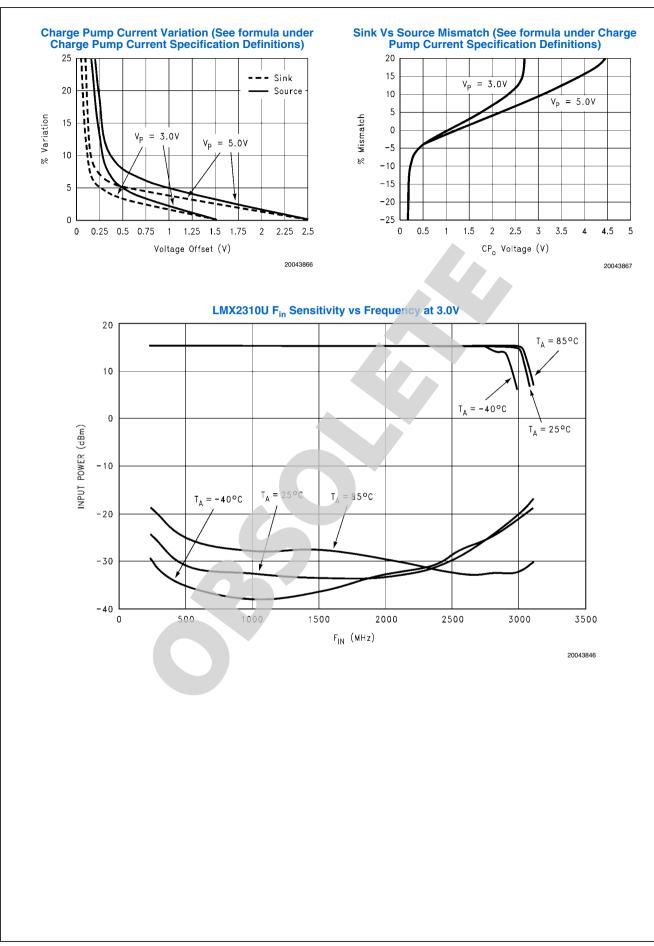

| ICPo vs VCPo                                         | CP Current vs. Voltage                      | $0.5V \le VCP_0 \le V_P - 0.5V$ $T_A = 25^{\circ}C (Note 8)$                                                                                      |                       | 8    | 15                  | %      |  |

| ICPo vs T <sub>A</sub>                               | CP Current vs. Temperature                  |                                                                                                                                                   |                       | 8    |                     | %      |  |

|                                                      | RFACE (Data, Clock, LE, CE)                 |                                                                                                                                                   |                       |      | <u> </u>            |        |  |

| V <sub>IH</sub>                                      | High-level Input Voltage                    | V <sub>µC</sub> = 1.72V to 5.5V                                                                                                                   | 0.8 V <sub>µC</sub>   |      |                     | V      |  |

| V <sub>IL</sub>                                      | Low-level Input Voltage                     | $V_{\mu C} = 1.72V$ to 5.5V                                                                                                                       |                       |      | 0.2 V <sub>µC</sub> | V      |  |

| I <sub>IH</sub>                                      | High-level Input Current                    | $V_{IH} = V_{\mu C} = 5.5V$                                                                                                                       | -1.0                  |      | 1.0                 | μA     |  |

| I <sub>IL</sub>                                      | Low-level Input Current                     | $V_{IL} = 0V, V_{\mu C} = 5.5V$                                                                                                                   | -1.0                  |      | 1.0                 | μA     |  |

| V <sub>OH</sub>                                      | High-level Output Voltage<br>(Pin 7–FoLD)   | I <sub>OH</sub> = 500 μA                                                                                                                          | $V_{\mu C} - 0.4$     |      |                     | V      |  |

|                                                      | High-level Output Voltage<br>(Pin 15–FL)    | I <sub>OH</sub> = -500 μA                                                                                                                         | V <sub>CC</sub> – 0.4 |      |                     | V      |  |

| V <sub>OL</sub>                                      | Low-level Output Voltage                    | I <sub>OL</sub> = 1.0 mA ( <i>Note 9</i> )                                                                                                        |                       | 0.1  | 0.4                 | V      |  |

| MICROWIRE T                                          | IMING (Data, Clock, LE, CE)                 |                                                                                                                                                   | •                     |      | · · ·               |        |  |

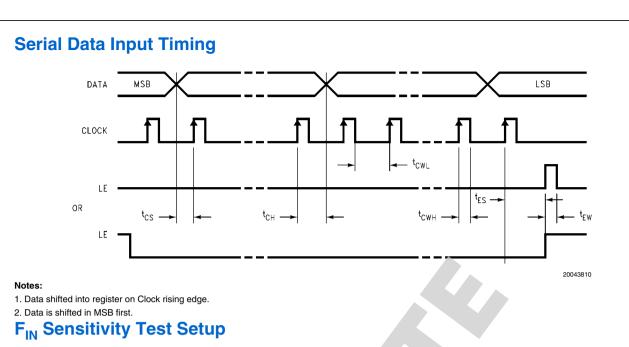

| t <sub>cs</sub>                                      | Data to Clock Set Up Time                   | (Note 10)                                                                                                                                         | 50                    |      |                     | ns     |  |

| t <sub>CH</sub>                                      | Data to Clock Hold Time                     | (Note 10)                                                                                                                                         | 20                    |      |                     | ns     |  |

| t <sub>CWH</sub>                                     | Clock Pulse Width High                      | (Note 10)                                                                                                                                         | 50                    |      |                     | ns     |  |

| t <sub>CWL</sub>                                     | Clock Pulse Width Low                       | (Note 10)                                                                                                                                         | 50                    |      |                     | ns     |  |

| t <sub>ES</sub>                                      | Clock to Load Enable Set Up<br>Time         | (Note 10)                                                                                                                                         | 50                    |      |                     | ns     |  |

| t <sub>EW</sub>                                      | Load Enable Pulse Width                     | (Note 10)                                                                                                                                         | 50                    |      |                     | ns     |  |

|                                                      | CHARACTERISTICS                             |                                                                                                                                                   | •                     | •    | • •                 |        |  |

| L <sub>N</sub> (f)                                   | Normalized Single Side-<br>Band Phase Noise | $F_{\phi} = 200 \text{ kHz}$ $F_{OSC} = 10 \text{ MHz}$ $V_{OSC} = 1.0 \text{ V}_{PP}$ $ICP_{O} = 4 \text{ mA}$ $T_{A} = 25^{\circ}C$ $(Note 11)$ |                       | -159 |                     | dBc/Hz |  |

| Symbol | Parameter              | Conditions ( <i>Note 3</i> )    | Min | Тур | Max | Units   |

|--------|------------------------|---------------------------------|-----|-----|-----|---------|

|        |                        | LMX2310U                        |     |     |     |         |

|        |                        | F <sub>IN</sub> = 2450 MHz      |     |     |     |         |

|        |                        | $F_{\phi} = 200 \text{ kHz}$    |     |     |     |         |

|        |                        | F <sub>OSC</sub> = 10 MHz       |     | -78 |     | dBc/Hz  |

|        |                        | $V_{OSC} = 1.0 V_{PP}$          |     | -70 |     |         |

|        |                        | ICP <sub>O</sub> = 4 mA         |     |     |     |         |

|        |                        | $T_A = 25^{\circ}C$             |     |     |     |         |

|        |                        | (Note 12)                       |     |     |     |         |

|        |                        | LMX2311U                        |     |     |     |         |

|        |                        | F <sub>IN</sub> = 1960 MHz      |     |     |     |         |

|        |                        | $F_{\phi} = 200 \text{ kHz}$    |     |     |     |         |

|        |                        | F <sub>OSC</sub> = 10 MHz       | -80 |     |     | dBc/Hz  |

|        |                        | $V_{OSC} = 1.0 V_{PP}$          |     |     |     | 000/112 |

|        |                        | ICP <sub>O</sub> = 4 mA         |     |     |     |         |

|        |                        | $T_A = 25^{\circ}C$             |     |     |     |         |

| _(f)   | Single Side-Band Phase | (Note 12)                       |     |     |     |         |

| -(1)   | Noise                  | LMX2312U                        |     |     |     |         |

|        |                        | F <sub>IN</sub> = 902 MHz       |     |     |     |         |

|        |                        | $F_{\varphi} = 200 \text{ kHz}$ |     |     |     |         |

|        |                        | F <sub>OSC</sub> = 10 MHz       |     | -85 |     | dBc/Hz  |

|        |                        | $V_{OSC} = 1.0 V_{PP}$          |     | -05 |     | UDC/112 |

|        |                        | ICP <sub>O</sub> = 4 mA         |     |     |     |         |

|        |                        | $T_A = 25^{\circ}C$             |     |     |     |         |

|        |                        | (Note 12)                       |     |     |     |         |

|        |                        | LMX2313U                        |     |     |     |         |

|        |                        | F <sub>IN</sub> = 450 MHz       |     |     |     |         |

|        |                        | $F_{\phi} = 50 \text{ kHz}$     |     |     |     |         |

|        |                        | F <sub>OSC</sub> = 10 MHz       |     | -85 |     | dBc/Hz  |

|        |                        | $V_{OSC} = 1.0 V_{PP}$          |     | -05 |     | UDC/TIZ |

|        |                        | $ICP_{O} = 4 \text{ mA}$        |     |     |     |         |

|        |                        | $T_A = 25^{\circ}C$             |     |     |     |         |

|        |                        | (Note 12)                       |     |     |     |         |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the conditions listed.

Note 2: This device is a high performance RF integrated circuit with an ESD rating <2 kV. Handling and assembly of this device should only be done at ESD free workstations.

Note 3: Typical Conditions are at a TA of 25°C.

Note 4: Icc current is measured with Clock, Data and LE pins connected to GND. OSCin and Fin pins are connected to Vcc. PWDN bit is program to 0. Icc current is the current into Vcc pin.

Note 5: See F<sub>IN</sub> Sensitivity Test Setup.

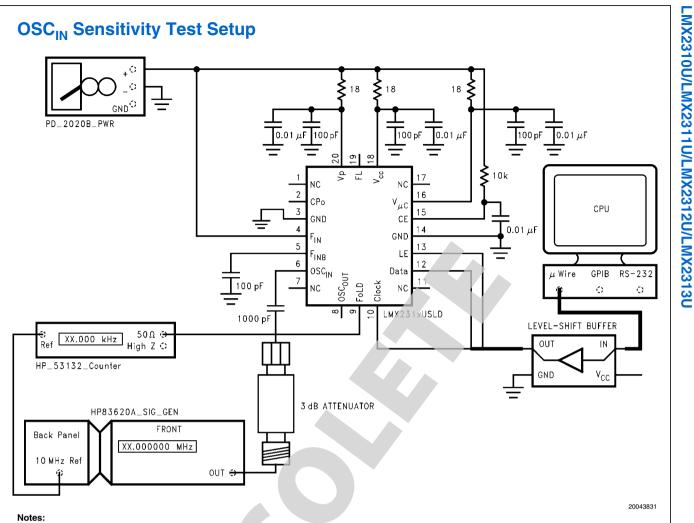

Note 6: See OSC<sub>IN</sub> Sensitivity Test Setup.

Note 7: Charge Pump Magnitude is controlled by CPo\_4X bit [R18].

Note 8: See Charge Pump Measurement Definition for detail on how these measurements are made.

Note 9: Analog Lock Detect open drain output pin only can be pulled up to  $V_{ext}$  that will not exceed 6.5V.

Note 10: See Serial Input Data Timing.

**Note 11:** Normalized Single-Side Band Phase Noise is defined as:  $L_N(f) = L(f) - 20 \log (F_{IN}/F_{\phi})$ , where L(f) is defined as the Single Side-Band Phase Noise. **Note 12:** Phase Noise is measured using a reference evaluation board with a loop bandwidth of approximately 12 kHz. The phase noise specification is the composite average of 3 measurements made at frequency offsets of 2.0 kHz, 2.5 kHz and 3.0 kHz.

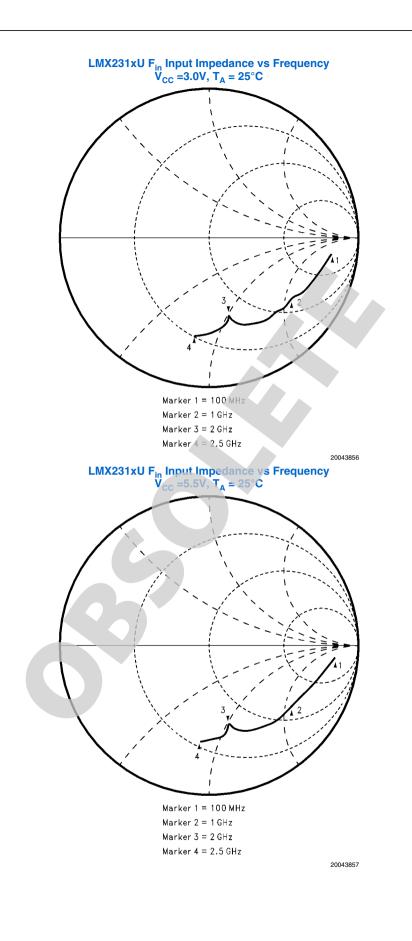

# **Typical Performance Characteristics**

|                          |                                 |                                      |                            |                                 | LMX231                               | xUSLD                      | F <sub>IN</sub> IMP             | EDANCE                               |                            |                                 |                                      |                          |

|--------------------------|---------------------------------|--------------------------------------|----------------------------|---------------------------------|--------------------------------------|----------------------------|---------------------------------|--------------------------------------|----------------------------|---------------------------------|--------------------------------------|--------------------------|

|                          |                                 | Vc                                   | <sub>c</sub> = 3.0V        | (T <sub>A</sub> = 2             | 5°C)                                 |                            |                                 | V <sub>C</sub>                       | <sub>C</sub> = 5.5V        | (T <sub>A</sub> = 2             | 5°C)                                 |                          |

|                          |                                 | F <sub>IN</sub><br>POWERED-U         | P                          | P                               | F <sub>IN</sub><br>POWERED-DOWN      |                            |                                 | F <sub>IN</sub><br>POWERED-UF        | D                          | P                               | F <sub>iN</sub><br>OWERED-DO         | WN                       |

| F <sub>IN</sub><br>(MHz) | Real<br>ZF <sub>IN</sub><br>(Ω) | Imaginary<br>ZF <sub>IN</sub><br>(Ω) | lZF <sub>IN</sub> l<br>(Ω) | Real<br>ZF <sub>IN</sub><br>(Ω) | Imaginary<br>ZF <sub>IN</sub><br>(Ω) | lZF <sub>IN</sub> l<br>(Ω) | Real<br>ZF <sub>IN</sub><br>(Ω) | Imaginary<br>ZF <sub>IN</sub><br>(Ω) | IZF <sub>IN</sub> I<br>(Ω) | Real<br>ZF <sub>IN</sub><br>(Ω) | lmaginary<br>ZF <sub>IN</sub><br>(Ω) | IZF <sub>IN</sub><br>(Ω) |

| 100                      | 452                             | -325                                 | 557                        | 440                             | -337                                 | 554                        | 460                             | -325                                 | 563                        | 444                             | -333                                 | 555                      |

| 200                      | 305                             | -278                                 | 413                        | 300                             | -276                                 | 408                        | 313                             | -277                                 | 418                        | 312                             | -275                                 | 416                      |

| 300                      | 225                             | -243                                 | 331                        | 225                             | -242                                 | 330                        | 235                             | -244                                 | 339                        | 237                             | -244                                 | 340                      |

| 400                      | 180                             | -219                                 | 283                        | 179                             | -217                                 | 281                        | 190                             | -221                                 | 291                        | 189                             | -221                                 | 291                      |

| 500                      | 147                             | –197                                 | 246                        | 145                             | -195                                 | 243                        | 155                             | -200                                 | 253                        | 155                             | -200                                 | 253                      |

| 600                      | 120                             | -175                                 | 212                        | 118                             | -173                                 | 209                        | 127                             | -179                                 | 219                        | 126                             | -179                                 | 219                      |

| 700                      | 102                             | -158                                 | 188                        | 100                             | -156                                 | 185                        | 108                             | -162                                 | 195                        | 107                             | -161                                 | 193                      |

| 800                      | 88                              | -141                                 | 166                        | 86                              | -139                                 | 163                        | 94                              | -146                                 | 174                        | 91                              | -143                                 | 169                      |

| 900                      | 78                              | -126                                 | 148                        | 75                              | -123                                 | 144                        | 83                              | -131                                 | 155                        | 81                              | -129                                 | 152                      |

| 1000                     | 73                              | -117                                 | 138                        | 72                              | –113                                 | 134                        | 78                              | -118                                 | 141                        | 75                              | –116                                 | 138                      |

| 1100                     | 64                              | -109                                 | 126                        | 63                              | -106                                 | 123                        | 69                              | -112                                 | 132                        | 68                              | -111                                 | 130                      |

| 1200                     | 57                              | -98                                  | 113                        | 55                              | -95                                  | 110                        | 61                              | -102                                 | 119                        | 59                              | -100                                 | 116                      |

| 1300                     | 52                              | -90                                  | 104                        | 52                              | -86                                  | 100                        | 55                              | -95                                  | 110                        | 55                              | -91                                  | 106                      |

| 1400                     | 46                              | -84                                  | 96                         | 46                              | -83                                  | 95                         | 49                              | -88                                  | 101                        | 50                              | -87                                  | 100                      |

| 1500                     | 41                              | -75                                  | 85                         | 40                              | -73                                  | 83                         | 44                              | _79                                  | 90                         | 42                              | -78                                  | 89                       |

| 1600                     | 39                              | -69                                  | 79                         | 37                              | -66                                  | 76                         | 41                              | -73                                  | 84                         | 40                              | -70                                  | 81                       |

| 1700                     | 35                              | -61                                  | 70                         | 34                              | -59                                  | 68                         | 37                              | -65                                  | 75                         | 36                              | -63                                  | 73                       |

| 1800                     | 34                              | -55                                  | 65                         | 33                              | -52                                  | 62                         | 35                              | -58                                  | 68                         | 34                              | -56                                  | 66                       |

| 1900                     | 35                              | -50                                  | 61                         | 35                              | -4.7                                 | 59                         | 35                              | -52                                  | 63                         | 35                              | -50                                  | 61                       |

| 2000                     | 37                              | -50                                  | 62                         | 37                              | -48                                  | 61                         | 38                              | -50                                  | 63                         | 38                              | -48                                  | 61                       |

| 2100                     | 34                              | -52                                  | 62                         | 33                              | -51                                  | 61                         | 36                              | -52                                  | 63                         | 34                              | -51                                  | 61                       |

| 2200                     | 29                              | -50                                  | 58                         | 27                              | -48                                  | 55                         | 32                              | -51                                  | 60                         | 30                              | -50                                  | 58                       |

| 2300                     | 25                              | -48                                  | 54                         | 23                              | -45                                  | 51                         | 27                              | -50                                  | 57                         | 25                              | -48                                  | 54                       |

| 2400                     | 20                              | -44                                  | 48                         | 19                              | 42                                   | 46                         | 23                              | -47                                  | 52                         | 21                              | -44                                  | 49                       |

| 2500                     | 18                              | -41                                  | 45                         | 16                              | -38                                  | 41                         | 20                              | -43                                  | 47                         | 18                              | -41                                  | 45                       |

### Notes:

- 1. LMX2310/1/2U Test Conditions: NA\_CNTR = 16, NB\_CNTR = 312, P = 1, FoLD2 = 1, FoLD1 = 1, FoLD0 = 0, PWDN = 0.

- 2. LMX2313U Test Conditions: NA\_CNTR = 0, NB\_CNTR = 625, P = 1, FoLD2 = 1, FoLD1 = 1, FoLD0 = 0, PWDN = 0.

- 3. Sensitivity limit is reached when the frequency error of the divided RF input is greater than or equal to 1 Hz.

- 1. Test Conditions: R\_CNTR = 1000, FoLD2 = 1, FoLD1 = 0, FoLD0 = 1, PWDN = 0.

- 2. Sensitivity limit is reached when the frequency error of the divided RF input is greater than or equal to 1 Hz.

# **1.0 Functional Description**

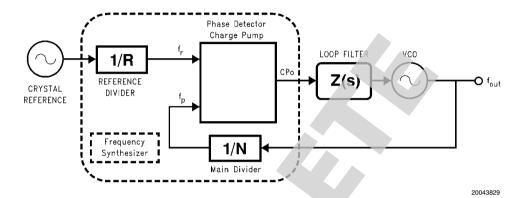

The basic phase-lock-loop (PLL) configuration consists of a high-stability crystal reference oscillator, a frequency synthesizer such as the National Semiconductor LMX2310/1/2/3U, a voltage controlled oscillator (VCO), and a passive loop filter. The frequency synthesizer includes a phase detector, a current mode charge pump, as well as a programmable reference divider and feedback frequency divider. The VCO frequency is established by dividing the crystal reference signal down via the reference divider to obtain a frequency that sets the comparison frequency. This reference signal,  $f_{\rm r}$ , is then presented to the input of a phase/frequency detector and compared with another signal,  $f_{\rm p}$ , which was obtained by dividing the crystal reference divider to reference divider to a phase/frequency detector and compared with another signal,  $f_{\rm p}$ , which was obtained by dividing the crystal reference divider to a phase detector and compared with another signal,  $f_{\rm p}$ , which was obtained by dividing the crystal reference divider to charge phase detector and compared with another signal,  $f_{\rm p}$ , which was obtained by dividing the crystal reference divider to charge phase detector and compared with another signal,  $f_{\rm p}$ , which was obtained by dividing the crystal reference divider to charge phase detector and compared with another signal,  $f_{\rm p}$ , which was obtained by dividing the crystal compared phase detector and compared phase detector and compared phase detector and compared phase detector and compared phase detector detector and compared phase detector detector and compared phase detector detector detector and compared phase detector detector detector detector and compared with another signal detector detecto

viding the VCO frequency down by way of the feedback counter. The phase/frequency detector measures the phase error between the  $f_r$  and  $f_p$  signals and outputs control signals that are directly proportional to the phase error. The charge pump then pumps charge into or out of the loop filter based on the magnitude and direction of the phase error. The loop filter converts the charge into a stable control voltage for the VCO. The phase/frequency detector's function is to adjust the voltage presented to the VCO until the feedback signal's frequency and phase match that of the reference signal. When this "phase-locked" condition exists, the RF VCO frequency will be N times that of the comparison frequency, where N is the feedback divider ratio.

# **1.1 REFERENCE OSCILLATOR**

The reference oscillator frequency for the RF PLL is provided from the external source via the OSC<sub>in</sub> pin. The low noise reference buffer circuit supports frequencies from 2 MHz to 50 MHz with a minimum input sensitivity of 0.5 V<sub>pp</sub>. The input can be driven from an external CMOS or TTL logic gate. The output of this buffer drives the R COUNTER. The output of the buffer also connects to an oscillator/buffer circuit. Its output connects to the OSC<sub>out</sub> pin. The oscillator/buffer circuit can be used as a buffer to provide the reference frequency to other circuitry. It can also be used as an oscillator with a crystal/ resonator with proper components connected between OSC<sub>in</sub> and OSC<sub>out</sub> pins to generate a reference frequency.

# 1.2 REFERENCE DIVIDER (R COUNTER)

The reference divider is comprised of a 15-bit CMOS binary counter that supports a continuous integer divide range from 2 to 32,767. The divide ratio should be chosen such that the maximum phase comparison frequency of 10 MHz is not exceeded. The reference divider circuit is clocked by the output of the reference buffer circuit. The output of the reference divider circuit. The frequency of the reference input of the phase detector circuit. The frequency of the reference input to the phase detector (also referred to as the comparison frequency) is equal to reference oscillator frequency divided by the reference divider ratio. Refer to Section 3.2.1 for details on programming the R COUNTER.

## **1.3 PRESCALERS**

The LMX2310/1/2U contains a selectable, dual modulus 32/33 and 16/17 prescaler. The LMX2313U contains a selectable, dual modulus 16/17 and 8/9 prescaler.

| PLL<br>Input<br>Frequency | PLL<br>Part<br>Numbers | Allowable<br>Prescaler<br>Values |  |

|---------------------------|------------------------|----------------------------------|--|

| F <sub>IN</sub> > 1.2 GHz | LMX2310/1U             | 32/33                            |  |

| F <sub>IN</sub> ≤ 1.2 GHz | LMX2310/1/2U           | 16/17 or 32/33                   |  |

| F <sub>IN</sub> ≤ 600 MHz | LMX2313U               | 8/9 or 16/17                     |  |

The complimentary  $F_{IN}$  and  $F_{INB}$  input pins drive the input of a bipolar, differential-pair amplifier. The output of the bipolar, differential-pair amplifier drives a chain of ECL D-type flipflops in a dual modulus configuration. The output of the prescaler is used to clock the subsequent programmable feedback divider. Refer to Section 3.3.2 for details on programming the Prescaler Value.

## **1.4 FEEDBACK DIVIDER (N COUNTER)**

The N COUNTER is clocked by the output of the prescaler. The N COUNTER is composed of a 13-bit programmable integer divider. The 5-bit swallow counter is part of the prescaler. Selecting a 32/33 prescaler provides a minimum continuous divider range from 992 to 262,143 while selecting a 16/17 prescaler value allows for continuous divider values from 240 to 131,071. In the LMX2313U, selecting a 8/9 prescaler provides a minimum continuous divider range from 56 to 65535.

| N = (P x NB_CNTR) + NA_CNTR  |                                     |  |  |  |  |

|------------------------------|-------------------------------------|--|--|--|--|

| $F_{IN} = N \times F_{\phi}$ |                                     |  |  |  |  |

| Definitions                  |                                     |  |  |  |  |

| $F_{\phi}$                   | Phase Detector Comparison Frequency |  |  |  |  |

| F <sub>IN</sub>              | RF Input Frequency                  |  |  |  |  |

| Р                            | Prescaler Value                     |  |  |  |  |

| NA_CNTR                      | A Counter Value                     |  |  |  |  |

| NB_CNTR                      | B Counter Value                     |  |  |  |  |

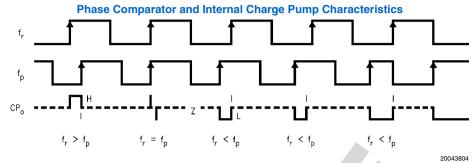

# 1.5 PHASE/FREQUENCY DETECTORS

The phase/frequency detector is driven from the N and R COUNTER outputs. The maximum frequency at the phase detector inputs is 10 MHz. The phase detector outputs control the charge pump. The polarity of the pump-up or pump-down

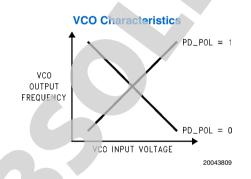

control signals are programmed using the PD\_POL control bit, depending on whether the RF VCO tuning characteristics are positive or negative (see programming description in Section 3.2.2). The phase/frequency detector has a detection range of  $-2\pi$  to  $+2\pi$ .

Note 13: The minimum width of the pump up and pump down current pulses occur at the CP<sub>o</sub> pin when the loop is phase-locked.

Note 14: The diagram assumes that PD\_POL = 1

Note 15:  $f_r$  is the phase comparator input from the R Divider

Note 16:  ${\rm f}_{\rm p}$  is the phase comparator input from the N Divider

Note 17:  $CP_o$  is charge pump output

# **1.6 CHARGE PUMP**

The charge pumps directs charge into or out of an external loop filter. The loop filter converts the charge into a stable control voltage which is applied to the tuning input of a VCO. The charge pump steers the VCO control voltage towards  $V_p$  during pump-up events and towards GND during pump-down events. When locked,  $CP_o$  is primarily in a TRI-STATE condition with small corrections occurring at the phase comparison rate. The charge pump output current magnitude can be selected as 1.0 mA or 4.0 mA by programming the ICPo\_4X bits. When TO\_CNTR[11:0] = 1, the charge pump output current magnitude is set to 4.0 mA. Refer to Section 3.2.3 and 3.4.2 for details on programming the charge pump output current magnitude.

# **1.7 MICROWIRE SERIAL INTERFACE**

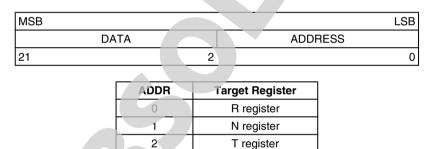

The programmable register set is accessed through the MI-CROWIRE serial interface. The interface is comprised of three signal pins: CLOCK, DATA and LE (Latch Enable). The MICROWIRE circuitry is referenced to  $V_{\mu C}$ , which allows the circuitry to operate down to a 1.72V source. Serial data is clocked into a 22-bit shift register from DATA on the rising edge of CLOCK. The serial data is clocked in MSB first. The last two bits decode the internal register address. On the rising edge of LE, the data stored in the shift register is loaded into one of the three latches based on the address bits. The synthesizer can be programmed even in the power-down state. A complete programming description is in Section 3.0.

# **1.8 MULTI-FUNCTION OUTPUTS**

The LMX2310/1/2/3U FoLD output pin is a multi-function output that can be configured as an analog lock detect, a digital lock detect, and a monitor of the output of the reference divider and the feedback divider circuits. The FoLD output pin is referenced to the V<sub>µC</sub> supply. The FoLD0, FoLD1 and FoLD2 bits are used to select the desired output function. A complete programming description of the FoLD output pin is in Section 3.2.5.

# 1.8.1 Analog Lock Detect

When programmed for analog lock detect, the analog lock detect status is available on the FoLD output pin. When the charge pump is inactive, the lock detect output goes to a high impedance in the open drain configuration and to a  $V_{\mu C}$  source in a push-pull configuration. It goes low when the charge pump is active during a comparison cycle. The analog lock detect status can be programmed in either an open drain or push-pull configuration. The push-pull output is referenced to  $V_{\mu C}$ .

## 1.8.2 Digital Lock Detect

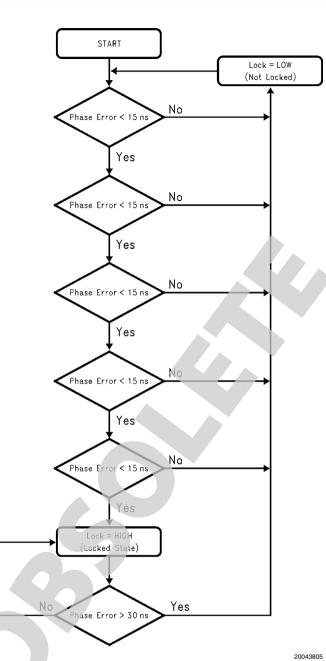

When programmed for digital lock detect, the digital lock detect status is available on the FoLD pin. The digital lock detect filter compares the phase difference of the inputs from the phase detector to a RC generated delay of approximately 15 ns. To enter the locked state (LD = High), the phase error must be less than the 15 ns RC delay for 5 consecutive reference cycles. Once in lock, the RC delay is changed to approximately 30 ns. To exit the locked state, the phase error must be greater than the 30 ns RC delay. When a PLL is in powerdown mode, the respective lock detect output is always low. A flow chart of the digital lock detect filter follows:

## 1.9 Fastlock™ OUTPUT

The FL pin can be used as the Fastlock output. The FL pin can also be programmed as constant low, constant high (referenced to  $V_{CC}$ ), or constant high impedance, selectable through the T register. When the device is configured in Fastlock mode, the charge pump current can be increased 4x while maintaining loop stability by synchronously switching a parallel loop filter resistor to ground with the FL pin, resulting in a ~2x increase in loop bandwidth. The loop bandwidth, the zero gain crossover point of the open loop gain, is effectively shifted up in frequency by a factor of the square root of 4 = 2during Fastlock mode. For  $\omega' = 2 \omega$ , the phase margin during Fastlock also will remain constant. The user calculates the loop filter component values for the normal steady state considerations. The device configuration ensures that as long as a second resistor, equal to the primary resistor value, is wired in appropriately, the loop will lock faster without any additional stability considerations.

The PLL can be configured to be in either the Fastlock mode continuously or in the Fastlock mode that uses a timeout counter to switch it back to the normal mode. In the Fastlock mode the charge pump current is set to 4 mA and the FL pin is set low. If the user sets the PLL to be in the Fastlock mode continuously he can send the R register with CPo 4X set low (R[18] = 0) and sets TO CNTR[11:0] to 1. The user can set the PLL to normal mode (1 mA mode and set the FL pin to TRI-STATE mode) by programming TO\_CNTR[11:0] to 0. If the user elects to use the timeout counter, he can program the timeout counter from 4 to 4095. The timeout counter will count down the programmed number of phase detector reference cycles. After the programmed number of phase detector reference cycles is reached, it will automatically set the charge pump current to the 1 mA mode and set the FL pin to TRI-STATE mode. A complete programming description is in Section 3.4.2.

# 2.0 Power-Down

The LMX2310/1/2/3U are power controlled through logical control of the CE pin in conjunction with programming of the PDWN and CPo\_TRI bits. A truth table is provided that describes how the state of the CE pin, the PDWN bit and CPo\_TRI bit set the operating mode of the device. A complete programming description of Power-Down is provided in Section 3.3.1.

| CE | PWDN | CPo_TRI | Operating Mode            |

|----|------|---------|---------------------------|

| 0  | Х    | Х       | Power-down (Asynchronous) |

| 1  | 0    | 0       | Normal Operation          |

| 1  | 1    | 0       | Power-down (Synchronous)  |

| 1  | 1    | 1       | Power-down (Asynchronous) |

### X = Don't Care

When the device enters the power-down mode, the oscillator buffer, RF prescaler, phase detector, and charge pump circuits are all disabled. The  $OSC_{IN}$ , CPo,  $F_{IN}$ ,  $F_{INB}$ , LD pins are all forced to a high impedance state. The reference divider

# 3.0 Programming Description

# 3.1 MICROWIRE INTERFACE

and feedback divider circuits are disabled and held at the load point during power-down. When the device is programmed to normal operation, the oscillator buffer, RF prescaler, phase detector, and charge pump circuits are all powered on. The feedback divider and the reference divider are held at the load point. This allows the RF prescaler, feedback divider, reference oscillator, the reference divider and prescaler circuitry to reach proper bias levels. After a 1.5 µs delay, the feedback and reference divider are enabled and they resume counting in "close" alignment (The maximum error is one prescaler cycle). The MICROWIRE control register remains active and capable of loading and latching in data while in the powerdown mode.

The synchronous power-down function is gated by the charge pump. When the device is configured for synchronous powerdown, the device will enter the power-down mode upon the completion of the next charge pump pulse event.

The asynchronous power-down function is NOT gated by the completion of a charge pump pulse event. When the device is configured for asynchronous power-down, the part will go into power-down mode immediately.

The MICROWIRE interface is comprised of a 22-bit shift register and three control registers. The shift register consists of a 20-bit DATA field and a 2-bit address (ADDR) field as shown below. Data is loaded into the shift register on the rising edges of the CLOCK signal MSB first. When Latch Enable transitions HIGH, data stored in the shift register is loaded into either the R, N or T register depending on the state of the ADDR bit. The DATA field assignments for the R, N and T registers are shown in Section 3.1.1.

# 3.1.1 Register Map

| Register | Mos   | t Significa | int Bit     |            |            | SHI                       | -T RE | EGISTER  | BIT I |    |      | N    |     |   |              | l | Lea  | st S | igni  | ficar | nt Bit |   |  |

|----------|-------|-------------|-------------|------------|------------|---------------------------|-------|----------|-------|----|------|------|-----|---|--------------|---|------|------|-------|-------|--------|---|--|

|          | 21    | 20          | 19          | 18         | 17         | 16                        | 15    | 14       | 13    | 12 | 11   | 10   | 9   | 8 | 7            | 6 | 5    | 4    | 3     | 2     | 1      | 0 |  |

|          |       | Data Field  |             |            |            |                           |       |          |       |    |      |      |     |   | lress<br>eld |   |      |      |       |       |        |   |  |

| R        | FoLD1 | FoLD0       | CPo_<br>TRI | CP0_<br>4x | PD_<br>POL |                           |       |          |       | R_ | _CNT | R[14 | :0] |   |              |   |      |      |       |       | 0      | 0 |  |

| Ν        | PWDN  | Р           |             |            |            |                           | B_C   | NTR[12:0 | D]    |    |      |      |     |   |              | A | ∖_CI | NTF  | R[4:C | )]    | 0      | 1 |  |

| Т        | 0     | 0           | 0           | 0          | 0          | 0 0 0 FoLD2 TO_CNTR[11:0] |       |          |       |    |      |      |     |   |              |   | 1    | 0    |       |       |        |   |  |

# 3.2 R REGISTER

The R register contains the R\_CNTR control word and PD\_POL, CPo\_4X, CP\_TRI, FoLD0, FoLD1 control bits. The detailed descriptions and programming information for each control word is discussed in the following sections.

| Register | Most Sig | nificant Bit | t                       |                        | SHIF       | T RE | GIST | ER B | IT LO | CATI | ON |    |   |             |   | Lea | st S | igni | ficar | nt Bit | ; |   |

|----------|----------|--------------|-------------------------|------------------------|------------|------|------|------|-------|------|----|----|---|-------------|---|-----|------|------|-------|--------|---|---|

|          | 21       | 20           | 19                      | 18                     | 17         | 16   | 15   | 14   | 13    | 12   | 11 | 10 | 9 | 8           | 7 | 6   | 5    | 4    | 3     | 2      | 1 | 0 |

|          |          | Data Field   |                         |                        |            |      |      |      |       |      |    |    |   | Addı<br>Fie |   |     |      |      |       |        |   |   |

| R        | FoLD1    | FoLD0        | CP <sub>O-</sub><br>TRI | CP <sub>O-</sub><br>4X | PD_<br>POL |      |      |      |       |      |    |    |   |             |   |     |      | 0    | 0     |        |   |   |

|          | •        |              |                         |                        |            |      |      |      |       |      |    |    |   |             |   |     |      |      |       |        |   |   |

# 3.2.1 R\_CNTR[14:0] Reference Divider (R COUNTER) R[16:2]

The reference divider can be programmed to support divide ratios from 2 to 32,767. Divide ratios of less than 2 are prohibited.

| Divider Value |   |   |   |   |   |   | R_( | CNTR[1 | 4:0] |   |   |   |   |   |   |

|---------------|---|---|---|---|---|---|-----|--------|------|---|---|---|---|---|---|

| 2             | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0      | 0    | 0 | 0 | 0 | 0 | 1 | 0 |

| 3             | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0      | 0    | 0 | 0 | 0 | 0 | 1 | 1 |

| •             | • | • | • | • | • | • | •   | •      | •    | • | • | • | • | • | • |

| 32,767        | 1 | 1 | 1 | 1 | 1 | 1 | 1   | 1      | 1    | 1 | 1 | 1 | 1 | 1 | 1 |

# 3.2.2 PD\_POL Phase Detector Polarity R[17]

The PD\_POL control bit is used to set the polarity of the phase detector based on the VCO tuning characteristic.

| Control Bit | Register Location | Description             | Func                               | tion                               |

|-------------|-------------------|-------------------------|------------------------------------|------------------------------------|

| Control Bit | negister Location | Description             | 0                                  | 1                                  |

| PD_POL      | R[17]             | Phase Detector Polarity | Negative VCO Tuning Characteristic | Positive VCO Tuning Characteristic |

# 3.2.3 CPo\_4X Charge Pump Output Current R[18]

The CPo\_4X control bit allows the charge pump output current magnitude to be switched from 1 mA to 4 mA. This happens asynchronously or immediately with the change in CPo\_4X bit.

| - | Control Bit | Register Location | Description                          | Func       | ction      |

|---|-------------|-------------------|--------------------------------------|------------|------------|

|   | Control Bit | Register Location | Description                          | 0          | 1          |

|   | CPo_4X      | R[18]             | Charge Pump Output Current Magnitude | 1X Current | 4X Current |

# 3.2.4 CPo\_TRI Charge Pump TRI-STATE R[19]

The CPo\_TRI control bit allows the charge pump to be switched between a normal operating mode and a high impedance output state. This happens asynchronously or immediately with the change in CPo\_TRI bit.

| Control Bit | Register Location | Description           | Funct                       | ion                                           |

|-------------|-------------------|-----------------------|-----------------------------|-----------------------------------------------|

| Control Bit | negister Location | Description           | 0                           | 1                                             |

| CPo_TRI     | R[19]             | Charge Pump TRI-STATE | Charge Pump Operates Normal | Charge Pump Output in High<br>Impedance State |

# 3.2.5 FoLD2,1,0 FoLD Output Truth Table T[14],R[21],R[20]

The FoLD2, FoLD1 and FoLD0 are used to select which signal is routed to FoLD pin.

| T[14] | R[21] | R[20] | Fol D Output State                                            |

|-------|-------|-------|---------------------------------------------------------------|

| FoLD2 | FoLD1 | FoLD0 | FoLD Output State                                             |

| 0     | 0     | 0     | Disabled (TRI-STATE FoLD)                                     |

| 0     | 0     | 1     | Lock Detect—Analog (Push/Pull), Reference to V <sub>µc</sub>  |

| 0     | 1     | 0     | Lock Detect—Analog (Open Drain)                               |

| 0     | 1     | 1     | Reset R and N Dividers and TRI-STATE Charge Pump              |

| 1     | 0     | 0     | Lock Detect—Digital (Push/Pull), Reference to V <sub>µC</sub> |

| 1     | 0     | 1     | R COUNTER Output (Push/Pull), Reference to $V_{\mu C}$        |

| 1     | 1     | 0     | N Counter Output (Push/Pull), Reference to V <sub>µC</sub>    |

| 1     | 1     | 1     | Reserved (Do Not Use)                                         |

# 3.3 N REGISTER

The N register contains the PWDN (Power-Down), P (Prescaler), NA\_CNTR, and NB\_CNTR control words. The detailed descriptions and programming information for each control word is discussed in the following sections.

| Register | Most | Signif | icant E | Bit |    |    | S⊦ | IIFT R | EGIS   | TER E | SIT LO | CATI | ИС |   |   |   | L   | .east | Sigr  | nifica | nt Bit           |   |

|----------|------|--------|---------|-----|----|----|----|--------|--------|-------|--------|------|----|---|---|---|-----|-------|-------|--------|------------------|---|

|          | 21   | 20     | 19      | 18  | 17 | 16 | 15 | 14     | 13     | 12    | 11     | 10   | 9  | 8 | 7 | 6 | 5   | 4     | 3     | 2      | 1                | 0 |

|          |      | -      | -       | -   | -  |    |    | Ľ      | Data F | ïeld  |        |      |    |   |   |   |     |       |       |        | Address<br>Field |   |

| N        | PWDN | Р      |         |     |    |    | I  | B_CN   | TR[12  | :0]   |        |      |    |   |   |   | A_C | NTR   | [4:0] |        | 0                | 1 |

# 3.3.1 PWDN Power-Down N[21]

The PWDN control bit along with  $CP_o$ \_TRI control bit is used to power-down the PLL. The LMX2310/1/2/3U can be synchronous or asynchronous powered down by first setting the  $CP_o$ \_TRI bit and then setting the PWDN bit. To power up from the synchronous Power-Down mode, the  $CP_o$ \_TRI bit will have to be reset to 0.

| N[21] | R[19]                | Operating Made            |

|-------|----------------------|---------------------------|

| PWDN  | CP <sub>O</sub> _TRI | Operating Mode            |

| 0     | 0                    | Normal Operation          |

| 1     | 0                    | Power-down (Synchronous)  |

| 1     | 1                    | Power-down (Asynchronous) |

# 3.3.2 P Prescaler N[20]

The LMX2310/1/2/3U contains two dual modulus prescalers. The P control bit is used to set the prescaler value.

| N[20] | Prescaler Value<br>LMX2310/1/2U | Prescaler Value<br>LMX2313U |

|-------|---------------------------------|-----------------------------|

| 0     | 16/17                           | 8/9                         |

| 1     | 32/33                           | 16/17                       |

| PLL Input Frequency       | Allowable Prescaler Values |

|---------------------------|----------------------------|

| F <sub>IN</sub> > 1.2 GHz | 32/33                      |

| F <sub>IN</sub> ≤ 1.2 GHz | 16/17 or 32/33             |

| F <sub>IN</sub> ≤ 600 MHz | 8/9 or 16/17               |

# 3.3.3 B\_CNTR[12:0] B COUNTER N[19:7]

The NB\_CNTR control word is used to program the B counter. The B counter is a 13-bit binary counter used in the programmable feedback divider. The B counter can be programmed to values ranging from 3 to 8,191. See Section 1.4 for details on how the value of the B counter should be selected.

| Divider Value |   | B_CNTR[12:0] |   |   |   |   |   |   |   |   |   |   |   |

|---------------|---|--------------|---|---|---|---|---|---|---|---|---|---|---|

| 3             | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4             | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| •             | • | •            | • | • | • | • | • | • | • | • | • | • | • |

| 8,191         | 1 | 1            | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

**NOTE:** B counter divide ratio must be  $\geq$  3.

# 3.3.4 A\_CNTR[4:0] A Counter N[6:2]

The NA\_CNTR control word is used to program the A counter. The A counter is a 5-bit swallow counter used in the programmable feedback divider. The A counter can be programmed to values ranging from 0 to 31. See Section 1.4 for details on how the value of the A counter should be selected.

| Divide<br>Ratio | A_CNTR[4:0] |   |   |   |   |  |  |  |  |  |  |  |  |

|-----------------|-------------|---|---|---|---|--|--|--|--|--|--|--|--|

| 0               | 0           | 0 | 0 | 0 | 0 |  |  |  |  |  |  |  |  |

| 1               | 0           | 0 | 0 | 0 | 1 |  |  |  |  |  |  |  |  |

| •               | •           | • | • | , | • |  |  |  |  |  |  |  |  |

| 31              | 1           | 1 | 1 | 1 | 1 |  |  |  |  |  |  |  |  |

**NOTES:** A counter divide ratio must be  $\leq$  P and A counter divide ratio must be  $\leq$  B counter divide ratio.

# 3.4 T REGISTER

The T register contains the TO\_CNTR control word and FoLD2 control bit. The detailed descriptions and programming information for each control word is discussed in the following sections.

| Register | Ν                 | /lost S | ignific | ant Bi | t |   |    | SHIFT REGISTER BIT LOCATION |               |    |    |                  |   |   |   |   | Least Significant Bit |   |   |   |   |   |

|----------|-------------------|---------|---------|--------|---|---|----|-----------------------------|---------------|----|----|------------------|---|---|---|---|-----------------------|---|---|---|---|---|

|          | 21 20 19 18 17 16 |         |         |        |   |   | 15 | 14                          | 13            | 12 | 11 | 10               | 9 | 8 | 7 | 6 | 5                     | 4 | 3 | 2 | 1 | 0 |

|          | Data Field        |         |         |        |   |   |    |                             |               |    |    | Address<br>Field |   |   |   |   |                       |   |   |   |   |   |

| Т        | 0                 | 0       | 0       | 0      | 0 | 0 | 0  | FoLD2                       | TO_CNTR[11:0] |    |    |                  |   |   |   |   |                       | 1 | 0 |   |   |   |

# 3.4.1 FoLD2 FoLD Output (P/O Output Truth Table) T[14]

See Section 3.2.5 for FoLD Output Truth Table details.

# 3.4.2 TO\_CNTR[11:0] Timeout Counter Table T[13:2]

When the Fastlock Timeout counter (TO\_CNTR) is loaded with 0, Fastlock is off, the FL pin will be in TRI-STATE mode, and the charge pump current will be the value specified by the Charge Pump Magnitude bit, R[18]. When the Timeout counter is loaded with 1, the FL pin is 0 (pulled low) and the charge pump current will be at the 4X state. When the Timeout counter is loaded with 2, the FL pin will again be set to 0 (pulled low), but the charge pump current will be controlled by R[18]. When the Timeout counter is loaded with 3, the FL pin is 1 (pulled high) with the charge pump current will be controlled by R[18]. When loaded with 4 through 4095, Fastlock is active and will time-out after the specified number of phase detector events.