# Precision Monolithics Inc.

### **FEATURES**

- . Compatible with Standards for Noise and Crosstalk in **Telephony Systems**

- Pin Compatible with DG508, HI-508A, LF11508

- **JFET Switches Rather Than CMOS**

- Low "ON" Resistance 220Ω Typical

- Low Output Leakage Current 100nA Max

- Digital Inputs Compatible with TTL and CMOS

- Input Overvoltage and Supply Loss Protected

### ORDERING INFORMATION†

CerDIP, plastic DIP, and TO-can package For rdering information 1990/91 Data Book, Section 2.

### **GENERAL DESCRIPTION**

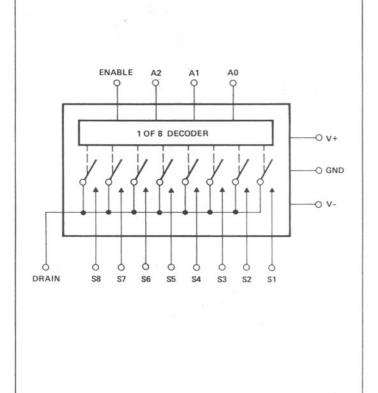

The MUX-88 is a monolithic eight-channel analog multiplexer ideally suited to shared-channel PCM CODEC systems. One-of-eight channels is selected upon the decoding of a 3 bit binary address. An enable input  $(\mathsf{E}_\mathsf{n})$  disables all switches when logic low providing package select. All logic control inputs have true TTL input compatibility eliminating the need for pull-up resistors necessary for some CMOS equivalent products.

Fabricated with Precision Monolithics' high performance Bipolar-JFET technology, this device offers low "ON" resistance, low leakage, fast settling time and excellent crosstalk isolation (98dB @ 20kHz). These characteristics make this device suitable for meeting system level communication requirements in shared-channel PCM CODECs.

Additional ruggedization results from built-in overvoltage, supply loss, and latch-up free circuit characteristics.

# **FUNCTIONAL DIAGRAM**

### **TRUTH TABLE**

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | EN | "ON"<br>CHANNEL |  |  |

|----------------|----------------|----------------|----|-----------------|--|--|

| Χ              | Х              | Х              | L  | NONE            |  |  |

| L              | L              | L              | Н  | 1               |  |  |

| L              | L              | Н              | Н  | 2               |  |  |

| L              | Н              | L              | Н  | 3               |  |  |

| L              | Н              | Н              | Н  | 4               |  |  |

| Н              | L              | L              | Н  | 5               |  |  |

| Н              | L              | Н              | Н  | 6               |  |  |

| Н              | Н              | L              | Н  | 7               |  |  |

| Н              | Н              | Н              | Н  | 8               |  |  |

# ABSOLUTE MAXIMUM RATINGS ( $T_A = +25$ °C, unless otherwise noted)

| Operating Temperature Range          |                     |

|--------------------------------------|---------------------|

| MUX-88EQ, FQ                         | 25°C to +85°C       |

| Storage Temperature Range            | 65°C to +150°C      |

| Lead Temperature (Soldering, 60 sec) | 300°C               |

| V+ Supply to V- Supply               | 36V                 |

| V+ Supply to Ground                  | 18V                 |

| Logic Input Voltage (Note 5)         | (V- or -4V) to V+   |

| Analog Input Voltage V- Supply -20   | V to V+ Supply +20V |

| ugh Any Pin              |                          | 25mA  |

|--------------------------|--------------------------|-------|

| ⊖ <sub>jA</sub> (Note 1) | θјс                      | UNITS |

| 100                      | 16                       | °C/W  |

|                          | ⊖ <sub>JA</sub> (Note 1) |       |

### NOTE:

# **ELECTRICAL CHARACTERISTICS** for V+=-15V and $-25^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ 85° C, unless otherwise noted.

|                                        |                       |                                            | M            | MUX-88E |     | MUX-88F   |          | 8F       |               |  |

|----------------------------------------|-----------------------|--------------------------------------------|--------------|---------|-----|-----------|----------|----------|---------------|--|

| PARAMETER                              | SYMBOL                | CONDITIONS                                 | MIN          | TYP     | MAX | MIN       | TYP      | MAX      | UNI           |  |

| "ON" Resistance                        | R <sub>ON</sub>       | $V_{S} = 0V, I_{S} = 200 \mu A$            | _            | _       | 400 |           |          | 520      |               |  |

| ARON With Applied Voltage              | $\Delta R_{ON}$       | $-10V \le V_S \le 10V$ , $I_S = 200 \mu A$ | _            | 1.5     | _   | _         | 4.5      | _        |               |  |

| B <sub>ON</sub> Match Between Switches | R <sub>ON Match</sub> | $V_S = 0V$ , $I_S = 200 \mu A$             | _            | 25      | _   | _         | 30       | _        |               |  |

| Source Current (Switch "OFF")          | I <sub>S(OFF)</sub>   | $V_S = 10V, V_D = -10V, (Note 1)$          | _            | _       | 10  | _         | _        | 10       | n             |  |

| Drain Current (Switch "OFF")           | I <sub>D(ØFF)</sub>   | $V_S = 10V, V_D = -10V, (Note 1)$          | _            | _       | 100 | _         | _        | 100      | n             |  |

| Leakage Curren (Switch "ON"            | ID(DN)+ IS(O          | N) V <sub>D</sub> = 10V, (Note 1)          | _            | _       | 100 | _         | _        | 100      | n             |  |

| Digital "1" Input Voltage              | VINH                  | (Note 5)                                   | 2            | _       | _   | 2         | _        | _        |               |  |

| Digital "0" Input Voltage              | V <sub>INL</sub>      | (Note 5)                                   |              | _       | 0.8 | _         | _        | 0.8      |               |  |

| Digital Input Current                  |                       | $y_{IN} = 0.7 \text{ to } +5 \text{ V}$    | _            | 1-1     | 20  | 7/-       | _        | 20       | ,             |  |

| Digital "0" Enable Current             | I <sub>INL(EN)</sub>  | V <sub>EN</sub> = 0.7V                     | _            | 11      | 20  |           | _        | 7 20     |               |  |

| Positive Supply Current                | 1+                    | All Digital Inputs Logic "0"               | _            | F       | 15  |           | <u> </u> | 15       |               |  |

| Negative Supply Current                | 1-                    | All Digital Inputs Logic "0"               | $\supset$ -/ | L       | 5   | 1-1       | _        | 5        |               |  |

| Switching Time (t <sub>TRAN</sub> )    | t <sub>PHL</sub>      | Figure 1, (Note 2)                         |              | 1.3     | 2.1 | 11        | 2.2      | 2.5      |               |  |

|                                        |                       | 10V Step 0.10%                             | _            | 1.3     | _   | $\sqrt{}$ | 1.7      | <u> </u> |               |  |

| Output Settling Time                   | ts                    | 10V Step 0.05%                             | _            | 1.5     | _   | _         | 1.9      |          | $\overline{}$ |  |

|                                        |                       | 10V Step 0.02%                             |              | 2.3     |     |           | 2.5      |          |               |  |

| Break-Before-Make Delay                | tOPEN                 |                                            |              | 0.8     | _   | _         | 1.0      | _        |               |  |

| Enable Delay "ON"                      | ton(EN)               |                                            | _            | 1.0     | _   | _         | 1.2      | _        |               |  |

| Enable Delay "OFF"                     | t <sub>OFF(EN)</sub>  |                                            | _            | 0.2     | _   | _         | 0.2      | _        |               |  |

| "OFF" Isolation                        | ISO <sub>OFF</sub>    | (Note 4)                                   | _            | 88      | _   | _         | 88       | _        | (             |  |

| Crosstalk                              | СТ                    | (Note 3)                                   | _            | 98      | _   | _         | 98       | _        | (             |  |

| Source Capacitance                     | C <sub>S(OFF)</sub>   | Switch "OFF", $V_S = 0V$ , $V_D = 0V$      | -            | 2.5     | _   | _         | 2.5      | _        |               |  |

| Drain Capacitance                      | C <sub>D(OFF)</sub>   | Switch "OFF", $V_S = 0V$ , $V_D = 0V$      | _            | 7       | _   | _         | 7        | _        |               |  |

| Input to Output Capacitance            | C <sub>DS(OFF)</sub>  | (Note 4)                                   | _            | 0.3     | _   | _         | 0.3      | _        |               |  |

| NOTES:                                 |                       |                                            |              |         |     |           |          |          |               |  |

### NOTES:

- Conditions applied to leakage tests insure worst case leakages. Exceeding 11V on the analog input may cause an "OFF" channel to turn "ON".

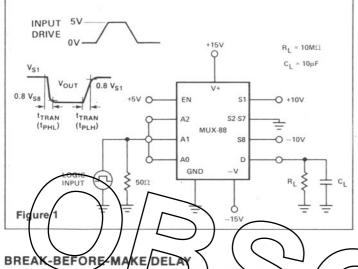

- Sample tested. The measurement conditions of Figure 1 insure worst case transition time.

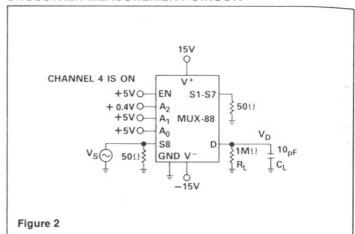

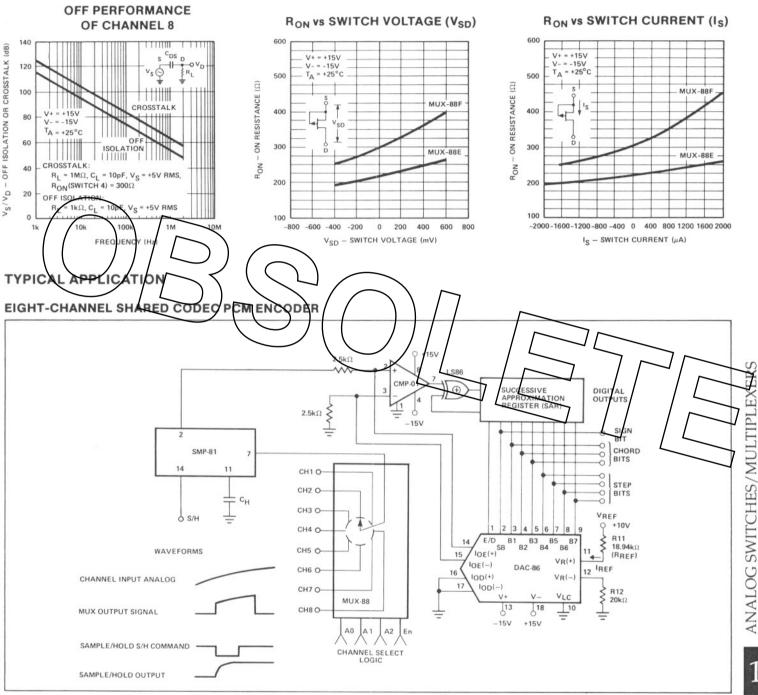

- 3. Crosstalk is measured by driving channel 8 with channel 4 ON.  $R_L = 1M\Omega$ ,  $C_L = 10pF$ ,  $V_S = 5V$  RMS, f = 20kHz. (See Figure 2)

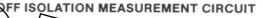

- 4. OFF isolation is measured by driving channel 8 with ALL channels OFF  $R_L = 1k\Omega$ ,  $C_L = 10pF$ ,  $V_S = 5V$  RMS, f = 20kHz.  $C_{DS}$  is computed from the OFF isolation measurement.

- Guaranteed by R<sub>ON</sub> and leakage current testing. For normal operation maximum analog signal voltages should be restricted to less than (V+)-4V.

## DICE

For applicable DICE information see MUX-08/MUX-24 data sheet.

Θ<sub>jA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>jA</sub> is specified for device in socket for CerDIP package.

# SWITCH LEAKAGE CURRENTS **vs ANALOG INPUT VOLTAGE**

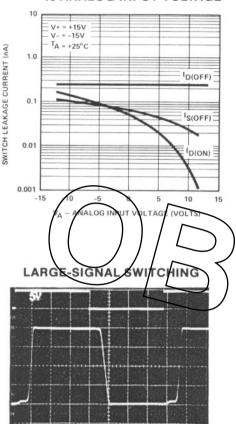

\*  $R_L = 10M\Omega$ ,  $C_L = 10pF$ ,  $V_1 = -10V$ ,  $V_8 = +10V$ Voltage = 5V/Div, Time =  $1\mu s/Div$ , See Transition Time Circuit of Figure 1.

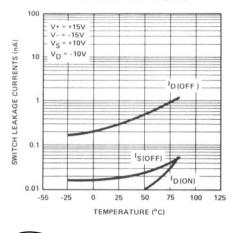

## **SWITCH LEAKAGE CURRENTS** vs TEMPERATURE

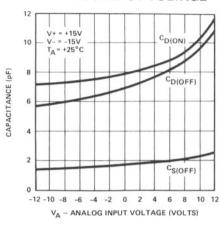

## SWITCH CAPACITANCE VS ANALOG INPUT VOLTAGE

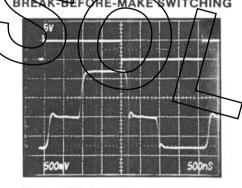

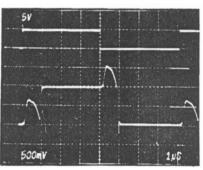

# EFORE-MAKE

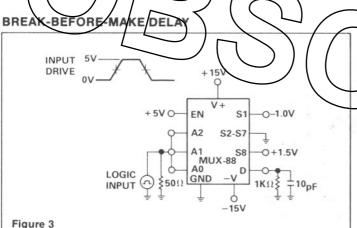

\*Voltage = 500mV/Div, Time = 500ns/Div, See Break-Before-Make Circuit of Figure 3.

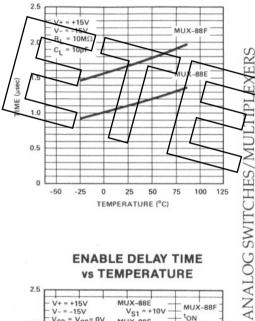

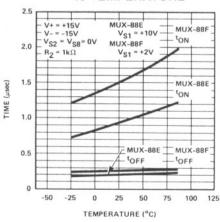

# TRANSITION TIMES **vs TEMPERATURE**

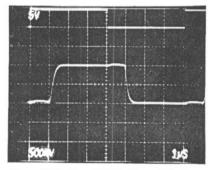

## **SMALL-SIGNAL SWITCHING**

${}^{\bullet}R_{L} = 1M\Omega, C_{L} = 10pF, V_{1} = -500mV,$ V<sub>S8</sub> = +500mV Voltage = 500mV/Div, Time =  $1\mu$ s/Div, See Transition Circuit of Figure 1.

# **SMALL-SIGNAL SWITCHING** WITH FILTERING

${}^{*}R_{L} = 1M\Omega$ ,  $C_{L} = 500pF$ ,  $V_{1} = -500mV$ ,  $V_{S8} = 500 \text{mV} \text{ Voltage} = 500 \text{mV/Div},$ Time =  $1\mu$ s/Div, See Transition Time Circuit of Figure 1.

# **ENABLE DELAY TIME** vs TEMPERATURE

### NOTE:

\*Top Waveforms: Digital Input 5V/Div Bottom Waveforms: Multiplex Output

### A.C. TEST CIRCUITS

### TRANSITION TIME

### CROSSTALK MEASUREMENT CIRCUIT

## APPLICATIONS INFORMATION

These analog multiplexers employ ion-implanted JFETs in a switch configuration designed to assure break-before-make action. The turn-off time is much faster than the turn-on time to guarantee this feature over the full operating temperature and input voltage range. Because the digital inputs only require a 2V logic "1" input level, power-consuming pull-up resistors are not required for TTL compatibility to insure break-before-make switching as is most often the case with CMOS multiplexers. The digital inputs utilize PNP input transistors where input current is maximum at the logic "0" level and drops to that of a reverse-biased diode (about 10nA) as the input voltage is raised above  $\approx$  1.4V.

The "ON" resistance,  $R_{ON}$ , of the analog switches is constant over the wide input voltage range of -15V to +11V with  $V_{SUPPLY} = \pm 15V$ . Higher input voltage is tolerable provided that some form of current limiting is employed (such as that of an op-amp output stage) to avoid exceeding junction temperature and power dissipation requirements. For normal

operation, however, positive input voltages should be restricted to 11V (or 4V less than the positive supply). This assures that the  $V_{GS}$  of an OFF switch remains greater than its  $V_P$ , and prevents that channel from being falsely turned ON.

When operating with negative input voltages, the gate-to-channel diode will be turned on if the voltage drop across an ON switch exceeds –0.6V. While this condition will cause an error in the output, it will not damage the switch. In lab tests, the multiplexer output load capacitor has increased to  $0.01\mu F$  in the Transition Time circuit, Figure 1. With  $V_{S1}=-10V$  and  $V_{S8}=+10V$ , the logic input was driven at a 1kHz rate. The positive-going slew rate was  $0.3V/\mu sec$  which is equivalent to a normal  $I_{DSS}$  of 3mA. The negative-going slew rate was  $0.7V/\mu sec$  which is equivalent to a "reverse"  $I_{DSS}$  of 7mA. Note that when switch 1 is first turned ON it has a drop of –20V across its terminals. In spite of that fact, the current is limited to approximately twice its normal  $I_{DSS}$ .

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

### **CROSSTALK IN PCM SYSTEMS**

In PAM or PCM systems crosstalk specifications for components, such as multiplexers, are related to overall system crosstalk specifications in a complex manner. Component specification must, of necessity, refer to the operation of the multiplexer in a non-sampling mode of operation. When rapid sequential sampling takes place, such as would be the case with a typical shared-channel CODEC, crosstalk will be caused by the off isolation properties of the multiplexer as well as by storage elements on chip and PC card stray capacitance. For example, the capacitance has the effect of conferencing the channels and increasing crosstalk. Thus, system crosstalk in a shared-channel PCM CODEC is influenced by multiplexed characteristics as well as PC card layout and the timing relationship between the multiplexer and the sample-hold circuit.