# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# **DS92LV1260**

# Six Channel 10 Bit BLVDS Deserializer

### **General Description**

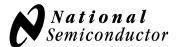

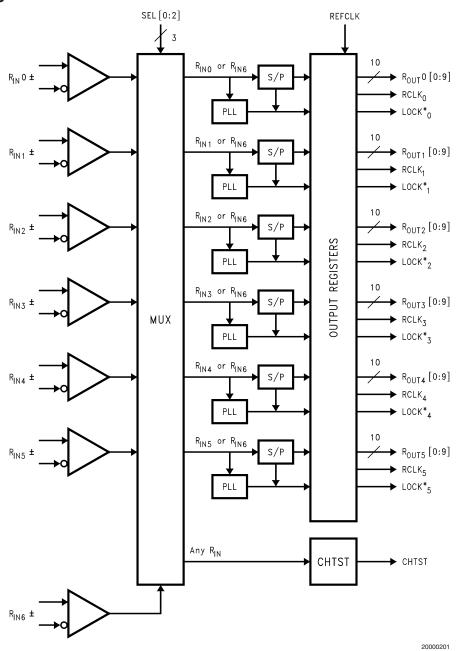

The DS92LV1260 integrates six deserializer devices into a single chip. The chip uses a 0.25u CMOS process technology. The DS92LV1260 can simultaneously deserialize up to six data streams that have been serialized by the National Semiconductor DS92LV1021 or DS92LV1023 Bus LVDS serializers. The device also includes a seventh serial input channel that serves as a redundant input.

Each deserializer block in the DS92LV1260 operates independently with its own clock recovery circuitry and lock-detect signaling.

The DS92LV1260 uses a single +3.3V power supply with a typical power dissipation of 1.2W at 3.3V with a PRBS-15 pattern. Refer to the Connection Diagrams for packaging information.

#### **Features**

- Deserializes one to six BusLVDS input serial data streams with embedded clocks

- Seven selectable serial inputs to support n+1 redundancy of deserialized streams

- Seventh channel has single pin monitor output that reflects input from seventh channel input

- Parallel clock rate up to 40MHz

- On chip filtering for PLL

- Absolute maximum worst case power dissipation = 1.9W at 3.6V

- High impedance inputs upon power off  $(V_{cc} = 0V)$

- Single power supply at +3.3V

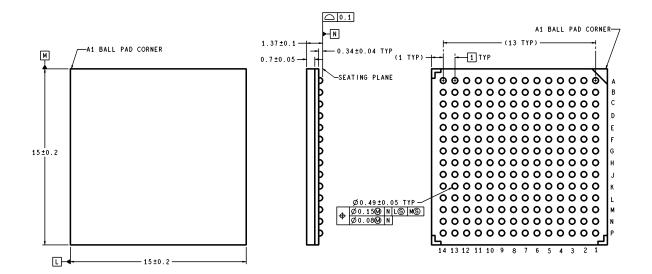

- 196-pin LBGA package (Low-profile Ball Grid Array) package

- Industrial temperature range operation: -40°C to +85°C

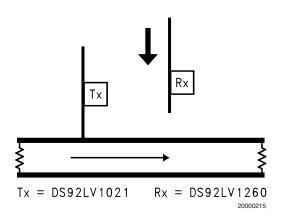

### **Block Diagram**

### Application

20000202

**Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{cc}$ ) -0.3 to 4V

Bus LVDS Input Voltage -0.3V to 3.9V

(Rin +/-)

Maximum Package 3.7W

Power Dissipation

@25°C

Package Thermal Resistance

$\theta_{JA}$  196 LBGA: 34°C/W  $\theta_{JC}$  196 LBGA: 8°C/W

Storage Temp. Range  $-65\,^{\circ}\text{C}$  to  $+150\,^{\circ}\text{C}$

Junction Termperature +150°C

Lead Temperature +225°C

(Soldering 10 Sec)

ESD Rating:

Human Body Model >3KV

Machine Model >750V

Reliability Information

Transistor Count 35,682

# Recommended Operating Conditions

Supply Voltage ( $V_{CC}$ ) 3.0V to 3.6V Operating Free Air -40°C to +85°C

Temperature (T<sub>A</sub>)

Operating Frequency 16-40 MHz

### **Electrical Characteristics**

Basic functionality and specifications per deserializer channel will be similar to National Semiconductor's DS92LV1212A.

| Symbol             | Parameter                              | Conditions                                                                                | Pin/Freq.          | Min  | Тур    | Max             | Units |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------------------|--------------------|------|--------|-----------------|-------|

| LVCMOS/            | LVTTL DC Specifications:               |                                                                                           |                    |      |        |                 |       |

| V <sub>IH</sub>    | High Level Input Voltage               |                                                                                           | REN,               | 2.0  |        | V <sub>CC</sub> | V     |

| V <sub>IL</sub>    | Low Level Input Voltage                |                                                                                           | REFCLK,            | GND  |        | 0.8             | V     |

| V <sub>CL</sub>    | Input Clamp Voltage                    |                                                                                           | PWRDWN, SEL (0:2), |      | -0.87  | -1.5            | V     |

| I <sub>IN</sub>    | Input Current                          | V <sub>in</sub> = 0 or 3.6V                                                               | R <sub>OUT</sub>   | -10  |        | +10             | uA    |

| V <sub>OH</sub>    | High Level Output Voltage              | I <sub>OH</sub> = -6mA                                                                    |                    | 2    | 3      | V <sub>CC</sub> | V     |

| V <sub>OL</sub>    | Low Level Output Voltage               | $I_{OL} = 6mA$                                                                            |                    | GND  | 0.18   | 0.4             | V     |

| l <sub>os</sub>    | Output short Circuit Current           | V <sub>out</sub> = 0V,(Note<br>4)                                                         | R <sub>out</sub> , | -15  | -46    | -85             | mA    |

| l <sub>oz</sub>    | TRI-STATE Output Current               | $\overline{\text{PWRDWN}}$ or REN = 0.8V, $V_{\text{out}} = \text{0V or}$ $V_{\text{CC}}$ | LOCK               | -10  | +/-0.2 | +10             | uA    |

| Bus LVDS           | DC specifications                      |                                                                                           | •                  |      |        |                 | •     |

| $V_{TH}$           | Differential Threshold High<br>Voltage | $VCM = 1.1V$ $(V_{RI+}-V_{RI-})$                                                          |                    |      | +3     | +50             | mV    |

| V <sub>TL</sub>    | Differential Threshold Low<br>Voltage  |                                                                                           | RI+, RI-           | -50  | -2     |                 | mV    |

| I <sub>IN</sub>    | Input Current                          | $V_{in} = +2.4V,$<br>$V_{cc} = 3.6 \text{ or } 0V$                                        |                    | -10  | +/- 1  | +10             | uA    |

|                    |                                        | $V_{in} = 0V,$<br>$V_{cc} = 3.6 \text{ or } 0V$                                           |                    | -10  | +/- 1  | +10             | uA    |

| Supply Co          | urrent                                 |                                                                                           |                    |      |        |                 |       |

| I <sub>CCR</sub>   | Worst Case Supply Current              | 3.6V, 40 MHz,<br>Checker Board<br>Pattern,<br>CL=15pF                                     |                    |      | 460    | 530             | mA    |

| I <sub>CCXR</sub>  | Supply Current when Powered Down       | PWRDN= 0.8V<br>REN = 0.8V                                                                 |                    |      | 0.36   | 1               | mA    |

| Timing Re          | equirements for REFCLK                 |                                                                                           |                    | ·    |        | ·               |       |

| t <sub>RFCP</sub>  | REFCLK Period                          |                                                                                           |                    | 25   |        | 62.5            | ns    |

| t <sub>RFDC</sub>  | REFCLK Duty Cycle                      |                                                                                           |                    | 40   | 50     | 60              | %     |

| $t_{RFCP}/t_{TCP}$ | Ratio of REFCLK to TCLK                |                                                                                           |                    | 0.95 |        | 1.05            |       |

#### **Electrical Characteristics** (Continued)

Basic functionality and specifications per deserializer channel will be similar to National Semiconductor's DS92LV1212A.

| I | Over recommended of | operating supply | and termperature | ranges unless | otherwise si | pecified.(Note 2) |  |

|---|---------------------|------------------|------------------|---------------|--------------|-------------------|--|

|   |                     |                  |                  |               |              |                   |  |

| Symbol             | Parameter                                   | Conditions                 | Pin/Freq.              | Min                      | Тур                      | Max                       | Units |

|--------------------|---------------------------------------------|----------------------------|------------------------|--------------------------|--------------------------|---------------------------|-------|

| t <sub>RFTT</sub>  | REFCLK Transition Time                      |                            |                        |                          |                          | 8                         | ns    |

| Deserialize        | er Switching Characteristics                |                            |                        |                          |                          |                           |       |

| t <sub>RCP</sub>   | RCLK Period                                 |                            | DOLK                   | 25                       |                          | 62.5                      | ns    |

| t <sub>RDC</sub>   | RCLK Duty Cycle                             |                            | RCLK                   | 43                       | 50                       | 55                        | %     |

|                    | Period of Bus LVDS signal                   | (Nicto 7)                  | CLITCT                 | 0.5                      |                          |                           |       |

| t <sub>CHTST</sub> | when CHTST is selected by MUX               | (Note 7)                   | CHTST                  | 25                       |                          |                           | ns    |

| t <sub>CLH</sub>   | CMOS/TTL Low-to-High<br>Transition Time     |                            |                        |                          | 1.7                      | 6                         | ns    |

| t <sub>CHL</sub>   | CMOS/TTL High-to-Low<br>Transition Time     |                            |                        |                          | 1.6                      | 6                         | ns    |

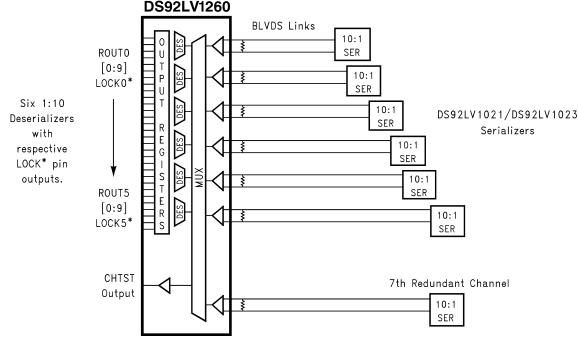

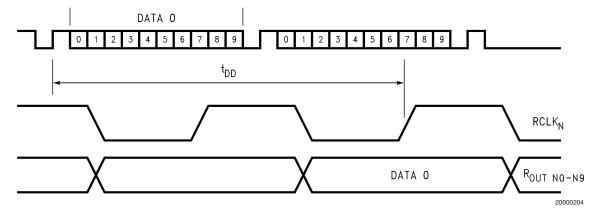

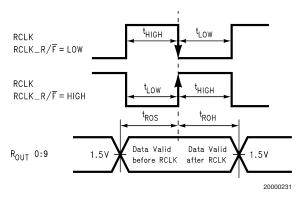

| t <sub>ROS</sub>   | Rout Data Valid before RCLK                 | Figure 2                   |                        | 0.4*t <sub>RCP</sub>     |                          |                           | ns    |

| t <sub>ROH</sub>   | Rout Data Valid after RCLK                  | Figure 2                   | Rout,<br>LOCK,<br>RCLK | -0.4*t <sub>RCP</sub>    |                          |                           | ns    |

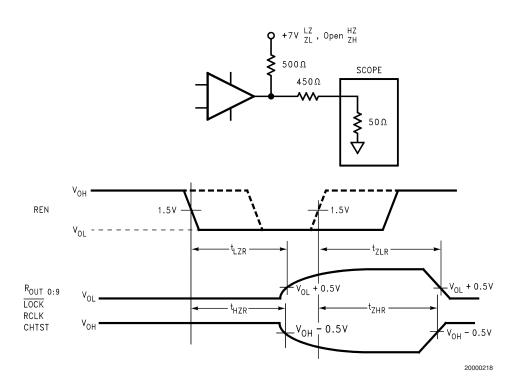

| t <sub>HZR</sub>   | High to TRI-STATE Delay                     |                            |                        |                          |                          | 10                        | ns    |

| t <sub>LZR</sub>   | Low to TRI-STATE Delay                      |                            |                        |                          |                          | 10                        | ns    |

| t <sub>ZHR</sub>   | TRI-STATE to High Delay                     |                            |                        |                          |                          | 12                        | ns    |

| t <sub>ZLR</sub>   | TRI-STATE to Low Delay                      |                            |                        |                          |                          | 12                        | ns    |

|                    |                                             | Figure 1                   | RCLK                   | 1.75*t <sub>RCP</sub> +5 | 1.75*t <sub>RCP</sub> +7 | 1.75*t <sub>RCP</sub> +10 | ns    |

| t <sub>DD</sub>    | Deserializer Delay                          | Room Temp<br>3.3V<br>40MHz |                        | 1.75*t <sub>RCP</sub> +6 | 1.75*t <sub>RCP</sub> +7 | 1.75*t <sub>RCP</sub> +9  | ns    |

| +                  | Deserializer PLL LOCK Time from PWRDN (with | Figure 3                   | 40MHz                  |                          |                          | 3                         | us    |

| t <sub>DSR1</sub>  | SYNCPAT)                                    | (Note 5)                   | 20MHz                  |                          |                          | 10                        | us    |

| +                  | Deserializer PLL Lock Time                  | Figure 4                   | 40MHz                  |                          |                          | 2                         | us    |

| t <sub>DSR2</sub>  | from SYNCPAT                                | (Note 5)                   | 20MHz                  |                          |                          | 5                         | us    |

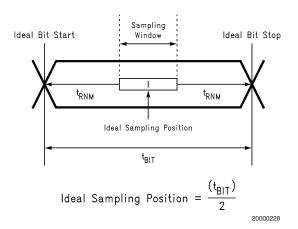

| t                  | Deserializer Noise Margin                   | (Note 6)                   | 40MHz                  | 450                      | 920                      |                           | ps    |

| t <sub>RNM</sub>   | Descrializer Noise Margin                   | (NOTE O)                   | 20MHz                  | 1200                     | 1960                     |                           | ps    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: Typical values are given for Vcc = 3.3V and TA =25°C

Note 3: Current into the device pins is defined as positive. Current out of device pins is defined as negative. Voltage are referenced to ground except VTH and VTL which are differential voltages.

Note 4: Only one output should be shorted at a time. Do not exceed maximum package power dissipation capacity.

Note 5: For the purpose of specifying deserializer PLL performance  $t_{DSR1}$  and  $t_{DSR2}$  are specified with the REFCLK running and stable, and specific conditions of the incoming data stream (SYNCPATs).  $t_{DSR1}$  is the time required for the deserializer to indicate lock upon power-up or when leaving the power-down mode.  $t_{DSR2}$  is the time required to indicate lock for the powered-up and enabled deserializer when the input (RI+ and RI-) conditions change from not receiving data to receiving synchronization patterns (SYNCPATs). The time to lock to random data is dependent upon the incoming data.

Note 6: t<sub>RNM</sub> is a measure of how much phase noise (jitter)the deserializer can tolerate in the incoming data stream before bit errors occur. The Deserializer Noise Margin is Guaranteed By Design (GBD) using statistical analysis.

Note 7: Because the Bus LVDS serial data stream is not decoded, the maximum frequency of the CHTST output driver could be exceeded if the data stream were switched to CHTST. The maximum frequency of the BUS LVDS input should not exceed the parallel clock rate.

# **AC Timing Diagrams and Test Circuits**

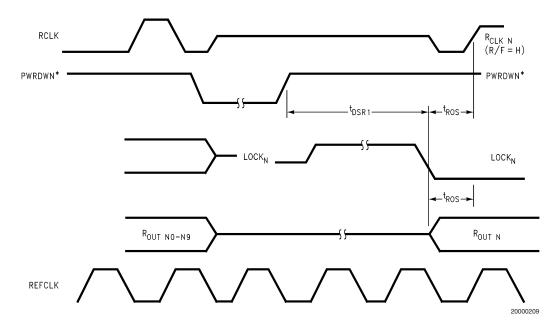

FIGURE 1. Deserializer Delay  $t_{\rm DD}$

FIGURE 2. Output Timing  $\rm t_{ROS}$  and  $\rm t_{ROH}$

FIGURE 3. Locktime from PWRDN\*  $t_{\rm DSR1}$

# AC Timing Diagrams and Test Circuits (Continued)

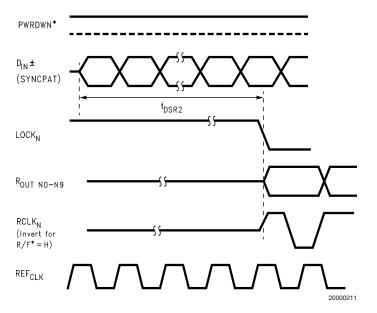

FIGURE 4. Locktime to SYNCPAT  $t_{\mbox{\scriptsize DSR2}}$

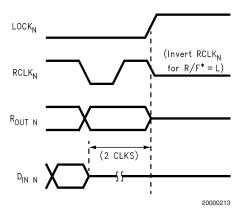

FIGURE 5. Unlock

FIGURE 6. Deserializer Data Valid Out Times

# AC Timing Diagrams and Test Circuits (Continued)

FIGURE 7. Deserializer TRI-STATE Test Circuit and Timing

# **Block Diagram**

## **Control Pins Truth Table**

| PWRDN | REN | SEL2 | SEL1 | SEL0 | Rout              | CHTST     | LOCK[0:5]      | RCLK[0:5]        |

|-------|-----|------|------|------|-------------------|-----------|----------------|------------------|

| Н     | Н   | L    | L    | L    | Din6 Decoded to   | Din0 (not | Active(Note 9) | Active(Notes 10, |

|       |     |      |      |      | Rout 0 (0:9)(Note | decoded)  |                | 11)              |

|       |     |      |      |      | 11)               |           |                |                  |

| Н     | Н   | L    | L    | Н    | Din6 Decoded to   | Din1 (not | Active(Note 9) | Active(Notes 10, |

|       |     |      |      |      | Rout 1 (0:9)(Note | decoded)  |                | 11)              |

|       |     |      |      |      | 11)               |           |                |                  |

| Н     | Н   | L    | Н    | L    | Din6 Decoded to   | Din2 (not | Active(Note 9) | Active(Notes 10, |

|       |     |      |      |      | Rout 2 (0:9)(Note | decoded)  |                | 11)              |

|       |     |      |      |      | 11)               |           |                |                  |

7

### **Control Pins Truth Table** (Continued)

| Н | Н | L | Н | Н | Din6 Decoded to   | Din3 (not | Active(Note 9) | Active(Notes 10, |

|---|---|---|---|---|-------------------|-----------|----------------|------------------|

|   |   |   |   |   | Rout 3 (0:9)(Note | decoded)  |                | 11)              |

|   |   |   |   |   | 11)               |           |                |                  |

| Н | Н | Н | L | L | Din6 Decoded to   | Din4 (not | Active(Note 9) | Active(Notes 10, |

|   |   |   |   |   | Rout 4 (0:9)(Note | decoded)  |                | 11)              |

|   |   |   |   |   | 11)               |           |                |                  |

| Н | Н | Н | L | Н | Din6 Decoded to   | Din5 (not | Active(Note 9) | Active(Notes 10, |

|   |   |   |   |   | Rout 5 (0:9)(Note | decoded)  |                | 11)              |

|   |   |   |   |   | 11)               |           |                |                  |

| Н | Н | Н | Н | L | Din6 is not       | Z         | Active(Note 9) | Active(Notes 10, |

|   |   |   |   |   | Decoded           |           |                | 11)              |

| Н | Н | Н | Н | Н | Din6 is not       | Din6 (not | Active(Note 9) | Active(Notes 10, |

|   |   |   |   |   | Decoded           | decoded)  |                | 11)              |

| L | Х | Х | Х | Х | Z                 | Z         | Z              | Z                |

| Н | L | Х | Х | Х | Z                 | Z         | Active(Note 9) | Z                |

Note 8: The routing of the Din inputs to the Deserializers and to the CHTST outputs are dependent on the states of SEL [0:2].

Note 9: LOCK Active indicates that the LOCK output will reflect the state of it's respective Deserializer with regard to the selected data stream.

Note 10: RCLK Active indicates that the RCLK will be running if the Deserializer is locked. The timing of RCLK [0:5] with respect to Rout [0:5][0:9] is determined by RCLK\_R/FFigure 5

Note 11: Rout n[0:9] and RCLK [0:5] are Tri-Stated when LOCKn[0:5] is High.

### **Functional Description**

The DS92LV1260 combines six 1:10 deserializers into a single chip. Each of the six deserializers accepts a BusLVDS data stream from National Semiconductor's DS92LV1021 or DS92LV1023 Serializer. The deserializers then recover the clock and data to deliver the resulting 10-bit wide words to the outputs. A seventh serial data input provides n+1 redundancy capability. The user can program the seventh input to be an alternative input to any of the six deserializers. Whichever input is replaced by the seventh input is then routed to the CHANNEL TEST (CHTST) pin on receiver output port.

Each of the 6 channels acts completely independent of each other. Each independent channel has outputs for a 10-bit wide data word, the recovered clock out, and the lock-detect output

The DS92LV1260 has three operating states: Initialization, Data Transfer, and Resynchronization. In addition, there are two passive states: Powerdown and TRI-STATE.

The following sections describe each operating mode and passive state.

#### Initialization

Before the DS92LV1260 receives and deserializes data, it and the transmitting serializer devices must initialize the link. Initialization refers to synchronizing the Serializer's and the Deserializer's PLL's to local clocks. The local clocks must be the same frequency or within a specified range if from different sources. After all devices synchronize to local clocks, the Deserializers synchronize to the Serializers as the second and final initialization step.

Step 1: After applying power to the Deserializer, the outputs are held in TRI-STATE and the on-chip power-sequencing circuitry disables the internal circuits. When  $V_{\rm cc}$  reaches  $V_{\rm cc} {\sf OK}$  (2.1V), the PLL in each deserializer begins locking to the local clock (REFCLK). A local on-board oscillator or other source provides the specified clock input to the REFCLK pin.

Step 2: The Deserializer PLL must synchronize to the Serializer to complete the initialization. Refer to the Serializer

data sheet for the proper operation during this step of the Initialization State. The Deserializer identifies the rising clock edge in a synchronization pattern or random data and after 80 clock cycles will synchronize to the data stream from the serializer. At the point where the Deserializer's PLL locks to the embedded clock, the LOCKn pin goes low and valid data appears on the output. Note that this differs from pervious deserializers where the LOCKn signal was not synchronous to valid data appearing on the outputs.

#### **Data Transfer**

After initialization, the serializer transfers data to the deserializers. The serial data stream includes a start and stop bit appended by the serializer, which frame the ten data bits. The start bit is always high and the stop bit is always low. The start and stop bits also function as clock bits embedded in the serial stream.

The Serializer transmits the data and clock bits (10+2 bits) at 12 times the TCLK frequency. For example, if TCLK is 40 MHz, the serial rate is 40 X 12 = 480 Mbps. Since only 10 bits are from input data, the serial 'payload' rate is 10 times the TCLK frequency. For instance, if TCLK = 40 MHz, the payload data is 40 X 10 = 400 Mbps. TCLK is provided by the data source and must be in the range 20 MHz to 40 MHz nominal.

When one of six Deserializer channels synchronizes to the input from a Serializer, it drives its LOCKn pin low and synchronously delivers valid data on the output. The Deserializer locks to the embedded clock, uses it to generate multiple internal data strobes, and drives the embedded clock to the RCLKn pin. The RCLKn is synchronous to the data on the ROUT[n0:n9] pins. While LOCKn is low, data on ROUT [n0:n9] is valid. Otherwise, ROUT[n0:n9] is invalid.

All ROUT,  $\overline{\mathsf{LOCK}}$ , and RCLK signals will drive a minimum of three CMOS input gates (15pF load) with a 40 MHz clock. This amount of drive allows bussing outputs of two Deserializers and a destination ASIC. REN controls TRI-STATE™ of all the outputs.

#### Data Transfer (Continued)

The Deserializer input pins are high impedance during Powerdown ( $\overline{PWRDN}$  low) and power-off ( $V_{CC}=0V$ ).

### Resynchronization

Whenever one of the six Deserializers loses lock, it will automatically try to resynchronize. For example, if the embedded clock edge is not detected two times in succession, the PLL loses lock and the  $\overline{\text{LOCKn}}$  pin is driven high. The system must monitor the  $\overline{\text{LOCKn}}$  pin to determine when data is valid.

The user has the choice of allowing the deserializer to resynch to the data stream or to force synchronization by pulsing the Serializer SYNC1 or SYNC2 pin. This scheme is left up to the user discretion. One recommendation is to provide a feedback loop using the  $\overline{\text{LOCKn}}$  pin itself to control the sync request of the Serializer (SYNC1 or SYNC2). Dual SYNC pins are given for multiple control in a multi-drop application.

#### **Powerdown**

The Powerdown state is a low power sleep mode that the Serializer and Deserializer typically occupy while waiting for initialization, or to reduce power consumption when no data is transfers. The Deserializer enters Powerdown when PWRDN is driven low. In Powerdown, the PLL stops and the outputs go into TRI-STATE, which reduces supply current to the microamp range. To exit Powerdown, the system drives PWRDN high.

Upon exiting Powerdown, the Deserializer enters the Initialization state. The system must then allow time to Initialize before data transfer can begin.

#### TRI-STATE

When the system drives REN pin low, the Deserializer enters TRI-STATE. This will TRI-STATE the receiver output pins (ROUT[00:59]) and RCLK[0:5]. When the system drives REN high, the Deserializer will return to the previous state as long as all other control pins remain static ( $\overline{\text{PWRDN}}$ , RCLK\_R/ $\overline{\text{F}}$ ).

## **Application Information**

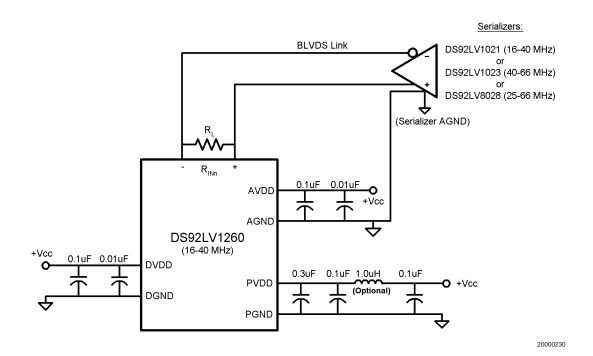

#### USING THE DS92LV1021 AND DS92LV1260

The DS92LV1260 combines six 1:10 deserializers into a single chip. Each of the six deserializers accepts a BusLVDS data stream up to 480 Mbps from National Semiconductor's DS92LV1021 or DS92LV1023 Serializer. The deserializers then recover the embedded two clock bits and data to deliver the resulting 10-bit wide words to the output. A seventh serial data input provides n+1 redundancy capability. The user can program the seventh input to be an alternative input to any of the six deserializers. Whichever input is replaced by the seventh input is then routed to the CHANNEL TEST (CHTST) pin on receiver output port. The Deserializer uses a separate reference clock (REFCLK) and an onboard PLL to extract the clock information from the incoming data stream and then deserialize the data. The Deserializer monitors the incoming clock information, determines lock status, and asserts the LOCKn output high when loss of lock occurs.

#### **POWER CONSIDERATIONS**

An all CMOS design of the Deserializer makes it an inherently low power device.

#### **POWERING UP THE DESERIALIZER**

The DS92LV1260 can be powered up at any time by following the proper sequence. The REFCLK input can be running before the Deserializer powers up, and it must be running in order for the Deserializer to lock to incoming data. The Deserializer outputs will remain in TRI-STATE until the Deserializer detects data transmission at its inputs and locks to the incoming data stream.

#### TRANSMITTING DATA

Once you power up the Deserializer, it must be phase locked to the transmitter to transmit data. Phase locking occurs when the Deserializer locks to incoming data or when the Serializer sends sync patterns. The Serializer sends SYNC patterns whenever the SYNC1 or SYNC2 inputs are high. The LOCKn output of the Deserializer remains high until it has locked to the incoming data stream. Connecting the LOCKn output of the Deserializer to one of the SYNC inputs of the Serializer will guarantee that enough SYNC patterns are sent to achieve Deserializer lock.

The Deserializer can also lock to incoming data by simply powering up the device and allowing the "random lock" circuitry to find and lock to the data stream.

### NOISE MARGIN

While the Deserializer LOCKn output is low, data at the Deserializer outputs (ROUT0-9) are valid, except for the specific case of loss of lock during transmission which is further discussed in the "Recovering from LOCK Loss" section below.

The Deserializer noise margin is the amount of input jitter (phase noise) that the Deserializer can tolerate and still reliably receive data. Various environmental and systematic factors include:

Serializer: TCLK jitter,  $V_{\text{CC}}$  noise (noise bandwidth and out-of-band noise)

Media: ISI, Large  $V_{CM}$  shifts Deserializer:  $V_{CC}$  noise

#### RECOVERING FROM LOCK LOSS

In the case where the Deserializer loses lock during data transmission, up to 1 cycle of data that was previously received can be invalid. This is due to the delay in the lock detection circuit. The lock detect circuit requires that invalid clock information be received 2 times in a row to indicate loss of lock. Since clock information has been lost, it is possible that data was also lost during these cycles. Therefore, after the Deserializer relocks to the incoming data stream and the Deserializer LOCKn pin goes low, at least one previous data cycle should be suspect for bit errors.

The Deserializer can relock to the incoming data stream by making the Serializer resend SYNC patterns, as described above, or by random locking, which can take more time, depending on the data patterns being received.

#### **HOT INSERTION**

All the BusLVDS devices are hot pluggable if you follow a few rules. When inserting, ensure the Ground pin(s) makes contact first, then the VCC pin(s), and then the I/O pins. When removing, the I/O pins should be unplugged first, then the VCC, then the Ground. Random lock hot insertion is illustrated in *Figure 11*.

#### TRANSMISSION MEDIA

The Serializer and Deserializer can also be used in point-to-point configurations, through PCB trace, or through twisted pair cable. In point-to-point configurations, the transmission media need only be terminated at the receiver end. Please note that in point-to-point configurations, the potential of offsetting the ground levels of the Serializer vs. the Deserializer must be considered. Also, Bus LVDS provides a +/– 1V common mode range at the receiver inputs.

#### FAILSAFE BIASING FOR THE DS92LV1260

The DS92LV1260 has internal failsafe biasing and an improved input threshold sensitivity of +/- 50mV versus +/- 100mV for the DS92LV1210 or DS92LV1212. This allows for greater differential noise margin in the DS92LV1260. However, in cases where the receiver input is not being actively driven, the increased sensitivity of the DS92LV1260 can pickup noise as a signal and cause unintentional locking . For example, this can occur when the input cable is disconnected

External resistors can be added to the receiver circuit board to prevent noise pick-up. Typically, the non-inverting receiver input is pulled up and the inverting receiver input is pulled down by high value resistors. The pull-up and pull-down resistors (R<sub>1</sub> and R<sub>2</sub>) provide a current path through the termination resistor (R<sub>L</sub>) which biases the receiver inputs when they are not connected to an active driver. The value of the pull-up and pull-down resistors should be chosen so that enough current is drawn to provide a +15mV drop across the termination resistor. Please see Figure 9 for the Failsafe Biasing Setup.

# PCB LAYOUT AND POWER SYSTEM CONSIDERATIONS

Circuit board layout and stack-up for the DS92LV1260 should be designed to provide noise-free power to the device. Good layout practice will separate high frequency or high level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. There are a few common practices which should be followed when designing PCB's for Bus LVDS Signaling. Recommended layout practices are:

### Application Information (Continued)

- Use at least 4 PCB board layers (Bus LVDS signals, ground, power, and TTL signals).

- Power system performance may be greatly improved by using thin dielectrics (4 to 10 mils) for power/ground sandwiches. This increases the intrinsic capacitance of the PCB power system which improves power supply filtering, especially at high frequencies, and makes the value and placement of external bypass capacitors less critical.

- Keep Serializers and Deserializers as close to the (Bus LVDS port side) connector as possible.

- Longer stubs lower the impedance of the bus, increase the load on the Serializer, and lower the threshold margin at the Deserializers. Deserializer devices should be placed much less than one inch from slot connectors. Because transition times are very fast on the Serializer Bus LVDS outputs, reducing stub lengths as much as possible is the best method to ensure signal integrity.

- Bypass each Bus LVDS device and also use distributed bulk capacitance between power planes.

- Surface mount capacitors placed close to power and ground pins work best. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range 0.001  $\mu\text{F}$  to 0.1  $\mu\text{F}$ . Tantalum capacitors may be in the range 2.2  $\mu\text{F}$  to 10  $\mu\text{F}$ . Voltage rating for tantalum capacitors should be at least 5X the power supply voltage being used. Randomly distributed by-pass capacitors should also be used.

Package and pin layout permitting, it is also recommended to use two vias at each power pin as well as all RF bypass capacitor terminals. Dual vias reduce the interconnect inductance between layers by up to half, thereby reducing interconnect inductance and extending the effective frequency range of the bypass components.

The outer layers of the PCB may be flooded with additional ground planes. These planes will improve shielding and isolation as well as increase the intrinsic capacitance of the power supply plane system. Naturally, to be effective.

tive, these planes must be tied to the ground supply plane at frequent intervals with vias. Frequent via placement improves signal integrity on signal transmission lines by providing short paths for image currents, which reduces signal distortion. Depending on which is greater, the planes should be pulled back from all transmission lines and component mounting pads a distance equal to the width of the widest transmission line or the thickness of the dielectric separating the transmission line from the internal power or ground plane(s). Doing so minimizes effects on transmission line impedances and reduces unwanted parasitic capacitances at component mounting pads.

- Use a termination resistor which best matches the differential impedance of your transmission line.

- Leave unused Bus LVDS receiver inputs open (floating).

Limit traces on unused inputs to <0.5 inches.</li>

- · Isolate TTL signals from Bus LVDS signals.

- · Use controlled impedance media.

The backplane and connectors should have a matched differential impedance.

For a typical application circuit, please see Figure 8.

There are more common practices which should be followed when designing PCBs for LVDS signaling. General application guidelines and hints may be found in the following application notes: AN-808, AN-903, AN-971, AN-977, and AN-1108. For packaging information on BGA's, please see AN-1126.

# USING $T_{DJIT}$ AND $T_{RNM}$ TO VALIDATE SIGNAL QUALITY

The parameter  $t_{\text{RNM}}$  is calculated by first measuring how much of the ideal bit the receiver needs to ensure correct sampling. After determining this amount, what remains of the ideal bit that is available for external sources of noise is called  $t_{\text{RNM}}$ .

The vertical limits of the mask are determined by the DS92LV1260 receiver input threshold of +/- 50mV.

Please refer to the eye mask pattern of Figure 10 for a graphic representation of  $\rm t_{DJIT}$  and  $\rm t_{RNM}$

FIGURE 8. Typical Applications Circuit

FIGURE 9. Failsafe Biasing Setup

FIGURE 10. Using  $t_{\text{DJIT}}$  and  $t_{\text{RNM}}$  to Generate an Eye Pattern Mask and Validate Signal Quality

FIGURE 11. Random Lock Hot Insertion

# Pin Diagram

#### Top View of DS92LV1260 (196 pin LBGA)

|                     |                     |                           |                    | rop v                 | lew of                                                  | D592LV             | 1260 (1            | 96 pin L           | .BGA)                |                    |                     |                     |                    |

|---------------------|---------------------|---------------------------|--------------------|-----------------------|---------------------------------------------------------|--------------------|--------------------|--------------------|----------------------|--------------------|---------------------|---------------------|--------------------|

| (A1)                | (A2)                | (A3)                      | (A4)               | (A5)                  | (A6)                                                    | (A7)               | (A8)               | (A9)               | (A 1 0)              | (A 1 1)            | (A 1 2)             | (A 1 3)             | (A 1 4)            |

| DGND                | REN                 | R <sub>INO</sub> -        | R <sub>INO</sub> + | AGND                  | R <sub>IN2</sub> -                                      | R <sub>IN2</sub> + | AGND               | R <sub>IN4</sub> - | R <sub>IN4</sub> +   | $AV_{DD}$          | R <sub>IN6</sub> -  | R <sub>IN6</sub> +  | PGND               |

| (B1)                | (B2)                | (B3)                      | (B4)               | (B5)                  | (B6)                                                    | (B7)               | (B8)               | (B9)               | (B10)                | (B11)              | (B12)               | (B13)               | (B14)              |

| N/C                 | DGND                | $DV_DD$                   | REF <sub>CLK</sub> | PWRDN*                | $AV_{DD}$                                               | AGND               | AGND               | $AV_{DD}$          | N/C                  | AGND               | PGND                | SEL2                | DGND               |

| (c1)                | (c2)                | $\left( \text{C3}\right)$ | (C4)               | (c5)                  | $(c_6)$                                                 | (c7)               | (c8)               | (C9)               | (C10)                | (C11)              | (C12)               | (C13)               | (C14)              |

| JTL2                | JTL1                | CHTST                     | RCLK_R/F*          | ' R <sub>IN 1</sub> - | R <sub>IN 1</sub> +                                     | $AV_{DD}$          | R <sub>IN3</sub> - | R <sub>IN3</sub> + | R <sub>IN5</sub> -   | R <sub>IN5</sub> + | SEL0                | SEL1                | N/C                |

| $\bigcirc$ 1        | D2                  | D3                        | D4                 | (D5)                  | D6                                                      | (D7)               | D8                 | D9                 | (D10)                | (D11)              | (D12)               | D13                 | (D14)              |

| JTL3                | JTL4                | JTL5                      | N/C                | DGND                  | $DV_{DD}$                                               | DGND               | N/C                | N/C                | PGND                 | N/C                | PVDD                | LOCK <sub>5</sub> * | N/C                |

| (E1)                | (E2)                | E3                        | E4)                | E5)                   | (E6)                                                    | (E7)               | (E8)               | (E9)               | (E10)                | (E11)              | (E 1 2)             | (E13)               | (E14)              |

| $PV_{DD}$           | R <sub>OUTO9</sub>  | N/C                       | R <sub>OUTO8</sub> | DGND                  | $DV_{DD}$                                               | $DV_DD$            | DGND               | $DV_{DD}$          | $DV_DD$              | N/C                | R <sub>OUT57</sub>  | R <sub>OUT58</sub>  | R <sub>OUT59</sub> |

| (F1)                | (F2)                | (F3)                      | (F4)               | (F5)                  | (F6)                                                    | (F7)               | (F8)               | (F9)               | (F10)                | (F11)              | (F12)               | (F13)               | (F14)              |

| $PV_{DD}$           | RCLK <sub>0</sub>   | LOCK <sub>0</sub> *       | R <sub>OUT07</sub> | DGND                  | DGND                                                    | $DV_{DD}$          | DGND               | DGND               | $DV_DD$              | N/C                | $AV_{DD}$           | RCLK <sub>5</sub>   | $PV_{DD}$          |

| (G1)                | $\left( G2\right)$  | $\left( G3\right)$        | $\left( G4\right)$ | (G5)                  | $\binom{G6}{}$                                          | (G7)               | (G8)               | (G9)               | (G10)                | (G11)              | (G12)               | (G13)               | (G14)              |

| PGND                | PGND                | R <sub>OUTO6</sub>        | R <sub>OUT05</sub> | DGND                  | $OV_{DD}$                                               | DGND               | DGND               | DGND               | $OV_{DD}$            | R <sub>OUT55</sub> | R <sub>OUT56</sub>  | PGND                | $PV_{DD}$          |

| (H1)                | (H2)                | (H3)                      | (H4)               | (H5)                  | (H6)                                                    | (H7)               | (H8)               | (H9)               | (H10)                | (H 1 1)            | (H 1 2)             | (H13)               | (H14)              |

| PGND                | R <sub>OUTO4</sub>  | R <sub>OUT02</sub>        | R <sub>OUTO3</sub> | DGND                  | $OV_{DD}$                                               | DGND               | DGND               | DGND               | $\overline{DV_{DD}}$ | R <sub>OUT54</sub> | R <sub>OUT53</sub>  | PGND                | PGND               |

| $\left( J1\right)$  | $\left( J2\right)$  | $\left( J3\right)$        | (J4)               | $\left( J5\right)$    | $\left( \begin{array}{c} \text{J6} \end{array} \right)$ | $\left( J7\right)$ | (J8)               | (J9)               | (J10)                | (J11)              | (J12)               | (J13)               | (J14)              |

| $PV_{DD}$           | R <sub>OUT12</sub>  | R <sub>OUT10</sub>        | PGND               | $OV_{DD}$             | DGND                                                    | DGND               | $OV_{DD}$          | $OV_{DD}$          | $OV_{DD}$            | R <sub>OUT52</sub> | R <sub>OUT51</sub>  | PGND                | $PV_{DD}$          |

| (K1)                | (K2)                | (K3)                      | (K4)               | (K5)                  | (K6)                                                    | (K7)               | (K8)               | (K9)               | (K10)                | (K11)              | (K12)               | (K13)               | (K14)              |

| $PV_{DD}$           | R <sub>OUT14</sub>  | R <sub>OUTOO</sub>        | R <sub>OUTO1</sub> | $DV_{DD}$             | $DV_DD$                                                 | $DV_DD$            | DGND               | DGND               | $DV_DD$              | N/C                | R <sub>OUT50</sub>  | R <sub>OUT40</sub>  | $PV_{DD}$          |

| (L1)                | (L2)                | (L3)                      | L4)                | (L5)                  | (L6)                                                    | (L7)               | (L8)               | (L9)               | (L10)                | (L11)              | (L12)               | (L13)               | (L14)              |

| R <sub>OUT13</sub>  | RCLK <sub>1</sub>   | R <sub>OUT 1 1</sub>      | N/C                | N/C                   | R <sub>OUT21</sub>                                      | N/C                | R <sub>OUT31</sub> | R <sub>OUT34</sub> | N/C                  | R <sub>OUT45</sub> | R <sub>OUT41</sub>  | R <sub>OUT44</sub>  | R <sub>OUT42</sub> |

| $\left( M1\right)$  | $\left( M2\right)$  | $\left( M3\right)$        | $\left( M4\right)$ | $\left( M5\right)$    | (M6)                                                    | $\left( M7\right)$ | (M8)               | (M9)               | (M 1 0)              | (M 1 1)            | (M 1 2)             | (M 1 3)             | (M 1 4)            |

| R <sub>OUT15</sub>  | R <sub>OUT 18</sub> | R <sub>OUT 19</sub>       | R <sub>OUT29</sub> | R <sub>OUT25</sub>    | R <sub>OUT23</sub>                                      | R <sub>OUT20</sub> | R <sub>OUT30</sub> | R <sub>OUT33</sub> | R <sub>OUT35</sub>   | R <sub>OUT36</sub> | R <sub>OUT46</sub>  | RCLK <sub>4</sub>   | R <sub>OUT43</sub> |

| $\left( N1\right)$  | $\left( N2\right)$  | N3                        | N4                 | (N5)                  | N6                                                      | $\left(N7\right)$  | (N8)               | (N9)               | (N 1 0)              | $\left(N11\right)$ | (N 1 2)             | (N 1 3)             | (N 1 4)            |

| R <sub>OUT16</sub>  | R <sub>OUT 17</sub> | LOCK <sub>2</sub> *       | R <sub>OUT27</sub> | RCLK <sub>2</sub>     | R <sub>OUT22</sub>                                      | PGND               | PGND               | R <sub>OUT32</sub> | RCLK <sub>3</sub>    | R <sub>OUT37</sub> | R <sub>OUT39</sub>  | R <sub>OUT47</sub>  | R <sub>OUT48</sub> |

| P1                  | (P2)                | P3                        | P4                 | (P5)                  | P6                                                      | (P7)               | (P8)               | (P9)               | (P10)                | (P11)              | (P12)               | (P13)               | (P14)              |

| LOCK <sub>1</sub> * | R <sub>OUT28</sub>  | R <sub>OUT26</sub>        | R <sub>OUT24</sub> | $PV_{DD}$             | $PV_{DD}$                                               | PGND               | PGND               | $PV_{DD}$          | $PV_{DD}$            | R <sub>OUT38</sub> | LOCK <sub>3</sub> * | LOCK <sub>4</sub> * | R <sub>OUT49</sub> |

|                     |                     |                           |                    |                       |                                                         |                    |                    |                    |                      |                    |                     |                     | 20000214           |

# **Pin Descriptions**

| Pins                                                       | Pin Name   | Туре              | Description                                                                                                                                                                                         |

|------------------------------------------------------------|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B2,B14                                                     | GND        | GND               | GND pins for ESD structures                                                                                                                                                                         |

| C12,C13,B13                                                | SEL (0:2)  | 3.3V<br>CMOS<br>I | These pins control which Bus LVDS input is steered to the CHTST output                                                                                                                              |

| A4-A3, C6-C5, A7-A6,<br>C9-C8, A10-A9,<br>C11-C10, A13-A12 | Rin(n) +/- | Bus<br>LVDS<br>I  | Bus LVDS differential input pins                                                                                                                                                                    |

| D12                                                        | PVdd       |                   | Supply voltage for PLL circuitry                                                                                                                                                                    |

| F12                                                        | AVdd       |                   | Supply voltage for input buffer circuitry                                                                                                                                                           |

| B12,A14,D10                                                | PGND       |                   | GND pin for PLL circuitry                                                                                                                                                                           |

| B11                                                        | AGND       |                   | GND pin for input buffer circuitry                                                                                                                                                                  |

| C7                                                         | AVdd       |                   | Supply voltage for LVDS REC.                                                                                                                                                                        |

| B9                                                         | AVdd       |                   | Supply voltage for LVDS REC.                                                                                                                                                                        |

| A11                                                        | AVdd       |                   | Supply voltage for Band Gap reference.                                                                                                                                                              |

| B7                                                         | AGND       |                   | GND pin for AVDD.                                                                                                                                                                                   |

| A8                                                         | AGND       |                   | GND pin for AVDD1.                                                                                                                                                                                  |

| B8                                                         | AGND       |                   | GND pin for BGVDD.                                                                                                                                                                                  |

| A5                                                         | AGND       |                   | GND pin for VDDI.                                                                                                                                                                                   |

| B6                                                         | AVdd       |                   | Supply voltage for input logic circuitry.                                                                                                                                                           |

| D7                                                         | DGND       |                   | Tie to digital ground.                                                                                                                                                                              |

| B5                                                         | PWRDN      | 3.3V<br>CMOS<br>I | Controls whether the device is active or in 'sleep' mode                                                                                                                                            |

| C4                                                         | RCLK_R/F   | 3.3V<br>CMOS<br>I | Controls the relation of Rout data to RCLK edge: RCLK_R/F = H setup and hold times are referred to the rising RCLK edge; RCLK_R/F = L setup and hold times are referenced to the falling RCLK edge. |

| A2                                                         | REN        | 3.3V<br>CMOS<br>I | Enables the Routn, RCLKn, and SYNCCLK outputs.                                                                                                                                                      |

| B4                                                         | REFCLK     | 3.3V<br>CMOS<br>I | Frequency reference clock input.                                                                                                                                                                    |

| D5                                                         | DGND       |                   | GND pin for VDDO                                                                                                                                                                                    |

| A1                                                         | DGND       |                   | GND for digital section.                                                                                                                                                                            |

| B1                                                         | N/C        |                   | Do not connect.                                                                                                                                                                                     |

| D6                                                         | DVdd       |                   | Supply voltage for digital section.                                                                                                                                                                 |

| B3                                                         | DVdd       |                   | Supply voltage for digital section.                                                                                                                                                                 |

| С3                                                         | CHTST      | 3.3V<br>CMOS<br>O | Allows low speed testing of the Rin inputs under control of the SEL (0:2) pins.                                                                                                                     |

| F3,P1,N3,P12,P13,D13                                       | LOCK (0:5) | 3.3V<br>CMOS<br>O | Indicates the status of the PLLs for the individual deserializers: $\overline{LOCK} = L$ indicates locked, $\overline{LOCK} = H$ indicates unlicked.                                                |

| E6,J5,K5,K10,J10,E9                                        | DVdd       |                   | Supply voltage for the logic circuitry.                                                                                                                                                             |

# Pin Descriptions (Continued)

| Pins                                                                                                                                                                                                                                                                    | Pin Name   | Туре              | Description                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|------------------------------------------------------------------------------------|

| K3, K4, H3, H4, H2, G4, G3, F4, E4, E2, J3, L3, J2, L1, K2, M1, N1, N2, M2, M3, M7, L6, N6, M6, P4, M5, P3, N4, P2, M4, M8, L8, N9, M9, L9, M10, M11, N11, P11, N12, K13, L12, L14, M14, L13, L11, M12, N13, N14, P14, K12, J12, J11, H12, H11, G11, G12, E12, E13, E14 | Rout nx    | 3.3V<br>CMOS<br>O | Outputs for the ten bit deserializers, $n = deserializer$ number, $x = bit$ number |

| E5,G5,J6,K8,H9,F8                                                                                                                                                                                                                                                       | DGND       |                   | GND pins for digital section.                                                      |

| F2,L2,N5,N10,M13,F13                                                                                                                                                                                                                                                    | RCLK (0:5) | 3.3V<br>CMOS<br>O | Recovered clock for each deserializer's output data.                               |

| D6, F7, E7, G6, H6, K7,<br>K6, J8, J9, G10, H10,<br>F10, E10                                                                                                                                                                                                            | DVdd       |                   | Supply voltage for output buffers.                                                 |

| D5, F6, F5, G7, H5, J7,<br>H7, H8, K9, G9, G8, F9,<br>E8                                                                                                                                                                                                                | DGND       |                   | GND pins for output buffers.                                                       |

| F1, E1, J1, K1, P6, P5,<br>P9, P10, J14, K14, G14,<br>F14                                                                                                                                                                                                               | PVdd       |                   | Supply voltages for PLL circuitry.                                                 |

| G2, G1, H1, J4, N7, P7,<br>P8, N8, J13, H14, H13,<br>G13                                                                                                                                                                                                                | PGND       |                   | GND pins for PLL circuitry.                                                        |

| C2,C1,D1,D2,D3,                                                                                                                                                                                                                                                         | JTL (1:5)  |                   | Reserved pins for JTAG access port.                                                |

| L4, L5, L7, L10, K11,<br>D11, B10, D9, E3, D4,<br>E11, F11, D8, D14, C14                                                                                                                                                                                                | N/C        |                   | Unused solder ball location. Do not connect.                                       |

### Physical Dimensions inches (millimeters)

unless otherwise noted

DIMENSIONS ARE IN MILLIMETERS

ILIR1964 (Rev B)

Order Number DS92LV1260TUJB **NS Package Number UJB196A**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor Americas Customer Support Center**

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560