### PART NUMBER

### TS82527-ROC

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### intط

### 82527 SERIAL COMMUNICATIONS CONTROLLER CONTROLLER AREA NETWORK PROTOCOL

Automotive

- Supports CAN Specification 2.0 - Standard Data and Remote Frames Extended Data and Remote Frames

- Programmable Global Mask Standard Message Identifier Extended Message Identifier

- 15 Message Objects of 8-Byte Data Length

- 14 Tx/Rx Buffers

- 1 Rx Buffer with Programmable Mask

- Flexible CPU Interface

- 8-Bit Multiplexed

- 16-Bit Multiplexed

- 8-Bit Non-Multiplexed

- (Synchronous/Asynchronous)

- Serial Interface

- Programmable Bit Rate

- Programmable Clock Output

- Flexible Interrupt Structure

- Flexible Status Interface

- Configurable Output Driver

- Configurable Input Comparator

- Two 8-Bit Bidirectional I/O Ports

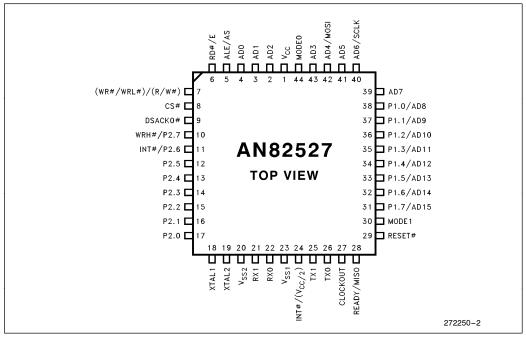

- 44-Lead PLCC Package

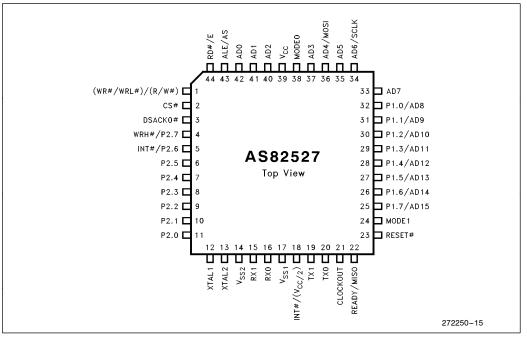

- 44-Lead QFP Package

- Pinout Compatibility with the 82526

The 82527 serial communications controller is a highly integrated device that performs serial communication according to the CAN protocol. It performs all serial communication functions such as transmission and reception of messages, message filtering, transmit search, and interrupt search with minimal interaction from the host microcontroller, or CPU.

The 82527 is Intel's first device to support the standard and extended message frames in CAN Specification 2.0 Part B. It has the capability to transmit, receive, and perform message filtering on extended message frames. Due to the backwardly compatible nature of CAN Specification 2.0, the 82527 also fully supports the standard message frames in CAN Specification 2.0 Part A.

The 82527 features a powerful CPU interface that offers flexibility to directly interface to many different CPUs. It can be configured to interface with CPUs using an 8-bit multiplexed, 16-bit multiplexed, or 8-bit non-multiplexed address/data bus for Intel and non-Intel architectures. A flexible serial interface (SPI) is also available when a parallel CPU interface is not required.

The 82527 provides storage for 15 message objects of 8-byte data length. Each message object can be configured as either transmit or receive except for the last message object. The last message object is a receive-only buffer with a special mask design to allow select groups of different message identifiers to be received.

The 82527 also implements a global masking feature for message filtering. This feature allows the user to globally mask any identifier bits of the incoming message. The programmable global mask can be used for both standard and extended messages.

The 82527 PLCC offers hardware, or pinout, compatibility with the 82526. It is pin-to-pin compatible with the 82526 except for pins 9, 30, and 44. These pins are used as chip selects on the 82526 and are used as CPU interface mode selection pins on the 82527.

The 82527 is fabricated using Intel's reliable CHMOS III 5V technology and is available in either 44-lead PLCC or 44-lead QFP for the automotive temperature range ( $-40^{\circ}$ C to  $+125^{\circ}$ C).

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1995 December 1995 Order Number: 272250-006

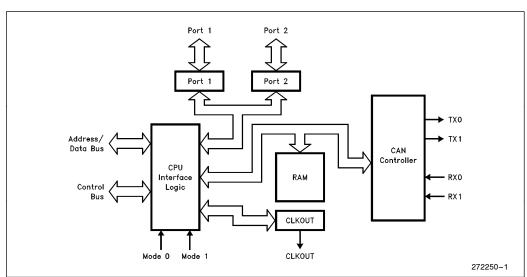

Figure 1. 82527 Block Diagram

Figure 2. 44-Pin PLCC Package

Figure 3. 44-Pin QFP Package

### PIN DESCRIPTION

The 82527 pins are described in this section. Table 1 presents the legend for interpreting the pin types.

| Table 1. Pin Type Legend             |                 |  |

|--------------------------------------|-----------------|--|

| Symbol Description                   |                 |  |

| I                                    | Input only pin  |  |

| 0                                    | Output only pin |  |

| I/O Pin can be either input or outpu |                 |  |

#### **PIN DESCRIPTIONS**

| Pin Name                     | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS1</sub>             | Ground   | GROUND connection must be connected externally to a V <sub>SS</sub> board plane. Provides digital ground.                                                                                                                                                                                                                                                                                |

| V <sub>SS2</sub>             | Ground   | GROUND connection must be connected externally to a $V_{SS}$ board plane. Provides ground for analog comparator.                                                                                                                                                                                                                                                                         |

| V <sub>CC</sub>              | Power    | POWER connection must be connected externally to $\pm$ 5V DC. Provides power for entire device.                                                                                                                                                                                                                                                                                          |

| XTAL1                        | Ι        | Input for an external clock. XTAL1 (along with XTAL2) are the crystal connections to an internal oscillator.                                                                                                                                                                                                                                                                             |

| XTAL2                        | 0        | Push-pull output from the internal oscillator. XTAL2 (along with XTAL1) are the crystal connections to an internal oscillator. If an external oscillator is used XTAL2 must be floated, or not be connected. XTAL2 must not be used as a clock output to drive other CPUs.                                                                                                               |

| CLKOUT                       | 0        | Programmable clock output. This output may be used to drive the oscillator of the host microcontroller.                                                                                                                                                                                                                                                                                  |

| RESET#                       | I        | Warm Reset: (V <sub>CC</sub> remains valid while RESET# is asserted), RESET# must be driven to a valid low level for 1 ms minimum.<br>Cold Reset: (V <sub>CC</sub> is driven to a valid level while RESET# is asserted), RESET# must be driven low for 1 ms minimum measured from a valid V <sub>CC</sub> level. No falling edge on the reset pin is required during a cold reset event. |

| CS#                          | I        | A low level on this pin enables CPU access to the 82527 device.                                                                                                                                                                                                                                                                                                                          |

| INT#<br>(V <sub>CC</sub> /2) | 0        | The interrupt pin is an open-drain output to the host microcontroller. $V_{CC}/2$ is<br>the power supply for the ISO low speed physical layer. The function of this pin is<br>determined by the MUX bit in the CPU Interface Register (Address 02H) as<br>follows:<br>$MUX = 1$ : pin 24 (PLCC) = $V_{CC}/2$ , pin 11 = INT #<br>MUX = 0: pin 24 (PLCC) = INT #                          |

| RX0<br>RX1                   |          | Inputs from the CAN bus line(s) to the input comparator. A recessive level is read when RX0 $>$ RX1. A dominant level is read when RX1 $>$ RX0. When the CoBy bit (Bus Configuration register) is programmed as a "1", the input comparator is bypassed and RX0 is the CAN bus line input.                                                                                               |

| TX0<br>TX1                   | 0<br>0   | Serial data push-pull output to the CAN bus line. During a recessive bit TX0 is high and TX1 is low. During a dominant bit TX0 is low and TX1 is high.                                                                                                                                                                                                                                   |

| Pin Name                                                                                                                   | Pin Type                                                                                             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AD0/A0/ICP<br>AD1/A1/CP<br>AD2/A2/CSAS<br>AD3/A3/STE<br>AD4/A4/MOSI<br>AD5/A5<br>AD6/A6/SCLK<br>AD7/A7                     | /O- - <br> /O- -                                         | Address/Data bus in 8-bit multiplexed mode.         Address bus in 8-bit non-multiplexed mode.         Low byte of A/D bus in 16-bit multiplexed mode.         In Serial Interface mode, the following pins have the following meaning:         AD0:       ICP         ICP       Idle Clock Polarity         AD1:       CP         Clock Phase         AD2:       CSAS         Chip Select Active State         AD3:       STE         Sync Transmit Enable         AD6:       SCLK         Serial Data Input |  |  |

| AD8/D0/P1.0<br>AD9/D1/P1.1<br>AD10/D2/P1.2<br>AD11/D3/P1.3<br>AD12/D4/P1.4<br>AD13/D5/P1.5<br>AD14/D6/P1.6<br>AD15/D7/P1.7 | I/O-O-I/O<br>I/O-O-I/O<br>I/O-O-I/O<br>I/O-O-I/O<br>I/O-O-I/O<br>I/O-O-I/O<br>I/O-O-I/O<br>I/O-O-I/O | High byte of A/D bus in 16-bit multiplexed mode.<br>Data bus in 8-bit non-multiplexed mode.<br>Low speed I/O port. P1 pins in 8-bit multiplexed mode and serial mode.<br>Port pins have weak pullups until the port is configured by writing to 9FH<br>and AFH.                                                                                                                                                                                                                                               |  |  |

| P2.0<br>P2.1<br>P2.2<br>P2.3<br>P2.4<br>P2.5<br>P2.6/INT#<br>P2.7/WRH#                                                     | 1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0-0<br>1/0-1                                             | P2 in all modes.<br>P2.6 is INT # when MUX = 1 and is open-drain.<br>P2.7 is WRH # in 16-bit multiplexed mode.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Mode0<br>Mode1                                                                                                             | I                                                                                                    | These pins select one of the four parallel interfaces. These pins are<br>weakly held low during reset.Mode1Mode0008-bit multiplexed — Intel00Serial Interface mode entered when $RD \# = 0$ ,<br>$WR \# = 0$ upon reset.0116-bit multiplexed — Intel108-bit multiplexed — non-Intel118-bit non-multiplexed                                                                                                                                                                                                    |  |  |

| ALE/AS                                                                                                                     | I-I                                                                                                  | ALE used for Intel modes.<br>AS used for non-Intel modes, except Mode 3 this pin must be tied high.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RD#<br>E                                                                                                                   | l<br>l                                                                                               | RD# used for Intel modes.<br>E used for non-Intel modes, except Mode 3 Asynchronous this pin must<br>be tied high.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| WR#/WRL#<br>R/W#                                                                                                           |                                                                                                      | WR# in 8-bit Intel mode and WRL# in 16-bit Intel mode.<br>R/W# used for non-Intel modes.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| READY<br>MISO                                                                                                              | 0<br>0                                                                                               | READY is an output to synchronize accesses from the host<br>microcontroller to the 82527. READY is an open-drain output to the host<br>microcontroller. MISO is the serial data output for the serial interface<br>mode.                                                                                                                                                                                                                                                                                      |  |  |

| DSACK0#                                                                                                                    | 0                                                                                                    | DSACK0# is an open-drain output to synchronize accesses from the host microcontroller to the 82527.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

#### **ELECTRICAL CHARACTERISTICS**

#### ABSOLUTE MAXIMUM RATINGS\*

Storage Temperature  $\dots -60^{\circ}C$  to  $+150^{\circ}C$  Voltage from Any Pin

to  $V_{SS}$  ..... -0.5V to +7.0V

Laboratory testing shows the 82527 will withstand up to 10 mA of injected current into both RX0 and RX1 pins for a total of 20 days without sustaining permanent damage. This high current condition may be the result of shorted signal lines. The 82527 will not function properly if the RX0/RX1 input voltage exceeds  $V_{CC}\!+\!0.5V.$

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

| Symbol            | Parameter                                                                           | Min                 | Max                 | Conditions                                      |

|-------------------|-------------------------------------------------------------------------------------|---------------------|---------------------|-------------------------------------------------|

| VIL               | Input Low Voltage (All except RX0, RX1, AD0-AD7 in Mode 3)                          | -0.5V               | 0.8V                |                                                 |

| V <sub>IL1</sub>  | Input Low Voltage for AD0–AD7 in<br>Mode 3                                          | -0.5V               | 0.5V                |                                                 |

| V <sub>IL2</sub>  | Input Low Voltage (RX0) for Comparator<br>Bypass Mode                               |                     | 0.5V                |                                                 |

| V <sub>IL3</sub>  | Input Low Voltage for Port 1 and Port 2<br>Pins Not Used for Interface to Host CPU  |                     | 0.3 V <sub>CC</sub> |                                                 |

| V <sub>IH</sub>   | Input High Voltage (All except RX0, RX1, RESET#)                                    | 3.0V                | $V_{CC}$ + 0.5V     |                                                 |

| V <sub>IH1</sub>  | Input High Voltage (RESET #)<br>Hysteresis on RESET #                               | 3.0V<br>200 mV      | $V_{CC}$ + 0.5V     |                                                 |

| V <sub>IH2</sub>  | Input High Voltage (RX0) for Comparator<br>Bypass Mode                              | 4.0V                |                     |                                                 |

| V <sub>IH3</sub>  | Input High Voltage for Port 1 and Port 2<br>Pins Not Used for Interface to Host CPU | 0.7 V <sub>CC</sub> |                     |                                                 |

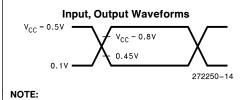

| V <sub>OL</sub>   | Output Low Voltage (All Outputs except TX0, TX1)                                    |                     | 0.45V               | $I_{OL} = 1.6 \text{ mA}$                       |

| V <sub>OH</sub>   | Output High Voltage (All Outputs except TX0, TX1, CLOCKOUT)                         | $V_{\rm CC}-0.8V$   |                     | $I_{OH} = -200 \ \mu A$                         |

| V <sub>OHR1</sub> | Output High Voltage (CLOCKOUT)                                                      | 0.8 V <sub>CC</sub> |                     | $I_{OH} = -80 \ \mu A$                          |

| I <sub>LK</sub>   | Input Leakage Current                                                               |                     | ±10 μA              | $v_{\text{SS}} < v_{\text{IN}} < v_{\text{CC}}$ |

| C <sub>IN</sub>   | PIN Capacitance**                                                                   |                     | 10 pF               | $f_{XTAL} = 1 \text{ KHz}$                      |

#### **D.C. Characteristics** $V_{CC} = 5V \pm 10\%$ ; $T_A = -40^{\circ}C$ to $+125^{\circ}C$

| Symbol             | Parameter                                                                                            | Min | Max              | Conditions                 |

|--------------------|------------------------------------------------------------------------------------------------------|-----|------------------|----------------------------|

| Icc                | Supply Current <sup>(1)</sup>                                                                        |     | 50 mA            | f <sub>XTAL</sub> = 16 MHz |

| I <sub>SLEEP</sub> | Sleep Current <sup>(1)</sup> with $V_{CC}/2$ Output Enabled, No Load with $V_{CC}/2$ Output Disabled |     | 700 μΑ<br>100 μΑ |                            |

| I <sub>PD</sub>    | Powerdown Current <sup>(1)</sup>                                                                     |     | 25 μΑ            | XTAL1 Clocked              |

### **D.C. Characteristics** $V_{CC} = 5V \pm 10\%$ ; $T_A = -40^{\circ}C$ to $+125^{\circ}C$

NOTES:

\*\*Typical value based on characterization data. Port pins are weakly held after reset until the port configuration registers are written (9FH, AFH). 1. All pins are driven to V<sub>SS</sub> or V<sub>CC</sub> including RX0 and RX1.

### PHYSICAL LAYER SPECIFICATIONS Load Condition: 100 pF

| <b>D.C. Characteristics</b> $V_{CC} = 1$ | $5V \pm 10\%$ ; $T_A = -40^{\circ}C \text{ to } + 125^{\circ}C$ |

|------------------------------------------|-----------------------------------------------------------------|

|------------------------------------------|-----------------------------------------------------------------|

| RX0/RX1 and TX0/TX1                                                                                                  | Min           | Max             | Conditions                                                                    |

|----------------------------------------------------------------------------------------------------------------------|---------------|-----------------|-------------------------------------------------------------------------------|

| Input Voltage                                                                                                        | -0.5V         | $V_{CC}$ + 0.5V |                                                                               |

| Common Mode Range                                                                                                    | $V_{SS} + 1V$ | $V_{CC} - 1V$   |                                                                               |

| Differential Input Threshold                                                                                         | $\pm$ 100 mV  |                 |                                                                               |

| Internal Delay 1: Sum of the Comparator Input<br>Delay and the TX0/TX1 Output Driver Delay                           |               | 60 ns           | Load on TX0, TX1 $=$<br>100 pF, +100 mV to<br>-100 mV RX0/RX1<br>differential |

| Internal Delay 2: Sum of the RX0 Pin Delay (if<br>the Comparator is Bypassed) and the TX0/TX1<br>Output Driver Delay |               | 50 ns           | Load on TX0, TX1 =<br>100 pF                                                  |

| Source Current on Each TX0, TX1                                                                                      |               | —10 mA          | $V_{OUT} = V_{CC} - 1.0V$                                                     |

| Sink Current on Each TX0, TX1                                                                                        |               | 10 mA           | $V_{OUT} = 1.0V$                                                              |

| Input Hysteresis for RX0/RX1                                                                                         |               | 0V              |                                                                               |

| V <sub>CC</sub> /2                                                                                                   |               |                 |                                                                               |

| V <sub>CC</sub> /2                                                                                                   | 2.38V         | 2.62V           | $I_{OUT} \le 75 \ \mu A, V_{CC} = 5V$                                         |

#### **CLOCKOUT SPECIFICATIONS**

Load Condition: 50 pF

| Parameter          | Min     | Max  |

|--------------------|---------|------|

| CLOCKOUT Frequency | XTAL/15 | XTAL |

| Symbol              | $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ , $T_A = -40^{\circ}C$ to<br>Parameter                                                                                                                            | Min    | Max                                                              | Conditions                       |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------|----------------------------------|

| 1/t <sub>XTAL</sub> | Oscillator Frequency                                                                                                                                                                                     | 8 MHz  | 16 MHz                                                           | Contaitionio                     |

| 1/t <sub>SCLK</sub> | System Clock Frequency                                                                                                                                                                                   | 4 MHz  | 10 MHz                                                           |                                  |

| 1/t <sub>MCLK</sub> | Memory Clock Frequency                                                                                                                                                                                   | 2 MHz  | 8 MHz                                                            |                                  |

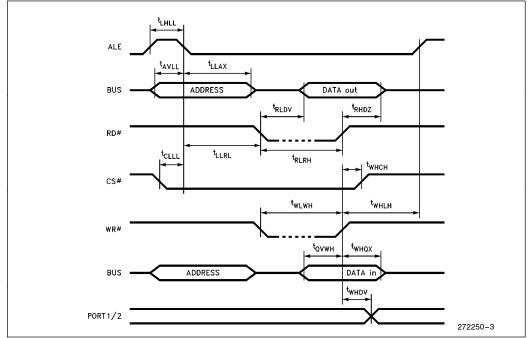

| t <sub>AVLL</sub>   | Address Valid to ALE Low                                                                                                                                                                                 | 7.5 ns |                                                                  |                                  |

| t <sub>LLAX</sub>   | Address Hold after ALE Low                                                                                                                                                                               | 10 ns  |                                                                  |                                  |

| t <sub>LHLL</sub>   | ALE High Time                                                                                                                                                                                            | 30 ns  |                                                                  |                                  |

| t <sub>LLRL</sub>   | ALE Low to RD# Low                                                                                                                                                                                       | 20 ns  |                                                                  |                                  |

| tCLLL               | CS # Low to ALE Low                                                                                                                                                                                      | 10 ns  |                                                                  |                                  |

| t <sub>QVWH</sub>   | Data Setup to WR # High                                                                                                                                                                                  | 27 ns  |                                                                  |                                  |

| t <sub>WHQX</sub>   | Input Data Hold after WR # High                                                                                                                                                                          | 10 ns  |                                                                  |                                  |

| twlwh               | WR # Pulse Width                                                                                                                                                                                         | 30 ns  |                                                                  |                                  |

| twhlh               | WR # High to Next ALE High                                                                                                                                                                               | 8 ns   |                                                                  |                                  |

| tWHCH               | WR# High to CS# High                                                                                                                                                                                     | 0 ns   |                                                                  |                                  |

| t <sub>RLRH</sub>   | RD # Pulse Width<br>This time is long enough to initiate a double<br>read cycle by loading the High Speed<br>Registers (04H, 05H), but is too short to<br>READ from 04H and 05H (See t <sub>RLDV</sub> ) | 40 ns  |                                                                  |                                  |

| t <sub>RLDV</sub>   | RD# Low to Data Valid<br>(Only for Registers 02H, 04H, 05H)                                                                                                                                              | 0 ns   | 55 ns                                                            |                                  |

| t <sub>RLDV1</sub>  | RD # Low Data to Data Valid (for Registers<br>except 02H, 04H, 05H)<br>for Read Cycle without a Previous Write <sup>(1)</sup><br>for Read Cycle with a Previous Write <sup>(1)</sup>                     |        | 1.5 t <sub>MCLK</sub> + 100 ns<br>3.5 t <sub>MCLK</sub> + 100 ns |                                  |

| t <sub>RHDZ</sub>   | Data Float after RD# High                                                                                                                                                                                | 0 ns   | 45 ns                                                            |                                  |

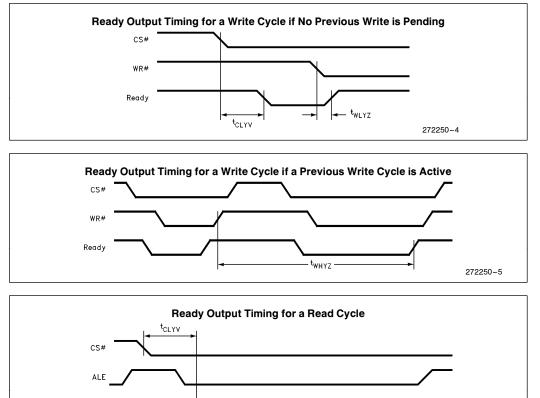

| t <sub>CLYV</sub>   | CS # Low to READY Setup<br>Condition: Load Capacitance on the READY<br>Output: 50 pF                                                                                                                     |        | 32 ns<br>40 ns                                                   | $V_{OL} = 1.0V$ $V_{OL} = 0.45V$ |

| t <sub>WLYZ</sub>   | WR # Low to READY Float for a Write Cycle<br>if No Previous Write is Pending <sup>(2)</sup>                                                                                                              |        | 145 ns                                                           |                                  |

| t <sub>WHYZ</sub>   | End of Last Write to READY Float for a Write Cycle if a Previous Write Cycle is Active <sup>(2)</sup>                                                                                                    |        | 2 t <sub>MCLK</sub> + 100 ns                                     |                                  |

| t <sub>RLYZ</sub>   | RD# Low to READY Float<br>(for registers except 02H, 04H, 05H)<br>for Read Cycle without a Previous Write <sup>(1)</sup><br>for Read Cycle with a Previous Write <sup>(1)</sup>                          |        | 2 t <sub>MCLK</sub> + 100 ns<br>4 t <sub>MCLK</sub> + 100 ns     |                                  |

### A.C. Characteristics for 8/16-Bit Multiplexed Intel Modes (Modes 0, 1)

#### A.C. Characteristics for 8/16-Bit Multiplexed Intel Modes (Modes 0, 1)

Conditions:  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ ,  $T_A = -40^{\circ}C$  to  $+ 125^{\circ}C$ ,  $C_L = 100$  pF (Continued)

| Symbol            | Parameter                                     | Min                                                           | Мах                                                           | Conditions |  |  |

|-------------------|-----------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|------------|--|--|

| t <sub>WHDV</sub> | WR # High to Output Data Valid<br>on Port 1/2 | t <sub>MCLK</sub>                                             | $2 t_{MCLK} + 500 ns$                                         |            |  |  |

| t <sub>COPO</sub> | CLKOUT Period                                 | (CD <sub>V</sub> + 1                                          | ) * t <sub>OSC</sub> (3)                                      |            |  |  |

| t <sub>CHCL</sub> | CLKOUT High Period                            | (CD <sub>V</sub> + 1) * 1/ <sub>2</sub> t <sub>OSC</sub> - 10 | (CD <sub>V</sub> + 1) * 1/ <sub>2</sub> t <sub>OSC</sub> + 15 |            |  |  |

#### NOTES:

References to WR# also pertain to WRH#.

1. Definition of "read cycle without a previous write": The time between the rising edge of WR#/WRH# (for the previous

The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the previous write": The time between the fising edge of WR #7WRH # (for the current write cycle) is less than 2 t<sub>MCLK</sub>. 3. Definition of CD<sub>V</sub> is the value loaded in the CLKOUT register representing the CLKOUT divisor.

#### A.C. Characteristics for 8/16-Bit Multiplexed Intel Modes (Modes 0, 1)

272250-6

t<sub>RLYZ</sub>

### A.C. Characteristics for 8/16-Bit Multiplexed Intel Modes (Modes 0, 1)

82527

RD#

Ready

| Parameter                                                                                                                                  | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillator Frequency                                                                                                                       | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| System Clock Frequency                                                                                                                     | 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Memory Clock Frequency                                                                                                                     | 2 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

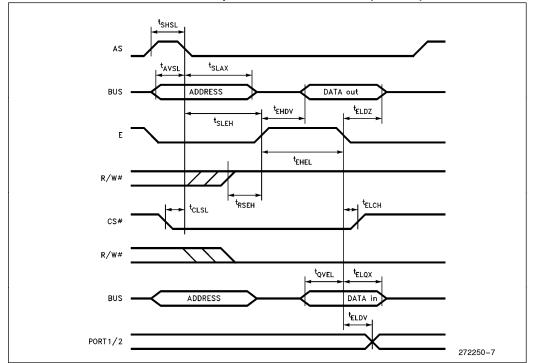

| Address Valid to AS Low                                                                                                                    | 7.5 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address Hold after AS Low                                                                                                                  | 10 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

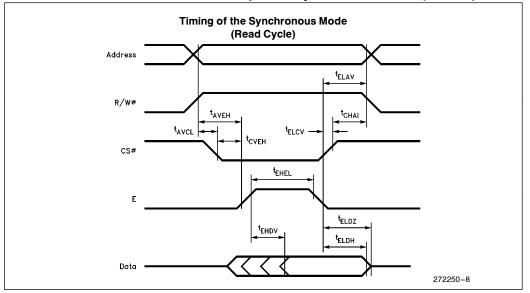

| Data Float after E Low                                                                                                                     | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| E High to Data Valid for Registers 02H,<br>04H, 05H                                                                                        | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| for Read Cycle without a Previous Write <sup>(1)</sup><br>for Read Cycle with a Previous Write<br>(for Registers except for 02H, 04H, 05H) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.5 t <sub>MCLK</sub> + 100 ns<br>3.5 t <sub>MCLK</sub> + 100 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

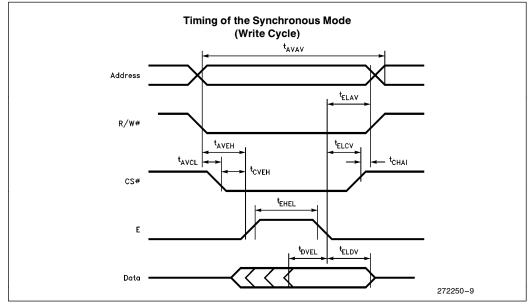

| Data Setup to E Low                                                                                                                        | 30 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Input Data Hold after E Low                                                                                                                | 20 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E Low to Output Data Valid on Port 1/2                                                                                                     | t <sub>MCLK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2 t <sub>MCLK</sub> + 500 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| E High Time                                                                                                                                | 45 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| End of Previous Write (Last E Low) to E<br>Low for a Write Cycle                                                                           | 2 t <sub>MCLK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AS High Time                                                                                                                               | 30 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Setup Time of R/W # to E High                                                                                                              | 30 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AS Low to E High                                                                                                                           | 20 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CS# Low to AS Low                                                                                                                          | 20 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E Low to CS # High                                                                                                                         | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                            | Oscillator Frequency<br>System Clock Frequency<br>Memory Clock Frequency<br>Address Valid to AS Low<br>Address Valid to AS Low<br>Address Hold after AS Low<br>Data Float after E Low<br>E High to Data Valid for Registers 02H,<br>04H, 05H<br>for Read Cycle without a Previous Write <sup>(1)</sup><br>for Read Cycle with a Previous Write <sup>(1)</sup><br>for Read Cycle with a Previous Write<br>(for Registers except for 02H, 04H, 05H)<br>Data Setup to E Low<br>Input Data Hold after E Low<br>E Low to Output Data Valid on Port 1/2<br>E High Time<br>End of Previous Write (Last E Low) to E<br>Low for a Write Cycle<br>AS High Time<br>Setup Time of R/W # to E High<br>AS Low to E High<br>CS # Low to AS Low | Oscillator Frequency8 MHzSystem Clock Frequency4 MHzMemory Clock Frequency2 MHzAddress Valid to AS Low7.5 nsAddress Valid to AS Low10 nsData Float after AS Low0 nsE High to Data Valid for Registers 02H,<br>04H, 05H0 nsfor Read Cycle without a Previous Write<br>(for Registers except for 02H, 04H, 05H)30 nsInput Data Hold after E Low30 nsInput Data Hold after E Low20 nsE Low to Output Data Valid on Port 1/2t_MCLKE High Time45 nsEnd of Previous Write (Last E Low) to E<br>Low for a Write Cycle2 t_MCLKAS High Time30 nsSetup Time of R/W# to E High30 nsAS Low to E High20 nsCS# Low to AS Low20 ns |

### A.C. Characteristics for 8-Bit Multiplexed Non-Intel Mode (Mode 2)

t<sub>CHCL</sub> NOTES:

tCOPD

**CLKOUT** Period

**CLKOUT High Period**

1. Definition of "Read Cycle without a Previous Write": The time between the falling edge of E (for the previous write cycle)

(CD<sub>V</sub> + 1) \*  $t_{OSC}^{(3)}$

$(CD_V + 1) * \frac{1}{2} t_{OSC} - 10$   $(CD_V + 1) * \frac{1}{2} t_{OSC} + 15$

and the rising edge of E (for the current read cycle) is greater than 2  $t_{MCLK}$ . 2. Definition of "Write Cycle with a Previous Write": The time between the falling edge of E (for the previous write cycle) and the falling edge of E (for the current write cycle) is less than 2  $t_{MCLK}$ . 3. Definition of CD<sub>V</sub> is the value loaded in the CLKOUT register representing the CLKOUT divisor.

A.C. Characteristics for 8-Bit Multiplexed Non-Intel Mode (Mode 2)

| Symbol              | Parameter                                                                                                                             | Min   | Max                            |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|

| 1/t <sub>XTAL</sub> | Oscillator Frequency                                                                                                                  | 8 MHz | 16 MHz                         |

| 1/t <sub>SCLK</sub> | System Clock Frequency                                                                                                                | 4 MHz | 10 MHz                         |

| 1/t <sub>MCLK</sub> | Memory Clock Frequency                                                                                                                | 2 MHz | 8 MHz                          |

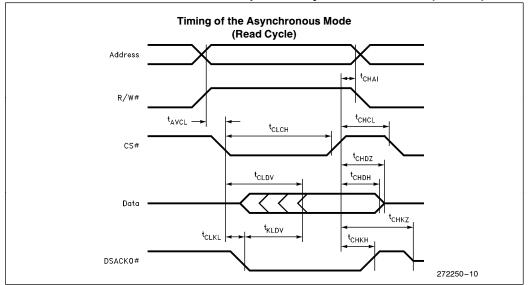

| t <sub>AVCL</sub>   | Address or R/W # Valid to CS # Low<br>Setup                                                                                           | 3 ns  |                                |

| t <sub>CLDV</sub>   | CS # Low to Data Valid<br>for High Speed Registers (02H, 04H, 05H)                                                                    | 0 ns  | 55 ns                          |

|                     | For Low Speed Registers<br>(Read Cycle without Previous Write) <sup>(1)</sup>                                                         | 0 ns  | 1.5 t <sub>MCLK</sub> + 100 ns |

|                     | For Low Speed Registers<br>(Read Cycle with Previous Write) <sup>(1)</sup>                                                            | 0 ns  | 3.5 t <sub>MCLK</sub> + 100 ns |

| t <sub>KLDV</sub>   | DSACK0# Low to Output Data Valid<br>for High Speed Read Register                                                                      |       | 23 ns                          |

|                     | For Low Speed Read Register                                                                                                           | <0 ns |                                |

| t <sub>CHDV</sub>   | 82527 Input Data Hold after CS# High                                                                                                  | 15 ns |                                |

| t <sub>CHDH</sub>   | 82527 Output Data Hold after CS# High                                                                                                 | 0 ns  |                                |

| t <sub>CHDZ</sub>   | CS# High to Output Data Float                                                                                                         |       | 35 ns                          |

| t <sub>CHKH1</sub>  | CS# High to DSACK0 $\# = 2.4V^{(3)}$                                                                                                  | 0 ns  | 55 ns                          |

| t <sub>CHKH2</sub>  | CS# High to DSACK0 $\# = 2.8V$                                                                                                        |       | 150 ns                         |

| t <sub>CHKZ</sub>   | CS# High to DSACK0# Float                                                                                                             | 0 ns  | 100 ns                         |

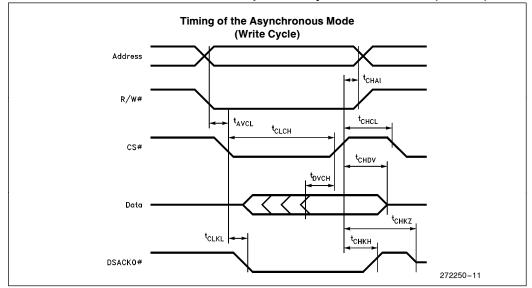

| t <sub>CHCL</sub>   | CS# Width between Successive Cycles                                                                                                   | 25 ns |                                |

| t <sub>CHAI</sub>   | CS# High to Address Invalid                                                                                                           | 7 ns  |                                |

| t <sub>CHRI</sub>   | CS# High to R/W# Invalid                                                                                                              | 5 ns  |                                |

| t <sub>CLCH</sub>   | CS# Width Low                                                                                                                         | 65 ns |                                |

| t <sub>DVCH</sub>   | CPU Write Data Valid to CS # High                                                                                                     | 20 ns |                                |

| t <sub>CLKL</sub>   | CS # Low to DSACK0 # Low<br>for High Speed Registers and Low Speed<br>Registers Write Access without Previous<br>Write <sup>(2)</sup> | 0 ns  | 67 ns                          |

| <sup>t</sup> CHKL   | End of Previous Write (CS # High) to<br>DSACK0 # Low for a Write Cycle with a<br>Previous Write <sup>(2)</sup>                        | 0 ns  | 2 t <sub>MCLK</sub> + 145 ns   |

#### A.C. Characteristics for 8-Bit Non-Multiplexed Asynchronous (Mode 3) Conditions: $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ , $C_L = 100 \text{ pF}$

### t<sub>CHCL</sub> NOTES:

**t**COPD

E and AS must be tied high in this mode.

**CLKOUT** Period

**CLKOUT High Period**

1. Definition of "Read Cycle without a Previous Write": The time between the rising edge of CS# (for the previous write cycle) and the falling edge of CS# (for the current read cycle) is greater than 2  $t_{MCLK}$ . 2. Definition of "Write Cycle without a Previous Write": The time between the rising edge of CS# (for the previous write

(CD<sub>V</sub> + 1) \* t<sub>OSC</sub><sup>(4)</sup>  $(CD_V + 1) * \frac{1}{2} t_{OSC} - 10 | (CD_V + 1) * \frac{1}{2} t_{OSC} + 15$

2. Definited of the system with a structure that a transformation of the system of th

voltage.

4. Definition of CD<sub>V</sub> is the value loaded in the CLKOUT register representing the CLKOUT divisor.

#### A.C. Characteristics for 8-Bit Non-Multiplexed Asynchronous Mode (Mode 3)

#### A.C. Characteristics for 8-Bit Non-Multiplexed Asynchronous Mode (Mode 3)

| Symbol              | Parameter                                                                | Min                                             | Мах                                              |

|---------------------|--------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------|

| 1/t <sub>XTAL</sub> | Oscillator Frequency                                                     | 8 MHz                                           | 16 MHz                                           |

| 1/t <sub>SCLK</sub> | System Clock Frequency                                                   | 4 MHz                                           | 10 MHz                                           |

| 1/t <sub>MCLK</sub> | Memory Clock Frequency                                                   | 2 MHz                                           | 8 MHz                                            |

| <sup>t</sup> ehdv   | E High to Data Valid out of High Speed<br>Register (02H, 04H, 05H)       |                                                 | 55 ns                                            |

|                     | Read Cycle without Previous Write for Low Speed Registers <sup>(1)</sup> |                                                 | 1.5 t <sub>MCLK</sub> + 100 ns                   |

|                     | Read Cycle with Previous Write for Low Speed Registers <sup>(1)</sup>    |                                                 | 3.5 t <sub>MCLK</sub> + 100 ns                   |

| t <sub>ELDH</sub>   | Data Hold after E Low for a Read<br>Cycle                                | 5 ns                                            |                                                  |

| t <sub>ELDZ</sub>   | Data Float after E Low                                                   |                                                 | 35 ns                                            |

| t <sub>ELDV</sub>   | Data Hold after E Low for a Write Cycle                                  | 15 ns                                           |                                                  |

| t <sub>AVEH</sub>   | Address and R/W# to E Setup                                              | 25 ns                                           |                                                  |

| t <sub>ELAV</sub>   | Address and R/W # Valid after E Falls                                    | 15 ns                                           |                                                  |

| t <sub>CVEH</sub>   | CS # Valid to E High                                                     | 0 ns                                            |                                                  |

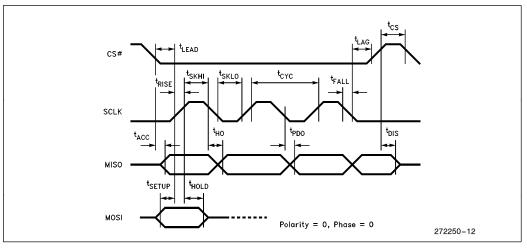

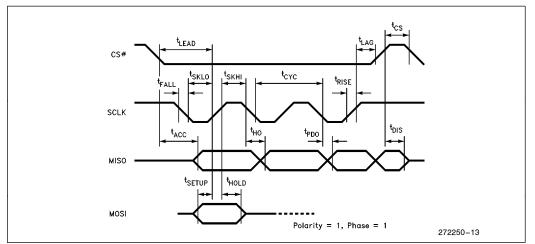

| t <sub>ELCV</sub>   | CS # Valid after E Low                                                   | 0 ns                                            |                                                  |