- IEEE 802.5 and IBM Token-Ring Network Compatible

- IEEE 802.3 and Blue Book Ethernet Network Compatible

- Pin and Software Compatible With the TMS380C16

- Configurable Network Type and Speed:

- Selectable by Host Software Control (Adapter Control Register)

- Selectable by Network Front-End

- Readable from Host (Adapter Control Register)

- Token-Ring Features

- 16- or 4-Megabit-per-Second Data Rates

- Supports up to 18K-Byte Frame Size (16 Mbps Operation Only)

- Supports Universal and Local Network Addressing

- Early Token Release Option (16 Mbps Operation Only)

- Compatible With the TMS38054

- Ethernet Features

- 10-Megabit-per-Second Data Rate

- Compatible With Most Ethernet Serial Network Interface Devices

- Full Duplex Ethernet Operation Allows Network Speed Self-test

- Expandable Local LAN Subsystem Memory Space up to 2 Megabytes

- Supports Multicast Addressing of Network Group Addresses Through Hashing

- Glueless Interface to DRAMs

- High-Performance 16-Bit CPU for Communications Protocol Processing

- Up to 8 Megabyte-per-Second High-Speed Bus Master DMA Interface

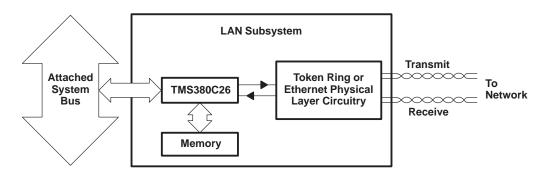

#### network commprocessor applications diagram

- Low-Cost Host-Slave I/O Interface Option

- Up to 32-Bit Host Address Bus

- Selectable Host System Bus Options

- 80x8x or 68xxx-Type Bus and Memory Organization

- 8- or 16-Bit Data Bus on 80x8x Buses

- Optional Parity Checking

- Dual-Port DMA and Direct I/O Transfers to Host Bus

- Specification for External Adapter-Bus Devices (SEADs) Supports External Hardware Interface for User-Defined External Logic

- Enhanced Address Copy Option (EACO) Interface Supports External Address Checking Logic for Bridging or External Custom Applications

- Support for Module High-Impedance In-Circuit Testing

- Built-in Real-Time Error Detection

- Bring-Up and Self-Test Diagnostics With Loopback

- Automatic Frame Buffer Management

- Slow-Clock Low-Power Mode

- Single 5-V Supply

- 1-µm CMOS Technology

- 250 mA Typical Latch-Up Immunity at 25°C

- ESD Protection Exceeds 2,000 V

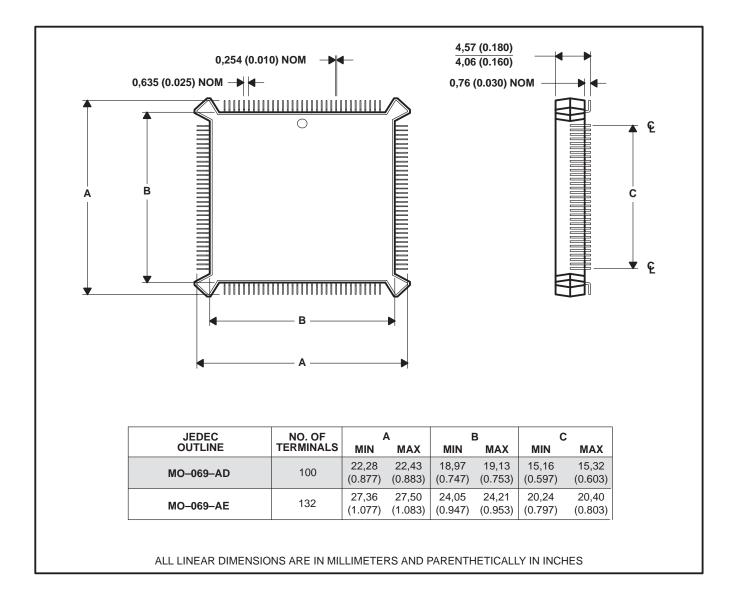

- 132-Pin JEDEC Plastic Quad Flat Package (PQ Suffix)

- Operating Temperature Range 0°C to 70 °C

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1993, Texas Instruments Incorporated

SPWS010A-APRIL 1992-REVISED MARCH 1993

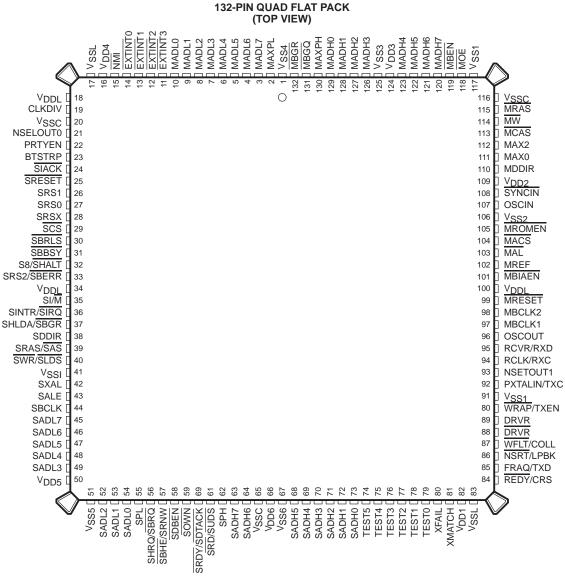

#### pinout

The pin assignments for TMS380C26 (132-pin quad flat-pack) are shown in Figure 1.

Figure 1. TMS380C26 Pinout

#### description

The TMS380C26 is a single-chip network communications processor (commprocessor) that supports token ring, or Ethernet Local Area Networks (LANs). Either token ring at data rates of 16 Mbps or 4 Mbps, or Ethernet at a data rate of 10 Mbps, can be selected. A flexible configuration scheme allows network type and speed to be configured by hardware or software. This allows the design of LAN subsystems which support both token ring and Ethernet networks, by electrically or physically switched network front-end circuits.

The TMS380C26 conforms to IEEE 802.5–1989 standards and has been verified to be completely IBM<sup>™</sup> Token-Ring compatible. By integrating the essential control building blocks needed on a LAN subsystem card into one device, the TMS380C26 can ensure that this IBM compatability is maintained in silicon.

The TMS380C26 conforms to ISO/IEC 8802–3 (ANSI/IEEE Std 802.3) CSMA/CD standards, and the Ethernet "Blue Book" standard.

The high degree of integration of the TMS380C26 makes it a virtual LAN subsystem on a single chip. Protocol handling, host system interfacing, memory interfacing, and communications processing are all provided through the TMS380C26. To complete LAN subsystem design, only the network interface hardware, local memory, and minimal additional components such as PALs and crystal oscillators need to be added.

The TMS380C26 provides a 32-bit system memory address reach with a high-speed bus-master DMA interface that supports rapid communications with the host system. In addition, the TMS380C26 supports direct I/O and a low-cost 8-bit pseudo-DMA interface that requires only a chip select to work directly on an 80x8x 8-bit slave I/O interface. Finally, selectable 80x8x or 68xxx-type host system bus and memory organization add to design flexibility.

The TMS380C26 supports addressing for up to two Megabytes of local memory. This expanded memory capacity can improve LAN subsystem performance by minimizing the frequency of host LAN subsystem communications by allowing larger blocks of information to be transferred at one time. The support of large local memory is important in applications that require large data transfers (such as graphics or data base transfers) and in heavily loaded networks where the extra memory can provide data buffers to store data until it can be processed by the host.

The proprietary CPU used in the TMS380C26 allows protocol software to be downloaded into RAM or stored in ROM in the local memory space. By moving protocols (such as LLC) to the LAN subsystem, overall system performance is increased. This is accomplished due to the the offloading of processing from the host system to the TMS380C26, which may also reduce LAN subsystem-to-host communications. As other protocol software is developed, greater differentiation of end products with enhanced system performance will be possible.

In addition, the TMS380C26 includes hardware counters that provide realtime error detection and automatic frame buffer management. These counters control system bus retries, burst size, and track host and LAN subsystem buffer status. Previously, these counters needed to be maintained in software. By integrating them into hardware, software overhead is removed and LAN subsystem performance is improved.

The TMS380C26 implements a TI-patented Enhanced Address Copy Option (EACO) interface. This interface supports external address checking devices, such as the TMS380SRA Source Routing Accelerator. The TMS380C26 has a 128-word external I/O space in its memory map to support external address-checker devices and other hardware extensions to the TMS380 architecture. Hardware designed in conformance with TI's Specification for External Adapter-bus Devices (SEADs) can map registers into this external I/O space and post interrupts to the TMS380C26.

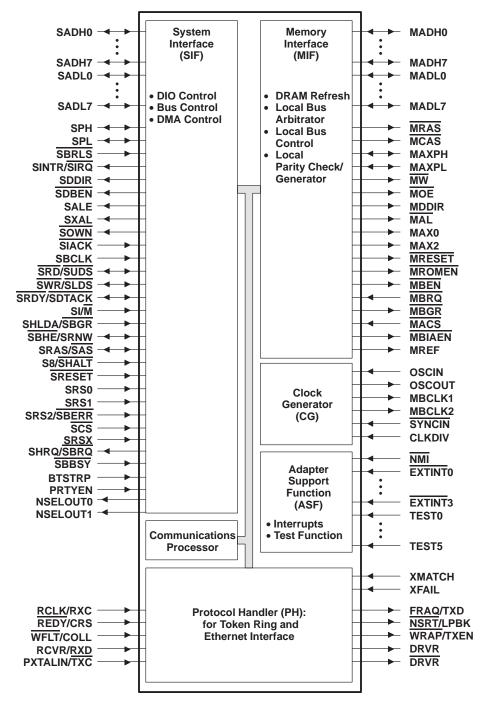

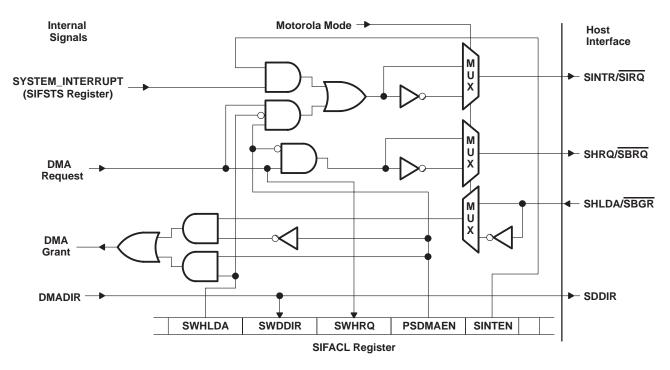

The major blocks of the TMS380C26 include the Communications Processor (CP), System Interface (SIF), Memory Interface (MIF), Protocol Handler (PH), Clock Generator (CG), and the Adapter Support Function (ASF) as shown in Figure 2.

The TMS380C26 is available in a 132-pin JEDEC plastic quad flat pack and is rated from 0°C to 70°C.

IBM is a registered trademark of International Business Machines Corporation.

#### SPWS010A-APRIL 1992-REVISED MARCH 1993

#### block diagram and signal descriptions

TMS380C26 has a bus interface to the host system, a bus interface to local memory, and an interface to the physical layer circuitry. As a rule of thumb in the pin nomenclature and descriptions that follow, pin names starting with the letter S attach to the host system bus and pin names starting with the letter M attach to the local memory bus. Active-low signals have names with overbars, e.g., SCS.

Figure 2. TMS380C26 COMMprocessor Block Diagram

SPWS010A-APRIL 1992-REVISED MARCH 1993

#### **Terminal Functions**

| PIN NAME                                                             | NO.                                           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------------|-----------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BTSTRP                                                               | 23                                            | IN  | Bootstrap. The value on this pin is loaded into the BOOT bit of the SIFACL register at reset (i.e., when the SRESET pin is asserted or the ARESET bit in the SIFACL register is set) to form a default value. This bit indicates whether chapters 0 and 31 of the memory map are RAM or ROM. If these chapters are RAM then the TMS380C26 is denied access to the local memory bus until the CPHALT bit in the SIFACL register is cleared.         H       =       Chapters 0 and 31 of local memory are RAM-based (see Note 1).         L       =       Chapters 0 and 31 of local memory are ROM-based. |  |  |

|                                                                      |                                               |     | Clock Divider Select. This pin must be pulled high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| CLKDIV                                                               | 19                                            | IN  | H = Indicates 64-MHz OSCIN (see Note 3).<br>L = Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| EXTINTO<br>EXTINT1<br>EXTINT2<br>EXTINT3                             | 14<br>13<br>12<br>11                          | IN  | Reserved; must be pulled high (see Note 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| MACS                                                                 | 104                                           | IN  | Reserved. Must be tied low (see Note 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

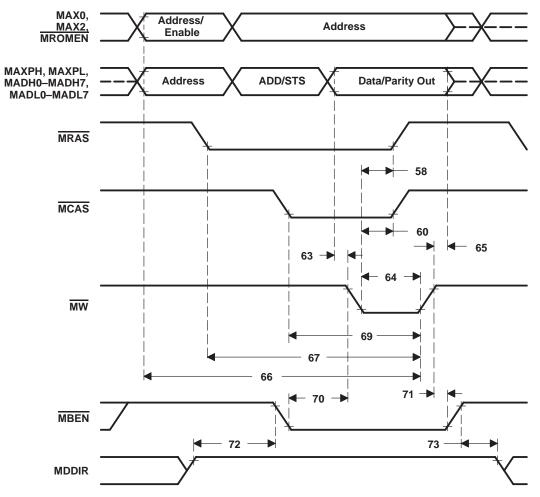

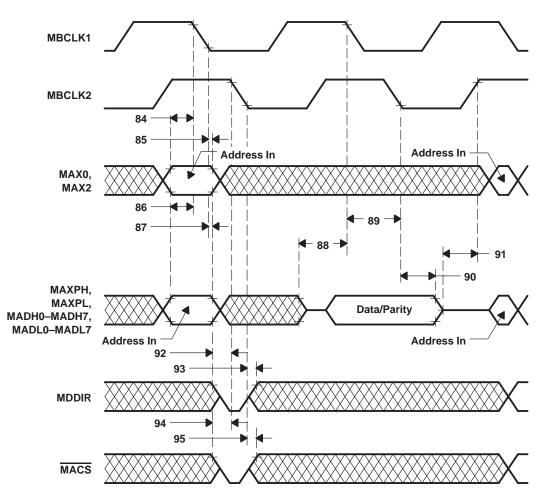

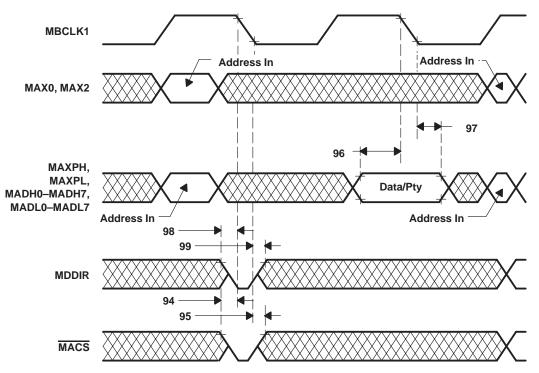

| MADH0<br>MADH1<br>MADH2<br>MADH3<br>MADH4<br>MADH5<br>MADH6<br>MADH7 | 129<br>128<br>127<br>126<br>123<br>122<br>121 | I/O | Local memory Address, Data and Status Bus – high byte. For the first quarter of the local memory cycle these bus lines carry address bits AX4 and A0 to A6; for the second quarter, they carry status bits; and for the third and fourth quarters, they carry data bits 0 to 7. The most significant bit is MADH0 and the least significant bit is MADH7.<br>Memory Cycle $\frac{10}{20} = \frac{20}{30} = \frac{40}{20}$ Signal                                                                                                                                                                          |  |  |

| MADH7                                                                | 120                                           |     | Signal AX4,A0–A6 Status D0–D7 D0–D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| MADL0<br>MADL1<br>MADL2<br>MADL3<br>MADL4<br>MADL5<br>MADL6<br>MADL7 | 10<br>9<br>7<br>6<br>5<br>4<br>3              | I/O | Local Memory Address, Data and Status Bus – low byte. For the first quarter of the local memory cycle, these bus lines carry address bits A7 to A14; for the second quarter, they carry address bits AX4 and A0 to A6; and for the third and fourth quarters, they carry data bits 8 to 15. The most significant bit is MADL0 and the least significant bit is MADL7.<br>Memory Cycle<br><u>1Q</u> <u>2Q</u> <u>3Q</u> <u>4Q</u><br>Signal A7–A14 AX4,A0–A6 D8–D15 D8–D15                                                                                                                                 |  |  |

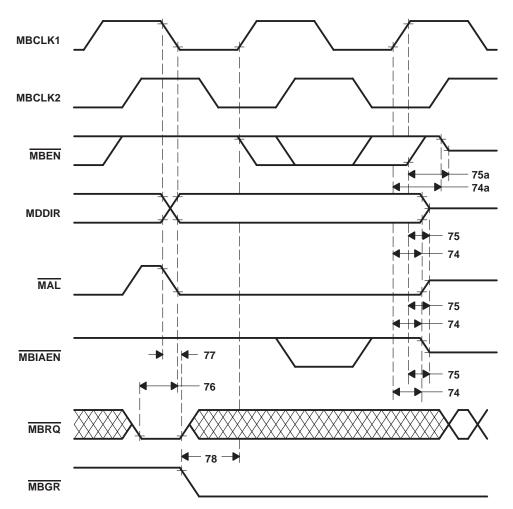

| MAL                                                                  | 103                                           | OUT | Memory Address Latch. This is a strobe signal for sampling the address at the start of the memory cycle; it is used by SRAMs and EPROMs. The full 20-bit word address is valid on MAX0, MAXPH, MAX2, MAXPL, MADH0-MADH7, and MADL0-MADL7. Three 8-bit transparent latches can therefore be used to retain a 20-bit static address throughout the cycle.<br>Rising edge = No signal latching.<br>Falling edge = Allows the above address signals to be latched.                                                                                                                                            |  |  |

| MAX0                                                                 | 111                                           | OUT | Local Memory Extended Address Bit. This signal drives AX0 at ROW address time and it drives A12<br>at COL address and DATA time for all cycles. This signal can be latched by MRAS. Driving A12 eases<br>interfacing to a BIA ROM.<br>Memory Cycle<br>1Q 2Q 3Q 4Q<br>Signal AX0 A12 A12 A12                                                                                                                                                                                                                                                                                                               |  |  |

| MAX2                                                                 | 112                                           | OUT | Local Memory Extended Address Bit. This signal drives AX2 at ROW address time, which can be latched by MRAS, and A14 at COL address, and DATA time for all cycles. Driving A14 eases interfacing to a BIA ROM.         Memory Cycle         1Q       2Q       3Q       4Q         Signal       AX2       A14       A14       A14                                                                                                                                                                                                                                                                          |  |  |

NOTES: 1. Pin has an internal pullup device to maintain a high voltage level when left unconnected (no etch or loads).

2. Pin should be connected to ground. 3. Pin should be tied to  $V_{CC}$  with a 4.7-k $\Omega$  pullup resistor. 4. Each pin must be individually tied to  $V_{CC}$  with a 1.0-k $\Omega$  pullup resistor.

SPWS010A-APRIL 1992-REVISED MARCH 1993

| PIN NAME         | NO.      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| МАХРН            | 130      | I/O | Local Memory Extended Address and Parity High Byte. For the first quarter of a memory cycle this signal carries the extended address bit (AX1); for the second quarter of a memory cycle this signal carries the extended address bit (AX0); and for the last half of the memory cyle this signal carries the parity bit for the high data byte.<br>Memory Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  |          |     | 1Q2Q3Q4QSignalAX1AX0ParityParity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MAXPL            | 2        | I/O | Local Memory Extended Address and Parity Low Byte. For the first quarter of a memory cycle this signal carries the extended address bit (AX3), for the second quarter of a memory cycle this signal carries extended address bit (AX2); and for the last half of the memory cycle this signal carries the parity bit for the low data byte.<br>Memory Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |          |     | <u>1Q 2Q 3Q 4Q</u><br>Signal AX3 AX2 Parity Parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

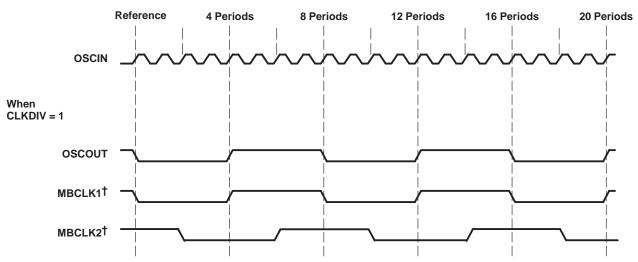

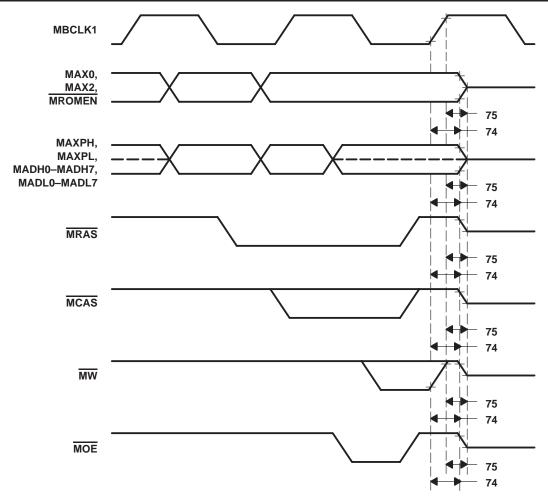

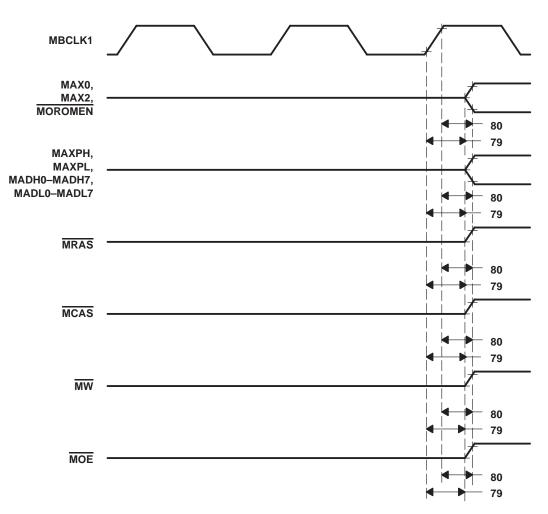

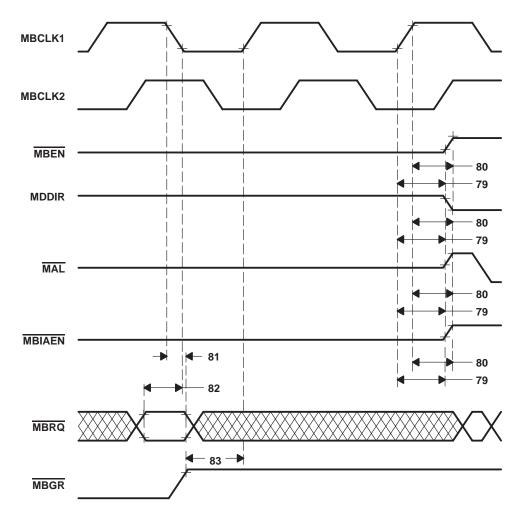

| MBCLK1<br>MBCLK2 | 97<br>98 | OUT | Local Bus Clock1 and local Bus Clock 2. These signals are referenced for all local bus transfers.<br>MBCLK2 lags MBCLK1 by a quarter of a cycle. These clocks operate at 8 MHz for a 64-MHz OSCIN<br>and 6 MHz for a 48-MHz OSCIN, which is twice the memory cycle rate. The MBCLK signals are<br>always a divide-by-8 of the OSCIN frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MBEN             | 119      | OUT | <ul> <li>Buffer Enable. This signal enables the bidirectional buffer outputs on the MADH, MAXPH, MAXPL, and MADL buses during the data phase. This signal is used in conjunction with MDDIR which selects the buffer output direction.</li> <li>H = Buffer output disabled.</li> <li>L = Buffer output enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MBGR             | 132      | OUT | Reserved. Must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  |          |     | Burned-In Address Enable. This is an output signal used to provide an output enable for the ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MBIAEN           | 101      | OUT | <ul> <li>containing the adapter's Burned-In Address (BIA).</li> <li>H = This signal is driven high for any WRITE accesses to the addresses between &gt;00.0000 and &gt;00.000F, or any accesses (Read/Write) to any other address.</li> <li>L = This signal is driven low for any READ from addresses between &gt;00.0000 and &gt;00.000F.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MBRQ             | 131      | IN  | Reserved. Must be pulled high (see Note 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

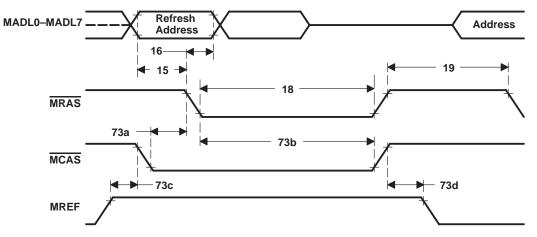

| MCAS             | 113      | OUT | <ul> <li>Column Address Strobe for DRAMs. The column address is valid for the 3/16 of the memory cycle following the row address portion of the cycle. This signal is driven low every memory cycle while the column address is valid on MADL0-MADL7, MAXPH, and MAXPL, except when one of the following conditions occurs:</li> <li>1) When the address accessed is in the BIA ROM (&gt;00.0000 - &gt;00.000F).</li> <li>2) When the address accessed is in the EPROM memory map (i.e., when the BOOT bit in the SIFACL register is zero and an access is made between &gt;00.0010 - &gt;00.FFFF) or &gt;1F.0000 - &gt;1F.FFFF).</li> <li>3) When the cycle is a refresh cycle, in which case MCAS is driven at the start of the cycle before MRAS (for DRAMs that have CAS-before-RAS refresh). For DRAMs that do not support CAS-before-RAS refresh, it may be necessary to disable MCAS with MREF during the refresh cycle.</li> </ul> |

| MDDIR            | 110      | OUT | <ul> <li>Data Direction. This signal is used as a direction control for bidirectional bus drivers. The signal becomes valid before MBEN active.</li> <li>H = TMS380C26 memory bus write.</li> <li>L = TMS380C26 memory bus read.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**Terminal Functions (continued)**

NOTE 4: Each pin must be individually tied to  $V_{CC}$  with a 1.0-k $\Omega$  pullup resistor.

SPWS010A-APRIL 1992-REVISED MARCH 1993

| PIN NAME | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MOE      | 118 | OUT | Memory Output Enable. This signal is used to enable the outputs of the DRAM memory during a read cycle. This signal is high for EPROM or BIA ROM read cycles.<br>H = Disable DRAM outputs.<br>L = Enable DRAM outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| MRAS     | 115 | OUT | Row Address Strobe for DRAMs. The row address lasts for the first 5/16 of the memory cycle. This signal is driven low every memory cycle while the row address is valid on MADL0-MADL7, MAXPH, and MAXPL for both RAM and ROM cycles. It is also driven low during refresh cycles when the refresh address is valid on MADL0-MADL7.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| MREF     | 102 | OUT | <ul> <li>DRAM Refresh Cycle in Progress. This signal is used to indicate that a DRAM refresh cycle is occurring. It is also used for disabling MCAS to all DRAMs that do not use a CAS before-RAS refresh.</li> <li>H = DRAM refresh cycle in process.</li> <li>L = Not a DRAM refresh cycle.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| MRESET   | 99  | OUT | Memory Bus Reset. This is a reset signal generated when either the ARESET bit in the SIFACL register is set or the SRESET pin is asserted. This signal is used for resetting external local bus glue logic.<br>H = External logic not reset.<br>L = External logic reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| MROMEN   | 105 | OUT | ROM Enable. During the first 5/16 of the memory cycle, this signal is used to provide a chip select<br>for ROMs when the BOOT bit of the SIFACL register is zero (i.e., when code is resident in ROM, not<br>RAM). It can be latched by MAL. It goes low for any read from addresses >00.0010 - >00.FFFF or<br>>1F.0000 - >1F.FFFF when the Boot bit in the SIFACL register is zero. It stays high for writes to these<br>addresses, accesses of other addresses, or accesses of any address when the BOOT bit is one.<br>During the final three quarters of the memory cycle, it outputs the A13 address signal for interfacing<br>to a BIA ROM. This means MBIAEN, MAX0, ROMEN, and MAX2 together form a glueless interface<br>for the BIA ROM. |  |  |

| MW       | 114 | OUT | L = ROM enabled.         Local Memory Write. This signal is used to specify a write cycle on the local memory bus. The data on the MADH0-MADH7 and MADL0-MADL7 buses is valid while MW is low. DRAMs latch data on the falling edge MW, while SRAMs latch data on the rising edge of MW.         H = Not a local memory write cycle.         L = Local memory write cycle.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| NMI      | 15  | IN  | Non-Maskable Interrupt Request. This pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| OSCIN    | 107 | IN  | External Oscillator Input. This line provides the clock frequency to the TMS380C26 for a 4-MHz internal bus. OSCIN should be 64 a MHz signal (see Note 5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| OSCOUT   | 96  | OUT | Oscillator Output. With OSCIN at 64 MHz and CLKDIV pulled high, this pin provides an 8 MHz output which can be used by TMS3054 for 4 Mbps operation without the need for an additional crystal.         CLKDIV       OSCOUT         L       Reserved         H       OSCIN/8         (if OSCIN = 64 MHz, then OSCOUT = 8 MHz).                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

**Terminal Functions (continued)**

NOTE 5: Pin has an expanded input voltage specification.

SPWS010A-APRIL 1992-REVISED MARCH 1993

| PIN NAME             | NO. | I/O              |                                                           | DESCRIF                                                               | PTION                                              |

|----------------------|-----|------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|

| PRTYEN               | 22  | IN               |                                                           | erted or the ARESET<br>checking for the loca<br>us checked for parity | (see Note 1).                                      |

|                      |     |                  | ,                                                         |                                                                       | nals are controlled by the host through the        |

|                      | 21  |                  | corresponding bits of the SIF/<br>the TMS380C26 is reset. | ACTL register. The val                                                | ue of these bits/signals can only be changed while |

| NSELOUT0<br>NSELOUT1 |     | 21 OUT<br>93 OUT | NSELOUT0                                                  | NSELOUT1                                                              | Description                                        |

| NOLLOOTT             | 00  | 001              | L                                                         | L                                                                     | Reserved                                           |

|                      |     |                  | L                                                         | Н                                                                     | 16 Mbps token ring                                 |

|                      |     |                  | Н                                                         | L                                                                     | Ethernet (802.3/Blue Book)                         |

|                      |     |                  | Н                                                         | Н                                                                     | 4 Mbps token ring                                  |

### **Terminal Functions (continued)**

SPWS010A-APRIL 1992-REVISED MARCH 1993

### **Terminal Functions (continued)**

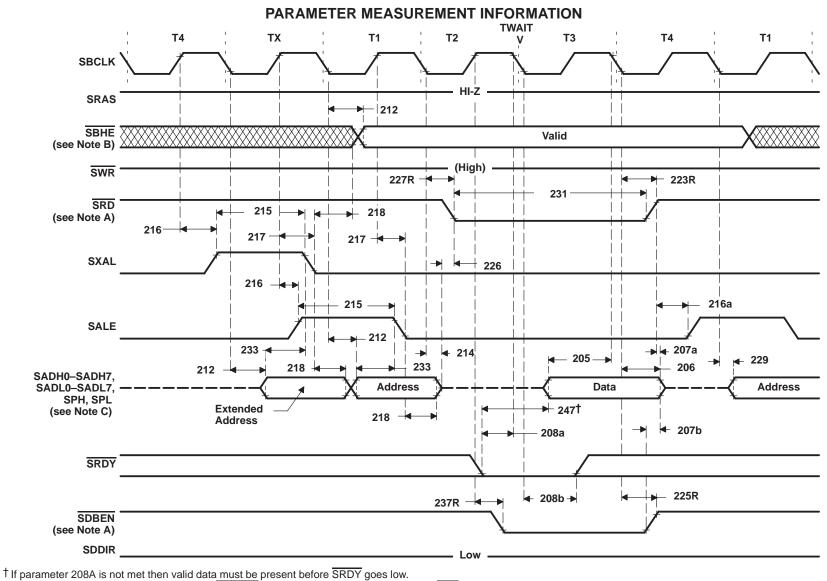

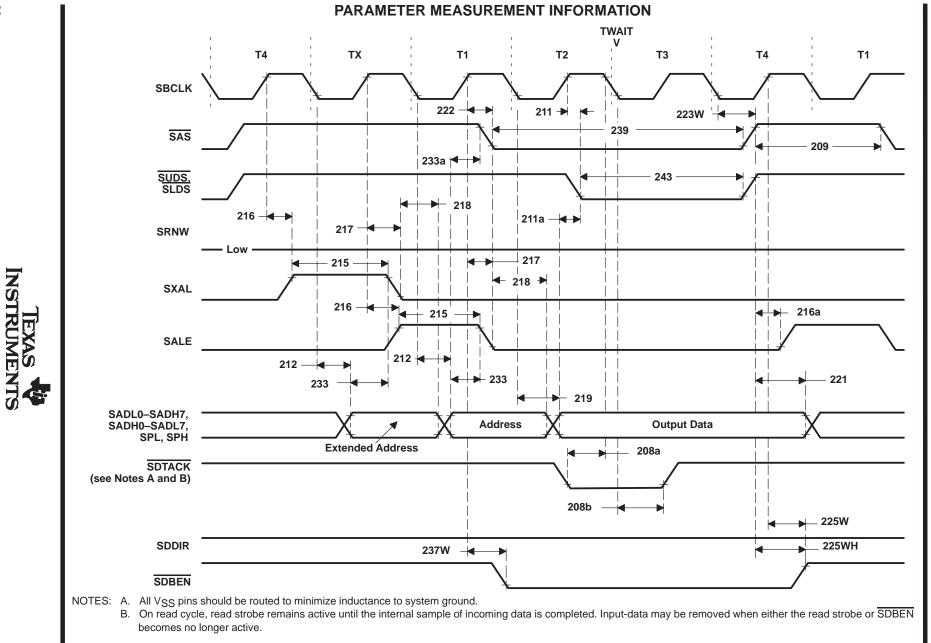

#### System Interface – Intel Mode (SI/ $\overline{M}$ = H)

| PIN NAME                                                             | NO.                                          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------|----------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SADH0<br>SADH1<br>SADH2<br>SADH3<br>SADH4<br>SADH5<br>SADH6<br>SADH7 | 73<br>72<br>71<br>70<br>69<br>68<br>64<br>63 | I/O | System Address/Data Bus—high byte (see Note 1).These lines make up the most significant byte of each address word (32-bit address bus) and data word (16-bit data bus). The most significant bit is SADH0, and the least significant bit is SADH7.<br>Address Multiplexing <sup>†</sup> : Bits 31 – 24 and bits 15 – 8.<br>Data Multiplexing <sup>†</sup> : Bits 15 – 8.                                                                                                                                                        |

| SADL0<br>SADL1<br>SADL2<br>SADL3<br>SADL4<br>SADL5<br>SADL6<br>SADL7 | 54<br>53<br>52<br>49<br>48<br>47<br>46<br>45 | I/O | System Address/Data Bus—low byte (see Note 1). These lines make up the least significant byte of each address word (32-bit address bus) and data word (16-bit data bus). The most significant bit is SADL0, and the least significant bit is SADL7.<br>Address Multiplexing <sup>†</sup> : Bits 23 – 16 and bits 7 – 0.<br>Data Multiplexing <sup>†</sup> : Bits 7 – 0.                                                                                                                                                         |

| SALE                                                                 | 43                                           | OUT | System Address Latch Enable. This is the enable pulse used to externally latch the 16 LSBs of the address from the SADH0 – SADH7 and SADL0 – SADL7 buses at the start of the DMA cycle. Systems that implement address parity can also externally latch the parity bits (SPH and SPL) for the latched address.                                                                                                                                                                                                                  |

| SBBSY                                                                | 31                                           | IN  | System Bus Busy. The TMS380C26 samples the value on this pin during arbitration. The sample has<br>one of (2) two values (see Note 1):<br>H = Not busy. The TMS380C26 may become Bus Master if the grant condition is met.<br>L = Busy. The TMS380C26 cannot become Bus Master.                                                                                                                                                                                                                                                 |

| SBCLK                                                                | 44                                           | IN  | System Bus Clock. The TMS380C26 requires the external clock to synchronize its bus timings for all DMA transfers.                                                                                                                                                                                                                                                                                                                                                                                                               |

| SBHE/SRNW                                                            | 57                                           | I/O | System Byte High Enable. This pin is a three-state output that is driven during DMA and an input at all other times.<br>H = System Byte High not enabled (see Note 1).<br>L = System Byte High enabled.                                                                                                                                                                                                                                                                                                                         |

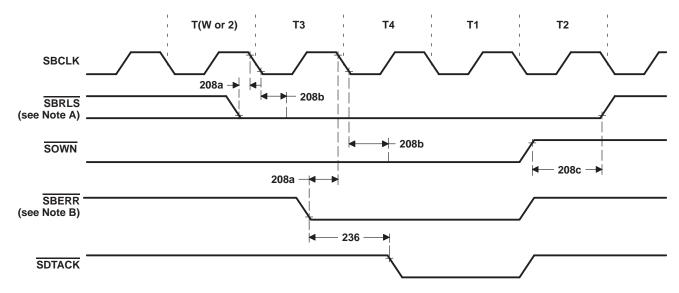

| SBRLS                                                                | 30                                           | IN  | <ul> <li>System Bus Release. This pin indicates to the TMS380C26 that a higher-priority device requires the system bus. The value on this pin is ignored when the TMS380C26 is <i>NOT</i> perfoming DMA. This signal is internally synchronized to SBCLK.</li> <li>H = The TMS380C26 can hold onto the system bus (see Note 1).</li> <li>L = The TMS380C26 should release the system bus upon completion of current DMA cycle. If the DMA transfer is not yet complete, the SIF will rearbitrate for the system bus.</li> </ul> |

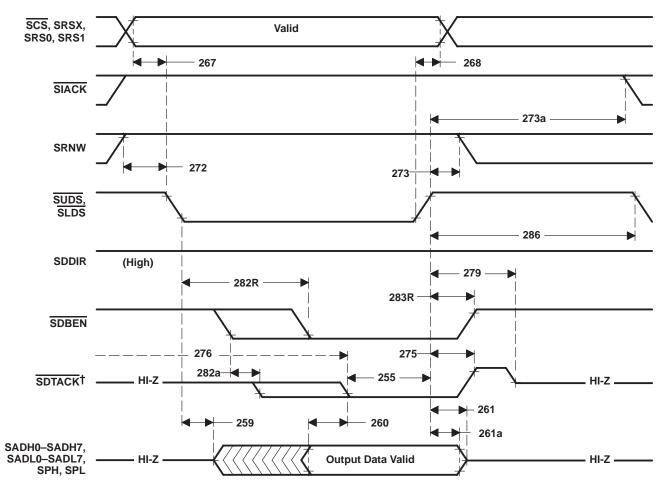

| SCS                                                                  | 29                                           | IN  | System Chip Select. Activates the system interface of the TMS380C26 for a DIO read or write.<br>H = Not selected (see Note 1).<br>L = Selected.                                                                                                                                                                                                                                                                                                                                                                                 |

| SDBEN                                                                | 58                                           | OUT | <ul> <li>System Data Bus Enable. This output signals to the external data buffers to begin driving data. This output is activated during both DIO and DMA.</li> <li>H = Keep external data buffers in high-impedance state.</li> <li>L = Cause external data buffers to begin driving data.</li> </ul>                                                                                                                                                                                                                          |

<sup>†</sup> Typical bit ordering for Intel and Motorola processor buses.

SPWS010A-APRIL 1992-REVISED MARCH 1993

### **Terminal Functions (continued)**

# System Interface – Intel Mode (SI/ $\overline{M}$ = H)

| PIN NAME           | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDDIR              | 38  | OUT | System Data Direction. This output provides to the external data buffers a signal indicating the direction in which the data is moving. During DIO writes and DMA reads, SDDIR is low (data direction input to the TMS380C26). During DIO reads and DMA writes, SDDIR is high (data direction output from the TMS380C26). When the system interface is <i>NOT</i> involved in a DIO or DMA operation, then SDDIR is high by default. |

|                    |     |     | DATASDDIRDIRECTIONDIODMAHoutputreadwriteLinputwriteread                                                                                                                                                                                                                                                                                                                                                                              |

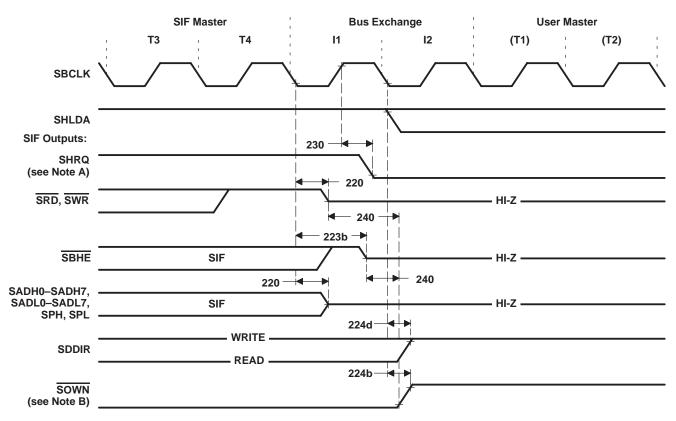

| SHLDA/SBGR         | 37  | IN  | System Hold Acknowledge. This pin indicates that the system DMA hold request has been acknowledged. It is internally synchronized to SBCLK (see Note 1).<br>H = Hold request acknowledged.<br>L = Hold request not acknowledged.                                                                                                                                                                                                     |

| SHRQ/SBRQ          | 56  | OUT | System Hold Request. This pin is used to request control of the system bus in preparation for a DMA transfer. This pin is internally synchronized to SBCLK.<br>H = System bus requested.<br>L = System bus not requested.                                                                                                                                                                                                            |

| SIACK              | 24  | IN  | System Interrupt Acknowledge. This signal is from the host processor to acknowledge the interrupt<br>request from the TMS380C26.<br>H = System interrupt not acknowledged (see Note 1).<br>L = System interrupt acknowledged: the TMS380C26 places its interrupt vector onto the system<br>bus.                                                                                                                                      |

| SI/₩               | 35  | IN  | <ul> <li>System Intel/Motorola Mode Select. The value on this pin specifies the system interface mode.</li> <li>H = Intel-compatible interface mode selected. Intel interface can be 8-bit or 16-bit mode (see S8/SHALT pin description and Note 1.)</li> <li>L = Motorola-compatible interface mode selected.</li> </ul>                                                                                                            |

| <b>SINTR</b> /SIRQ | 36  | OUT | System Interrupt Request. TMS380C26 activates this output to signal an interrupt request to the host processor.<br>H = Interrupt request by TMS380C26.<br>L = No interrupt request.                                                                                                                                                                                                                                                  |

| SOWN               | 59  | OUT | System Bus Owned. This signal indicates to external devices that TMS380C26 has control of the system bus. This signal drives the enable signal of the bus transceiver chips, which drive the address and bus control signals.<br>H = TMS380C26 does not have control of the system bus.                                                                                                                                              |

| SPH                | 62  | I/O | L = TMS380C26 has control of the system bus.<br>System Parity High. The optional odd-parity bit for each address or data byte transmitted over SADH0-SADH7 (see Note 1).                                                                                                                                                                                                                                                             |

| SPL                | 55  | I/O | System Parity Low. The optional odd-parity bit for each address or data byte transmitted over SADL0-SADL7 (see Note 1).                                                                                                                                                                                                                                                                                                              |

SPWS010A-APRIL 1992-REVISED MARCH 1993

### **Terminal Functions (continued)**

### System Interface – Intel Mode (SI/M = H)

| PIN NAME             | NO.            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRAS/SAS             | 39             | I/O | System Memory Address Strobe (see Note 3). This pin used to latch the SCS, SRSX – SRS2 register input signals. In a minimum-chip system, SRAS is tied to the SALE output of the System Bus. The latching capability can be defeated since the internal latch for these inputs remains transparent as long as SRAS remains high. This permits SRAS to be pulled high and the signals at the SCS, SRSX – SRS2, and SBHE to be applied independently of the SALE strobe from the system bus. During DMA this pin remains an input. |

|                      |                |     | High= transparent modeLow= Holds latched values of SCS, SRSX–SRS2, and SBHEFalling edge= latches SCS, SRSX – SRS2, and SBHE                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |                |     | System Read Strobe (see Note 3). Active-low strobe indicating that a read cycle is performed on the system bus. This pin is an input during DIO and an output during DMA.                                                                                                                                                                                                                                                                                                                                                       |

| SRD/SUDS             | 61             | I/O | <ul> <li>H = Read cyle is not occurring.</li> <li>L = If DMA: host provides data to system bus.</li> <li>If DIO: SIF provides data to system bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                    |

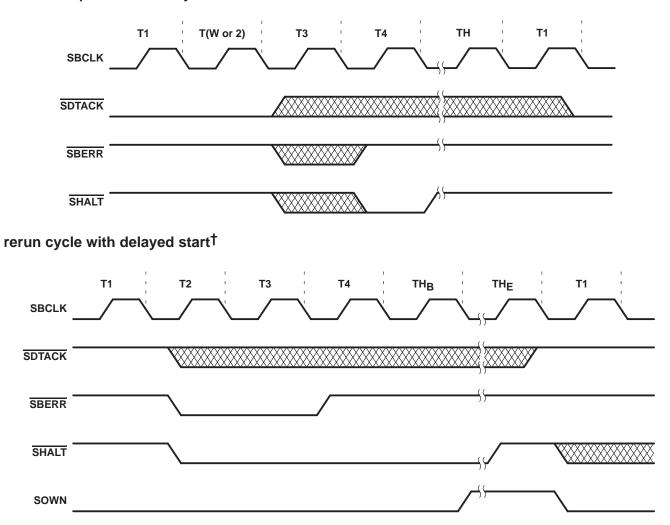

| SRDY/SDTACK          | 60             | I/O | System Bus Ready (see Note 3). The purpose of this signal is to indicate to the bus master that a data transfer is complete. This signal is asynchonous, but during DMA and pseudo-DMA cycles it is internally synchronized to SBCLK. During DMA cycles, it must be asserted before the falling edge of SBCLK in state T2 in order to prevent a wait state. This signal is an output when the TMS380C26 is selected for DIO, and an input otherwise.                                                                            |

|                      |                |     | <ul> <li>H = System bus NOT ready.</li> <li>L = Data transfer is complete; system bus is ready.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SRESET               | 25             | IN  | System Reset. This input signal is activated to place the TMS380C26 into a known initial state.<br>Hardware reset will put most of the TMS380C26 output pins into a high-impedance state and place<br>all blocks into the reset state. DMA bus width selection is latched on the rising edge of SRESET.<br>H = No system reset.                                                                                                                                                                                                 |

|                      |                |     | L = System reset.<br>Rising edge = Latch bus width for DMA operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SRSX<br>SRS0<br>SRS1 | 28<br>27<br>26 | IN  | System Register Select. These inputs select the word or byte to be transferred during a system DIO access. The most significant bit is SRSX and the least significant bit is SRS2 (see Note 1).                                                                                                                                                                                                                                                                                                                                 |

| SRS2/SBERR           | 33             |     | MSb         LSb           Registered selected         =         SRSX         SRS0         SRS1         SRS2/SBERR                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      |                |     | System Write Strobe (see Note 3). This pin serves as an active-low write strobe. This pin is an input during DIO and an output during DMA.                                                                                                                                                                                                                                                                                                                                                                                      |

| SWR/SLDS             | 40             | I/O | <ul> <li>H = Write cycle is not occurring.</li> <li>L = If DMA: data to be drivien from SIF to host bus.</li> <li>If DIO: on the rising edge, the data is latched and written to the selected register.</li> </ul>                                                                                                                                                                                                                                                                                                              |

| SXAL                 | 42             | OUT | System Extended Address Latch. This output provides the enable pulse used to externally latch the most significant 16 bits of the 32-bit system address during DMA. SXAL is activated prior to the first cycle of each block DMA transfer, and thereafter as necessary (whenever an increment of the DMA address counter causes a carry-out of the lower 16 bits). Systems that implement parity on addresses can use SXAL to externally latch the parity bits (available on SPL and SPH) for the DMA address extension.        |

NOTES: 1. Pin has an internal pullup device to maintain a high voltage level when left unconnected (no etch or loads).

3. Pin should be tied to V<sub>CC</sub> with a 4.7-k $\Omega$  pullup resistor.

SPWS010A-APRIL 1992-REVISED MARCH 1993

### **Terminal Functions (continued)**

### System Interface – Intel Mode (SI/ $\overline{M}$ = H)

| PIN NAME | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNCIN   | 108 | IN  | Reserved. This signal must be left unconnected (see Note 1).                                                                                                                                                                                                                                                                       |

| S8/SHALT | 32  | IN  | System 8/16-bit bus select. This pin selects the bus width used for communications through the system interface. On the rising edge of SRESET, the TMS380C26 latches the DMA bus width; otherwise the value on this pin dynamically selects the DIO bus width.<br>H = Selects 8-bit mode (see Note 1).<br>L = Selects 16-bit mode. |

SPWS010A-APRIL 1992-REVISED MARCH 1993

### **Terminal Functions (continued)**

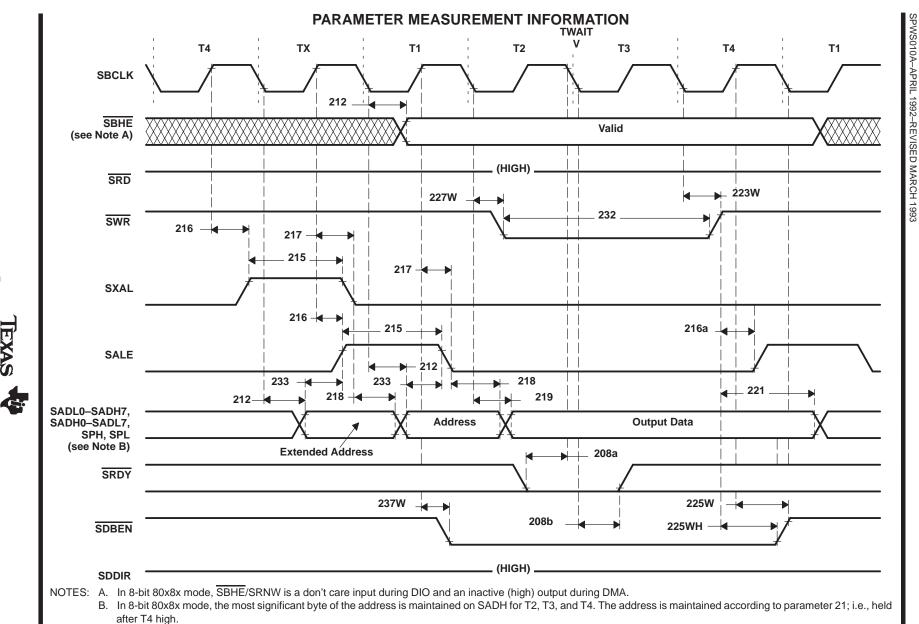

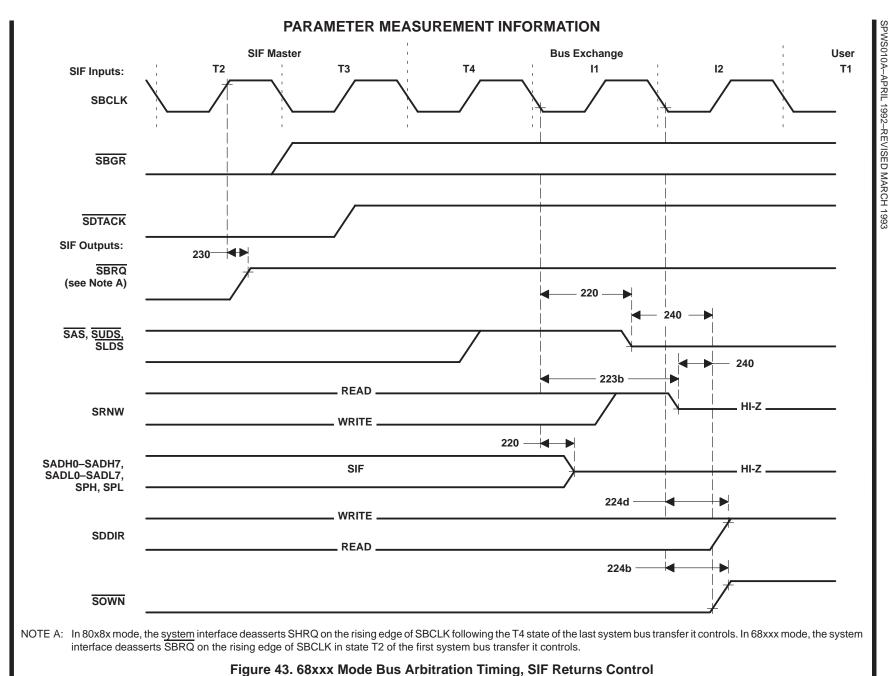

# System Interface – Motorola Mode (SI $\overline{M}$ = L)

| PIN NAME                                                             | NO.                                          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------|----------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SADH0<br>SADH1<br>SADH2<br>SADH3<br>SADH4<br>SADH5<br>SADH6<br>SADH7 | 73<br>72<br>71<br>70<br>69<br>68<br>64<br>63 | I/O | System Address/Data Bus—high byte (see Note 1).These lines make up the most significant byte of each address word (32-bit address bus) and data word (16-bit data bus). The most significant bit is SADH0, and the least significant bit is SADH7.<br>Address Multiplexing <sup>†</sup> : Bits 31 – 24 and bits 15 – 8.<br>Data Multiplexing <sup>†</sup> : Bits 15 – 8.                                                                                                                                                        |

| SADL0<br>SADL1<br>SADL2<br>SADL3<br>SADL4<br>SADL5<br>SADL6<br>SADL7 | 54<br>53<br>52<br>49<br>48<br>47<br>46<br>45 | I/O | System Address/Data Bus—low byte (see Note 1). These lines make up the least significant byte of each address word (32-bit address bus) and data word (16-bit data bus). The most significant bit is SADL0, and the least significant bit is SADL7.<br>Address Multiplexing <sup>†</sup> : Bits 23 – 16 and bits 7 – 0.<br>Data Multiplexing <sup>†</sup> : Bits 7 – 0.                                                                                                                                                         |

| SALE                                                                 | 43                                           | OUT | System Address Latch Enable. This is the enable pulse used to externally latch the 16 LSBs of the address from the SADH0 – SADH7 and SADL0 – SADL7 buses at the start of the DMA cycle. Systems that implement address parity can also externally latch the parity bits (SPH and SPL) for the latched address.                                                                                                                                                                                                                  |

| SBBSY                                                                | 31                                           | IN  | System Bus Busy. The TMS380C26 samples the value on this pin during arbitration. The sample has<br>one of (2) two values (see Note 1):<br>H = Not busy. The TMS380C26 may become Bus Master if the grant condition is met.<br>L = Busy. The TMS380C26 cannot become Bus Master.                                                                                                                                                                                                                                                 |

| SBCLK                                                                | 44                                           | IN  | System Bus Clock. The TMS380C26 requires the external clock to synchronize its bus timings for<br>all DMA transfers.                                                                                                                                                                                                                                                                                                                                                                                                            |

| SBHE/SRNW                                                            | 57                                           | I/O | System Read Not Write. This pin serves as a control signal to indicate a read or write cycle.<br>H = Read Cycle (see Note 1).<br>L = Write Cycle                                                                                                                                                                                                                                                                                                                                                                                |

| SBRLS                                                                | 30                                           | IN  | <ul> <li>System Bus Release. This pin indicates to the TMS380C26 that a higher-priority device requires the system bus. The value on this pin is ignored when the TMS380C26 is <i>NOT</i> perfoming DMA. This signal is internally synchronized to SBCLK.</li> <li>H = The TMS380C26 can hold onto the system bus (see Note 1).</li> <li>L = The TMS380C26 should release the system bus upon completion of current DMA cycle. If the DMA transfer is not yet complete, the SIF will rearbitrate for the system bus.</li> </ul> |

| SCS                                                                  | 29                                           | IN  | System Chip Select. Activates the system interface of TMS380C26 for a DIO read or write.<br>H = Not selected (see Note 1).<br>L = Selected.                                                                                                                                                                                                                                                                                                                                                                                     |

| SDBEN                                                                | 58                                           | OUT | <ul> <li>System Data Bus Enable. This output signals to the external data buffers to begin driving data. This output is activated during both DIO and DMA.</li> <li>H = Keep external data buffers in high-impedance state.</li> <li>L = Cause external data buffers to begin driving data.</li> </ul>                                                                                                                                                                                                                          |

<sup>†</sup> Typical bit ordering for Intel and Motorola processor buses.

SPWS010A-APRIL 1992-REVISED MARCH 1993

### **Terminal Functions (continued)**

# System Interface – Motorola Mode (SI/ $\overline{M}$ = L)

| PIN NAME                | NO.      | I/O  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDDIR                   | 38       | OUT  | System Data Direction. This output provides to the external data buffers a signal indicating the direction in which the data is moving. During DIO writes and DMA reads, SDDIR is low (data direction input to the TMS380C26). During DIO reads and DMA writes, SDDIR is high (data direction output from the TMS380C26). When the system interface is NOT involved in a DIO or DMA operation, then SDDIR is high by default.         DATA         SDDIR       DIRECTION       DIO       DMA         H       output       read       write |

|                         |          |      | L input write read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SHLDA/ <b>SBGR</b>      | 37       | IN   | System Bus Grant. This pin serves as an active-low bus grant, as defined in the standard 68000 interface, and is internally synchronized to SBCLK (see Note 1).                                                                                                                                                                                                                                                                                                                                                                            |

|                         |          |      | H = System bus not granted,<br>L = System bus granted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SHRQ/ <mark>SBRQ</mark> | 56       | OUT  | System Bus Request. This pin is used to request control of the system bus in preparation for a DMA transfer. This pin is internally synchronized to SBCLK.<br>H = System bus not requested.<br>L = System bus requested.                                                                                                                                                                                                                                                                                                                   |

|                         |          |      | System Interrupt Acknowledge. This signal is from the host processor to acknowledge the interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         |          |      | request from the TMS380C26.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SIACK                   | 24       | i IN | <ul> <li>H = System interrupt not acknowledged (see Note 1).</li> <li>L = System interrupt acknowledged: the TMS380C26 places its interrupt vector onto the system bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

|                         | -        |      | System Intel/Motorola Mode Select. The value on this pin specifies the system interface mode.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

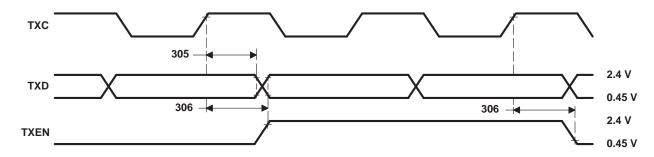

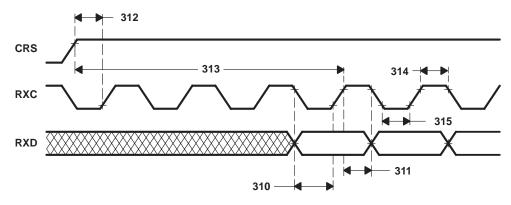

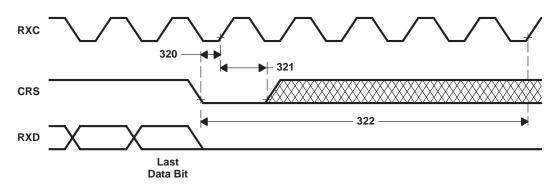

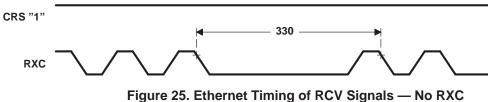

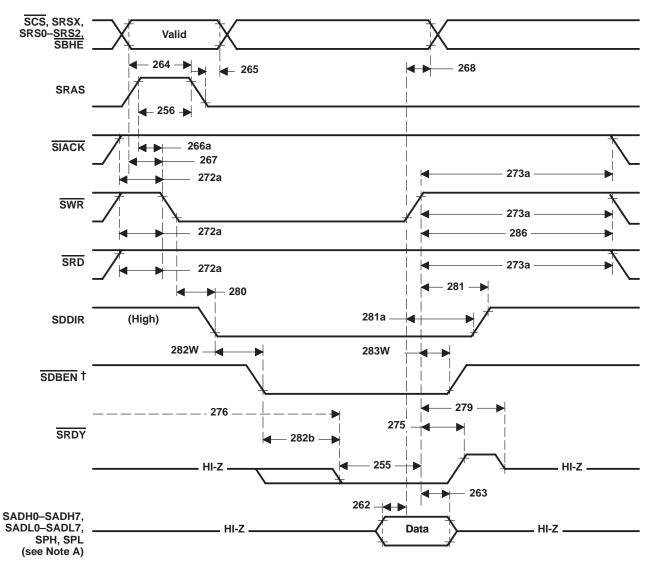

| SI/M                    | 35       | IN   | <ul> <li>H = Intel-compatible interface mode selected.</li> <li>L = Motorola-compatible interface mode selected. Motorola interface mode is always 16 bits.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |