## National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

## LM4953 Boomer® Audio Power Amplifier Series

# Ground-Referenced, Ultra Low Noise, Ceramic Speaker Driver

#### **General Description**

The LM4953 is an audio power amplifier designed for driving Ceramic Speaker in portable applications. When powered by a 3.6V supply, it is capable of forcing 12.6Vpp across a  $2\mu\text{F}+30\Omega$  bridge-tied-load (BTL) with less than 1% THD+N.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM4953 does not require bootstrap capacitors, or snubber circuits. Therefore it is ideally suited for display applications requiring high power and minimal size.

The LM4953 features a low-power consumption shutdown mode. Additionally, the LM4953 features an internal thermal shutdown protection mechanism.

The LM4953 contains advanced pop & click circuitry that eliminates noises which would otherwise occur during turn-on and turn-off transitions.

The LM4953 is unity-gain stable and can be configured by external gain-setting resistors.

#### **Key Specifications**

- Quiescent Power Supply Current (V<sub>dd</sub> = 3V) 7mA(typ)

- BTL Voltage Swing

$(2\mu F + 30\Omega \text{ load}, 1\% \text{ THD+N}, V_{dd} = 3.6V)$  12.6V<sub>pp</sub> (typ)

■ Shutdown Current

1µA (max)

#### **Features**

- Pop & click circuitry eliminates noise during turn-on and turn-off transitions

- Low, 1µA (max) shutdown current

- Low, 7mA (typ) quiescent current

- 12.6Vpp mono BTL output, load =  $2\mu$ F+  $30\Omega$

- Thermal shutdown

- Unity-gain stable

- External gain configuration capability

### **Applications**

- Cellphone

- PDA

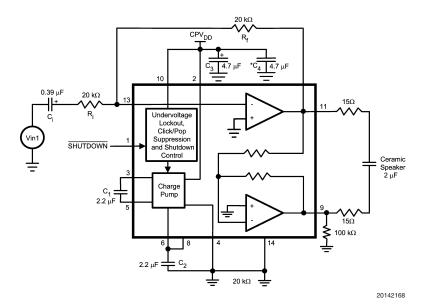

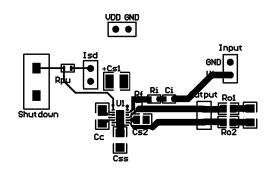

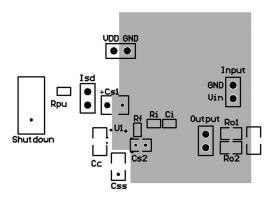

## **Typical Application**

FIGURE 1. Typical Application Circuit

Boomer® is a registered trademark of National Semiconductor Corporation.

## **Connection Diagram**

Top View Order Number LM4953SD See NS Package Number SDA14A

## **Pin Descriptions**

| Pin | Name                | Function                                         |  |

|-----|---------------------|--------------------------------------------------|--|

| 1   | SD                  | Active Low Shutdown                              |  |

| 2   | CP <sub>VDD</sub>   | Charge Pump Power Supply                         |  |

| 3   | CCP+                | Positive Terminal - Charge Pump Flying Capacitor |  |

| 4   | PGND                | Power Ground                                     |  |

| 5   | CCP-                | Negative Terminal - Charge Pump Flying Capacitor |  |

| 6   | V <sub>CP_OUT</sub> | Charge Pump Output                               |  |

| 7   | NC                  | No Connect                                       |  |

| 8   | AV <sub>SS</sub>    | Negative Power Supply - Amplifier                |  |

| 9   | OUT B               | Output B                                         |  |

| 10  | AV <sub>DD</sub>    | Positive Power Supply - Amplifier                |  |

| 11  | OUT A               | Output A                                         |  |

| 12  | NC                  | No Connect                                       |  |

| 13  | V <sub>IN</sub>     | Signal Input                                     |  |

| 14  | SGND                | Signal Ground                                    |  |

www.national.com 2

### **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage  $(V_{DD})$  4.5V Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C Input Voltage -0.3V to  $V_{DD} + 0.3$ V Power Dissipation (Note 3) Internally Limited ESD Susceptibility (Note 4) 2000V ESD Susceptibility (Note 5)

Junction Temperature 150°C

Thermal Resistance

See AN-1187 'Leadless Leadframe Packaging (LLP).'

## **Operating Ratings**

Temperature Range

$$\begin{split} T_{MIN} &\leq T_{A} \leq T_{MAX} & -40^{\circ}\text{C} \leq T_{A} \leq 85^{\circ}\text{C} \\ \text{Supply Voltage (V}_{DD}) & 1.6\text{V} \leq V_{DD} \leq 4.2\text{V} \end{split}$$

## Electrical Characteristics $V_{DD} = 3.6V$

The following specifications apply for  $V_{DD}$  = 3.6V,  $A_{V-BTL}$  = 6dB,  $Z_L$  =  $2\mu F + 30\Omega$  unless otherwise specified. Limits apply to  $T_A$  =  $25^{\circ}C$ . See Figure 1.

| Symbol               | Parameter                                        | Conditions                                                       | LM              | LM4953                |          |

|----------------------|--------------------------------------------------|------------------------------------------------------------------|-----------------|-----------------------|----------|

|                      |                                                  |                                                                  | Typ<br>(Note 6) | Limit<br>(Notes 7, 8) |          |

| I <sub>DD</sub>      | Quiescent Power Supply<br>Current                | $V_{IN} = 0$ , $R_{LOAD} = 2\mu F + 30\Omega$                    | 8               |                       | mA (max) |

| I <sub>standby</sub> | Quiescent Power Supply Current Auto Standby Mode | $V_{IN} = 0$ , $Z_{LOAD} = 2\mu F + 30\Omega$                    | 2.7             |                       | mA       |

| I <sub>SD</sub>      | Shutdown Current                                 | V <sub>SD</sub> = GND                                            | 0.1             | 1                     | μA (max) |

| V <sub>SDIH</sub>    | Shutdown Voltage Input High                      | SD1<br>SD2                                                       |                 | 0.7*CPVdd             | V (min)  |

| V <sub>SDIL</sub>    | Shutdown Voltage Input Low                       | SD1<br>SD2                                                       |                 | 0.3*CPVdd             | V (max)  |

| T <sub>WU</sub>      | Wake-up Time                                     |                                                                  | 125             |                       | μsec     |

| V <sub>os</sub>      | Output Offset Voltage                            |                                                                  | 1               | 10                    | mV (max) |

| V <sub>OUT</sub>     | Output Voltage Swing                             | THD = 1% (max); f = 1kHz<br>$R_L = 2\mu F + 30\Omega$ , Mono BTL | 12.6            |                       | Vpp      |

| THD+N                | Total Harmonic Distortion + Noise                | $V_{OUT} = 6Vp-p, f_{IN} = 1kHz$                                 | 0.02            |                       | %        |

| €os                  | Output Noise                                     | A-Weighted Filter, V <sub>IN</sub> = 0V                          | 15              |                       | μV       |

| PSRR                 | Power Supply Rejection                           | V <sub>RIPPLE</sub> = 200mVp-p, f = 217Hz,<br>Input Referred     | 67              |                       | dB       |

| ronn                 | Ratio                                            | V <sub>RIPPLE</sub> = 200mVp-p, f = 1kHz,<br>Input Referred      | 65              |                       | dB       |

| SNR                  | Signal-to-Noise Ratio                            | $Z_L = 2\mu F + 30\Omega$ , $V_{OUT} = 6Vp-p$                    | 105             |                       | dB       |

## Electrical Characteristics $V_{DD} = 3.0V$

The following specifications apply for  $V_{DD}$  = 3.0V,  $A_{V-BTL}$  = 6dB,  $Z_L$  =  $2\mu F + 30\Omega$  unless otherwise specified. Limits apply to  $T_A$  = 25°C. See Figure 1.

| Symbol               | Parameter                                           | Conditions                                    | LM4953   |              | Units (Limits) |

|----------------------|-----------------------------------------------------|-----------------------------------------------|----------|--------------|----------------|

|                      |                                                     |                                               | Тур      | Limit        |                |

|                      |                                                     |                                               | (Note 6) | (Notes 7, 8) | _              |

| I <sub>DD</sub>      | Quiescent Power Supply<br>Current                   | $V_{IN} = 0$ , $Z_{LOAD} = 2\mu F + 30\Omega$ | 7        | 10           | mA (max)       |

| I <sub>standby</sub> | Quiescent Power Supply<br>Current Auto Standby Mode | $V_{IN} = 0$ , $Z_{LOAD} = 2\mu F + 30\Omega$ | 2.3      |              | mA             |

| I <sub>SD</sub>      | Shutdown Current                                    | $V_{SD-LC} = V_{SD-RC} = GND$                 | 0.1      | 1            | μA (max)       |

| V <sub>SDIH</sub>    | Shutdown Voltage Input High                         | SD1<br>SD2                                    |          | 0.7*CPVdd    | V (min)        |

Electrical Characteristics  $V_{DD} = 3.0V$  (Continued) The following specifications apply for  $V_{DD} = 3.0V$ ,  $A_{V-BTL} = 6dB$ ,  $Z_L = 2\mu F + 30\Omega$  unless otherwise specified. Limits apply to  $T_A = 3.0V$ ,  $T_A$ 25°C. See Figure 1.

| Symbol            | Parameter                            | Conditions                                                       | LM4953          |                       | Units (Limits) |

|-------------------|--------------------------------------|------------------------------------------------------------------|-----------------|-----------------------|----------------|

|                   |                                      |                                                                  | Typ<br>(Note 6) | Limit<br>(Notes 7, 8) |                |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low           | SD1<br>SD2                                                       |                 | 0.3*CPVdd             | V (max)        |

| T <sub>WU</sub>   | Wake-up Time                         |                                                                  | 125             |                       | μsec           |

| V <sub>os</sub>   | Output Offset Voltage                |                                                                  | 1               | 10                    | mV (max)       |

| V <sub>OUT</sub>  | Output Voltage Swing                 | THD = 1% (max); f = 1kHz<br>$Z_L = 2\mu F + 30\Omega$ , Mono BTL | 10.2            |                       | Vpp            |

| THD+N             | Total Harmonic Distortion +<br>Noise | $V_{OUT} = 8.5$ Vp-p, $f_{IN} = 1$ kHz                           | 0.02            |                       | %              |

| ∈os               | Output Noise                         | A-Weighted Filter, V <sub>IN</sub> = 0V                          | 15              |                       | μV             |

| PSRR              | Power Supply Rejection<br>Ratio      | V <sub>RIPPLE</sub> = 200mVp-p, f = 217Hz,<br>Input Referred     | 73              |                       | dB             |

|                   |                                      | V <sub>RIPPLE</sub> = 200mVp-p, f = 1kHz,<br>Input Referred      | 68              |                       | dB             |

| SNR               | Signal-to-Noise Ratio                | $Z_L = 2\mu F + 30\Omega, V_{OUT} = 8.5Vp-p$                     | 105             |                       | dB             |

Note 1: All voltages are measured with respect to the GND pin unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions that guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given; however, the typical value is a good indication of device performance.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4xxx typical application (shown in Figure 1) with  $V_{DD} = yyV$ ,  $R_L = 2\mu F + 30\Omega$  mono BTL operation the total power dissipation is xxxW.  $\theta_{JA} = 40^{\circ}$ C/W.

Note 4: Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

Note 5: Machine Model, 220pF-240pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9: If the product is in shutdown mode and VDD exceeds 3.6V (to a max of 4V VDD), then most of the excess current will flow through the ESD protection circuits. If the source impedance limits the current to a max of 10mA, then the part will be protected. If the part is enabled when V<sub>DD</sub> is above 4V, circuit performance will be curtailed or the part may be permanently damaged.

www.national.com

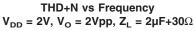

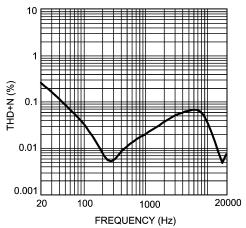

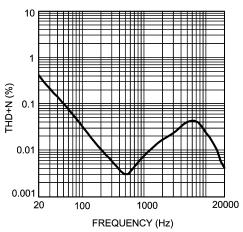

## **Typical Performance Characteristics**

20142112

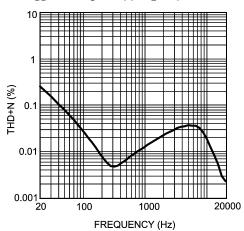

THD+N vs Frequency  $V_{DD}$  = 3.6V,  $V_{O}$  = 8.5Vpp,  $Z_{L}$  = 2 $\mu$ F+30 $\Omega$

20142114

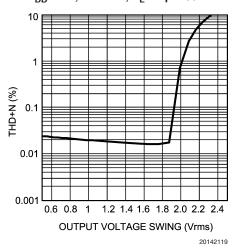

THD+N vs Output Voltage  $V_{DD}$  = 2V, f = 1kHz,  $Z_L$  = 2 $\mu$ F+30 $\Omega$

THD+N vs Frequency  $V_{DD}$  = 3V,  $V_{O}$  = 6Vpp,  $Z_{L}$  = 2 $\mu$ F+30 $\Omega$

20142113

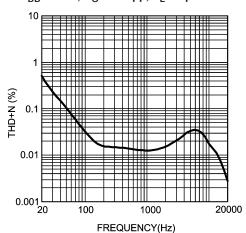

THD+N vs Frequency  $\label{eq:VDD} V_{DD}$  = 4.2V,  $V_{O}$  = 10Vpp,  $Z_{L}$  = 2 $\mu$ F+30 $\Omega$

20142118

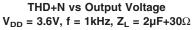

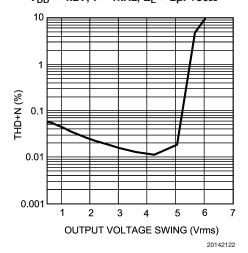

## THD+N vs Output Voltage $V_{DD}$ = 3V, f = 1kHz, $Z_L$ = 2 $\mu$ F+30 $\Omega$

## **Typical Performance Characteristics** (Continued)

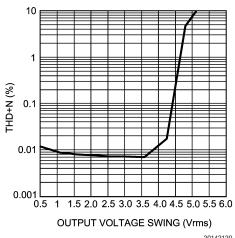

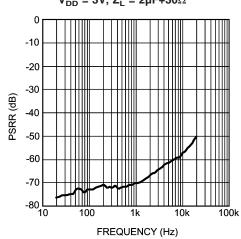

#### **PSRR vs Frequency** $V_{DD} = 2V$ , $Z_L = 2\mu F + 30\Omega$

**PSRR vs Frequency**

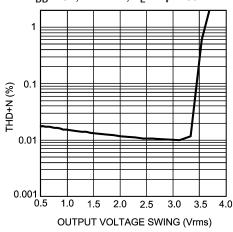

THD+N vs Output Voltage  $V_{DD}$  = 4.2V, f = 1kHz,  $Z_L$  = 2 $\mu$ F+30 $\Omega$

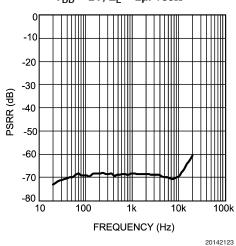

**PSRR vs Frequency**  $V_{DD}$  = 3V,  $Z_L$  =  $2\mu$ F+30 $\Omega$

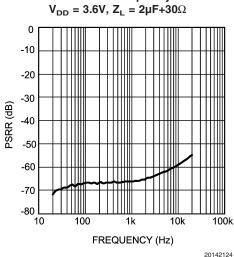

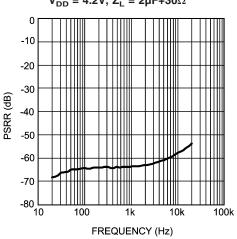

**PSRR vs Frequency**  $V_{DD} = 4.2V, Z_{L} = 2\mu F + 30\Omega$

20142126

## **Typical Performance Characteristics** (Continued)

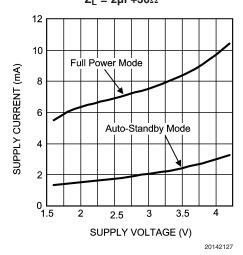

## Supply Current vs Supply Voltage $\label{eq:ZL} Z_L = 2\mu F + 30\Omega$

### **Application Information**

#### **ELIMINATING THE OUTPUT COUPLING CAPACITOR**

The LM4953 features a low noise inverting charge pump that generates an internal negative supply voltage. This allows the outputs of the LM4953 to be biased about GND instead of a nominal DC voltage, like traditional headphone amplifiers. Because there is no DC component, the large DC blocking capacitors (typically 220µF) are not necessary. The coupling capacitors are replaced by two, small ceramic charge pump capacitors, saving board space and cost.

Eliminating the output coupling capacitors also improves low frequency response. In traditional headphone amplifiers, the headphone impedance and the output capacitor form a high pass filter that not only blocks the DC component of the output, but also attenuates low frequencies, impacting the bass response. Because the LM4953 does not require the output coupling capacitors, the low frequency response of the device is not degraded by external components.

In addition to eliminating the output coupling capacitors, the ground referenced output nearly doubles the available dynamic range of the LM4953 when compared to a traditional headphone amplifier operating from the same supply voltage.

#### **BRIDGE CONFIGURATION EXPLANATION**

The Audio Amplifier portion of the LM4953has two internal amplifiers allowing different amplifier configurations. The first amplifier's gain is externally configurable, whereas the second amplifier is internally fixed in a unity-gain, inverting configuration. The closed-loop gain of the first amplifier is set by selecting the ratio of Rf to Ri while the second amplifier's gain is fixed by the two internal  $20k\Omega$  resistors. Figure 1 shows that the output of amplifier one serves as the input to amplifier two. This results in both amplifiers producing signals identical in magnitude, but out of phase by  $180^\circ$ . Consequently, the differential gain for the Audio Amplifier is

$$A_{VD} = 2 * (Rf/Ri)$$

By driving the load differentially through outputs OUT A and OUT B, an amplifier configuration commonly referred to as "bridged mode" is established. Bridged mode operation is different from the classic single-ended amplifier configuration where one side of the load is connected to ground.

A bridge amplifier design has a few distinct advantages over the single-ended configuration. It provides differential drive to the load, thus doubling the output swing for a specified supply voltage. Four times the output power is possible as compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or clipped. In order to choose an amplifier's closed-loop gain without causing excessive clipping, please refer to the **Audio Power Amplifier Design** section.

The bridge configuration also creates a second advantage over single-ended amplifiers. Since the differential outputs, OUT A and OUT B, are biased at half-supply, no net DC voltage exists across the load. This eliminates the need for an output coupling capacitor which is required in a single supply, single-ended amplifier configuration. Without an output coupling capacitor, the half-supply bias across the load would result in both increased internal IC power dissipation and also possible loudspeaker damage.

## OUTPUT TRANSIENT ('CLICK AND POPS') ELIMINATED

The LM4953 contains advanced circuitry that virtually eliminates output transients ('clicks and pops'). This circuitry prevents all traces of transients when the supply voltage is first applied or when the part resumes operation after coming out of shutdown mode.

#### **POWER DISSIPATION**

Power dissipation is a major concern when using any power amplifier and must be thoroughly understood to ensure a successful design. Equation 1 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (V_{DD})^2 / (2\pi^2 Z_L)$$

(1)

Since the LM4953 has two operational amplifiers in one package, the maximum internal power dissipation point is twice that of the number which results from Equation 1. Even with large internal power dissipation, the LM4953 does not require heat sinking over a large range of ambient temperatures. The maximum power dissipation point obtained must not be greater than the power dissipation that results from Equation 2:

$$P_{DMAX} = (T_{JMAX} - T_A) / (\theta_{JA})$$

(2)

Depending on the ambient temperature,  $T_A$ , of the system surroundings, Equation 2 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 1 is greater than that of Equation 2, then either the supply voltage must be decreased, the load impedance increased or  $T_A$  reduced. Power dissipation is a function of output power and thus, if typical operation is not around the maximum power dissipation point, the ambient temperature may be increased accordingly.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 3V power supply typically use a 4.7µF capacitor in parallel with a 0.1µF ceramic filter capacitor to stabilize the power supply's output, reduce noise on the supply line, and improve the supply's transient response. Keep the length of leads and traces that connect capacitors between the LM4953's power supply pin and ground as short as possible.

#### **AUTOMATIC STANDBY MODE**

The LM4953 features Automatic Standby Mode circuitry (patent pending). In the absence of an input signal, after approximately 3 seconds, the LM4953 goes into low current standby mode. The LM4953 recovers into full power operating mode immediately after a signal, which is greater than the input threshold voltage, is applied to either the left or right input pins. The input threshold voltage is not a static value, as the supply voltage increases, the input threshold voltage decreases. This feature reduces power supply current consumption in battery operated applications.

To ensure correct operation of Automatic Standby Mode, proper layout techniques should be implemented. Separating PGND and SGND can help reduce noise entering the LM4953 in noisy environments. It is also important to use

#### **Application Information** (Continued)

correct power off sequencing. The device should be in shutdown and then powered off in order to ensure proper functionality of the Auto-Standby feature. While Automatic Standby Mode reduces power consumption very effectively during silent periods, maximum power saving is achieved by putting the device into shutdown when it is not in use.

#### MICRO POWER SHUTDOWN

The voltage applied to the  $\overline{SD}$  controls the LM4953's shutdown function. When active, the LM4953's micropower shutdown feature turns off the amplifiers' bias circuitry, reducing the supply current. The trigger point is  $0.3^*CPV_{DD}$  for a logic-low level, and  $0.7^*CPV_{DD}$  for logic-high level. The low  $0.01\mu A$  (typ) shutdown current is achieved by applying a voltage that is as near as ground a possible to the  $\overline{SD}$  pins. A voltage that is higher than ground may increase the shutdown current.

There are a few ways to control the micro-power shutdown. These include using a single-pole, single-throw switch, a microprocessor, or a microcontroller. When using a switch, connect an external  $100k\Omega$  pull-up resistor between the  $\overline{SD}$  pins and  $V_{DD}$ . Connect the switch between the  $\overline{SD}$  pins and ground. Select normal amplifier operation by opening the switch. Closing the switch connects the  $\overline{SD}$  pins to ground, activating micro-power shutdown. The switch and resistor guarantee that the  $\overline{SD}$  pins will not float. This prevents unwanted state changes. In a system with a microprocessor or microcontroller, use a digital output to apply the control voltage to the  $\overline{SD}$  pins. Driving the  $\overline{SD}$  pins with active circuitry eliminates the pull-up resistor.

#### **EXPOSED-DAP CONSIDERATIONS**

It is essential that the exposed Die Attach Paddle (DAP), for the LM4953, is NOT connected to GND. For optimal operation it should be connected to AVss and VCP-OUT (Pins 6 and 8).

#### **SELECTING PROPER EXTERNAL COMPONENTS**

Optimizing the LM4953's performance requires properly selecting external components. Though the LM4953 operates well when using external components with wide tolerances, best performance is achieved by optimizing component values.

#### **Charge Pump Capacitor Selection**

Use low ESR (equivalent series resistance) (<100m $\Omega$ ) ceramic capacitors with an X7R dielectric for best performance. Low ESR capacitors keep the charge pump output impedance to a minimum, extending the headroom on the

negative supply. Higher ESR capacitors result in reduced output power from the audio amplifiers.

Charge pump load regulation and output impedance are affected by the value of the flying capacitor (C1). A larger valued C1 (up to 3.3uF) improves load regulation and minimizes charge pump output resistance. Beyond 3.3uF, the switch-on resistance dominates the output impedance for capacitor values above 2.2uF.

The output ripple is affected by the value and ESR of the output capacitor (C2). Larger capacitors reduce output ripple on the negative power supply. Lower ESR capacitors minimize the output ripple and reduce the output impedance of the charge pump.

The LM4953 charge pump design is optimized for 2.2uF, low ESR, ceramic, flying, and output capacitors.

#### **Input Capacitor Value Selection**

Amplifying the lowest audio frequencies requires high value input coupling capacitors ( $C_i$  in Figure 1). A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. Applications using speakers with this limited frequency response reap little improvement by using high value input and output capacitors.

Besides affecting system cost and size,  $C_i$  has an effect on the LM4953's click and pop performance. The magnitude of the pop is directly proportional to the input capacitor's size. Thus, pops can be minimized by selecting an input capacitor value that is no higher than necessary to meet the desired –3dB frequency.

As shown in Figure 1, the internal input resistor,  $R_i$  and the input capacitor,  $C_i$ , produce a -3dB high pass filter cutoff frequency that is found using Equation (3). Conventional headphone amplifiers require output capacitors; Equation (3) can be used, along with the value of  $R_L$ , to determine towards the value of output capacitor needed to produce a -3dB high pass filter cutoff frequency.

$$f_{i-3dB} = 1 / 2\pi R_i C_i$$

(3)

Also, careful consideration must be taken in selecting a certain type of capacitor to be used in the system. Different types of capacitors (tantalum, electrolytic, ceramic) have unique performance characteristics and may affect overall system performance. (See the section entitled Charge Pump Capacitor Selection.)

## **Application Information** (Continued)

LM4953 DEMO BOARD ARTWORK

**Top Layer**

20142194

Mid Layer 2

2014219

Mid Layer 1

NATIONAL SEMICONDUCTOR LM4953SD Audio Amplifier Ceramic Speaker Driver

20142195

#### **Bottom Layer**

NATIONAL SEMICONDUCTOR LM4953SD Audio Amplifier Ceramic Speaker Driver

## **Revision History**

| Rev | Date     | Description                                                                                       |

|-----|----------|---------------------------------------------------------------------------------------------------|

| 1.0 | 2/18/05  | Started D/S by copying LM4926 (DS201161).                                                         |

| 1.2 | 9/13/05  | Added the Typ Perf curves and Application Info section.                                           |

| 1.3 | 9/14/05  | Added more Typ Perf curves. First WEB release on the D/S.                                         |

| 1.4 | 9/19/05  | Fixed some typo, then re-released D/S to the WEB.                                                 |

| 1.5 | 11/11/05 | Added the LLP boards, then re-released D/S to the WEB not released on this date                   |

| 1.6 | 11/14/05 | Added the LLP boards, then re-released D/S to the WEB (per Nisha).                                |

| 1.7 | 11/15/05 | Text edit.                                                                                        |

| 1.8 | 12/21/05 | Added the EXPOSED-DAP CONSIDERATIONS (Application Info section), then re-released D/S to the WEB. |

| 1.9 | 2/01/06  | Edited 20142168 (Typ Appl ckt), then re-released D/S to the WEB.                                  |

11 www.national.com

## Physical Dimensions inches (millimeters) unless otherwise noted **DIMENSIONS ARE IN MILLIMETERS** (2.8) (14X 0.6) - (14X 0.25) RECOMMENDED LAND PATTERN PIN 1 INDEX AREA 0 8 MAX (45° X 0.25) п 14X 0.4±0.1 0 В A 12X 0.5 ⊕ 0.1M C AS BS 2X 3 SDA14A (Rev A) LLP Package Order Number LM4953SD NS Package Number SDA14A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560