Features

## Single-Ended-to-Differential LVECL/LVPECL 2:1 Multiplexer

#### **General Description**

The MAX9380 is a high-speed, low-jitter 2:1 multiplexer for clock and data distribution applications. The device selects one of the two single-ended inputs and converts it to a differential output.

The MAX9380 features low part-to-part skew of 33ps and propagation delay of 263ps.

The MAX9380 operates from a +3.0V to +3.8V supply for LVPECL applications or from a -3.0V to -3.8V supply for LVECL applications. The input is selected by a single select input. The select and data inputs feature internal pulldown resistors that ensure a low default state if left open.

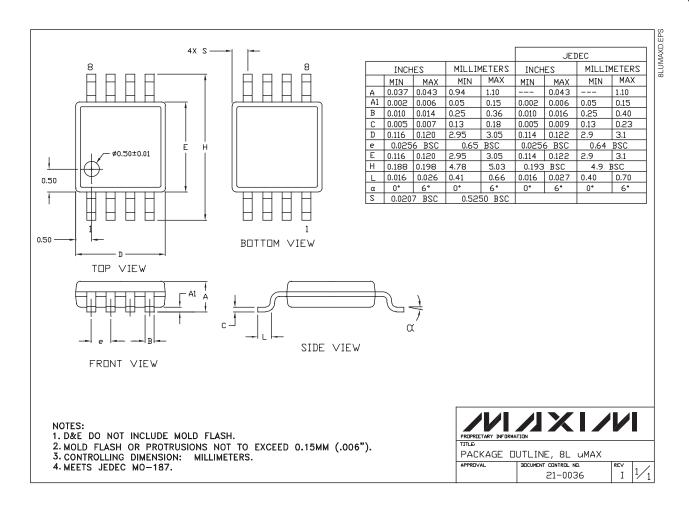

These devices are specified for operation from -40°C to +85°C, and are available in space-saving 8-pin µMAX and SO packages.

## **♦ Low 20mA Supply Current**

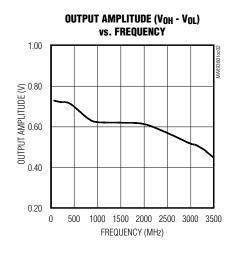

♦ >300mV Differential Output at 3.5GHz

- ♦ 33ps (typ) Part-to-Part Skew

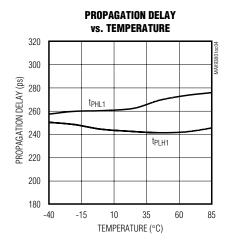

- ♦ 263ps (typ) Propagation Delay

- ♦ <0.2ps<sub>RMS</sub> Added Random Jitter

- ♦ High-Speed Select Input

- ♦ Output Low with Open Inputs

- ♦ Pin Compatible with MC10EP58

#### **Applications**

Precision Clock Distribution

**DSLAM**

DLC

Base Station

**ATE**

#### **Ordering Information**

| PART        | TEMP. RANGE    | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX9380EUA* | -40°C to +85°C | 8 µMAX      |

| MAX9380ESA  | -40°C to +85°C | 8 SO-EP**   |

<sup>\*</sup>Future product—contact factory for availability.

#### Input/Output Function Table

| INPUTS                               | OUTPUTS |   |  |  |  |

|--------------------------------------|---------|---|--|--|--|

| Da (SEL = high) or<br>Db (SEL = low) | Q       | Q |  |  |  |

| High                                 | Н       | L |  |  |  |

| Low or open                          | Ĺ       | Н |  |  |  |

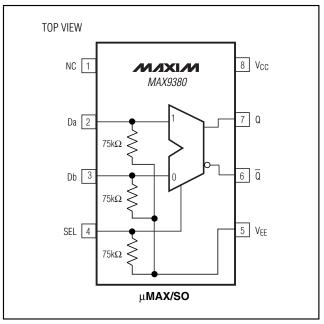

#### Pin Configuration

MIXIM

Maxim Integrated Products 1

<sup>\*\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> - V <sub>EE</sub>    | 0.3V to +4.1V            |

|--------------------------------------|--------------------------|

| Inputs (Da, Db, SEL)                 | VEE - 0.3V to VCC + 0.3V |

| Output Current (Continuous)          | 50mA                     |

| Output Current (Surge)               | 100mA                    |

| Junction-to-Ambient Thermal Resistar | nce in Still Air         |

| 8-Pin μMAX                           | +221°C/W                 |

| 8-Pin SO*                            | +170°C/W                 |

| Junction-to-Ambient Thermal Resistar | nce with                 |

| 500LFPM Airflow                      |                          |

| 8-Pin μMAX                           | +155°C/W                 |

| 8-Pin SO*                            | +99°C/W                  |

| Junction-to-Case Thermal Resistance           |             |

|-----------------------------------------------|-------------|

| 8-Pin μMAX+39°C                               | /W          |

| 8-Pin SO+40°C                                 | /W          |

| Operating Temperature Range40°C to +85        | °C          |

| Junction Temperature+150                      | $^{\circ}C$ |

| Storage Temperature Range65°C to +150         | ľ°С         |

| ESD Protection                                |             |

| Human Body Model (Inputs and Outputs)2        |             |

| Soldering Temperature (10s)+300               | °C          |

| * Rating is for exposed paddle not connected. |             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} - V_{EE} = +3.0 \text{V to } +3.8 \text{V}, \text{ outputs terminated with } 50\Omega \text{ to } V_{CC} - 2.0 \text{V}, \text{ unless otherwise noted.})$  (Notes 1, 2, 3)

| DADAMETED                              | OVMBOL                                                            | COMPITIONS     |                         | -40°C                      |                            | +25°C                   |                            |                           | +85°C                   |                            |                            | што   |

|----------------------------------------|-------------------------------------------------------------------|----------------|-------------------------|----------------------------|----------------------------|-------------------------|----------------------------|---------------------------|-------------------------|----------------------------|----------------------------|-------|

| PARAMETER                              | SYMBOL                                                            | CONDITIONS     | MIN                     | TYP                        | MAX                        | MIN                     | TYP                        | MAX                       | MIN                     | TYP                        | MAX                        | UNITS |

| INPUTS (Da, Db, SEL)                   |                                                                   |                |                         |                            |                            |                         |                            |                           |                         |                            |                            |       |

| Input High Voltage                     | V <sub>IH</sub>                                                   |                | V <sub>CC</sub> - 1.210 |                            | V <sub>CC</sub> - 0.885    | V <sub>CC</sub> - 1.145 |                            | V <sub>CC</sub> - 0.820   | V <sub>CC</sub> - 1.085 |                            | V <sub>CC</sub> - 0.760    | V     |

| Input Low Voltage                      | V <sub>IL</sub>                                                   |                | V <sub>CC</sub> - 1.935 |                            | V <sub>CC</sub> - 1.610    | V <sub>CC</sub> - 1.870 |                            | V <sub>CC</sub> - 1.545   | V <sub>CC</sub> - 1.81  |                            | V <sub>CC</sub> -<br>1.485 | V     |

| Input High Current                     | I <sub>IH</sub>                                                   | VIN = VIH(MAX) |                         |                            | 150                        |                         |                            | 150                       |                         |                            | 150                        | μΑ    |

| Input Low Current                      | w Current I <sub>IL</sub> V <sub>IN</sub> = V <sub>IL</sub> (MIN) |                | 0.5                     |                            |                            | 0.5                     |                            |                           | 0.5                     |                            |                            | μΑ    |

| OUTPUTS $(Q, \overline{Q})$            |                                                                   |                |                         |                            |                            |                         |                            |                           |                         |                            |                            |       |

| Single-Ended<br>Output High<br>Voltage | Voн                                                               | Figure 1       |                         | V <sub>CC</sub> -<br>0.979 | V <sub>CC</sub> -<br>0.885 | V <sub>CC</sub> - 1.07  | V <sub>CC</sub> -<br>0.959 | V <sub>CC</sub> - 0.82    | V <sub>CC</sub> -       | V <sub>CC</sub> -<br>0.947 | V <sub>CC</sub> - 0.76     | V     |

| Single-Ended<br>Output Low<br>Voltage  | V <sub>OL</sub>                                                   | Figure 1       | V <sub>CC</sub> - 1.935 | V <sub>CC</sub> -<br>1.721 | V <sub>CC</sub> -<br>1.685 | V <sub>CC</sub> - 1.87  | V <sub>CC</sub> - 1.698    | V <sub>CC</sub> -<br>1.62 | V <sub>CC</sub> -       | V <sub>CC</sub> -<br>1.681 | V <sub>CC</sub> -<br>1.56  | V     |

| Differential Output<br>Voltage         | V <sub>OH</sub> -                                                 | Figure 1       | 550                     | 748                        |                            | 550                     | 741                        |                           | 550                     | 734                        |                            | mV    |

| POWER SUPPLY                           |                                                                   |                |                         |                            |                            |                         |                            |                           |                         |                            |                            |       |

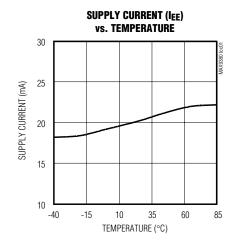

| Supply Current                         | I <sub>EE</sub>                                                   | (Note 4)       |                         | 18                         | 26                         |                         | 20                         | 26                        |                         | 22                         | 30                         | mA    |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} - V_{EE} = +3.0 \text{V to } +3.8 \text{V}, \text{ outputs loaded with } 50\Omega \text{ to } V_{CC} - 2 \text{V}, \text{V}_{IH} = V_{CC} - 1.11 \text{V}, \text{V}_{IL} = V_{CC} - 1.53 \text{V}, \text{ input frequency} = 2.0 \text{GHz}, \text{input transition time} = 125 \text{ps} (20\% \text{ to } 80\%). \text{Typical values are at } V_{CC} - V_{EE} = +3.3 \text{V}, \text{ unless otherwise noted.}) (Notes 1, 5)$

| PARAMETER                             | SYMBOL                          | CONDITIONS                                 |                                           | -40°C |     | +25°C |     | +85°C |     |     | UNITS |     |             |

|---------------------------------------|---------------------------------|--------------------------------------------|-------------------------------------------|-------|-----|-------|-----|-------|-----|-----|-------|-----|-------------|

| PARAMETER                             | STINIBUL                        |                                            |                                           | MIN   | TYP | MAX   | MIN | TYP   | MAX | MIN | TYP   | MAX | UNITS       |

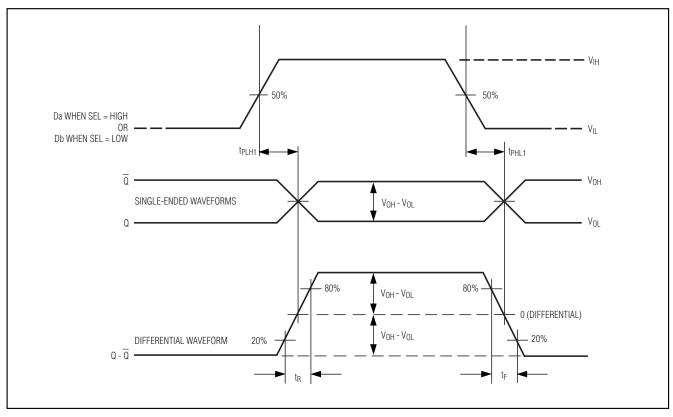

| Data Input-to-Output<br>Delay         | tPLH1,<br>tPHL1                 | Figure 1                                   |                                           | 176   | 258 | 298   | 192 | 263   | 316 | 222 | 277   | 385 | ps          |

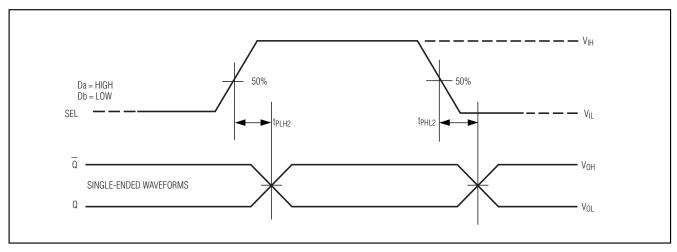

| Select Input-to-<br>Output Delay      | tPLH2,<br>tPHL2,                | Figure                                     | Figure 2                                  |       | 304 | 329   | 219 | 308   | 360 | 247 | 318   | 392 | ps          |

| Part-to-Part Skew                     | tskpp                           | Data input to output (Note 6)              |                                           |       | 27  | 122   |     | 33    | 124 |     | 14    | 163 | ps          |

| Added Random<br>Jitter (Note 7)       | t <sub>RJ</sub>                 | f <sub>IN</sub> = 3.2GHz,<br>clock pattern |                                           |       |     | 1.2   |     | 0.2   | 1.2 |     |       | 1.2 | ps<br>(RMS) |

| Added Deterministic                   | to i                            | 2.0Gb<br>PRBS                              | ps, 2 <sup>23</sup> - 1                   |       |     | 51    |     | 36    | 51  |     |       | 51  | ps          |

| Jitter (Note 7)                       |                                 | 3.2Gb<br>PRBS                              | ps, 2 <sup>23</sup> - 1                   |       |     | 77    |     | 48    | 77  |     |       | 77  | (p-p)       |

| Switching Frequency                   | <b>.</b>                        | Figure                                     | V <sub>OH</sub> - V <sub>OL</sub> ≥ 300mV | 3.0   | 3.5 |       | 3.0 | 3.5   |     | 3.0 | 3.5   |     | CLI-        |

|                                       | quency f <sub>MAX</sub>         | IMAX 1                                     | V <sub>OH</sub> - V <sub>OL</sub> ≥ 550mV | 2.0   |     |       | 2.0 |       |     | 2.0 |       |     | GHz         |

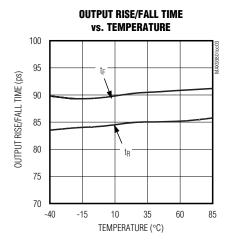

| Output Rise/Fall<br>Time (20% to 80%) | t <sub>R</sub> , t <sub>F</sub> | Figure 1                                   |                                           | 50    |     | 96    | 50  |       | 96  | 50  |       | 98  | ps          |

- Note 1: Measurements are made with the device in thermal equilibrium.

- Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative.

- Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full operating temperature range.

- Note 4: All pins are open except V<sub>CC</sub> and V<sub>EE</sub>.

- **Note 5:** Guaranteed by design and characterization. Limits are set to  $\pm 6$  sigma.

- Note 6: Measured between outputs of different parts at the signal crossing points under identical conditions for a same-edge transition.

- Note 7: Device jitter added to the input signal.

#### **Typical Operating Characteristics**

$(V_{CC} - V_{EE} = +3.3V, V_{IH} = V_{CC} - 1.165V, V_{IL} = V_{CC} - 1.475V,$  outputs loaded with  $50\Omega$  to  $V_{CC} - 2.0V$ , input frequency = 1GHz, input transition time = 125ps (20% to 80%), unless otherwise noted.)

### Pin Description

| PIN               | NAME            | FUNCTION                                                                                                                                                                              |

|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | NC              | No Connection. Not internally connected.                                                                                                                                              |

| 2                 | Da              | Single-Ended LVECL/LVPECL Data Input. Da is low default through internal 75k $\Omega$ pulldown resistor.                                                                              |

| 3                 | Db              | Single-Ended LVECL/LVPECL Data Input. Db is low default through internal 75k $\Omega$ pulldown resistor.                                                                              |

| 4                 | SEL             | Single-Ended Control Input. SEL is low default through an internal 75k $\Omega$ pulldown resistor selecting Db. Setting SEL to high selects Da.                                       |

| 5                 | V <sub>EE</sub> | Negative Supply Voltage                                                                                                                                                               |

| 6                 | Q               | Differential LVECL/LVPECL Output. Open Emitter. $\overline{\mathbb{Q}}$ is default high when inputs are open.                                                                         |

| 7                 | Q               | Differential LVECL/LVPECL Output. Open Emitter. Q is default low when inputs are open.                                                                                                |

| 8                 | Vcc             | Positive Supply Voltage. Bypass V <sub>CC</sub> to V <sub>EE</sub> with 0.1µF and 0.01µF capacitors as close to the device as possible, with the smaller capacitor closest to the IC. |

| Exposed<br>Paddle | EP              | Exposed paddle (MAX9380ESA-EP only). Connect to VEE internally. See package dimension.                                                                                                |

Figure 1. Data Input-to-Output Propagation Delay and Transition Timing Diagram

Figure 2. Select Input-to-Output Propagation Delay and Transition Timing Diagram

#### **Detailed Description**

The MAX9380 is a high-speed, low-jitter 2:1 multiplexer designed for clock and data distribution. The device selects one of the two single-ended inputs.

The multiplexer function is controlled by the single-ended SEL input. A high level on the SEL input selects the single-ended data input Da. Similarly, a low level on the SEL input selects the single-ended data input Db. The selected input is converted to a differential signal at the Q and  $\overline{\mathbb{Q}}$  outputs.

The inputs Da, Db, and SEL have a  $75 k\Omega$  pulldown to VEE. This ensures that an open input has a low state. All inputs can be driven from a single-ended LVECL/LVPECL signal or to VEE and VCC.

#### Applications Information\_ LVECL/LVPECL

In LVECL systems, the positive supply voltage is conventionally chosen to be system ground. This arrangement produces the best noise immunity since ground is normally a system-wide reference voltage. Operate the MAX9380 with  $V_{\rm CC}=0$  (ground) and  $V_{\rm EE}=-3.3V$  for an LVECL system.

The MAX9380 operates in LVPECL systems by connecting  $V_{EE}$  to ground and  $V_{CC}$  to a positive supply voltage. Connect  $V_{CC}$  = +3.3V and  $V_{EE}$  = 0 for an LVPECL system.

#### **Power-Supply Bypassing**

Adequate power-supply bypassing is necessary to maximize the performance and noise immunity. This is particularly true of use in an LVPECL system where the power-supply voltage is used as a reference. Bypass VCC to VEE with high-frequency surface-mount ceramic 0.1 $\mu$ F and 0.01 $\mu$ F capacitors in parallel as close to the device as possible, with the 0.01 $\mu$ F capacitor closest to the device pins. Use multiple parallel vias for ground plane connection to minimize inductance.

#### **Circuit Board Traces**

Input and output trace characteristics affect the performance of ECL devices. Connect each of the MAX9380 inputs and outputs to a  $50\Omega$  characteristic impedance trace. Avoid discontinuities in differential impedance and maximize common-mode noise immunity by maintaining the distance between differential traces and avoid sharp corners. Minimize the number of vias to prevent impedance discontinuities. Reduce reflections by maintaining the  $50\Omega$  characteristic impedance through connectors and across cables. Minimize skew by matching the electrical length of the traces.

#### **Output Termination**

Terminate outputs through  $50\Omega$  to VCC - 2V or use an equivalent Thevenin termination. When a single-ended signal is taken from a differential output, terminate both outputs. For example, if the Q output of the MAX9380 is connected to a single-ended input, terminate both the Q and  $\overline{Q}$  outputs.

# MAX9380

# Single-Ended-to-Differential LVECL/LVPECL 2:1 Multiplexer

#### **Chip Information**

TRANSISTOR COUNT: 242

PROCESS: Bipolar

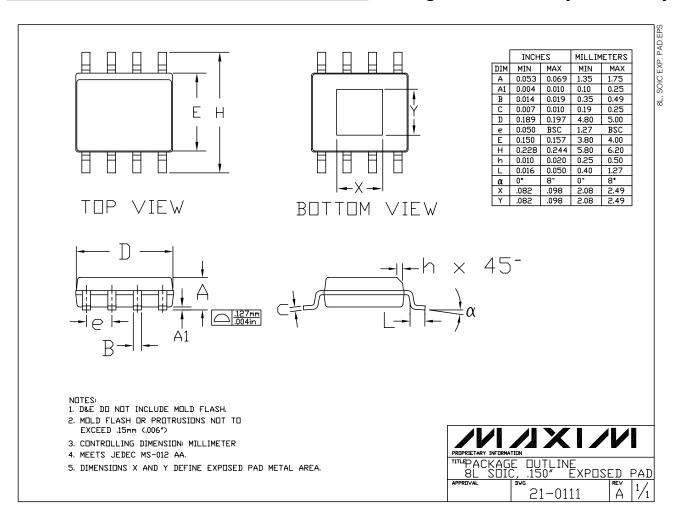

#### **Package Information**

#### Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

SUPPORT

#### **MAX9380**

#### **Part Number Table**

#### Notes:

- 1. See the MAX9380 QuickView Data Sheet for further information on this product family or download the MAX9380 full data sheet (PDF, 176kB).

- 2. Other options and links for purchasing parts are listed at: http://www.maxim-ic.com/sales.

- 3. Didn't Find What You Need? Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; + = RoHS/lead-free; # = RoHS/lead-exempt. More: See full data sheet or Part Naming Conventions.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number  | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE DRAWING CODE/VAR *                           | Temp         | RoHS/Lead-Free?<br>Materials Analysis    |

|--------------|----------------|---------------|----------------------------------------------------------------------|--------------|------------------------------------------|

| MAX9380EKA   |                |               |                                                                      | -40C to +85C | RoHS/Lead-Free: No                       |

| MAX9380EKA-T |                |               | SOT-23;8 pin;<br>Dwg: 21-0078F (PDF)<br>Use pkgcode/variation: K8-1* | -40C to +85C | RoHS/Lead-Free: No<br>Materials Analysis |

Didn't Find What You Need?

CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy