National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

June 1998

ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 8-Bit μP Compatible A/D Converters

🗙 National Semiconductor

# ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 8-Bit µP Compatible A/D Converters

## **General Description**

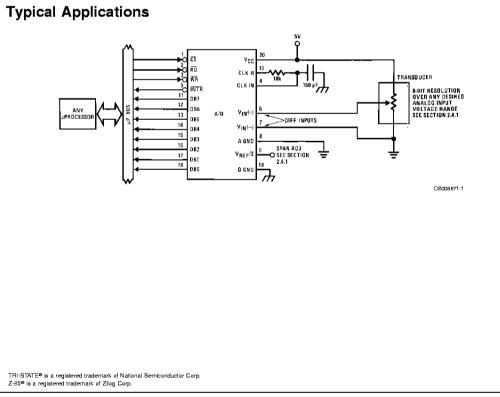

The ADC0801, ADC0802, ADC0803, ADC0804 and ADC0805 are CMOS 8-bit successive approximation A/D converters that use a differential potentiometric ladder—similar to the 256R products. These converters are designed to allow operation with the NSC800 and INS8080A derivative control bus with TRI-STATE® output latches directly driving the data bus. These A/Ds appear like memory locations or I/O ports to the microprocessor and no interfacing logic is needed.

Differential analog voltage inputs allow increasing the common-mode rejection and offsetting the analog zero input voltage value. In addition, the voltage reference input can be adjusted to allow encoding any smaller analog voltage span to the full 8 bits of resolution.

### Features

- Compatible with 8080 μP derivatives—no interfacing logic needed - access time - 135 ns

- Easy interface to all microprocessors, or operates "stand alone"

- Differential analog voltage inputs

- Logic inputs and outputs meet both MOS and TTL voltage level specifications

- Works with 2.5V (LM336) voltage reference

- On-chip clock generator

- 0V to 5V analog input voltage range with single 5V supply

- No zero adjust required

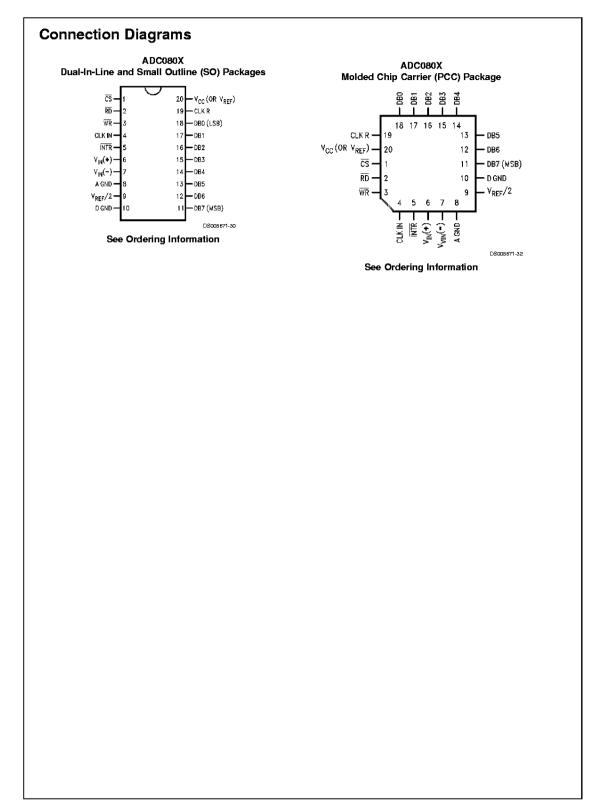

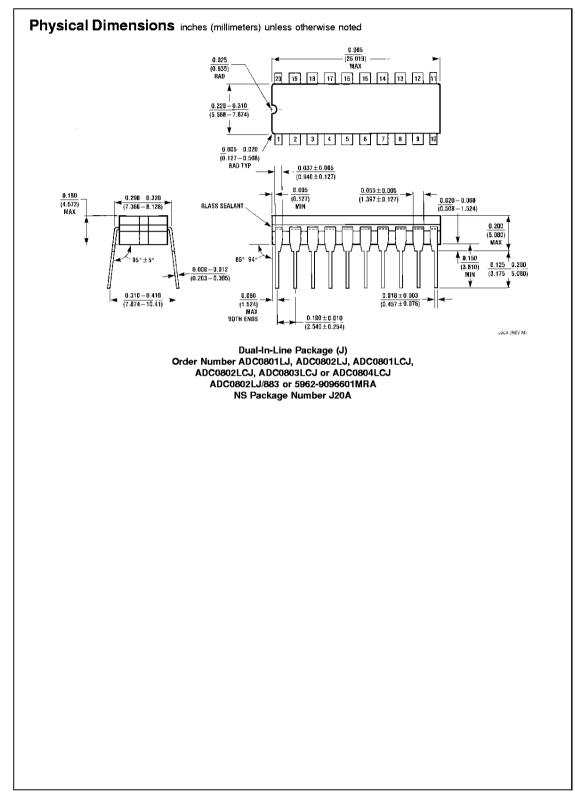

- 0.3" standard width 20-pin DIP package

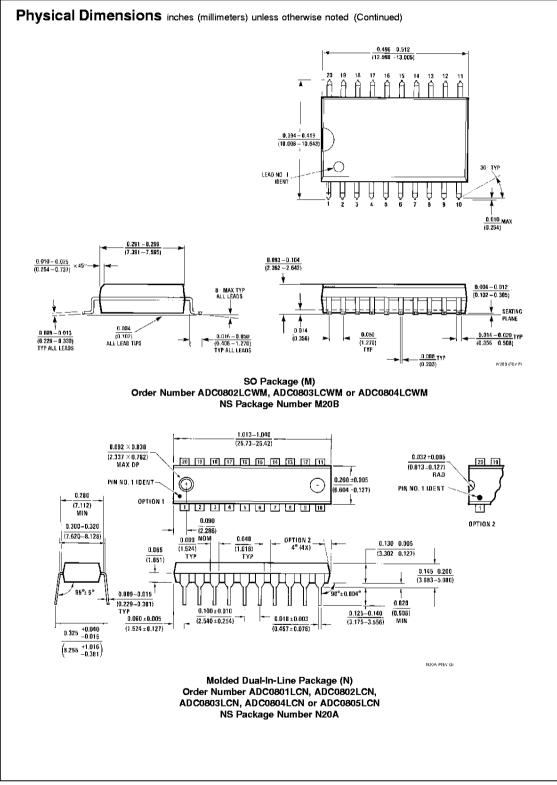

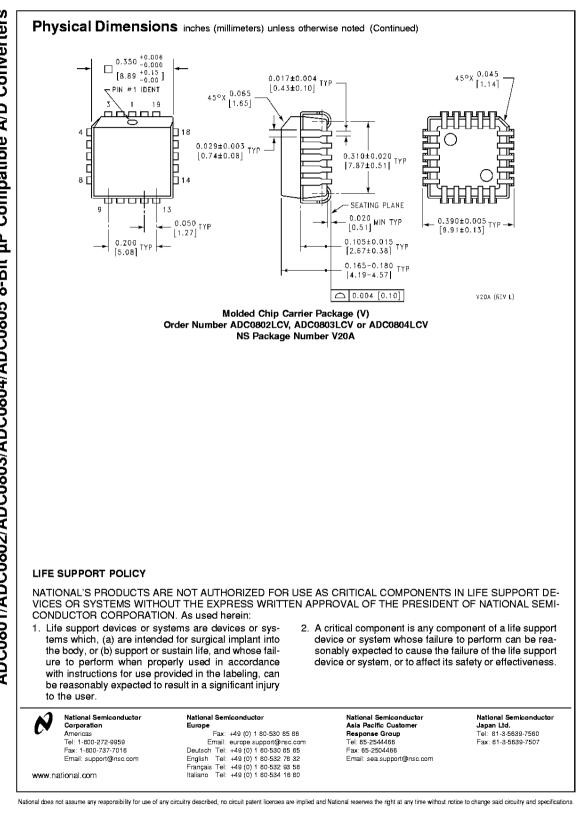

- 20-pin molded chip carrier or small outline package

- Operates ratiometrically or with 5 V<sub>DC</sub>, 2.5 V<sub>DC</sub>, or analog span adjusted voltage reference

### **Key Specifications**

- Resolution: 8 bits

- Total error: ±1/4 LSB, ±1/2 LSB and ±1 LSB

- Conversion time: 100 µs

© 1999 National Semiconductor Corporation DS005671

## Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

## Operating Ratings (Notes 1, 2)

| 11,5 8,100,11                      |                                  |

|------------------------------------|----------------------------------|

| Voltage                            |                                  |

| Logic Control Inputs               | -0.3V to +18V                    |

| At Other Input and Outputs         | –0.3V to (V <sub>CC</sub> +0.3V) |

| Lead Temp. (Soldering, 10 seconds) |                                  |

| Dual-In-Line Package (plastic)     | 260°C                            |

| Dual-In-Line Package (ceramic)     | 300°C                            |

| Surface Mount Package              |                                  |

| Vapor Phase (60 seconds)           | 215°C                            |

| Infrared (15 seconds)              | 220°C                            |

|                                    |                                  |

Temperature Range  $T_{MIN} \leq T_A \leq T_{MAX}$ ADC0801/02LJ, ADC0802LJ/883 –55°C≤T<sub>A</sub>≤+125°C –40°C≤T<sub>A</sub>≤+85°C ADC0801/02/03/04LCJ ADC0801/02/03/05LCN –40°C≤T<sub>A</sub>≤+85°C ADC0804LCN 0°C≤T₄≤+70°C 0°C≤T<sub>A</sub>≤+70°C ADC0802/03/04LCV ADC0802/03/04LCWM 0°C≤T<sub>A</sub>≤+70°C Range of  $V_{\rm CC}$ 4.5  $V_{\text{DC}}$  to 6.3  $V_{\text{DC}}$

## **Electrical Characteristics**

Supply Voltage (V<sub>CC</sub>) (Note 3)

The following specifications apply for V<sub>CC</sub>=5 V<sub>DC</sub>,  $T_{MIN} \le T_A \le T_{MAX}$  and  $f_{CLK}$ =640 kHz unless otherwise specified.

6.5V

| Parameter                                    | Conditions                                   | Min      | Тур   | Max                   | Units           |

|----------------------------------------------|----------------------------------------------|----------|-------|-----------------------|-----------------|

| ADC0801: Total Adjusted Error (Note 8)       | With Full-Scale Adj.                         |          |       | ±1⁄4                  | LSB             |

|                                              | (See Section 2.5.2)                          |          |       |                       |                 |

| ADC0802: Total Unadjusted Error (Note 8)     | V <sub>REF</sub> /2=2.500 V <sub>DC</sub>    |          |       | ±1⁄2                  | LSB             |

| ADC0803: Total Adjusted Error (Note 8)       | With Full-Scale Adj.                         |          |       | ±1⁄2                  | LSB             |

|                                              | (See Section 2.5.2)                          |          |       |                       |                 |

| ADC0804: Total Unadjusted Error (Note 8)     | V <sub>REF</sub> /2=2.500 V <sub>DC</sub>    |          |       | ±1                    | LSB             |

| ADC0805: Total Unadjusted Error (Note 8)     | V <sub>REF</sub> /2-No Connection            |          |       | ±1                    | LSB             |

| V <sub>REF</sub> /2 Input Resistance (Pin 9) | ADC0801/02/03/05                             | 2.5      | 8.0   |                       | kΩ              |

|                                              | ADC0804 (Note 9)                             | 0.75     | 1.1   |                       | kΩ              |

| Analog Input Voltage Range                   | (Note 4) V(+) or V(-)                        | Gnd-0.05 |       | V <sub>CC</sub> +0.05 | V <sub>DC</sub> |

| DC Common-Mode Error                         | Over Analog Input Voltage                    |          | ±1/16 | ±1⁄8                  | LSB             |

|                                              | Range                                        |          |       |                       |                 |

| Power Supply Sensitivity                     | V <sub>CC</sub> =5 V <sub>DC</sub> ±10% Over |          | ±1/16 | ±1⁄8                  | LSB             |

|                                              | Allowed $V_{IN}(+)$ and $V_{IN}(-)$          |          |       |                       |                 |

|                                              | Voltage Range (Note 4)                       |          |       |                       |                 |

## **AC Electrical Characteristics**

| Symbol                            | Parameter                             | Conditions                                        | Min  | Тур | Max  | Units              |  |

|-----------------------------------|---------------------------------------|---------------------------------------------------|------|-----|------|--------------------|--|

| Т <sub>с</sub>                    | Conversion Time                       | f <sub>CLK</sub> =640 kHz (Note 6)                | 103  |     | 114  | μs                 |  |

| т <sub>с</sub>                    | Conversion Time                       | (Notes 5, 6)                                      | 66   |     | 73   | 1/f <sub>CLK</sub> |  |

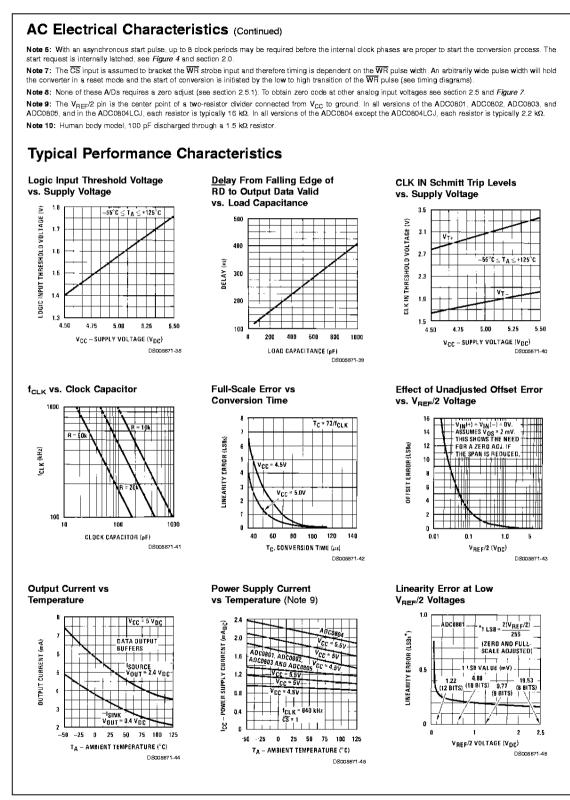

| f <sub>CLK</sub>                  | Clock Frequency                       | V <sub>CC</sub> =5V, (Note 5)                     | 100  | 640 | 1460 | kHz                |  |

|                                   | Clock Duty Cycle                      |                                                   | 40   |     | 60   | %                  |  |

| CR                                | Conversion Rate in Free-Running       | INTR tied to WR with                              | 8770 |     | 9708 | conv/s             |  |

|                                   | Mode                                  | CS =0 V <sub>DC</sub> , f <sub>CLK</sub> =640 kHz |      |     |      |                    |  |

| tw(WR)L                           | Width of WR Input (Start Pulse Width) | CS =0 V <sub>DC</sub> (Note 7)                    | 100  |     |      | ns                 |  |

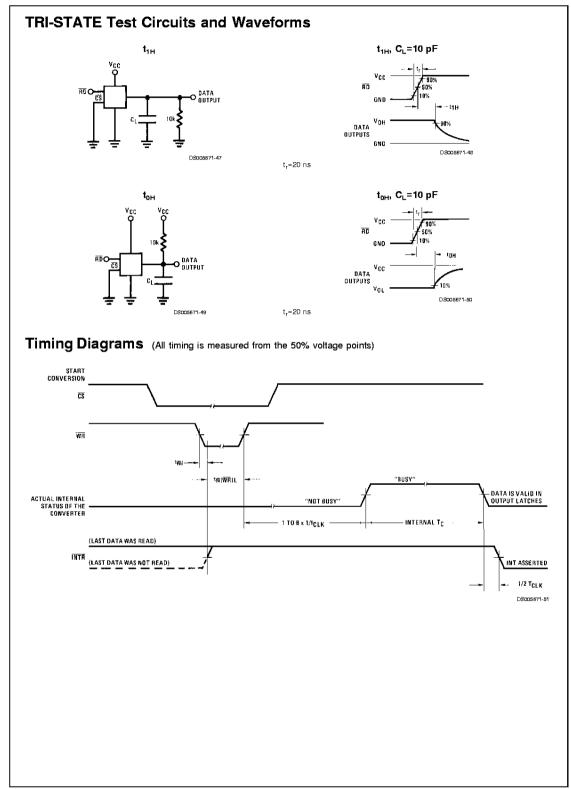

| t <sub>ACC</sub>                  | Access Time (Delay from Falling       | C <sub>L</sub> =100 pF                            |      | 135 | 200  | ns                 |  |

|                                   | Edge of RD to Output Data Valid)      |                                                   |      |     |      |                    |  |

| t <sub>1H</sub> , t <sub>он</sub> | TRI-STATE Control (Delay              | C <sub>L</sub> =10 pF, R <sub>L</sub> =10k        |      | 125 | 200  | ns                 |  |

|                                   | from Rising Edge of RD to             | (See TRI-STATE Test                               |      |     |      |                    |  |

|                                   | Hi-Z State)                           | Circuits)                                         |      |     |      |                    |  |

| t <sub>wi</sub> , t <sub>Ri</sub> | Delay from Falling Edge               |                                                   |      | 300 | 450  | ns                 |  |

|                                   | of WR or RD to Reset of INTR          |                                                   |      |     |      |                    |  |

| Symbol               | Parameter                                              | Conditions                                                       | Min           | Тур         | Max       | Units            |

|----------------------|--------------------------------------------------------|------------------------------------------------------------------|---------------|-------------|-----------|------------------|

| C <sub>IN</sub>      | Input Capacitance of Logic                             |                                                                  |               | 5           | 7.5       | pF               |

|                      | Control Inputs                                         |                                                                  |               |             |           |                  |

| Соит                 | TRI-STATE Output                                       |                                                                  |               | 5           | 7.5       | pF               |

|                      | Capacitance (Data Buffers)                             |                                                                  |               |             |           |                  |

| CONTROL              | NPUTS [Note: CLK IN (Pin 4) is the input o             | f a Schmitt trigger circuit and is the                           | erefore sp    | ecified sep | parately] |                  |

| V <sub>IN</sub> (1)  | Logical "1" Input Voltage                              | $V_{CC}$ =5.25 $V_{DC}$                                          | 2.0           |             | 15        | VDC              |

|                      | (Except Pin 4 CLK IN)                                  |                                                                  |               |             |           |                  |

| V <sub>IN</sub> (0)  | Logical "0" Input Voltage                              | $V_{CC}$ =4.75 $V_{DC}$                                          |               |             | 0.8       | V <sub>DC</sub>  |

|                      | (Except Pin 4 CLK IN)                                  |                                                                  |               |             |           |                  |

| l <sub>in</sub> (1)  | Logical "1" Input Current                              | V <sub>IN</sub> =5 V <sub>DC</sub>                               |               | 0.005       | 1         | μA <sub>DC</sub> |

|                      | (All Inputs)                                           |                                                                  |               |             |           |                  |

| l <sub>in</sub> (0)  | Logical "0" Input Current                              | V <sub>IN</sub> =0 V <sub>DC</sub>                               | -1            | -0.005      |           | μA <sub>DC</sub> |

|                      | (All Inputs)                                           |                                                                  |               |             |           |                  |

| CLOCK IN             | AND CLOCK R                                            | •                                                                |               |             |           |                  |

| V <sub>⊤</sub> +     | CLK IN (Pin 4) Positive Going                          |                                                                  | 2.7           | 3.1         | 3.5       | V <sub>DC</sub>  |

|                      | Threshold Voltage                                      |                                                                  |               |             |           |                  |

| V <sub>T</sub> -     | CLK IN (Pin 4) Negative                                |                                                                  | 1.5           | 1.8         | 2.1       | V <sub>DC</sub>  |

|                      | Going Threshold Voltage                                |                                                                  |               |             |           |                  |

| V <sub>H</sub>       | CLK IN (Pin 4) Hysteresis                              |                                                                  | 0.6           | 1.3         | 2.0       | V <sub>DC</sub>  |

|                      | (V <sub>⊤</sub> +)–(V <sub>⊤</sub> –)                  |                                                                  |               |             |           |                  |

| V <sub>OUT</sub> (0) | Logical "0" CLK R Output                               | I <sub>O</sub> =360 μA                                           |               |             | 0.4       | V <sub>DC</sub>  |

|                      | Voltage                                                | $V_{CC}$ =4.75 $V_{DC}$                                          |               |             |           |                  |

| V <sub>OUT</sub> (1) | Logical "1" CLK R Output                               | I <sub>O</sub> =–360 μA                                          | 2.4           |             |           | V <sub>DC</sub>  |

|                      | Voltage                                                | $V_{CC}$ =4.75 $V_{DC}$                                          |               |             |           |                  |

| DATA OUT             | PUTS AND INTR                                          | •                                                                |               |             |           |                  |

| V <sub>OUT</sub> (0) | Logical "0" Output Voltage                             |                                                                  |               |             |           |                  |

|                      | Data Outputs                                           | $I_{OUT}$ =1.6 mA, $V_{CC}$ =4.75 $V_{DC}$                       |               |             | 0.4       | V <sub>DC</sub>  |

|                      | INTR Output                                            | $I_{OUT}$ =1.0 mA, $V_{CC}$ =4.75 $V_{DC}$                       |               |             | 0.4       | VDC              |

| V <sub>OUT</sub> (1) | Logical "1" Output Voltage                             | I <sub>O</sub> =-360 μA, V <sub>CC</sub> =4.75 V <sub>DC</sub>   | 2.4           |             |           | V <sub>DC</sub>  |

| V <sub>OUT</sub> (1) | Logical "1" Output Voltage                             | I <sub>O</sub> =-10 μA, V <sub>CC</sub> =4.75 V <sub>DC</sub>    | 4.5           |             |           | VDC              |

| lout                 | TRI-STATE Disabled Output                              | V <sub>OUT</sub> =0 V <sub>DC</sub>                              | -3            |             |           | μΑ <sub>DC</sub> |

|                      | Leakage (All Data Buffers)                             | V <sub>OUT</sub> =5 V <sub>DC</sub>                              |               |             | 3         | μΑ <sub>DC</sub> |

| ISOURCE              |                                                        | V <sub>OUT</sub> Short to Gnd, T <sub>A</sub> =25°C              | 4.5           | 6           |           | mA <sub>DC</sub> |

| Isink                |                                                        | V <sub>OUT</sub> Short to V <sub>CC</sub> , T <sub>A</sub> =25°C | 9.0           | 16          |           | mA <sub>DC</sub> |

| POWER SU             | PPLY                                                   |                                                                  |               | - I I       |           |                  |

| I <sub>cc</sub>      | Supply Current (Includes                               | f <sub>CLK</sub> =640 kHz,                                       |               |             |           |                  |

|                      | Ladder Current)                                        | $V_{\text{REF}}/2=NC, T_{\text{A}}=25^{\circ}C$                  |               |             |           |                  |

|                      |                                                        | and $\overline{CS} = 5V$                                         |               |             |           |                  |

|                      | ADC0801/02/03/04LCJ/05                                 |                                                                  |               | 1.1         | 1.8       | mA               |

|                      | ADC0804LCN/LCV/LCWM                                    |                                                                  |               | 1.9         | 2.5       | mA               |

| Note 1 Abe           | blute Maximum Ratings indicate limits beyond which dan | I and AC ala                                                     | ntrinel coord |             |           |                  |

Note 4: For  $V_{IN}(-) \ge V_{IN}(+)$  the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input (see block diagram) which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the  $V_{CC}$  supply. Be careful, during testing at low  $V_{CC}$  levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct-especially at elevated temperatures, and cause errors for analog inputs near full-scale. The specially at solve are the supply voltage by nore than 50 mV to with the order to dive diverge will therefore require a minimum supply voltage of 4.950  $V_{DC}$  over temperature variations, initial tolerance and loading.

Note 5: Accuracy is guaranteed at f<sub>CLK</sub> = 640 kHz. At higher clock frequencies accuracy can degrade. For lower clock frequencies, the duty cycle limits can be extended so long as the minimum clock high time interval or minimum clock low time interval is no less than 275 ns.

6

10

14

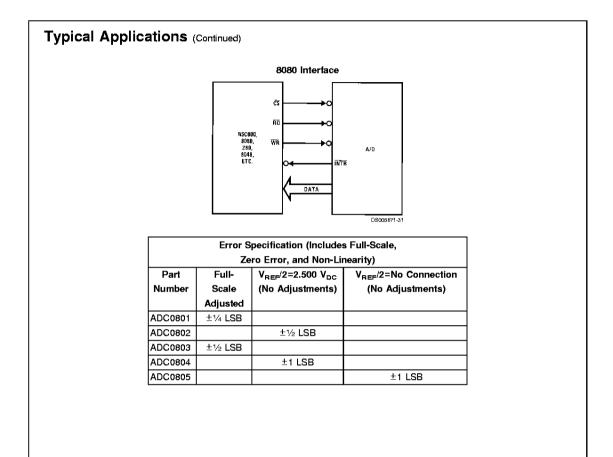

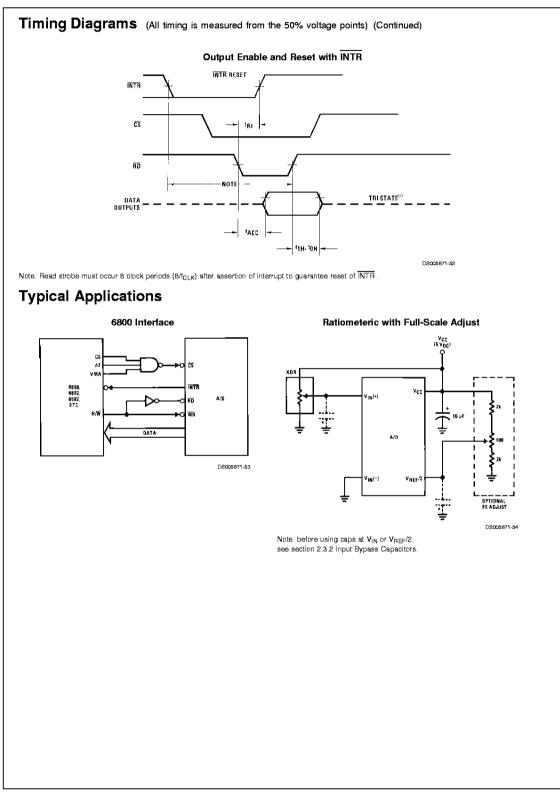

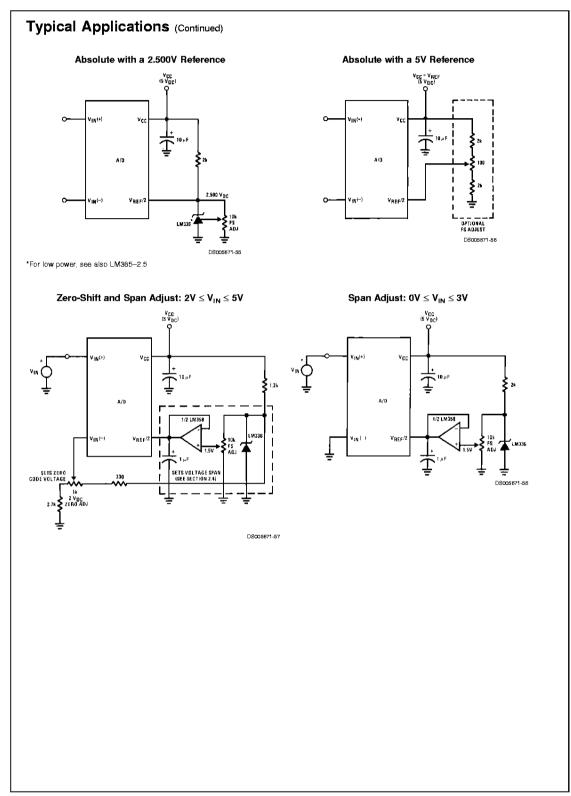

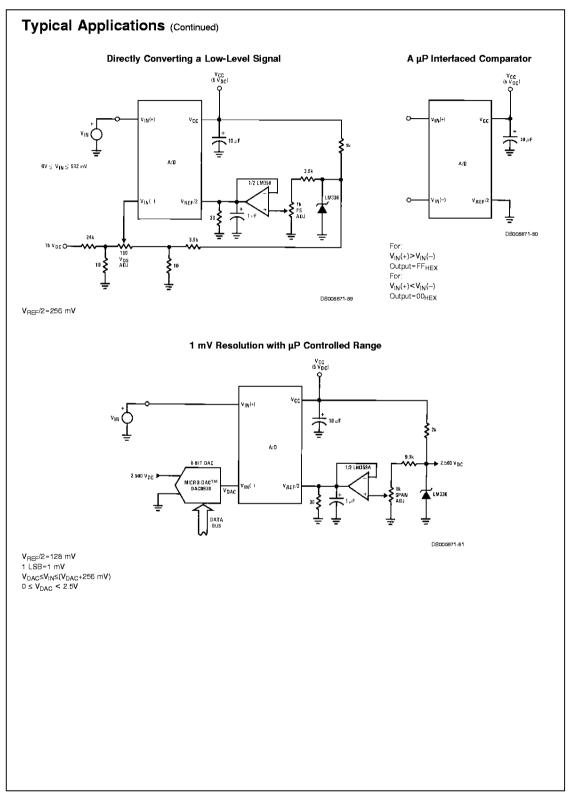

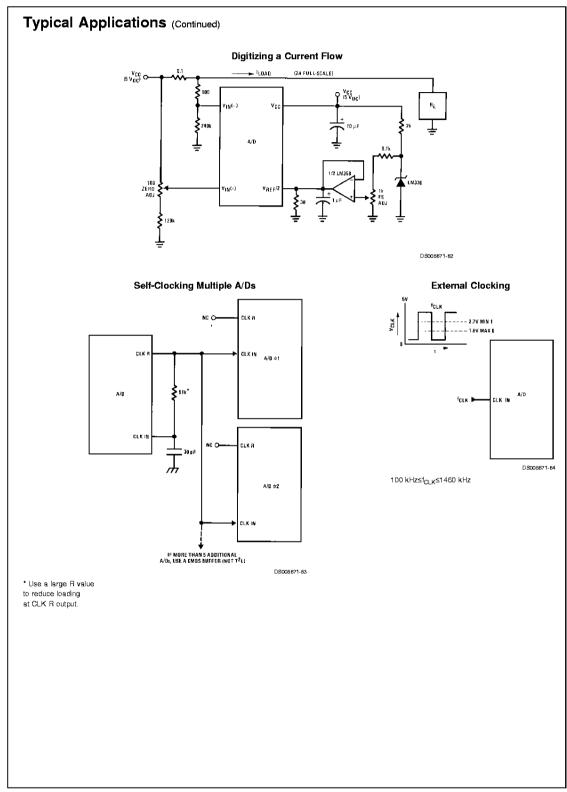

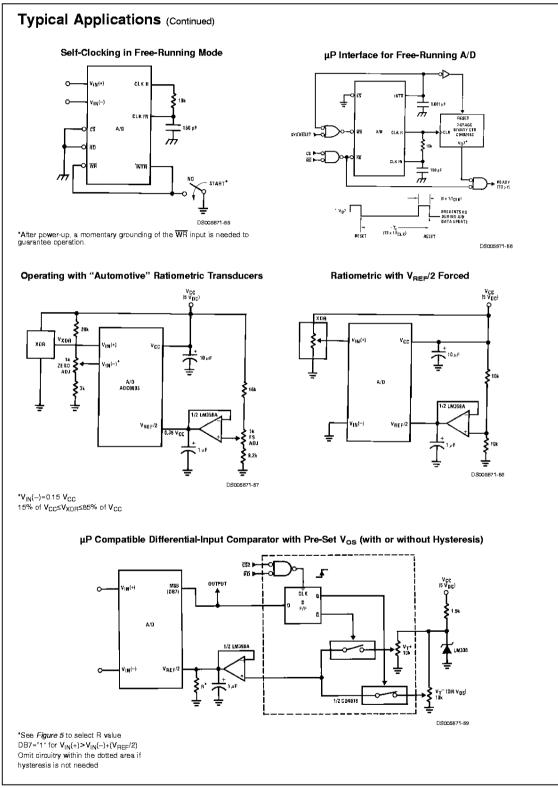

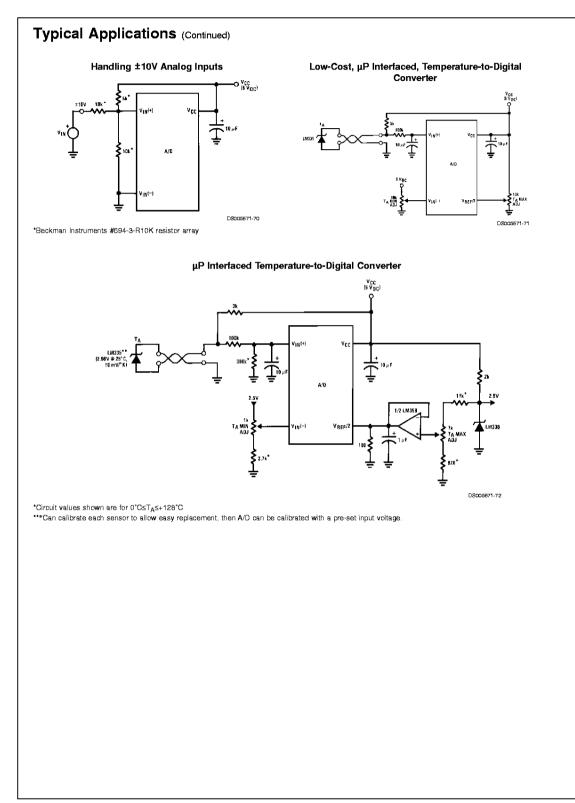

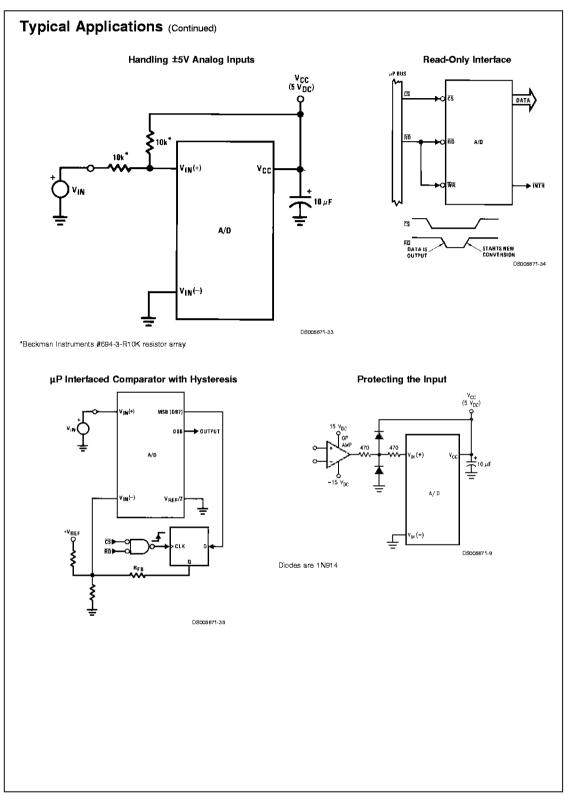

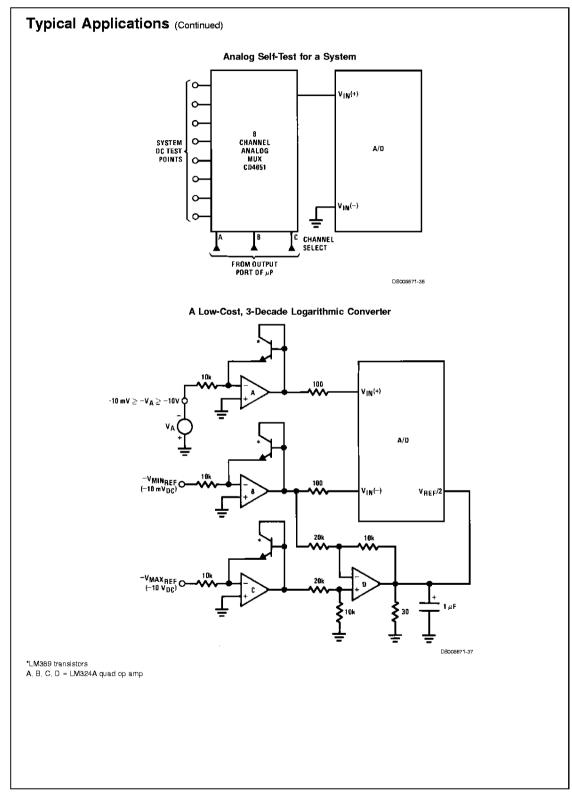

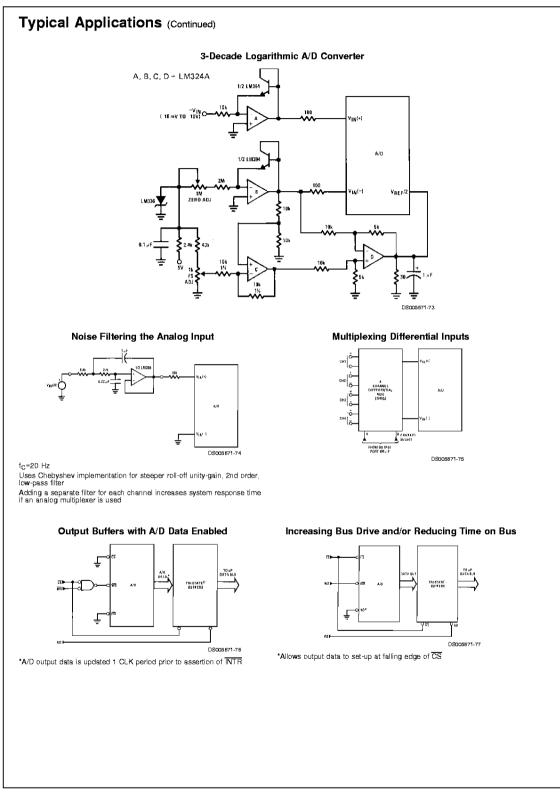

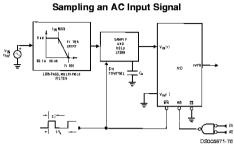

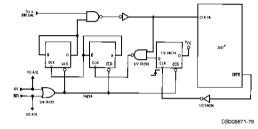

## Typical Applications (Continued)

Note 11: Oversample whenever possible [keep ts > 2t(-60)] to eliminate input frequency folding (aliasing) and to allow for the skirt response of the filter. Note 12: Consider the amplitude errors which are introduced within the passband of the filter.

(Complete shutdown takes ≈ 30 seconds.)

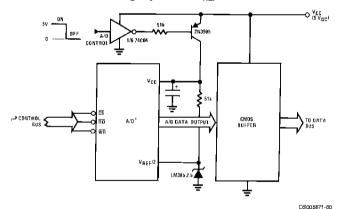

### Power Savings by A/D and $V_{\text{REF}}$ Shutdown

\*Use ADC0801, 02, 03 or 05 for lowest power consumption. Note: Logic inputs can be driven to  $V_{CC}$  with A/D supply at zero volts. Buffer prevents data bus from overdriving output of A/D when in shutdown mode.

## **Functional Description**

### 1.0 UNDERSTANDING A/D ERROR SPECS

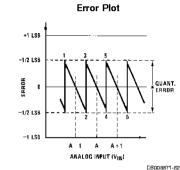

A perfect A/D transfer characteristic (staircase waveform) is shown in *Figure 1*. The horizontal scale is analog input voltage and the particular points labeled are in steps of 1 LSB (19.53 mV with 2.5V tied to the  $V_{\text{REF}}/2$  pin). The digital output codes that correspond to these inputs are shown as D-1, D, and D+1. For the perfect A/D, not only will center-value

(A–1, A, A+1, . . . . ) analog inputs produce the correct output digital codes, but also each riser (the transitions between adjacent output codes) will be located  $\pm \sqrt{2}$  LSB away from each center-value. As shown, the risers are ideal and have no width. Correct digital output codes will be provided for a range of analog input voltages that extend  $\pm \sqrt{2}$  LSB from the ideal center-values. Each tread (the range of analog input voltage that provides the same digital output code) is therefore 1 LSB wide.

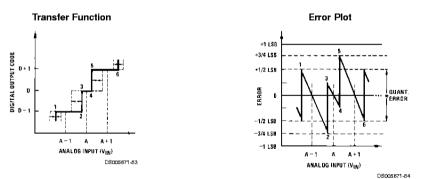

Figure 2 shows a worst case error plot for the ADC0801. All center-valued inputs are guaranteed to produce the correct output codes and the adjacent risers are guaranteed to be no closer to the center-value points than  $\pm \frac{1}{4}$  LSB. In other words, if we apply an analog input equal to the center-value  $\pm \frac{1}{4}$  LSB, we guarantee that the A/D will produce the correct digital code. The maximum range of the position of the code transition is indicated by the horizontal arrow and it is guarantee to be no more than  $\frac{1}{4}$  LSB.

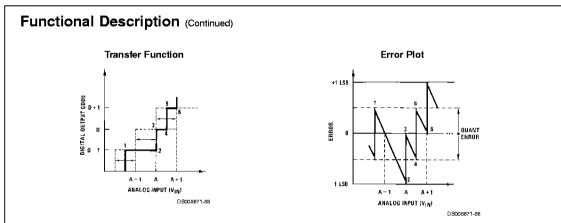

The error curve of *Figure 3* shows a worst case error plot for the ADC0802. Here we guarantee that if we apply an analog input equal to the LSB analog voltage center-value the A/D will produce the correct digital code.

Next to each transfer function is shown the corresponding error plot. Many people may be more familiar with error plots than transfer functions. The analog input voltage to the A/D is provided by either a linear ramp or by the discrete output steps of a high resolution DAC. Notice that the error is continuously displayed and includes the quantization uncertainty of the A/D. For example the error at point 1 of *Figure 1* is +½ LSB because the digital code appeared ½ LSB in advance of the center-value of the tread. The error plots always have a constant negative slope and the abrupt upside steps are always 1 LSB in magnitude.

FIGURE 1. Clarifying the Error Specs of an A/D Converter Accuracy=±0 LSB: A Perfect A/D

FIGURE 2. Clarifying the Error Specs of an A/D Converter Accuracy=±1/4 LSB

FIGURE 3. Clarifying the Error Specs of an A/D Converter Accuracy=±1/2 LSB

### 2.0 FUNCTIONAL DESCRIPTION

The ADC0801 series contains a circuit equivalent of the 256R network. Analog switches are sequenced by successive approximation logic to match the analog difference input voltage [V<sub>IN</sub>(+) – V<sub>IN</sub>(-)] to a corresponding tap on the R network. The most significant bit is tested first and after 8 comparisons (64 clock cycles) a digital 8-bit binary code (1111 1111 = full-scale) is transferred to an output latch and then an interrupt is asserted (INTR makes a high-to-low transition). A conversion in process can be interrupted by issuing a second start command. The device may be operated in the free-running mode by connecting INTR to the WR input with  $\overline{CS} = 0$ . To ensure start-up under all possible conditions, an external WR pulse is required during the first power-up cycle.

On the high-to-low transition of the  $\overline{WR}$  input the internal SAR latches and the shift register stages are reset. As long as the  $\overline{CS}$  input and  $\overline{WR}$  input remain low, the A/D will remain in a reset state. Conversion will start from 1 to 8 clock periods after at least one of these inputs makes a low-to-high transition.

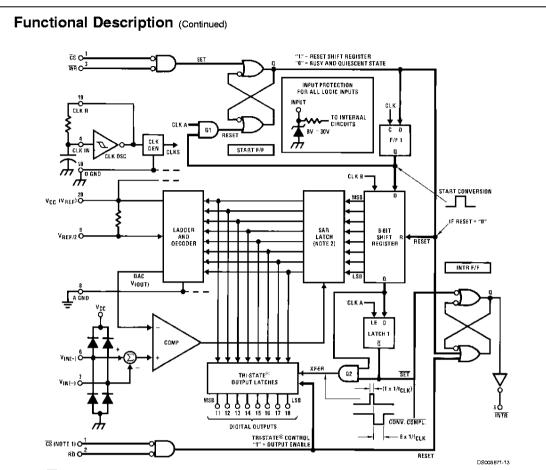

A functional diagram of the A/D converter is shown in *Figure* 4. All of the package pinouts are shown and the major logic control paths are drawn in heavier weight lines.

The converter is started by having  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  simultaneously low. This sets the start flip-flop (F/F) and the resulting "1" level resets the 8-bit shift register, resets the Interrupt (INTR) F/F and inputs a "1" to the D flop, F/F1, which is at the input end of the 8-bit shift register. Internal clock signals then transfer this "1" to the Q output of F/F1. The AND gate, G1, combines this "1" output with a clock signal to provide a reset signal to the start F/F. If the set signal is no longer present (either WR or CS is a "1") the start F/F is reset and the 8-bit shift register then can have the "1" clocked in, which starts the conversion process. If the set signal were to still be present, this reset pulse would have no effect (both outputs of the start F/F would momentarily be at a "1" level) and the 8-bit shift register would continue to be held in the reset mode. This logic therefore allows for wide CS and WR signals and the converter will start after at least one of these signals returns high and the internal clocks again provide a reset signal for the start F/F.

Note 13: CS shown twice for clarity. Note 14: SAR = Successive Approximation Register

#### FIGURE 4. Block Diagram

After the "1" is clocked through the 8-bit shift register (which completes the SAR search) it appears as the input to the D-type latch, LATCH 1. As soon as this "1" is output from the shift register, the AND gate, G2, causes the new digital word to transfer to the TRI-STATE output latches. When LATCH 1 is subsequently enabled, the Q output makes a high-to-low transition which causes the INTR F/F to set. An inverting buffer then supplies the INTR input signal.

Note that this  $\overline{SET}$  control of the INTR F/F remains low for 8 of the external clock periods (as the internal clocks run at  $\frac{1}{16}$  of the frequency of the external clock). If the data output is continuously enabled ( $\overline{CS}$  and  $\overline{RD}$  both held low), the INTR output will still signal the end of conversion (by a high-to-low transition), because the  $\overline{SET}$  input can control the Q output of the INTR F/F even though the RESET input is constantly at a "1" level in this operating mode. This INTR output will therefore stay low for the duration of the SET signal, which is 8 periods of the external clock frequency (assuming the A/D is not started during this interval).

When operating in the free-running or continuous conversion mode (INTR pin tied to WR and CS wired low—see also section 2.8), the START F/F is SET by the high-to-low transition of the INTR signal. This resets the SHIFT REGISTER

which causes the input to the D-type latch, LATCH 1, to go low. As the latch enable input is still present, the  $\overline{Q}$  output will go high, which then allows the INTR F/F to be RESET. This reduces the width of the resulting INTR output pulse to only a few propagation delays (approximately 300 ns).

When data is to be read, the combination of both  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  being low will cause the INTR F/F to be reset and the TRI-STATE output latches will be enabled to provide the 8-bit digital outputs.

#### 2.1 Digital Control Inputs

The digital control inputs ( $\overline{CS}$ ,  $\overline{RD}$ , and  $\overline{WR}$ ) meet standard T<sup>2</sup>L logic voltage levels. These signals have been renamed when compared to the standard A/D Start and Output Enable labels. In addition, these inputs are active low to allow an easy interface to microprocessor control busses. For non-microprocessor based applications, the  $\overline{CS}$  input (pin 1) can be grounded and the standard A/D Start function is obtained by an active low pulse applied at the  $\overline{WR}$  input (pin 3) and the Output Enable function is caused by an active low pulse at the  $\overline{RD}$  input (pin 2).

#### 2.2 Analog Differential Voltage Inputs and Common-Mode Rejection

This A/D has additional applications flexibility due to the analog differential voltage input. The V<sub>IN</sub>(–) input (pin 7) can be used to automatically subtract a fixed voltage value from the input reading (tare correction). This is also useful in 4 mA–20 mA current loop conversion. In addition, common-mode noise can be reduced by use of the differential input.

The time interval between sampling V<sub>IN</sub>(+) and V<sub>IN</sub>(-) is 4-1/<sub>2</sub> clock periods. The maximum error voltage due to this slight time difference between the input voltage samples is given by:

$$\Delta V_{e}(MAX) = (V_{P}) (2\pi f_{cm}) \left(\frac{4.5}{f_{CLK}}\right)$$

where:

$\Delta V_e$  is the error voltage due to sampling delay

V<sub>P</sub> is the peak value of the common-mode voltage

$f_{\rm cm}$  is the common-mode frequency

As an example, to keep this error to 1/4 LSB ( $\sim 5$  mV) when operating with a 60 Hz common-mode frequency,  $f_{cm}$ , and using a 640 kHz A/D clock,  $f_{CLK}$ , would allow a peak value of the common-mode voltage,  $V_{\rm P}$ , which is given by:

$$V_{\mathsf{P}} = \frac{[\Delta V_{\mathsf{e}(\mathsf{MAX})} (\mathfrak{f}_{\mathsf{CLK}})]}{(2\pi \mathfrak{f}_{\mathsf{Cm}}) (4.5)}$$

or

$$V_{\rm P} = \frac{(5 \times 10^{-3}) (640 \times 10^3)}{(6.28) (60) (4.5)}$$

which gives

V<sub>P</sub>≅1.9V.

The allowed range of analog input voltages usually places more severe restrictions on input common-mode noise levels.

An analog input voltage with a reduced span and a relatively large zero offset can be handled easily by making use of the differential input (see section 2.4 Reference Voltage).

#### 2.3 Analog Inputs

#### 2.3 1 Input Current

#### Normal Mode

Due to the internal switching action, displacement currents will flow at the analog inputs. This is due to on-chip stray capacitance to ground as shown in *Figure 5*.

$r_{ON} \text{ of } SW 1 \text{ and } SW 2 \cong 5 \text{ } \text{k}\Omega$   $r = r_{ON} C_{STRAY} \cong 5 \text{ } \text{k}\Omega \text{ } \text{x} 12 \text{ } \text{pF} = 60 \text{ } \text{ns}$

FIGURE 5. Analog Input Impedance

The voltage on this capacitance is switched and will result in currents entering the V<sub>IN</sub>(+) input pin and leaving the V<sub>IN</sub>(-) input which will depend on the analog differential input voltage levels. These current transients occur at the leading edge of the internal clocks. They rapidly decay and *do not cause errors* as the on-chip comparator is strobed at the end of the clock period.

#### Fault Mode

If the voltage source applied to the V<sub>IN</sub>(+) or V<sub>IN</sub>(-) pin exceeds the allowed operating range of V<sub>CC</sub>+50 mV, large input currents can flow through a parasitic diode to the V<sub>CC</sub> pin. If these currents can exceed the 1 mA max allowed spec, an external diode (1N914) should be added to bypass this current to the V<sub>CC</sub> pin (with the current bypassed with this diode, the voltage at the V<sub>IN</sub>(+) pin can exceed the V<sub>CC</sub> voltage by the forward voltage of this diode).

#### 2.3.2 Input Bypass Capacitors

Bypass capacitors at the inputs will average these charges and cause a DC current to flow through the output resistances of the analog signal sources. This charge pumping action is worse for continuous conversions with the V<sub>IN</sub>(+) input voltage at full-scale. For continuous conversions with a 640 kHz clock frequency with the  $V_{\rm IN}(\text{+})$  input at 5V, this DC current is at a maximum of approximately 5 µA. Therefore, bypass capacitors should not be used at the analog inputs or the  $V_{BEE}/2$  pin for high resistance sources (> 1 k $\Omega$ ). If input bypass capacitors are necessary for noise filtering and high source resistance is desirable to minimize capacitor size, the detrimental effects of the voltage drop across this input resistance, which is due to the average value of the input current, can be eliminated with a full-scale adjustment while the given source resistor and input bypass capacitor are both in place. This is possible because the average value of the input current is a precise linear function of the differential input voltage.

#### 2.3.3 Input Source Resistance

Large values of source resistance where an input bypass capacitor is not used, *will not cause errors* as the input currents settle out prior to the comparison time. If a low pass filter is required in the system, use a low valued series resistor ( $\leq 1 \text{ k}\Omega$ ) for a passive RC section or add an op amp RC active low pass filter. For low source resistance applications, ( $\leq 1 \text{ k}\Omega$ ), a 0.1 µF bypass capacitor at the inputs will prevent noise pickup due to series lead inductance of a long wire. A

$100\Omega$  series resistor can be used to isolate this capacitor — both the R and C are placed outside the feedback loop — from the output of an op amp, if used.

#### 2.3.4 Noise

The leads to the analog inputs (pins 6 and 7) should be kept as short as possible to minimize input noise coupling. Both noise and undesired digital clock coupling to these inputs can cause system errors. The source resistance for these inputs should, in general, be kept below 5 kΩ. Larger values of source resistance can cause undesired system noise pickup. Input bypass capacitors, placed from the analog inputs to ground, will eliminate system noise pickup but can create analog scale errors as these capacitors will average the transient input switching currents of the A/D (see section 2.3.1.). This scale error depends on both a large source resistance and the use of an input bypass capacitor. This error can be eliminated by doing a full-scale adjustment of the A/D (adjust  $V_{\text{REF}}/2$  for a proper full-scale reading — see section 2.5.2 on Full-Scale Adjustment) with the source resistance and input bypass capacitor in place.

#### 2.4 Reference Voltage

#### 2.4.1 Span Adjust

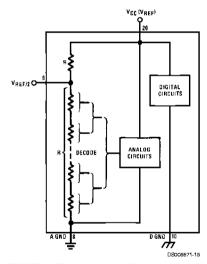

For maximum applications flexibility, these A/Ds have been designed to accommodate a 5  $V_{\rm DC}$ , 2.5  $V_{\rm DC}$  or an adjusted voltage reference. This has been achieved in the design of the IC as shown in *Figure 6*.

FIGURE 6. The V<sub>REFERENCE</sub> Design on the IC

Notice that the reference voltage for the IC is either  ${\rm V}_2$  of the voltage applied to the  $V_{\rm CC}$  supply pin, or is equal to the voltage that is externally forced at the  $V_{\rm REF}/2$  pin. This allows for a ratiometric voltage reference using the  $V_{\rm CC}$  supply, a 5  $V_{\rm DC}$  reference voltage can be used for the  $V_{\rm CC}$  supply or a voltage less than 2.5  $V_{\rm DC}$  can be applied to the  $V_{\rm REF}/2$  input for increased application flexibility. The internal gain to the  $V_{\rm REF}/2$  input is 2, making the full-scale differential input voltage twice the voltage at pin 9.

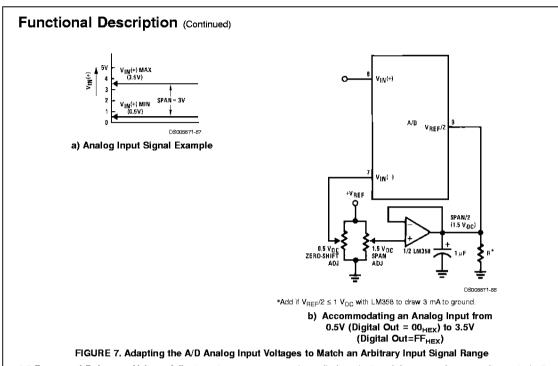

An example of the use of an adjusted reference voltage is to accommodate a reduced span — or dynamic voltage range of the analog input voltage. If the analog input voltage were to range from 0.5 V<sub>DC</sub> to 3.5 V<sub>DC</sub>, instead of 0V to 5 V<sub>DC</sub>, the span would be 3V as shown in *Figure* 7. With 0.5 V<sub>DC</sub> applied to the V<sub>IN</sub>(–) pin to absorb the offset, the reference voltage can be made equal to ½ of the 3V span or 1.5 V<sub>DC</sub>. The A/D now will encode the V<sub>IN</sub>(+) signal from 0.5V to 3.5 V with the 0.5V input corresponding to zero and the 3.5 V<sub>DC</sub> input corresponding to full-scale. The full 8 bits of resolution are therefore applied over this reduced analog input voltage range.

#### 2.4.2 Reference Accuracy Requirements

The converter can be operated in a ratiometric mode or an absolute mode. In ratiometric converter applications, the magnitude of the reference voltage is a factor in both the output of the source transducer and the output of the A/D converter and therefore cancels out in the final digital output code. The ADC0805 is specified particularly for use in ratiometric applications with no adjustments required. In absolute conversion applications, both the initial value and the temperature stability of the reference voltage are important factors in the accuracy of the A/D converter. For V<sub>REF</sub>/2 voltages of 2.4  $V_{DC}$  nominal value, initial errors of ±10 mV<sub>DC</sub> will cause conversion errors of ±1 LSB due to the gain of 2 of the VBEE/2 input. In reduced span applications, the initial value and the stability of the  $V_{\text{REF}}/2$  input voltage become even more important. For example, if the span is reduced to 2.5V, the analog input LSB voltage value is correspondingly reduced from 20 mV (5V span) to 10 mV and 1 LSB at the V<sub>REF</sub>/2 input becomes 5 mV. As can be seen, this reduces the allowed initial tolerance of the reference voltage and requires correspondingly less absolute change with temperature variations. Note that spans smaller than 2.5V place even tighter requirements on the initial accuracy and stability of the reference source.

In general, the magnitude of the reference voltage will require an initial adjustment. Errors due to an improper value of reference voltage appear as full-scale errors in the A/D transfer function. IC voltage regulators may be used for references if the ambient temperature changes are not excessive. The LM336B 2.5V IC reference diode (from National Semiconductor) has a temperature stability of 1.8 mV typ (6 mV max) over 0°C<T\_A<+70°C. Other temperature range parts are also available.

2.5 Errors and Reference Voltage Adjustments

#### 2.5.1 Zero Error

The zero of the A/D does not require adjustment. If the minimum analog input voltage value,  $V_{\rm IN(MIN)}$ , is not ground, a zero offset can be done. The converter can be made to output 0000 0000 digital code for this minimum input voltage by biasing the A/D  $V_{\rm IN}(-)$  input at this  $V_{\rm IN(MIN)}$  value (see Applications section). This utilizes the differential mode operation of the A/D.

The zero error of the A/D converter relates to the location of the first riser of the transfer function and can be measured by grounding the V<sub>IN</sub> (-) input and applying a small magnitude positive voltage to the V<sub>IN</sub> (+) input. Zero error is the difference between the actual DC input voltage that is necessary to just cause an output digital code transition from 0000 0000 to 0000 0001 and the ideal ½ LSB value (½ LSB = 9.8 mV for V<sub>REF</sub>/2=2.500 V<sub>DC</sub>).

#### 2.5.2 Full-Scale

The full-scale adjustment can be made by applying a differential input voltage that is 1% 2 LSB less than the desired analog full-scale voltage range and then adjusting the magnitude of the  $V_{\rm REF}/2$  input (pin 9 or the  $V_{\rm CC}$  supply if pin 9 is not used) for a digital output code that is just changing from 1111 1110 to 1111 1111.

# 2.5.3 Adjusting for an Arbitrary Analog Input Voltage Range

If the analog zero voltage of the A/D is shifted away from ground (for example, to accommodate an analog input signal that does not go to ground) this new zero reference should be properly adjusted first. A  $V_{\rm IN}(+)$  voltage that equals this desired zero reference plus ½ LSB (where the LSB is calculated for the desired analog span, 1 LSB=analog span/256)

is applied to pin 6 and the zero reference voltage at pin 7 should then be adjusted to just obtain the  $00_{\rm HEX}$  to  $01_{\rm HEX}$  code transition.

The full-scale adjustment should then be made (with the proper  $V_{\rm IN}(-)$  voltage applied) by forcing a voltage to the  $V_{\rm IN}(+)$  input which is given by:

$$V_{IN} (+) \text{ fs adj} = V_{MAX} - 1.5 \left[ \frac{(V_{MAX} - V_{MIN})}{256} \right]$$

where:

$V_{\mathsf{MAX}}\text{=}\mathsf{The}$  high end of the analog input range and

$V_{MIN}$ =the low end (the offset zero) of the analog range. (Both are ground referenced.)

The  $V_{\rm REF}/2$  (or  $V_{\rm CC})$  voltage is then adjusted to provide a code change from  ${\rm FE}_{\rm HEX}$  to  ${\rm FF}_{\rm HEX}$ . This completes the adjustment procedure.

#### 2.6 Clocking Option

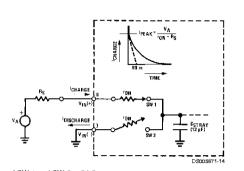

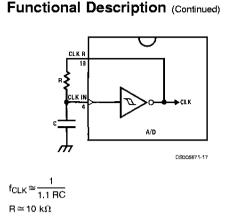

The clock for the A/D can be derived from the CPU clock or an external RC can be added to provide self-clocking. The CLK IN (pin 4) makes use of a Schmitt trigger as shown in *Figure 8.*

#### FIGURE 8. Self-Clocking the A/D

Heavy capacitive or DC loading of the clock R pin should be avoided as this will disturb normal converter operation. Loads less than 50 pF, such as driving up to 7 A/D converter clock inputs from a single clock R pin of 1 converter, are allowed. For larger clock line loading, a CMOS or low power TTL buffer or PNP input logic should be used to minimize the loading on the clock R pin (do not use a standard TTL buffer).

#### 2.7 Restart During a Conversion

If the A/D is restarted ( $\overline{CS}$  and  $\overline{WR}$  go low and return high) during a conversion, the converter is reset and a new conversion is started. The output data latch is not updated if the conversion in process is not allowed to be completed, therefore the data of the previous conversion remains in this latch. The INTR output simply remains at the "1" level.

#### 2.8 Continuous Conversions

For operation in the free-running mode an initializing pulse should be used, following power-up, to ensure circuit operation. In this application, the  $\overline{CS}$  input is grounded and the  $\overline{WR}$  input is tied to the  $\overline{INTR}$  output. This  $\overline{WR}$  and  $\overline{INTR}$  node should be momentarily forced to logic low following a power-up cycle to guarantee operation.

#### 2.9 Driving the Data Bus

This MOS A/D, like MOS microprocessors and memories, will require a bus driver when the total capacitance of the data bus gets large. Other circuitry, which is tied to the data bus, will add to the total capacitive loading, even in TRI-STATE (high impedance mode). Backplane bussing also greatly adds to the stray capacitance of the data bus.

There are some alternatives available to the designer to handle this problem. Basically, the capacitive loading of the data bus slows down the response time, even though DC specifications are still met. For systems operating with a relatively slow CPU clock frequency, more time is available in which to establish proper logic levels on the bus and therefore higher capacitive loads can be driven (see typical characteristics curves).

At higher CPU clock frequencies time can be extended for I/O reads (and/or writes) by inserting wait states (8080) or using clock extending circuits (6800).

Finally, if time is short and capacitive loading is high, external bus drivers must be used. These can be TRI-STATE buffers (low power Schottky such as the DM74LS240 series is recommended) or special higher drive current products which are designed as bus drivers. High current bipolar bus drivers with PNP inputs are recommended.

#### 2.10 Power Supplies

Noise spikes on the V<sub>CC</sub> supply line can cause conversion errors as the comparator will respond to this noise. A low inductance tantalum filter capacitor should be used close to the converter V<sub>CC</sub> pin and values of 1 µF or greater are recommended. If an unregulated voltage is available in the system, a separate LM340LAZ-5.0, TO-92, 5V voltage regulator for the converter (and other analog circuitry) will greatly reduce digital noise on the V<sub>CC</sub> supply.

#### 2.11 Wiring and Hook-Up Precautions

Standard digital wire wrap sockets are not satisfactory for breadboarding this A/D converter. Sockets on PC boards can be used and all logic signal wires and leads should be grouped and kept as far away as possible from the analog signal leads. Exposed leads to the analog inputs can cause undesired digital noise and hum pickup, therefore shielded leads may be necessary in many applications.

A single point analog ground that is separate from the logic ground points should be used. The power supply bypass capacitor and the self-clocking capacitor (if used) should both be returned to digital ground. Any  $V_{\text{REF}}/2$  bypass capacitors, analog input filter capacitors, or input signal shielding should be returned to the analog ground point. A test for proper grounding is to measure the zero error of the A/D converter. Zero errors in excess of  $\frac{1}{4}$  LSB can usually be traced to improper board layout and wiring (see section 2.5.1 for measuring the zero error).

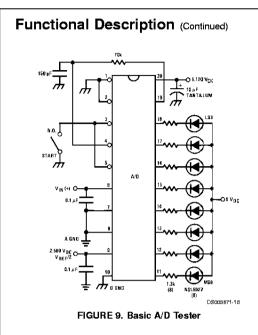

#### 3.0 TESTING THE A/D CONVERTER

There are many degrees of complexity associated with testing an A/D converter. One of the simplest tests is to apply a known analog input voltage to the converter and use LEDs to display the resulting digital output code as shown in *Figure 9*. For ease of testing, the  $V_{\rm REF}/2$  (pin 9) should be supplied with 2.560 V<sub>DC</sub> and a V<sub>CC</sub> supply voltage of 5.12 V<sub>DC</sub> should be used. This provides an LSB value of 20 mV.

If a full-scale adjustment is to be made, an analog input voltage of 5.090 V<sub>DC</sub> (5.120–1½ LSB) should be applied to the V<sub>IN</sub>(+) pin with the V<sub>IN</sub>(-) pin grounded. The value of the V<sub>REF</sub>/2 input voltage should then be adjusted until the digital output code is just changing from 1111 1110 to 1111 1111. This value of V<sub>REF</sub>/2 should then be used for all the tests.

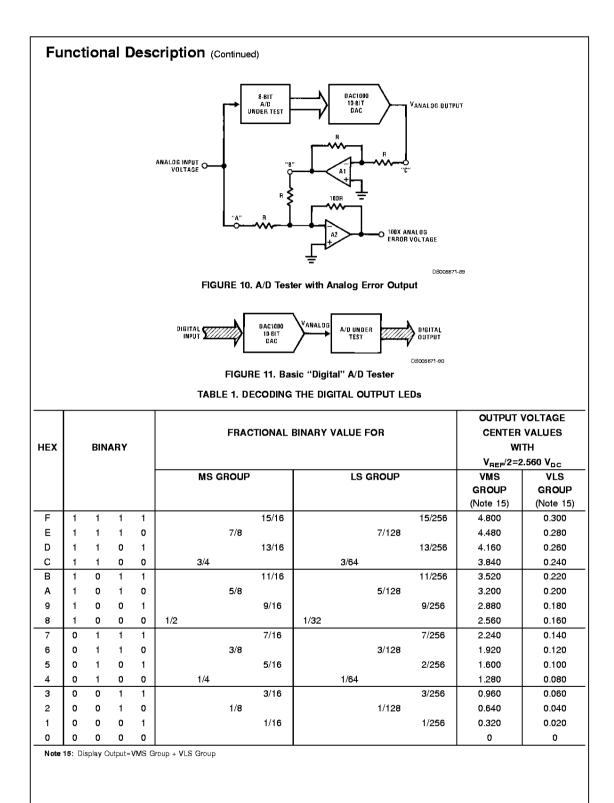

The digital output LED display can be decoded by dividing the 8 bits into 2 hex characters, the 4 most significant (MS) and the 4 least significant (LS). *Table 1* shows the fractional binary equivalent of these two 4-bit groups. By adding the voltages obtained from the "VMS" and "VLS" columns in *Table 1*, the nominal value of the digital display (when  $V_{\rm REF}/2 = 2.560$ V) can be determined. For example, for an output LED display of 1011 0110 or B6 (in hex), the voltage values from the table are 3.520 + 0.120 or 3.640 V<sub>DC</sub>. These voltage values represent the center-values of a perfect A/D counter. The effects of quantization error have to be accounted for in the interpretation of the test results.

For a higher speed test system, or to obtain plotted data, a digital-to-analog converter is needed for the test set-up. An accurate 10-bit DAC can serve as the precision voltage source for the A/D. Errors of the A/D under test can be expressed as either analog voltages or differences in 2 digital words.

A basic A/D tester that uses a DAC and provides the error as an analog output voltage is shown in *Figure 8*. The 2 op amps can be eliminated if a lab DVM with a numerical subtraction feature is available to read the difference voltage, "A-C", directly. The analog input voltage can be supplied by a low frequency ramp generator and an X-Y plotter can be used to provide analog error (Y axis) versus analog input (X axis).

For operation with a microprocessor or a computer-based test system, it is more convenient to present the errors digitally. This can be done with the circuit of *Figure 11*, where the output code transitions can be detected as the 10-bit DAC is incremented. This provides  $\frac{1}{4}$  LSB steps for the 8-bit A/D under test. If the results of this test are automatically plotted with the analog input on the X axis and the error (in LSB's) as the Y axis, a useful transfer function of the A/D under test results. For acceptance testing, the plot is not necessary and the testing speed can be increased by establishing internal limits on the allowed error for each code.

#### 4.0 MICROPROCESSOR INTERFACING

To dicuss the interface with 8080A and 6800 microprocessors, a common sample subroutine structure is used. The microprocessor starts the A/D, reads and stores the results of 16 successive conversions, then returns to the user's program. The 16 data bytes are stored in 16 successive memory locations. All Data and Addresses will be given in hexadecimal form. Software and hardware details are provided separately for each type of microprocessor.

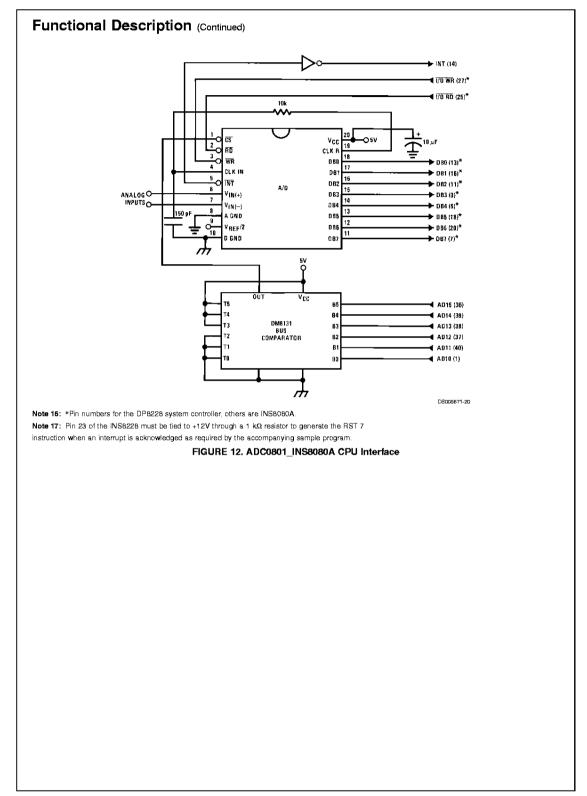

# 4.1 Interfacing 8080 Microprocessor Derivatives (8048, 8085)

This converter has been designed to directly interface with derivatives of the 8080 microprocessor. The A/D can be mapped into memory space (using standard memory address decoding for  $\overline{CS}$  and the MEMR and MEMW strobes) or it can be controlled as an I/O device by using the  $\overline{I/OR}$  and  $\overline{I/OW}$  strobes and decoding the address bits A0  $\rightarrow$  A7 (or address bits A8  $\rightarrow$  A15 as they will contain the same 8-bit address information) to obtain the  $\overline{CS}$  input. Using the I/O space provides 256 additional addresses and may allow a simpler 8-bit address decoder but the data can only be input to the accumulator. To make use of the additional memory reference instructions, the A/D should be mapped into memory space. An example of an A/D in I/O space is shown in *Figure 12*.

| unctic | onal Desc | ription (Continued) |                      |                                     |

|--------|-----------|---------------------|----------------------|-------------------------------------|

|        | SA        | MPLE PROGRAM FOR    | Figure 12 ADC0801–IN | IS8080A CPU INTERFACE               |

| 0038   | C3 00 03  | RST 7:              | JMP LD DATA          |                                     |

| •      | •         | •                   |                      |                                     |

| •      | •         | •                   |                      |                                     |

| 0100   | 21 00 02  | START:              | LXI H 0200H          | ; HL pair will point to             |

|        |           |                     |                      | ; data storage locations            |

| 0103   | 31 00 04  | RETURN:             | LXI SP 0400H         | ; Initialize stack pointer (Note 1) |

| 0106   | 7D        |                     | MOVA, L              | ; Test # of bytes entered           |

| 0107   | FE OF     |                     | CPI OF H             | ; If # = 16. JMP to                 |

| 0109   | CA 13 01  |                     | JZ CONT              | ;userprogram                        |

| 0100   | D3 E0     |                     | OUT EO H             | ; Start A/D                         |

| 010E   | FB        |                     | EI                   | ;Enable interrupt                   |

| 010F   | 00        | L00P:               | NOP                  | ; Loop until end of                 |

| 0110   | C3 OF 01  |                     | JMP LOOP             | ; conversion                        |

| 0113   | •         | CONT:               | •                    |                                     |

| •      | •         | •                   | •                    |                                     |

| •      | •         | (User program to    | •                    |                                     |

| •      | •         | process data)       | •                    |                                     |

| •      | •         | •                   | •                    |                                     |

| •      | •         | •                   | •                    |                                     |

| 0300   | DB EO     | LD DATA:            | IN EO H              | ; Load data into accumulator        |

| 0302   | 77        |                     | MOV M, A             | ; Store data                        |

| 0303   | 23        |                     | INXH                 | ; Increment storage pointer         |

| 0304   | C3 03 01  |                     | JMP RETURN           |                                     |

DS005571-99

Note 18: The stack pointer must be dimensioned because a RST 7 instruction pushes the PC onto the stack.

Note 19: All address used were arbitrarily chosen.

The standard control bus signals of the 8080  $\overline{CS}$ ,  $\overline{RD}$  and  $\overline{WR}$ ) can be directly wired to the digital control inputs of the A/D and the bus timing requirements are met to allow both starting the converter and outputting the data onto the data bus. A bus driver should be used for larger microprocessor systems where the data bus leaves the PC board and/or must drive capacitive loads larger than 100 pF.

# 4.1.1 Sample 8080A CPU Interfacing Circuitry and Program

The following sample program and associated hardware shown in *Figure 12* may be used to input data from the converter to the INS8080A CPU chip set (comprised of the INS8080A microprocessor, the INS8228 system controller and the INS8224 clock generator). For simplicity, the *A/D* is controlled as an I/O device, specifically an 8-bit bi-directional port located at an arbitrarily chosen port address, E0. The TRI-STATE output capability of the A/D eliminates the need for a peripheral interface device, however address decoding is still required to generate the appropriate  $\overline{CS}$  for the converter.

It is important to note that in systems where the A/D converter is 1-of-8 or less I/O mapped devices, no address decoding circuitry is necessary. Each of the 8 address bits (A0 to A7) can be directly used as  $\overline{\text{CS}}$  inputs—one for each I/O device.

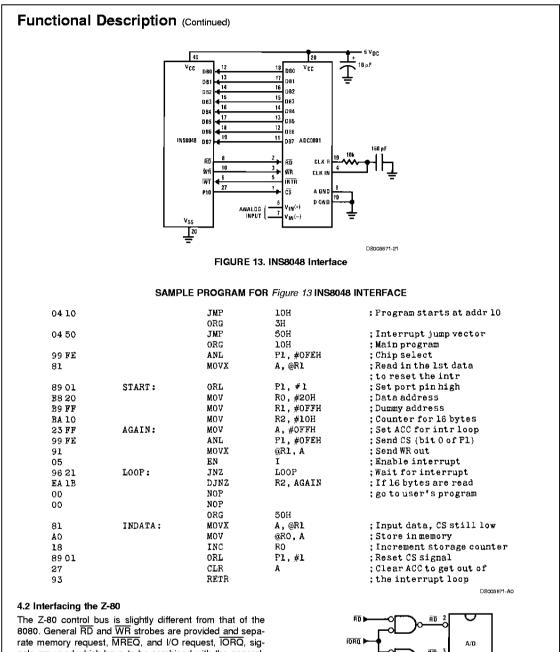

#### 4.1.2 INS8048 Interface

The INS8048 interface technique with the ADC0801 series (see *Figure 13*) is simpler than the 8080A CPU interface. There are 24 I/O lines and three test input lines in the 8048. With these extra I/O lines available, one of the I/O lines (bit 0 of port 1) is used as the chip select signal to the A/D, thus eliminating the use of an external address decoder. Bus control signals  $\overline{RD}$ ,  $\overline{WR}$  and  $\overline{INT}$  of the 8048 are tied directly to the A/D. The 16 converted data words are stored at on-chip RAM locations from 20 to 2F (Hex). The  $\overline{RD}$  and  $\overline{WR}$  signals are generated by reading from and writing into a dummy address, respectively. A sample interface program is shown below.

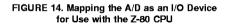

rate memory request, MREQ, and I/O request, IORQ, sigrate memory request, MREQ, and I/O request, IORQ, signals are used which have to be combined with the generalized strobes to provide the equivalent 8080 signals. An advantage of operating the A/D in I/O space with the Z-80 is that the CPU will automatically insert one wait state (the RD and WR strobes are extended one clock period) to allow more time for the I/O devices to respond. Logic to map the A/D in I/O space is shown in *Figure 14*.

DS005571-23

1032

WB

Additional I/O advantages exist as software DMA routines are available and use can be made of the output data transfer which exists on the upper 8 address lines (A8 to A15) dur-

www.national.com

ing I/O input instructions. For example, MUX channel selection for the A/D can be accomplished with this operating mode.

# 4.3 Interfacing 6800 Microprocessor Derivatives (6502, etc.)

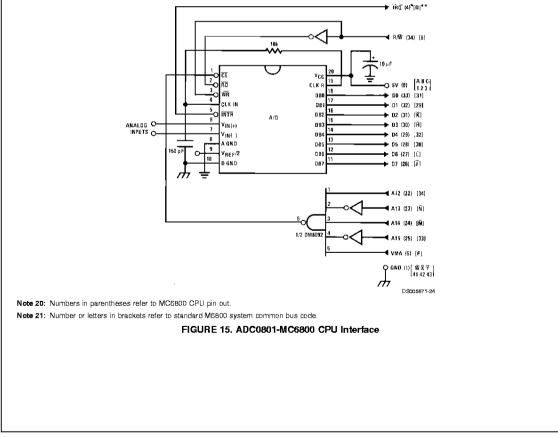

The control bus for the 6800 microprocessor derivatives does not use the  $\overline{RD}$  and  $\overline{WR}$  strobe signals. Instead it employs a single R/W line and additional timing, if needed, can be derived fom the  $\phi$ 2 clock. All I/O devices are memory mapped in the 6800 system, and a special signal, VMA, indicates that the current address is valid. *Figure 15* shows an interface schematic where the A/D is memory mapped in the 6800 system. For simplicity, the  $\overline{CS}$  decoding is shown using  $\frac{V_2}{DM8092}$ . Note that in many 6800 systems, an already decoded  $\overline{4/5}$  line is brought out to the common bus at pin 21. This can be tied directly to the  $\overline{CS}$  pin of the A/D, provided that no other devices are addressed at HX ADDR: 4XXX or 5XXX.

The following subroutine performs essentially the same function as in the case of the 8080A interface and it can be called from anywhere in the user's program.

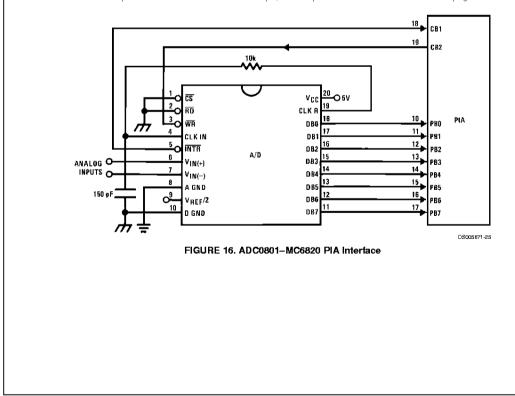

In *Figure 16* the ADC0801 series is interfaced to the M6800 microprocessor through (the arbitrarily chosen) Port B of the MC6820 or MC6821 Peripheral Interface Adapter, (PIA). Here the  $\overline{\text{CS}}$  pin of the A/D is grounded since the PIA is al-

ready memory mapped in the M6800 system and no  $\overline{CS}$  decoding is necessary. Also notice that the A/D output data lines are connected to the microprocessor bus under program control through the PIA and therefore the A/D  $\overline{RD}$  pin can be grounded.

A sample interface program equivalent to the previous one is shown below *Figure 16*. The PIA Data and Control Registers of Port B are located at HEX addresses 8006 and 8007, respectively.

### 5.0 GENERAL APPLICATIONS

The following applications show some interesting uses for the A/D. The fact that one particular microprocessor is used is not meant to be restrictive. Each of these application circuits would have its counterpart using any microprocessor that is desired.

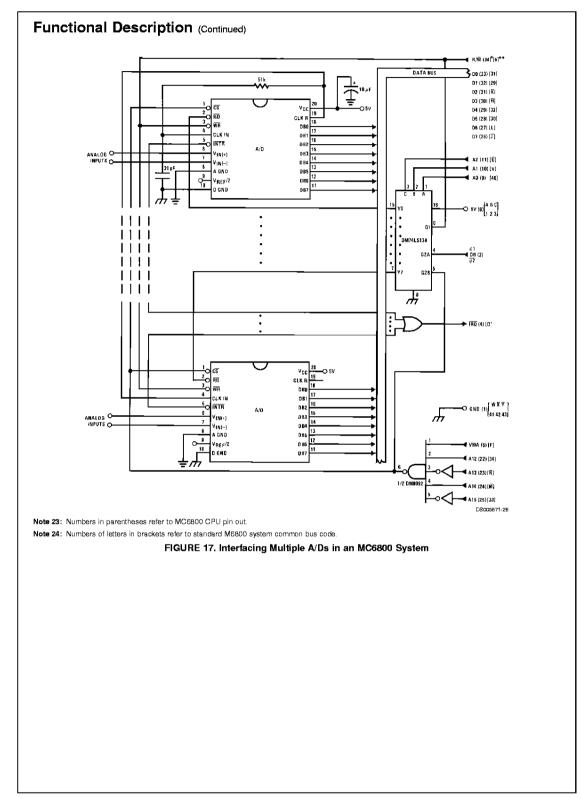

#### 5.1 Multiple ADC0801 Series to MC6800 CPU Interface

To transfer analog data from several channels to a single microprocessor system, a multiple converter scheme presents several advantages over the conventional multiplexer single-converter approach. With the ADC0801 series, the differential inputs allow individual span adjustment for each channel. Furthermore, all analog input channels are sensed simultaneously, which essentially divides the microprocessor's total system servicing time by the number of channels, since all conversions occur simultaneously. This scheme is shown in *Figure 17*.

| 0010 | DF 36    | DATAIN | STX  | TEMP2   | ; Save contents of X    |

|------|----------|--------|------|---------|-------------------------|

| 0012 | CE 00 2C |        | LDX  | #\$002C | ; Upon IRQ low CPU      |

| 0015 | FF FF F8 |        | STX  | \$FFF8  | ; jumps to 002C         |

| 0018 | B7 50 00 |        | STAA | \$5000  | ; Start ADC0801         |

| 001B | OE       |        | CLI  |         |                         |

| 0010 | 3E       | CONVRT | WAI  |         | ;Wait for interrupt     |

| 001D | DE 34    |        | LDX  | TEMP1   |                         |

| 001F | 8C 02 0F |        | CPX  | #\$020F | ; Is final data stored? |

| 0022 | 27 14    |        | BEQ  | ENDP    |                         |

| 0024 | B7 50 00 |        | STAA | \$5000  | ; Restarts ADC0801      |

| 0027 | 08       |        | INX  |         |                         |

| 0028 | DF 34    |        | STX  | TEMP1   |                         |

| 002A | 20 F0    |        | BRA  | CONVRT  |                         |

| 0020 | DE 34    | INTRPT | LDX  | TEMP1   |                         |

| 002E | B6 50 00 |        | LDAA | \$5000  | ; Read data             |

| 0031 | A7 00    |        | STAA | Х       | ;Store it at X          |

| 0033 | 3B       |        | RTI  |         |                         |

| 0034 | 02 00    | TEMP1  | FDB  | \$0200  | ; Starting address for  |

|      |          |        |      |         | ; data storage          |

| 0036 | 00 00    | TEMP2  | FDB  | \$0000  |                         |

| 0038 | CE 02 00 | ENDP   | LDX  | #\$0200 | ;Reinitialize TEMP1     |

| 003B | DF 34    |        | STX  | TEMP1   |                         |

| 003D | DE 36    |        | LDX  | TEMP2   |                         |

| 003F | 39       |        | RTS  |         | ; Return from subroutin |

|      |          |        |      |         | ;Touser's program       |

DS005571-A1

Note 22: In order for the microprocessor to service subroutines and interrupts, the stack pointer must be dimensioned in the user's program.

SAMPLE PROGRAM FOR Figure 16 ADC0801-MC6820 PIA INTERFACE

|      |          |        | 5    |         |                            |

|------|----------|--------|------|---------|----------------------------|

| 0010 | CE 00 38 | DATAIN | LDX  | #\$0038 | ; Upon IRQ low CPU         |

| 0013 | FF FF F8 |        | STX  | \$FFF8  | ; jumps to 0038            |

| 0016 | B6 80 06 |        | LDAA | PIAORB  | ; Clear possible IRQ flags |

| 0019 | 4F       |        | CLRA |         |                            |

| 001A | B7 80 07 |        | STAA | PIACRB  |                            |

| 001D | B7 80 06 |        | STAA | PIAORB  | ; Set Port Bas input       |

| 0020 | OE       |        | CLI  |         |                            |

| 0021 | C6 34    |        | LDAB | #\$34   |                            |

| 0023 | 86 3D    |        | LDAA | #\$3D   |                            |

| 0025 | F7 80 07 | CONVRT | STAB | PIACRB  | ; Starts ADCO801           |

| 0028 | B7 80 07 |        | STAA | PIACRB  |                            |

| 002B | 3E       |        | WAI  |         | ;Wait for interrupt        |

| 0020 | DE 40    |        | LDX  | TEMP1   |                            |

| 002E | 8C 02 0F |        | CPX  | #\$020F | ; Is final data stored?    |

| 0031 | 27 OF    |        | BEQ  | ENDP    |                            |

| 0033 | 08       |        | INX  |         |                            |

| 0034 | DF 40    |        | STX  | TEMP1   |                            |

| 0036 | 20 ED    |        | BRA  | CONVRT  |                            |

| 0038 | DE 40    | INTRPT | LDX  | TEMPL   |                            |

| 003A | B6 80 06 |        | LDAA | PIAORB  | ;Read data in              |

| 003D | A7 00    |        | STAA | х       | ; Store it at X            |

| 003F | 3B       |        | RTI  |         |                            |

| 0040 | 02 00    | TEMP1  | FDB  | \$0200  | ; Starting address for     |

|      |          |        |      |         | ; data storage             |

| 0042 | CE 02 00 | ENDP   | LDX  | #\$0200 | ;Reinitialize TEMP1        |

| 0045 | DF 40    |        | STX  | TEMPL   |                            |

| 0047 | 39       |        | RTS  |         | ; Return from Subroutine   |

|      |          | PIAORB | EQU  | \$8006  | ;To user's program         |

|      |          | PIACRB | EQU  | \$8007  | -                          |

|      |          |        | -    |         | DS005571-A2                |

|      |          |        |      |         |                            |

The following schematic and sample subroutine (DATA IN) may be used to interface (up to) 8 ADC0801's directly to the MC6800 CPU. This scheme can easily be extended to allow the interface of more converters. In this configuration the converters are (arbitrarily) located at HEX address 5000 in the MC6800 memory space. To save components, the clock signal is derived from just one RC pair on the first converter. This output drives the other A/Ds.

All the converters are started simultaneously with a STORE instruction at HEX address 5000. Note that any other HEX address of the form 5XXX will be decoded by the circuit, pulling all the  $\overline{CS}$  inputs low. This can easily be avoided by using a more definitive address decoding scheme. All the interrupts are ORed together to insure that all A/Ds have completed their conversion before the microprocessor is interrupted.

The subroutine, DATA IN, may be called from anywhere in the user's program. Once called, this routine initializes the

CPU, starts all the converters simultaneously and waits for the interrupt signal. Upon receiving the interrupt, it reads the converters (from HEX addresses 5000 through 5007) and stores the data successively at (arbitrarily chosen) HEX addresses 0200 to 0207, before returning to the user's program. All CPU registers then recover the original data they had before servicing DATA IN.

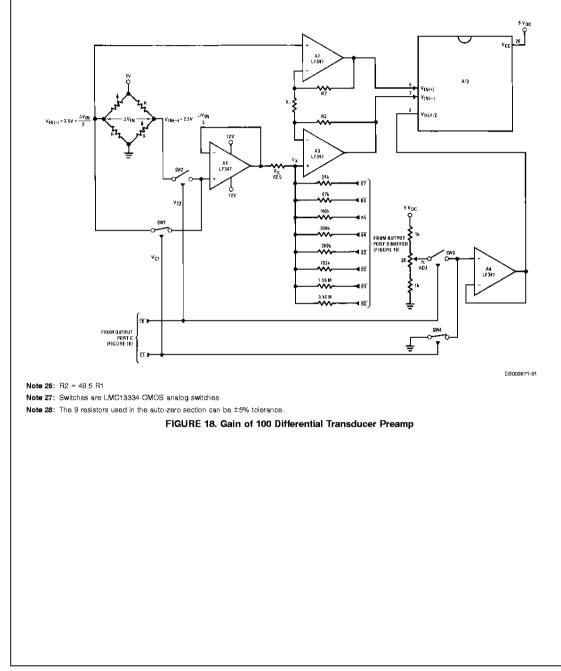

# 5.2 Auto-Zeroed Differential Transducer Amplifier and A/D Converter

The differential inputs of the ADC0801 series eliminate the need to perform a differential to single ended conversion for a differential transducer. Thus, one op amp can be eliminated since the differential to single ended conversion is provided by the differential input of the ADC0801 series. In general, a transducer preamp is required to take advantage of the full A/D converter input dynamic range.

| unctional Description (Continued)                                           |          |        |           |         |                             |  |  |  |  |  |

|-----------------------------------------------------------------------------|----------|--------|-----------|---------|-----------------------------|--|--|--|--|--|

| SAMPLE PROGRAM FOR Figure 17 INTERFACING MULTIPLE A/D'S IN AN MC6800 SYSTEM |          |        |           |         |                             |  |  |  |  |  |

| ADDRESS                                                                     | HEX CODE |        | MNEMONICS |         | COMMENTS                    |  |  |  |  |  |

| 0010                                                                        | DF 44    | DATAIN | STX       | TEMP    | ; Save Contents of X        |  |  |  |  |  |

| 0012                                                                        | CE 00 2A |        | LDX       | #\$002A | ; Upon IRQ LOW CPU          |  |  |  |  |  |

| 0015                                                                        | FF FF F8 |        | STX       | \$FFF8  | ; Jumps to 002A             |  |  |  |  |  |

| 0018                                                                        | B7 50 00 |        | STAA      | \$5000  | ;Starts all A/D's           |  |  |  |  |  |

| 001B                                                                        | OE       |        | CLI       |         |                             |  |  |  |  |  |

| 0010                                                                        | 3E       |        | WAI       |         | ;Wait for interrupt         |  |  |  |  |  |

| 001D                                                                        | CE 50 00 |        | LDX       | #\$5000 |                             |  |  |  |  |  |

| 0020                                                                        | DF 40    |        | STX       | INDEX1  | ; Reset both INDEX          |  |  |  |  |  |

| 0022                                                                        | CE 02 00 |        | LDX       | #\$0200 | ; 1 and 2 to starting       |  |  |  |  |  |

| 0025                                                                        | DF 42    |        | STX       | INDEX2  | ; addresses                 |  |  |  |  |  |

| 0027                                                                        | DE 44    |        | LDX       | TEMP    |                             |  |  |  |  |  |

| 0029                                                                        | 39       |        | RTS       |         | ; Return from subroutine    |  |  |  |  |  |

| 002A                                                                        | DE 40    | INTRPT | LDX       | INDEX1  | ; INDEX1 $\rightarrow$ X    |  |  |  |  |  |

| 0020                                                                        | A6 00    |        | LDAA      | Х       | ;Read data in from A/D at X |  |  |  |  |  |

| 002E                                                                        | 08       |        | INX       |         | ; Increment X by one        |  |  |  |  |  |

| 002F                                                                        | DF 40    |        | STX       | INDEX1  | $; x \rightarrow indexi$    |  |  |  |  |  |

| 0031                                                                        | DE 42    |        | LDX       | INDEX2  | ; INDEX2 $\rightarrow$ X    |  |  |  |  |  |

DS005571-A3

#### SAMPLE PROGRAM FOR Figure 17 INTERFACING MULTIPLE A/D's IN AN MC6800 SYSTEM

| ADDRESS | HEX CODE |        | MNEMONICS |         | COMMENTS                            |

|---------|----------|--------|-----------|---------|-------------------------------------|

| 0033    | A7 00    |        | STAA      | х       | ; Store data at X                   |

| 0035    | 80 02 07 |        | CPX       | #\$0207 | ;Have all A/D's been read?          |

| 0038    | 27 05    |        | BEQ       | RETURN  | ; Yes: branch to RETURN             |

| 003A    | 08       |        | INX       |         | ; No : increment X by one           |

| 003B    | DF 42    |        | STX       | INDEX2  | $; x \rightarrow $ INDEX2           |

| 003D    | 20 EB    |        | BRA       | INTRPT  | ; Branch to 002A                    |

| 003F    | 3B       | RETURN | RTI       |         |                                     |

| 0040    | 50 00    | INDEX1 | FDB       | \$5000  | ; Starting address for A/D          |

| 0042    | 02 00    | INDEX2 | FDB       | \$0200  | ; Starting address for data storage |

| 0044    | 00 00    | TEMP   | FDB       | \$0000  |                                     |

DS005571-A4

Note 25: In order for the microprocessor to service subroutines and interrupts, the stack pointer must be dimensioned in the user's program

For amplification of DC input signals, a major system error is the input offset voltage of the amplifiers used for the preamp. Figure 18 is a gain of 100 differential preamp whose offset voltage errors will be cancelled by a zeroing subroutine which is performed by the INS8080A microprocessor system. The total allowable input offset voltage error for this preamp is only 50 µV for 1/4 LSB error. This would obviously require very precise amplifiers. The expression for the differential output voltage of the preamp is:

$$V_{O} = [V_{IN}(+) - V_{IN}(-)] \begin{bmatrix} 1 + \frac{2R2}{R1} \end{bmatrix} +$$

$$\underbrace{V_{OS_2} - V_{OS_1} - V_{OS_3} \pm I_XR_X}_{DC \text{ ERBOB TERM}} \begin{pmatrix} 1 + \frac{2R2}{R1} \end{bmatrix}$$

where  $I_X$  is the current through resistor  $R_X$ . All of the offset error terms can be cancelled by making  $\pm I_X R_X = V_{OS1}$  +  $V_{\rm OS3}$  -  $V_{\rm OS2}.$  This is the principle of this auto-zeroing scheme.

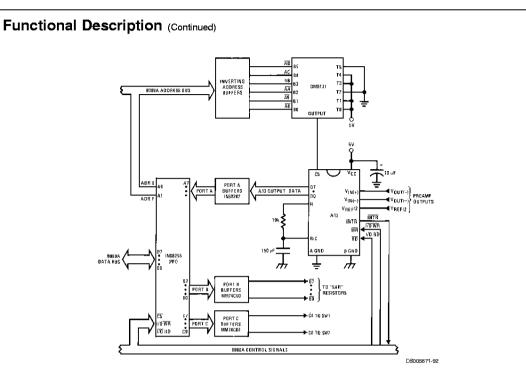

The INS8080A uses the 3 I/O ports of an INS8255 Programable Peripheral Interface (PPI) to control the auto zeroing and input data from the ADC0801 as shown in Figure 19. The PPI is programmed for basic I/O operation (mode 0) with Port A being an input port and Ports B and C being output ports. Two bits of Port C are used to alternately open or close the 2 switches at the input of the preamp. Switch SW1 is closed to force the preamp's differential input to be zero during the zeroing subroutine and then opened and SW2 is then closed for conversion of the actual differential input signal. Using 2 switches in this manner eliminates concern for the ON resistance of the switches as they must conduct only the input bias current of the input amplifiers.

Output Port B is used as a successive approximation register by the 8080 and the binary scaled resistors in series with each output bit create a D/A converter. During the zeroing subroutine, the voltage at  $V_{\rm \times}$  increases or decreases as required to make the differential output voltage equal to zero. This is accomplished by ensuring that the voltage at the output of A1 is approximately 2.5V so that a logic "1" (5V) on

any output of Port B will source current into node V<sub>X</sub> thus raising the voltage at V<sub>X</sub> and making the output differential more negative. Conversely, a logic "0" (0V) will pull current out of node V<sub>X</sub> and decrease the voltage, causing the differential output to become more positive. For the resistor values shown, V<sub>X</sub> can move  $\pm 12$  mV with a resolution of 50  $\mu$ V, which will null the offset error term to 1/4 LSB of full-scale for

the ADC0801. It is important that the voltage levels that drive the auto-zero resistors be constant. Also, for symmetry, a logic swing of 0V to 5V is convenient. To achieve this, a CMOS buffer is used for the logic output signals of Port B and this CMOS package is powered with a stable 5V source. Buffer amplifier A1 is necessary so that it can source or sink the D/A output current.

FIGURE 19. Microprocessor Interface Circuitry for Differential Preamp

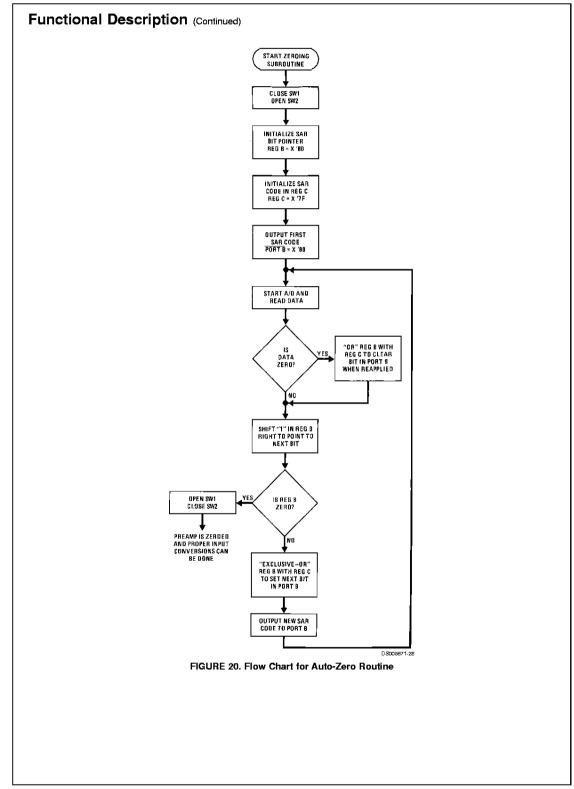

A flow chart for the zeroing subroutine is shown in *Figure 20*. It must be noted that the ADC0801 series will output an all zero code when it converts a negative input [V<sub>IN</sub>(-)  $\geq$  V<sub>IN</sub>(+)]. Also, a logic inversion exists as all of the I/O ports are buffered with inverting gates.

Basically, if the data read is zero, the differential output voltage is negative, so a bit in Port B is cleared to pull  $V_X$  more negative which will make the output more positive for the next conversion. If the data read is not zero, the output voltage is positive so a bit in Port B is set to make  $V_X$  more positive and the output more negative. This continues for 8 approximations and the differential output eventually converges to within 5 mV of zero.

The actual program is given in *Figure 21*. All addresses used are compatible with the BLC 80/10 microcomputer system. In particular:

- Port A and the ADC0801 are at port address E4

- Port B is at port address E5

- Port C is at port address E6

- PPI control word port is at port address E7

Program Counter automatically goes to ADDR:3C3D upon acknowledgement of an interrupt from the ADC0801

#### 5.3 Multiple A/D Converters in a Z-80 Interrupt Driven Mode

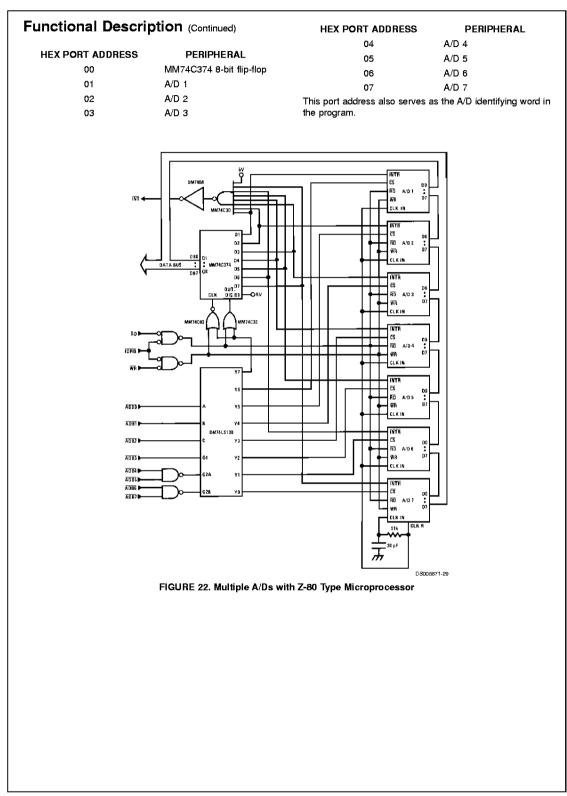

In data acquisition systems where more than one A/D converter (or other peripheral device) will be interrupting program execution of a microprocessor, there is obviously a need for the CPU to determine which device requires servicing. *Figure 22* and the accompanying software is a method of determining which of 7 ADC0801 converters has completed a conversion (INTR asserted) and is requesting an interrupt. This circuit allows starting the A/D converters in any sequence, but will input and store valid data from the converters with a priority sequence of A/D 1 being read first, A/D 2 second, etc., through A/D 7 which would have the lowest priority for data being read. Only the converters whose INT is asserted will be read.

The key to decoding circuitry is the DM74LS373, 8-bit D type flip-flop. When the Z-80 acknowledges the interrupt, the program is vectored to a data input Z-80 subroutine. This subroutine will read a peripheral status word from the DM74LS373 which contains the logic state of the  $\overline{\rm INTR}$  outputs of all the converters. Each converter which initiates an interrupt will place a logic "0" in a unique bit position in the status word and the subroutine will determine the identity of the converter and execute a data read. An identifier word (which indicates which A/D the data came from) is stored in the next sequential memory location above the location of the data so the program can keep track of the identity of the data entered.

| 3D00         | 3E90                         | MVI 90                                                            |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |