# **ADC701 SHC702**

# 16-Bit 512kHz SAMPLING A/D CONVERTER SYSTEM

## **FEATURES**

- CONVERSION RATE: to 512kHz Over Temp

- NO MISSING CODES AT 16 BITS

- SPURIOUS-FREE DYNAMIC RANGE: 107dB

- LOW NONLINEARITY: ±0.0015%

- ◆ SELECTABLE INPUT RANGES: ±5V, ±10V, 0 to +10V, 0 to +5V, -10V to 0

- LOW POWER DISSIPATION: 2.8W Typical Including Sample/Hold

- METAL AND CERAMIC DIP PACKAGES

## **APPLICATIONS**

- MEDICAL IMAGING

- SONAR

- PROFESSIONAL AUDIO RECORDING

- AUTOMATIC TEST EQUIPMENT

- HIGH PERFORMANCE FFT SPECTRUM ANALYSIS

- ULTRASOUND SIGNAL PROCESSING

- HIGH SPEED DATA ACQUISITION

- REPLACES DISCRETE MODULAR ADCs

## DESCRIPTION

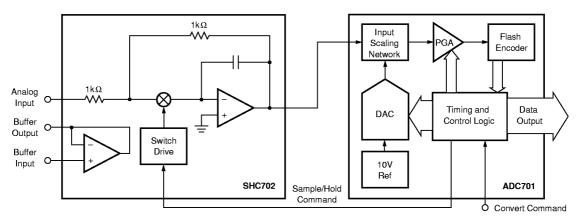

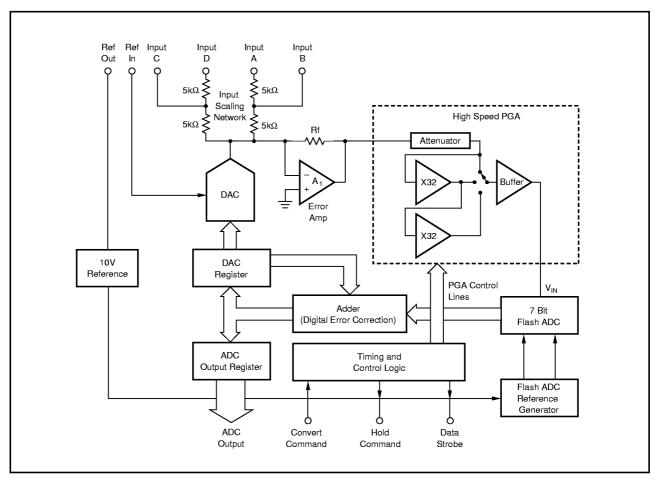

The ADC701 is a very high speed 16-bit analog-to-digital converter based on a three-step subranging architecture. Outstanding dynamic performance is achieved with the SHC702 companion sample/hold amplifier. Both devices use hybrid construction for applications where reliability, small size, and low power consumption are especially important.

Excellent linearity and stability are assured through use of a new ultra-precise monolithic D/A converter and a low-drift reference circuit. Custom monolithic op amps provide very high bandwidth and low noise in all sections of the analog signal path. Logic is CMOS/TTL compatible and is designed for maximum flexibility.

International Airport Industrial Park • Mailing Address: POBox 11400, Tucson, AZ 85734 • Street Address: 6730S. Tucson Blvd., Tucson, AZ 85706 • Tel.: (520) 746-1111 • Twx: 910-952-1111

Internat: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BERCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

## **ELECTRICAL (ADC701 ONLY)**

At  $T_A = +25^{\circ}C$ , 500kHz sampling rate,  $\pm V_{CC} = \pm 15V$ ,  $\pm V_{DD1} = \pm 5V$ ,  $+V_{DD2} = +5V$ , and five-minute warmup in a convection environment, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          | ADC701JH                          |                                                                                                             |                                                                                          |                | ADC701KH                                |                                         |                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------|-----------------------------------------|-----------------------------------------|-----------------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                          | CONDITIONS                                                                                               | MIN                               | TYP                                                                                                         | MAX                                                                                      | MIN            | TYP                                     | MAX                                     | UNITS                                                           |  |

| RESOLUTION                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |                                   |                                                                                                             | 16                                                                                       |                |                                         | *                                       | Bits                                                            |  |

| INPUTS                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| ANALOG                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| Voltage Ranges                                                                                                                                                                                                                                                                                                                                                                                                     | Unipolar                                                                                                 |                                   | 1 I                                                                                                         | to +5, <b>0</b> to                                                                       | <br>  ±10 =10  | to 0                                    |                                         | V                                                               |  |

| Voltage Hanges                                                                                                                                                                                                                                                                                                                                                                                                     | Bipolar                                                                                                  |                                   | •                                                                                                           |                                                                                          | ±10, 10        | 10 0                                    |                                         | v                                                               |  |

| Resistance                                                                                                                                                                                                                                                                                                                                                                                                         | 0 to +5V Range                                                                                           | 2.45                              | 2.5                                                                                                         | 2.55                                                                                     | *              | *                                       | *                                       | kΩ                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 to +10V, −10 to 0, ±5V Ranges                                                                          | 4.9                               | 5                                                                                                           | 5.1                                                                                      | *              | *                                       | *                                       | kΩ                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                    | ±1 <b>0V</b> Range                                                                                       | 9.8                               | 10                                                                                                          | 10.2                                                                                     | *              | *                                       | *                                       | kΩ                                                              |  |

| Capacitance                                                                                                                                                                                                                                                                                                                                                                                                        | All Ranges                                                                                               |                                   | 5                                                                                                           |                                                                                          |                | *                                       |                                         | pF                                                              |  |

| DIGITAL                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| Logic Family                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |                                   | ٦                                                                                                           | ITL-Compa                                                                                |                | OS                                      |                                         |                                                                 |  |

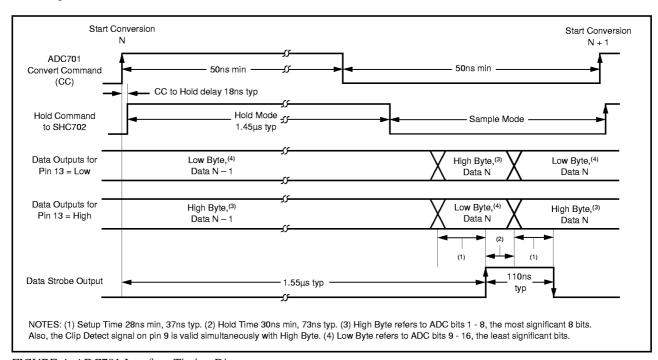

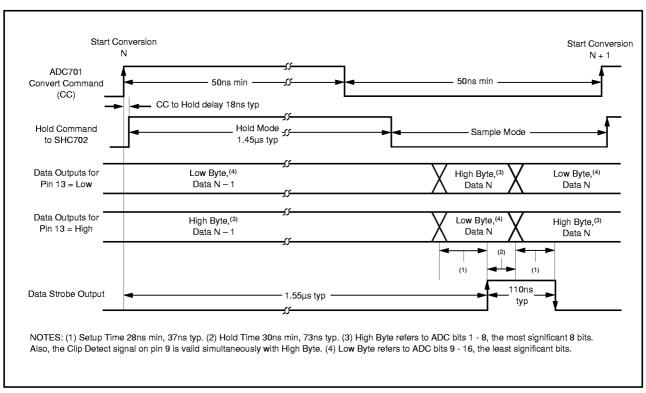

| Convert Command                                                                                                                                                                                                                                                                                                                                                                                                    | Start Conversion                                                                                         |                                   |                                                                                                             |                                                                                          | gEdge          |                                         |                                         |                                                                 |  |

| Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                        | t = Conversion Period                                                                                    | 50                                |                                                                                                             | t – <b>50</b>                                                                            |                |                                         | Î                                       | ns                                                              |  |

| TRANSFER CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| ACCURACY                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| Gain Error <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                          | 0 to +10V Range                                                                                          |                                   | ±0.03                                                                                                       | ±0.1                                                                                     |                | *                                       | *                                       | %                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                    | ±10V Range                                                                                               |                                   | ±0.03                                                                                                       | ±0.1                                                                                     |                | *                                       | *                                       | %                                                               |  |

| Power Supply Sensitivity of Gain                                                                                                                                                                                                                                                                                                                                                                                   | All Ranges, All Supplies                                                                                 |                                   | ±0.005                                                                                                      | ±0.1                                                                                     |                | *                                       | *                                       | %/ <b>V</b>                                                     |  |

| Input Offset Error <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                  | 0 to +10V Range                                                                                          |                                   | ±1                                                                                                          | ±3                                                                                       |                | *                                       | *                                       | mV                                                              |  |

| D 0 10                                                                                                                                                                                                                                                                                                                                                                                                             | ±10V Range                                                                                               |                                   | ±5                                                                                                          | ±10                                                                                      |                | *                                       | *                                       | mV                                                              |  |

| Power Supply Sensitivity of Offset                                                                                                                                                                                                                                                                                                                                                                                 | All Ranges, All Supplies                                                                                 |                                   | ±0.006                                                                                                      | ±0.1                                                                                     |                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | *                                       | %FSR/V                                                          |  |

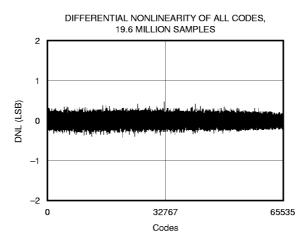

| Integral Linearity Error <sup>(2)</sup><br>Differential Linearity Error <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                             |                                                                                                          |                                   | ±0.002<br>±0.0006                                                                                           | ±0.003                                                                                   |                | ±0.0012                                 | *                                       | %FSR <sup>(3)</sup><br>%FSR                                     |  |

| No Missing Codes                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                          |                                   | i ±0.0006 i<br>Guaranteed                                                                                   |                                                                                          |                | I<br>Guaranteed                         |                                         | 70F3N                                                           |  |

| Noise                                                                                                                                                                                                                                                                                                                                                                                                              | R <sub>SOURCE</sub> ≤ 50Ω                                                                                | ,                                 | 0.6                                                                                                         | 1                                                                                        |                | *                                       | '                                       | LSB rms                                                         |  |

| CONVERSION CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                         | - GOUNCE                                                                                                 |                                   |                                                                                                             |                                                                                          |                | <u> </u>                                |                                         |                                                                 |  |

| Sample Rate                                                                                                                                                                                                                                                                                                                                                                                                        | Unadjusted                                                                                               | DC                                |                                                                                                             | 512                                                                                      | *              |                                         | *                                       | kHz                                                             |  |

| Conversion Time <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                     | Unadjusted                                                                                               |                                   | 1.45                                                                                                        | 1.5                                                                                      |                | *                                       | *                                       | μs                                                              |  |

| OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         | ,                                                               |  |

| DIGITAL                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| Logic Family                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |                                   | ' '                                                                                                         | TL-Compa                                                                                 | i<br>tible CMC | ı ı<br>S                                |                                         |                                                                 |  |

| Data Coding                                                                                                                                                                                                                                                                                                                                                                                                        | Unipolar Ranges                                                                                          |                                   |                                                                                                             | Straigh                                                                                  |                | _                                       |                                         |                                                                 |  |

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                | Bipolar Ranges                                                                                           |                                   |                                                                                                             | _                                                                                        | Binary         |                                         |                                         |                                                                 |  |

| Logic "0" Levels (V <sub>OL</sub> )                                                                                                                                                                                                                                                                                                                                                                                | I <sub>OL</sub> ≤ 3.2mA                                                                                  |                                   | 0.1                                                                                                         | 0.4                                                                                      |                | *                                       | *                                       | V                                                               |  |

| Logic "1" Levels (V <sub>OH</sub> )                                                                                                                                                                                                                                                                                                                                                                                | I <sub>OH</sub> ≤ 80μA                                                                                   | 4                                 | 4.9                                                                                                         |                                                                                          | *              | *                                       |                                         | V                                                               |  |

| Data Valid Setup Time Before Strobe                                                                                                                                                                                                                                                                                                                                                                                | Both Edges                                                                                               | 28                                | 37                                                                                                          |                                                                                          | *              | *                                       |                                         | ns                                                              |  |

| INTERNAL REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| Voltage                                                                                                                                                                                                                                                                                                                                                                                                            | $R_{LOAD} \ge 5k\Omega$                                                                                  | +9.995                            | +10.000                                                                                                     | +10.005                                                                                  | *              | *                                       | *                                       | V                                                               |  |

| Current Available to External Loads                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          | 2                                 | 5                                                                                                           |                                                                                          | *              | *                                       |                                         | m <b>A</b>                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

| POWER SUPPLY REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |                                   |                                                                                                             |                                                                                          |                |                                         |                                         |                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                    | Operating                                                                                                | +14.25                            | +15                                                                                                         | +15.75                                                                                   | *              | *                                       | *                                       | ٧                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                    | Operating                                                                                                | -14.25                            | -15                                                                                                         | -15.75                                                                                   | *              | *                                       | *                                       | ٧                                                               |  |

| Supply Voltages:+V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                | Operating                                                                                                | -14.25<br>+4.75                   | –15<br>+5                                                                                                   | -15.75<br>+5.25                                                                          | * *            | * *                                     | * *                                     | V<br>V                                                          |  |

| Supply Voltages:+V <sub>CC</sub><br>-V <sub>CC</sub><br>+V <sub>DD1</sub><br>-V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                     | Operating                                                                                                | -14.25<br>+4.75<br>-4.25          | –15<br>+5<br>–5                                                                                             | −15.75<br>+5.25<br>−6                                                                    | *              | * * * * * *                             | * * * * *                               | V<br>V<br>V                                                     |  |

| Supply Voltages:+V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub>                                                                                                                                                                                                                                                                                                            |                                                                                                          | -14.25<br>+4.75                   | -15<br>+5<br>-5<br>+5                                                                                       | -15.75<br>+5.25<br>-6<br>+5.25                                                           | * * * *        | * * * * *                               | * * * * *                               | V<br>V<br>V                                                     |  |

| Supply Voltages: $+V_{CC}$ $-V_{CC}$ $+V_{DD1}$ $-V_{DD1}$ $+V_{DD2}$ Supply Currents: $+I_{CC}$                                                                                                                                                                                                                                                                                                                   | Operating Operating                                                                                      | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5<br>25                                                                                 | -15.75<br>+5.25<br>-6<br>+5.25<br>30                                                     | *              | * * * * * * * *                         |                                         | V<br>V<br>V<br>mA                                               |  |

| Supply Voltages:+V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents:+I <sub>CC</sub> -I <sub>CC</sub>                                                                                                                                                                                                                                                          |                                                                                                          | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5                                                                                       | -15.75<br>+5.25<br>-6<br>+5.25                                                           | *              | * * * * * * * * * * * * * * * * * * * * | *                                       | V<br>V<br>V                                                     |  |

| Supply Voltages: $+V_{CC}$ $-V_{CC}$ $+V_{DD1}$ $-V_{DD1}$ $+V_{DD2}$ Supply Currents: $+I_{CC}$                                                                                                                                                                                                                                                                                                                   |                                                                                                          | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5<br>25<br>33                                                                           | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45                                               | *              | * * * * * * * * * * * * * * * * * * * * | *                                       | V<br>V<br>V<br>mA<br>mA                                         |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub>                                                                                                                                                                                                                                      |                                                                                                          | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45                                                                     | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55                                         | *              | * * * * * * * * * * * * * * * * * * * * | *<br>*<br>*<br>*                        | V<br>V<br>V<br>mA<br>mA                                         |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub>                                                                                                                                                                                                  |                                                                                                          | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37                                                               | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50                                   | *              |                                         | * * *                                   | V<br>V<br>V<br>MA<br>MA<br>MA                                   |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation                                                                                                                                                                                | Operating<br>Nominal Voltages                                                                            | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133                                                        | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150                            | *              |                                         | *<br>*<br>*<br>*                        | V<br>V<br>V<br>MA<br>MA<br>MA<br>MA                             |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range                                                                                                                    | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max                                | -14.25<br>+4.75<br>-4.25          | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95                                                | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3                     | *              | * * * * * * * * * * * * * * * * * * * * | *<br>*<br>*<br>*                        | V<br>V<br>V<br>WA<br>MA<br>MA<br>MA<br>W                        |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range Gain Error                                                                                                         | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max  All Ranges                    | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95                                                | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15       | * *            | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * *                 | V<br>V<br>V<br>W<br>MA<br>MA<br>MA<br>MA<br>W                   |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range Gain Error                                                                                                         | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max All Ranges All Unipolar Ranges | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95                                                | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15<br>±5 | * *            | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * *   | V<br>V<br>V<br>W<br>MA<br>MA<br>MA<br>W<br>**C                  |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU  Specification Temperature Range Gain Error Input Offset Error                                                                                     | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max  All Ranges                    | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95<br>±10<br>±1<br>±1                             | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15       | * *            |                                         | + * * * * * * * * * * * * * * * * * * * | V V V W MA MA MA MA W                                           |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range Gain Error Input Offset Error                                                                                      | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max All Ranges All Unipolar Ranges | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95<br>±10<br>±1<br>±1<br>±0.2                     | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15<br>±5 | * *            |                                         | +70<br>*<br>*<br>±<br>±0.5              | V V V W MA MA MA MA W   C C C C C C C C C C C C C C C C C       |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range Gain Error Input Offset Error  Integral Linearity Error <sup>(2)</sup> Differential Linearity Error <sup>(2)</sup> | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max All Ranges All Unipolar Ranges | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95<br>±10<br>±1<br>±0.2<br>±0.05                  | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15<br>±5 | * * *          | * * *                                   | +70<br>+70<br>*<br>±0.5<br>±0.3         | V V V W MA MA MA MA W                                           |  |

| +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range Gain Error Input Offset Error  Integral Linearity Error <sup>(2)</sup> Differential Linearity Error <sup>(2)</sup> No Missing Codes                                   | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max All Ranges All Unipolar Ranges | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95<br>±10<br>±1<br>±1<br>±0.2<br>±0.05<br>Typical | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15<br>±5 | * * *          | * * * * * * * * * * * * * * * * * * *   | +70<br>+70<br>*<br>±0.5<br>±0.3         | V V V W MA MA MA MA W  C ppm/°C ppm FSR/°C ppm/°C ppm/°C ppm/°C |  |

| Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD1</sub> +V <sub>DD2</sub> Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD1</sub> +I <sub>DD2</sub> Power Dissipation  PERFORMANCE OVER TEMPERATU Specification Temperature Range Gain Error Input Offset Error  Integral Linearity Error <sup>(2)</sup> Differential Linearity Error <sup>(2)</sup> | Operating  Nominal Voltages  RE  T <sub>A</sub> Min to T <sub>A</sub> Max All Ranges All Unipolar Ranges | -14.25<br>+4.75<br>-4.25<br>+4.25 | -15<br>+5<br>-5<br>+5<br>25<br>33<br>45<br>37<br>133<br>1.95<br>±10<br>±1<br>±0.2<br>±0.05                  | -15.75<br>+5.25<br>-6<br>+5.25<br>30<br>45<br>55<br>50<br>150<br>2.3<br>+55<br>±15<br>±5 | * * *          | * * *                                   | +70<br>+70<br>*<br>±0.5<br>±0.3         | V V V W MA MA MA MA W   C C C C C C C C C C C C C C C C C       |  |

<sup>\*</sup> Same specifications as ADC701JH.

## **SPECIFICATIONS**

## **ELECTRICAL (SHC702 ONLY)**

At  $T_A = +25^{\circ}C$ , 500kHz sampling rate,  $\pm V_{CC} = \pm 15V$ ,  $+V_{DD1} = +5V$ , and five-minute warmup in a convection environment, unless otherwise noted.

|                                             |                                             |        | SHC702JM   |       |             |

|---------------------------------------------|---------------------------------------------|--------|------------|-------|-------------|

| PARAMETER                                   | CONDITIONS                                  | MIN    | TYP        | MAX   | UNITS       |

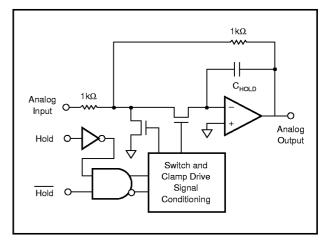

| INPUTS (Without Input Buffer)               | _                                           |        |            |       |             |

| ANALOG                                      |                                             |        |            |       |             |

| Voltage Range                               |                                             | ±10.25 | ±11        |       | V           |

| Resistance                                  |                                             | 0.98   | 1          | 1.02  | kΩ          |

| Capacitance                                 |                                             |        | 3          |       | pF          |

| DIGITAL                                     |                                             |        |            |       |             |

| Logic Family                                |                                             |        | LSTTL      | _     |             |

| Input Loading                               |                                             |        | 2          |       | LSTTL Loads |

| TRANSFER CHARACTERISTICS                    |                                             |        |            |       |             |

| ACCURACY                                    |                                             |        |            |       |             |

| Gain                                        | $R_{SOURCE} = 0\Omega$                      |        | -1         |       | V/V         |

| Gain Error                                  | $R_{SOURCE} = 0\Omega$                      |        | ±0.02      | ±0.1  | %           |

| Linearity Error                             | Sample Mode                                 |        | ±0.0003    |       | %FSR        |

| Offset Error                                | Sample Mode                                 |        | ±0.5       | ±3    | mV          |

| Charge Offset (Pedestal) Error              | Sample/Hold Mode, $R_{SOURCE} \le 50\Omega$ |        | ±0.5       | ±5    | mV          |

| Droop Rate                                  | Hold Mode                                   |        | ±0.2       | ±2    | μV/μs       |

| Dynamic Nonlinearity                        | Sample/Hold Mode                            |        | ±0.0005    |       | %FSR        |

| Power Supply Sensitivity                    | Offset Plus Charge Offset, All Supplies     |        | ±0.003     |       | %FSR/V      |

| DYNAMIC CHARACTERISTICS                     |                                             |        |            |       | _           |

| Acquisition Time                            | 10V Step to ±150μV                          |        | 600        |       | ns          |

|                                             | 5V Step to ±150μV                           |        | 500        |       | ns          |

| Sample-to-Hold Settling Time <sup>(5)</sup> | to ±1 <b>50</b> μV                          |        | 120        |       | ns          |

| Aperture Delay Time                         |                                             |        | 20         |       | ns          |

| Aperture Uncertainty (Jitter)               |                                             |        | 10         | 25    | ps rms      |

| Slew Rate                                   | V +4V                                       |        | 150<br>3.1 |       | V/μs<br>MHz |

| Small Signal Bandwidth Full-Power Bandwidth | $V_{IN} = \pm 1V$ $V_{IN} = \pm 10V$        |        | 2          |       | MHz         |

| Feedthrough Rejection                       | Hold Mode, 10Vp-p Square Wave Input         |        | 0.001      |       |             |

| <u> </u>                                    | Hold Wode, 10Vp-p Square Wave Input         |        | 0.001      |       | /6          |

| ОИТРИТ                                      |                                             |        | _          |       | T           |

| Voltage Range                               | $R_{LOAD} \ge 1k\Omega$                     | ±10.25 | ±11        |       | V           |

| Output Current                              |                                             | ±40    | 1          | l     | mA          |

| Short Circuit Protection                    | $R_{LOAD} = 0\Omega$<br>DC                  |        | Indefinite | 1 01  |             |

| Output Impedance                            | l DC                                        |        | 0.01       | 0.1   | Ω           |

| INPUT BUFFER CHARACTERISTICS                |                                             |        |            |       | _           |

| INPUT                                       |                                             |        | l          |       |             |

| Impedance                                   |                                             |        | 1013    3  |       | Ω   pF      |

| Bias Current                                | $V_{IN} = \pm 10V$                          |        | ±2         | ±15   | p <b>A</b>  |

| Offset Voltage                              | $R_{SOURCE} \le 10k\Omega$                  |        | ±0.3       | ±1.5  | mV          |

| Voltage Range                               |                                             | ±10.25 | ±11        |       | V           |

| DYNAMIC CHARACTERISTICS                     |                                             |        |            |       |             |

| Slew Rate                                   |                                             | 20     | 35         |       | V/µs        |

| Full-Power Bandwidth                        | $V_{IN} = \pm 10V$                          |        | 570        |       | kHz         |

| Settling Time                               | 10V Step to ±150μV                          |        | 1.7        |       | μs          |

| OUTPUT                                      |                                             |        |            |       |             |

| Output Current                              |                                             | ±15    | ±20        |       | mA          |

| Short Circuit Protection                    | $R_{LOAD} = 0\Omega$                        |        | Indefinite |       |             |

| POWER SUPPLY REQUIREMENTS                   |                                             |        |            |       |             |

| Voltage: +V <sub>CC</sub>                   | Operating                                   | +13.5  | +15        | +16.5 | V           |

| -V <sub>cc</sub>                            |                                             | -13.5  | -15        | -16.5 | v           |

| $+V_{DD1}$                                  |                                             | +4.75  | +5         | +5.25 | V           |

| Current: +I <sub>CC</sub>                   | Operating                                   |        | 33         | 40    | mA          |

| -I <sub>cc</sub>                            |                                             |        | 18         | 25    | m <b>A</b>  |

| +I <sub>DD1</sub>                           | Name of St. II                              |        | 5          | 10    | mA          |

| Power Dissipation                           | Nominal Voltages                            |        | 790        | 950   | m <b>W</b>  |

| PERFORMANCE OVER TEMPERATURE                |                                             |        |            |       |             |

| Specification Temperature Range             | T <sub>A</sub> Min to T <sub>A</sub> Max    | 0      |            | +70   | °C          |

| Sample/Hold Gain Error                      | $R_{SOURCE} = 0\Omega$                      |        | ±1         | ±5    | ppm/°C      |

| Sample/Hold Offset Error                    | $R_{SOURCE} \le 50\Omega$                   |        | ±10        | ±30   | μV/°C       |

| Sample/Hold Charge Offset Error             | R <sub>SOURCE</sub> ≤ 50Ω                   |        | ±10        | ±80   | μV/°C       |

| Droop Rate                                  | B                                           |        | 1          | ±50   | μV/μs       |

| Buffer Offset Error                         | R <sub>SOURCE</sub> ≤ 10kΩ                  | I      | ±3         | ±15   | μV/°C       |

NOTES: (1) Adjustable to zero. Tested and guaranteed for 0 to +10V and ±10V ranges only. (2) Peak-to-peak based on 99.9% of all codes. (3) FSR means full-scale range and depends on the input range selected. (4) ADC conversion time is defined as the time that the Sample/Hold must remain in the Hold mode; i.e., the duration of the Sample/Hold command. This time must be added to the Sample/Hold acquisition time to obtain the total system throughput time. (5) Given for reference only — this time overlaps with the ADC701 conversion time and does not affect system throughput rate.

## **SPECIFICATIONS**

## **ELECTRICAL (COMBINED ADC701/SHC702)**

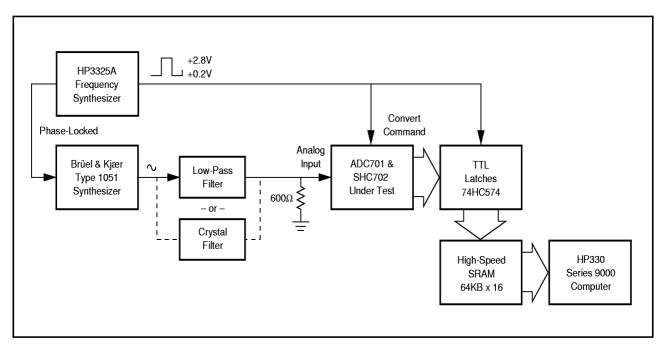

$At T_A = +25^{\circ}C, 500 \text{kHz sampling rate}, \pm V_{CC} = \pm 15 \text{V}, \pm V_{DD1} = \pm 5 \text{V}, +V_{DD2} = +5 \text{V}, \text{ and five-minute warmup in a convection environment}, \pm 5 \text{V input range, unless otherwise noted.}$

| PARAMETER                                 | CONDITIONS                                                                        | MIN | TYP    | MAX  | UNITS |

|-------------------------------------------|-----------------------------------------------------------------------------------|-----|--------|------|-------|

| Sample Rate                               | Unadjusted                                                                        | DC  |        | 512  | kHz   |

| Dynamic Nonlinearity                      |                                                                                   |     | ±0.002 |      | %FSR  |

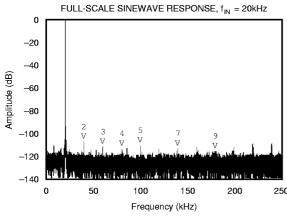

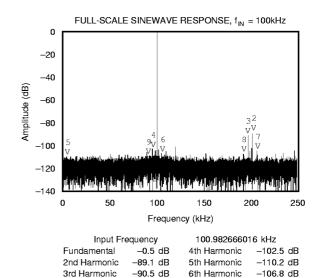

| Total Harmonic Distortion (THD)           | f <sub>IN</sub> = 20kHz (-0.3dB)                                                  |     | -103   |      | dB    |

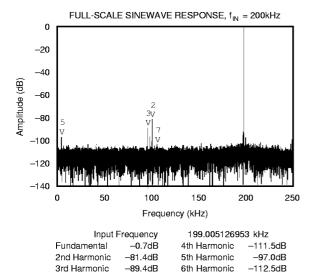

|                                           | f <sub>IN</sub> = 199kHz (-0.2dB)                                                 |     | -82    |      | dB    |

| Spurious-Free Dynamic Range (SFDR)        | f <sub>IN</sub> = 20kHz (-0.3dB)                                                  |     | 107    |      | dB    |

|                                           | f <sub>IN</sub> = 199kHz (-12dB)                                                  |     | 94     |      | dB    |

| Two-Tone Intermodulation Distortion (IMD) | $f_1 = 195 \text{kHz} (-6.5 \text{dB}), f_2 = 200 \text{kHz} (-6.5 \text{dB})$    |     | -81    |      | dBC   |

|                                           | $f_1 = 195 \text{kHz} (-12.5 \text{dB}), fF_2 = 200 \text{kHz} (-12.5 \text{dB})$ |     | -86    |      | dBC   |

| Signal-to-Noise Ratio (SNR)               | f <sub>IN</sub> = 5kHz (-0.5dB)                                                   |     | 93     |      | dB    |

| Total Power Dissipation                   | Operating                                                                         |     | 2.8    | 3.25 | W     |

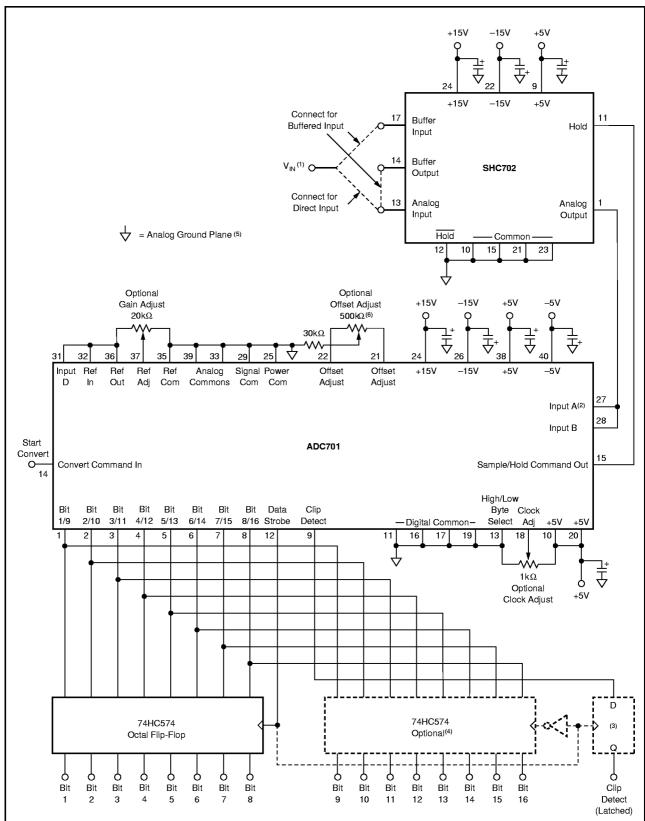

## **ADC701 PIN ASSIGNMENTS**

| PIN NO. | DESCRIPTION                        | PIN NO. | DESCRIPTION                    |

|---------|------------------------------------|---------|--------------------------------|

| 1       | Bit 1/9 (Bit 1 = MSB)              | 40      | -V <sub>DD1</sub> (-5V) Analog |

| 2       | Bit 2/10                           | 39      | Common (Analog)                |

| 3       | Bit 3/11                           | 38      | +V <sub>DD1</sub> (+5V) Analog |

| 4       | Bit 4/12                           | 37      | Reference (Gain) Adjust        |

| 5       | Bit 5/13                           | 36      | +10V Reference Output(2)       |

| 6       | Bit 6/14                           | 35      | Common (Reference)             |

| 7       | Bit 7/15                           | 34      | DNC                            |

| 8       | Bit 8/16                           | 33      | Common (Analog)                |

| 9       | Clip Detect Output                 | 32      | +10V Reference Input(2)        |

| 10      | +V <sub>DD2</sub> (+5V) Digital    | 31      | Input D (1)                    |

| 11      | Common (Digital)                   | 30      | Input C (1)                    |

| 12      | Data Strobe                        | 29      | Common (Signal)                |

| 13      | High/Low Byte Select               | 28      | Input B (1)                    |

| 14      | Convert Command                    | 27      | Input A (1)                    |

| 15      | Sample/Hold Control <sup>(3)</sup> | 26      | -V <sub>CC</sub> (−15V) Analog |

| 16      | Common (Digital)                   | 25      | Common (Power)                 |

| 17      | Common (Digital)                   | 24      | +V <sub>CC</sub> (+15V) Analog |

| 18      | Clock Adjust                       | 23      | DNC <sup>(4)</sup>             |

| 19      | Common (Digital)                   | 22      | Offset Adjust                  |

| 20      | +V <sub>DD2</sub> (+5V) Digital    | 21      | Offset Adjust                  |

NOTES: (1) Refer to Input Connection Table. (2) Reference Input is normally connected to Reference Output, unless an external 10V reference is used. (3) Sample/Hold Control goes high to activate Hold mode. (4) DNC = Do Not Connect.

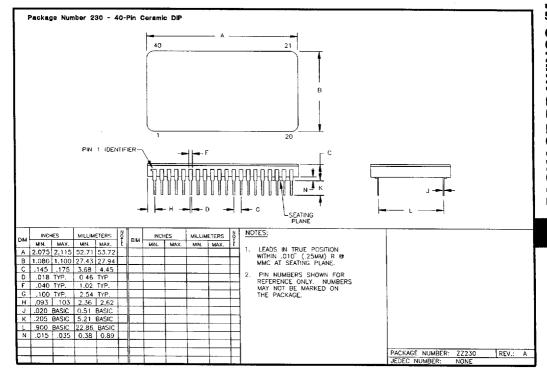

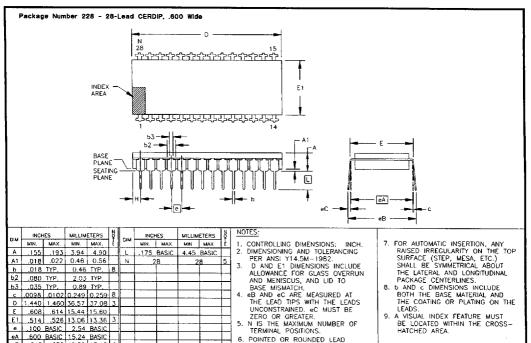

## **PACKAGING INFORMATION**

| PRODUCT  | PACKAGE           | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|-------------------|------------------------------------------|

| ADC701JH | Metal and Ceramic | 230                                      |

| ADC701KH | Metal and Ceramic | 230                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

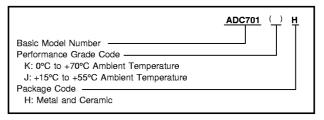

## **ADC701 ORDERING INFORMATION**

#### **ADC701 ABSOLUTE MAXIMUM RATINGS**

## **ADC701 OUTPUT CODING**

|                                       |                                          | AL INPUT VOLTAGE TO A y by -1 for SHC702 Input Y | OUTPUT CODE                                 |                                            |                |

|---------------------------------------|------------------------------------------|--------------------------------------------------|---------------------------------------------|--------------------------------------------|----------------|

| INPUT LEVEL<br>(Exact Center of Code) | <b>0–10V RANGE</b><br>(1LSB ≈153μV)      | ± <b>10V RANGE</b><br>(1LSB ≈05μV                | ± <b>5V RANGE</b><br>(1LSB ≈153μ <b>V</b> ) | (1 = Logic High) MSB LSB                   | CLIP<br>DETECT |

| Underrange<br>-FS<br>-FS + 1LSB       | < -76μV<br>0V<br>+153μV                  | < -10.000153V<br>-10V<br>-9.999695V              | < -5.000076V<br>-5V<br>-4.999847V           | 0000 0000 0000 0000<br>0000 0000 0000 000  | 1<br>0<br>0    |

| -3/4FS<br>-1/2FS<br>-1/4FS            | +1.25V<br>+2.5V<br>+3.75V                | −7.5V<br>−5V<br>−2.5V                            | −3.75V<br>−2.5V<br>−1.25V                   | 0010 0000 0000 0000<br>0100 0000 0000 0000 | 0<br>0<br>0    |

| -1LSB<br>Mid-Scale<br>+1LSB           | +4.999847V<br>+5V<br>+5.000153V          | −305μV<br>0V<br>+305μV                           | –153μV<br>0V<br>+153μV                      | 0111 1111 1111 1111<br>1000 0000 0000 0000 | 0<br>0<br>0    |

| +1/4FS<br>+1/2FS<br>+3/4FS            | +6.25V<br>+7.5V<br>+8.75V                | +2.5V<br>+5V<br>+7.5V                            | +1.25V<br>+2.5V<br>+3.75V                   | 1010 0000 0000 0000<br>1100 0000 0000 0000 | 0<br>0<br>0    |

| +FS -2LSB<br>+FS - 1LSB<br>Overrange  | +9.999695V<br>+9.999847V<br>> +9.999924V | +9.99939V<br>+9.999695V<br>> +9.999847V          | +4.999695V<br>+4.999847V<br>> +4.999924V    | 1111 1111 1111 1110<br>1111 1111 1111 1111 | 0<br>0<br>1    |

## **SHC702 PIN ASSIGNMENTS**

| PIN NO. | DESCRIPTION                    | PIN NO. | DESCRIPTION                     |

|---------|--------------------------------|---------|---------------------------------|

| 1       | Sample/Hold Output             | 24      | +V <sub>CC</sub> (+15V) Analog  |

| 2       | NC <sup>(3)</sup>              | 23      | Common (Power)                  |

| 3       | NC                             | 22      | –V <sub>CC</sub> (–15V) Analog  |

| 4       | NC                             | 21      | Common (Analog)                 |

| 5       | NC                             | 20      | NC                              |

| 6       | NC                             | 19      | NC                              |

| 7       | NC                             | 18      | NC                              |

| 8       | NC                             | 17      | Buffer Amp Input <sup>(2)</sup> |

| 9       | +V <sub>DD1</sub> (+5V) Analog | 16      | NC                              |

| 10      | Common (Digital)               | 15      | Common (Signal)                 |

| 11      | Hold Input <sup>(1)</sup>      | 14      | Buffer Amp Output               |

| 12      | Hold Input <sup>(1)</sup>      | 13      | Analog Input                    |

NOTES: (1) Hold mode is activated only when pin 12 is low and pin 11 is high. For normal use with ADC701, pin 12 is grounded and pin 11 is connected to ADC701 Sample/Hold control (ADC701 pin 15). (2) If the buffer amp is not used, pin 17 should be grounded. (3) NC = No Internal Connection.

#### **PACKAGING INFORMATION**

| PRODUCT  | PACKAGE | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|---------|------------------------------------------|

| SHC702JM | 24-Pin  | 037                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

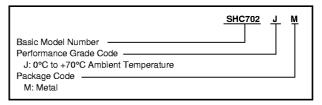

#### SHC702 ORDERING INFORMATION

## **SHC702 ABSOLUTE MAXIMUM RATINGS**

| ±V <sub>cc</sub> +V <sub>DD1</sub> Analog and Buffer Inputs Outputs Inde | +7V                                             |

|--------------------------------------------------------------------------|-------------------------------------------------|

| Logic Inputs  Case Temperature  Junction Temperature                     | -0.5V to (+V <sub>DD1</sub> + 0.3V)<br>+ +150°C |

| Storage Temperature                                                      | 1.5W                                            |