## Low-Voltage CMOS Quad **2-Input AND Gate** With 5V-Tolerant Inputs

The MC74LCX08 is a high performance, guad 2-input AND gate operating from a 2.7 to 3.6V supply. High impedance TTL compatible inputs significantly reduce current loading to input drivers while TTL compatible outputs offer improved switching noise performance. A VI specification of 5.5V allows MC74LCX08 inputs to be safely driven from 5V devices.

Current drive capability is 24mA at the outputs.

- Designed for 2.7 to 3.6V V<sub>CC</sub> Operation

- 5V Tolerant Inputs Interface Capability With 5V TTL Logic

- LVTTL Compatible

- LVCMOS Compatible

- 24mA Balanced Output Sink and Source Capability

- Near Zero Static Supply Current (10μA) Substantially Reduces System **Power Requirements**

- Latchup Performance Exceeds 500mA

- ESD Performance: Human Body Model >2000V; Machine Model >200V

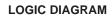

#### **PIN NAMES**

| Pins   | Function    |  |

|--------|-------------|--|

| An, Bn | Data Inputs |  |

| On     | Outputs     |  |

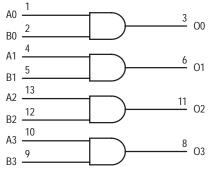

#### **FUNCTION TABLE**

| INP | UTS | OUTPUTS |

|-----|-----|---------|

| An  | Bn  | On      |

| L   | L   | L       |

| L   | Н   | L       |

| Н   | L   | L       |

| Н   | Н   | Н       |

11/96

#### **ABSOLUTE MAXIMUM RATINGS\***

| Symbol           | Parameter                        | Value                             | Condition            | Unit |

|------------------|----------------------------------|-----------------------------------|----------------------|------|

| VCC              | DC Supply Voltage                | -0.5 to +7.0                      |                      | V    |

| VI               | DC Input Voltage                 | $-0.5 \le V_1 \le +7.0$           |                      | V    |

| VO               | DC Output Voltage                | $-0.5 \le V_{O} \le V_{CC} + 0.5$ | Note 1.              | V    |

| Iк               | DC Input Diode Current           | DC Input Diode Current -50        |                      | mA   |

| Іок              | DC Output Diode Current          | -50                               | V <sub>O</sub> < GND | mA   |

|                  |                                  | +50                               | VO > ACC             | mA   |

| IO               | DC Output Source/Sink Current    | ±50                               |                      | mA   |

| ICC              | DC Supply Current Per Supply Pin | ±100                              |                      | mA   |

| I <sub>GND</sub> | DC Ground Current Per Ground Pin | ±100                              |                      | mA   |

| T <sub>STG</sub> | Storage Temperature Range        | -65 to +150                       |                      | °C   |

\* Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute-maximum-rated conditions is not implied.

1. Output in HIGH or LOW State. IO absolute maximum rating must be observed.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol         | Parameter                                                                                     | Min        | Тур        | Max        | Unit |

|----------------|-----------------------------------------------------------------------------------------------|------------|------------|------------|------|

| VCC            | Supply Voltage Operating<br>Data Retention Only                                               | 2.0<br>1.5 | 3.3<br>3.3 | 3.6<br>3.6 | V    |

| VI             | Input Voltage                                                                                 | 0          |            | 5.5        | V    |

| VO             | Output Voltage (HIGH or LOW State)                                                            | 0          |            | VCC        | V    |

| IОН            | HIGH Level Output Current, $V_{CC} = 3.0V - 3.6V$                                             |            |            | -24        | mA   |

| IOL            | LOW Level Output Current, $V_{CC} = 3.0V - 3.6V$                                              |            |            | 24         | mA   |

| ЮН             | HIGH Level Output Current, $V_{CC} = 2.7V - 3.0V$                                             |            |            | -12        | mA   |

| IOL            | LOW Level Output Current, $V_{CC} = 2.7V - 3.0V$                                              |            |            | 12         | mA   |

| Т <sub>А</sub> | Operating Free–Air Temperature                                                                | -40        |            | +85        | °C   |

| Δt/ΔV          | Input Transition Rise or Fall Rate, V <sub>IN</sub> from 0.8V to 2.0V, V <sub>CC</sub> = 3.0V | 0          |            | 10         | ns/V |

#### DC ELECTRICAL CHARACTERISTICS

|        |                                    | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$     |                       | C to +85°C |      |

|--------|------------------------------------|-----------------------------------------------------|-----------------------|------------|------|

| Symbol | Characteristic                     | Condition                                           | Min                   | Max        | Unit |

| VIH    | HIGH Level Input Voltage (Note 2.) | $2.7V \le V_{CC} \le 3.6V$                          | 2.0                   |            | V    |

| VIL    | LOW Level Input Voltage (Note 2.)  | $2.7V \le V_{CC} \le 3.6V$                          |                       | 0.8        | V    |

| VOH    | HIGH Level Output Voltage          | $2.7V \leq V_{CC} \leq 3.6V; \ I_{OH} = -100 \mu A$ | V <sub>CC</sub> - 0.2 |            | V    |

|        |                                    | $V_{CC} = 2.7V; I_{OH} = -12mA$                     | 2.2                   |            |      |

|        |                                    | $V_{CC} = 3.0V; I_{OH} = -18mA$                     | 2.4                   |            |      |

|        |                                    | $V_{CC} = 3.0V; I_{OH} = -24mA$                     | 2.2                   |            |      |

| VOL    | LOW Level Output Voltage           | $2.7V \leq V_{CC} \leq 3.6V; \ I_{OL} = 100 \mu A$  |                       | 0.2        | V    |

|        |                                    | $V_{CC} = 2.7V; I_{OL} = 12mA$                      |                       | 0.4        |      |

|        |                                    | $V_{CC} = 3.0V; I_{OL} = 16mA$                      |                       | 0.4        |      |

|        |                                    | $V_{CC} = 3.0V; I_{OL} = 24mA$                      |                       | 0.55       |      |

2. These values of VI are used to test DC electrical characteristics only.

#### DC ELECTRICAL CHARACTERISTICS (continued)

|        |                                       |                                                                                              | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |      |

|--------|---------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------|------|------|

| Symbol | Characteristic                        | Condition                                                                                    | Min                                           | Max  | Unit |

| Ц      | Input Leakage Current                 | $2.7V \leq V_{CC} \leq 3.6V; \ 0V \leq V_I \leq 5.5V$                                        |                                               | ±5.0 | μΑ   |

| ICC    | Quiescent Supply Current              | $2.7 \leq V_{CC} \leq 3.6 \text{V}; \ \text{V}_{I} = \text{GND} \ \text{or} \ \text{V}_{CC}$ |                                               | 10   | μΑ   |

|        |                                       | $2.7 \leq V_{CC} \leq 3.6 \text{V}; \ 3.6 \leq \text{V}_I \leq 5.5 \text{V}$                 |                                               | ±10  | μΑ   |

| ΔICC   | Increase in I <sub>CC</sub> per Input | $2.7 \leq V_{CC} \leq 3.6 \text{V}; \ \text{V}_{IH} = \text{V}_{CC} - 0.6 \text{V}$          |                                               | 500  | μΑ   |

#### AC CHARACTERISTICS ( $t_R = t_F = 2.5ns$ ; $C_L = 50pF$ ; $R_L = 500\Omega$ )

|                                        |                                      |          |                       | Limits         |                        |      |

|----------------------------------------|--------------------------------------|----------|-----------------------|----------------|------------------------|------|

|                                        |                                      |          | Тд                    | _ = −40°C to + | -85°C                  | 1    |

|                                        |                                      |          | V <sub>CC</sub> = 3.0 | )V to 3.6V     | V <sub>CC</sub> = 2.7V | 1    |

| Symbol                                 | Parameter                            | Waveform | Min                   | Мах            | Max                    | Unit |

| <sup>t</sup> PLH<br><sup>t</sup> PHL   | Propagation Delay<br>Input to Output | 1        | 1.5<br>1.5            | 5.5<br>5.5     | 6.2<br>6.2             | ns   |

| <sup>t</sup> OSHL<br><sup>t</sup> OSLH | Output-to-Output Skew<br>(Note 3.)   |          |                       | 1.0<br>1.0     |                        | ns   |

Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t<sub>OSHL</sub>) or LOW-to-HIGH (t<sub>OSLH</sub>); parameter guaranteed by design.

#### DYNAMIC SWITCHING CHARACTERISTICS

|        |                                      |                                                               |     | T <sub>A</sub> = +25°C |     |      |  |

|--------|--------------------------------------|---------------------------------------------------------------|-----|------------------------|-----|------|--|

| Symbol | Characteristic                       | Condition                                                     | Min | Тур                    | Max | Unit |  |

| VOLP   | Dynamic LOW Peak Voltage (Note 4.)   | $V_{CC}$ = 3.3V, $C_L$ = 50pF, $V_{IH}$ = 3.3V, $V_{IL}$ = 0V |     | 0.8                    |     | V    |  |

| VOLV   | Dynamic LOW Valley Voltage (Note 4.) | $V_{CC}$ = 3.3V, $C_L$ = 50pF, $V_{IH}$ = 3.3V, $V_{IL}$ = 0V |     | 0.8                    |     | V    |  |

4. Number of outputs defined as "n". Measured with "n-1" outputs switching from HIGH-to-LOW or LOW-to-HIGH. The remaining output is measured in the LOW state.

#### CAPACITIVE CHARACTERISTICS

| Symbol          | Parameter                     | Condition                                      | Typical | Unit |

|-----------------|-------------------------------|------------------------------------------------|---------|------|

| C <sub>IN</sub> | Input Capacitance             | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$       | 7       | pF   |

| COUT            | Output Capacitance            | $V_{CC} = 3.3$ V, $V_{I} = 0$ V or $V_{CC}$    | 8       | pF   |

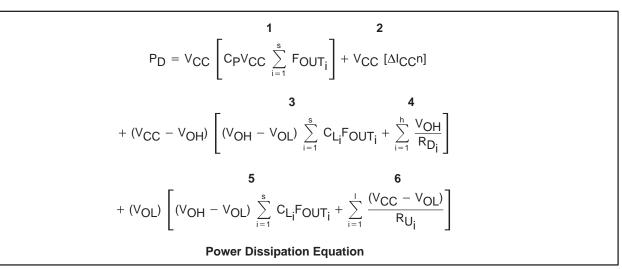

| C <sub>PD</sub> | Power Dissipation Capacitance | 10MHz, $V_{CC}$ = 3.3V, $V_I$ = 0V or $V_{CC}$ | 25      | pF   |

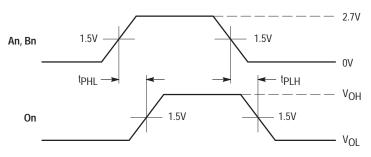

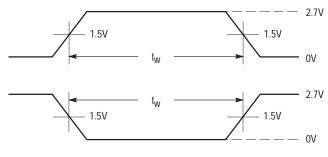

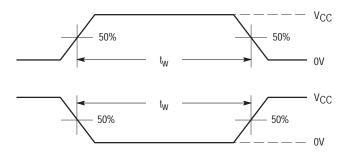

**PROPAGATION DELAYS**  $t_R = t_F = 2.5ns$ , 10% to 90%; f = 1MHz;  $t_W = 500ns$

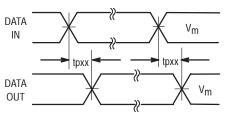

#### Figure 1. AC Waveforms

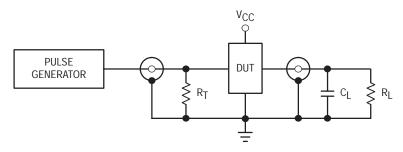

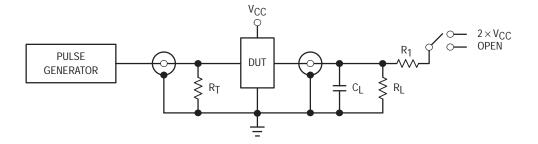

$\begin{array}{l} C_L = 50 pF \mbox{ or equivalent (Includes jig and probe capacitance)} \\ R_L = R_1 = 500 \Omega \mbox{ or equivalent} \\ R_T = Z_{OUT} \mbox{ of pulse generator (typically 50 \Omega)} \end{array}$

## Low Voltage Cross Reference to Motorola's Low Voltage Logic Families

| Company | Family        | Pkg<br>Code | Package            | Motorola<br>Replacement | Pkg<br>Code | Comments                                                                                                |

|---------|---------------|-------------|--------------------|-------------------------|-------------|---------------------------------------------------------------------------------------------------------|

| TI      | SN74LVTxxx    | D           | JEDEC SOIC         | MC74LCXxxx              | D           | LCX has lower drive, but less power                                                                     |

| TI      | SN74LVTxxx    | DB          | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | LCX has lower drive, but less power                                                                     |

| TI      | SN74LVTxxx    | DW          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | LCX has lower drive, but less power                                                                     |

| TI      | SN74LVTxxx    | PW          | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | LCX has lower drive, but less power                                                                     |

| TI      | SN74LVT16xxx  | DL          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| TI      | SN74LVT16xxx  | DGG         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | LCX has lower drive, but less power                                                                     |

| ТІ      | SN74LVCxxx    | D           | JEDEC SOIC         | MC74LCXxxx              | D           | Direct replacement. LVC has no Power down High–Z feature. Many are NOT 5V–tolerant                      |

| ТІ      | SN74LVCxxx    | DB          | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | Direct replacement. LVC has no Power down High–Z feature. Many are NOT 5V–tolerant                      |

| ТІ      | SN74LVCxxx    | DW          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement. LVC has no Power down High–Z feature. Many are NOT 5V–tolerant                      |

| ТІ      | SN74LVCxxx    | PW          | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | Direct replacement. LVC has no Power down High–Z feature. Many are NOT 5V–tolerant                      |

| TI      | SN74LVC16xxx  | DL          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| ТІ      | SN74LVC16xxx  | DGG         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement. LVC has no Power down High–Z feature. Many are NOT 5V–tolerant                      |

| ТΙ      | SN74LVC4245   | DB          | 5.3 mm SSOP II     |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| TI      | SN74LVC4245   | DW          | Wide JEDEC SOIC    | MC74LVX4245             | DW          | Similar replacement                                                                                     |

| TI      | SN74LVC4245   | PW          | 4.4 mm TSSOP       | MC74LVX4245             | DT          | Similar replacement                                                                                     |

| TI      | SN74ALVC16xxx | DL          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| ТІ      | SN74ALVC16xxx | DGG         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | ALVC is slightly faster, but LCX16xxx offers 5V toler-<br>ance                                          |

| ті      | SN74LVxxx     | D           | JEDEC SOIC         | MC74LVXxxx              | D           | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs. Alternate: 74LVQxxx |

| ТІ      | SN74LVxxx     | DB          | 5.3 mm SSOP II     |                         | SD          | For LVX, use TSSOP. Not footprint compatible. Alter-<br>nate: 74LVQxxx                                  |

| ТІ      | SN74LVxxx     | DW          | Wide JEDEC SOIC    | MC74LVXxxx              | DW          | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs. Alternate: 74LVQxxx |

| ТІ      | SN74LVxxx     | PW          | 4.4 mm TSSOP       | MC74LVXxxx              | DT          | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs. Alternate: 74LVQxxx |

| Philips | 74LVTxxx      | D           | JEDEC SOIC         | MC74LCXxxx              | D           | LCX has lower drive, but less power                                                                     |

| Philips | 74LVTxxx      | DB          | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | LCX has lower drive, but less power                                                                     |

| Philips | 74LVTxxx      | D           | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | LCX has lower drive, but less power                                                                     |

| Philips | 74LVTxxx      | PW          | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | LCX has lower drive, but less power                                                                     |

| Philips | 74LVT16xxx    | DL          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Philips | 74LVT16xxx    | DGG         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | LCX has lower drive, but less power                                                                     |

| Philips | 74LVCxxx      | D           | JEDEC SOIC         | MC74LCXxxx              | D           | Direct replacement. Many LVC are NOT 5V-tolerant                                                        |

| Philips | 74LVCxxx      | DB          | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | Direct replacement. Many LVC are NOT 5V-tolerant                                                        |

| Philips | 74LVCxxx      | D           | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement. Many LVC are NOT 5V-tolerant                                                        |

| Philips | 74LVCxxx      | PW          | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | Direct replacement. Many LVC are NOT 5V-tolerant                                                        |

| Philips | 74LVC16xxx    | DL          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Philips | 74LVC16xxx    | DGG         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement. Many LVC are NOT 5V-tolerant                                                        |

| Philips | 74LVC4245     | DB          | 5.3 mm SSOP II     |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Philips | 74LVC4245     | D           | Wide JEDEC SOIC    | MC74LVX4245             | DW          | Similar replacement                                                                                     |

NOTE: Motorola cannot guarantee device compatibility and assumes no liability for device incompatibility either implied or stated in this Cross Reference Guide. Compatibility must be verified by the user.

Bold: Direct replacement (See above Note); Italics: Similar replacement; Blank: Either no replacement or no footprint compatible package.

| Company      | Family           | Pkg<br>Code | Package            | Motorola<br>Replacement | Pkg<br>Code | Comments                                                                                                |

|--------------|------------------|-------------|--------------------|-------------------------|-------------|---------------------------------------------------------------------------------------------------------|

| Philips      | 74LVC4245        | PW          | 4.4 mm TSSOP       | MC74LVX4245             | DT          | Similar replacement                                                                                     |

| Philips      | 74ALVC16xxx      | DL          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Philips      | 74ALVC16xxx      | DGG         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | ALVC is slightly faster, but LCX16xxx offers 5V toler-<br>ance                                          |

| Philips      | 74LVxxx          | N           | PDIP               | MC74LVXxxx              | Ν           | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs                      |

| Philips      | 74LVxxx          | D           | JEDEC SOIC         | MC74LVXxxx              | D           | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs. Alternate: 74LVQxxx |

| Philips      | 74LVxxx          | DB          | 5.3 mm SSOP II     |                         | SD          | For LVX, use TSSOP. Not footprint compatible. Alternate: 74LVQxxx                                       |

| Philips      | 74LVxxx          | D           | Wide JEDEC SOIC    | MC74LVXxxx              | DW          | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs Alternate: 74LVQxxx  |

| Philips      | 74LVxxx          | PW          | 4.4 mm TSSOP       | MC74LVXxxx              | DT          | LVX has 4mA drive vs. 6mA for LV. LVX is much faster<br>and has 5V tolerant inputs. Alternate: 74LVQxxx |

| IDT          | IDT74FCT3xxx     | Р           | PDIP               |                         |             | Use SOIC. Not footprint compatible                                                                      |

| IDT          | IDT74FCT3xxx     | SO          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement. LCX also features 5V tolerance                                                      |

| IDT          | IDT74FCT3xxx     | PY          | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | Direct replacement. LCX also features 5V tolerance                                                      |

| IDT          | IDT74FCT163xxx   | PV          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| IDT          | IDT74FCT163xxx   | PA          | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement. LCX also features 5V tolerance                                                      |

| IDT          | IDT74FCT3xxxA    | Р           | PDIP               |                         |             | Use SOIC. Not footprint compatible                                                                      |

| IDT          | IDT74FCT3xxxA    | SO          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | FCT3A slightly faster, but LCX offers 5V tolerance                                                      |

| IDT          | IDT74FCT3xxxA    | PY          | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | FCT3A slightly faster, but LCX offers 5V tolerance                                                      |

| IDT          | IDT74FCT163xxxA  | PV          | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| IDT          | IDT74FCT163xxxA  | PA          | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement. LCX also features 5V tolerance                                                      |

| Pericom      | PI74FCT163xxx    | V           | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74FCT163xxx    | А           | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement. LCX also features 5V tolerance                                                      |

| Pericom      | PI74FCT163xxxA   | V           | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74FCT163xxxA   | A           | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement. LCX also features 5V tolerance                                                      |

| Pericom      | PI74LPTxxx       | W           | JEDEC SOIC         | MC74LCXxxx              | D           | Direct replacement. LCX also features power down high–Z                                                 |

| Pericom      | PI74LPTxxx       | S           | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement. LCX also features power down high–Z                                                 |

| Pericom      | PI74LPTxxx       | Q           | QSOP               |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74LPTxxx       | R           | Thin QSOP          |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74LPTxxx       | L           | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | Direct replacement. LCX also features power down high–Z                                                 |

| Pericom      | PI74LPTxxxA/C    | W           | JEDEC SOIC         | MC74LCXxxx              | D           | LPTA/C slightly faster                                                                                  |

| Pericom      | PI74LPTxxxA/C    | S           | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | LPTA/C slightly faster                                                                                  |

| Pericom      | PI74LPTxxxA/C    | Q           | QSOP               |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74LPTxxxA/C    | R           | Thin QSOP          |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74LPTxxxA/C    | L           | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | LPTA/C slightly faster                                                                                  |

| Pericom      | PI74LPT16xxx/A/C | V           | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                                                     |

| Pericom      | PI74LPT16xxx/A/C | A           | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement                                                                                      |

| Pericom      | PI74LCXxxx       | W           | JEDEC SOIC         | MC74LCXxxx              | D           | Direct replacement                                                                                      |

| Pericom      | PI74LCXxxx       | S           | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement                                                                                      |

| Pericom      | PI74LCXxxx       | L           | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | Direct replacement                                                                                      |

| Pericom      | PI74LCX16xxx     | A           | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement                                                                                      |

| Quality Semi | QS74FCT3xxx      | so          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement. LCX also features power down                                                        |

NOTE: Motorola cannot guarantee device compatibility and assumes no liability for device incompatibility either implied or stated in this Cross Reference Guide. Compatibility must be verified by the user.

Bold: Direct replacement (See above Note); Italics: Similar replacement; Blank: Either no replacement or no footprint compatible package.

| Company      | Family         | Pkg<br>Code | Package            | Motorola<br>Replacement | Pkg<br>Code | Comments                                                                 |

|--------------|----------------|-------------|--------------------|-------------------------|-------------|--------------------------------------------------------------------------|

| Quality Semi | QS74FCT3xxx    | Q           | QSOP               |                         |             | Use TSSOP. Not footprint compatible                                      |

| Quality Semi | QS74FCT3xxxA   | SO          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | FCT3A slightly faster, but LCX offers 5V tolerance                       |

| Quality Semi | QS74FCT3xxxA   | Q           | QSOP               |                         |             | Use TSSOP. Not footprint compatible                                      |

| Quality Semi | QS74FCT163xxxA | Q2          | QVSOP              |                         |             | Use TSSOP. Not footprint compatible. LCX also features power down high–Z |

| Quality Semi | QS74LCXxxx     | SO          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement. Careful, QSI may not be spec compatible to LCX       |

| Quality Semi | QS74LCXxxx     | Q           | QSOP               |                         |             | Use TSSOP. Not footprint compatible                                      |

| Quality Semi | QS74LCX16xxx   | Q2          | QVSOP              |                         |             | Use TSSOP. Careful, QSI may not be spec compatible to LCX                |

| Toshiba      | TC74LCXxxx     | FN          | JEDEC SOIC         | MC74LCXxxx              | D           | Direct replacement                                                       |

| Toshiba      | TC74LCXxxx     | FW          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement                                                       |

| Toshiba      | TC74LCXxxx     | F           | EIAJ SOIC          | MC74LCXxxx              | М           | Direct replacement                                                       |

| Toshiba      | TC74LCXxxx     | FS          | 4.4 mm SSOP I      | MC74LCXxxx              | DT          | Direct replacement. TSSOP is footprint compatible with this SSOP         |

| Toshiba      | TC74LCX16xxx   | FT          | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement                                                       |

| Toshiba      | TC74LVXxxx     | FN          | JEDEC SOIC         | MC74LVXxxx              | D           | Direct replacement                                                       |

| Toshiba      | TC74LVXxxx     | FW          | Wide JEDEC SOIC    | MC74LVXxxx              | DW          | Direct replacement                                                       |

| Toshiba      | TC74LVXxxx     | F           | EIAJ SOIC I        | MC74LVXxxx              | М           | Direct replacement                                                       |

| Toshiba      | TC74LVXxxx     | FS          | 4.4 mm SSOP        | MC74LVXxxx              | DT          | Direct replacement. TSSOP is footprint compatible with this SSOP         |

| Toshiba      | TC74LVQxxx     | FN          | JEDEC SOIC         | MC74LVQxxx              | D           | Direct replacement                                                       |

| Toshiba      | TC74LVQxxx     | FW          | Wide JEDEC SOIC    | MC74LVQxxx              | DW          | Direct replacement                                                       |

| Toshiba      | TC74LVQxxx     | F           | EIAJ SOIC          | MC74LVQxxx              | М           | Direct replacement                                                       |

| Toshiba      | TC74LVQxxx     | FS          | 4.4 mm SSOP I      | MC74LVQxxx              | DT          | Direct replacement. TSSOP is footprint compatible with this SSOP         |

| Toshiba      | TC74LVX4245    | FS          | 4.4 mm SSOP I      | MC74LVX4245             | DT          | Direct replacement. TSSOP is footprint compatible with this SSOP         |

| National     | 74LCXxxx       | М           | JEDEC SOIC         | MC74LCXxxx              | D           | Direct replacement                                                       |

| National     | 74LCXxxx       | MSA         | 5.3 mm SSOP II     | MC74LCXxxx              | SD          | Direct replacement                                                       |

| National     | 74LCXxxx       | WM          | Wide JEDEC SOIC    | MC74LCXxxx              | DW          | Direct replacement                                                       |

| National     | 74LCXxxx       | SJ          | EIAJ SOIC          | MC74LCXxxx              | М           | Direct replacement                                                       |

| National     | 74LCXxxx       | MTC         | 4.4 mm TSSOP       | MC74LCXxxx              | DT          | Direct replacement                                                       |

| National     | 74LCX16xxx     | MEA         | 48/56 7.5 mm SSOP  |                         |             | Use TSSOP. Not footprint compatible                                      |

| National     | 74LCX16xxx     | MTD         | 48/56 6.1 mm TSSOP | MC74LCX16xxx            | DT          | Direct replacement                                                       |

| National     | 74LVXxxx       | М           | JEDEC SOIC         | MC74LVXxxx              | D           | Direct replacement                                                       |

| National     | 74LVXxxx       | WM          | Wide JEDEC SOIC    | MC74LVXxxx              | DW          | Direct replacement                                                       |

| National     | 74LVXxxx       | SJ          | EIAJ SOIC          | MC74LVXxxx              | М           | Direct replacement                                                       |

| National     | 74LVXxxx       | МТС         | 4.4 mm TSSOP       | MC74LVXxxx              | DT          | Direct replacement                                                       |

| National     | 74LVQxxx       | М           | JEDEC SOIC         | MC74LVQxxx              | D           | Direct replacement                                                       |

| National     | 74LVQxxx       | WM          | Wide JEDEC SOIC    | MC74LVQxxx              | DW          | Direct replacement                                                       |

| National     | 74LVQxxx       | SJ          | EIAJ SOIC          | MC74LVQxxx              | М           | Direct replacement                                                       |

| National     | 74LVQxxx       | QSC         | QSOP               |                         |             | Use TSSOP. Not footprint compatible                                      |

| National     | 74LVX4245      | М           | JEDEC SOIC         | MC74LVX4245             | D           | Direct replacement                                                       |

| National     | 74LVX4245      | мтс         | 4.4 mm TSSOP       | MC74LVX4245             | DT          | Direct replacement                                                       |

NOTE: Motorola cannot guarantee device compatibility and assumes no liability for device incompatibility either implied or stated in this Cross Reference Guide. Compatibility must be verified by the user.

Bold: Direct replacement (See above Note); Italics: Similar replacement; Blank: Either no replacement or no footprint compatible package.

## Introducing LCX Motorola's Low-Voltage CMOS Logic Family

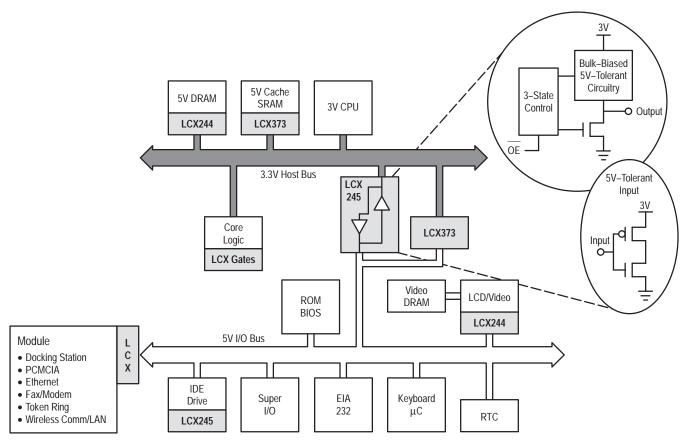

Motorola's 3V LCX family features 5V-tolerant inputs and outputs that enable easy transition from 5V to mixed 3V/5V systems or to 3V systems. Low power, low switching noise and fast switching speeds make this family perfect for low power portable applications as well as high-end, advanced workstation applications.

The unique feature of this family is its ability to interface to pure 3V or both 3V and 5V buses in the same design without sacrificing performance. The LCX family improves system performance by drastically reducing static and dynamic power consumption which extends battery life for portable and handheld applications. Customers also realize simplified system design in mixed voltage environments, as well as expedited development of their low voltage systems. The 3V/5V interface using LCX, requires no other special components that would be necessary to protect other low voltage logic families that cannot tolerate signals beyond the V<sub>CC</sub> supply level.

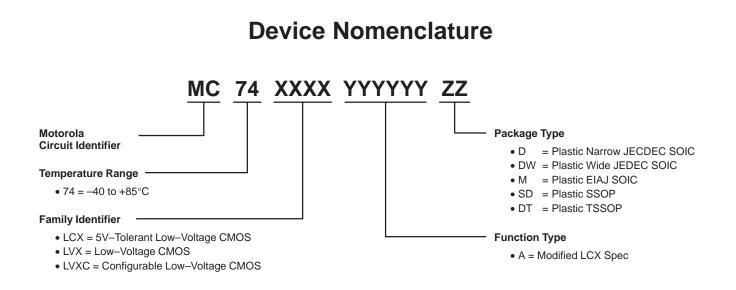

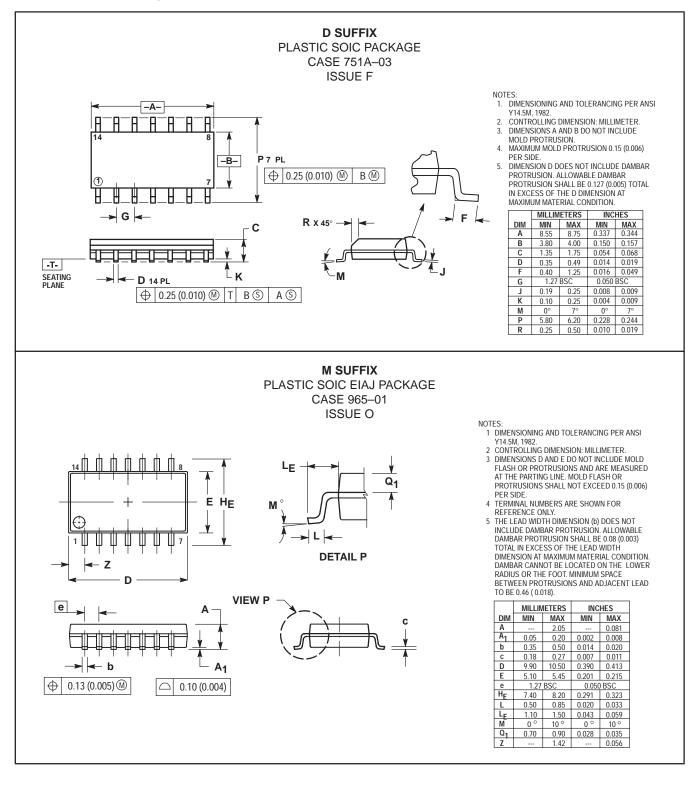

The Motorola LCX family is available in industry standard JEDEC SOIC, EIAJ SOIC, SSOP type 2, and TSSOP packages. LCX family specifications range from –40°C to +85°C. The LCX family was developed in accordance with an alliance including Motorola and two other major semiconductor suppliers, so there are alternate sources available now.

- Designed for 2.7 to 3.6V V<sub>CC</sub> Operation

- 5V Tolerant Interface Capability With 5V TTL Logic

- Supports Live Insertion/Withdrawal (3-State Devices)

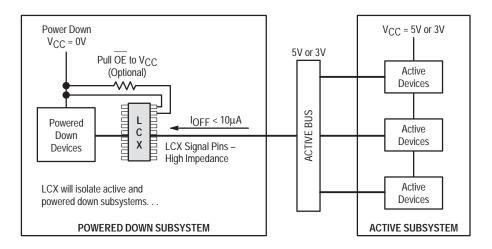

- IOFF Specification Guarantees High Impedance When V<sub>CC</sub> = 0V (3–State Devices)

- LVTTL Compatible

- LVCMOS Compatible

- 24mA Balanced Output Sink and Source Capability

- Near Zero Static Supply Current in All Three Logic States (10μA) Substantially Reduces System Power Requirements

- Latchup Performance Exceeds 500mA

- ESD Performance: Human Body Model >2000V; Machine Model >200V

## **LCX Family Specifications**

To assist the designer in evaluating the performance of Motorola's LCX family, data specifications and actual performance information are included here.

| Symbol           | Parameter                        | Value                               | Condition                        | Unit |

|------------------|----------------------------------|-------------------------------------|----------------------------------|------|

| VCC              | DC Supply Voltage                | -0.5 to +7.0                        |                                  | V    |

| VI               | DC Input Voltage                 | $-0.5 \le V_I \le +7.0$             |                                  | V    |

| VO               | DC Output Voltage                | $-0.5 \le V_{O} \le +7.0$           | Output in 3–State                | V    |

|                  |                                  | $-0.5 \leq V_{O} \leq V_{CC} + 0.5$ | Note 1.                          | V    |

| IIК              | DC Input Diode Current           | -50                                 | V <sub>I</sub> < GND             | mA   |

| Іок              | DC Output Diode Current          | -50                                 | V <sub>O</sub> < GND             | mA   |

|                  |                                  | +50                                 | V <sub>O</sub> > V <sub>CC</sub> | mA   |

| IO               | DC Output Source/Sink Current    | ±50                                 |                                  | mA   |

| ICC              | DC Supply Current Per Supply Pin | ±100                                |                                  | mA   |

| IGND             | DC Ground Current Per Ground Pin | ±100                                |                                  | mA   |

| T <sub>STG</sub> | Storage Temperature Range        | -65 to +150                         |                                  | °C   |

#### ABSOLUTE MAXIMUM RATINGS\*

\* Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute-maximum-rated conditions is not implied.

1. Output in HIGH or LOW State.  $\mathrm{I}_{O}$  absolute maximum rating must be observed.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                                                                                     |            | Тур        | Max                    | Unit |

|-----------------|-----------------------------------------------------------------------------------------------|------------|------------|------------------------|------|

| VCC             | Supply Voltage Operating Data Retention Only                                                  | 2.0<br>1.5 | 3.3<br>3.3 | 3.6<br>3.6             | V    |

| VI              | Input Voltage                                                                                 | 0          |            | 5.5                    | V    |

| VO              | Output Voltage (HIGH or LOW State)<br>(3–State)                                               | 0<br>0     |            | V <sub>CC</sub><br>5.5 | V    |

| ЮН              | HIGH Level Output Current, V <sub>CC</sub> = 3.0V – 3.6V                                      |            |            | -24                    | mA   |

| IOL             | LOW Level Output Current, V <sub>CC</sub> = 3.0V – 3.6V                                       |            |            | 24                     | mA   |

| ЮН              | HIGH Level Output Current, $V_{CC} = 2.7V - 3.0V$                                             |            |            | -12                    | mA   |

| I <sub>OL</sub> | LOW Level Output Current, V <sub>CC</sub> = 2.7V – 3.0V                                       |            |            | 12                     | mA   |

| T <sub>A</sub>  | Operating Free–Air Temperature                                                                | -40        |            | +85                    | °C   |

| Δt/ΔV           | Input Transition Rise or Fall Rate, V <sub>IN</sub> from 0.8V to 2.0V, V <sub>CC</sub> = 3.0V | 0          |            | 10                     | ns/V |

#### DC ELECTRICAL CHARACTERISTICS

|                 |                                       |                                                                                                         |                       | T <sub>A</sub> = −40°C to +85°C |      |

|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|------|

| Symbol          | Characteristic                        | Condition                                                                                               | Min                   | Max                             | Unit |

| VIH             | HIGH Level Input Voltage (Note 2.)    | $2.7V \le V_{CC} \le 3.6V$                                                                              | 2.0                   |                                 | V    |

| VIL             | LOW Level Input Voltage (Note 2.)     | $2.7V \le V_{CC} \le 3.6V$                                                                              |                       | 0.8                             | V    |

| VOH             | HIGH Level Output Voltage             | $2.7V \le V_{CC} \le 3.6V; I_{OH} = -100\mu A$                                                          | V <sub>CC</sub> – 0.2 |                                 | V    |

|                 |                                       | $V_{CC} = 2.7V; I_{OH} = -12mA$                                                                         | 2.2                   |                                 | 1    |

|                 |                                       | $V_{CC} = 3.0V; I_{OH} = -18mA$                                                                         | 2.4                   |                                 |      |

|                 |                                       | $V_{CC} = 3.0V; I_{OH} = -24mA$                                                                         | 2.2                   |                                 | 1    |

| VOL             | LOW Level Output Voltage              | $2.7V \le V_{CC} \le 3.6V; I_{OL} = 100\mu A$                                                           |                       | 0.2                             | V    |

|                 |                                       | V <sub>CC</sub> = 2.7V; I <sub>OL</sub> = 12mA                                                          |                       | 0.4                             | 1    |

|                 |                                       | V <sub>CC</sub> = 3.0V; I <sub>OL</sub> = 16mA                                                          |                       | 0.4                             |      |

|                 |                                       | $V_{CC} = 3.0V; I_{OL} = 24mA$                                                                          |                       | 0.55                            | 1    |

| lj              | Input Leakage Current                 | $2.7 \text{V} \le \text{V}_{CC} \le 3.6 \text{V}; \ 0 \text{V} \le \text{V}_{I} \le 5.5 \text{V}$       |                       | ±5.0                            | μΑ   |

| I <sub>OZ</sub> | 3-State Output Current                | $2.7 \leq V_{CC} \leq 3.6V; \ 0V \leq V_O \leq 5.5V; \\ V_I = V_{IH} \ or \ V_{IL}$                     |                       | ±5.0                            | μA   |

| IOFF            | Power-Off Leakage Current (Note 3.)   | $V_{CC} = 0V; V_{I} \text{ or } V_{O} = 5.5V$                                                           |                       | 10                              | μΑ   |

| ICC             | Quiescent Supply Current              | $2.7 \le V_{CC} \le 3.6V; V_I = GND \text{ or } V_{CC}$                                                 |                       | 10                              | μΑ   |

|                 |                                       | $2.7 \leq V_{CC} \leq 3.6 \text{V}; \ 3.6 \leq \text{V}_{I} \text{ or } \text{V}_{O} \leq 5.5 \text{V}$ |                       | ±10                             | μΑ   |

| ∆ICC            | Increase in I <sub>CC</sub> per Input | $2.7 \le V_{CC} \le 3.6V; V_{IH} = V_{CC} - 0.6V$                                                       |                       | 500                             | μA   |

2. These values of VI are used to test DC electrical characteristics only.

3. IOFF is applicable only to devices with 3-state outputs.

#### DYNAMIC SWITCHING CHARACTERISTICS

|                  |                                      |                                                                                                                                                                                                      | T <sub>A</sub> = +25°C |     |     |      |

|------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|------|

| Symbol           | Characteristic                       | Condition                                                                                                                                                                                            | Min                    | Тур | Max | Unit |

| V <sub>OLP</sub> | Dynamic LOW Peak Voltage (Note 4.)   | $V_{\mbox{\scriptsize CC}}$ = 3.3V, $\mbox{\scriptsize C}_{\mbox{\scriptsize L}}$ = 50pF, $\mbox{\scriptsize V}_{\mbox{\scriptsize IH}}$ = 3.3V, $\mbox{\scriptsize V}_{\mbox{\scriptsize IL}}$ = 0V |                        | 0.8 |     | V    |

| VOLV             | Dynamic LOW Valley Voltage (Note 4.) | $V_{CC}$ = 3.3V, $C_L$ = 50pF, $V_{IH}$ = 3.3V, $V_{IL}$ = 0V                                                                                                                                        |                        | 0.8 |     | V    |

Number of outputs defined as "n". Measured with "n-1" outputs switching from HIGH-to-LOW or LOW-to-HIGH. The remaining output is measured in the LOW state.

## LCX Family Specifications

#### **CAPACITIVE CHARACTERISTICS**

| Symbol           | Parameter                          | Condition                                      | Typical | Unit |

|------------------|------------------------------------|------------------------------------------------|---------|------|

| C <sub>IN</sub>  | Input Capacitance                  | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$       | 7       | pF   |

| COUT             | Output Capacitance                 | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$       | 8       | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance (Note 5.) | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$       | 8       | pF   |

| C <sub>PD</sub>  | Power Dissipation Capacitance      | 10MHz, $V_{CC}$ = 3.3V, $V_I$ = 0V or $V_{CC}$ | Note 6. | pF   |

5. Bidirectional devices only.

6. Function dependent, see individual datasheets.

| TEST                                | SWITCH |

|-------------------------------------|--------|

| <sup>t</sup> PLH <sup>, t</sup> PHL | Open   |

| tPZL, tPLZ                          | 6V     |

| Open Collector/Drain tPLH and tPHL  | 6V     |

| <sup>t</sup> PZH <sup>, t</sup> PHZ | GND    |

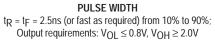

$C_L = 50 pF$  or equivalent (Includes jig and probe capacitance)  $R_L = R_1 = 500\Omega$  or equivalent  $R_T = Z_{OUT}$  of pulse generator (typically 50 $\Omega$ )

Figure 2. LCX Test Circuit

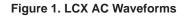

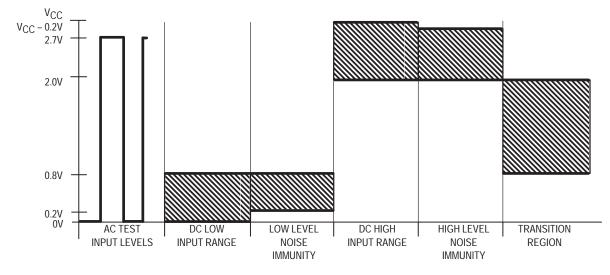

$\begin{array}{l} \textbf{PULSE WIDTH} \\ t_R = t_F = 2.5ns \text{ (or fast as required) from 10% to 90\%;} \\ \text{Output requirements: } V_{OL} \leq 0.8V, \ V_{OH} \geq 2.0V \end{array}$

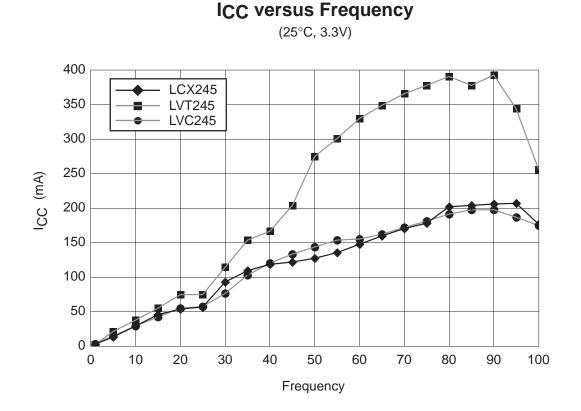

#### Figure 3. LVX AC Waveforms

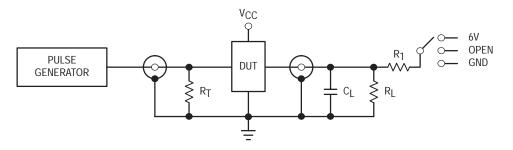

| TEST                                                                   | SWITCH            |

|------------------------------------------------------------------------|-------------------|

| <sup>t</sup> PLH, <sup>t</sup> PHL, <sup>t</sup> PZH, <sup>t</sup> PHZ | Open              |

| <sup>t</sup> PZL, <sup>t</sup> PLZ                                     | $2 \times V_{CC}$ |

$C_1 = 50 \text{pF}$  or equivalent (Includes jig and probe capacitance)

$R_L = R_1 = 500\Omega$  or equivalent

$R_T = Z_{OUT}$  of pulse generator (typically 50 $\Omega$ )

#### Figure 4. LVX Test Circuit

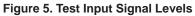

#### LCXxxx Devices

### **Test Conditions**

Figure 5 describes the input signal voltage levels to be used when testing LCX circuits. The AC test conditions follow industry convention requiring V<sub>IN</sub> to range from 0 V for a logic LOW to 2.7V for a logic HIGH. The DC parameters are normally tested with V<sub>I</sub> at guaranteed input levels, that is V<sub>IH</sub> to V<sub>IL</sub> (see datasheets for details). Care must be taken to adequately decouple these high performance parts and to protect the test signals from electrical noise. In an electrically designed for high speed work), DC input levels may need adjustment to increase the noise margin allowance for the tester. This noise will not likely be seen in a system environment.

Noise immunity testing is performed by raising V<sub>I</sub> to the nominal supply voltage of 3.3V then dropping to a level corresponding to V<sub>IH</sub> characteristics, and then raising it again to the 3.3V level. Noise tests are performed on the V<sub>IL</sub> characteristics by raising V<sub>I</sub> from 0 V to V<sub>IL</sub>, then returning to 0 V. Both V<sub>IH</sub> and V<sub>IL</sub> noise immunity tests should not induce a switch condition on the appropriate outputs of the LCX device.

Good high frequency wiring practices should be used in constructing test jigs. Leads on the load capacitor should be as short as possible to minimize ripples on the output wave form transitions and to minimize undershoot. Generous ground metal (preferably a ground plane) should be used for the same reasons. A V<sub>CC</sub> bypass capacitor should be provided at the test socket, also with minimum lead lengths.

### **Rise and Fall Times**

Input signals should have rise and fall times of 2.5ns or less (10% to 90%), and signal swing of 0V to 2.7V. Rise and fall times less than or equal to 1ns should be used for testing  $f_{max}$  or pulse widths.

CMOS devices tend to oscillate when the input rise and fall times become lengthy. As a direct result of its increased performance, LCX devices can be more sensitive to slow input rise and fall times than other lower performance technologies. Recommended edge rate is  $\leq 10$  ms/V.

It is important to understand why this oscillation occurs. Consider the outputs, where the problem is initiated. Usually, CMOS outputs drive capacitive loads with low DC leakage. When the output changes from a HIGH level to a LOW level, or from a LOW level to a HIGH level, this capacitance is charged or discharged. With the present high performance technologies, charging or discharging takes place in a very short time, typically 2–3ns. The requirement to charge or discharge the capacitive loads quickly creates a condition where the instantaneous current change through the output structure is quite high. A voltage is generated across the  $V_{CC}$  or ground leads inside the package due to the lead inductance. The internal ground of the chip will change in reference to the outside world because of this induced voltage.

Next, consider the inputs. If the internal ground changes, the input voltage level appears to change to the DUT. If the input rise time is slow enough, its level might still be in the threshold region, or very close to it, when the output switches. If the internally–induced voltage is large enough, it is possible to shift the threshold enough so that it re–crosses the input level. If the gain of the device is sufficient and the input rise or fall time is slow enough, then the device may go into oscillation. As device propagation delays become shorter, the inputs will have less time to rise or fall through the threshold region. As device gains increase, the outputs will swing more, creating more induced voltage. Instantaneous current change will be greater as outputs become quicker, generating more induced voltage.

Package–related causes of output oscillation are not entirely to blame for problems with input rise and fall time measurements. All testers have  $V_{CC}$  and ground leads with some finite inductance. This inductance must be added to the inductance of the package to determine the overall voltage which will be induced when the outputs change. As the reference for the input signals moves further away from the pin under test, the test will be more susceptible to problems caused by the inductance of the leads and stray noise. Any noise on the input signal will also cause problems.

### **Enable and Disable Times**

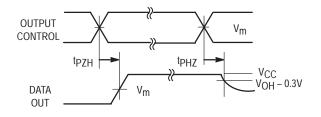

Figure 9 and Figure 10 show that the disable times are measured at the point where the output voltage has risen or fallen by 0.3V from the voltage rail level (i.e., ground for tpj 7 or V<sub>CC</sub> for t<sub>PHZ</sub>). This change enhances the repeatability of measurements, reduces test times, and gives the system designer more realistic delay times to use in calculating minimum cycle times. Since the high-impedance state rising or falling waveform is RC-controlled, the first 0.3V of change is more linear and is less susceptible to external influences. More importantly, perhaps from the system designer's point of view, a change in voltage of 0.3V is adequate to ensure that a device output has turned OFF. Measuring to a larger change in voltage merely exaggerates the apparent Disable time artificially penalizing system performance (since the designer must use the Enable and Disable times to figure worst case timing.)

# Propagation Delay, f<sub>max</sub>, Set, Hold, and Recovery Times

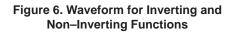

A 1 MHz square wave is recommended for most propagation delay tests. The repetition rate must necessarily be increased for testing  $f_{max}$ . A 50% duty cycle should always be used when testing  $f_{max}$ . Two pulse generators are usually required for testing such parameters as setup time ( $t_s$ ), hold time ( $t_h$ ), recovery time ( $t_{REC}$ ) shown in Figure 8.

### **Electrostatic Discharge**

Precautions should be taken to prevent damage to devices by electrostatic discharge. Static charge tends to accumulate on insulated surfaces such as synthetic fabrics or carpeting, plastic sheets, trays, foam, tubes or bags, and on ungrounded electrical tools or appliances. The problem is much worse in a dry atmosphere. In general, it is recommended that individuals take the precaution of touching a known ground before handling devices. To effectively avoid electrostatic damage to LCX devices, it is recommended that individuals wear a grounded wrist strap when handling devices. More often, handling equipment, which is not properly grounded, causes damage to parts. Ensure that all plastic parts of the tester, which are near the device, are conductive and connected to ground.

V<sub>m</sub> = 1.5V

Figure 8. Setup Time, Hold Time and Recovery Time

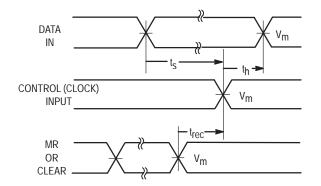

Figure 7. Propagational Delay, Pulse Width and trec Waveforms

#### Figure 9. 3–State Output High Enable and Disable Times

V<sub>m</sub> = 1.5V

Figure 10. 3–State Output Low Enable and Disable Times

## **Definitions of Symbols**

#### **DC Characteristics**

Currents Positive current is defined as conventional current flow into a device. Negative current is defined as current flow out of a device.

Voltages All voltages are referenced to the ground pin.

- ICC The current flowing into the V<sub>CC</sub> supply terminal when the device is at a quiescent state.

- ICCH The current flowing into the V<sub>CC</sub> supply terminal when the outputs are in the HIGH state.

- ICCL The current flowing into the V<sub>CC</sub> supply terminal when the outputs are in the LOW state.

- ICCZ The current flowing into the V<sub>CC</sub> supply terminal when the outputs are disabled (high impedance).

- $\Delta I_{CC}$  Additional I<sub>CC</sub> due to TTL HIGH levels (V<sub>CC</sub>-0.6V) forced on CMOS inputs.

- II Input Current. The current flowing into or out of an input when a specified LOW or HIGH voltage is applied to that input.

- IOH Output HIGH Current. The current flowing out of an output which is in the HIGH state.

- IOL Output LOW Current. The current flowing into an output which is in the LOW state.

- IOS Output Short Circuit Current. The current flowing out of an output in the HIGH state when that output is shorted to ground (or other specified potential).

- I<sub>OZ</sub> Output high impedance current. The current flowing into or out of a disabled output when specified LOW or HIGH voltage is applied to that output.

- IOFF Input/Output power-off leakage current. The maximum leakage current into or out of the input/output transistors when forcing the input/output from 0V to 5.5V with V<sub>CC</sub> = 0V.

- V<sub>CC</sub> Supply Voltage. The range of power supply voltages over which the device is guaranteed to operate.

- VIH Input HIGH Voltage. The minimum input voltage that is recognized as a DC HIGH level.

- VIL Input LOW Voltage. The maximum input voltage that is recognized as a DC LOW level.

- V<sub>OH</sub> Output HIGH Voltage. The voltage at an output conditioned HIGH with a specified output load and V<sub>CC</sub> supply voltage.

- VOL Output LOW Voltage. The voltage at an output conditioned LOW with a specified output load and V<sub>CC</sub> supply voltage.

- VOLP Maximum (peak) voltage induced on a static LOW output during switching of other outputs.

- VOLV Minimum (valley) voltage induced on a static LOW output during switching of other outputs.

#### **AC Characteristics**

$f_{max}$  Toggle Frequency/Operating Frequency – The maximum rate at which clock pulses may be applied to a sequential circuit. Above this frequency the device may cease to function properly.

**tp<sub>LH</sub> Propagation Delay Time** – The time between the specified reference points, on the input and output voltage waveforms, with the output changing from the defined LOW level to the defined HIGH level.

**tpHL Propagation Delay Time** – The time between the specified reference points, on the input and output voltage waveforms, with the output changing from the defined HIGH level to the defined LOW level.

$t_{\bm{W}}$  **Pulse Width** – The time between specified amplitude points of the leading and trailing edges of a pulse.

$t_{h}$  Hold Time – The interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition.

$t_{s}$  Setup Time – The interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition.

**tpHZ Output Disable Time (of a 3–state Output) from HIGH Level** – The time between specified levels on the input and a voltage 0.3V below the steady state output HIGH level with the 3–state output changing from the defined HIGH level to a high impedance (OFF) state.

**tp\_z** Output Disable Time (of a 3–state Output) from LOW Level – The time between specified levels on the input and a voltage 0.3V above the steady state output LOW level with the 3–state output changing from the defined LOW level to a high impedance (OFF) state.

**tpzH Output Enable Time (of a 3–state Output) to a HIGH Level** – The time between the specified levels of the input and output voltage waveforms with the 3–state output changing from a high impedance (OFF) state to a HIGH level.

**tpzL Output Enable Time (of a 3–state Output) to a LOW Level** – The time between the specified levels of the input and output voltage waveforms with the 3–state output changing from a high impedance (OFF) state to a LOW level.

$t_{rec}$  Recovery Time – The time between the specified level on the trailing edge of an asynchronous input control pulse and the same level on a synchronous input (clock) pulse such that the device will respond to the synchronous input.

## **LCX Family Characteristics**

## LCX and LVT Products

| Product Family                          | 74LCX244                   | 74LVC244A               | 74LVT244A               |

|-----------------------------------------|----------------------------|-------------------------|-------------------------|

| Technology                              | CMOS                       | CMOS                    | BiCMOS                  |

| I <sub>CCL</sub> (mA)                   | 0.01                       | 0.01                    | 12.0                    |

| ICC vs Frequency (50MHz)                | 130mA                      | 145mA                   | 275mA                   |

| Speed                                   | 6.5ns                      | 6.5ns                   | 4.1ns                   |

| Drive (2.0V/0.55V)<br>JEDEC (2.4V/0.4V) | >–24mA/24mA<br>–18mA/16mA  | -24mA/24mA<br>-12mA/??? | –32mA/64mA<br>–8mA/16mA |

| 5V Tolerant Inputs<br>Outputs           | YES<br>YES                 | YES<br>YES              | YES<br>YES*             |

| Power–Down High–Z (IOFF)                | <b>YES (10</b> μ <b>A)</b> | NO                      | YES (±100μA)            |

| Data Retention                          | YES                        | YES                     | NO                      |

\* LVT claims, but does not specify, 5V–Tolerant outputs. LCX can be used to replace LVC; be careful when exchanging LCX with LVC as not all LVC functions have 5V–tolerance!!

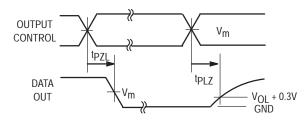

The following graph compares the 5V-tolerance capability of LCX, LVC and LVT. When LCX is not driving the bus (outputs are disabled), the levels on that bus can exceed the LCX  $V_{CC}$  with no adverse effect on the device or any loading on the bus. In fact, test data shows that a disabled LCX output can "tolerate" signals over 13V on the outputs!

## **5V Output Tolerance**

$(I_{OZ} vs V_{OUt}, V_{CC} = 2.7V, +25^{\circ}C)$

### LCX Family Characteristics

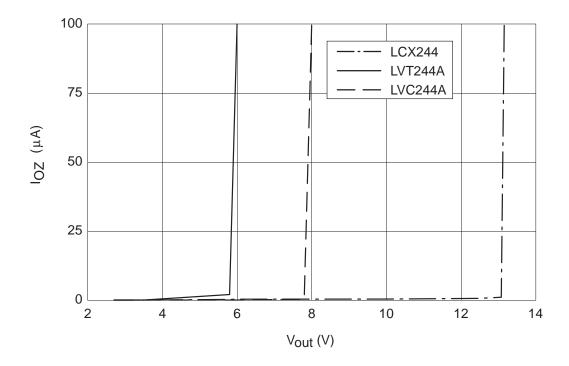

Another advantage of the LCX family is the low dynamic current. Low dynamic current means low power consumption. Low power consumption means smaller power supplies, longer battery life and physically smaller systems. The following graph shows the Motorola 74LCX245's I<sub>CC</sub> vs. Frequency performance with 8 outputs switching. To give an idea of power improvement that can be had with low voltage logic, a 74LCX245 consumes about the same power running at 35MHz that a 74F245 does statically. At 100MHz the LCX device only consumes about 200mA.

## LCX — Low–Voltage CMOS Logic (WIth 5V–Tolerant Inputs and Outputs)

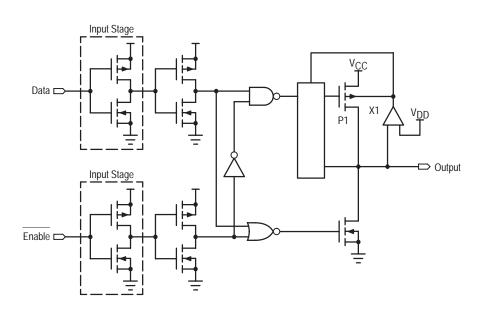

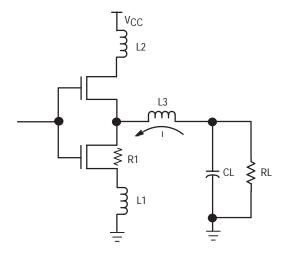

The LCX family represents Motorola's Low-Voltage CMOS family. These devices offer mixed 3V-5V capability and are recommended for applications where 3.3V and 5V subsystems interface with one another and where low power consumption is a necessity. The input and output (Note 1) structures of the LCX family of products will tolerate input and output node exposure to signals or DC levels that exceed the V<sub>CC</sub> level (Note 2). Refer to Figure 11 for schematic description of a typical LCX circuit. Note that the output PMOS device P1 has its bulk potential supplied by the output of the comparator X1 rather than by V<sub>CC</sub> as in conventional CMOS. The circuitry contained within the comparator is designed such that the output is always the greater of V<sub>CC</sub> or V<sub>O</sub>. This technique circumvents the P+/N- bulk-source forward junction that usually appears between the PMOS drain at the output and the bulk connection of the output PMOS which is usually tied to V<sub>CC</sub>. Eliminating this junction is fundamental to the powered-down high Z and overvoltage tolerance features that distinguish Motorola's LCX family from other Low-Voltage CMOS products.

NOTE 1: U.S. Patent 5,451,889.

NOTE 2: Output overvoltage is permitted unconditionally for 3–stated outputs. For active outputs, see datasheet.

## LVX-Low Voltage Dual Supply Translating Transceivers

In applications where 3.3V signals must be "stepped up" to 5V, in order to interface full swing CMOS busses, LCX may not be the proper solution. The LVX translating transceiver designs have an entirely different approach to solve the mixed supply interface problem. These devices are not overvoltage tolerant, but rather true voltage translators meaning that they receive 3V signals and output 5V signals, and receive 5V signals and output 3V signals (which can also be accomplished with LCX). This is done by dividing the devices internally so that the A–side circuitry is isolated from the B–side circuitry. The dual supply architecture allows the LVX translators to interface 3V and 5V signals with near–zero static power dissipation.

The MC74LVX4245 A–side is dedicated to 5V operation, with V<sub>CCA</sub> specified over the 4.5V–5.5V range. The B–side is dedicated to 3.3V, with V<sub>CCB</sub> specified over the 2.7V–3.6V range.

The MC74LVXC3245 offers enhanced interfacing features. The B-side is designed to operate over an extended range of I/O and supply levels. The VCCB is permitted to be set to any value between 2.7V and 5.5V. The I/O levels on the B-side will track or scale automatically according to the level set on V<sub>CCB</sub>. The B-side operation is completely independent of V<sub>CCA</sub>. The A-port and control input buffers are referenced to VCCA, totally independent of V<sub>CCB</sub>. The configurable dual supply translating transceiver, LVXC3245, is designed to tolerate floating inputs on the B-port when V<sub>CCA</sub> and the control signals are set to valid operating levels. The combination of this on-the-fly interface flexibility together with "empty socket" tolerance is intended to benefit designers of PC card systems (or PCMCIA) where expansion cards with different supply potentials must be accommodated.

The LVX dual supply translators offer switching speeds equivalent to 5V FCT/FAST but with low ground noise and very low power dissipation.

Figure 11. Simplified LCX Schematic Diagram

## **LCX Applications Information**

#### Introduction

Many system designers concerned about reducing power in mobile computing and communications are unnecessarily avoiding the use of 3.3V products because of either cost or the *dreaded* 3V/5V interface. Cost may be a concern, but nearly every new 3.3V device has better performance – either increased speed, reduced power, or both – when compared to a 5V "counterpart". In the long run it could easily cost the equipment maker more to continue with older technology rather than make the move to 3.3V or mixed 3.3V/5V systems.

There are three major reasons that chip manufacturers are accelerating the introduction of low voltage devices. First-DRAM manufacturers are worried about damage to products with fine geometries. As memory becomes more dense, feature geometries by necessity shrink. Voltages as high as 5V would damage these compactly designed RAMs. Second-as processor manufacturers have increased the performance of their chips, they have found that packages could not handle the increased power dissipation need. The enabling factor was to move to 3.3V supplies. Power dissipation varies roughly by the ratio of the squares of the  $V_{C,CS}$ ,  $(P_D \cong (V_{C,C}^2)$  (capacitance) (frequency)), so the ratio of reduction in power is  $3.3^2/5^2$  (11/25) when moving from 5V to 3.3V. Third-Battery-powered system manufactures are continually working for extended battery life. Obviously a 56+% reduction in power would considerably extend battery life. There are other benefits as well. Smaller packaging can be used to house the low voltage chips-saving board space and making the end product smaller and lighter. Smaller or fewer power supplies are required, and costly, spacehogging heat dissipating equipment can be eliminated.

Most 3.3V logic families can directly interface with only 3.3V products. LVC, LVX, VHC, LVQ/FACT AC, FCT3, and HC product families are lines that may work well for pure 3.3V system interface. Of these families only LVX and redesigned LVC guarantee 5V–tolerant inputs. The other families can tolerate maximum input and output levels of only V<sub>CC</sub>+0.5V. If a 5V TTL bus voltage swings to levels that exceed these specifications then the non 5V–tolerant products may be damaged, destroyed, load the bus, or current may be sourced into the 3.3V supply. Not only is it important to be 5V–tolerant on the inputs but to be 5V–tolerant on the outputs as well.

The LCX logic family provides the necessary circuitry to bridge the technology gap between the 5V and 3.3V worlds. The inputs of this low voltage family can be safely driven to 5.5V, guaranteed, easily handling a 5V TTL or 5V CMOS interface on the input bus. When the LCX device outputs, or I/Os, have finished their tasks and are in the high–impedance state, the voltage levels on the bus to which they are tied may rise well above the 3.3V V<sub>CC</sub>, up to 5.5V without loading the bus or causing damage to the device or power supply, guaranteed. This capability has been properly termed 5V

*tolerant*, rather than 3.3V/5V translation which is a misnomer. (Products that are powered by 3.3V supplies do not drive 5V rail-to-rail output swings. Dual 3.3V/5V supply devices are needed to drive 5V CMOS level outputs. See 74LVXC3245 and 74LVX4245-translating transceivers.)

There is no longer reason to fear mixed voltage designs. The LCX CMOS family is available now to help you bridge the 3.3V-5V interface.

#### **Interfacing Dual Systems**

To properly interface between integrated circuits, it is imperative that input and output specifications be reviewed and voltage and current levels satisfied. Output specifications ( $V_{OH}$  and  $V_{OL}$ ) of the driving device must meet or exceed the input requirements ( $V_{IH}$  and  $V_{IL}$ ) of the receiving device for the interface to function properly. Meeting these requirements protects against malfunction when operating at different environments which may induce noise to the interface.

The 5V power supply has been the standard for many years in the IC world. Several product families have been introduced with varying speeds, drive capabilities, and power requirements. Because of this many I/O standards have evolved complicating the interface between 5V devices. The move to 3.3V power supplies actually simplifies the interface problem. Pure Bipolar products cannot function at 3.3V, so the core technology is either BiCMOS or pure CMOS. In a pure 3.3V MOS environment the interface can be made directly–inputs and outputs. However, it will be several years before all system components operate from 3.3V supplies. This is especially true for peripheral devices such as printers, displays, and faxes.

## Interfacing 5V–TTL to Pure 3.3V Logic (No 5V–Tolerance)

When the desired interface is 5V-TTL to pure 3.3V CMOS (such as FACT AC or LVQ), the solution becomes a little messy. The designer must make sure that the 5V-TTL outputs do not exceed the 3.3V CMOS input specifications. There are a few options available to protect the 3.3V device from excessive input current. The 3.3V and 5V power supplies should be regulated together. It would also be a benefit to run the 5V supply on the low side reducing the VCC-VOH difference. If, however, the power supplies are not regulated together and the supplies end up at 5V+10% and 3.3V-10% then the CMOS input specifications would likely be violated. To keep within the CMOS input specification the 5V-TTL output cannot exceed 0.5V + V<sub>CC</sub> of the CMOS device. The simplest way to insure that VOH remains within the input specification of the CMOS part is to use a parallel termination resistor tied to ground. There are also CMOS switches that can be placed between the 5V and 3.3V devices to reduce the VOH, but this solution is very expensive.

## Interfacing 5V–CMOS to Pure 3.3V Logic (No 5V–Tolerance)

When the interface is a 5V CMOS device and a 3.3V CMOS device *without 5V-tolerance*, the problem is much the same as with the 5V–TTL interface–but worse. The output of the 5V device must be reduced or large currents will flow into the 3.3V device. This type of interface is simply not recommended.

## Interfacing Pure 3.3V Logic to 5V Inputs (No 5V Output Tolerance)

Interfacing 3.3V CMOS to 5V-TTL inputs can be done directly. LVCMOS/LVTTL output specifications and 5V-TTL input specifications are compatible. However, when interfacing pure 3.3V parts (no 5V-tolerance) to a 5V bus there is no protection against 5V signals when the 3.3V output is disabled. If the 5V bus voltage levels exceed the VCC of the 3.3V device, leakage current into the 3.3V device will occur-loading the bus. Also, be aware of 5V buses with pull-up resistors. If pull-up resistors are used then pull-down resistors may be necessary to compensate and reduce the high voltage level to within the 0.5V + V<sub>CC</sub> range of the 3.3V device. Interfacing a 3.3V CMOS output to a 5V CMOS input is discouraged. The output swing of the 3.3V device is insufficient to reliably drive the 5V CMOS device without the assistance of a pull-up resistor. If a pull-up resistor to 5V V<sub>CC</sub> is used to raise the input level to the required V<sub>IH</sub>=3.15V (for V<sub>CC</sub>=5V, higher for higher V<sub>CC</sub>s) then a massive current flow may result into the 3.3V device.

#### Interfacing to 5V–Tolerant LCX CMOS Logic

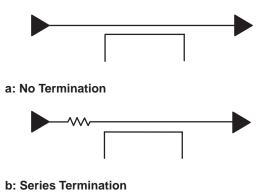

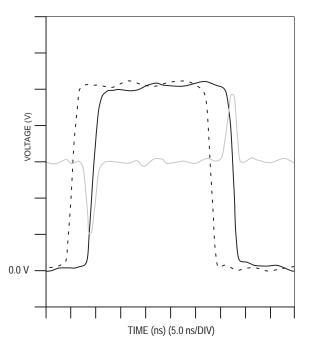

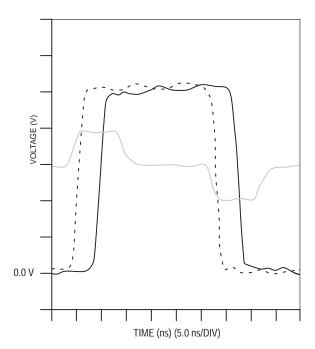

Many of the problems and concerns associated with pure 3.3V interface can be resolved simply by using 5V-tolerant LCX CMOS Logic. LCX tolerates 5V-TTL or 5V CMOS levels on its inputs. There is no inherent leakage path that can damage the device or in any way adversely affect this interface.