# 8-PIN HIGH-EFFICIENCY, OFFLINE LED LIGHTING CONTROLLER

Check for Samples: UCL64010

#### **FEATURES**

- LED Lighting Current Driver Controller with Energy Saving Features

- Quasi-Resonant Mode Operation for Reduced EMI and Low Switching Losses (Low Voltage Switching)

- Low Standby Current for Deep Dimming Efficiency Power Consumption

- Low Startup Current: 25 μA Maximum

- Programmable Line and Load Overvoltage Protection

- Provides Open LED Protection

- Internal Overtemperature Protection

- Current Limit Protection

- Cycle-by-Cycle Power Limit

- Primary-Side Overcurrent Hiccup Restart Mode

- 1-A Sink TrueDrive<sup>™</sup>, –0.75-A Source Gate Drive Output

- Programmable Soft-Start

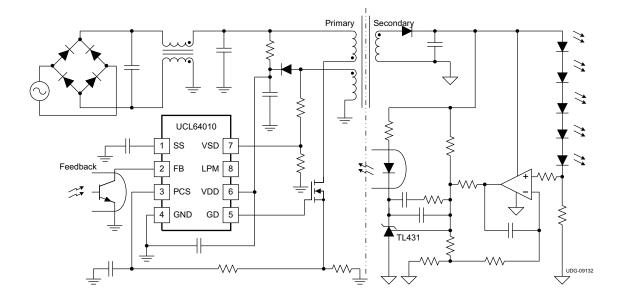

## **APPLICATIONS**

- Residential LED Lighting Drivers for A19 E12/E26/27, GU10, MR16, PAR30/38 Integral Lamps

- Drivers for Wall Sconces, Pathway Lighting and Overhead Lighting

- Drivers for Wall Washing, Architectural and Display Lighting

## **DESCRIPTION**

The UCL64010 is a PWM controller with advanced energy features to provide high efficiency driving for LED lighting applications.

The UCL64010 incorporates frequency fold back and low power mode operation to reduce the operation frequency at light load and no load operations.

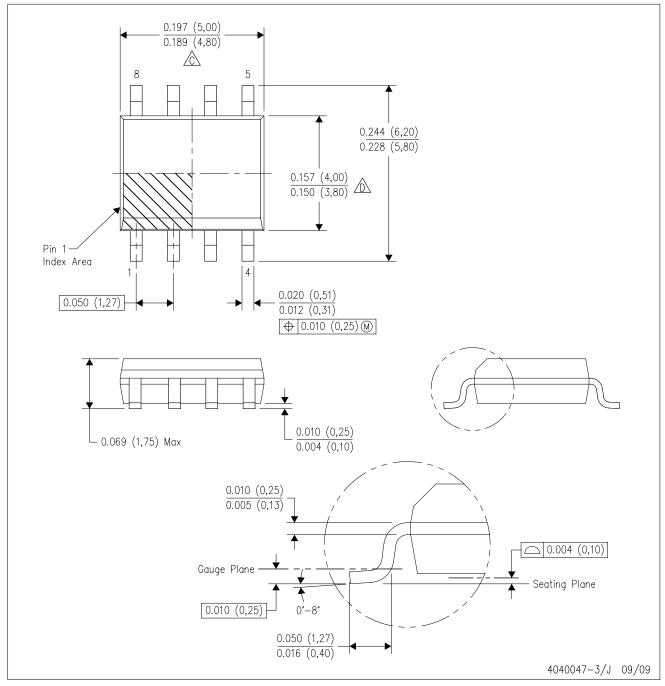

The UCL64010 is offered in the 8-pin SOIC (D) package. Operating junction temperature range is -40°C to 105°C.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TrueDrive is a trademark of Texas Instruments.

SLUS983 – OCTOBER 2009 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                       |                               |                                       | UCL64010    | UNIT |

|---------------------------------------|-------------------------------|---------------------------------------|-------------|------|

| VDD                                   | Supply voltage range          | I <sub>DD</sub> < 20 mA               | 27          | V    |

| I <sub>DD</sub>                       | Supply current                |                                       | 20          | mA   |

| I <sub>GD(sink)</sub>                 | Output sink current (peak)    |                                       | 1.2         | ^    |

| I <sub>GD(source)</sub>               | Output source current (peak)  |                                       | -0.8        | Α    |

| · · · · · · · · · · · · · · · · · · · | Analog inputs                 | FB, PCS, SS                           | -0.3 to 6.0 | V    |

| V <sub>VSD</sub>                      |                               |                                       | -1.0 to 6.0 | V    |

| I <sub>VSD(source)</sub>              |                               |                                       | -1.0        | mA   |

| $V_{LPM}$                             |                               | VDD = 0 V to 30 V                     | 30          | V    |

|                                       | Power dissipation             | SOIC-8 package, T <sub>A</sub> = 25°C | 650         | mW   |

| T <sub>J</sub>                        | Operating junction temperatur | e range                               | -55 to 150  |      |

| T <sub>stg</sub>                      | Storage temperature           |                                       | -65 to 150  | °C   |

| T <sub>LEAD</sub>                     | Lead temperature 1,6 mm (1/   | 16 inch) from case for 10 seconds     | 300         |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal.

## RECOMMENDED OPERATING CONDITIONS

|          |                                | MIN | MAX | UNIT |

|----------|--------------------------------|-----|-----|------|

| VDD      | Input voltage                  |     | 21  | ٧    |

| $I_{GD}$ | Output sink current            | 0   |     | Α    |

| $T_J$    | Operating junction temperature | -40 | 105 | ů    |

**ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                  | MIN M | ΑX  | UNIT |

|------------------|-------|-----|------|

| Human body model | 20    | 000 |      |

| CDM              | 1!    | 500 | V    |

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS**

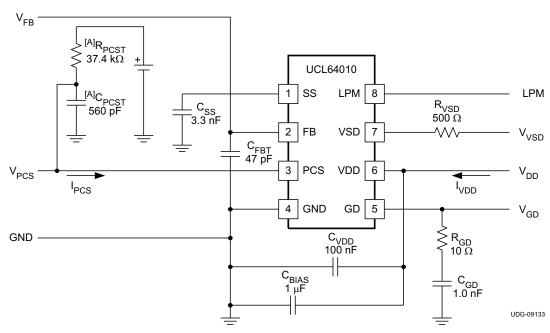

VDD = 15 V, 0.1- $\mu$ F capacitor from VDD to GND, 3.3-nF capacitor from SS to GND charged over 3.5 V, 500- $\Omega$  resistor from VSD to -0.1 V, FB = 4.8 V, LPM = not connected, 1-nF capacitor from GD to GND, PCS = GND,  $T_A$  = -40°C to 105°C, (unless otherwise noted)

|                           | PARAMETER                                     | TEST CONDITIONS                                      | MIN      | TYP  | MAX  | UNIT |

|---------------------------|-----------------------------------------------|------------------------------------------------------|----------|------|------|------|

| OVERALL                   |                                               |                                                      |          |      |      |      |

| I <sub>STARTUP</sub>      | Startup current                               | VDD = V <sub>UVLO</sub> -0.3 V                       |          | 12   | 25   |      |

| I <sub>LPM</sub>          | Standby current                               | V <sub>FB</sub> = 0 V                                |          | 350  | 550  | μΑ   |

|                           | Operating ourrent                             | Not switching                                        |          | 2.5  | 3.5  | mA   |

| I <sub>DD</sub>           | Operating current                             | 130 kHz, QR mode                                     |          | 5.0  | 7.0  | IIIA |

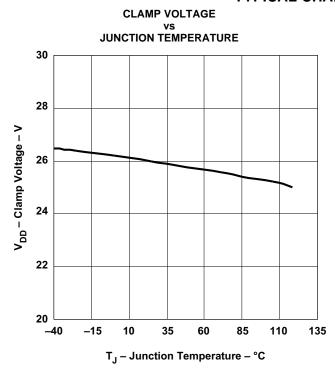

|                           | VDD clamp                                     | FB = GND, I <sub>DD</sub> = 10 mA                    | 21       | 26   | 27   | V    |

| UNDERVOLTA                | AGE LOCKOUT                                   |                                                      | ·        |      |      |      |

| VDD <sub>(uvlo)</sub>     | Startup threshold                             |                                                      | 10.3     | 13.0 | 15.3 |      |

|                           | Stop threshold                                |                                                      | 6.3      | 8    | 9.3  | V    |

| ΔVDD <sub>(uvlo)</sub>    | Hysteresis                                    |                                                      | 4.0      | 5.0  | 6.0  |      |

| PWM (Ramp)(               | 1)                                            |                                                      | <u>.</u> |      |      |      |

| D <sub>MIN</sub>          | Minimum duty cycle                            | V <sub>SS</sub> = GND, V <sub>FB</sub> = 2 V         |          |      | 0%   |      |

| D <sub>MAX</sub>          | Maximum duty cycle                            | QR mode, f <sub>S</sub> = max, (open loop)           |          | 99%  |      |      |

| OSCILLATOR                | (OSC)                                         |                                                      | ,        |      |      |      |

| f <sub>QR(max)</sub>      | Maximum QR and DCM frequency                  |                                                      | 117      | 130  | 143  |      |

| f <sub>QR(min)</sub>      | Minimum QR and FFM frequency                  | V <sub>FB</sub> = 1.3 V                              | 32       | 40   | 48   | kHz  |

| f <sub>SS</sub>           | Soft start frequency                          | V <sub>SS</sub> = 2.0 V                              | 32       | 40   | 48   |      |

| dT <sub>S</sub> /dFB      | VCO gain                                      | T <sub>S</sub> for 1.6 V < V <sub>FB</sub> < 1.8 V   | -38      | -30  | -22  | μs/V |

| FEEDBACK (F               | FB)                                           |                                                      | ,        |      |      |      |

| R <sub>FB</sub>           | Feedback pullup resistor                      |                                                      | 12       | 20   | 28   | kΩ   |

| $V_{FB}$                  | FB, no load                                   | QR mode                                              | 3.30     | 4.87 | 6.00 |      |

|                           | Low power mode ON threshold                   | V <sub>FB</sub> threshold                            | 0.3      | 0.5  | 0.7  |      |

|                           | Low power mode OFF threshold                  | V <sub>FB</sub> threshold                            | 1.2      | 1.4  | 1.6  | V    |

|                           | Low power mode hysteresis                     | V <sub>FB</sub> threshold                            |          | 0.9  |      |      |

|                           | Burst hysteresis                              | V <sub>FB</sub> during low power mode                | 0.13     | 0.25 | 0.42 |      |

| LOW POWER                 | MODE                                          |                                                      | ,        |      |      |      |

| R <sub>DS(on)</sub>       | LPM on resistance                             | V <sub>LPM</sub> = 1 V                               | 1.0      | 2.4  | 3.8  | kΩ   |

| I <sub>LPM(leakage)</sub> | LPM leakage/off current                       | V <sub>FB</sub> = 0.44 V, V <sub>STATUS</sub> = 15 V | -0.1     |      | 2.0  | μΑ   |

| PEAK CURRE                | NT SENSE (PCS) <sup>(1)</sup>                 |                                                      | ,        |      |      |      |

| A <sub>PCS(FB)</sub>      | Gain, FB = $\Delta V_{FB} / \Delta V_{PCS}$   | QR mode                                              |          | 2.5  |      | V/V  |

| . ,                       | Shutdown threshold                            | V <sub>FB</sub> = 2.4 V, V <sub>SS</sub> = 0 V       | 1.13     | 1.25 | 1.38 | V    |

|                           | PCS to output delay time (power limit)        | PCS = 1.0 V <sub>PULSE</sub>                         |          | 175  | 300  |      |

|                           | PCS to output delay time (over current fault) | PCS = 1.45 V <sub>PULSE</sub>                        |          | 100  | 150  | ns   |

|                           | PCS discharge impedance                       | PCS = 0.1 V, V <sub>SS</sub> = 0 V                   | 25       | 115  | 250  | Ω    |

| V <sub>PCS(os)</sub>      | PCS offset                                    | SS mode, V <sub>SS</sub> ≤ 2.0 V, via FB             | 0.35     | 0.40 | 0.45 | V    |

$<sup>(1) \</sup>quad \mathsf{R}_{\mathsf{PCST}} \text{ and } \mathsf{C}_{\mathsf{PCST}} \text{ are not connected in the circuit for maximum and minimum duty cycle tests, current sense tests and power limit tests. }$

## **ELECTRICAL CHARACTERISTICS (continued)**

$VDD = 15 \text{ V}, 0.1\text{-}\mu\text{F} \text{ capacitor from VDD to GND, } 3.3\text{-}n\text{F} \text{ capacitor from SS to GND charged over } 3.5 \text{ V}, 500\text{-}\Omega \text{ resistor from VSD to } -0.1 \text{ V}, \text{FB} = 4.8 \text{ V}, \text{LPM} = \text{not connected, } 1\text{-}n\text{F} \text{ capacitor from GD to GND, } \text{PCS} = \text{GND, } T_A = -40^{\circ}\text{C} \text{ to } 105^{\circ}\text{C},$ (unless otherwise noted)

|                        | PARAMETER                          | TEST CONDITIONS                                                                   | MIN  | TYP  | MAX  | UNIT |

|------------------------|------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

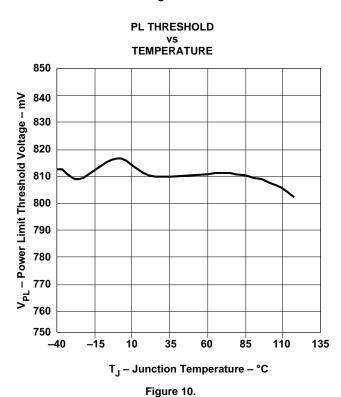

| POWER LIMIT            | Γ (PL) <sup>(2)</sup>              |                                                                                   |      |      |      |      |

| I <sub>PL(Pcs)</sub>   | PCS current                        | I <sub>VSD</sub> = -300 μA                                                        | -165 | -150 | -135 | μΑ   |

|                        | PCS working range                  | QR mode, peak PCS voltage                                                         | 0.70 | 0.81 | 0.92 | V    |

| V <sub>PL</sub>        | PL threshold                       | Peak CS voltage + PCS offset                                                      | 1.05 | 1.20 | 1.37 | V    |

| SOFT START             | (SS)                               |                                                                                   |      |      |      |      |

| I <sub>SS(chg)</sub>   | Softstart charge current           | V <sub>SS</sub> = GND                                                             | -8.3 | -6.0 | -4.5 | μA   |

| I <sub>SS(dis)</sub>   | Softstart discharge current        | V <sub>SS</sub> = 0.5 V                                                           | 2.0  | 5.0  | 10   | mA   |

| V <sub>SS</sub>        | Switching ON threshold             | Output switching start                                                            | 0.8  | 1.0  | 1.2  | V    |

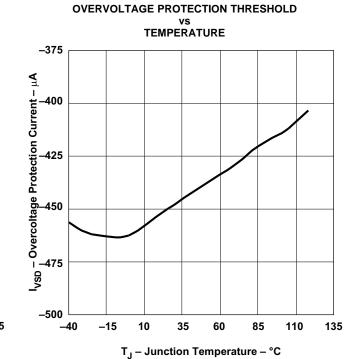

| VALLEY SWI             | TCHING DETECT (VSD)                |                                                                                   |      |      |      |      |

| I <sub>VSD(line)</sub> | Valley switching detect            | I <sub>VSD</sub> threshold, GD = HI                                               | -512 | -450 | -370 | μΑ   |

| V <sub>VSD(on)</sub>   | VSD voltage at OUT = HIGH          | $V_{FB} = 4.8 \text{ V}, V_{SS} = 5.0 \text{ V}, I_{VSD(on)}, = -300 \mu\text{A}$ | -125 |      | -25  | mV   |

| V <sub>VSD(load)</sub> | Load overvoltage protection        | V <sub>VSD</sub> threshold, GD = LO                                               | 3.37 | 3.75 | 4.13 | ٧    |

|                        | ROTECTION (TSP)(3)                 |                                                                                   |      |      |      |      |

|                        | Thermal shutdown (TSP) temperature |                                                                                   |      | 140  |      | °C   |

|                        | Thermal shutdown hysteresis        |                                                                                   |      | 15   |      |      |

| GATE DRIVE             |                                    |                                                                                   |      |      |      |      |

| t <sub>RISE</sub>      | Rise time                          | 10% to 90% of 13 V typical out clamp                                              |      | 50   | 75   |      |

| t <sub>FALL</sub>      | Fall time                          |                                                                                   |      | 10   | 20   | ns   |

$R_{PCST}$  and  $C_{PCST}$  are not connected in the circuit for maximum and minimum duty cycle tests, current sense tests and power limit tests. Specified by design. Not production tested.

## **OPEN LOOP TEST CIRCUIT**

R<sub>PCST</sub> and C<sub>PCST</sub> are not connected for maximum and minimum duty cycle tests, current sense tests and power limit tests

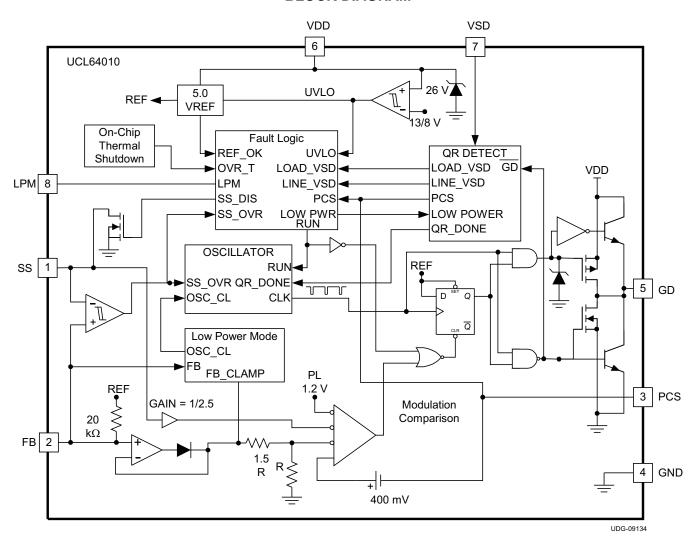

## **BLOCK DIAGRAM**

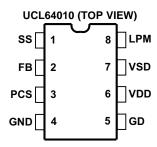

## **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGES                | PART NUMBER |  |  |

|----------------|-------------------------|-------------|--|--|

| -40°C to 105°C | SOIC (D) <sup>(1)</sup> | UCL64010D   |  |  |

(1) SOIC (D) package is available taped and reeled by adding "R" to the above part numbers. Reeled quantities for UCL64010DR is 2,500 devices per reel.

## **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| PIN  |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FB   | 2   | I   | Feedback input or control input from the output sensing network to the PWM comparator used to control the peak current in the power MOSFET. An internal 20-kΩ resistor is between this pin and the internal 5-V regulated voltage. The voltage of this pin controls the mode of operation in one of the three modes: quasi resonant (QR), frequency foldback mode (FFM) and low power mode (LPM).                                                                                                                                                                                    |

| GND  | 4   | _   | Ground for internal circuitry. Connect a ceramic 0.1-µF bypass capacitor between VDD and GND, with the capacitor as close to these two pins as possible.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GD   | 5   | 0   | 1-A sink (TrueDrive <sup>™</sup> ) and 0.75-A source gate drive output. This output drives the power MOSFET and switches between GND and the lower of VDD or the 13-V internal output clamp.                                                                                                                                                                                                                                                                                                                                                                                         |

| LPM  | 8   | 0   | The low power mode pin is an ACTIVE HIGH open drain signal that indicates the device has entered low power mode. LPM pin is high during UVLO, (VDD < startup threshold), and softstart, (SS < FB).                                                                                                                                                                                                                                                                                                                                                                                   |

| PCS  | 3   | I   | Peak current sense input, also programs power limit and is used to control modulation and activate overcurrent protection. The PCS voltage input originates across a current sense resistor and ground. Power limit is programmed with an effective series resistance between this pin and the current sense resistor.                                                                                                                                                                                                                                                               |

| SS   | 1   | I   | Soft-start programming pin. Program the soft-start rate with a capacitor to ground; the rate is determined by the capacitance and the internal soft-start charge current. Placement of the soft-start capacitor is critical and should be placed as close as possible to the SS pin and GND, keeping trace length to a minimum. All faults discharge the SS pin to GND through an internal MOSFET with an $R_{DS(on)}$ of approximately 100 $\Omega$ . The internal modulator comparator reacts to the lowest of the SS voltage, the internal FB voltage and the peak current limit. |

| VDD  | 6   | I   | Provides power to the device. Use a ceramic 0.1-µF by-pass capacitor for high-frequency filtering of the VDD pin, as described in the GND pin description. Operating energy is usually delivered from auxiliary winding. To prevent hiccup operation during start-up, a larger energy storage cap is also needed between VDD and GND.                                                                                                                                                                                                                                                |

| VSD  | 7   | 1   | The valley switching detect (VSD) pin senses line, load and resonant conditions using the primary bias winding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### APPLICATION INFORMATION

## **FUNCTIONAL DESCRIPTION**

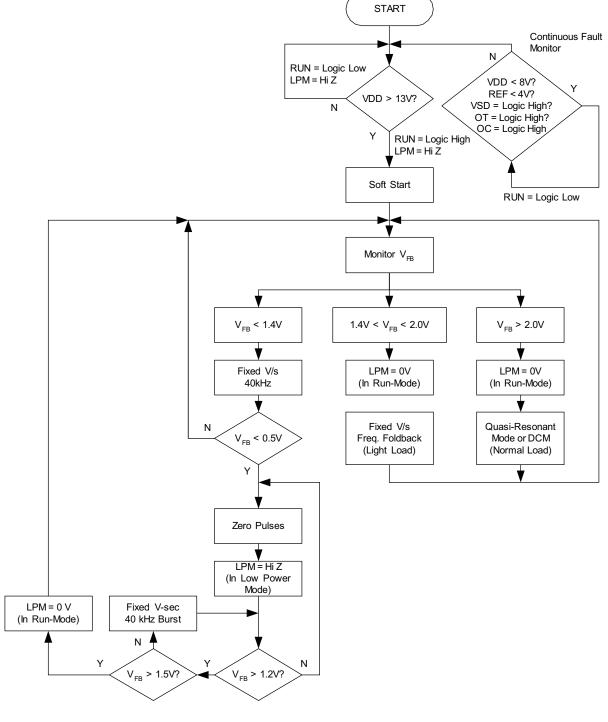

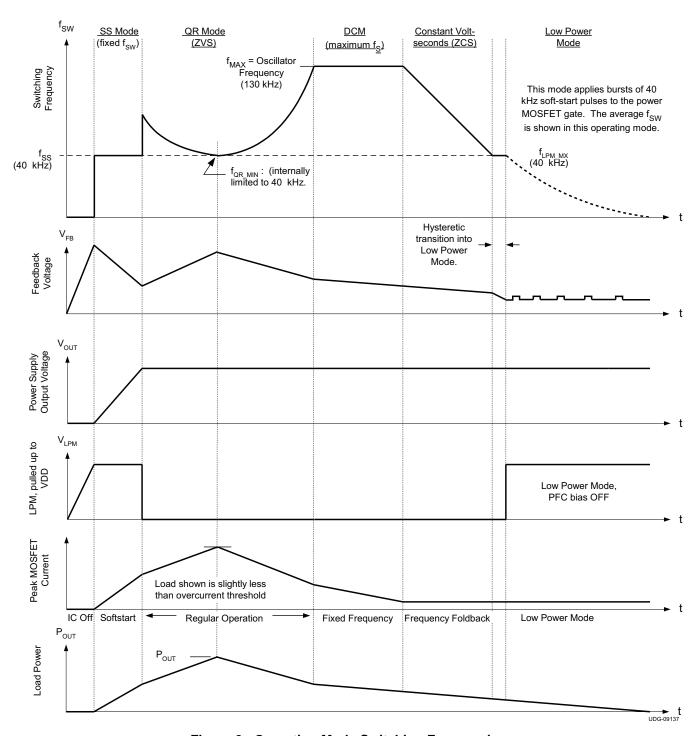

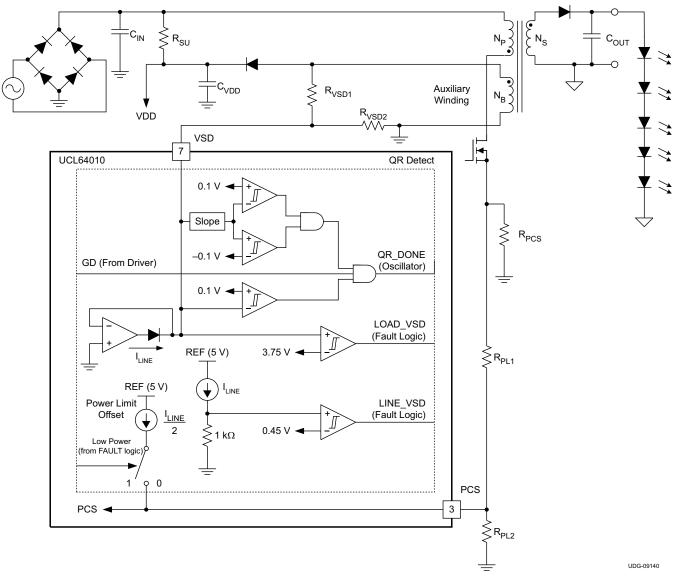

The UCL64010 is a multi-mode LED Lighting controller, as illustrated in Figure 1 and Figure 2. The mode of operation depends upon input and dimming conditions. Under all modes of operation, the UCL64010 terminates the GD = HI signal based on the switch current. Thus, the UCL64010 always operates in current mode control so that the power MOSFET current is always limited.

Figure 1. Control Flow Chart

UDG-09136

Figure 2. Operation Mode Switching Frequencies

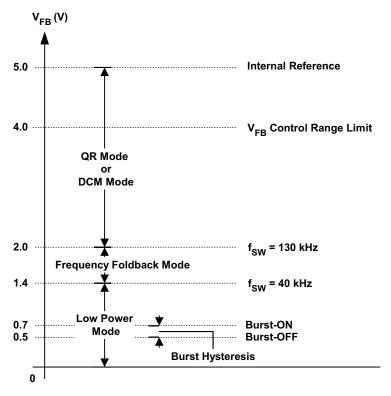

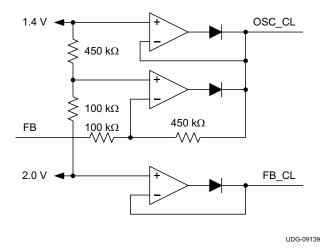

Under normal operating conditions, the FB pin commands the operating mode of the UCL64010 at the voltage thresholds shown in Figure 3. Soft-start and fault responses are exceptions. During soft-start mode the UCL64010 controls the converter at a fixed constant switching frequency of 40 kHz. The soft-start mode is latched-OFF when  $V_{FB}$  becomes less than  $V_{SS}$  for the first time after UVLO<sub>ON</sub>. The soft-start state cannot be recovered until after passing UVLO<sub>OFF</sub>, and then, UVLO<sub>ON</sub>.

Figure 3. Mode Control with FB Pin Voltage

At normal rated operating loads (from 100% to approximately 30% full rated power) the UCL64010 controls the converter in quasi-resonant mode (QRM) or discontinuous conduction mode (DCM), where DCM operation is at the clamped maximum switching frequency (130 kHz). For loads that are between approximately 30% and 10% full rated power, the converter operates in frequency foldback mode (FFM), where the peak switch current is constant and the output is regulated by modulating the switching frequency for a given and fixed  $V_{\text{IN}}$ . Effectively, operation in FFM results in the application of constant volt-seconds to the flyback transformer each switching cycle. Voltage regulation in FFM is achieved by varying the switching frequency in the range from 130 kHz to 40 kHz. For extremely light loads (below approximately 10% full rated power), the converter is controlled using bursts of 40-kHz pulses. Keep in mind that the aforementioned boundaries of steady-state operation are approximate because they are subject to converter design parameters.

Refer to the typical applications block diagram for the electrical connections to implement the features.

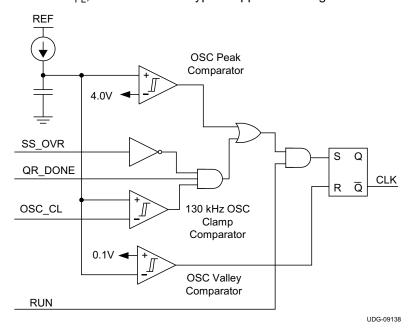

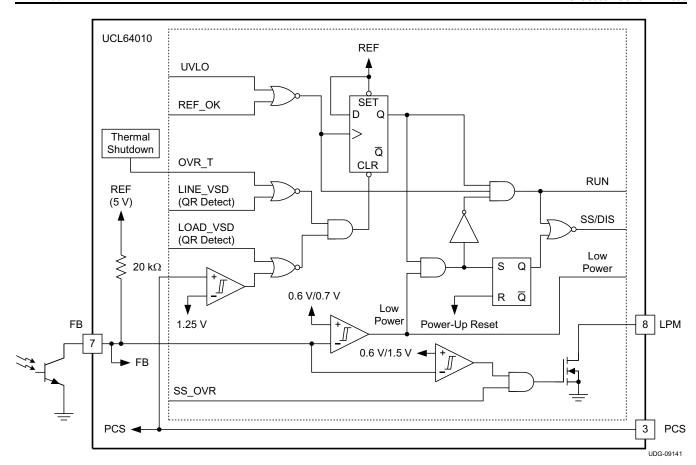

Details of the functional boxes in the Block Diagram are shown in Figure 4, Figure 5, Figure 6 and Figure 7 showing how the UCL64010 executes the command of the FB voltage to have the responses that are shown in Figure 3, Figure 1 and Figure 2. The details of the functional boxes also show the various fault detections and responses that are included in the UCL64010. During all modes of operation, this controller operates in current mode control. This allows the UCL64010 to monitor the FB voltage to determine and respond to the varying load levels.

Quasi-resonant mode and DCM occurs for feedback voltages  $V_{FB}$  between 2.0 V and 4.0 V, respectively. In turn, the PCS voltage is commanded to be between 0.4 V and 0.8 V. A cycle-by-cycle power limit imposes a fixed 0.8-V limit on the PCS voltage. An overcurrent shutdown threshold in the fault logic gives added protection against high-current, slew-rate shorted winding faults, shown in Figure 7. The power limit feature in the QR DETECT circuit of Figure 6 adds an offset to the PCS signal that is proportional to the line voltage. The power limit feature is programmed with  $R_{Pl}$ , as shown in the typical application diagram.

Figure 4. Oscillator Details

Figure 5. Mode Clamp Details

Figure 6. QR Detect Details

Figure 7. Fault Logic Details

#### **Quasi-Resonant / DCM Control**

Quasi-resonant (QR) and DCM operation occur for feedback voltages  $V_{FB}$  between 2.0 V and 4.0 V. In turn, the peak PCS voltage is commanded to be between 0.4 V and 0.8 V. During this control mode, the rising edge of GD always occurs at the valley of the resonant ring after demagnetization. Resonant valley switching is an integral part of QR operation. Resonant valley switching is also imposed if the system operates at the maximum switching frequency clamp. In other words, the frequency varies in DCM operation in order to have the switching event occur on the first resonant valley that occurs after a 7.7- $\mu$ s (130-kHz) interval. Notice that the PCS pin has an internal dependent current source, 1/2  $I_{LINE}$ . This current source is part of the cycle-by-cycle power limit function that is discussed in the Protection Features section.

#### **Frequency Foldback Mode Control**

Frequency foldback mode uses elements of the FAULT LOGIC, shown in Figure 7 and the mode clamp circuit, shown in Figure 5. At the minimum operating frequency, the internal oscillator sawtooth waveform has a peak of 4.0 V and a valley of 0.1 V. When the FB voltage is between 2.0 V and 1.4 V, the FB\_CL signal in Figure 5 commands the oscillator in a voltage controlled oscillator (VCO) mode by clamping the peak oscillator voltage. The additional clamps in the OSCILLATOR restrict VCO operation between 40 kHz and 130 kHz. The FB\_CL voltage is reflected to the modulator comparator effectively clamping the reflected PCS command to 0.4 V.

#### **Low Power Mode Control**

Low power mode uses elements of the FAULT LOGIC, shown in Figure 7 and the mode clamps circuit, shown in Figure 5. The OSC\_CL signal clamps the Low Power-mode operating frequency at 40 kHz. Thus, when the FB voltage is between 1.4 V and 0.5 V, the controller is commanding an excess of energy to be transferred to the load which in turn, drives the error higher and FB lower. When FB reaches 0.5 V, GD pulses are terminated and do not resume until FB reaches 0.7 V. In this mode, the converter operates in hysteretic control with the GD pulse terminated at a fixed PCS voltage level of 0.4 V. The power limit offset is turned OFF during Low Power mode and it returns to ON when FB is above 1.4 V, as depicted in Figure 7. H mode reduces the average switching frequency in order to minimize switching losses and increase the efficiency at light load conditions.

## **Fault Logic**

Advanced logic control coordinates the fault detections to provide proper power supply recovery. This provides the conditioning for the thermal protection. Line overvoltage protection and load overvoltage protection are implemented in this block. It prevents operation when the internal reference is below 4.5 V. If a fault is detected in the thermal shutdown, line overvoltage protection, load overvoltage protection, or REF, the UCL64010 undergoes a shutdown/retry cycle.

Refer to the fault logic diagram in Figure 7 and the QR detect diagram in Figure 6 to program line overvoltage protection and load overvoltage protection. To program the load overvoltage protection, select the  $R_{VSD1}-R_{VSD2}$  divider ratio to be 3.75 V at the desired output shut-down voltage. To program line overvoltage protection, select the impedance of the  $R_{VSD1}-R_{VSD2}$  combination to draw 450  $\mu$ A when the  $V_{VSD}$  is 0.45 V during the ON-time of the power MOSFET at the highest allowable input voltage.

#### Oscillator

The oscillator, shown in Figure 4, is internally set and trimmed so it is clamped by the circuit in Figure 4 to a nominal 130-kHz maximum operating frequency. It also has a minimum frequency clamp of 40 kHz. If the FB voltage tries to drive operation to less than 40 kHz, the converter operates in low power mode.

#### **Low Power**

The LPM pin is an open drain output, as shown in Figure 7. The LPM output goes into the OFF-state when FB falls below 0.5 V and it returns to the ON-state (low impedance to GND) when FB rises above 1.4 V.

## **OPERATING MODE PROGRAMMING**

Boundaries of the operating modes are programmed by the flyback transformer and the four components  $R_{PL}$ ,  $R_{PCS}$ ,  $R_{VSD1}$  and  $R_{VSD2}$ ; shown in Figure 1.

The transformer characteristics that predominantly affect the modes are the magnetizing inductance of the primary and the magnitude of the output voltage, reflected to the primary. To a lesser degree (yet significant), the boundaries are affected by the MOSFET output capacitance and transformer leakage inductance. The design procedure here is to select a magnetizing inductance and a reflected output voltage that operates at the DCM/CCM boundary at maximum load and maximum line. The actual inductance should be noticeably smaller to account for the ring between the magnetizing inductance and the total stray capacitance measured at the drain of the power MOSFET. This programs the QR/DCM boundary of operation. All other mode boundaries are preset with the thresholds in the oscillator and green-mode blocks.

#### PROTECTION FEATURES

The UCL64010 has many protection features. Refer to Figures 1, 4, 8, 9 and 10 for detailed block descriptions that show how the features are integrated into the normal control functions.

#### Overtemperature

Overtemperature lockout typically occurs when the substrate temperature reaches 140°C. Retry is allowed if the substrate temperature reduces by the hysteresis value. Upon an overtemperature fault, C<sub>SS</sub> on softstart is discharged and LPM is forced to a high impedance.

#### **Cycle-by-Cycle Power Limit**

The cycle terminates when the PCS voltage plus the power limit offset exceeds 1.2 V.

4 Submit Documentation Feedback

In order to have power limited over the full line voltage range of the QR Flyback converter, the PCS pin voltage must have a component that is proportional to the primary current plus a component that is proportional to the line voltage due to predictable switching frequency variations due to line voltage. At power limit, the PCS pin voltage plus the internal PCS offset is compared against a constant 1.2-V reference in the PWM comparator. Thus during cycle-by-cycle power limit, the peak PCS voltage is typically 0.8 V.

The current that is sourced from the VSD pin ( $I_{LINE}$ ) is reflected to a dependent current source of ½  $I_{LINE}$ , that is connected to the PCS pin. The power limit function can be programmed by a resistor,  $R_{PL}$ , that is between the PCS pin and the current sense resistor. The current,  $I_{LINE}$ , is proportional to line voltage by the transformer turns ratio  $N_B/N_P$  and resistor  $R_{VSD1}$ . Current  $I_{LINE}$  is programmed to set the line over voltage protection. Resistor  $R_{PL}$  results in the addition of a voltage to the current sense signal that is proportional to the line voltage. The proper amount of additional voltage has the effect of limiting the power on a cycle-by-cycle basis. Note that  $R_{PCS}$ ,  $R_{PL}$ ,  $R_{VSD1}$  and  $R_{VSD2}$  must be adjusted as a set due to the functional interactions.

#### **Current Limit**

When the primary current exceeds maximum current level which is indicated by a voltage of 1.25 V at the PCS pin, the device initiates a shutdown. Retry occurs after a UVLO<sub>OFF</sub>/UVLO<sub>ON</sub> cycle.

## **Overvoltage Protection Function**

Input line overvoltage and LED open string protection is programmed with the transformer turn ratios,  $R_{VSD1}$  and  $R_{VSD2}$ . The VSD pin has a 0-V voltage source that can only source current; VSD cannot sink current.

Open String LED protection occurs when the VSD pin is clamped at 0 V. When the bias winding is negative, during GD = HI or portions of the resonant ring, the 0-V voltage source clamps VSD to 0 V and the current that is sourced from the VSD pin is mirrored to the Line\_VSD comparator and the QR detection circuit. The Line\_VSD comparator initiates a shutdown-retry sequence if VSD sources any more than 450  $\mu$ A.

Open String LED protection occurs when the VSD pin voltage is positive. When the bias winding is positive, during demagnetization or portions of the resonant ring, the VSD pin voltage is positive. If the VSD voltage is greater than 3.75 V, the device initiates a shutdown. Retry occurs after a UVLO<sub>OFF</sub>/UVLO<sub>ON</sub> cycle.

#### **Undervoltage Lockout**

Protection is provided to guard against operation during unfavorable bias conditions. Undervoltage lockout (UVLO) always monitors VDD to prevent operation below the UVLO threshold.

Product Folder Link(s): UCL64010

## TYPICAL CHARACTERISTICS

JUNCTION TEMPERATURE 140 f<sub>SW(max)</sub> - Maximum Switching Frequency - kHz 138 136 134 132 130 128 126 124 122 120 **-40** -15 10 35 60 85 110 135

**SWITCHING FREQUENCY**

Figure 8.

Figure 9.

$T_J$  – Junction Temperature – °C

Figure 11.

Submit Documentation Feedback

#### PACKAGE OPTION ADDENDUM

www.ti.com 14-Oct-2009

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|------------------------------|

| UCL64010D        | PREVIEW               | SOIC            | D                  | 8    | 75             | TBD                     | Call TI          | Call TI                      |

| UCL64010DR       | PREVIEW               | SOIC            | D                  | 8    | 2500           | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## D (R-PDSO-G8)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AA.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated