# **Low Dropout Regulator**

The MC33267 is a positive fixed 5.0 V regulator that is specifically designed to maintain proper voltage regulation with an extremely low input-to-output voltage differential. This device is capable of supplying output currents in excess of 500 mA and contains internal current limiting and thermal shutdown protection. Also featured is an on-chip power-up reset circuit that is ideally suited for use in microprocessor based systems. Whenever the regulator output voltage is below nominal, the reset output is held low. A programmable time delay is initiated after the regulator has reached its nominal level and upon timeout, the reset output is released.

Due to the low dropout voltage specifications, the MC33267 is ideally suited for use in battery powered industrial and consumer equipment where an extension of useful battery life is desirable. This device is contained in an economical five lead TO-220 type package.

- Low Input-to-Output Voltage Differential

- Output Current in Excess of 500 mA

- On-Chip Power-Up Reset Circuit with Programmable Delay

- Internal Current Limiting with Thermal Shutdown

- Economical Five Lead TO-220 Type Packages

#### **ORDERING INFORMATION**

| Device     | Tested Operating Temperature Range                     | Package       |

|------------|--------------------------------------------------------|---------------|

| MC33267T   | T 40 % to 1105%C                                       | Plastic Power |

| MC33267TV  | $T_J = -40^{\circ} \text{ to } +125^{\circ}\text{C}$   | Plastic Power |

| MC33267D2T | $T_{J} = -40^{\circ} \text{ to } +105^{\circ}\text{C}$ | Surface Mount |

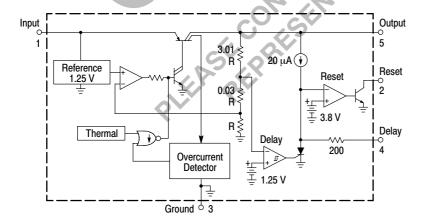

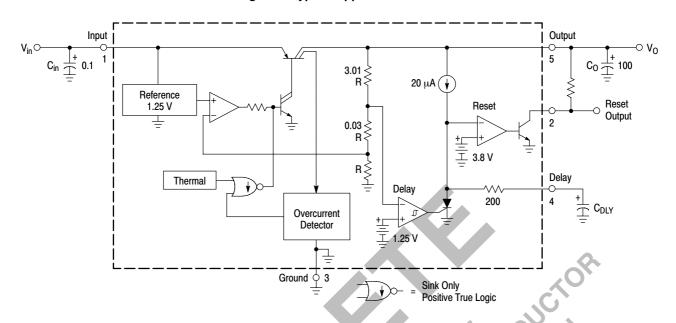

#### Representative Block Diagram

This device contains 37 active transistors.

ON Semiconductor®

http://onsemi.com

LOW DROPOUT

REGULATOR with

POWER-UP RESET

SEMICONDUCTOR TECHNICAL DATA

Pin 1. V<sub>CC</sub> Input 2. Reset

3. Ground

4. Delay

ay put

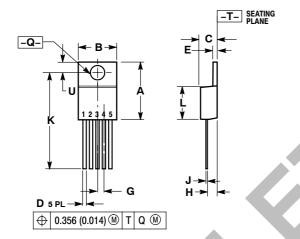

T SUFFIX

PLASTIC PACKAGE

CASE 314D

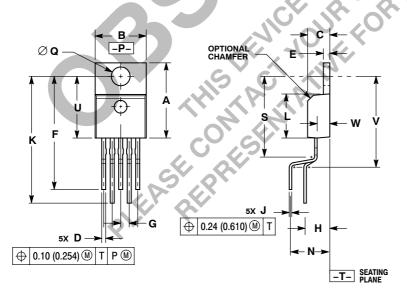

TV SUFFIX

PLASTIC PACKAGE

CASE 314B

Heatsink surface connected to Pin 3.

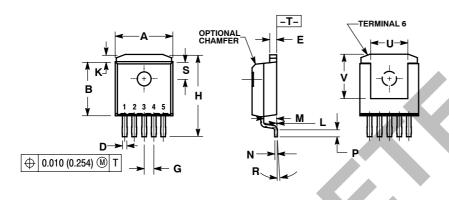

**D2T SUFFIX**PLASTIC PACKAGE

CASE 936A

(D<sup>2</sup>PAK)

Heatsink surface (shown as terminal 6 in case outline drawing) is connected to Pin 3.

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                                             | Symbol                                                                                                           | Value                                                                | Unit                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------|

| Input Voltage Range                                                                                                                                                                                                                                                                                | V <sub>in</sub>                                                                                                  | – 20 to + 40                                                         | Vdc                                    |

| Delay Voltage Range                                                                                                                                                                                                                                                                                | $V_{\rm DLYR}$                                                                                                   | – 0.3 to V <sub>O</sub>                                              | V                                      |

| Delay Sink Current                                                                                                                                                                                                                                                                                 | I <sub>DLY(sink)</sub>                                                                                           | 25                                                                   | mA                                     |

| Reset Voltage Range                                                                                                                                                                                                                                                                                | $V_{RR}$                                                                                                         | – 0.3 to +15                                                         | V                                      |

| Reset Sink Current                                                                                                                                                                                                                                                                                 | I <sub>R(sink)</sub>                                                                                             | 50                                                                   | mA                                     |

| Power Dissipation Case 314B and 314D (TO-220 Type)  T <sub>A</sub> = 25°C Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case Case 936A (D <sup>2</sup> PAK) [Note 1]  T <sub>A</sub> = 90°C Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case | P <sub>D</sub><br>R <sub>θJA</sub><br>R <sub>θJC</sub><br>P <sub>D</sub><br>R <sub>θJA</sub><br>R <sub>θJC</sub> | Internally Limited<br>62.5<br>4.0<br>Internally Limited<br>70<br>5.0 | W<br>°C/W<br>°C/W<br>W<br>°C/W<br>°C/W |

| Operating Junction Temperature Range                                                                                                                                                                                                                                                               | TJ                                                                                                               | -40 to +150                                                          | °C                                     |

| Storage Temperature Range                                                                                                                                                                                                                                                                          | T <sub>stg</sub>                                                                                                 | -55 to +150                                                          | °C                                     |

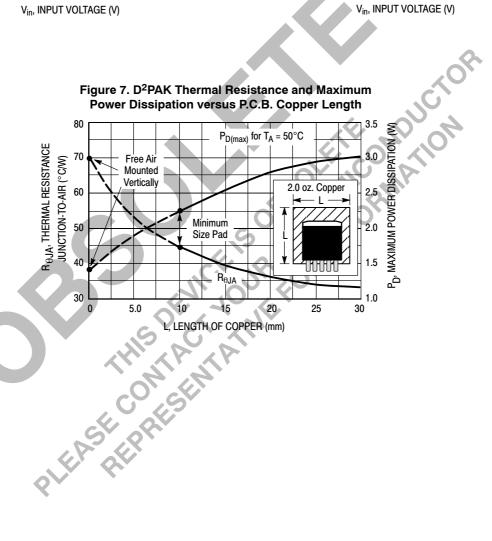

NOTE: 1. D<sup>2</sup>PAK Junction-to-Ambient Thermal Resistance is for vertical mounting. Refer to Figure 7 for board mounted thermal resistance.

# **ELECTRICAL CHARACTERISTICS** (V<sub>in</sub> = 14.4 V, I<sub>O</sub> = 5.0 mA, C<sub>O</sub> = 100 $\mu$ F, C<sub>O(ESR)</sub> $\leq$ 0.3 $\Omega$ , T<sub>J</sub> = 25°C (Note 2), unless otherwise noted.)

| Characteristic                                                                                           | Symbol                           | Min              | Тур                    | Max                    | Unit |

|----------------------------------------------------------------------------------------------------------|----------------------------------|------------------|------------------------|------------------------|------|

| Output Voltage ( $I_O$ = 5.0 mA to 500 mA, $V_{in}$ = 6.0 V to 28 V) $T_J$ = 25°C $T_J$ = -40° to +125°C | ORVO S                           | 4.95<br>4.9      | 5.05                   | 5.15<br>5.2            | V    |

| Line Regulation (V <sub>in</sub> = 6.0 V to 26 V)                                                        | Reg <sub>line</sub>              | -                | 3.0                    | 50                     | mV   |

| Load Regulation (I <sub>O</sub> = 5.0 mA to 500 mA)                                                      | Reg <sub>load</sub>              | _                | 1.0                    | 50                     | mV   |

| Bias Current $I_O = 0$ mA $I_O = 150$ mA $I_O = 500$ mA $I_O = 500$ mA, $V_{in} = 6.2$ V                 | B                                | -<br>-<br>-<br>- | 12<br>22<br>100<br>120 | 20<br>40<br>200<br>300 | mA   |

| Ripple Rejection (f = 120 Hz, $V_{in}$ = 7.0 V to 17 V, $I_{O}$ = 350 mA, $C_{O}$ = 100 $\mu$ F)         | RR                               | 60               | 80                     | -                      | dB   |

| Dropout Voltage (I <sub>O</sub> = 500 mA)                                                                | V <sub>in</sub> – V <sub>O</sub> | -                | 0.58                   | 0.8                    | V    |

| Delay Comparator Threshold (V <sub>O</sub> Decreasing)                                                   | V <sub>th(DLY)</sub>             | 4.8              | V <sub>O</sub> – 0.15  | V <sub>O</sub> – 0.08  | V    |

| Delay Pin Source Current                                                                                 | I <sub>DLY(source)</sub>         | 12               | 20                     | 28                     | μΑ   |

| Reset Comparator Threshold                                                                               | V <sub>th(R)</sub>               | 3.6              | 3.8                    | 4.0                    | V    |

| Reset Sink Saturation (I <sub>sink</sub> = 10 mA)                                                        | V <sub>CE(sat)</sub>             | -                | 0.2                    | 0.8                    | V    |

| Reset Off-State Leakage (V <sub>CE</sub> = 5.0 V)                                                        | I <sub>R(leak)</sub>             | -                | 0.3                    | 10                     | μΑ   |

NOTE: 2. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

Figure 1. Typical Application Circuit

#### **APPLICATION CIRCUIT INFORMATION**

The MC33267 is a low dropout, positive fixed 5.0 V, 500 mA regulator. Protection features include output current limiting and thermal shutdown. System protection consists of an on-chip power-up microprocessor reset circuit.

A typical applications circuit is shown in Figure 1. The input bypass capacitor  $(C_{in})$  is recommended if the regulator is located an appreciable distance ( $\geq 4''$ ) from the supply input filter. This will reduce the circuit's sensitivity to the input line impedance at high frequencies.

These regulators are not internally compensated and thus require an external output capacitor ( $C_O$ ) for stability. The recommended capacitance is  $100~\mu F$  with an equivalent series resistance (ESR) of less than  $0.3~\Omega.$  A minimum capacitance of  $33~\mu F$  with a maximum ESR of  $3.0~\Omega$  can be used in applications where space is a premium, however, these limits must be observed over the entire operating temperature range of the regulator circuit.

With economical electrolytic capacitors, cold temperature operation can pose a serious stability problem. As the

electrolyte freezes, around  $-30^{\circ}$ C, the capacitance will decrease and the ESR will increase drastically, causing the circuit to oscillate. Quality electrolytic capacitors with extended temperature ranges of  $-40^{\circ}$ C to  $+85^{\circ}$ C and  $-55^{\circ}$ C to  $+105^{\circ}$ C are readily available. It is suggested that oven testing of the entire circuit be performed with maximum load, minimum input voltage, and minimum ambient temperature.

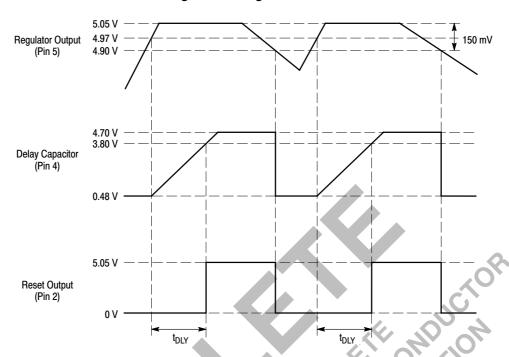

Figure 2 shows the reset circuit timing relationship. Note that whenever the regulator's output is less than 4.9 V, the delay capacitor ( $C_{DLY}$ ) is immediately discharged, and the reset output is held in a low state. As the regulator's output voltage increases beyond 4.97 V, the delay comparator will allow the 20  $\mu$ A current source to charge  $C_{DLY}$ . The reset output will go to a high state when  $C_{DLY}$  crosses the 3.8 V threshold of the reset comparator. The reset delay time is controlled by the value selected for  $C_{DLY}$ . The required system reset time is governed by the microprocessor and usually a reset signal which lasts several machine cycles is sufficient.

Figure 2. Timing Waveforms

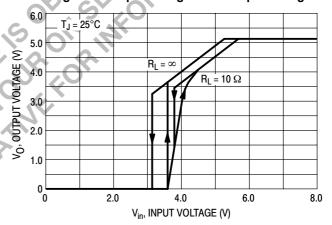

Figure 4. Output Voltage versus Input Voltage

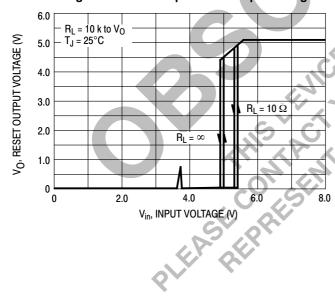

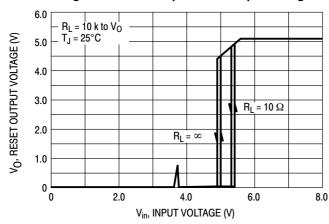

Figure 5. Reset Output versus Input Voltage

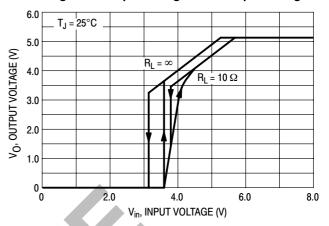

Figure 6. Output Voltage versus Input Voltage

Figure 7. D<sup>2</sup>PAK Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

#### PACKAGE DIMENSIONS

#### T SUFFIX

PLASTIC PACKAGE CASE 314D-04 (TO-220 TYPE) ISSUE E

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 114-3M, 1962.

CONTROLLING DIMENSION: INCH.

DIMENSION D DOES NOT INCLUDE

INTERCONNECT BAR (DAMBAR) PROTRUSION.

DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 10.92 (0.043) MAXIMUM.

|     | INCHES |       | MILLIN | ETERS  |  |

|-----|--------|-------|--------|--------|--|

| DIM | MIN    | MAX   | MIN    | MAX    |  |

| A   | 0.572  | 0.613 | 14.529 | 15.570 |  |

| В   | 0.390  | 0.415 | 9.906  | 10.541 |  |

| C   | 0.170  | 0.180 | 4.318  | 4.572  |  |

| D   | 0.025  | 0.038 | 0.635  | 0.965  |  |

| E   | 0.048  | 0.055 | 1.219  | 1.397  |  |

| G   | 0.067  | BSC   |        | BSC    |  |

| Н   | 0.087  | 0.112 | 2.210  | 2.845  |  |

| J   | 0.015  | 0.025 | 0.381  | 0.635  |  |

| K   | 0.990  | 1.045 | 25.146 | 26.543 |  |

| L   | 0.320  | 0.365 | 8.128  | 9.271  |  |

| Q   | 0.140  | 0.153 | 3.556  | 3.886  |  |

| , U | 0.105  | 0.117 | 2.667  | 2.972  |  |

|     | CC     |       |        |        |  |

| SEN | CC     |       |        |        |  |

### TV SUFFIX PLASTIC PACKAGE

CASE 314B-05 (TO-220 TYPE) ISSUE J

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION D DOES NOT INCLUDE INTERCONNECT BAR (DAMBAR) PROTRUSION. DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 0.043 (1.092) MAXIMUM.

|     | INCHES    |       | INCHES    |        | MILLIN | IETERS |

|-----|-----------|-------|-----------|--------|--------|--------|

| DIM | MIN       | MAX   | MIN       | MAX    |        |        |

| Α   | 0.572     | 0.613 | 14.529    | 15.570 |        |        |

| В   | 0.390     | 0.415 | 9.906     | 10.541 |        |        |

| C   | 0.170     | 0.180 | 4.318     | 4.572  |        |        |

| D   | 0.025     | 0.038 | 0.635     | 0.965  |        |        |

| Е   | 0.048     | 0.055 | 1.219     | 1.397  |        |        |

| F   | 0.850     | 0.935 | 21.590    | 23.749 |        |        |

| G   | 0.067 BSC |       | 1.702 BSC |        |        |        |

| Н   | 0.166     | BSC   | 4.216     | BSC    |        |        |

| J   | 0.015     | 0.025 | 0.381     | 0.635  |        |        |

| K   | 0.900     | 1.100 | 22.860    | 27.940 |        |        |

| L   | 0.320     | 0.365 | 8.128     | 9.271  |        |        |

| N   | 0.320 BSC |       | 8.128     | BSC    |        |        |

| Q   | 0.140     | 0.153 | 3.556     | 3.886  |        |        |

| S   |           | 0.620 |           | 15.748 |        |        |

| U   | 0.468     | 0.505 | 11.888    | 12.827 |        |        |

| ٧   |           | 0.735 |           | 18.669 |        |        |

| w   | 0.090     | 0 110 | 2 286     | 2 794  |        |        |

#### PACKAGE DIMENSIONS

#### **D2T SUFFIX**

PLASTIC PACKAGE CASE 936A-02 (D<sup>2</sup>PAK) **ISSUE B**

#### NOTES

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: INCH.

- TAB CONTOUR OPTIONAL WITHIN DIMENSIONS A AND K.

- DIMENSIONS U AND V ESTABLISH A MINIMUM MOUNTING SURFACE FOR TERMINAL 6.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH OR GATE PROTRUSIONS. MOLD FLASH AND GATE PROTRUSIONS NOT TO EXCEED 0.025 (0.635) MAXIMUM.

|     | INCHES    |       | MILLIMETERS |        |  |

|-----|-----------|-------|-------------|--------|--|

| DIM | MIN       | MAX   | MIN         | MAX    |  |

| Α   | 0.386     | 0.403 | 9.804       | 10.236 |  |

| В   | 0.356     | 0.368 | 9.042       | 9.347  |  |

| С   | 0.170     | 0.180 | 4.318       | 4.572  |  |

| D   | 0.026     | 0.036 | 0.660       | 0.914  |  |

| Ε   | 0.045     | 0.055 | 1.143       | 1.397  |  |

| G   | 0.067     | BSC   | 1.702 BSC   |        |  |

| Н   | 0.539     | 0.579 | 13.691      | 14.707 |  |

| K   | 0.050 REF |       | 1.270 REF   |        |  |

| L   | 0.000     | 0.010 | 0.000       | 0.254  |  |

| M   | 0.088     | 0.102 | 2.235       | 2.591  |  |

| N   | 0.018     | 0.026 | 0.457       | 0.660  |  |

| P   | 0.058     | 0.078 | 1.473       | 1.981  |  |

| R   | 5°REF     |       | 5°I         | REF    |  |

| S   | 0.116 REF |       | 2.946       | REF    |  |

| U   | 0.200 MIN |       | 5.080       | MIN    |  |

| V   | 0.250 MIN |       | 6.350       | MIN    |  |

demarks of f

fy, reprefit or f

for f

file of the fi ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) . Solitude services are inject to make triangles without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

N. American Technical Support: 800-282-9855 Toll Free

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

USA/Canada

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative