# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

101.P

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Rene

Custo

April

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

(iii) prevention against any malfunction or mishap.

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

Rev. 7.0 Sept. 1999

#### **Description**

The HD404339 Series is 4-bit HMCS400-Series microcomputer with large-capacity memory designed to increase program productivity. Each microcomputer has an A/D converter, input capture timer, and a 32-kHz oscillator circuit for clock use all built in. They also come with high-voltage I/O pins that can directly drive a fluorescent display.

The HD404339 Series includes six chips: the HD404339 with 16-kword ROM; the HD4043312 with 12-kword ROM; the HD404338 with 8-kword ROM; the HD404336 with 6-kword ROM; the HD4074339 with 16-kword PROM.

The HD4074339 is a PROM version ZTAT™ microcomputer. Programs can be written to the PROM by a PROM writer, which can dramatically shorten system development periods and smooth the process from debugging to mass production. (The PROM program specifications are the same as for the 27256.)

ZTAT™: Zero Turn Around Time ZTAT is a trademark of Hitachi Ltd.

#### **Features**

- 54 I/O pins

- One input-only pin

- 53 input/output pins: 30 pins are high-voltage pins (40 V, max.)

- On-chip A/D converter (8-bit × 12-channel)

- Three timers

- One event counter input

- One timer output

- One input capture timer

- 8-bit clock-synchronous serial interface (1 channel)

- Alarm output

- Built-in oscillators

- Ceramic or crystal oscillator

- External clock drive is also possible

- Subclock: 32.768-kHz crystal oscillator

- Seven interrupt sources

- Two by external sources

- Three by timers

- One each by the A/D converter and serial interface

- Four low-power dissipation modes

- Standby mode

- Stop mode

- Watch mode

- Subactive mode

- Instruction cycle time: 1  $\mu$ s ( $f_{OSC} = 4$  MHz, 1/4 division ratio)

- 1/4, 1/8, 1/16, 1/32 system clock division ratio can be selected

# Ordering Information

| Туре     | Product Name | Model Name  | ROM (words) | RAM (digit) | Package |

|----------|--------------|-------------|-------------|-------------|---------|

| Mask ROM | HD404334     | HD404334S   | 4,096       | 512         | DP-64S  |

|          |              | HD404334FS  | _           |             | FP-64B  |

|          | HD404336     | HD404336S   | 6,144       |             | DP-64S  |

|          |              | HD404336FS  | _           |             | FP-64B  |

|          | HD404338     | HD404338S   | 8,912       |             | DP-64S  |

|          |              | HD404338FS  |             |             | FP-64B  |

|          | HD4043312    | HD4043312S  | 12,288      |             | DP-64S  |

|          |              | HD4043312FS | 0,          |             | FP-64B  |

|          | HD404339     | HD404339S   | 16,384      |             | DP-64S  |

|          |              | HD404339FS  | 70          | . —         | FP-64B  |

| ZTAT™    | HD4074339    | HD4074339S  | 16,384      | K           | DP64S   |

|          |              | HD4074339FS | •           |             | FP-64B  |

#### **Recommended PROM Programmers and Socket Adapters**

| PROM Programm | ner        | Socket Adapte | er          |              |

|---------------|------------|---------------|-------------|--------------|

| Manufacture   | Model Name | Package       | Manufacture | Model Name   |

| DATA I/O corp | 121 B      | DP-64S        | Hitachi     | HS4339ESS01H |

|               |            | FP-64B        |             | HS4339ESF01H |

| AVAL corp     | PKW-1000   | DP-64S        | Hitachi     | HS4339ESS01H |

|               |            | FP-64B        |             | HS4339ESF01H |

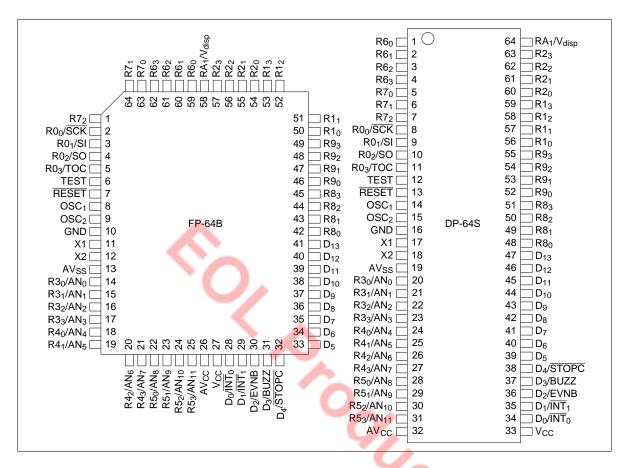

#### **Pin Arrangement**

# **Pin Description**

| Pin | Number |  |

|-----|--------|--|

|-----|--------|--|

|                  |                                                                        | - III Number |                         |     |                                                                                                                                                                       |  |  |

|------------------|------------------------------------------------------------------------|--------------|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Item             | Symbol                                                                 | DP-64S       | FP-64B                  | I/O | Function                                                                                                                                                              |  |  |

| Power supply     | V <sub>cc</sub>                                                        | 33           | 27                      |     | Applies power voltage                                                                                                                                                 |  |  |

|                  | GND                                                                    | 16           | 10                      |     | Connected to ground                                                                                                                                                   |  |  |

|                  | V <sub>disp</sub> (shared with RA <sub>1</sub> )                       | 64           | 58                      |     | Used as a high-voltage output power supply pin when selected by the mask option                                                                                       |  |  |

| Test             | TEST                                                                   | 12           | 6                       | 1   | Cannot be used in user applications. Connect this pin to GND.                                                                                                         |  |  |

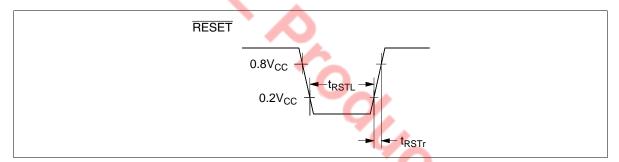

| Reset            | RESET                                                                  | 13           | 7                       | I   | Resets the MCU                                                                                                                                                        |  |  |

| Oscillator       | OSC <sub>1</sub>                                                       | 14           | 8                       | I   | Input/output pin for the internal oscillator. Connect these pins to the ceramic or crystal oscillator, or OSC <sub>1</sub> to an external oscillator circuit.         |  |  |

|                  | OSC <sub>2</sub>                                                       | 15           | 9                       | 0   | -                                                                                                                                                                     |  |  |

|                  | X1                                                                     | 17           | 11                      |     | Used with a 32.768-kHz crystal oscillator for clock purposes                                                                                                          |  |  |

|                  | X2                                                                     | 18           | 12                      | 0   |                                                                                                                                                                       |  |  |

| Port             | D <sub>0</sub> -D <sub>13</sub>                                        | 34–47        | 28–41                   | I/O | Input/output pins addressed individually by bits; $D_0-D_{13}$ are all high-voltage I/O pins. Each pin can be individually configured as selected by the mask option. |  |  |

|                  | RA <sub>1</sub>                                                        | 64           | 58                      | I   | One-bit high-voltage input port pin                                                                                                                                   |  |  |

|                  | R0 <sub>0</sub> -R0 <sub>3</sub> ,<br>R3 <sub>0</sub> -R7 <sub>2</sub> | 00 04        | 1–5,<br>14–25,<br>59–64 | I/O | Four-bit input/output pins consisting of standard voltage pins                                                                                                        |  |  |

|                  | R1 <sub>0</sub> -R2 <sub>3</sub> ,<br>R8 <sub>0</sub> -R9 <sub>3</sub> | 48–63        | 42–57                   | I/O | Four-bit input/output pins consisting of high voltage pins                                                                                                            |  |  |

| Interrupt        | ĪNT₀, ĪNT₁                                                             | 34, 35       | 28, 29                  | I   | Input pins for external interrupts                                                                                                                                    |  |  |

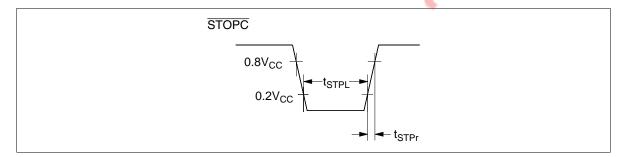

| Stop clear       | STOPC                                                                  | 38           | 32                      | I   | Input pin for transition from stop mode to active mode                                                                                                                |  |  |

| Serial interface | SCK                                                                    | 8            | 2                       | I/O | Serial interface clock input/output pin                                                                                                                               |  |  |

|                  | SI                                                                     | 9            | 3                       | I   | Serial interface receive data input pin                                                                                                                               |  |  |

|                  | SO                                                                     | 10           | 4                       | 0   | Serial interface transmit data output pin                                                                                                                             |  |  |

| Timer            | TOC                                                                    | 11           | 5                       | 0   | Timer output pin                                                                                                                                                      |  |  |

|                  | EVNB                                                                   | 36           | 30                      | I   | Event count input pin                                                                                                                                                 |  |  |

| Alarm            | BUZZ                                                                   | 37           | 31                      | 0   | Square waveform output pin                                                                                                                                            |  |  |

|               |                                   | Pin Num | ber    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------------------------------|---------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Item          | Symbol                            | DP-64S  | FP-64B | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A/D converter | AV <sub>cc</sub>                  | 32      | 26     |     | Power supply for the A/D converter. Connect this pin as close as possible to the $V_{\rm CC}$ pin and at the same voltage as $V_{\rm CC}$ . If the power supply voltage to be used for the A/D converter is not equal to $V_{\rm CC}$ , connect a 0.1- $\mu F$ bypass capacitor between the AV $_{\rm CC}$ and AV $_{\rm SS}$ pins. (However, this is not necessary when the AV $_{\rm CC}$ pin is directly connected to the V $_{\rm CC}$ pin.) |

|               | AV <sub>SS</sub>                  | 19      | 13     |     | Ground for the A/D converter. Connect this pin as close as possible to GND at the same voltage as GND.                                                                                                                                                                                                                                                                                                                                           |

|               | AN <sub>0</sub> -AN <sub>11</sub> | 20–31   | 14–25  | I   | Analog input pins for the A/D converter                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |                                   |         |        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **Pin Description in PROM Mode**

The HD4074339 is a PROM version of a ZTAT™ microcomputer. In PROM mode, the MCU stops operating, thus allowing the user to program the on-chip PROM.

| Pin Number |        | MCU Mode                          |          | PROM Mode                    |     |

|------------|--------|-----------------------------------|----------|------------------------------|-----|

| DP-64S     | FP-64B | Pin                               | I/O      | Pin                          | I/O |

| 1          | 59     | R6 <sub>0</sub>                   | I/O      | O <sub>4</sub>               | I/O |

| 2          | 60     | R6 <sub>1</sub>                   | I/O      | O <sub>3</sub>               | I/O |

| 3          | 61     | R6 <sub>2</sub>                   | I/O      | $O_{\!\scriptscriptstyle 2}$ | I/O |

| 4          | 62     | R6 <sub>3</sub>                   | I/O      | O <sub>1</sub>               | I/O |

| 5          | 63     | R7 <sub>0</sub>                   | I/O      | O <sub>o</sub>               | I/O |

| 6          | 64     | R7 <sub>1</sub>                   | I/O      |                              |     |

| 7          | 1      | R7 <sub>2</sub>                   | I/O      |                              |     |

| 8          | 2      | R0₀/SCK                           | I/O      | V <sub>cc</sub>              |     |

| 9          | 3      | R0 <sub>1</sub> /SI               | I/O      | V <sub>cc</sub>              |     |

| 10         | 4      | R0 <sub>2</sub> /SO               | I/O      |                              |     |

| 11         | 5      | R0₃/TOC                           | I/O      |                              |     |

| 12         | 6      | TEST                              | $\wedge$ | $V_{PP}$                     |     |

| 13         | 7      | RESET                             |          | RESET                        | I   |

| 14         | 8      | OSC <sub>1</sub>                  |          | V <sub>cc</sub>              |     |

| 15         | 9      | OSC <sub>2</sub>                  | 0        |                              |     |

| 16         | 10     | GND                               | _        | GND                          |     |

| 17         | 11     | X1                                | I S      | GND                          |     |

| 18         | 12     | X2                                | 0        |                              |     |

| 19         | 13     | AV <sub>ss</sub>                  | _        | GND                          |     |

| 20         | 14     | R3 <sub>0</sub> /AN <sub>0</sub>  | I/O      | O <sub>0</sub>               | I/O |

| 21         | 15     | R3 <sub>1</sub> /AN <sub>1</sub>  | I/O      | O <sub>1</sub>               | I/O |

| 22         | 16     | R3 <sub>2</sub> /AN <sub>2</sub>  | I/O      | O <sub>2</sub>               | I/O |

| 23         | 17     | R3 <sub>3</sub> /AN <sub>3</sub>  | I/O      | O <sub>3</sub>               | I/O |

| 24         | 18     | R4 <sub>0</sub> /AN <sub>4</sub>  | I/O      | O <sub>4</sub>               | I/O |

| 25         | 19     | R4 <sub>1</sub> /AN <sub>5</sub>  | I/O      | O <sub>5</sub>               | I/O |

| 26         | 20     | R4 <sub>2</sub> /AN <sub>6</sub>  | I/O      | O <sub>6</sub>               | I/O |

| 27         | 21     | R4 <sub>3</sub> /AN <sub>7</sub>  | I/O      | O <sub>7</sub>               | I/O |

| 28         | 22     | R5 <sub>0</sub> /AN <sub>8</sub>  | I/O      |                              |     |

| 29         | 23     | R5 <sub>1</sub> /AN <sub>9</sub>  | I/O      |                              |     |

| 30         | 24     | R5 <sub>2</sub> /AN <sub>10</sub> | I/O      |                              |     |

| Pin Number |        | MCU Mode                          |     | PROM Mode       |     |

|------------|--------|-----------------------------------|-----|-----------------|-----|

| DP-64S     | FP-64B | Pin                               | I/O | Pin             | 1/0 |

| 31         | 25     | R5 <sub>3</sub> /AN <sub>11</sub> | I/O |                 |     |

| 32         | 26     | AV <sub>cc</sub>                  | _   | V <sub>cc</sub> |     |

| 33         | 27     | V <sub>cc</sub>                   | _   | V <sub>cc</sub> |     |

| 34         | 28     | $D_0/\overline{INT}_0$            | I/O | M <sub>o</sub>  | I   |

| 35         | 29     | D <sub>1</sub> /INT <sub>1</sub>  | I/O | M <sub>1</sub>  | I   |

| 36         | 30     | D <sub>2</sub> /EVNB              | I/O | A <sub>1</sub>  | I   |

| 37         | 31     | D <sub>3</sub> /BUZZ              | I/O | $A_2$           | I   |

| 38         | 32     | D₄/STOPC                          | I/O |                 |     |

| 39         | 33     | D <sub>5</sub>                    | I/O | $A_3$           | I   |

| 40         | 34     | D <sub>6</sub>                    | I/O | $A_4$           | I   |

| 41         | 35     | D <sub>7</sub>                    | I/O | $A_9$           | I   |

| 42         | 36     | D <sub>8</sub>                    | I/O | V <sub>cc</sub> |     |

| 43         | 37     | D <sub>9</sub>                    | I/O |                 |     |

| 44         | 38     | D <sub>10</sub>                   | I/O |                 |     |

| 45         | 39     | D <sub>11</sub>                   | I/O |                 |     |

| 46         | 40     | D <sub>12</sub>                   | I/O |                 |     |

| 47         | 41     | D <sub>13</sub>                   | I/O |                 |     |

| 48         | 42     | R8₀                               | I/O | CE              | I   |

| 49         | 43     | R8₁                               | I/O | ŌĒ              | I   |

| 50         | 44     | R8 <sub>2</sub>                   | I/O | A <sub>13</sub> | I   |

| 51         | 45     | R8 <sub>3</sub>                   | I/O | A <sub>14</sub> | I   |

| 52         | 46     | R9₀                               | I/O |                 |     |

| 53         | 47     | R9₁                               | I/O | 40              |     |

| 54         | 48     | R9 <sub>2</sub>                   | I/O | CX              |     |

| 55         | 49     | R9 <sub>3</sub>                   | I/O |                 |     |

| 56         | 50     | R1 <sub>0</sub>                   | I/O | $A_5$           | l   |

| 57         | 51     | R1₁                               | I/O | $A_6$           | I   |

| 58         | 52     | R1 <sub>2</sub>                   | I/O | A <sub>7</sub>  | l   |

| 59         | 53     | R1 <sub>3</sub>                   | I/O | A <sub>8</sub>  | l   |

| 60         | 54     | R2 <sub>0</sub>                   | I/O | $A_0$           | l   |

| 61         | 55     | R2 <sub>1</sub>                   | I/O | A <sub>10</sub> | l   |

| 62         | 56     | R2 <sub>2</sub>                   | I/O | A <sub>11</sub> | l   |

| 63         | 57     | R2 <sub>3</sub>                   | I/O | A <sub>12</sub> | l   |

| 64         | 58     | $RA_1/V_{disp}$                   | I   |                 |     |

Notes: 1. I/O: Input/output pin; I: Input pin; O: Output pin

<sup>2.</sup>  $O_0$  to  $O_4$  consist of two pins each. Tie each pair together before using them.

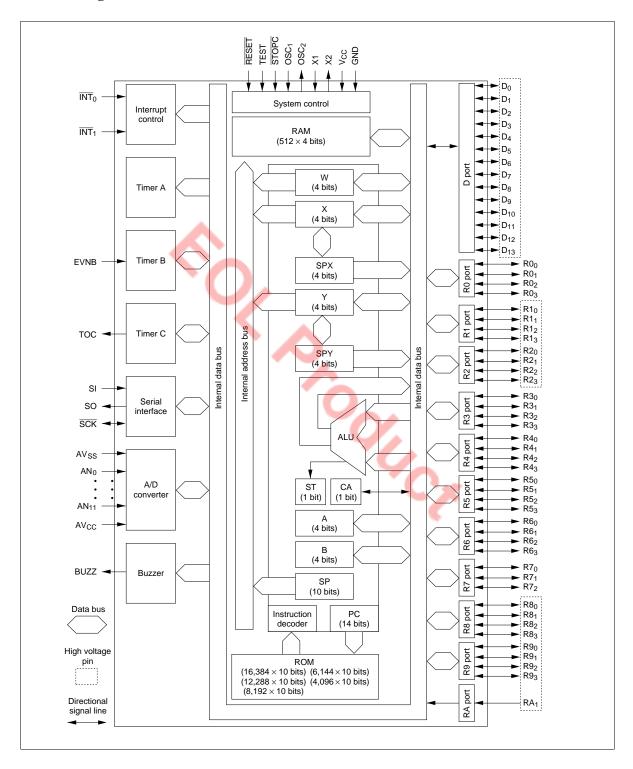

### **Block Diagram**

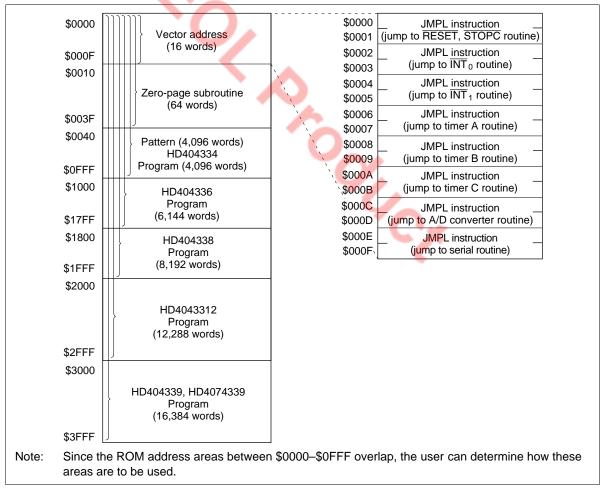

#### **Memory Map**

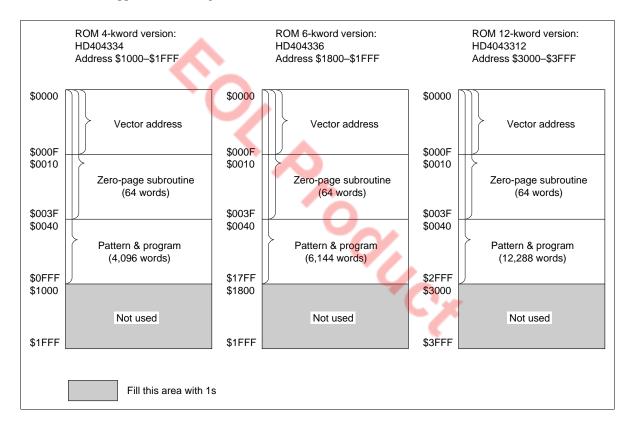

#### **ROM Memory Map**

**Vector Address Area (\$0000–\$000F):** Reserved for JMPL instructions that branch to the start addresses of the reset and interrupt routines.

**Zero-Page Subroutine Area** (\$0000–\$003F): Reserved for subroutines. The program branches to a subroutine in this area in response to the CAL instruction.

Pattern Area (\$0000-\$0FFF): Contains ROM data that can be referenced with the P instruction.

**Program Area** (\$0000-\$0FFF (HD404334), \$0000-\$17FF (HD404336), \$0000-\$1FFF (HD404338), \$0000-\$2FFF (HD4043312), \$0000-\$3FFF (HD404339, HD4074339)): The entire ROM area can be used for program coding.

Figure 1 ROM Memory Map

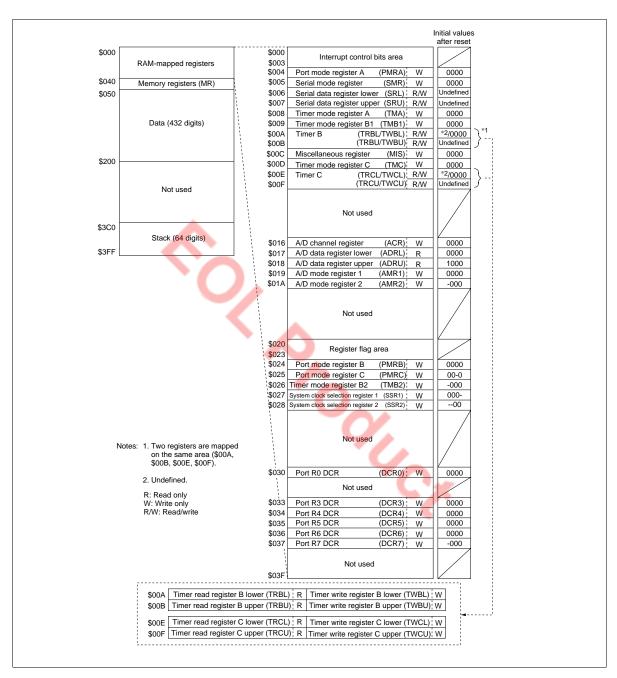

#### **RAM Memory Map**

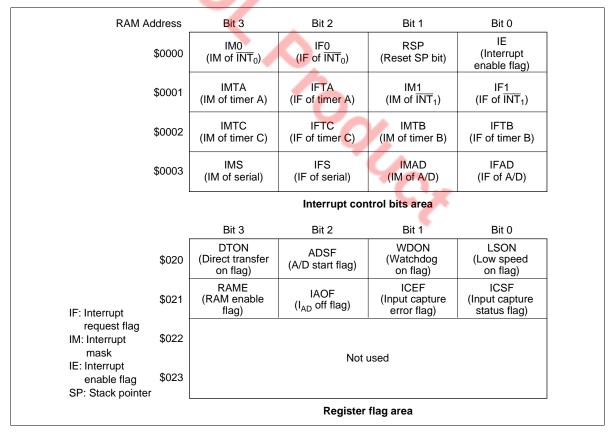

Figure 2 RAM Memory Map and Initial Values

Table 1 Initial Values of Flags after MCU Reset

| Item                 |                                  | Initial Value |  |

|----------------------|----------------------------------|---------------|--|

| Interrupt flags/mask | Interrupt enable flag (IE)       | 0             |  |

|                      | Interrupt request flag (IF)      | 0             |  |

|                      | Interrupt mask (IM)              | 1             |  |

| Bit registers        | Watchdog timer on flag (WDON)    | 0             |  |

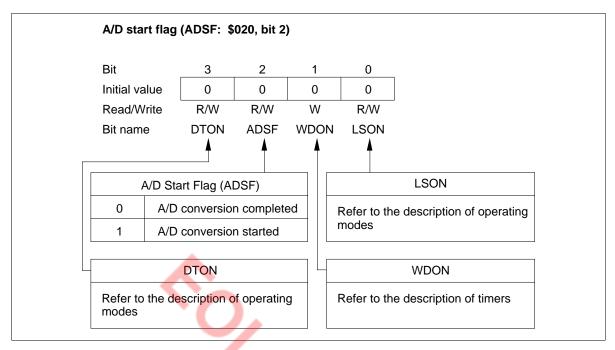

|                      | A/D start flag (ADSF)            | 0             |  |

|                      | Input capture status flag (ICSF) | 0             |  |

|                      | Input capture error flag (ICEF)  | 0             |  |

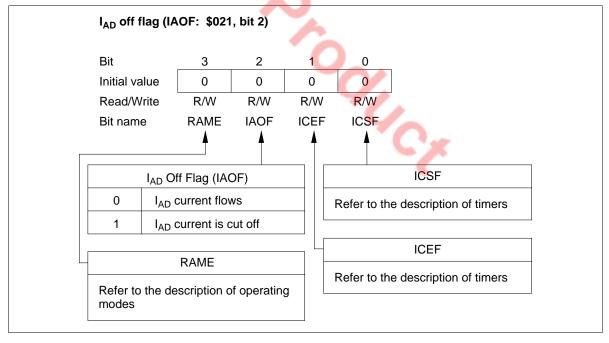

|                      | I <sub>AD</sub> off flag (IAOF)  | 0             |  |

|                      | RAM enable flag (RAME)           | 0             |  |

|                      | Low speed on flag (LSON)         | 0             |  |

|                      | Direct transfer on flag (DTON)   | 0             |  |

Figure 3 Interrupt Control Bits and Register Flag Areas Configuration

|          | SEM/SEMD                    | REM/REMD     | TM/TMD    |

|----------|-----------------------------|--------------|-----------|

| IE       | Allowed                     | Allowed      | Allowed   |

| IM       |                             |              |           |

| LSON     |                             |              |           |

| IAOF     |                             |              |           |

| IF       | Not executed                | Allowed      | Allowed   |

| ICSF     |                             |              |           |

| ICEF     |                             |              |           |

| RAME     |                             |              |           |

| RSP      | Not executed                | Allowed      | Inhibited |

| WDON     | Allowed                     | Not executed | Inhibited |

| ADSF     | Allowed                     | Inhibited    | Allowed   |

| DTON     | Not executed in active mode | Allowed      | Allowed   |

|          | Used in subactive mode      |              |           |

| Not used | Not executed                | Not executed | Inhibited |

Note: WDON is reset by MCU reset or by STOPC enable for stop mode cancellation.

The REM or REMD instruction must not be executed for ADSF during A/D conversion.

DTON is always reset in active mode. If the TM or TMD instruction is executed for the inhibited bits or non-existing bits, the value in ST becomes invalid.

Figure 4 Usage Limitations of RAM Bit Manipulation Instructions

| Memory registers<br>\$040 MR(0)<br>\$041 MR(1)                                  | \$3C0      | Stack area<br>Level 16<br>Level 15 | ] ' (        | 6                 |                     |                      |                     |

|---------------------------------------------------------------------------------|------------|------------------------------------|--------------|-------------------|---------------------|----------------------|---------------------|

| \$042 MR(2)                                                                     |            | Level 14                           |              |                   |                     |                      |                     |

| \$043 MR(3)                                                                     |            | Level 13                           |              |                   |                     |                      |                     |

| \$044 MR(4)                                                                     |            | Level 12                           |              |                   |                     |                      |                     |

| \$045 MR(5)                                                                     |            | Level 11                           |              |                   |                     |                      |                     |

| \$046 MR(6)                                                                     |            | Level 10                           |              |                   |                     |                      |                     |

| \$047 MR(7)                                                                     |            | Level 9                            |              | Bit 3             | Bit 2               | Bit 1                | Bit 0               |

| \$048 MR(8)                                                                     |            | Level 8                            | \$3FC        | ST                | PC <sub>13</sub>    | $\overline{PC}_{12}$ | PC <sub>11</sub>    |

| \$049 MR(9)                                                                     |            | Level 7                            | \$51.0       | 01                | 1 013               | 1 012                | 1 011               |

| \$04A MR(10)                                                                    |            | Level 6                            | \$3FD        | PC <sub>10</sub>  | $\overline{PC}_{q}$ | $\overline{PC}_8$    | PC <sub>7</sub>     |

| \$04B MR(11)                                                                    |            | Level 5                            | ψοι <i>Β</i> | 1 0 10            | 1 09                | 108                  | 107                 |

| \$04C MR(12)                                                                    |            | Level 4                            | \$3FE        | CA                | $\overline{PC}_6$   | $\overline{PC}_{5}$  | $\overline{PC}_{4}$ |

| \$04D MR(13)                                                                    |            | Level 3                            | Ψ01 Ε        |                   | 106                 | 5                    | 1 04                |

| \$04E MR(14)                                                                    |            | Level 2                            | \$3FF        | $\overline{PC}_3$ | $\overline{PC}_2$   | $\overline{PC}_{1}$  | $\overline{PC}_0$   |

| \$04F MR(15)                                                                    | \$3FF      | Level 1                            | ΨΟΙΙ         | 103               | 102                 | 1 01                 | 100                 |

| PC <sub>13</sub> –PC <sub>0</sub> : Progra<br>ST: Status flag<br>CA: Carry flag | am counter |                                    |              |                   |                     |                      |                     |

Figure 5 Configuration of Memory Registers and Stack Area, and Stack Position

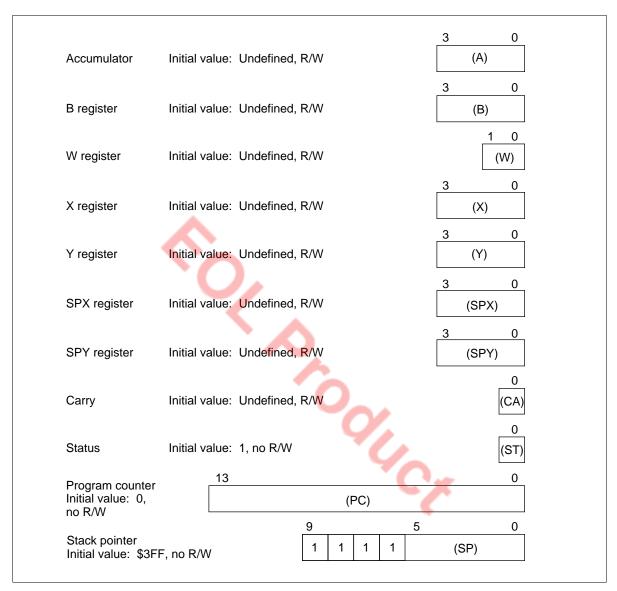

### **Registers and Flags**

Figure 6 Registers and Flags

#### **Addressing Modes**

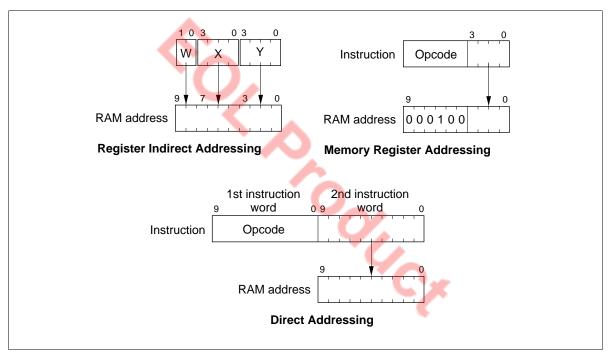

#### **RAM Addressing Modes**

**Register Indirect Addressing Mode:** The contents of the W, X, and Y registers (10 bits total) are used as a RAM address.

**Direct Addressing Mode:** A direct addressing instruction consists of two words. The first word contains the opcode, and the contents of the second word (10 bits) are used as a RAM address.

**Memory Register Addressing Mode (LAMR, XMRA):** The memory registers (MR), which are located in 16 addresses from \$040 to \$04F, are accessed with the LAMR and XMRA instructions.

Figure 7 RAM Addressing Modes

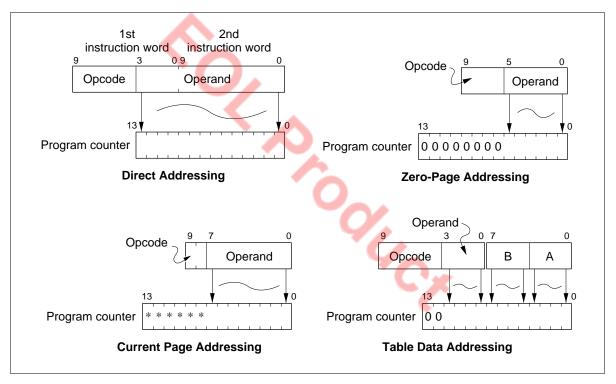

#### **ROM Addressing Modes**

**Direct Addressing Mode:** A program can branch to any address in ROM memory space by executing the JMPL, BRL, or CALL instruction.

**Current Page Addressing Mode:** A program can branch to any address in the current page (256 words per page) by executing the BR instruction.

**Zero-Page Addressing Mode:** A program can branch to any subroutine located in the zero-page subroutine area (\$0000–\$003F) by executing the CAL instruction.

**Table Data Addressing Mode:** A program can branch to an address determined by the contents of 4-bit immediate data, the accumulator, and the B register by executing the TBR instruction.

Figure 8 ROM Addressing Modes

#### **Instruction Set**

Table 2 **Instruction Set Classification**

| Instruction Type     | nstruction Type Function                                                                      |                         |

|----------------------|-----------------------------------------------------------------------------------------------|-------------------------|

| Immediate            | Transferring constants to the accumulator, B register, and RAM.                               | 4                       |

| Register-to-register | Transferring contents of the B, Y, SPX, SPY, or memory registers to the accumulator.          | 8                       |

| RAM addressing       | Available when accessing RAM in register indirect addressing mode.                            | 13                      |

| RAM register         | Transferring data between the accumulator and memory.                                         | 10                      |

| Arithmetic           | Performing arithmetic operations with the contents of the accumulator, B register, or memory. | 25                      |

| Compare              | Comparing contents of the accumulator or memory with a constant.                              | 12                      |

| RAM bit manipulation | Bit set, bit reset, and bit test.                                                             | 6                       |

| ROM addressing       | Branching and jump instructions based on the status condition.                                | 8                       |

| Input/output         | Controlling the input/output of the R and D ports; ROM data reference with the P instruction. | 11                      |

| Control              | Controlling the serial communication interface and low-power dissipation modes.               | 4                       |

|                      |                                                                                               | Total: 101 instructions |

## **Interrupts**

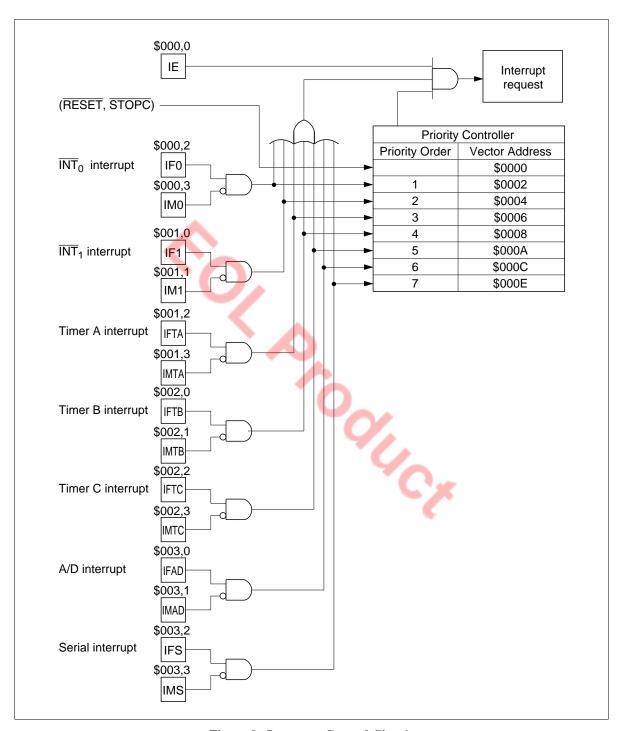

Figure 9 Interrupt Control Circuit

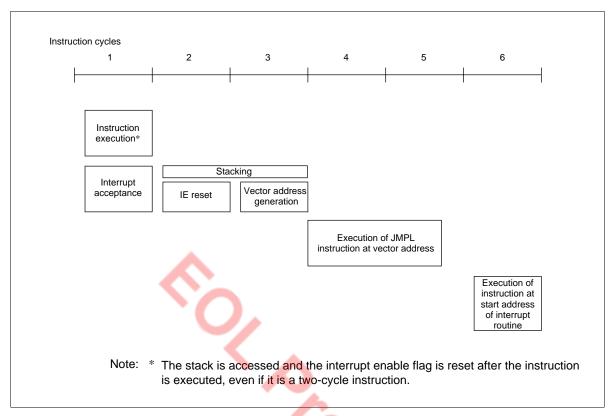

Figure 10 Interrupt Processing Sequence

## **Operating Modes**

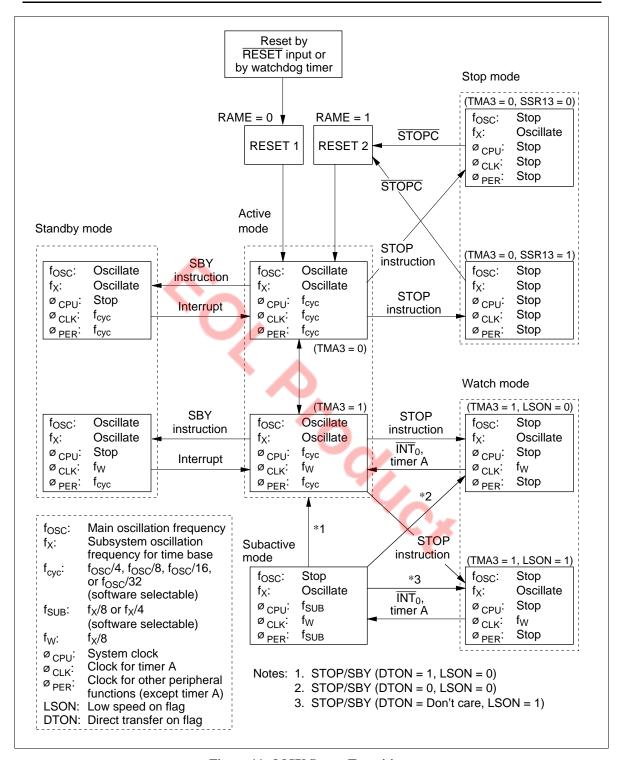

The MCU has five operating modes as shown in table 3. Transitions between operating modes are shown in figure 11.

**Table 3** Operations in Each Operating Mode

| Function             | Active Mode | Subactive<br>Mode | Standby Mode | Watch Mode | Stop Mode |

|----------------------|-------------|-------------------|--------------|------------|-----------|

| System oscillator    | OP          | Stopped           | OP           | Stopped    | Stopped   |

| Subsystem oscillator | OP          | OP                | OP           | OP         | * OP      |

| CPU                  | OP          | OP                | Retained     | Retained   | Reset     |

| RAM                  | OP          | OP                | Retained     | Retained   | Retained  |

| Timer A              | OP          | OP                | OP           | OP         | Reset     |

| Timers B, C          | OP          | OP                | OP           | Stopped    | Reset     |

| Serial               | OP          | OP                | OP           | Stopped    | Reset     |

| A/D                  | ОР          | Stopped           | OP           | Stopped    | Reset     |

| I/O                  | OP          | OP                | Retained     | Retained   | Reset     |

Notes: OP implies in operation.

COCK

<sup>\*</sup> Oscillation can be switched on or off with bit 3 of system clock selection register 1 (SSR1: \$027).

**Figure 11 MCU Status Transitions**

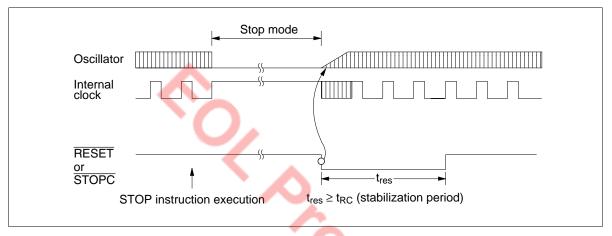

In stop mode, the system oscillator is stopped. To ensure a proper oscillation stabilization period of at least  $t_{RC}$  when clearing stop mode, execute the cancellation according to the timing chart in figure 12.

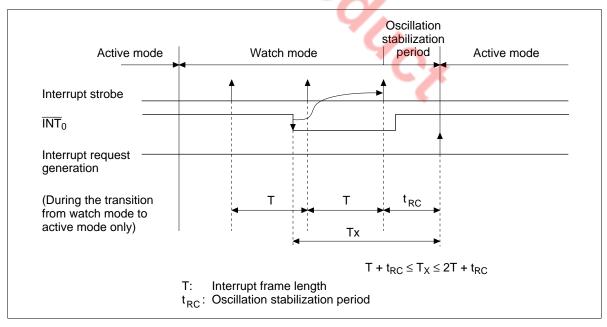

In watch and subactive modes, a timer A or  $\overline{INT}_0$  interrupt can be accepted during the interrupt frame period T (see figure 13).

Note: In watch and subactive modes, an interrupt will not be properly detected if the  $\overline{\text{INT}}_0$  high or low level period is shorter than the interrupt frame period T. Thus, when operating in watch and subactive modes, maintain the  $\overline{\text{INT}}_0$  high or low level period longer than period T to ensure interrupt detection.

Figure 12 Timing of Stop Mode Cancellation

Figure 13 Interrupt Frame

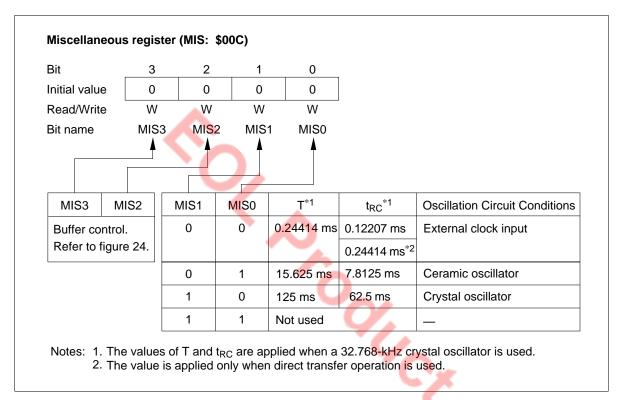

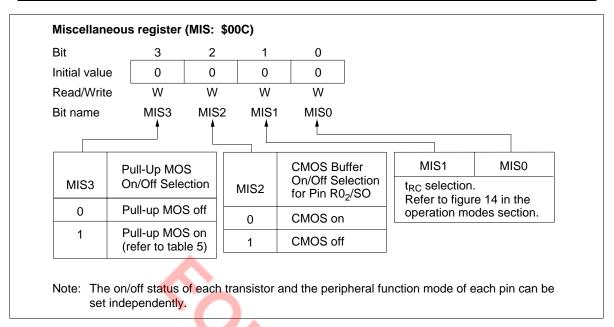

The MCU automatically provides an oscillation stabilization period  $t_{RC}$  when operation switches from watch mode to active mode. The interrupt frame period T and one of three values for  $t_{RC}$  can be selected with the miscellaneous register (MIS: \$00C), as listed in figure 14.

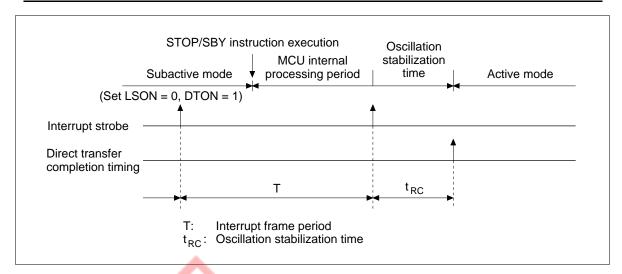

Operation can switch directly from subactive mode to active mode, as illustrated in figure 15. In this case, the transition time  $T_D$  obeys the following relationship.

$$t_{\scriptscriptstyle RC} < T_{\scriptscriptstyle D} < T + t_{\scriptscriptstyle RC}$$

Figure 14 Miscellaneous Register

Figure 15 Direct Transition Timing

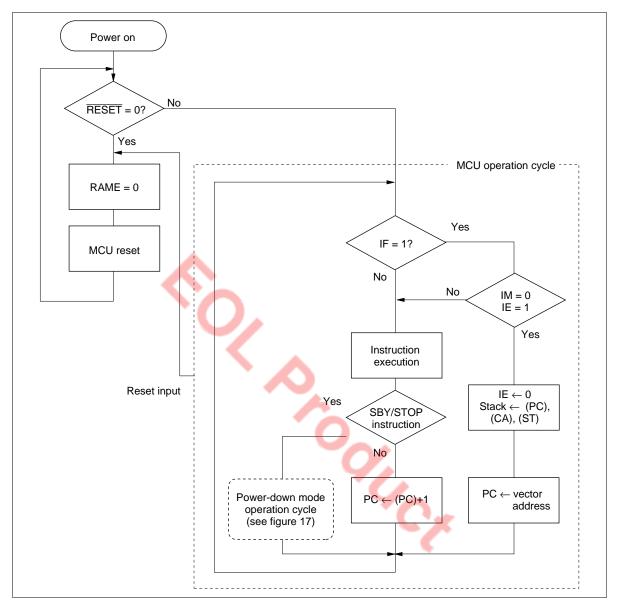

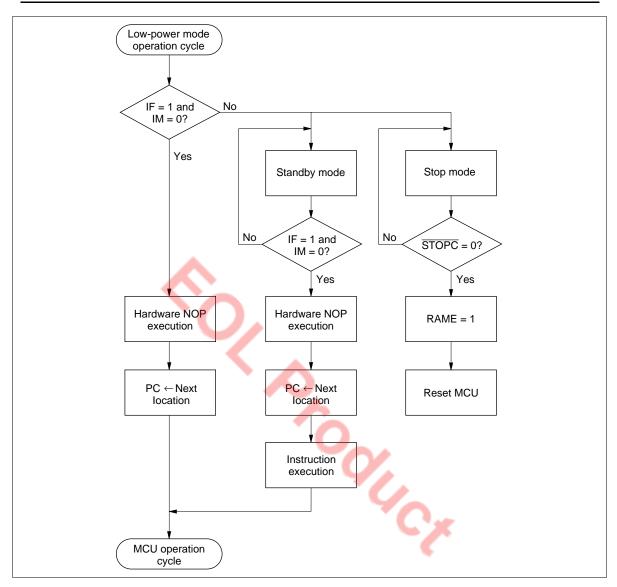

**MCU Operation Sequence:** The MCU operation flow is shown in figures 16 and 17. RESET input is asynchronous, and causes an immediate transition to the reset state from any MPU operation state.

The low-power mode operation sequence is shown in figure 17. With the IE flag cleared and an interrupt flag set together with its interrupt mask cleared, if a STOP/SBY instruction is executed, the instruction is cancelled (regarded as an NOP) and the following instruction is executed. Before executing a STOP/SBY instruction, make sure all interrupt flags are cleared or all interrupts are masked.

Office

Figure 16 MCU Operation Sequence (Power On)

Figure 17 MCU Operating Sequence (Low-Power Mode Operation)

#### **Oscillator Circuit**

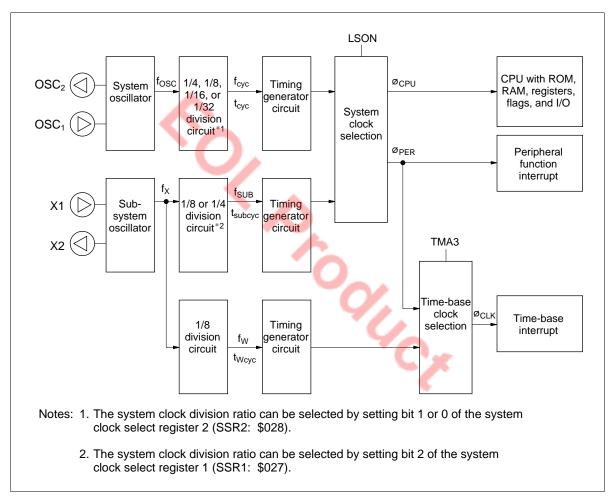

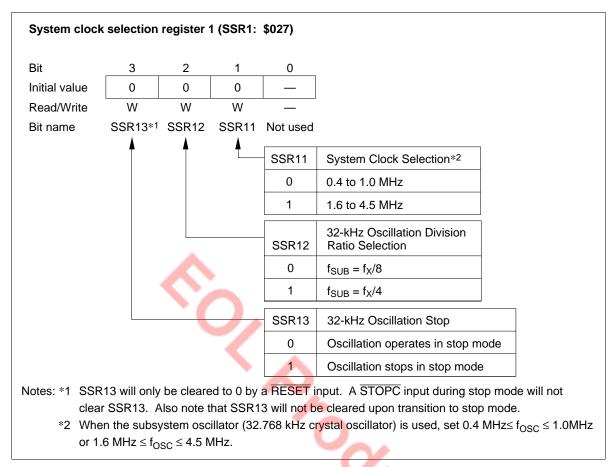

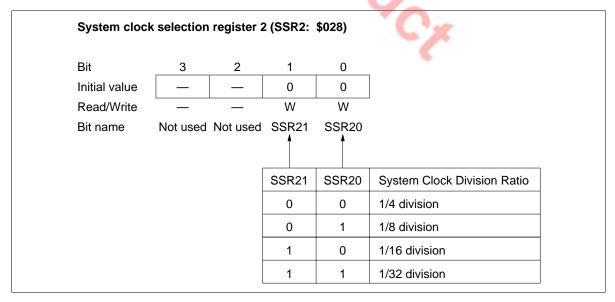

Figure 18 shows a block diagram of the clock generation circuit. The system clock frequency of the oscillator connected to OSC<sub>1</sub> and OSC<sub>2</sub> can be selected by system clock selection registers 1 and 2 (SSR1, 2: \$027, \$028) as shown in figures 20 and 21.

The system clock division ratio can be set by software to be 1/4, 1/8, 1/16, or 1/32. The subsystem clock division ratio can be set by software to be 1/4 or 1/8.

Figure 18 Clock Generation Circuit

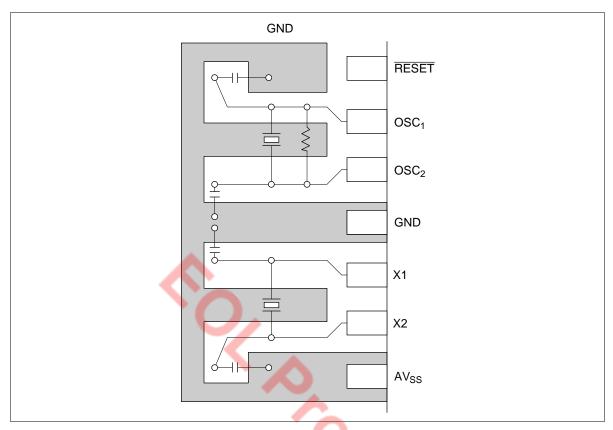

Figure 19 Typical Layout of Crystal and Ceramic Oscillators

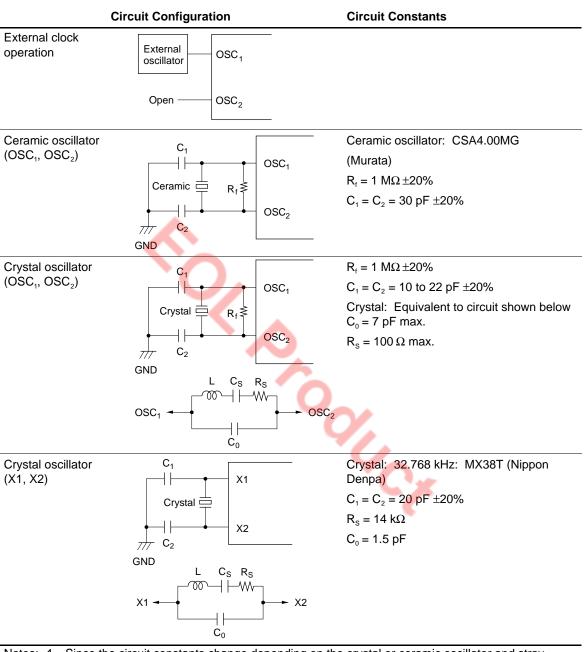

**Table 4** Oscillator Circuit Examples

- Notes: 1. Since the circuit constants change depending on the crystal or ceramic oscillator and stray capacitance of the board, the user should consult with the crystal or ceramic oscillator manufacturer to determine the circuit parameters.

- 2. Wiring among OSC<sub>1</sub>, OSC<sub>2</sub>, X1, X2 and elements should be as short as possible, and must not cross other wiring (see figure 19).

- 3. When a 32.768-kHz crystal oscillator is not used, fix pin X1 to GND and leave pin X2 open.

Figure 20 System Clock Selection Register 1 (SSR1)

Figure 21 System Clock Selection Register 2 (SSR2)

#### I/O Ports

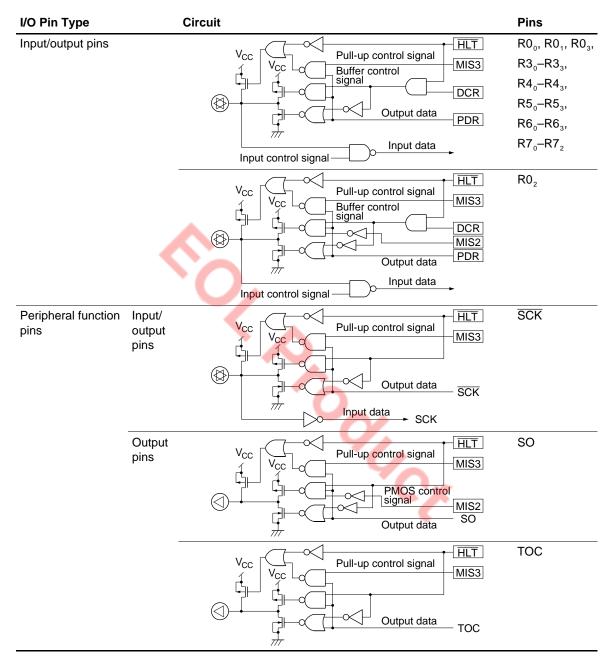

The MCU has 53 input/output pins  $(D_0-D_{13}, RO_0-R9_3)$  and one input-only pin  $(RA_1)$ .

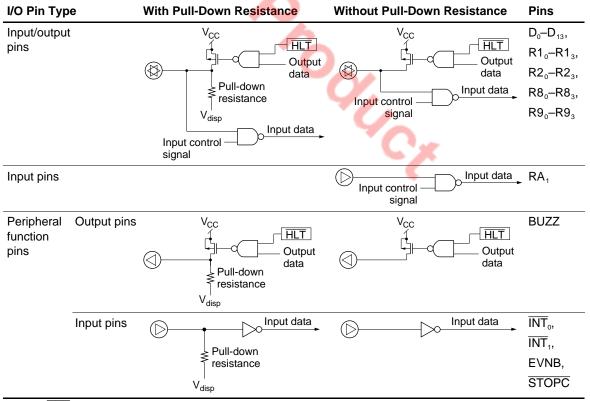

- The 30 pins consisting of ports D<sub>0</sub>–D<sub>13</sub>, R1, R2, R8, and R9 are all high-voltage I/O pins. RA<sub>1</sub> is a highvoltage input-only pin. The high-voltage pins can be equipped with or without pull-down resistance, as selected by the mask option.

- All standard voltage output pins are CMOS output pins. However, the R0<sub>2</sub>/SO pin can be programmed for NMOS open-drain output.

- In stop mode, input/output pins go to the high-impedance state.

- All standard voltage input/output pins have pull-up MOS built in, which can be individually turned on or off by software (Table 5).

Pull-up MOS on/off settings can be made independently of settings as on-chip supporting module pins.

Table 5 Control of Standard I/O Pins by Program

| MIS3 (bit 3 of MIS)    |      | 0    |   |    |    | 1 |    |    |    |

|------------------------|------|------|---|----|----|---|----|----|----|

| DCR                    |      | 0 <  |   | 1  |    | 0 |    | 1  |    |

| PDR                    |      | 0    | 1 | 0  | 1  | 0 | 1  | 0  | 1  |

| CMOS buffer            | PMOS | _    |   | _  | On | _ | _  | _  | On |

|                        | NMOS | _    | _ | On | _  | _ | _  | On | _  |

| Pull-up MOS            |      | _    | _ | +0 | )  | _ | On | _  | On |

| Note: — indicates off. |      | O/CX |   |    |    |   |    |    |    |

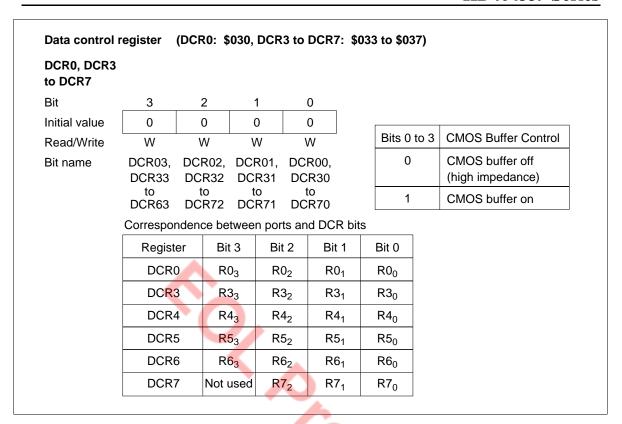

Figure 22 Data Control Register (DCR)

Table 6 Circuit Configurations of Standard I/O Pins

| I/O Pin Type              | Circuit         | Pins                              |

|---------------------------|-----------------|-----------------------------------|

| Peripheral function Input | V <sub>cc</sub> | SI                                |

| pins pins                 | Input data      | HLT                               |

|                           | V <sub>CC</sub> | AN <sub>0</sub> -AN <sub>11</sub> |

|                           |                 | HLT MIS3 PDR                      |

|                           |                 | —— A/D input                      |

|                           | Input control   |                                   |

- Notes: 1. In stop mode, the MCU is reset and the peripheral function selection is cancelled. The HLT signal goes low, and input/output pins enter the high-impedance state.

- 2. The HLT signal is 1 in active, standby, watch, and subactive modes.

Table 7 Circuit Configurations for High-Voltage Input/Output Pins

Note: HLT goes high in active, standby, watch, and subactive modes.

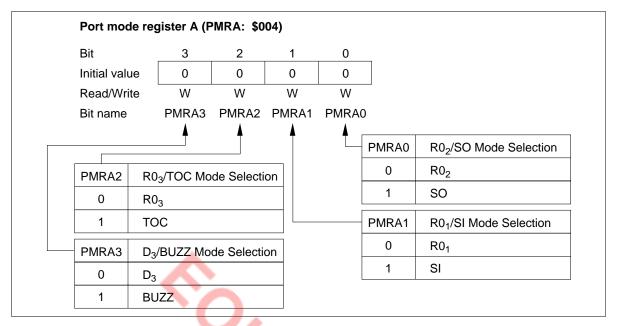

Figure 23 Port Mode Register A (PMRA)

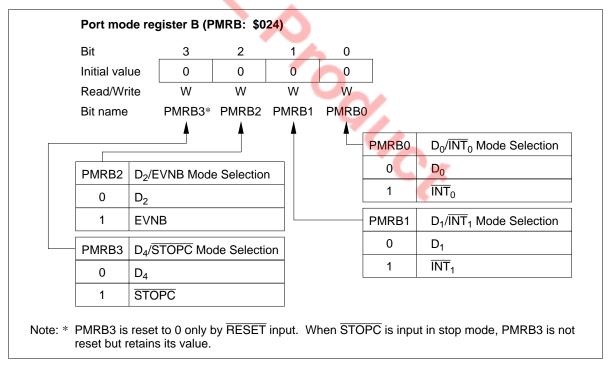

Figure 24 Port Mode Register B (PMRB)

Figure 25 Miscellaneous Register

#### **Prescaler**

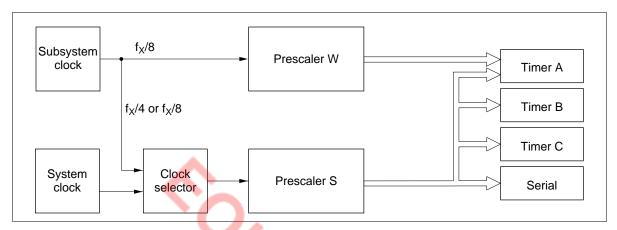

The MCU has two built-in prescalers, S and W (PSS, PSW). They divide the system clock and subsystem clock, and output these divided clocks to the peripheral function modules, as shown in figure 26.

Figure 26 Prescaler Output Supply

NO OLICA

#### **Timers**

The MCU has three built-in timers A, B, and C. The functions of each timer are listed in table 7.

#### Timer A

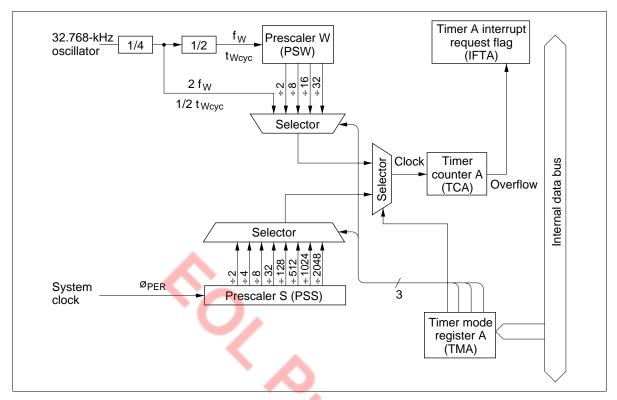

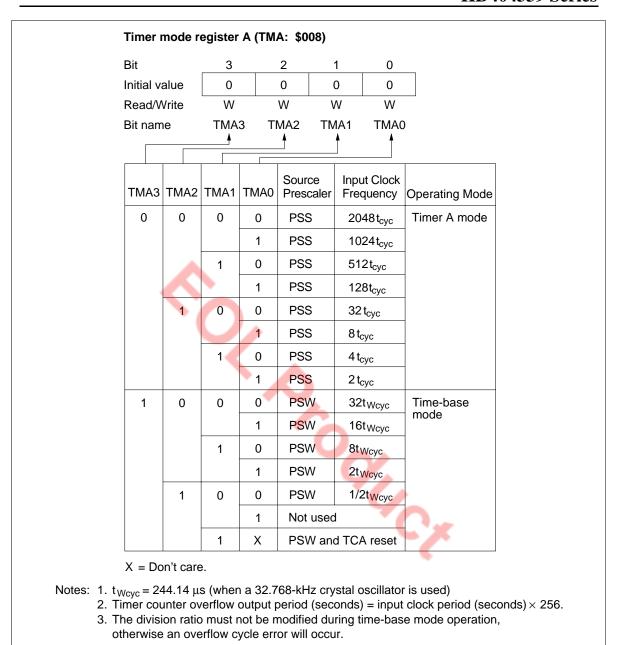

Timer A is an 8-bit free-running timer that can also be used as a clock time-base with a 32.768-kHz subsystem oscillator. Timer A has the following features:

- One of eight internal clocks can be selected from prescaler S according to the setting of timer mode register A (TMA: \$008)

- In time-base mode, one of five internal clocks can be selected from prescaler W according to the setting of timer mode register A

- An interrupt request can be generated when timer counter A (TCA) overflows

- Input clock frequency must not be modified during timer A operation

**Table 7** Timer Functions

| Functions       |                | Timer A   | Timer B                 | Timer C   |   |

|-----------------|----------------|-----------|-------------------------|-----------|---|

| Clock source    | Prescaler S    | Available | Available               | Available | J |

|                 | Prescaler W    | Available | _                       | _         |   |

|                 | External event | <u> </u>  | Available               | _         |   |

| Timer functions | Free-running   | Available | Available               | Available |   |

|                 | Time base      | Available | 7-/                     | _         |   |

|                 | Event counter  | _         | Available               | _         |   |

|                 | Reload         | _         | Availa <mark>ble</mark> | Available |   |

|                 | Watchdog       | _         | - (                     | Available |   |

|                 | Input capture  | _         | Available               | _         |   |

| Timer output    | PWM            | _         | _                       | Available |   |

Figure 27 Timer A Block Diagram

Offick

Figure 28 Timer Mode Register A (TMA)

#### Timer B

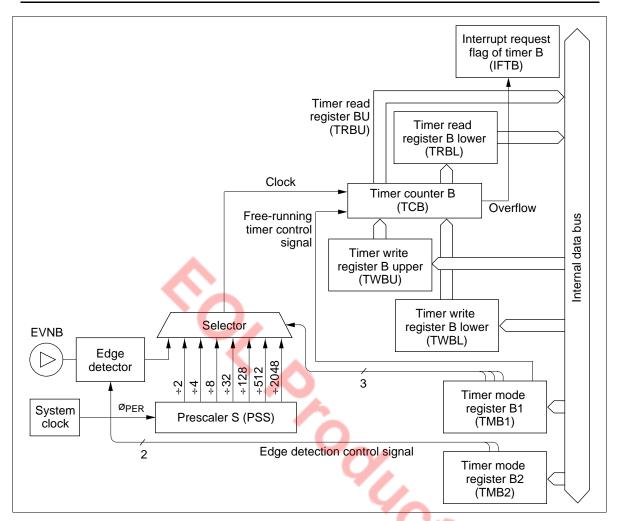

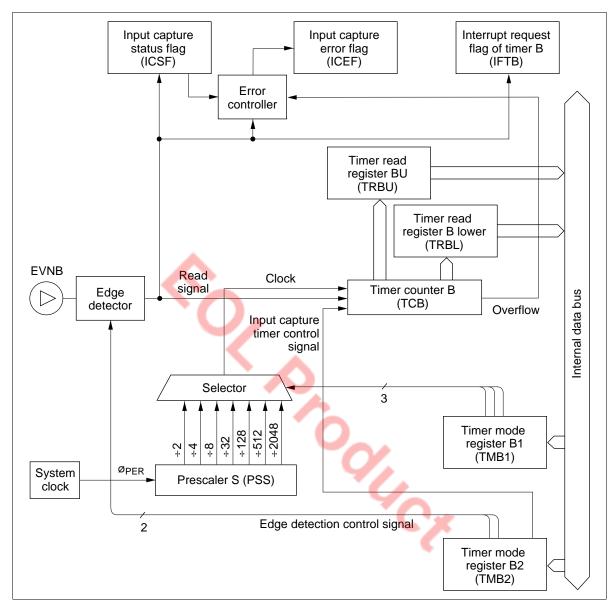

Timer B is an 8-bit multifunction timer that includes free-running, reload, and input capture timer features. These are described as follows.

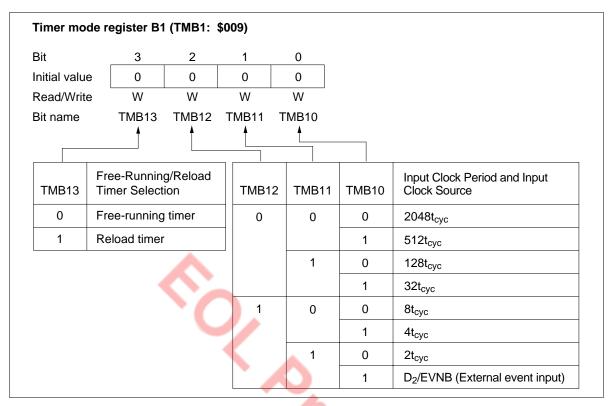

- By setting timer mode register B1 (TMB1: \$009), one of seven internal clocks supplied from prescaler S can be selected, or timer B can be used as an external event counter

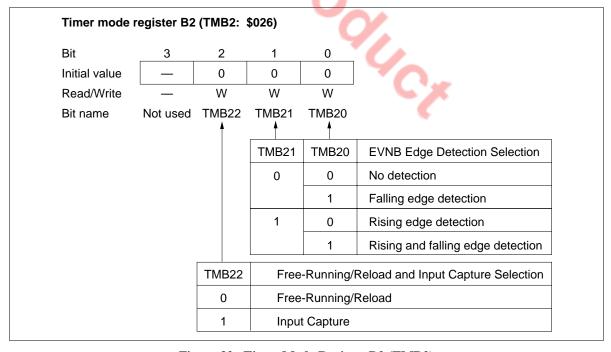

- By setting timer mode register B2 (TMB2: \$026), detection edge type of EVNB can be selected.

- By setting timer write register BL, U (TWBL, U: \$00A, \$00B), timer counter B (TCB) can be written to during reload timer operation

- By setting timer read register BL, U (TRBL, U: \$00A, \$00B), the contents of timer counter B can be read out

- Timer B can be used as an input capture timer to count the clock cycles between trigger edges input as an external event

- An interrupt can be requested when timer counter B overflows or when a trigger input edge is received during input capture operation

Figure 29 Timer B Free-Running and Reload Operation Block Diagram

Figure 30 Timer B Input Capture Operation Block Diagram

Figure 31 Timer Mode Register B1 (TMB1)

Figure 32 Timer Mode Register B2 (TMB2)

#### Timer C

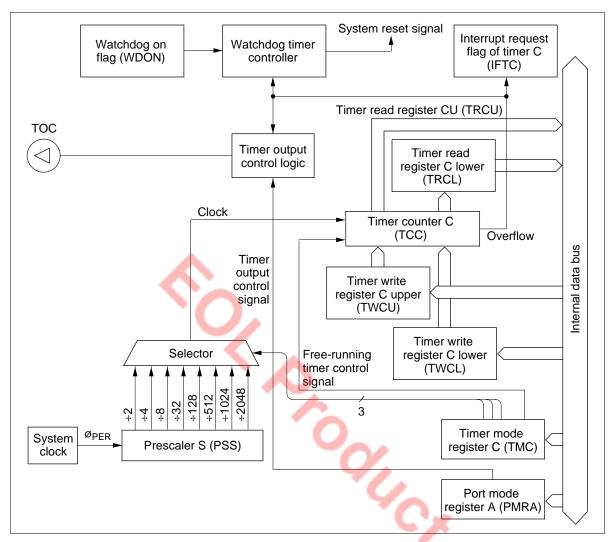

Timer C is an 8-bit multifunction timer that includes free-running, reload, and watchdog timer features, which are described as follows.

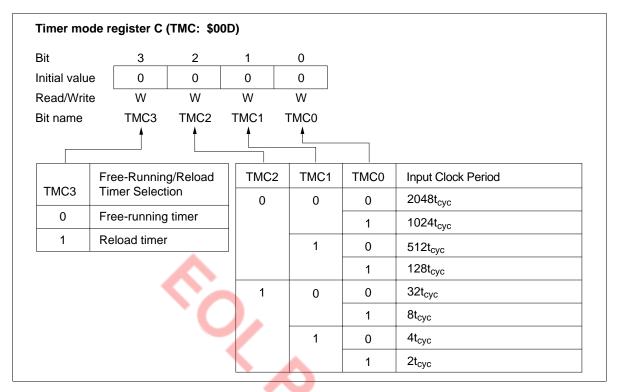

- By setting timer mode register C (TMC: \$00D), one of eight internal clocks supplied from prescaler S can be selected

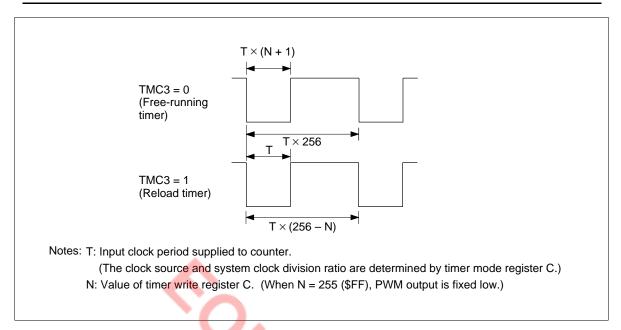

- By selecting pin TOC with bit 2 (PMRA2) of port mode register A (PMRA: \$004), timer C output (PWM output) is enabled

- By setting timer write register CL, U (TWCL, U: \$00E, \$00F), timer counter C (TCC) can be written to

- By setting timer read register CL, U (TRCL, U: \$00E, \$00F), the contents of timer counter C can be read out

- An interrupt can be requested when timer counter C overflows

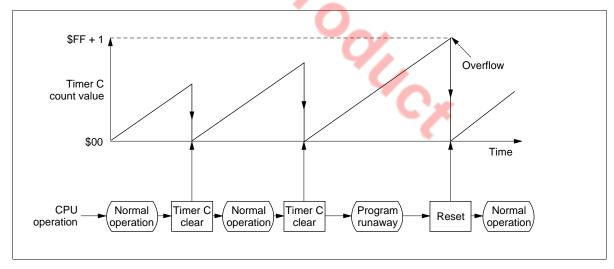

- Timer counter C can be used as a watchdog timer for detecting runaway programs

Figure 33 Timer C Block Diagram

Figure 34 Timer Mode Register C (TMC)

Figure 35 Watchdog Timer Operation Flowchart

Figure 36 PWM Output Waveform

NO OLCA

#### **Notes on Use**

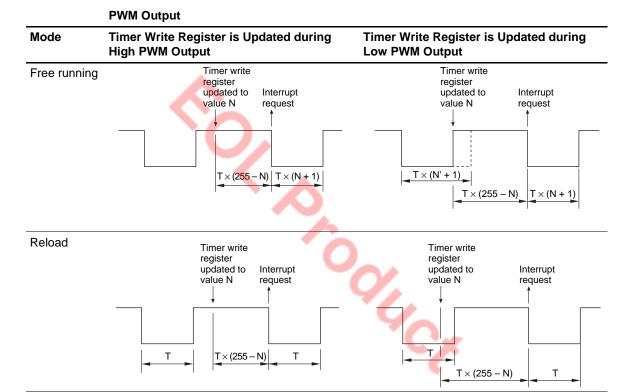

When using the timer output as PWM output, note the following point. From the update of the timer write register until the occurrence of the overflow interrupt, the PWM output differs from the period and duty settings, as shown in table 8. The PWM output should therefore not be used until after the overflow interrupt following the update of the timer write register. After the overflow, the PWM output will have the set period and duty cycle.

Table 8 PWM Output Following Update of Timer Write Register

#### **Alarm Output Function**

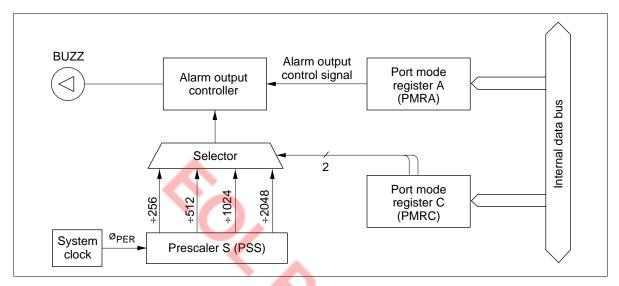

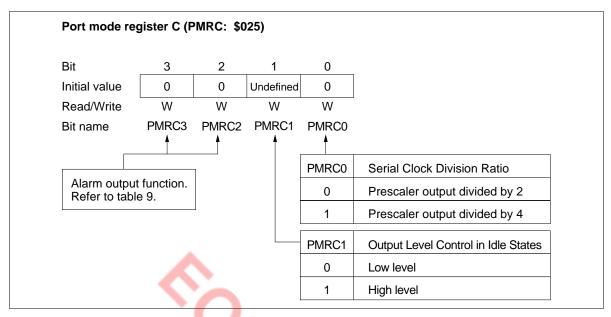

The MCU has an alarm output function built in. By setting port mode register C (PMRC: \$025), one of four alarm frequencies supplied from the PSS can be selected.

Figure 37 Alarm Output Function Block Diagram

Table 9 Port Mode Register C

#### **PMRC**

| Bit 3 | Bit 2 | System Clock Divisor | 9,  |

|-------|-------|----------------------|-----|

| 0     | 0     | ÷ 2048               | 0   |

|       | 1     | ÷ 1024               | 10- |

| 1     | 0     | ÷ 512                |     |

|       | 1     | ÷ 256                |     |

#### **Serial Interface**

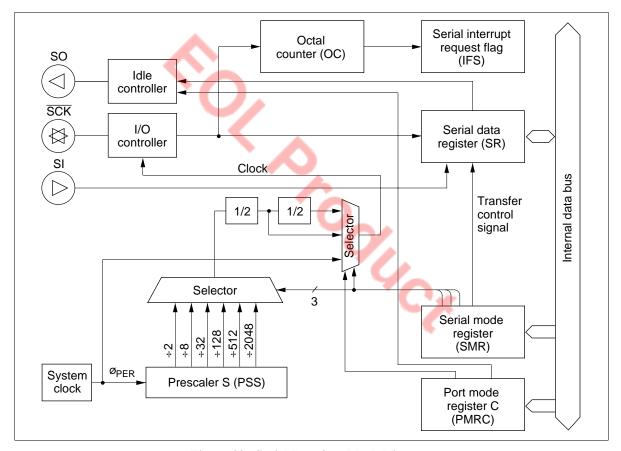

The MCU has a one-channel serial interface built in with the following features.

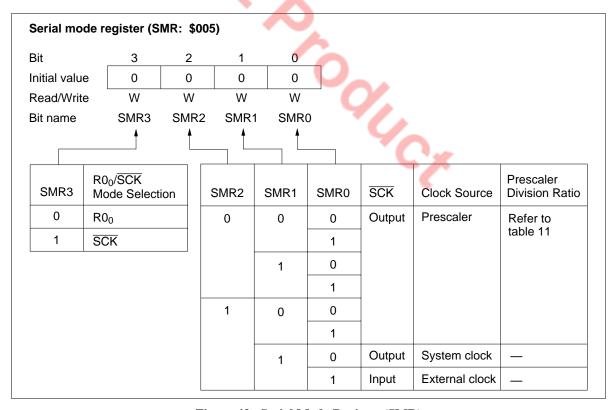

- One of 13 different internal clocks or an external clock can be selected as the transmit clock. The internal clocks include the six prescaler outputs divided by two and by four, and the system clock.

- During idle status, the serial output pin can be controlled to be high or low output

- · Transmit clock errors can be detected

- An interrupt request can be generated after transfer has completed when an error occurs

Figure 38 Serial Interface Block Diagram

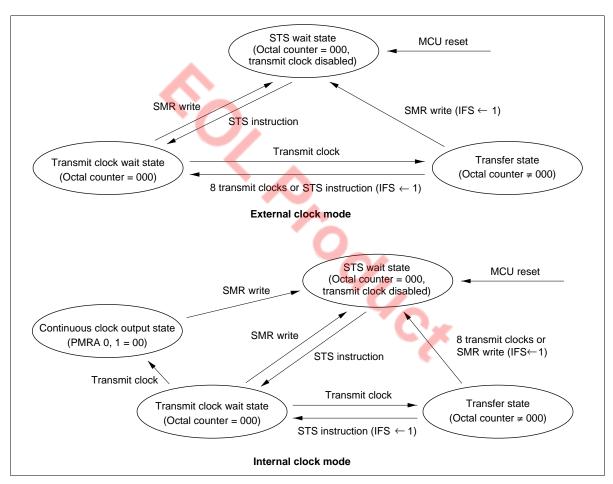

**Table 10** Serial Interface Operating Modes

| SMR   | PMRA  |       |                              |  |  |  |  |  |

|-------|-------|-------|------------------------------|--|--|--|--|--|

| Bit 3 | Bit 1 | Bit 0 | Operating Mode               |  |  |  |  |  |

| 1     | 0     | 0     | Continuous clock output mode |  |  |  |  |  |

|       |       | 1     | Transmit mode                |  |  |  |  |  |

|       | 1     | 0     | Receive mode                 |  |  |  |  |  |

|       |       | 1     | Transmit/receive mode        |  |  |  |  |  |

Figure 39 Serial Interface State Transitions

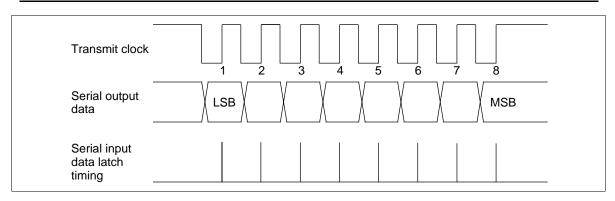

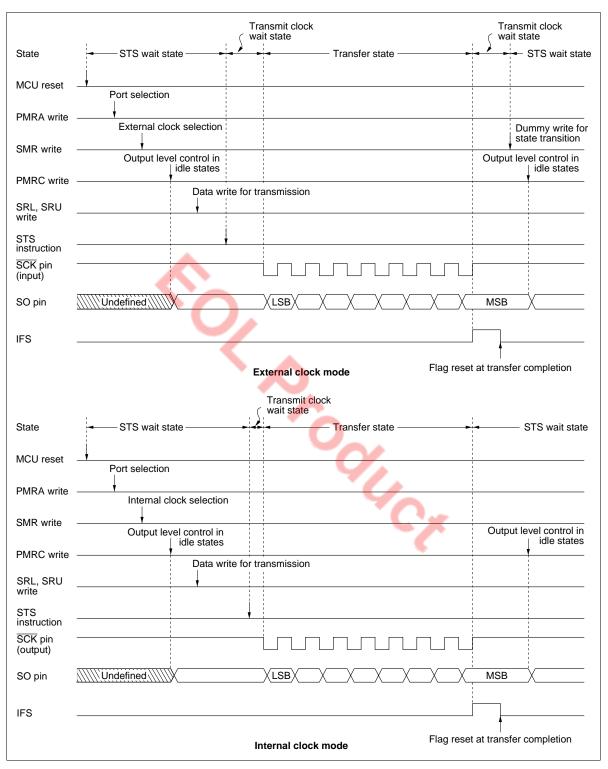

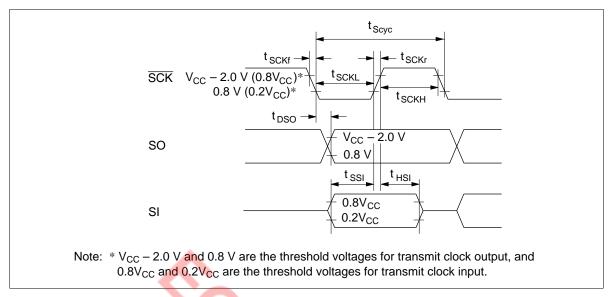

Figure 40 Serial Interface Timing

Figure 41 Example of Serial Interface Operation Sequence

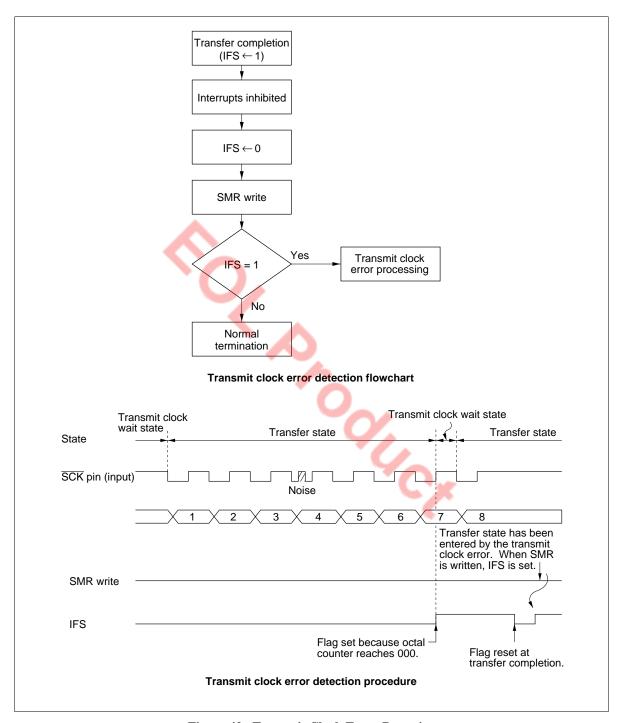

Transmit clock errors are detected as illustrated in figure 42.

Figure 42 Transmit Clock Error Detection

**Table 11** Transmit Clock Selection

| PMRC  | SMR   |       |       |                      |                                 |

|-------|-------|-------|-------|----------------------|---------------------------------|

| Bit 0 | Bit 2 | Bit 1 | Bit 0 | System Clock Divisor | <b>Transmit Clock Frequency</b> |

| 0     | 0     | 0     | 0     | ÷ 2048               | 4096t <sub>cyc</sub>            |

|       |       |       | 1     | ÷ 512                | 1024t <sub>cyc</sub>            |

|       |       | 1     | 0     | ÷ 128                | 256t <sub>cyc</sub>             |

|       |       |       | 1     | ÷ 32                 | 64t <sub>cyc</sub>              |

|       | 1     | 0     | 0     | ÷ 8                  | 16t <sub>cyc</sub>              |

|       |       |       | 1     | ÷ 2                  | 4t <sub>cyc</sub>               |

| 1     | 0     | 0     | 0     | ÷ 4096               | 8192t <sub>cyc</sub>            |

|       |       |       | 1     | ÷ 1024               | 2048t <sub>cyc</sub>            |

|       |       | 1     | 0     | ÷ 256                | 512t <sub>cyc</sub>             |

|       |       | •     | 1     | ÷ 64                 | 128t <sub>cyc</sub>             |

|       | 1     | 0     | 0     | ÷ 16                 | 32t <sub>cyc</sub>              |

|       |       |       | 1     | ÷ 4                  | 8t <sub>cyc</sub>               |

Figure 43 Serial Mode Register (SMR)

Figure 44 Port Mode Register C (PMRC)

#### A/D Converter

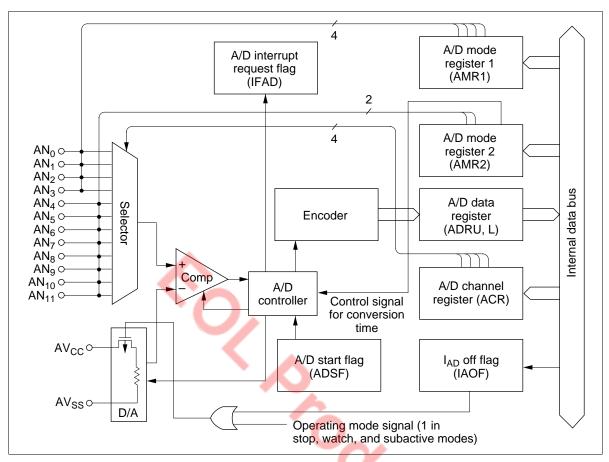

The MCU also contains a built-in A/D converter that uses a sequential comparison method with a resistance ladder. It can perform digital conversion of twelve analog inputs with 8-bit resolution. The following describes the A/D converter.

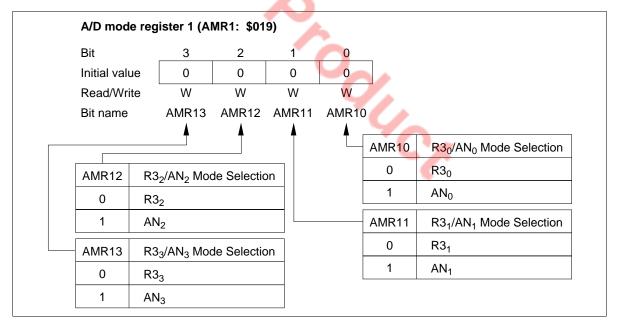

- A/D mode register 1 (AMR1: \$019) is used to select digital or analog ports

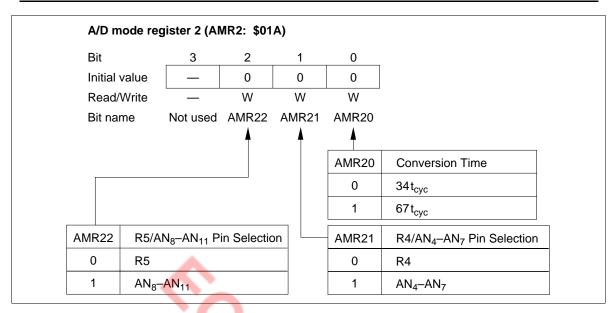

- A/D mode register 2 (AMR2: \$01A) is used to set the A/D conversion speed and to select digital or analog ports

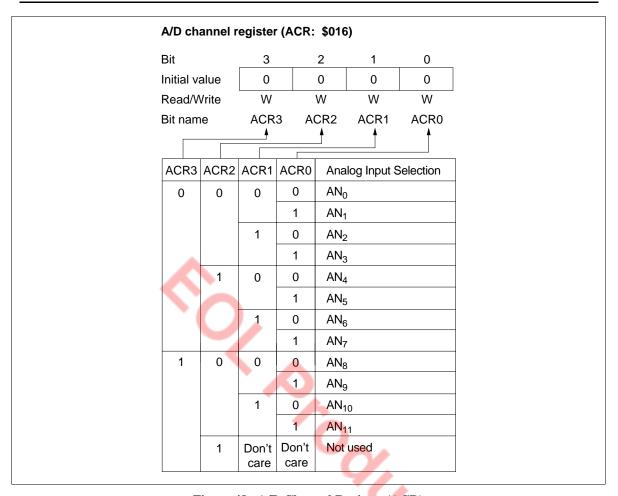

- The A/D channel register (ACR: \$016) is used to select an analog input channel

- A/D conversion is started by setting the A/D start flag (ADSF: \$020, 2) to 1. After the conversion is completed, converted data is stored in the A/D data register, and at the same time the A/D start flag is cleared to 0.

- By setting the I<sub>AD</sub> off flag (IAOF: \$021, 2) to 1, the current flowing through the resistance ladder can be cut off even while operating in standby or active mode

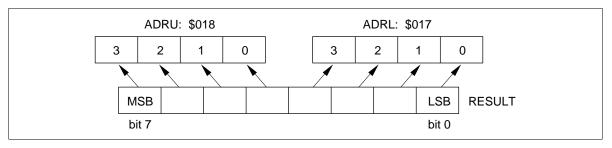

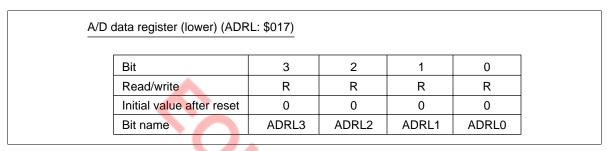

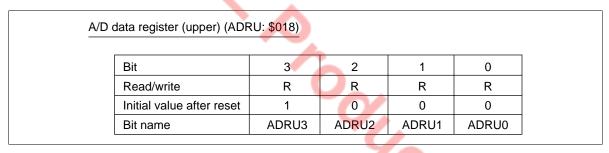

- The A/D data register is a read-only register consisting of a lower 4 bits and upper 4 bits (ADRL: \$017, ADRU: \$018). This register is not cleared by a reset. Data reads during A/D conversion are not guaranteed. After A/D conversion ends, the resultant 8-bit data is set in this register and held until the start of the next conversion (figures 51 to 53).

OCHCX

Figure 45 A/D Converter Block Diagram

#### **Notes on Usage**

- Use the SEM or SEMD instruction for writing to the A/D start flag (ADSF)

- Do not write to the A/D start flag during A/D conversion

- Data in the A/D data register during A/D conversion is undefined

- Since the operation of the A/D converter is based on the clock from the system oscillator, the A/D converter does not operate in stop, watch, or subactive mode. In addition, to save power while in these modes, all current flowing through the converter's resistance ladder is cut off.

- If the power supply for the A/D converter is to be different from V<sub>CC</sub>, connect a 0.1-μF bypass capacitor between the AV<sub>CC</sub> and AV<sub>SS</sub> pins. (However, this is not necessary when the AV<sub>CC</sub> pin is directly connected to the V<sub>CC</sub> pin.)

- The port data register (PDR) is initialized to 1 by an MCU reset. At this time, if pull-up MOS is selected as active by bit 3 of the miscellaneous register (MIS3), the port will be pulled up to V<sub>CC</sub>. When using a shared R port/analog input pin as an input pin, clear PDR to 0. Otherwise, if pull-up MOS is selected by MIS3 and PDR is set to 1, a pin selected by bit 1 of the A/D mode registr as an analog pin will remain pulled up.

Figure 46 A/D Mode Register 1 (AMR1)

Figure 47 A/D Mode Register 2 (AMR2)

Figure 48 A/D Channel Register (ACR)

Figure 49 A/D Start Flag (ADSF)

Figure 50 I<sub>AD</sub> Off Flag (IAOF)

Figure 51 A/D Data Register

Figure 52 A/D Data Register (Lower) (ADRL)

Figure 53 A/D Data Register (Upper) (ADRU)

#### **Notes on Mounting**

Assemble all parts including the HD404339 Series on a board, noting the points described below.

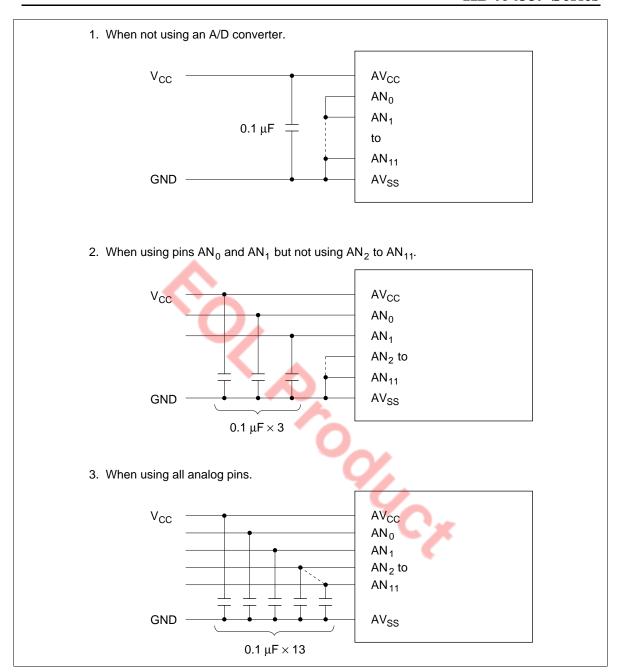

- 1. Connect layered ceramic type capacitors (about 0.1  $\mu$ F) between AV<sub>CC</sub> and AV<sub>SS</sub>, between V<sub>CC</sub> and GND, and between used analog pins and AV<sub>SS</sub>.

- 2. Connect unused analog pins to AV<sub>ss</sub>.

Figure 54 Example of Connections (AV $_{CC}$  to AV $_{SS}$ )

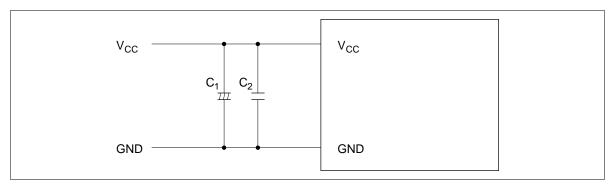

Between the  $V_{CC}$  and GND lines, connect capacitors designed for use in ordinary power supply circuits. An example connection is described in figure 54.

No resistors can be inserted in series in the power supply circuit, so the capacitors should be connected in parallel. The capacitors are a large capacitance  $C_1$  and a small capacitance  $C_2$ .

Figure 55 Example of Connections ( $V_{CC}$  to GND)

#### **Absolute Maximum Ratings**

| Item                             | Symbol             | Value                           | Unit | Notes  |

|----------------------------------|--------------------|---------------------------------|------|--------|

| Supply voltage                   | V <sub>cc</sub>    | -0.3 to +7.0                    | V    |        |

| Programming voltage              | V <sub>PP</sub>    | -0.3 to +14.0                   | V    | 1      |

| Pin voltage                      | V <sub>T</sub>     | $-0.3$ to $V_{cc} + 0.3$        | V    | 2      |

|                                  |                    | $V_{cc}$ – 45 to $V_{cc}$ + 0.3 | V    | 3      |

| Total permissible input current  | $\Sigma I_{\circ}$ | 70                              | mA   | 4      |

| Total permissible output current | -∑I <sub>o</sub>   | 150                             | mA   | 5      |

| Maximum input current            | Io                 | 4                               | mA   | 6, 7   |

|                                  |                    | 20                              | mA   | 6, 8   |

| Maximum output current           | -I <sub>0</sub>    | 4                               | mA   | 9, 10  |

|                                  |                    | 30                              | mA   | 10, 11 |

| Operating temperature            | T <sub>opr</sub>   | –20 to +75                      | °C   |        |

| Storage temperature              | T <sub>stg</sub>   | –55 to +125                     | °C   |        |

Notes: Permanent damage may occur if these absolute maximum ratings are exceeded. Normal operation must be under the conditions stated in the electrical characteristics tables. If these conditions are exceeded, the LSI may malfunction or its reliability may be affected.

- 1. Applies to pin TEST (V<sub>PP</sub>) of HD4074339.

- 2. Applies to all standard voltage pins.

- 3. Applies to high-voltage pins.

- 4. The total permissible input current is the total of input currents simultaneously flowing in from all the I/O pins to GND.

- 5. The total permissible output current is the total of output currents simultaneously flowing out from  $V_{cc}$  to all I/O pins.

- 6. The maximum input current is the maximum current flowing from each I/O pin to GND.

- 7. Applies to ports R3, R4, and R5.

- 8. Applies to ports R0, R6, and R7.

- 9. Applies to ports R0 and R3 to R7.

- 10. The maximum output current is the maximum current flowing from  $V_{cc}$  to each I/O pin.

- 11. Applies to ports  $D_0-D_{13}$ , R1, R2, R8, and R9.

#### **Electrical Characteristics**

DC Characteristics ( $V_{CC}$  = 4.0 to 5.5 V, GND = 0 V,  $V_{disp}$  =  $V_{CC}$  – 40 V to  $V_{CC}$ ,  $T_a$  = –20 to +75°C, unless otherwise specified)

| Item                                  | Symbol            | Pins                                                     | Min                   | Тур | Max                   | Unit | <b>Test Condition</b>                             | Notes |

|---------------------------------------|-------------------|----------------------------------------------------------|-----------------------|-----|-----------------------|------|---------------------------------------------------|-------|

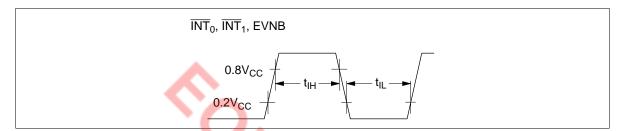

| Input high voltage                    | V <sub>IH</sub>   | RESET, SCK,<br>SI, INT <sub>0</sub> , INT <sub>1</sub> , | 0.8V <sub>cc</sub>    | _   | V <sub>CC</sub> + 0.3 | V    |                                                   |       |

|                                       |                   | $\overline{\text{STOPC}}$ , EVNB                         |                       |     |                       |      |                                                   |       |

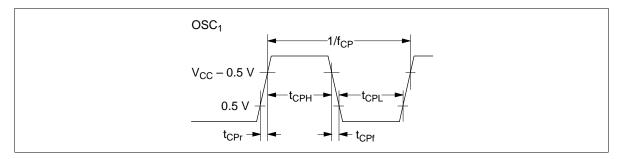

|                                       |                   | OSC <sub>1</sub>                                         | V <sub>cc</sub> - 0.5 | _   | V <sub>cc</sub> + 0.3 | V    |                                                   |       |

| Input low voltage                     | $V_{IL}$          | RESET, SCK,<br>SI                                        | -0.3                  | _   | 0.2V <sub>cc</sub>    | V    |                                                   |       |

|                                       |                   | INT <sub>0</sub> , INT <sub>1</sub> ,<br>STOPC, EVNB     | V <sub>cc</sub> - 40  | _   | 0.2V <sub>cc</sub>    | V    |                                                   |       |

|                                       | 4                 | OSC <sub>1</sub>                                         | -0.3                  | _   | 0.5                   | V    |                                                   |       |

| Output high voltage                   | V <sub>OH</sub>   | SCK, SO, TOC                                             | V <sub>cc</sub> - 0.5 |     | _                     | V    | $-I_{OH} = 0.5 \text{ mA}$                        |       |

| Output low voltage                    | V <sub>OL</sub>   | SCK, SO, TOC                                             | _                     | _   | 0.4                   | V    | I <sub>OL</sub> = 0.4 mA                          |       |

| I/O leakage<br>current                | I <sub>IL</sub>   | RESET, SCK,<br>SI, SO,TOC,<br>OSC,                       | <b>⊘</b>              | _   | 1                     | μА   | $V_{in} = 0 \text{ V to } V_{CC}$                 | 1     |

|                                       |                   | INT <sub>0</sub> , INT <sub>1</sub> ,<br>STOPC, EVNB     | _                     |     | 20                    | μΑ   | $V_{in} = V_{CC} - 40 \text{ to}$ $V_{CC}$        | 1     |

| Current dissipation in active mode    | I <sub>cc</sub>   | V <sub>cc</sub>                                          | _                     | 7   | 5.0                   | mA   | $V_{CC} = 5 \text{ V},$ $f_{OSC} = 4 \text{ MHz}$ | 2, 5  |

|                                       |                   |                                                          | _                     | _   | 8.0                   | mA   | -                                                 | 2, 6  |

| Current dissipation in standby mode   | I <sub>SBY</sub>  | V <sub>cc</sub>                                          | _                     | _   | 2.0                   | mA   | $V_{cc} = 5 \text{ V},$ $f_{osc} = 4 \text{ MHz}$ | 3     |

| Current dissipation in subactive mode | I <sub>SUB</sub>  | V <sub>cc</sub>                                          | _                     | _   | 100                   | μΑ   | $V_{cc} = 5 \text{ V},$ 32 kHz oscillator         | 4, 5  |

|                                       |                   |                                                          | _                     | _   | 320                   | μΑ   | -                                                 | 4, 6  |

| Current dissipation in watch mode     | I <sub>WTC</sub>  | V <sub>cc</sub>                                          | _                     | _   | 20                    | μА   | $V_{cc} = 5 \text{ V},$ 32 kHz oscillator         | 4     |

| Current dissipation in stop mode      | I <sub>STOP</sub> | V <sub>cc</sub>                                          | _                     | _   | 10                    | μА   | X1 = GND,<br>X2 = Open                            | 4, 5  |

|                                       |                   |                                                          | _                     | _   | 20                    | μΑ   | -                                                 | 4, 6  |

| Stop mode retaining voltage           | $V_{STOP}$        | V <sub>cc</sub>                                          | 2                     | _   |                       | V    |                                                   |       |

Notes: 1. Excludes current flowing through pull-up MOS and output buffers.

2.  $I_{cc}$  is the source current when no I/O current is flowing while the MCU is in reset state.

Test conditions: MCU: Reset

Pins: RESET, TEST at GND

R0, R3 $_{\scriptscriptstyle 0}$  to R7 $_{\scriptscriptstyle 2}$  at V  $_{\scriptscriptstyle CC}$

$D_0$ – $D_{13}$ , R1, R2, R8, R9, RA<sub>1</sub> at  $V_{disp}$

3. I<sub>SBY</sub> is the source current when no I/O current is flowing while the MCU timer is operating.

Test conditions: MCU: I/O reset

Standby mode

Pins:  $\overline{\text{RESET}}$  at  $V_{\text{cc}}$

TEST at GND

R0, R3 $_{\scriptscriptstyle 0}$  to R7 $_{\scriptscriptstyle 2}$  at V $_{\scriptscriptstyle CC}$

$D_0$ - $D_{13}$ , R1, R2, R8, R9, RA<sub>1</sub> at  $V_{disp}$

4. This is the source current when no I/O current is flowing.

Test conditions: Pins: R0, R3<sub>0</sub> to R7<sub>2</sub> at V<sub>cc</sub>

D<sub>0</sub>-D<sub>13</sub>, R1, R2, R8, R9, RA<sub>1</sub> at GND

- 5. Applies to the HD404334, HD404336, HD404338, HD4043312, and HD404339.

- 6. Applies to the HD4074339.

I/O Characteristics for High-Voltage Pins ( $V_{CC}$  = 4.0 to 5.5 V, GND = 0 V,  $V_{disp}$  =  $V_{CC}$  – 40 V to  $V_{CC}$ ,  $T_a$  = –20 to +75°C, unless otherwise specified)

| Item               | Symbol          | Pins                                  | Min                   | Тур | Max                   | Unit | Test Condition                              | Note |

|--------------------|-----------------|---------------------------------------|-----------------------|-----|-----------------------|------|---------------------------------------------|------|

| Input high voltage | V <sub>IH</sub> | D <sub>0</sub> -D <sub>13</sub> , R1, | 0.7V <sub>cc</sub>    | _   | V <sub>CC</sub> + 0.3 | V    |                                             |      |

|                    |                 | R2, R8, R9,                           |                       |     |                       |      |                                             |      |

|                    |                 | $RA_1$                                |                       |     |                       |      |                                             |      |

| Input low voltage  | V <sub>IL</sub> | D <sub>0</sub> -D <sub>13</sub> , R1, | V <sub>cc</sub> - 40  | _   | 0.3V <sub>cc</sub>    | V    |                                             |      |

|                    |                 | R2, R8, R9,                           |                       |     |                       |      |                                             |      |

|                    |                 | $RA_1$                                |                       |     |                       |      |                                             |      |

| Output high        | V <sub>OH</sub> | D <sub>0</sub> -D <sub>13</sub> , R1, | V <sub>cc</sub> - 3.0 | _   | _                     | V    | -I <sub>OH</sub> = 15 mA                    |      |

| voltage            |                 | R2, R8, R9,                           |                       |     |                       |      |                                             |      |

|                    |                 | BUZZ                                  |                       |     |                       |      |                                             |      |

|                    |                 |                                       | V <sub>CC</sub> - 2.0 | _   | _                     | V    | -I <sub>OH</sub> = 10 mA                    |      |

|                    |                 |                                       | V <sub>CC</sub> - 1.0 | _   | _                     | V    | $-I_{OH} = 4 \text{ mA}$                    |      |