September 2014

# FSA9591 — USB Accessory Detection Switch with Integrated **Linear Battery Charger**

#### **Features**

- Detection:

- **USB Data Cable**

- **UART Serial Link**

- Charger Detection (CDP, DCP)

- Factory-Mode Cables

- Teletype (TTY) Converter

- Linear Charger with up to 950 mA Charging Current Full-Speed and High-Speed 2.0 Compliant

- Automatic Switching with Available Interrupt

- **UART: RxD & TxD**

- USB: FS and HS 2.0 Compliant

- Switch Type: USB, UART

## Description

The FSA9591 is a USB accessory detection switch with an integrated lithium ion (Li+) linear battery charger. The FSA9591 is capable of detecting factory test modes, car kit type 1 and travel adapter charger, USB data port, and USB chargers. Compliant with the USB battery charging rev. 1.1 specification, the FSA9591 can detect USB Standard Downstream Ports (SDP), Dedicated Charging Ports (DCP), and Charging Downstream Ports (CDP).

The integrated linear charger uses constant current, constant voltage, and thermal control loops to charge Li+ batteries and provide protection. The FSA9591 also includes two programmable LDOs, capable of supplying 300mA each, for powering other devices in mobile phones. Battery presence detection via DETBAT\_N and charging current sensing through VICHG are also provided. V<sub>BUS IN</sub> pin can tolerate up to 28 V.

## **Applications**

- Cell Phones, Smart Phones, PDAs

- Tablets, Portable Media Players

- Gaming Devices, Digital Cameras

## **Ordering Information**

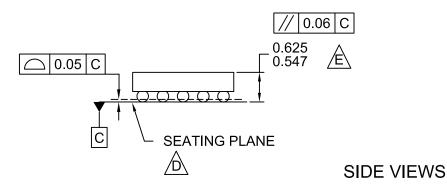

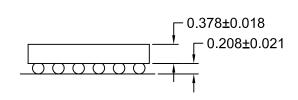

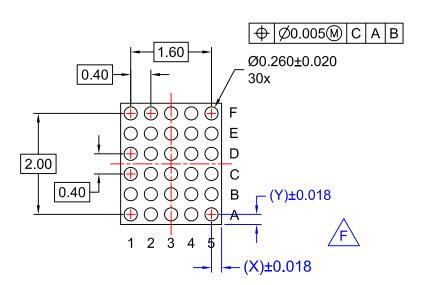

| Part Number    | Operating<br>Temperature Range | Top<br>Mark | Package                                                    |

|----------------|--------------------------------|-------------|------------------------------------------------------------|

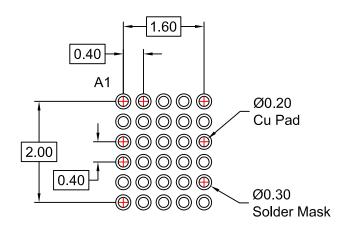

| FSA9591UCX (1) | -40 to +85°C                   | NT          | 30-Lead WLCSP (2.38 mm x 1.98 mm x 0.625 mm, 0.4 mm Pitch) |

1. Includes backside lamination.

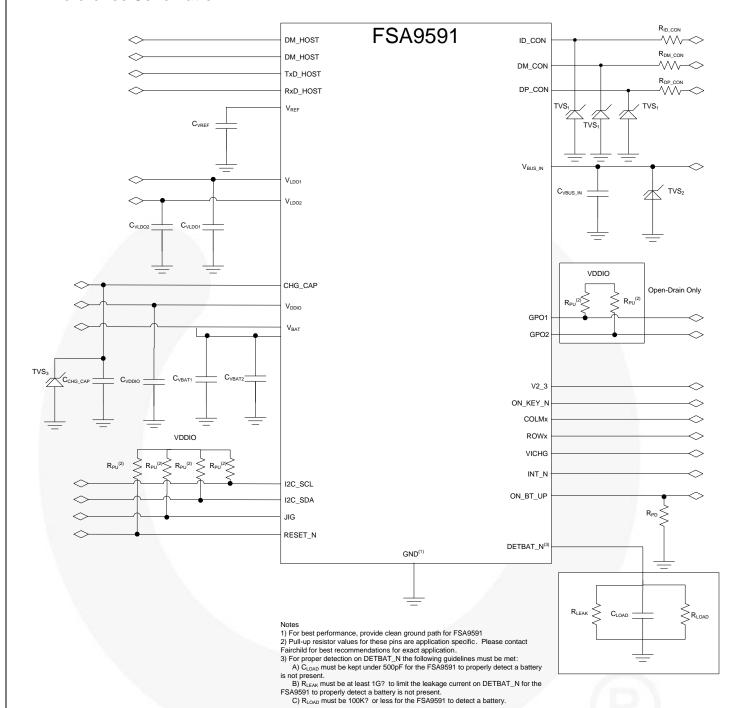

# **Typical Application** USB Data **USB CHARGING FACTORY TEST** OVT PROTECTION 5-PIN 2 obc 3 def MICRO-USB PORT 4 ghi 5 jkl 6 mno 7 pqrs 8 tuv 9 wxyz \*+ 0 - #1 FSA9591 Figure 1. Mobile Phone Example

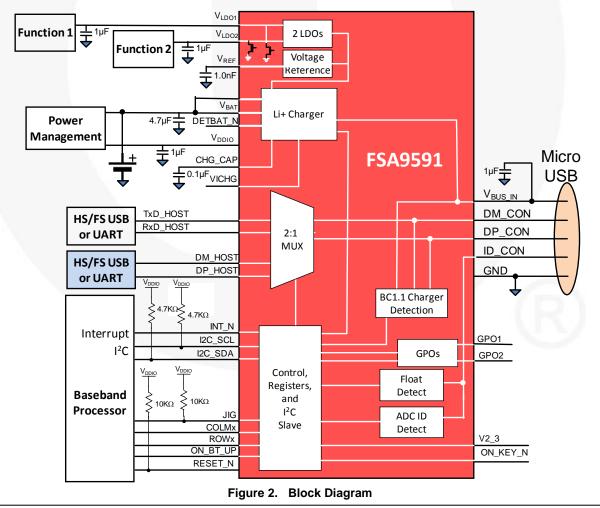

## **Block Diagram**

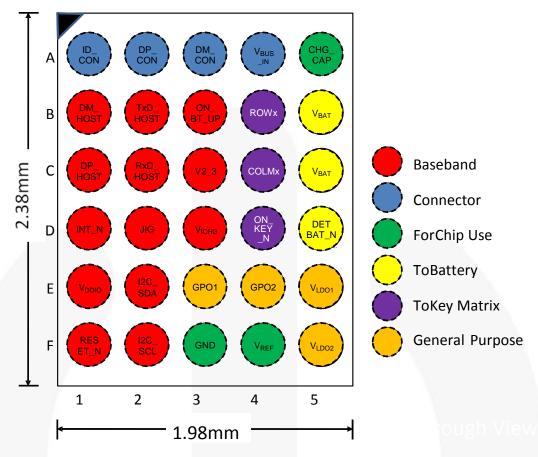

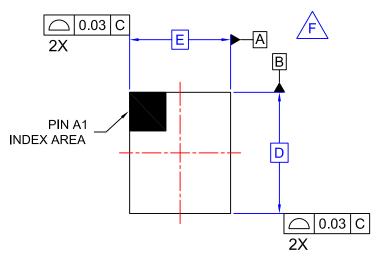

## **Pin Configuration**

Figure 3. Pin Assignment (Top Through View)

## **Pin Descriptions**

| Name                | Ball    | Туре        | Default<br>State   | Description                                                                                                                  |  |  |  |

|---------------------|---------|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| USB Interfa         | се      |             |                    |                                                                                                                              |  |  |  |

| DP_HOST             | C1      | Signal Path | Open               | D+ signal switch path; dedicated USB port to be connected to the USB transceiver on the phone                                |  |  |  |

| DM_HOST             | B1      | Signal Path | Open               | D- signal switch path; dedicated USB port to be connected to the USB transceiver on the phone                                |  |  |  |

| <b>UART Interf</b>  | асе     |             |                    |                                                                                                                              |  |  |  |

| TxD_HOST            | B2      | Signal Path | Open               | Transmitter (Tx) switch path from UART on the phone to the D- pin of the USB connector                                       |  |  |  |

| RxD_HOST            | C2      | Signal Path | Open               | Receiver (Rx) switch path from UART on the phone to the D+ pin of the USB connector                                          |  |  |  |

| Connector I         | nterfac | 9           |                    |                                                                                                                              |  |  |  |

| GND                 | F3      | Ground      | N/A                | Ground                                                                                                                       |  |  |  |

| ID_CON              | A1      | Signal Path | Pull-Up<br>Current | Connected to the USB connector ID pin and used for detecting accessories                                                     |  |  |  |

| DP_CON              | A2      | Signal Path | Open               | Connected to the USB connector D+ pin; depending on the signaling mode, this pin can be switched to DP_HOST or RxD_HOST pins |  |  |  |

| DM_CON              | А3      | Signal Path | Open               | Connected to the USB connector D- pin; depending on the signaling mode, this can switched to DM_HOST or TxD_HOST pins        |  |  |  |

| V <sub>BUS_IN</sub> | A4      | Power Path  | N/A                | Input voltage supply pin to be connected to the VBUS pin of the USB connector                                                |  |  |  |

| Name              | Ball  | Туре                                      | Default<br>State |                                                                                                                             |                                        | Description                                                                     | on          |                  |                       |  |

|-------------------|-------|-------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|-------------|------------------|-----------------------|--|

| Power Inter       | face  |                                           |                  |                                                                                                                             |                                        |                                                                                 |             |                  |                       |  |

| $V_{\text{DDIO}}$ | E1    | Power                                     | N/A              | Factory and I <sup>2</sup> C interface I/O supply pin                                                                       |                                        |                                                                                 |             |                  |                       |  |

| $V_{BAT}$         | B5,C5 | Power Path                                | N/A              | Battery charger output and chip supply pin to be connected to mobile phone battery                                          |                                        |                                                                                 |             |                  |                       |  |

| V <sub>LDO1</sub> | E5    | Power                                     | Hi-Z             | Programma                                                                                                                   | ole first LDO regu                     | ulator output                                                                   |             |                  |                       |  |

| $V_{LDO2}$        | F5    | Power                                     | Hi-Z             | Programma                                                                                                                   | ole second LDO                         | regulator output                                                                |             |                  |                       |  |

| $V_{REF}$         | F4    | Power                                     | Hi-Z             |                                                                                                                             |                                        | iternal use. Can o<br>r LDO operation.                                          | output a ma | aximum of 1 m    | A external            |  |

| CHG_CAP           | A5    | Power                                     | Hi-Z             |                                                                                                                             | acitor for charger<br>µF typical value | that forms a low-                                                               | voltage po  | wer supply for   | rinternal             |  |

| $V_{ICHG}$        | D3    | Power                                     | Hi-Z             | Analog sign                                                                                                                 | al proportional to                     | the charging curr                                                               | ent flowing | g to battery fro | m V <sub>BUS_IN</sub> |  |

| Other Interf      | ace   |                                           |                  |                                                                                                                             |                                        |                                                                                 |             |                  |                       |  |

| JIG               | D2    | Open-Drain<br>Output (V <sub>DDIO</sub> ) | Hi-Z             | Output control signal driven by the FSA9591 and used by the processor for factory test modes (active LOW open drain output) |                                        |                                                                                 |             |                  |                       |  |

| ON_KEY_N          | D4    | Input<br>(Comparator)                     | N/A              | Input that in                                                                                                               | dicates whether t                      | he phone ON key                                                                 | / has been  | pressed (activ   | ve LOW)               |  |

|                   |       |                                           |                  | Switch connected to the V2_3 pin to boot up the processor during factory mode when the ON_KEY_N signal is asserted          |                                        |                                                                                 |             |                  |                       |  |

|                   |       |                                           |                  |                                                                                                                             | VBUS                                   | ON_KEY_N                                                                        | JIG         | ON_BT_UP =       |                       |  |

| ON DT LID         | Do    | Outtak and Dark                           | Hi-Z             |                                                                                                                             | Valid VBUS                             | Х                                                                               | Х           | V2_3             |                       |  |

| ON_BT_UP          | В3    | Switched Path                             | ΠI-Z             |                                                                                                                             | LOW                                    | LOW                                                                             | Х           | V2_3             |                       |  |

|                   |       |                                           |                  |                                                                                                                             | LOW                                    | HIGH                                                                            | LOW         | V2_3             |                       |  |

|                   |       |                                           |                  |                                                                                                                             | LOW                                    | HIGH                                                                            | Hi-Z        | VZ_3<br>Hi-Z     |                       |  |

|                   |       |                                           |                  |                                                                                                                             |                                        |                                                                                 |             |                  |                       |  |

| V2_3              | С3    | Switched Path                             | Hi-Z             | Pin switched description)                                                                                                   | to ON_BT_UP f                          | for realizing ON_E                                                              | 3T_UP fun   | ctionality (see  | ON_BT_UP              |  |

|                   |       |                                           |                  |                                                                                                                             |                                        | v signal from a hig<br>or key matrix circu                                      |             |                  |                       |  |

|                   |       |                                           |                  |                                                                                                                             | V <sub>BAT</sub>                       | ON_KEY_N                                                                        | N COL       | Mx/ROWx          |                       |  |

| COLMx             | C4    | Switched Path                             | Hi-Z             |                                                                                                                             | LOW                                    | Х                                                                               |             | OPEN             |                       |  |

|                   |       |                                           |                  |                                                                                                                             | <b>V</b> ALID                          | HIGH                                                                            | ı           | OPEN             |                       |  |

|                   |       |                                           |                  |                                                                                                                             | <b>V</b> ALID                          | LOW                                                                             | 5           | SHORT            |                       |  |

|                   | ς     |                                           |                  |                                                                                                                             |                                        | nal from a high-vonatrix circuitry. Sv                                          |             |                  | oltage closed         |  |

|                   |       |                                           |                  |                                                                                                                             | V <sub>BAT</sub>                       | ON_KEY_N                                                                        | N COL       | Mx/ROWx          |                       |  |

| ROWx              | B4    | Switched Path                             | Hi-Z             |                                                                                                                             | LOW                                    | Х                                                                               |             | OPEN             |                       |  |

|                   |       |                                           |                  |                                                                                                                             | <b>V</b> ALID                          | HIGH                                                                            |             | OPEN             |                       |  |

|                   |       |                                           |                  |                                                                                                                             | <b>V</b> ALID                          | LOW                                                                             | 5           | SHORT            |                       |  |

| RESET_N           | F1    | Open-Drain<br>Output (V <sub>DDIO</sub> ) | N/A              |                                                                                                                             |                                        | ocessor with dete<br>alling edge and th                                         |             |                  |                       |  |

| GPO1              | E3    | Output (V <sub>DDIO</sub> )               | N/A              |                                                                                                                             |                                        | programmed from                                                                 |             |                  | 1]. This can          |  |

| GPO2              | E4    | Output (V <sub>DDIO</sub> )               | N/A              |                                                                                                                             |                                        | tput programmed in based on the re                                              |             |                  |                       |  |

| DETBAT_N          | D5    | Input<br>(Comparator)                     | N/A              | DETBAT_N:<br>DETBAT_N:                                                                                                      | HIGH when bat                          | nine the battery p<br>tery is not presen<br>ery is present or v<br>y pulled up. | t.          | •                | , regardless          |  |

| Name                       | Ball | Type Default<br>State                  |      | Description                                                                                                                                                                                |

|----------------------------|------|----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C Interface | Э    |                                        |      |                                                                                                                                                                                            |

| I2C_SCL                    | F2   | Input (V <sub>DDIO</sub> )             | N/A  | I <sup>2</sup> C serial clock signal to be connected to the phone-based I <sup>2</sup> C master                                                                                            |

| I2C_SDA                    | E2   | Open-Drain I/O<br>(V <sub>DDIO</sub> ) | Hi-Z | I <sup>2</sup> C serial data signal to be connected to the phone-based I <sup>2</sup> C master                                                                                             |

| INT_N                      | D1   | CMOS Output<br>(V <sub>DDIO</sub> )    | Low  | Interrupt active LOW output used to prompt the phone baseband processor to read the I <sup>2</sup> C register bits or indicate a change in ID_CON pin status or accessories' attach status |

## 1. Functionality

The FSA9591 is USB port accessory detector and switch with integrated 28 V over-voltage tolerance. Fully controlled using  $I^2C$ , FSA9591 enables high-speed USB 2.0 Standard Downstream Port (SDP), USB Charging Downstream Port (CDP) battery charger, USB Dedicated Charging Port (DCP) charger data cables to use a common connector micro or mini USB 2.0 port. Factory-mode cables can be detected and switched to use either the UART or USB data path. The FSA9591 can be programmed for manual switching or automatic switching of data paths.

#### 1.1. Functional Overview

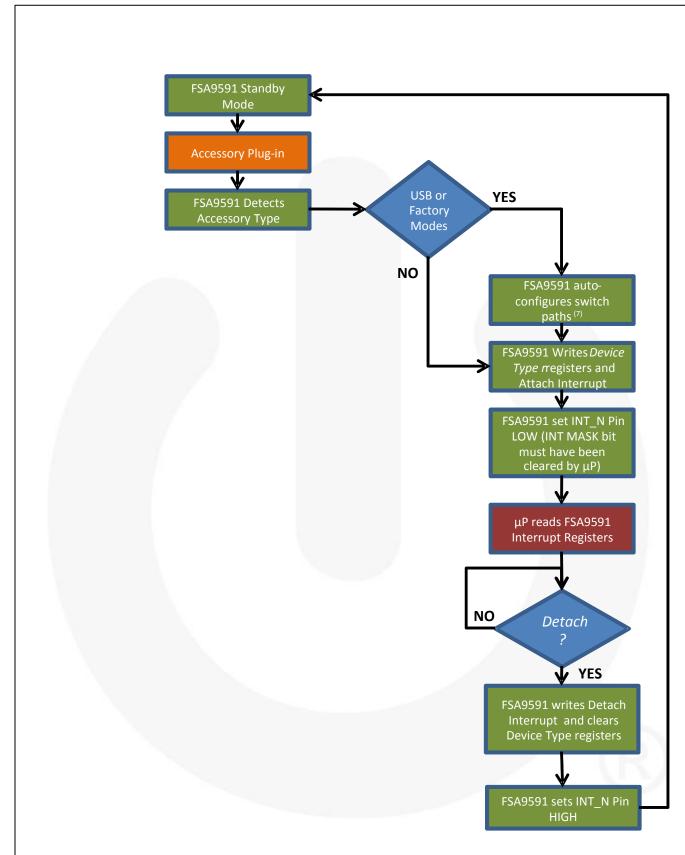

The FSA9591 is designed for minimal software requirements for proper operation. The flow diagram in Figure 4 walks through the fundamental steps of operation and contains references to more detailed information.

| Flow Diagram                                                                                          | State                      | Datasheet<br>Section | Description                                                                                                    |

|-------------------------------------------------------------------------------------------------------|----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|

| Power-up &                                                                                            | Power-Up & Reset           | Section 2            | Applies power to the device and resets state of the device                                                     |

| Reset                                                                                                 | I <sup>2</sup> C           | Section 3            | Communication with device through I <sup>2</sup> C                                                             |

| I <sup>2</sup> C                                                                                      | Configuration              | Section 4            | Configures the device using I <sup>2</sup> C and the interna registers (which can be bypassed during power up) |

| Configuration                                                                                         | Detection                  | Section 5            | Manages accessory detection, including attachment and detachment                                               |

| Accessory                                                                                             | Processor<br>Communication | Section 1            | How the detection of the accessory is indicated the processor                                                  |

| Plug-in  Detection  Processor Communication  Switch Configuration  Active Signals  Accessory Detached | Switch Configuration       | Section 7            | Configuration of switches based on detection                                                                   |

| igure 4. Basic Operation Flow                                                                         | Active Signal              | Section 11           | Signal performance of selected configuration                                                                   |

## 2. Power-Up & Reset

The FSA9591 does not need special power sequencing for correct operation. The main power for accessory detection is provided by  $V_{\text{BAT}}$  only.  $V_{\text{DDIO}}$  is only used for  $I^2C$  interface and interrupt processing. The linear charger power is provided by  $V_{\text{BUS\_IN}}$ .

Table 1 summarizes the enabled features of each power state. The valid voltages levels for each power supply can be found in Section 12.2

**Table 1. Power States Summary**

|                              |                           |                  |                            | Enabled Functionality                                         |                         |          |     |  |  |  |

|------------------------------|---------------------------|------------------|----------------------------|---------------------------------------------------------------|-------------------------|----------|-----|--|--|--|

| Valid<br>V <sub>BUS_IN</sub> | Valid<br>V <sub>BAT</sub> | (0)              | Power State                | Processor<br>Communication<br>(I <sup>2</sup> C & Interrupts) | Detection/<br>Switching | Charging | LDO |  |  |  |

| N                            | N                         | N                | Power Down                 |                                                               | NO                      |          |     |  |  |  |

| N                            | N                         | Y <sup>(3)</sup> | Not Typical                | Illegal State                                                 |                         |          |     |  |  |  |

| N                            | Υ                         | N                | Detection/Switching Active | NO                                                            | YES                     | NO       | YES |  |  |  |

| N                            | Υ                         | Υ                | Detection/Switching Active | YES                                                           | YES                     | NO       | YES |  |  |  |

| Y                            | N                         | N                | Charging Only              | NO                                                            | NO                      | YES      | NO  |  |  |  |

| Y                            | N                         | Y <sup>(3)</sup> | Not Typical                | NO                                                            | NO                      | YES      | NO  |  |  |  |

| Y                            | Υ                         | N                | Powered On State           | NO                                                            | YES                     | YES      | YES |  |  |  |

| Y                            | Υ                         | Υ                | Powered On State           | YES                                                           | YES                     | YES      | YES |  |  |  |

#### Notes:

- 2. V<sub>DDIO</sub> is expected to be the same supply used by the baseband I/Os.

- 3. Typically  $V_{DDIO}$  is only present when  $V_{BAT}$  is valid.

- 4. X=Don't care.

#### 2.1. Reset

When the device is reset, all the registers are initialized to the default values shown in Section 12.14 and all switch paths are open. After reset or power up, FSA9591 enters Standby Mode and is ready to detect accessories sensed on the  $V_{\text{BUS\_IN}}$  or ID\_CON pins.

#### 2.1.1. Hardware Reset

Power-On Reset (POR) is caused by the initial rising edge of  $V_{\text{BAT}}$  or  $V_{\text{BUS\_IN.}}$

#### 2.1.2. Software Reset

The device can be reset through software by writing to the Reset bit in the Register (1BH).

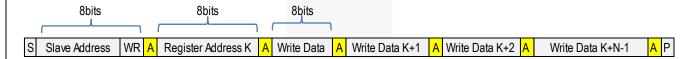

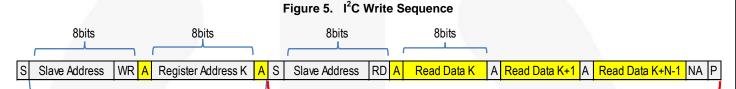

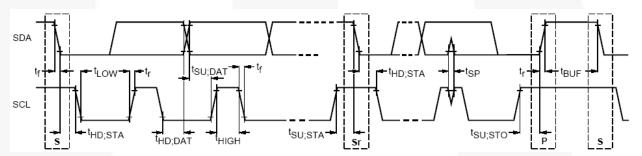

## 3. I<sup>2</sup>C

The FSA9591 integrates a full fast-mode  $I^2C$  slave controller compliant with the  $I^2C$  specification version 2.1. The FSA9591  $I^2C$  interface runs up to 400 kHz.

The slave address is shown in Table 2. Status information and configuration occurs via the I<sup>2</sup>C interface. *Please see Section* 12.12 for more information.

Table 2. I<sup>2</sup>C Slave Address

| Name          | Size (Bits) | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0        |

|---------------|-------------|-------|-------|-------|-------|-------|-------|-------|--------------|

| Slave Address | 8           | 0     | 1     | 0     | 0     | 1     | 0     | 1     | Read / Write |

Note: A single-byte write is initiated by the master with P immediately following first data byte.

Single- or multi-byte read executed from current register location (single-byte read initiated by Register address to read specified master with NA immediately following first data byte).

Note: If no register specified, master reads from the current register. In this case, only sequence in red bracket is needed.

Figure 6. I<sup>2</sup>C Read Sequence

## Legend

|   | From Master to Slave | S | Start Condition       | NA | NOT Acknowledge (SDA HIGH) | RD | Read=1         |

|---|----------------------|---|-----------------------|----|----------------------------|----|----------------|

| ĺ | From Slave to Master | Α | Acknowledge (SDA LOW) | WR | Write=0                    | Р  | Stop Condition |

## 4. Configuration

FSA9591 requires minimal configuration for proper detection, charging and reporting. Follow these steps for full configuration:

- Write Control register (02h) to configure manual or automatic switching modes.

- If using manual switching modes, write Manual SW 1 register (13h) to configure switches.

- Write Control register (02h) to clear INT Mask bit. This enables interrupts to the baseband.

The linear charger defaults to automatic charging at either 90mA or 450mA based on the accessory that was detected.

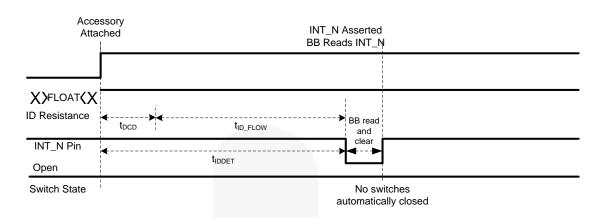

#### 5. Detection

The FSA9591 monitors both V<sub>BUS\_IN</sub> and ID\_CON to detect accessories. The ID\_CON detection is a "resistive detection" that reads the resistance to GND on the ID\_CON pin to determine the accessory attached. Table 3 shows assignment of accessories based on resistor values. FSA9591 can also detect accessories

with ID resistances outside the specified ranges; these are detected in the same manner as the defined accessories. FSA9591 interrupts the baseband processor and provides the correct ADC value, as shown in Table 3.

Table 3. ID\_CON Accessory Detection

|    | ADC Code |         |         | ı   | Equivalent R <sub>ID</sub> | (6)                   | Description                 |                                               |  |

|----|----------|---------|---------|-----|----------------------------|-----------------------|-----------------------------|-----------------------------------------------|--|

| 4  | 3        | 2       | 1       | 0   | Min.                       | Target                | Max.                        | Description                                   |  |

| 1  | 0        | 1       | 0       | 1   | 117.4 kΩ                   | 121 kΩ                | 124.6 kΩ                    | Unknown Accessory                             |  |

| 1  | 0        | 1       | 1       | 0   | 145.5 kΩ                   | 150 kΩ                | 154.5 kΩ                    | Unknown Accessory                             |  |

| 1  | 0        | 1       | 1       | 1   | 176.4 kΩ                   | 200 kΩ <sup>(5)</sup> | 206.0 kΩ                    | Travel Adapter (TA) or Car Kit Type 1 Charger |  |

| 1  | 1        | 0       | 0       | 0   | 247.3 kΩ                   | 255 kΩ                | 262.7 kΩ                    | Factory Mode Boot OFF-USB                     |  |

| 1  | 1        | 0       | 0       | 1   | 291.9 kΩ                   | 301 kΩ                | 310.1 kΩ                    | Factory Mode Boot ON-USB                      |  |

| 1  | 1        | 0       | 1       | 0   | 354.0 kΩ                   | 365 kΩ                | 375.9 kΩ                    | Unknown Accessory                             |  |

| 1  | 1        | 0       | 1       | 1   | 428.7 kΩ                   | 442 k $\Omega^{(5)}$  | 455.3 kΩ                    | Unknown Accessory                             |  |

| 1  | 1        | 1       | 0       | 0   | 507.3 kΩ                   | 523 kΩ                | 538.7 kΩ                    | Factory Mode Boot OFF-UART                    |  |

| 1  | 1        | 1       | 0       | 1   | 600.4 kΩ                   | 619 kΩ                | 637.6 kΩ                    | Factory Mode Boot ON-UART                     |  |

| 1  | 1        | 1       | 1       | 0   | 750.0 kΩ                   | 1000 kΩ               | 1030.0 kΩ Unknown Accessory |                                               |  |

| No | t 'h1F c | r any c | ode abo | ove | 3 ΜΩ                       | None of the a         | above ranges                | Unknown Accessory                             |  |

#### Note:

- 5. These accessories need  $V_{\text{BUS}}$  to be valid to be detected since they are charger accessories.

- 6. For resistances between the defined regions, the FSA9591 detects the ADC value above OR below the given resistance.

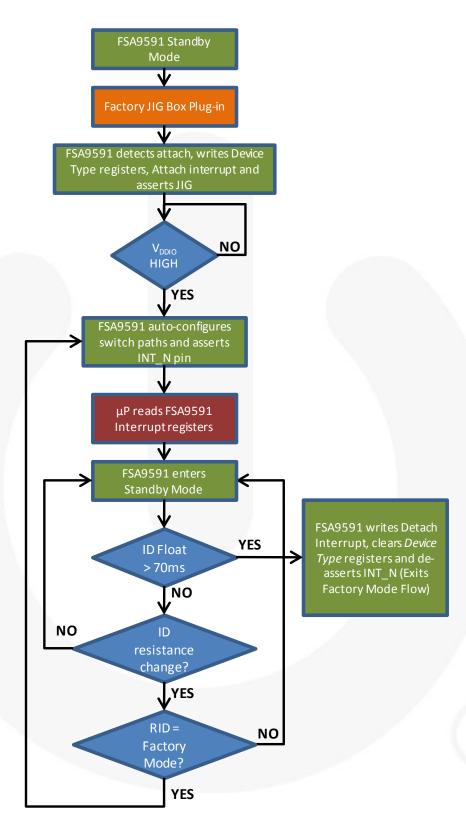

Factory modes are initiated with the attachment of special test hardware, called a "JIG box," for factory testing. The FSA9591 automatically configures switch paths to any of the factory-mode accessories when the appropriate resistor is sensed on the ID\_CON pin. A change of resistor on the ID\_CON pin dynamically switches between factory modes and autoconfigures the appropriate switch paths without detaching and attaching the cable.

The different factory mode accessories with the associated resistor values (1% standard resistors) on the ID\_CON pin and The switch paths for factory modes are listed in Table 4. The FSA9591 allows HS USB, FS USB, and UART signals to be passed on both ports with equal performance. This allows greater flexibility when designing with the FSA9591.

Table 4. ID CON Factory Cable Detection

| Configuration Typ       | DP_CON DM_CON |          | ID_CON   |        |        |        |

|-------------------------|---------------|----------|----------|--------|--------|--------|

| Factory Mode Jig: UART  | Boot_On       | DP_HOST1 | DM_HOST1 | 600 kΩ | 619 kΩ | 637 kΩ |

| Factory Mode Sig. OAR I | Boot_Off      | DP_HOST1 | DM_HOST1 | 507 kΩ | 523 kΩ | 538 kΩ |

| Factory Mode lightISP   | Boot_On       | DP_Host  | DM_Host  | 292 kΩ | 301 kΩ | 310 kΩ |

| Factory Mode Jig: USB   | Boot_Off      | DP_Host  | DM_Host  | 247 kΩ | 255 kΩ | 262 kΩ |

The FSA9591 detection algorithms monitor both the  $V_{\text{BUS}}$  and ID pins of the USB interface. Based on the detection results, multiple registers are updated and the INTB pin is asserted to indicate to the baseband processor that an accessory was detected and to read the registers for the complete information. The detection algorithm allows the application to control the timing of the detection algorithm and the configuration of the internal switches. The flow diagram in Figure 8 shows the operation of the detection algorithm.

Figure 7. Factory Cable Detection

#### Note:

7. Factory modes require V<sub>DDIO</sub>=HIGH before configuring the switches. Refer to the factory mode flow diagram in Figure 8 for details.

Figure 8. Factory Cable Detection Flow Chart

#### 5.1. USB Port Detection

The types of USB 2.0 ports the FSA9591 can detect are summarized in Table 5.

Table 5. ID CON and VBUS Detection Table for USB Devices

| V                   | DD CON               | DM CON            | ID_CON   | Resistance | e to GND | Accessory Detected <sup>(8)</sup>                                                                   |

|---------------------|----------------------|-------------------|----------|------------|----------|-----------------------------------------------------------------------------------------------------|

| V <sub>BUS_IN</sub> | DP_CON               | DM_CON            | Min.     | Тур.       | Max.     | Accessory Detected                                                                                  |

| 5V                  | Not Checked          | Not Checked       | 174.6 kΩ | 200 kΩ     | 206 kΩ   | TA (Travel Adapter) Charger (180 k $\Omega$ ) and Car Kit Charger Type 1 only (200 k $\Omega$ ) (9) |

| 5V                  | Shorted to<br>DM_CON | Shorted to DP_CON | 3 ΜΩ     | Open       | Open     | USB Dedicated Charging Port, Travel Adapter or Dedicated Charger (DCP) <sup>(9)</sup>               |

| 5V                  | DP_HOST              | DM_HOST           | 3 ΜΩ     | Open       | Open     | USB Charging Downstream Port (CDP) <sup>(9)</sup>                                                   |

| 5V                  | DP_HOST              | DM_HOST           | 3 ΜΩ     | Open       | Open     | USB Standard Downstream Port (SDP) <sup>(9)</sup>                                                   |

#### Notes:

- 8. The accessory type is reported in the Device Type 1 (0Ah) register for each valid accessory detected.

- The FSA9591 follows the battery charging 1.1 specification, which uses DP\_CON and DM\_CON to determine the USB accessory attached. Refer to Battery Charging 1.1 specification for further details.

For SDP and CDP USB accessories, the following pin mapping is automatically configured:

- DP HOST=DP CON

- DM HOST=DM CON

For DCP charger, the DP\_HOST and DM\_HOST switches are open. For all USB accessories, V<sub>BUS\_IN</sub> has Over-Voltage Tolerance (OVT) up to 28 V.

#### 6. Processor Communication

Typical communication steps between the processor and the FSA9591 during accessory detection are:

- INTB is asserted LOW, indicating a change in accessory detection.

- Processor reads the Interrupt 1 (03h) register to determine if an attach or detach event was detected.

- Processor reads the Status registers to determine the exact accessory detected.

- a. Device Type 1 (09h): Indicates which USB, Car Kit CDP, or DCP accessory was detected.

- b. Device Type 2 (0Ah): Indicates which factory mode or unknown accessory was detected.

## 7. Switch Configuration

FSA9591 devices have two methods of configuring the internal switches: it can auto-configure the switches or the switches can be configured manually by the processor. Typical applications use Auto-Configuration Mode and do not require interaction with the baseband to configure the switches correctly.

#### 7.1. Manual Switching

Manual switching is enabled by writing the following registers:

Manual Switch (13h): Configures the switches for DM\_CON and DP\_CON in addition to manual control of the JIG output.

#### 8. GPOs

The FSA9591 has two general-purpose outputs (GPOs) that typically turn on the functionality powered by the LDOs. The default state for the GPOs is push-pull outputs with GPO1\_OD and GPO2\_OD set LOW. If open-drain outputs are required, GPO1\_OD and GPO2\_OD should be set HIGH.

#### 9. LDOs

The two Low Drop Out (LDO) regulators, which are powered from  $V_{BAT}$ , are programmable from 1.8 V to 3.6 V in increments of 100 mV. A 0.6 V reference on VREF must be enabled by writing the register bit GPO[REF\_EN] to turn it on. This reference needs to turn on at least 20ms prior to the LDOs turning on to allow time to stabilize the reference if 0.1 nF bypass capacitance is used.

## 10. ON\_KEY Keypad Functionality

The functionality of ON\_BT\_UP is described in Table 6.

Table 6. ON\_KEY\_N and ON\_BT\_UP Truth Table

| VBUS       | ON_KEY_N | JIG  | ON_BT_UP |

|------------|----------|------|----------|

| Valid VBUS | X        | X    | V2_3     |

| LOW        | LOW      | X    | V2_3     |

| LOW        | HIGH     | LOW  | V2_3     |

| LOW        | HIGH     | Hi-Z | Hi-Z     |

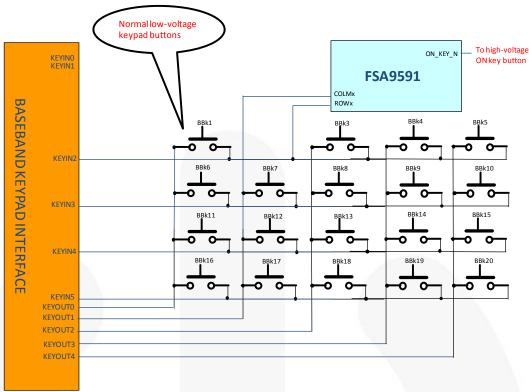

How to translate ON\_KEY\_N to a position in the row and column matrix of the processor keypad is shown in Figure 9.

Figure 9. On Key to COLMx and ROWx Mappings

This is the way the FSA9591 translates the ON\_KEY\_N pin, where the COLMx and ROWx create a virtual button that would have occupied the missing BBk2 switch in the matrix above. Internal to the FSA9591, there is an analog switch that connects COLMx to ROWx based on ON\_KEY\_N as outlined in Table 7. With ON\_KEY\_N pulled HIGH to  $V_{\text{BAT}}$ , a valid  $V_{\text{BAT}}$  must be present for the keypad functionality to work properly.

Table 7. COLMx/ROWx Truth Table

| V <sub>BAT</sub> | ON_KEY_N | COLMx/ROWx |

|------------------|----------|------------|

| LOW              | X        | OPEN       |

| VALID            | HIGH     | OPEN       |

| VALID            | LOW      | SHORT      |

#### 11. Linear Charger

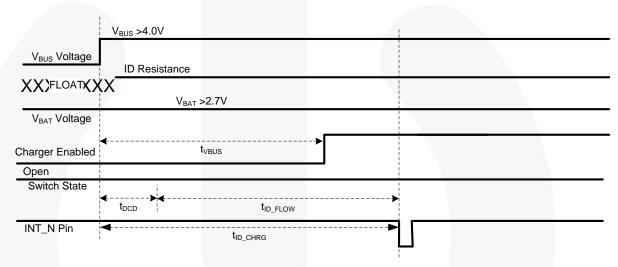

#### 11.1. Charging

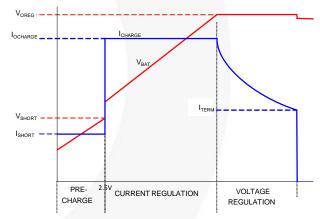

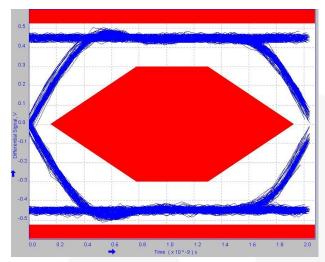

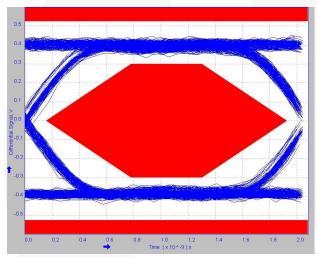

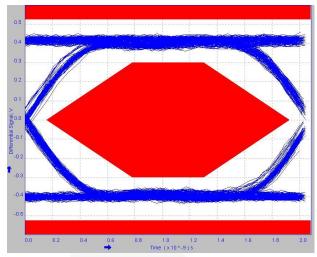

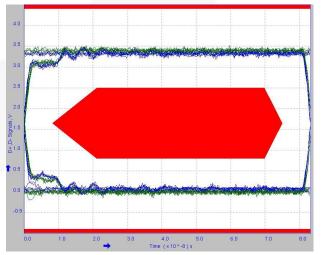

Figure 10 shows the different stages of the Li+ linear charger when a charger is connected to the USB pins and a battery is present and discharged below 2.5 V. Generally, the prequalification (called "PRE-CHARGE" in Figure 10) stage is when the battery voltage is below 2.5 V when an  $I_{\rm SHORT}$  current of 90 mA charges the battery to  $V_{\rm SHORT}$  voltage of 2.5 V. Then the Fast Charge stage starts if a battery charger is detected and the current is increased considerably to a programmable  $I_{\rm OCHARGE}$  level ("CURRENT REGULATION" in Figure 10). The battery voltage climbs quickly based on the drop caused by the current across the load elements of the battery. Then the voltage climbs linearly until the constant voltage stage is reached at the programmable voltage of  $V_{\rm OREG}$ . The current is monitored during this stage ("VOLTAGE REGULATION" in the figure) and, when it reaches the end of current  $I_{\rm TERM}$ , charging either halts or progresses to the top off charging if enabled.

Figure 10. Default Charging Profile

#### 11.1.1. Pre-Qualification Charging Stage

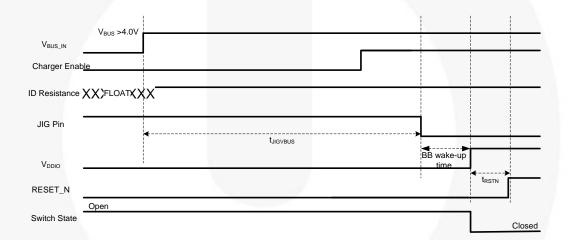

A typical battery has a protection circuit within the battery pack to disconnect the terminals below 2.7 V external to the FSA9591. If it gets below 2.7 V, the battery pack terminals are disconnected externally with the load switch within the battery pack, causing battery voltage  $V_{\text{BAT}}$  to decay quickly to ground since all that is holding  $V_{\text{BAT}}$  up is the decoupling capacitors externally. Another way that  $V_{\text{BAT}}$  can get so low is if  $V_{\text{BAT}}$  is shorted to ground accidentally. Both of these occurrences are very rare in a typical system since a dead battery is typically above 3 V and only goes below 3V over a long period of time via leakage.

When VBUS\_IN is first detected as being within its valid range, two timers are started, a 30-minute timer for the dead battery provision (if that is enabled) via the Charger Ctrl1[DBP\_EN] bit (enabled by default since the processor is usually not operating at this low battery voltage range) and a programmable timer for total charging elapsed time enabled (enabled by default as a 5-hour timer via the Charger Ctrl1 [TC\_EN] and Charger Ctrl1 [TC\_Time] bits).

The linear charger is expected to always take its power from VBUS\_IN while monitoring  $V_{BAT}$  to determine the optimal charging profile for the shortest charging cycle.

If VBUS\_IN is detected when  $V_{BAT}$  is below 2.5 V, a charging current of 90mA is used to trickle charge the battery. If it is not a short circuit,  $V_{BAT}$  should recover very quickly above 2.5 V since it is only charging decoupling capacitors.  $V_{DDIO}$  and  $V_{BAT}$  are below the operational voltage of the detection portion, so detection is not performed, nor does FSA9591 communicate over the  $I^2C$  lines as the linear charger charges the battery above the prequalification stage.

If there is a short circuit and the charger Ctrl1 [DBP\_EN] bit is enabled (default case), the timer continues up to 30 minutes and expires, shutting down the charger. This limits the short-circuit current of 90mA to be drawn only for 30 minutes. The only way to recover from this fault condition is to remove the short circuit. If the short circuit is not removed, detaching and re-attaching the charger restarts the dead battery provision timer for another 30 minutes before shutting off again.

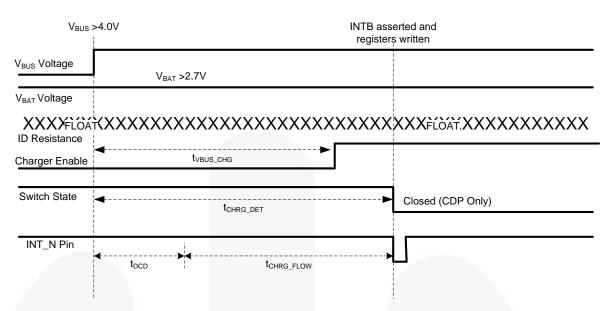

#### 11.1.2. Constant Current/Constant Voltage Charging Stage

In this stage,  $V_{BAT}$  is above the pre-qualification voltage of 2.5 V, but below the programmed Charger Ctrl5 [CV\_Voltage] value. The charger detection interrogates the DP\_CON, DM\_CON, and ID\_CON lines to determine if a Dedicated Charger Port (DCP), Charging Downstream Port (CDP), car kit charger (200 k $\Omega$  on ID\_CON), or a Travel Adapter (TA, 180 k $\Omega$  on ID\_CON) has been detected. If a charger is detected, the default charging current stays at the fast charge current of 450 mA (default) specified in Charger Ctrl3 [FC\_Current] bits. Soft-start techniques are used to gradually increase current to minimize undesirable transients. If a charger is not detected and a USB Standard Downstream Port (SDP) is detected, the fast charge current drops to 90 mA like the pre-qualification current and continues to charge up the battery. This is summarized in Table 8.

**Table 8. Default Charging Currents**

| FC_Override | Auto_FC | Accessory<br>Detected        | Fast Charge<br>Current |

|-------------|---------|------------------------------|------------------------|

| 1           | Χ       | X                            | FC_Current             |

| 0           | 0       | X                            | 90 mA                  |

| 0           | 1       | CDP / DCP/<br>Car Kit Type 1 | FC_Current             |

| 0           | 1       | SDP / Unknown /<br>Factory   | 90mA                   |

Thermal issues are also considered (see Thermal Regulation section below) since this is the stage when there is the maximum voltage difference between V<sub>BUS IN</sub> and V<sub>BAT</sub>. Similar to the prequalification stage, communication with the baseband is not possible, at least initially, when VBAT is between 2.5 V and the weak-battery threshold (Charger Ctrl2 [WB\_Threshold]) so the FSA9591 must be able to charge the battery properly without interaction with the baseband. The 30-minute dead-battery provision timer continues during this stage. When this timer expires and V<sub>BAT</sub> does not exceed the weak battery threshold, the charger is disabled in compliance with the Battery Charging USB specifications for Dead Battery Provision (DBP). If the processor wakes up prior to the weak-battery threshold, it can change the weak-battery threshold via the Charger Ctrl2 [WB Threshold] bits to a value consistent with actual wake up voltage and/or disable the dead battery timer via the Charger Ctrl1 [DBP\_EN] bit.

Beyond the weak-battery threshold, the processor is expected to be up and controlling the charging process. The constant current is expected to be increased to match the battery charge capacity and the timers for total elapsed charging time can be changed accordingly. The constant voltage threshold is also expected to be set based on battery type and battery temperature, which should be monitored by the processor via separate controls. Thermal regulation within the FSA9591 may have little correlation to the battery temperature since the heat dissipation of the PCB that the FSA9591 is soldered to may be completely different from the heat dissipation within the battery pack.

When the programmed constant voltage threshold (programmed by Charger Ctrl5[CV\_Voltage] bits) is approached, the fast charging current loop is gradually changed to a constant voltage loop where the current is allowed to decay. Charging continues until the end of charge current (set by Charger Ctrl4 [EC\_Current] bits) is crossed.

If the top-off timer (set by Charger Ctrl1 [TopOff\_EN] bit) is disabled and Charger Ctrl1 [AutoStop] bit is set, all charging stops and the charger monitors  $V_{BAT}$ . If  $V_{BAT}$  falls 150 mV below the programmed constant voltage, the fast charge charging cycle starts again. A debounce time of 60 ms prior to restarting this cycle prevents glitches or temporary GSM current load of up to 2 A for <1 ms. If the top-off timer is enabled and the AutoStop bit is set; for 30 minutes after the end of charge current threshold has been crossed, the constant voltage charge cycle continues. After that, all charging is stopped and  $V_{BAT}$  is monitored again for a drop of 150 mV. If the Charger Ctrl1 [AutoStop] bit is not set, the constant voltage state is never left and the charger keeps trickle charging the battery to keep the voltage at the programmed Charger Ctrl5 [CV\_Voltage] voltage.

The FSA9591 maintains this constant voltage with  $\pm 0.5\%$  at room temperature to ensure optimal battery performance. The timer measuring the total charging elapsed time continues until the end of charge current threshold is crossed and does not include the top-off timer. If the total time exceeds the time in the Charger Ctrl2 [TC\_Time] bits, charging is stopped and the processor (if the voltage is high enough for the processor to function) can interrogate the source of the problem, correct it, then disables and re-enables the charger again to restart charging. If the voltage is not high enough for the processor to function, the problem with the battery needs to be solved and the USB cable needs to be unplugged and plugged back in again.

#### 11.1.3. Timers

The FSA9591 contains multiple timers to ensure that the battery is safely charged under all conditions. These timers include the dead-battery provision timer of 30 minutes, the total-charge timer of 5 to 7 hours, and the top-off timer of 30 minutes. Each timer can be enabled or disabled through I<sup>2</sup>C register accesses. The total-charge timer value can be programmed through I<sup>2</sup>C also.

The timers do not reset when an OVP event occurs. If  $V_{BAT}$  is above the weak-battery threshold and the baseband is active, the FSA9591 causes an interrupt when the OVP occurs and when the OVP event is disabled. This allows the baseband to control the timers based on the system needs. When OVP is detected, charging stops until the OVP event has recovered.

If  $V_{BAT}$  is below the weak-battery threshold and the dead-battery timer is active, FSA9591 takes the most conservative approach and keeps the DBP timer running when OVP is detected.

#### 11.1.4. Thermal Regulation

The FSA9591 contains a thermal regulation loop that is enabled when the junction temperature exceeds 120°C. When this temperature is exceeded, the FSA9591 starts to regulate the current to lower the temperature. It does this by reducing the fast charge current to 90 mA (it is most likely to be in the fast charge cycle since that is when there's maximum power consumption by the linear charger), waits 1 ms, increases the current to 200 mA, waits 1ms, continues along the fast charge currents specified in the Charger Ctrl3 [FC\_Current] where the wait between fast charge current steps is 1ms. This algorithm allows for the fastest recovery from a thermal regulation event while still averaging a current that keeps the temperature below 120°C.

The FSA9591 also terminates charging completely if the junction temperature exceeds 140°C. In both cases, the FSA9591 indicates which temperature event occurred via the Interrupt 1 [TREG\_EN] and Interrupt 1 [TSD\_EN] bits and indicates the removal of these conditions via the Interrupt2 [TREG\_DIS] and Interrupt2 [TSD\_DIS] bits. Temperature is continuously monitored whenever the charger is enabled.

#### 11.1.5. OVP, OCP, VBUS\_IN Regulation

The FSA9591 contains programmable over-voltage protection (OVP) on VBUS\_IN, ranging from 6.5 V to 8.0 V, as specified in the Charger Ctrl2 [OVP\_Threshold] bits with the default setting of 7 V. If OVP is detected, the FSA9591 terminates charging functionality if charging is active when OVP is detected. The FSA9591 interrupts the processor when the OVP event via the Interrupt 1[OVP\_EN] bit is detected and when the OVP event is removed via the Interrupt 1[OVP\_DIS] bit. The FSA9591 VBUS\_IN can tolerate voltages up to 28 V to handle the worst-case automotive scenarios for USB VBUS voltage.

$V_{BUS\_IN}$  is typically 5 V ±5-10%, depending on the charging current. If the FSA9591 linear charger is programmed to a higher current than the charger can support, a  $V_{BUS\_IN}$  control loop actively regulates the charging current to maintain at least 4.3 V (typical) on  $V_{BUS\_IN}$ . The FSA9591 attempts to lower the charger current to allow  $V_{BUS\_IN}$  to recover to at least 4.3 V. In cases where the charger  $V_{BUS\_IN}$  is not limited by the charger current, the FSA9591 attempts to lower the current until it reaches the minimum current level and then disables the charger. This  $V_{BUS\_IN}$  regulation loop is enabled by default and controlled by the Vbus\_Reg\_Dis bit in the Charger\_Ctrl1 register.

If the  $V_{\text{BUS\_IN}}$  regulation loop is disabled, the charging cycle is stopped when  $V_{\text{BUS\_IN}}$  falls below the  $V_{\text{BUS\_IN}}$  valid falling threshold of 3.5 V. Charging remains stopped until the  $V_{\text{BUS\_IN}}$  voltage rises above the rising  $V_{\text{BUS\_IN}}$  valid threshold of 3.7 V and stays above this threshold.

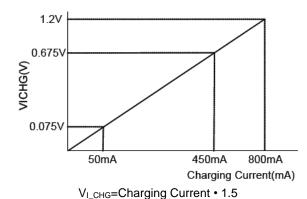

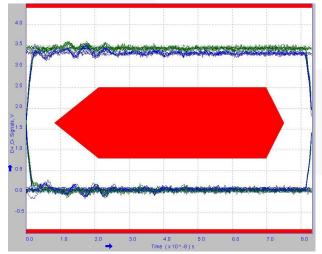

#### 11.2. VICHG

The VICHG is utilized by the host system to identify the amount of current flowing through the charger FET. VICHG is enabled by writing the VICHG\_EN bit in the register. When disabled, VICHG has an internal pull-down of 15 k $\Omega$ . V<sub>ICHG</sub> should not exceed 2.0 V when enabled.

Figure 11. VI\_CHG Characteristic

## 11.3. DETBAT N

For a typical battery pack, there is an extra terminal with a thermistor NTC resistor between this terminal and ground, which is expected to be much less than 100 k $\Omega$ . This terminal is tied to the DETBAT\_N pin for a system to disable the charger whenever a battery is not present. DETBAT\_N internally has a current source that detects the absence of any path to ground that is >100 k $\Omega$  on the DETBAT\_N pin. Once a HIGH is detected on DETBAT\_N, the charger is immediately disabled.

Some systems, for factory operation or other uses, may leave the charger enabled regardless of whether the battery pack is present or not. In these systems, it is expected that DETBAT\_N is tied LOW — always with a resistance to ground of 10 k $\Omega$ .

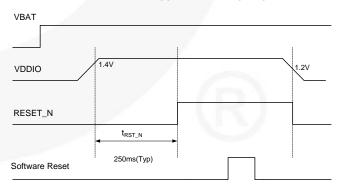

#### 11.4. **RESET\_N**

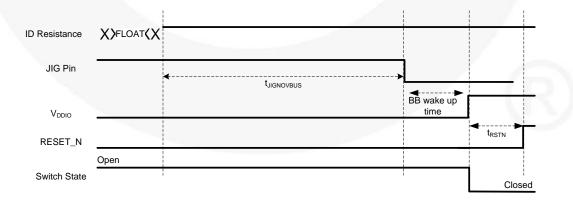

RESET\_N output is used as a system-level Power-On Reset (POR) triggered when  $V_{\text{DDIO}}$  is above 1.4 V. This RESET\_N open-drain output is pulled-down upon FSA9591 power up and released to HIGH after 250 ms (typically from when  $V_{\text{DDIO}}$  crosses 1.4 V on its rising edge). RESET\_N requires a valid  $V_{\text{BAT}}$  for RESET\_N to be actively pulled LOW after power up. This is a tight threshold comparator of  $V_{\text{DDIO}}$  with a hysteresis of 200 mV to accommodate a slowly rising signal. When  $V_{\text{DDIO}}$  falls below 1.2 V, RESET\_N is pulled LOW again. This timing is shown in Figure 12. RESET\_N is not reset on a software reset and is not intended to be a system-level reset, but a POR on VDDIO. The 250 ms timer is reset if  $V_{\text{DDIO}}$  triggers the falling-edge reset.

Figure 12. RESET\_N Timing

## 12. Product Specifications

## 12.1. Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol              |                                          | Parameter                                       |                                                                        | Min. | Max. | Unit     |

|---------------------|------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------|------|------|----------|

| $V_{BAT}$           | Supply Voltage from Battery              |                                                 |                                                                        | -0.5 | 6.0  | V        |

| V <sub>BUS_IN</sub> | Supply Voltage from USB Cor              | nnector                                         |                                                                        | -0.5 | 28.0 | V        |

| $V_{\text{DDIO}}$   | Supply Voltage from Baseban              | d                                               |                                                                        | -0.5 | 6.0  | V        |

| $V_{SW}$            | Switch I/O Voltage                       | USB                                             |                                                                        | -1.0 | 6.0  | V        |

| VSW                 | Switch i/O voltage                       | UART                                            |                                                                        | -1.0 | 6.0  | V        |

| Vio                 | I/O Voltage                              | I2C_SDA, I2C_SCL, INT_N, G                      | 2C_SDA, I2C_SCL, INT_N, GPO1, GPO2, RESET_N<br>IIG, DETBAT_N, ON_KEY_N |      |      | V        |

| VΙΟ                 | 1/O voltage                              | JIG, DETBAT_N, ON_KEY_N                         |                                                                        |      |      | V        |

| I <sub>IK</sub>     | Input Clamp Diode Current                |                                                 |                                                                        |      |      | mA       |

| la                  | Switch I/O Current                       | USB at T <sub>A</sub> =85°C                     |                                                                        |      | 25   | mA       |

| I <sub>SW</sub>     | (Continuous)                             | UART at T <sub>A</sub> =85°C                    |                                                                        |      | 12   |          |

| I <sub>SWPEAK</sub> | Peak Switch Current (Pulsed              | at 1ms Duration, <10% Duty Cycle                | 9)                                                                     |      | 150  | mA       |

| T <sub>STG</sub>    | Storage Temperature Range                |                                                 |                                                                        | -65  | +150 | °C       |

| $T_J$               | Maximum Junction Temperatu               | ure                                             |                                                                        |      | +150 | °C       |

| TL                  | Lead Temperature (Soldering              | , 10 Seconds)                                   |                                                                        |      | +260 | °C       |

|                     |                                          | USB Connector Pins                              | Air Gap                                                                | 15.0 |      |          |

|                     | IEC 61000-4-2 System                     | (DP_CON, DM_CON, $V_{BUS\_IN}$ , ID_CON) to GND | Contact                                                                | 8.0  |      |          |

| ESD                 | Human Rody Model JEDEC                   | IESD22 A114                                     | USB Pins                                                               | 4.0  |      | kV       |

|                     | Tidiliali body Wodel, JEDEO              | luman Body Model, JEDEC JESD22-A114             |                                                                        | 2.0  |      |          |

|                     | Charged Device Model, JEDEC JESD22-C101  |                                                 | All Pins                                                               | 1.5  |      |          |

| Surge               | IEC 61000-4-5 Surge Test <sup>(10)</sup> |                                                 | V <sub>BUS_IN</sub>                                                    | 24   |      | V        |

| Surge               | TEO 01000-4-3 Surge Test                 |                                                 | DP_CON/DM_CON                                                          | 10   |      | <b>V</b> |

#### Note

#### 12.2. Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                 |                                                | Parameter                                                      | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| $V_{BAT}$              | Battery Supply Voltage                         |                                                                | 2.7  |      | 4.4  | V    |

| V <sub>BUSIN_DET</sub> | V <sub>BUS_IN</sub> Voltage for Vali           | d Detection                                                    | 4.0  | 5.0  | 6.0  | V    |

| V <sub>BUSIN_CHG</sub> | V <sub>BUS_IN</sub> Voltage for Vali           | IS_IN Voltage for Valid Charging                               |      | 5.00 | 6.00 | V    |

| $V_{BUS}$ - $V_{BAT}$  | V <sub>BUS_IN</sub> – V <sub>BAT</sub> Voltage | <sub>US_IN</sub> – V <sub>BAT</sub> Voltage for Valid Charging |      |      |      | mV   |

| $V_{DDIO}$             | I/O Supply Voltage                             |                                                                | 1.6  | 1.8  | 3.6  | V    |

| \/                     | Switch I/O Voltage                             | USB Path Active                                                | 0    |      | 3.6  | V    |

| $V_{\sf SW}$           |                                                | UART Path Active                                               | 0    |      | 3.6  |      |

| ID <sub>CAP</sub>      | Capacitive Load on ID                          | _CON Pin for Reliable Accessory Detection                      |      |      | 1.0  | nF   |

| T <sub>A</sub>         | Operating Temperature                          | 9                                                              | -40  |      | +85  | ۰C   |

| TJ                     | Junction Temperature                           |                                                                | -40  |      | +125 | °C   |

| $\Theta_{JA}$          | Thermal Resistance Ju                          | inction-to-Ambient                                             |      | 60   |      | °C/W |

<sup>10.</sup> Modified voltage requirements: voltage impulse into an open-circuit with a 1.2 µs ramp-up rate and a 50 µs ramp-down rate.

## 12.3. Switch Path DC Electrical Characteristics

Unless otherwise specified, recommended  $T_A$  and  $T_J$  temperature ranges ( $T_A$ =-40 to +85°C,  $T_J$ =-40 to +125°C). All typical values are at  $T_A$ =25°C unless otherwise specified.

## 12.3.1. IO Specifications

| Symbol                   | Parameter                                                                                      | Voltage               | Conditions                           | Min.                   | Тур.                 | Max.                  | Unit |

|--------------------------|------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|------------------------|----------------------|-----------------------|------|

| INT_N (Pu                | sh-Pull)                                                                                       | V <sub>DDIO</sub> (V) |                                      |                        |                      |                       |      |

| V <sub>OH</sub>          | Output High Voltage                                                                            | 1.6 to 3.6            | I <sub>OH</sub> =-3 mA               | 0.8•V <sub>DDIO</sub>  |                      |                       | V    |

| V <sub>OL</sub>          | Output Low Voltage                                                                             | 1.6 to 3.6            | I <sub>OL</sub> =3 mA                |                        |                      | 0.2•V <sub>DDIO</sub> | V    |

| JIG, RESE                | T_N (Open-Drain)                                                                               | V <sub>DDIO</sub> (V) |                                      | <u>'</u>               |                      | 1                     |      |

| V <sub>OL</sub>          | Output Low Voltage                                                                             | 1.6 to 3.6            | I <sub>OL</sub> =3 mA                |                        |                      | 0.2•V <sub>DDIO</sub> | V    |

| RESET_N                  | Generation                                                                                     | V <sub>BAT</sub> (V)  |                                      | <u>'</u>               |                      |                       |      |

| V <sub>RSTN</sub>        | V <sub>DDIO</sub> Threshold for Generating RESET_N Output                                      | 3.0 to 4.4            |                                      |                        | 0.2•V <sub>BAT</sub> |                       | V    |

| t <sub>RSTN</sub>        | RESET_N Active Timeout Period;<br>from V <sub>DDIO</sub> ≥1.4V to RESET_N=HIGH <sup>(11)</sup> | 3.0 to 4.4            | RST_TO=00                            | 200                    | 250                  | 300                   | ms   |

| General-P                | urpose Outputs (GPO1 and GPO2)                                                                 | V <sub>DDIO</sub> (V) |                                      |                        |                      |                       |      |

| V <sub>OH</sub>          | Output High Voltage, GPO [GPOx_OD]=0                                                           | 1.6 to 3.6            | I <sub>OH</sub> =-3 mA               | 0.8•V <sub>DDIO</sub>  |                      |                       | V    |

| V <sub>OL</sub>          | Output Low Voltage, GPO [GPOx_OD]=X                                                            | 1.6 to 3.6            | I <sub>OL</sub> =3 mA                |                        |                      | 0.2•V <sub>DDIO</sub> | V    |

| Comparat                 | or Input (ON_KEY_N)                                                                            | V <sub>BAT</sub> (V)  |                                      |                        | A,                   | •                     |      |

| V <sub>IH</sub>          | High-Level Input Voltage                                                                       | 3.0 to 4.4            |                                      | 1.1                    |                      |                       | V    |

| V <sub>IL</sub>          | Low-Level Input Voltage                                                                        | 3.0 to 4.4            |                                      |                        |                      | 0.4                   | V    |

| I <sup>2</sup> C Interfa | ce Pins – Fast Mode (I2C_SDA,I2C_SCL)                                                          | V <sub>DDIO</sub> (V) |                                      |                        | 1]                   |                       |      |

| V <sub>IL</sub>          | Low-Level Input Voltage                                                                        | 1.6 to 3.6            |                                      |                        |                      | 0.3•V <sub>DDIO</sub> | V    |

| V <sub>IH</sub>          | High-Level Input Voltage                                                                       | 1.6 to 3.6            |                                      | 0.7•V <sub>DDIO</sub>  |                      |                       | V    |

|                          | Illustrated of Orbital Triangularity                                                           | 4.04-0.0              | V <sub>DDIO</sub> >2 V               | 0.05•V <sub>DDIO</sub> |                      |                       | V    |

| $V_{HYS}$                | Hysteresis of Schmitt Trigger Inputs                                                           | 1.6 to 3.6            | V <sub>DDIO</sub> <2 V               | 0.1•V <sub>DDIO</sub>  | l l                  |                       | V    |

| I <sub>I2C</sub>         | Input Current of I2C_SDA and I2C_SCL Pins                                                      | 1.6 to 3.6            | Input Voltage<br>0.26 V to<br>2.34 V | -10                    |                      | 10                    | μA   |

| V                        | Low-Level Output Voltage at 3 mA Sink Current                                                  | 204-44                | V <sub>DDIO</sub> >2 V               | 0                      |                      | 0.4                   | V    |

| V <sub>OL1</sub>         | (Open-Drain)                                                                                   | 3.0 to 4.4            | V <sub>DDIO</sub> <2 V               |                        |                      | 0.2V <sub>DDIO</sub>  | V    |

## 12.4. Switches

| Symbol               | Parameter                                 | V <sub>BAT</sub> (V) | Conditions                                                   | T <sub>A</sub> =-40 to +85°C,<br>T <sub>J</sub> =-40 to +125°C |       |       | Unit |

|----------------------|-------------------------------------------|----------------------|--------------------------------------------------------------|----------------------------------------------------------------|-------|-------|------|

|                      |                                           |                      |                                                              | Min.                                                           | Тур.  | Max.  |      |

| I <sub>OFF</sub>     | Power-Off Leakage Current                 | 0                    | All Data Ports, V <sub>SW</sub> =1 V to 4.4 V                |                                                                |       | 10    | μA   |

| I <sub>NO(OFF)</sub> | Off Leakage Current                       | 4.4                  | I/O pins=0.3 V, 4.1 V, or Floating                           | -0.100                                                         | 0.006 | 0.100 | μΑ   |

| I <sub>IDSHRT</sub>  | Short Circuit Current <sup>(11)</sup>     | 3.0 to 4.4           | Current Limit if ID_CON=0 V                                  |                                                                | 20    |       | μA   |

| USB Swite            | ch ON Path                                |                      |                                                              |                                                                |       |       |      |

| USB Analo            | og Signal Range                           | 3.0 to 4.4           |                                                              | 0                                                              |       | 3.6   | V    |

| R <sub>ONUSB</sub>   | USB Switch On Resistance <sup>(12)</sup>  | 3.0 to 4.4           | HS-USB $V_{D+/D}$ =0 V, 0.4 V, $I_{ON}$ =8 mA,               |                                                                | 8.0   | 16.0  | Ω    |

|                      |                                           |                      | FS-USB V <sub>SW</sub> =0 V, 3.6 V, I <sub>ON</sub> =24 mA   |                                                                | 11.5  | 19.0  |      |

| UART Sw              | itch ON Paths                             |                      |                                                              |                                                                |       |       |      |

| $V_{AR}$             | Analog Signal Range                       | 3.0 to 4.4           |                                                              | 0                                                              |       | 3.6   | V    |

| ר                    | UART Switch On Resistance <sup>(12)</sup> | 204544               | HS-USB V <sub>D+/D-</sub> =0 V, 0.4 V, I <sub>ON</sub> =8 mA |                                                                | 8.0   | 16.0  |      |

| Ronuart              | UART Switch On Resistance                 | 3.0 to 4.4           | FS-USB V <sub>SW</sub> =0 V, 3.6 V, I <sub>ON</sub> =24 mA   |                                                                | 11.5  | 19.0  | Ω    |

| ON_BT_U              | P to V2_3 Switch and COLMx to             | ROWx Switch          | ch Characteristics                                           |                                                                |       | •     |      |

| R <sub>ONMISC</sub>  | Switch On Resistance <sup>(12)</sup>      | 3.0 to 4.4           | V <sub>SW</sub> =0V to 4.4 V, I <sub>ON</sub> =1 mA          |                                                                | 36    |       | Ω    |

#### Notes:

- 11. Limits based on electrical characterization data.

- 12. On resistance is the voltage drop between the two terminals at the indicated current through the switch.

## 12.5. LDOs

| Symbol              | Parameter                                    | V <sub>BAT</sub> (V) | Conditions                                                         | T <sub>A</sub> =-40 to +85°C,<br>T <sub>J</sub> =-40 to +125°C |      |      | Unit          |

|---------------------|----------------------------------------------|----------------------|--------------------------------------------------------------------|----------------------------------------------------------------|------|------|---------------|

|                     |                                              | · /                  |                                                                    | Min.                                                           | Тур. | Max. |               |

| $V_{LDO}$           | LDO Output Voltage<br>Programmable Range     | 3.0 to 4.4           | I <sub>LDO</sub> =300 mA                                           | 1.8                                                            |      | 3.6  | V             |

| V <sub>STEP</sub>   | LDO Voltage Steps                            | 3.0 to 4.4           | See LDOx_Ctrl [LDOx_Voltage] for Exact Values                      |                                                                | 100  |      | mV            |

| $V_{DROP}$          | Dropout Voltage                              | 3.0 to 4.4           | I <sub>LDO</sub> =300 mA                                           |                                                                | 250  |      | mV            |

| I <sub>LDOMIN</sub> | Minimum Output Current                       | 3.0 to 4.4           |                                                                    | 0                                                              |      |      | mA            |

| I <sub>LDOMAX</sub> | Maximum Output Current                       | 3.0 to 4.4           |                                                                    | 300                                                            |      |      | mA            |

| $d_{VLDOR}$         | Output Voltage Accuracy                      | 3.0 to 4.4           | Over Range of LDO Output Voltage at T <sub>A</sub> =25°C           | -2.0                                                           |      | 2.0  | %             |

| $d_{VLDOF}$         | Output Voltage Accuracy Over Full Range      | 3.0 to 4.4           | Over Range of LDO Output Voltage                                   | -3.0                                                           | 10   | 3.0  | %             |

| d <sub>LINE</sub>   | Line Regulation <sup>(13)</sup>              | See<br>Conditions    | $V_{BAT}$ = $V_{LDO1(NOM(}$ +0.5 V to 3.6 V, $I_{LDO}$ =1 mA       |                                                                | 0.15 | 3.00 | %/V           |

| d <sub>LOAD</sub>   | Load Regulation <sup>(13)</sup>              | 3.8                  | I <sub>LDO</sub> =1 mA to 300 mA                                   |                                                                | 12   | 70   | μV/mA         |

| I <sub>LDO_SC</sub> | Maximum Current Limit                        | 3.0 to 4.4           | Short-Circuit Current Limit or Startup<br>Peak Current             |                                                                | 620  | 900  | mA            |

| PSRR                | Power Supply Rejection Ratio <sup>(13)</sup> | 3.0 to 4.4           | f=1 kHz                                                            |                                                                | 50   |      | dB            |

| e <sub>N</sub>      | Output Noise Voltage <sup>(13)</sup>         | 3.0 to 4.4           | f=10 Hz to 100 kHz                                                 |                                                                | 100  |      | $\mu V_{RMS}$ |