### **GC1011A DIGITAL RECEIVER**

### 1.0 FUNCTIONAL DESCRIPTION

Fabricated in 1 micron CMOS technology, the GC1011A chip is an all digital receiver which can extract narrow band signals from wide band digitized sources. At full rate operation (70 MHz input rate), the input bandwidth can be up to 35 MHz wide. Any signal within the input bandwidth can be down-converted to zero frequency, low pass filtered, and output at a reduced sample rate. The narrow band output can be formatted as either a complex data stream, or a real data stream. In the complex output mode the output sample rate ranges from (1/64)<sup>th</sup> to (1/65,536)<sup>th</sup> of the input rate in steps of (1/4N) where N is an integer ranging from 16 to 16,384. The output sample rate is doubled in the real output mode.

The user may select a standard output filter which has a passband covering 80% of the output bandwidth and has more than 70 dB of out-of-band rejection, or a wider, 90% passband filter which has 50 dB of out-of-band rejection.

The 28 bit accumulator in the chip's digital oscillator circuit provides a tuning accuracy equal to the input clock rate divided by  $2^{28}$ . With a 60 MHz clock rate the tuning resolution is 0.2 Hz giving a tuning accuracy of +/- 0.1 Hz. The phase noise in the oscillator is low enough to provide a spur free dynamic range of over 75 dB. All arithmetic following the oscillator is performed to sufficient accuracy to provide over 90 dB of noise free dynamic range. This allows the chip to generate and preserve up to 20 dB of narrow band processing gain. The gain of the output signal can be adjusted in 6 dB steps.

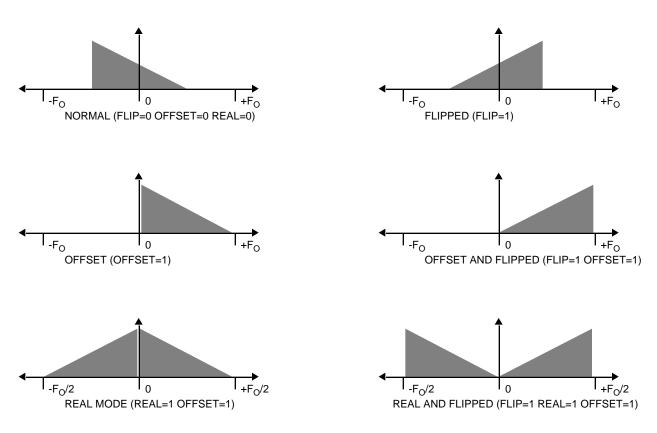

The chip's output circuit allows the user to select a real or complex data output format, to select spectral inversion, or to offset the output spectrum by half of the output sample rate. The filtered signal is output in a bit-serial format. The user has control over the bit-serial format including its rate, its bit-strobe format and its frame-strobe format.

On chip diagnostics are provided to simplify system debug and maintenance.

The chip receives configuration and control information over a microprocessor compatible bus consisting of an 8 bit data I/O port, a 4 bit address port, a read/write bit, and a control select strobe.

The GC1011A chip replaces the GC1011 chip. The new features include improved real output formatting and a symmetric rounding algorithm which removes unwanted DC rounding bias from the output.

#### 1.1 KEY FEATURES

- 70 million samples per second input rate

- 0.1 Hz tuning resolution

- >70 dB dynamic range

- Programmable output bandwidth

- 12 bit inputs, 16 bit outputs

- Real or complex output formats

- Built in strobe/sync generator

- Microprocessor interface for control, output, and diagnostics

- Power down mode

- Built in diagnostics

- 750 mW power at 50 MHz, 5 volts

- 200 mW at 30 MHz, 3.3 volts

- Small, 44 pin Leaded chip carrier package

#### 1.2 BLOCK DIAGRAM

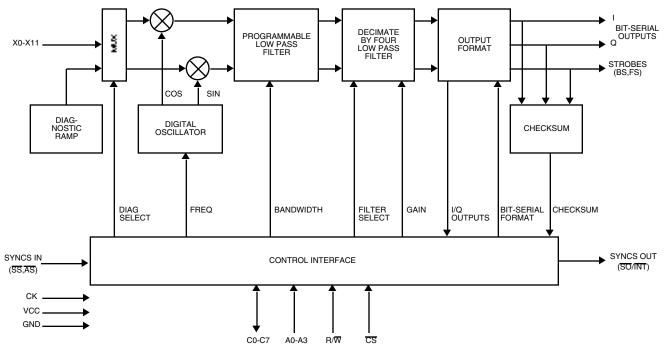

A block diagram illustrating the major functions of the chip is shown in Figure 1

Each of these functions are described below.

#### 1.3 CONTROL INTERFACE

The control interface performs four major functions: It allows an external processor to configure the chip, it allows an external processor to capture and read output samples from the chip, it allows an external processor to perform diagnostics, and it generates internal synchronization strobes.

The chip is configured by writing control information into 8 bit control registers within the chip. The contents of these control registers and how to use them are described in Section 3. The registers are written to or read from using the C[0:7], A[0:3], R/W, and  $\overline{CS}$  pins. Each control register has been assigned a unique address within the chip. An external processor (a microprocessor, computer, or DSP chip) can write into a register by setting A[0:3] to the desired register address, setting the R/W pin low, setting D[0:7] to the desired value and then pulsing  $\overline{CS}$  low.

To read from a control register the processor must set A[0:3] to the desired address, set R/W high, and then set  $\overline{CS}$  low. The chip will then drive C[0:7] with the contents of the selected register. After the processor has read the value from C[0:7] it should set  $\overline{CS}$  high. The C[0:7] pins are turned off (high impedance) whenever  $\overline{CS}$  is high or R/W is low. The chip will only drive these pins when  $\overline{CS}$  is low and R/W is high.

#### **GC1011A DIGITAL RECEIVER**

Control register addresses 12, 13, 14, and 15 are reserved to allow an external processor to read output samples from the chip. Addresses 12 and 13 are the I-registers which store the 16 bit real part of the output sample. Addresses 14 and 15 are the Q-registers which store the imaginary part. In the real mode the I registers store the even-time output samples and the Q registers store the odd-time output samples. Output ready and missed flags are provided in control register 10 in order to synchronize the storing and reading of the output samples. An interrupt output pin is also provided on the chip which can be used to interrupt the external processor when a new sample is ready. See the description of control register 10 in Section 3.7 for more details. The setup, hold and pulse width requirements for control read or write operations are given in Section 4.4.

Checksums are read from the chip during diagnostics using address 11. More details on the diagnostic modes is given in Section 1.9.

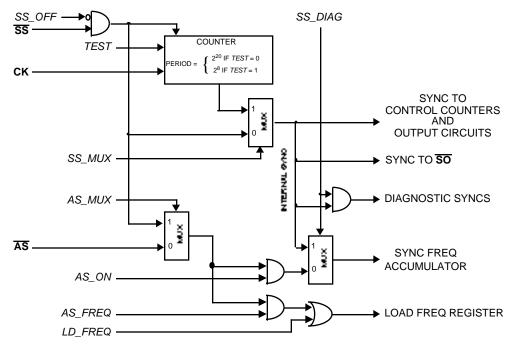

The control interface also generates the chip's internal sync strobes. The user may select to synchronize the chip using an external sync strobe ( $\overline{SS}$ ), or use the chip's internal sync counter. The internal sync counter can be synchronized to  $\overline{SS}$ , or left to free run (See SS\_OFF in Section 3.2). The period of the internal sync counter can be either 256 clocks or 2<sup>20</sup> clocks. The 256 clock period is intended to be used for chip test purposes only. The internal sync counter can also be used to periodically re-synchronize all of the counters in the chip during normal operating modes if the chip's decimation ratio is set to a power of 2. Except for diagnostics the sync counter cannot be used for non-power of 2 decimation modes.

#### 1.4 DIGITAL OSCILLATOR

The digital oscillator generates sine and cosine sequences which are used to mix the desired signal down to zero frequency. The digital oscillator contains a 28 bit frequency register, a 28 bit frequency accumulator, and a sine-cosine generator. The tuning frequency of the oscillator is set by loading a 28 bit frequency word from the control registers into the frequency register. If the frequency register is set to the

word **FREQ**, then the tuning frequency will be: Frequency =  $\frac{\text{Sample Rate}}{2^{28}}$ **FREQ**.

The frequency word **FREQ** is stored into the control registers at control addresses 0,1,2 and 3. The 28 bit word is then transferred into the frequency register using one of the following methods:

- (1) The frequency register is always loading (the frequency changes immediately as the frequency word is loaded into the control registers).

- (2) The frequency register is loaded when the user sets a control register bit.

- (3) The frequency register is synchronously loaded when the accumulator sync strobe (AS) goes low.

(4) The frequency register is synchronously loaded when the system sync strobe (SS) goes low.

See Section 3.2 for more details on the frequency load modes.

The 28 bit frequency word is accumulated in the 28 bit frequency accumulator. The frequency accumulator will normally free run, but can be synchronously cleared by either the system sync  $(\overline{SS})$  or the

- 3 -

accumulator sync ( $\overline{AS}$ ). The accumulator clear modes are controlled by bits in control register 4. See Section 3.2 for details.

The upper 13 frequency accumulator bits are used to generate the oscillator's sine and cosine outputs. These sines and cosines are generated to 12 bit accuracy. The spectral purity of the oscillator is illustrated in the following figures.

Figure 2. DLO SPECTRUM: FREQ = (HEX) 1234567

Figure 4. DLO SPECTRUM: FREQ = (HEX) 5678910

The oscillator's peak spur levels, as can be seen from these plots, are well below -75 dB.

#### 1.5 MIXER

The mixer multiplies the 12 bit input samples by the 12 bit sine and cosine values coming from the digital oscillator. An input signal at the oscillator's tuning frequency will be centered at zero frequency after passing through the mixer.

#### 1.6 PROGRAMMABLE LOW PASS FILTER

The mixer's output is filtered to isolate the desired signal using a programmable bandwidth low pass filter. The filter reduces the sample rate by a factor of D, where D is a user specified integer ranging from 16 to 16,384. The value of D is stored in control registers 8 and 9. The out-of-band rejection of the filter is over 72 dB.

#### 1.7 DECIMATE BY FOUR FILTER

The programmable bandwidth filter is followed by a 64 tap filter which, in the complex mode, reduces the sample rate by an additional factor of 4, giving an overall bandwidth (and sample rate) reduction of 4**D**. In the real mode the final filter only reduces the sample rate by a factor of two. The user may select a choice of two spectral responses for this filter. The standard response has a 3 dB passband which covers 80% of the output Nyquist rate and has an out-of-band rejection of over 70 dB. The optional response has a 3 dB passband covering 90% of the Nyquist rate, but only 50 dB of out-of-band rejection. The spectral response of these filters is shown in the following figures.

e Here H

THE MAXIMUM OUT-OF-BAND ALIASING IS SHOWN BY THE DOTTED LINE

This document contains information which may be changed at any time without notice

#### **GC1011A DIGITAL RECEIVER**

#### **DATA SHEET**

Figure 7. FILTER RESPONSE: 90% FILTER

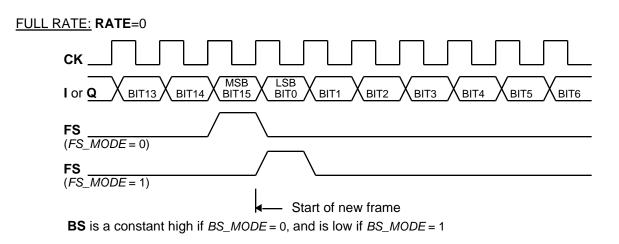

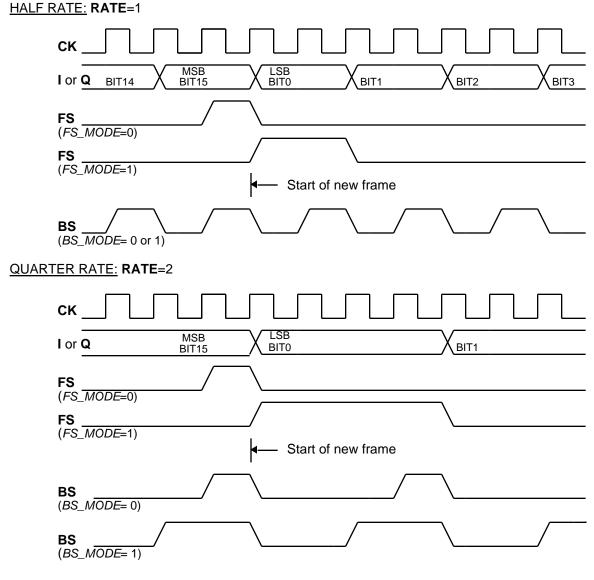

#### 1.8 OUTPUT FORMATTING

The output format circuit adjusts the gain of the filter output, optionally flips the output spectrum, optionally offsets the spectrum by one-fourth the Nyquist rate, optionally converts the complex output stream to a real one at twice the rate, and rounds the samples to 16 bits. The rounded outputs are passed to the control interface where they can be read by an external processor. They are also passed through a parallel to serial conversion circuit and output as bit-serial streams. Separate bit-serial outputs are provided for the I and Q halves of the complex output.

The bit-serial output has several programmable features. The user can select:

- (1) The rate of the bit-serial stream. The bit rate is programmable to be a power of two division of the clock.

- (2) MSB first or LSB first orientation. The 16 bit data is normally output LSB first, but can optionally be output MSB first.

- (3) Multiplexed I/Q format. The user can have the I and Q outputs multiplexed together so that the bit streams contain the 16 bit I sample followed by the 16 bit Q sample. The I and Q outputs are identical in this mode.

- (4) The format of the bit strobe. A bit strobe is provided as a clock for the bit-serial stream. The bit strobe can be selected to have a 50% duty cycle, or to have a pulse width equal to a system clock period. The user can also select the active high or active low polarity of the bit strobe. The clock pulse mode is suitable to be used as a clock enable signal. The bit strobe is a constant high or low level (depending upon the mode and polarity selected) when the bit rate is set to be equal to the clock rate.

- (5) The format of the frame strobe. A frame strobe is provided at the start of each output frame. The strobe is either one bit-period wide synchronous with the first bit of the frame, or it is active during the clock cycle before the start of each frame. The active high or low polarity of the strobe is programmable. The frame rate is equal to the complex output rate.

The programmable bit rate allows the user to select the number of times that each 16 bit output sample repeats during a frame. If the frame period is 64 clocks (i.e., the chip is decimating by a factor of 64), then the same 16 bit output sample will be repeated 4 times when the bit rate is equal to the system clock rate. If the bit rate is set to one-half, then the sample will only repeat twice. If the bit rate is set to one-fourth, then there will be exactly one output sample per frame. The higher bit rates allow one to multiplex the outputs from multiple GC1011A chips into a single time division multiplexed (TDM) stream. If the bit rate is set so that each output sample is repeated four times in a frame, then the outputs from four chips can be multiplexed into a TDM stream by selecting the first chip's output for the first 16 bit-strobes of the frame, selecting the second chip's output for the next 16 strobes, selecting the third chip's output for the next 16 strobes, and then selecting the last chip's output for the final 16 strobes of the frame.

In the real output mode the frame rate is double the complex mode rate and the output signal is shifted in frequency so that it is centered from 0 to  $F_O/2$ , where  $F_O$  is the output sample rate. The I and Q output streams are identical in the real mode. For compatibility with system designs using the older GC1011 chip see the REAL\_FS bit described in Section 3.7.

The output format circuitry is synchronized by the **SS** input sync. This allows one to synchronize the output frame timing of multiple GC1011A chips.

| GRAYCHIP,INC.                  | - 8 -                   | NOVEMBER 24, 1992              |

|--------------------------------|-------------------------|--------------------------------|

| This document contains informa | ation which may be char | ged at any time without notice |

#### 1.9 DIAGNOSTICS

An input ramp generator, a sync period generator, and a checksum generator are provided on the chip in order to run diagnostic tests. Diagnostics are performed by turning on the ramp generator, enabling the diagnostic syncs, letting the chip operate for at least 4 sync periods, reading the checksum and comparing it to its predicted value. A new checksum is generated every sync period. The input ramp sequence is the same for every sync period and the chip is re-initialized at the beginning of each sync period so that each checksum should be the same once the chip's data path has been flushed. The chip requires at least 3 sync periods to flush, so the fourth and following checksums should be valid. The test is then repeated for several different tuning frequencies, decimation settings, and output modes.

The sync period is 2<sup>20</sup> clocks, or approximately 1 million clock cycles, so four sync periods will be about 4 million clocks. This represents a delay of less than 15 milliseconds for a clock rate of 60 MHz.

The following table lists the expected checksums for four test configurations. All values are in HEX.

| CONTROL REGISTER             | <u>TEST 1</u> | <u>TEST 2</u> | <u>TEST 3</u> | <u>TEST 4</u> |

|------------------------------|---------------|---------------|---------------|---------------|

| FREQ (REG 0,1,2,3)           | 0000101       | 0F0F0F0       | 55AA55A       | AA55AA5       |

| SYNC MODE (REG 4)            | A9            | A9            | A9            | A9            |

| OUTPUT MODE (REG 5           | 5) 01         | 51            | F2            | 0C            |

| FILTER MODE (REG 6)          | 50            | 66            | 7D            | 4B            |

| GAIN (REG 7)                 | 0             | 1             | 2             | 3             |

| <b>DECIMATION</b> (REG 8,9   | ) 000F        | 0020          | 0F30          | 30C1          |

| EXPECTED CHECKSUMS (GC1011A) |               |               |               |               |

| (REG 11)                     | 32            | 9E            | 22            | 52            |

| EXPECTED CHECKSUMS (GC1011)  |               |               |               |               |

| (REG 11)                     | 96            | EB            | 9A            | A6            |

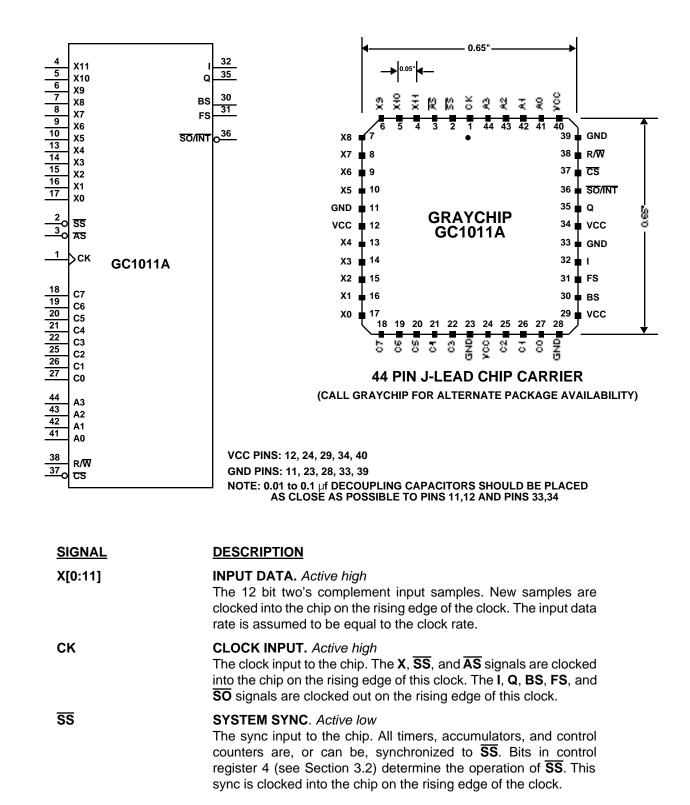

#### 2.0 PIN DESCRIPTIONS

| ĀS            | ACCUMULATOR SYNC. Active low<br>The accumulator sync is provided to synchronously change tuning<br>frequencies. This sync can be used to load a new tuning frequency<br>into the frequency register and/or to clear the frequency<br>accumulator. This signal is clocked into the chip on the rising edge<br>of the clock.                                                                                                                                                                                                                                                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I             | <b>IN-PHASE OUTPUT STREAM</b> . Active high<br>The I part of each complex output sample is output as a bit serial<br>stream on this pin. The bits are clocked out on the rising edge of<br>the clock.                                                                                                                                                                                                                                                                                                                                                                      |

| Q             | <b>QUADRATURE OUTPUT STREAM</b> . Active high<br>The Q part of each complex output sample is output as a bit serial<br>stream on this pin. The bits are clocked out on the rising edge of<br>the clock.                                                                                                                                                                                                                                                                                                                                                                    |

| BS            | <b>BIT STROBE</b> . <i>Programmable active high or low level</i><br>This strobe is output synchronous with the <b>I</b> and <b>Q</b> bit streams.<br>The strobe occurs once per bit and is either one clock wide or has<br>a 50% duty cycle. The high/low polarity of the strobe is<br>programmable. See Section 3.3 for details.                                                                                                                                                                                                                                          |

| FS            | <b>FRAME STROBE</b> . <i>Programmable active high or low level</i><br>This strobe marks the beginning of an output frame. The strobe is<br>either one clock cycle wide, or is the width of a data bit at the<br>selected bit rate. The high/low polarity of this signal is<br>programmable. See Section 3.3 for details.                                                                                                                                                                                                                                                   |

| <u>SO/INT</u> | <b>SYNC OUT OR INTERRUPT OUT</b> . <i>Active low</i><br>This signal is either a sync output or is an interrupt output<br>depending upon a bit in control register 10. As a sync output, the<br>signal is a delayed version of the input system sync $\overline{SS}$ , or is the<br>internally generated sync which has a period of $2^{20}$ clocks, or is a<br>one-shot sync strobe. As an interrupt output, the signal is the<br>READY flag from control register 10. This flag goes active when a<br>new output sample is ready in control registers 12, 13, 14, and 15. |

| C[0:7]        | <b>CONTROL DATA I/O BUS</b> . <i>Active high</i><br>This is the 8 bit control data I/O bus. Control register data is loaded<br>into the chip or read from the chip through these pins. The chip will<br>only drive these pins when <b>CS</b> is low and <b>R/W</b> is high.                                                                                                                                                                                                                                                                                                |

| A[0:3]        | <b>CONTROL ADDRESS BUS</b> . <i>Active high</i><br>These pins are used to address the 16 control registers within the<br>chip. Each of the 16 control registers within the chip are assigned<br>a unique address. A control register can be written to or read from<br>by setting <b>A[0:3]</b> to the register's address.                                                                                                                                                                                                                                                 |

| R/₩           | <b>READ/WRITE CONTROL</b> . <i>High for read, low for write</i><br>This pin determines if the control bus cycle is a read or write<br>operation. The pin is high for a read and is low for a write.                                                                                                                                                                                                                                                                                                                                                                        |

| CS            | <b>CONTROL STROBE</b> . <i>Active low</i><br>This control strobe enables the read or write operation. The<br>contents of the register selected by <b>A[0:3]</b> will be output on <b>C[0:7]</b><br>when <b>R/W</b> is high and <b>CS</b> is low. If <b>R/W</b> is low when <b>CS</b> goes low,<br>then the selected register will be loaded with the contents of<br><b>C[0:7]</b> .                                                                                                                                                                                        |

| GRAYCHIP,INC.                  | - 11 -                  | NOVEMBER 24, 1992              |

|--------------------------------|-------------------------|--------------------------------|

| This document contains informa | ation which may be chan | ged at any time without notice |

#### 3.0 CONTROL REGISTERS

The chip is configured and controlled through the use of 16 eight bit control registers. These registers are accessed for reading or writing using the control bus pins ( $\overline{CS}$ ,  $R/\overline{W}$ , A[0:3], and C[0:7]) described in the previous section. The register names and their addresses are:

| ADDRESS | NAME        | ADDRESS | NAME              |

|---------|-------------|---------|-------------------|

| 0       | FREQ byte 0 | 8       | Decimation byte 0 |

| 1       | FREQ byte 1 | 9       | Decimation byte 1 |

| 2       | FREQ byte 2 | 10      | Output Status     |

| 3       | FREQ byte 3 | 11      | Checksum          |

| 4       | Sync mode   | 12      | I-output byte 0   |

| 5       | Output mode | 13      | I-output byte 1   |

| 6       | Filter mode | 14      | Q-output byte 0   |

| 7       | Gain        | 15      | Q-output byte 1   |

The following sections describe each of these registers. The type of each register bit is either R or R/W indicating whether the bit is read only or read/write. All bits are active high.

#### 3.1 FREQUENCY WORD REGISTERS

Registers 0, 1, 2, and 3 contain the 28 bit frequency tuning word. Bit 0 is the LSB, bit 27 is the MSB.

| ADDRESS 0                   | ):          | FREQUENCY BYTE 0 |                     |                                               |

|-----------------------------|-------------|------------------|---------------------|-----------------------------------------------|

| <u>BIT</u>                  | <u>TYPI</u> | <u>E</u>         | NAME                | DESCRIPTION                                   |

| 0-7                         | R/W         |                  | FREQ[0:7]           | Byte 0 (least significant) of frequency word  |

| ADDRESS 1                   | :           | FREQUEN          | CY BYTE 1           |                                               |

| <u>BIT</u>                  | <u>TYP</u>  | E                | NAME                | DESCRIPTION                                   |

| 0-7                         | R/W         |                  | <b>FREQ</b> [8:15]  | Byte 1 of frequency word                      |

| ADDRESS 2: FREQUENCY BYTE 2 |             | CY BYTE 2        |                     |                                               |

| <u>BIT</u>                  | <u>TYP</u>  | E                | NAME                | DESCRIPTION                                   |

| 0-7                         | R/W         |                  | <b>FREQ</b> [16:23] | Byte 2 of frequency word                      |

| ADDRESS 3                   | 8:          | FREQUEN          | CY BYTE 3           |                                               |

| <u>BIT</u>                  | <u>TYP</u>  | E                | NAME                | DESCRIPTION                                   |

| 0-3                         | R/W         |                  | FREQ[24:27]         | 4 most significant bits of the frequency word |

| 4-7                         | R/W         |                  | -                   | unused                                        |

If the desired tuning frequency is F, then the frequency word should be set to:  $FREQ = 2^{28}F/(clock rate)$

#### 3.2 SYNC MODE REGISTER

The sync mode register controls the action of the **SS** and **AS** sync strobes and how they affect the chip's internal timers, counters, and accumulators.

| ADDRESS 4 | l: Sync Moo | de Register |                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-----------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BIT       | TYPE        | NAME        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               |  |

| 0 (LSB)   | R/W         | SS_OFF      | This bit disables the <b>SS</b> input.                                                                                                                                                                                                                                                                                                                                                    |  |

| 1         | R/W         | AS_ON       | Enables the accumulator sync $\overline{AS}$ . Normally the frequency accumulator will free run. This bit causes the frequency accumulator to be initialized to the contents of the frequency register when $\overline{AS}$ goes low. $\overline{SS}$ , instead of $\overline{AS}$ , will reset the accumulator if AS_MUX is set and $\overline{SS}$ is not disabled by SS_OFF.           |  |

| 2         | R/W         | AS_MUX      | Use $\overline{SS}$ for the accumulator sync. The $\overline{AS}$ input is ignored and the $\overline{SS}$ strobe is used in its place when this bit is set and $\overline{SS}$ is not disabled by SS_OFF. (See AS_ON and AS_FREQ).                                                                                                                                                       |  |

| 3         | R/W         | LD_FREQ     | Load the frequency register in the digital oscillator<br>with the contents of the frequency word registers. If<br>left on, this bit will cause the frequency register to<br>load whenever a frequency word register is<br>changed.                                                                                                                                                        |  |

| 4         | R/W         | AS_FREQ     | Enables the synchronous frequency load mode.<br>When this bit is set and $\overline{AS}$ goes low, the frequency<br>register will be synchronously loaded with the<br>contents of the frequency control registers. $\overline{SS}$ ,<br>instead of $\overline{AS}$ , will load the frequency register if<br>AS_MUX is set and $\overline{SS}$ is not disabled by SS_OFF.                  |  |

| 5         | R/W         | SS_DIAG     | Enables diagnostic syncs. This bit routes the internal sync to the checksum generator and to all accumulators and control counters within the chip. This forces the chip to re-initialize at the start of every sync period. The internal sync period will be $2^{20}$ clocks if SS_MUX is set, otherwise it will be determined by the period of an externally provided <b>SS</b> strobe. |  |

| 6         | R/W         | TEST        | Shortens the internal sync counter period from $2^{20}$ clocks to $2^{8}$ clocks. This mode is used to test chips at the factory.                                                                                                                                                                                                                                                         |  |

| 7 (MSB)   | R/W         | SS_MUX      | Use the sync counter's terminal count strobe for the internal sync instead of the sync input $\overline{SS}$ . The internal sync is output on the $\overline{SO}$ pin.                                                                                                                                                                                                                    |  |

The operation of these control bits are illustrated in Figure 8 on the next page.

GRAYCHIP,INC. - 14 - NOVEMBER 24, 1992 This document contains information which may be changed at any time without notice

Figure 8. SYNC CONTROLS

#### 3.3 OUTPUT MODE REGISTER

The output mode register contains the controls for the bit-serial outputs.

| ADDRESS 5: Output mode register |             |                   |                                                                                                                                                                                                                                      |

|---------------------------------|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>BIT</u>                      | <u>TYPE</u> | NAME              | DESCRIPTION                                                                                                                                                                                                                          |

| 0-3                             | R/W         | <b>RATE</b> [0:3] | The bit rate select. The bit serial rate is:<br>Bit rate = 2 <sup>-RATE</sup> (clock rate)                                                                                                                                           |

| 4                               | R/W         | BS_MODE           | Changes the mode of <b>BS</b> . Normally <b>BS</b> pulses high during the clock cycle before a bit transition. This bit changes <b>BS</b> so that it is a 50% duty cycle clock with its rising edge in the middle of each bit period |

| 5                               | R/W         | BS_POL            | Changes the polarity of <b>BS</b> .                                                                                                                                                                                                  |

| 6                               | R/W         | FS_MODE           | Changes the mode of <b>FS</b> . Normally <b>FS</b> pulses high<br>during the clock cycle before the start of a new<br>frame. This bit changes <b>FS</b> so that it will be high for<br>the first bit period of each new frame.       |

| 7                               | R/W         | FS_POL            | Changes the polarity of <b>FS</b> .                                                                                                                                                                                                  |

These controls are illustrated in the timing diagrams shown in Figure 9 on the next page. Note that the polarity shown for **BS** and **FS** can be changed using *BS\_POL* and *FS\_POL*.

GRAYCHIP,INC. - 17 - NOVEMBER 24, 1992 This document contains information which may be changed at any time without notice

#### 3.4 FILTER MODE REGISTER

This register controls filtering, output formatting and the diagnostic input mode.

| ADDRESS | 6: Filter Mod | le Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT     | TYPE          | NAME        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0       | R/W           | FSEL        | Use the 90% filter instead of the 80% filter.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1       | R/W           | REAL        | Use real output format instead of complex. The OFFSET and REAL_FS (see Section 3.7) control bits must also be high for the real mode to work. The output data rate is double the complex data rate in this mode.                                                                                                                                                                                                                                       |

| 2       | R/W           | OFFSET      | Offset the output spectrum. In the complex output mode (REAL=0), this bit forces the output spectrum to be centered at $F_{CK}/2$ , where $F_{CK}$ is the output sample rate. This mode is useful for single-sideband AM signals because it moves the lower band edge up to zero frequency where it belongs. The upper half of the spectrum, in the complex mode, will appear as negative frequencies. This mode is mandatory in the real output mode. |

| 3       | R/W           | FLIP        | Flip the output spectrum. This bit inverts the output spectrum. In the complex mode the spectrum is flipped about zero. In the real mode the spectrum is flipped about $F_{CK}/4$ , where $F_{CK}$ is the real mode's output sample rate.                                                                                                                                                                                                              |

| 4       | R/W           | IQ_MUX      | Multiplex the I and Q outputs together. In this mode<br>the bit -serial output alternates between the 16 bit I<br>sample and the 16 bit Q sample. The I sample is<br>output first in each frame followed by the Q sample.<br>The I and Q samples alternate, 16 bits each, until<br>the end of the frame. The I and the Q pins output<br>identical bit-streams in this mode.                                                                            |

| 5       | R/W           | MSB_MODE    | Output MSB first instead of LSB first. Normally the 16 bit samples are output LSB first. The MSB is output first when this bit is set.                                                                                                                                                                                                                                                                                                                 |

| 6       | R/W           | DIAG        | Use the diagnostic ramp for the input to the chip instead of the $X$ input. The ramp counts from -2048 to +2047 and then starts over again.                                                                                                                                                                                                                                                                                                            |

| 7       | R/W           | POWER_DOWN  | Allows the <b>AS</b> input to gate the chip's internal clock.<br>The clock is always enabled when this bit is low.                                                                                                                                                                                                                                                                                                                                     |

The effect on the output spectrum of the REAL, OFFSET and FLIP bits is illustrated in the following diagram. (F<sub>O</sub> is the output sample rate))

The POWER\_DOWN control bit is used in conjunction with the  $\overline{AS}$  input pin to decrease the power consumed by the GC1011A chip in a stand-by mode. The power can be reduced by a factor of N (to a minimum of about 1mW) by setting the POWER\_DOWN control bit and then pulsing  $\overline{AS}$  low for one clock cycle out of N. All control registers retain their state during power down, but the chip's I, Q, BS, FS and SO output signals will not be valid. Note that an internal clock rate ( $F_{CK}/N$ ) less than 10 Hz may damage the chip.

#### 3.5 GAIN CONTROL REGISTER

This register sets the output gain.

| ADDRESS 7: Gain Control Register |             | rol Register |                                                                                                             |

|----------------------------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------|

| <u>BIT</u>                       | <u>TYPE</u> | NAME         | DESCRIPTION                                                                                                 |

| 0-3                              | R/W         | GAIN[0:3]    | The 4 bit gain word. The gain is equal to 2 <sup>GAIN</sup> , allowing gain adjustments in 6 dB increments. |

| 4-7                              | R/W         | -            | Unused                                                                                                      |

The chip has unity gain when the decimation in the programmable low-pass filter has been set to a power of two. If the decimation is not a power of two, then the gain is given by  $G=(D/P)^4$ , where D is the decimation in the programmable low-pass filter (See Section 3.6) and P is the next power of two greater than **D**. For example, if **D** is 30 the gain would be  $(30/32)^4$ =0.772, or -2.2 dB. If **D** is 33 the gain would be (33/64)<sup>4</sup>=0.071, or -23 dB. The nominal gain setting in the first example would be zero and would be 3 or 4 in the second example.

The overall gain of the chip is given by:

$$G = 2^{GAIN} (D/P)^4.$$

In dB this is approximately:

$G_{dB} = (6xGAIN) + (80 \log(D/P)).$

If the gain is too high, the chip will clip the samples to +/- full scale and will set the overflow bit in the output status register (See Section 3.7).

#### 3.6 **DECIMATION CONTROL REGISTERS**

These registers set the decimation ratio in the programmable low-pass filter.

| ADDRESS 8: | Decimation  | n Byte 0  |                      |

|------------|-------------|-----------|----------------------|

| <u>BIT</u> | <u>TYPE</u> | NAME      | DESCRIPTION          |

| 0-7        | R/W         | DEC[0:7]  | 8 LSBs of DEC        |

| ADDRESS 9: | Decimation  | n Byte 1  |                      |

| <u>BIT</u> | TYPE        | NAME      | DESCRIPTION          |

| 0-5        | R/W         | DEC[8:13] | 6 MSBs of <b>DEC</b> |

| 6,7        | R/W         | -         | Unused               |

A decimation ratio of D is set by programming DEC to be equal to (D-1). The minimum value of DEC is 15 and the maximum is 16,383 corresponding to the minimum decimation of 16 and maximum of 16,384.

#### 3.7 OUTPUT STATUS REGISTER

This register contains flags and status information for the output samples.

| ADDRESS 10: Output Status Register |             | tatus Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>BIT</u>                         | <u>TYPE</u> | NAME           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0                                  | R/W         | READY          | Tells the chip that the user is ready to capture an output sample. The chip clears this bit when it has captured the sample.                                                                                                                                                                                                                                                                                                                               |

| 1                                  | R/Clear     | MISSED         | The chip sets this bit high if a new output sample<br>was ready but the user had not set READY high.<br>This lets the user know if a sample has been<br>missed. This bit is cleared by writing a 0 to the bit.<br>Attempting to write a 1 to this bit does nothing.                                                                                                                                                                                        |

| 2                                  | R/W         | OVERFLOW       | The chip sets this bit when an overflow occurs. This<br>bit can be used to indicate if the gain is set too high.<br>This bit stays high until the user clears it.                                                                                                                                                                                                                                                                                          |

| 3                                  | R/W         | INT_ENABLE     | This bit is used in the interrupt mode (See bit 4 below) to turn on the interrupt output. If this bit is off the <b>INT</b> output pin is forced high. When this bit is high the <b>INT</b> output pin is equal to READY. When READY goes low, meaning that a new sample has been captured, the <b>INT</b> pin will go low. If <b>INT</b> is tied to a processor's interrupt input, then the processor will be interrupted whenever a new sample is ready. |

| 4                                  | R/W         | INT_MODE       | This bit selects the <b>INT</b> signal for output on pin <b>SO/INT</b> . Normally <b>SO</b> is output on the pin.                                                                                                                                                                                                                                                                                                                                          |

| 5                                  | R/W         | STROBE_MODE    | This bit selects the one-shot sync strobe for output<br>on the $\overline{SO}$ pin. When this bit is low the $\overline{SO}$ sync is<br>determined by SS_MUX (see Section 3.2).                                                                                                                                                                                                                                                                            |

| 6                                  | R/W         | STROBE         | This bit will generate a one clock cycle wide $\overline{SO}$ strobe each time it is set. STROBE_MODE must be set before this bit is set and INT_MODE must be low. This bit must be cleared before a new strobe can be generated.                                                                                                                                                                                                                          |

| 7                                  | R/W         | REAL_FS        | Used in the real output mode to double the frame<br>rate. If this bit is not set in the real mode, then the<br>chip will operate in the GC1011 real output mode. In<br>the GC1011 mode two real samples are output<br>every frame and the frame rate remains the same<br>as in the complex mode. The I stream will output the<br>even indexed time samples (time=0,2,4,6,) and<br>the Q stream will output the odd time samples.                           |

The READY signal is used to capture output samples and to read them into an external processor. The user captures outputs by setting the READY bit and then waiting for the bit to be cleared by the chip. When the bit goes low the processor can read the samples out of the I and Q output registers described in

| GRAYCHIP,INC.               | - 21 -                          | NOVEMBER 24, 1992          |  |  |

|-----------------------------|---------------------------------|----------------------------|--|--|

| This designs of southing in | aformation which may be changed | at any time without nation |  |  |

This document contains information which may be changed at any time without notice

section 3.9. The processor can wait for READY to go low by either continuously reading this register, or it can use the interrupt output **INT** to tell it when the sample is ready. To use the interrupt output mode the user must tie the **SO**/**INT** output pin from the chip to an interrupt input of the processor and must set the INT\_MODE bit in this register. The processor can then capture samples by setting READY and then setting INT\_ENABLE (INT\_ENABLE should be set after READY in order to avoid a spurious interrupt due to the interrupt being enabled before READY has settled to its high state). The processor will be interrupted when READY goes low again. When it is interrupted the processor can turn off INT\_ENABLE, read the I/Q outputs, and then start over again.

The MISSED flag is provided to let the processor know if it has taken too long to read the I/Q samples before rearming the READY bit. If the processor wants to use the MISSED flag it should clear the flag the first time it sets the READY bit and then check it after setting the READY bit thereafter. The READY bit is set and the MISSED bit cleared by writing a 01(hex) to this register. The READY bit is set and the MISSED bit is left alone by writing a 03(hex) to this register. If interrupts are used, then the user should also set the INT\_MODE bit at the same time by writing an 11(hex) or 13(hex) to the register followed by a 1B(hex) to enable the interrupts.

The one-shot strobe is generated by turning INT\_MODE off, STROBE\_MODE on and STROBE off. **SO** strobes are then generated by setting the STROBE bit. This is done by writing a 20(hex) to this register followed by a 60(hex).

#### 3.8 CHECKSUM REGISTER

This read-only register stores the checksums generated in the diagnostic mode.

| ADDRESS 11: C | HECKSUM |

|---------------|---------|

|---------------|---------|

| <u>BIT</u> | TYPE | NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         |

|------------|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-7        | R    | CHECK[0:7] | The 8 bit checksum. The checksum is generated as<br>a non-linear feedback accumulation of the <b>BS</b> , <b>FS</b> ,<br><b>I</b> , and <b>Q</b> output bits. The current checksum is stored<br>in this register and the checksum generator is<br>cleared whenever the internal sync goes low (see<br>SS_MUX in Section 3.2 for the modes of the<br>internal sync). |

#### 3.9 I AND Q OUTPUT REGISTERS

These registers are used to capture output samples.

| ADDRESS 1         | 2: I-Output B    | Syte 0                |                                                                 |

|-------------------|------------------|-----------------------|-----------------------------------------------------------------|

| BIT               | <u>TYPE</u>      | NAME                  | DESCRIPTION                                                     |

| 0-7               | R                | I[0:7]                | Least significant 8 bits of the I output.                       |

| ADDRESS 1         | 3: I-Output B    | Syte 1                |                                                                 |

| BIT               | <u>TYPE</u>      | NAME                  | DESCRIPTION                                                     |

| 0-7               | R                | I[8:15]               | Most significant 8 bits of the I output.                        |

| ADDRESS 1         |                  |                       |                                                                 |

| ADDITEOU          | 4: Q-Output      | Byte 0                |                                                                 |

| BIT               | 4: Q-Output      | Byte 0<br><u>NAME</u> | DESCRIPTION                                                     |

|                   |                  | •                     | DESCRIPTION<br>Least significant 8 bits of the <b>Q</b> output. |

| <u>BIT</u>        | <u>TYPE</u><br>R | <u>NAME</u><br>Q[0:7] |                                                                 |

| <u>ВІТ</u><br>0-7 | <u>TYPE</u><br>R | <u>NAME</u><br>Q[0:7] |                                                                 |

The user reads the I and Q outputs through these read-only registers. The captured samples can be used for gain control, analysis, display, or diagnostics.

### 4.0 SPECIFICATIONS

#### 4.1 ABSOLUTE MAXIMUM RATINGS

Referenced to GND:

| PARAMETER        |                                          |      | <u>TYP</u> | MAX                  | <u>UNITS</u> |

|------------------|------------------------------------------|------|------------|----------------------|--------------|

| V <sub>CC</sub>  | DC Supply Voltage                        | -0.3 |            | 7                    | V            |

| V <sub>IN</sub>  | Input voltage (undershoot and overshoot) | -0.7 |            | V <sub>CC</sub> +0.7 | V            |

| T <sub>STG</sub> | Storage Temperature                      | -65  |            | 150                  | °C           |

| F <sub>CK</sub>  | Clock Rate <sup>1</sup>                  | 10   |            |                      | Hz           |

#### 4.2 RECOMMENDED OPERATING CONDITIONS

| PARAMETER       |                                  | MIN | <u>TYP</u> | MAX | <u>UNITS</u> |

|-----------------|----------------------------------|-----|------------|-----|--------------|

| V <sub>CC</sub> | DC Supply Voltage                | 3.0 | 5.0        | 6.0 | V            |

| T <sub>A</sub>  | Temperature Ambient, no air flow | 0   |            | 60  | °C           |

#### 4.3 DC CHARACTERISTICS

All parameters are at V\_{CC}=5V and temperature is 0 to 60  $^\circ \rm C$  ambient unless noted

| PARAM            | ETER                                         |                             | <u>MIN</u>     | <u>TYP</u> | <u>MAX</u> | <u>UNITS</u> |

|------------------|----------------------------------------------|-----------------------------|----------------|------------|------------|--------------|

| V <sub>IL</sub>  | Voltage input low                            |                             |                |            | 0.8        | V            |

| V <sub>IH</sub>  | Voltage input high                           | V <sub>CC</sub> =5V         | 2.0            |            |            | V            |

|                  |                                              | V <sub>CC</sub> =3.3V       | 1.5            |            |            | V            |

| I <sub>IN</sub>  | Input current (V <sub>IN</sub> =0V)          |                             |                | +/-50      |            | μA           |

| V <sub>OL</sub>  | Voltage output low (I <sub>OL</sub> = 4mA)   |                             |                |            | 0.5        | V            |

| V <sub>OH</sub>  | Voltage output high (I <sub>OH</sub> = -4ma) | V <sub>CC</sub> =5V         | 2.5            |            | 5          | V            |

|                  |                                              | V <sub>CC</sub> =3.3V       | 1.5            |            | 3.3        | V            |

| C <sub>IN</sub>  | Data input capacitance (All inputs ex        | cept <b>CK</b> and <b>C</b> | <b>[0:7]</b> ) | 4          |            | pF           |

| C <sub>CK</sub>  | Clock input capacitance (CK input)           |                             |                | 8          |            | pF           |

| C <sub>CON</sub> | Control data capacitance (C[0:7] I/C         | ) pins)                     |                | 6          |            | pF           |

1. The chip may be damaged if power is applied for more than 1 second and the clock is below this rate.

This document contains information which may be changed at any time without notice

#### 4.4 AC CHARACTERISTICS

Commercial temperature range (0 to  $60^{\circ}$ C), V<sub>CC</sub> +/- 5%, unless noted.

| PARA              | METER                                                   |                                      |                                        |                       | MIN        | <u>TYP</u> | MAX      | <u>UNITS</u> |

|-------------------|---------------------------------------------------------|--------------------------------------|----------------------------------------|-----------------------|------------|------------|----------|--------------|

| F <sub>СК</sub>   | Clock frequency <sup>1</sup>                            | GC1011A                              | V <sub>CC</sub> =                      | 5v<br>3.3v            | 0.1<br>0.1 |            | 70<br>42 | MHz          |

|                   |                                                         | GC1011                               | V <sub>CC</sub> =                      | 5v<br>3.3v            | 20<br>0.1  |            | 70<br>42 | MHz          |

| t <sub>CKL</sub>  | Clock low period (I                                     | Below V <sub>IL</sub> )              | V <sub>CC</sub> =                      | 5v<br>3.3V            | 6<br>10    |            |          | ns           |

| t <sub>СКН</sub>  | Clock high period                                       | (Above V <sub>IH</sub> )             | V <sub>CC</sub> =                      | 5v<br>3.3v            | 6<br>10    |            |          | ns           |

| t <sub>SU</sub>   | Data setup ( <b>X</b> , <b>AS</b> ,                     | or <b>SS</b> ) before                | CK goes<br>V <sub>CC</sub> =           | -                     | 2<br>4     |            |          | ns           |

| t <sub>HD</sub>   | Data hold time (X,                                      | AS, or SS) afte                      | er <b>CK</b> go                        | es high               | 0          |            |          | ns           |

| t <sub>DLY</sub>  | Data output delay                                       | (I, Q, BS, FS,                       | or <b>SO</b> ) fr<br>V <sub>CC</sub> = |                       |            |            | 9<br>14  | ns           |

| t <sub>CSU</sub>  | Control setup befo ( <b>A</b> , <b>R/W</b> during read, |                                      |                                        | write)                | 5          |            |          | ns           |

| t <sub>CHD</sub>  | Control hold after ( <b>A</b> , <b>R/W</b> during read  |                                      | <b>C</b> during                        | g write)              | 5          |            |          | ns           |

| t <sub>CSPW</sub> | Control strobe puls                                     | se width (Write                      | e operatio                             | on)                   | 20         |            |          | ns           |

| t <sub>CDLY</sub> | Control output dela (Read operation)                    | ay to <b>C</b> after <b>C</b>        | <b>S</b> goes lo                       | ow <sup>3</sup>       |            |            | 30       | ns           |

| t <sub>CZ</sub>   | Control tristate del                                    | ay after <b>CS</b> go                | oes high                               |                       |            |            | 10       | ns           |

| I <sub>CCQ</sub>  | Quiescent supply of                                     | current (V <sub>IN</sub> =0          | or $V_{CC}$ ,                          | F <sub>CK</sub> =100I | Hz)        |            | 200      | μA           |

| I <sub>CC</sub>   | Supply current (F <sub>C</sub>                          | <sub>K</sub> =50 MHz, V <sub>(</sub> | <sub>CC</sub> =5.0V,                   | <b>D</b> =64)         |            |            | 150      | mA           |

|                   |                                                         | ,                                    | VCC FO                                 | ск                    | 64         |            |          |              |

ICC (MAX) =  $\frac{\text{VCC}}{5}$   $\frac{\text{FCK}}{50'\text{M}}$  0.56 + 0.44  $\frac{64}{\text{'D}}$  150 mA

<sup>1.</sup> The chip may not operate properly at clock frequencies below MIN and above MAX,

**D** is the decimation ratio (see Section 3.6)

<sup>2.</sup> Capacitive output load is 20 pf. Delays are measured from the rising edge of the clock to the output level rising above  $V_{IH}$  or falling below  $V_{IL}$ .

<sup>3.</sup> Capacitive output load is 80 pf.

#### 5.0 APPLICATION NOTES

#### 5.1 POWER AND GROUND CONNECTIONS

The GC1011A chip is a very high performance chip which requires solid power and ground connections to avoid noise on the V<sub>CC</sub> and GND pins. If possible the GC1011A chip should be mounted on a circuit board with dedicated power and ground planes and with at least two decoupling capacitors (0.01 and 0.1  $\mu$ f) adjacent to each GC1011A chip. If dedicated power and ground planes are not possible, then the user should place decoupling capacitors adjacent to each V<sub>CC</sub> and GND pair.

#### **IMPORTANT**

The GC1011A chip may not operate properly if these power and ground guidelines are violated.

#### 5.2 STATIC SENSITIVE DEVICE

The GC1011A chip is fabricated in a high performance CMOS process which is sensitive to the high voltage transients caused by static electricity. These parts can be permanently damaged by static electricity and should only be handled in static free environments.

#### 5.3 70 MHZ OPERATION

Care must be taken in generating the clock when operating the GC1011A chip at its full 70 MHz clock rate. The user must insure that the clock is above 2 volts for at least 6 nanoseconds and is below 1 volt for at least 6 nanoseconds. At 70 MHz the clock period is only 14 nanoseconds so that the clock must have a duty cycle of exactly 50%, and the rise and fall times can only be one nanosecond each. One must also be careful to prevent clock undershoot below ground. An ideal clock at 70 MHz would be a square wave with a low voltage of 0.5 volts and a high voltage of 2.5 volts.

#### 5.4 REDUCED VOLTAGE OPERATION

The power consumed by the GC1011A chip can be greatly reduced by operating the chip at the lowest  $V_{CC}$  voltage which will meet the application's timing requirements. When operating at a reduced voltage, GRAYCHIP recommends driving the GC1011A chip inputs with the 5 volt to 3 volt interface chips sold by Performance Semiconductor.

#### 5.5 SYNCHRONIZING MULTIPLE GC1011A CHIPS

A system containing a bank of GC1011A chips will need to be synchronized so that the output frames from each chip are aligned, and, if desired, so that their frequency accumulators are running synchronously. The GC1000 Input Switch chip has built in sync counters which are designed specifically for this purpose. If the GC1000 chip is not used, then the one-shot strobe (see Section 3.7) can be used. The bank of chips should be interconnected so that the  $\overline{SO}$  pin of one GC1011A chip is tied to the  $\overline{SS}$  input of all of the chips. The one-shot strobe mode can then be used to simultaneously synchronize all of the chips. The one-shot mode of the second GC1011A chip should be tied to the  $\overline{AS}$  input of all of the chips. The one-shot mode of the second chip can be used to synchronize the frequency accumulators whenever the tuning frequency has been changed.

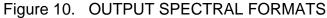

#### 5.6 PROCESSING COMPLEX DATA

Two GC1011A chips can be used to process complex input data by using one chip to process the I-input data and the other to process the Q-input data. If the two chips are synchronized as discussed above, then the complex output stream can be reconstructed by adding and subtracting the I and Q outputs of the two chips. A programmable gate array chip such as from XILINX would be ideal for this post-processing. The configuration for processing complex data is illustrated in Figure 11.

Figure 11. PROCESSING COMPLEX INPUT DATA

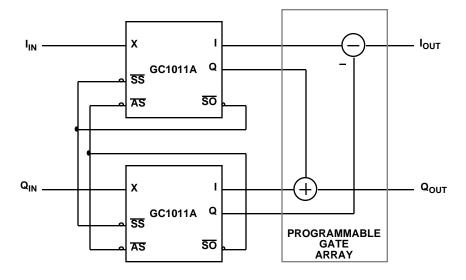

#### 5.7 EXAMPLE RECEIVER ARCHITECTURE

An example digital receiver architecture using the GC1011A chip is shown in Figure 12.

#### Figure 12. EXAMPLE DIGITAL RECEIVER ARCHITECTURE

The receiver contains an analog front end which downconverts up to 30MHz of radio spectrum to an IF frequency around 15MHz<sup>1</sup>. It also adjusts the gain of the signal so that it fills the dynamic range of the analog to digital converter (ADC). The ADC digitizes the signal to 8 or 10 bits<sup>2</sup> at a sampling rate of 60 MHZ. The GC1011A chip tunes, downconverts, and narrowband filters desired frequencies from within the 30 MHz band. The GC1011A output is then processed by a DSP chip for any final filtering, demodulation or signal analysis. The DSP chip also handles the user interface and provides tuning controls to the GC1011A chip and analog front end.

For applications which do not require the DSP chip at the back end, a simplified architecture can realized by replacing the DSP chip with an digital to analog converter.

<sup>1.</sup> Note that the HF spectrum (1 to 30MHz) can be digitized directly.

<sup>2.</sup> The GC1011A chip will accept a 12 bit ADC output as soon as 60 MHZ 12 bit ADCs are available.

2314 Ramona St. Palo Alto, CA. 94301

# GC1011A

## **DIGITAL RECEIVER CHIP**

## DATASHEET

Revised

November 24, 1992

This datasheet contains information which may be changed at any time without notice.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated