### 82353 Advanced Data Path

| <b>CONTENTS</b> PAGE                           | CONTENTS PAG                          |

|------------------------------------------------|---------------------------------------|

| 1.0 82353 BLOCK DIAGRAM 1-142                  | 6.0 FUNCTIONAL DIAGRAMS 1-16          |

| <b>2.0 INTRODUCTION</b> 1-143                  | 6.1 Single Read of Memory 1-16        |

|                                                | 6.2 Burst Read of Memory 1-16         |

| <b>3.0 QUICK REFERENCE</b> 1-143               | 6.3 Single Write of Memory 1-17       |

| 3.1 Pin Quick Reference 1-143                  | 6.4 Burst Write of Memory 1-17        |

| 3.2 Multiplexed Pin Listing 1-144              | 6.5 Host Read of System 1-18          |

| 4.0 82353 FUNCTIONAL                           | 6.6 HCLK 1x/2x 1-18                   |

| <b>DESCRIPTION</b> 1-145                       | 6.7 Host Latch Modes 1-18             |

| 4.1 Host Interface 1-147                       | 6.8 Parity Errors 1-18                |

| 4.1.1 Host Transparent Mode 1-147              | 7.0 ELECTRICAL                        |

| 4.1.2 Host Clocked Mode 1-149                  | CHARACTERISTICS 1-18                  |

| 4.1.3 Host 82385 Mode 1-150                    | 7.1 D.C. Specifications 1-18          |

| 4.2 System Interface 1-150                     | 7.1.1 Absolute Maximum                |

| 4.2.1 Buffered Mode 1-151                      | Ratings 1-18                          |

| 4.2.2 Standard Mode 1-152                      | 7.1.2 D.C. Characteristics 1-16       |

| 4.3 Memory Interface 1-153                     | 7.2 A.C. Specifications 1-18          |

| 4.3.1 Memory Write Interface 1-153             | 7.3 Driver Characterization Data 1-20 |

| 4.3.2 Memory Read Interface 1-154              | 7.3.1 Capacitive Derating Curve 1-20  |

| 5.0 DETAILED PIN DESCRIPTIONS 1-158            | 7.3.2 Output V/I Plots 1-20           |

| 5.1 Host Interface 1-158                       | 8.0 DEVICE PINOUT INFORMATION 1-2     |

| 5.1.1 Host Pins Available to All               | 8.1 Pin Listing (Numerical Order) 1-2 |

| Modes 1-158                                    | 8.2 Pin List (Alphabetical Order) 1-2 |

| 5.1.2 Transparent Mode Pins 1-160              | 8.3 Pinout Diagram 1-2                |

| 5.1.3 Clock Mode Pins 1-161                    | 9.0 THERMAL SPECIFICATIONS 1-2        |

| 5.1.4 82385 Mode Pins 1-161                    | 9.0 THERMAL SPECIFICATIONS 1-2        |

| 5.2 System Interface 1-162                     | 10.0 REVISION SUMMARY 1-2             |

| 5.2.1 System Pins Available in Both Modes1-162 |                                       |

| 5.2.2 Standard Mode Pins 1-163                 |                                       |

| 5.2.3 Buffered Mode Pins 1-164                 |                                       |

| 5.3 Memory Interface 1-165                     |                                       |

#### 1.0 82353 BLOCK DIAGRAM

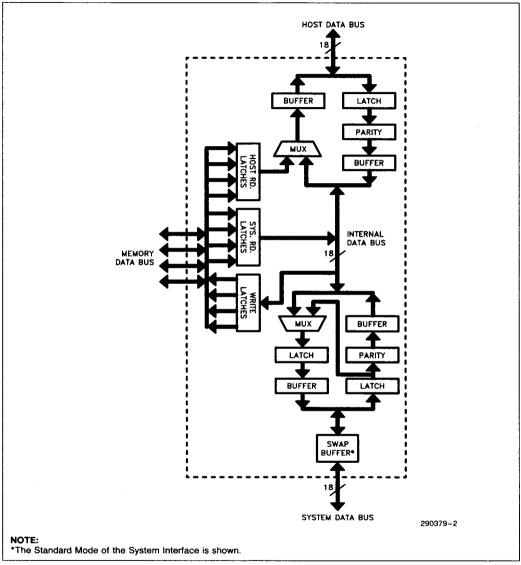

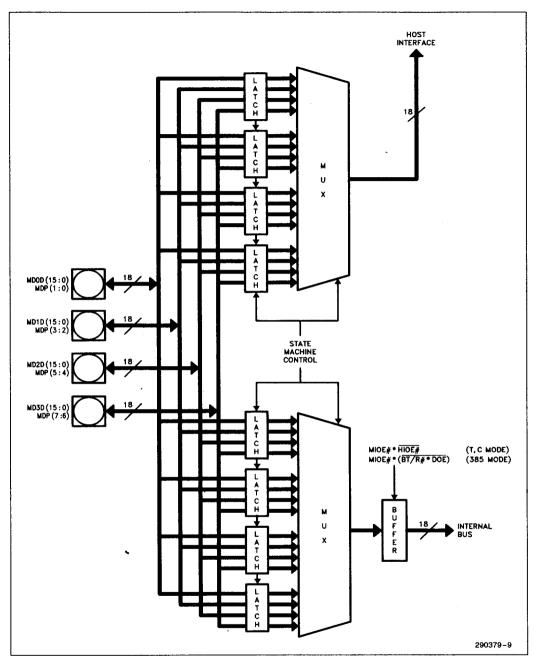

The following illustration is a simplified block diagram of the 82353 Advanced Data Path. It is provided for conceptual purposes only.

Figure 1.1. 82353 Internal Block Diagram

#### l Mama

#### 2.0 INTRODUCTION

The 82353 Advanced Data Path (ADP), works closely with the 82359 EISA DRAM Controller to provide an extremely flexible system conforming to the EISA bus specification.

The 82353 ADP and associated 82359 DRAM Controller provide a unique bus structure, utilizing two distinct electrically isolated buses. One bus, labeled "Host Bus", accommodates the host CPU/cache combination. The second bus, labeled "System Bus", accommodates standard I/O and add-in peripherals and follows EISA timings. Each of the busses have their own address/data path to main memory.

The 82353 provides a dual ported data path between the system and host data bus to the DRAM data bus. This dual ported architecture allows accesses to DRAM by host masters without incurring arbitration. Integrated into the 82353 are first and second level posted write latches to support zero wait state writes. A burst read or write capability of up to 16 sequential words is provided.

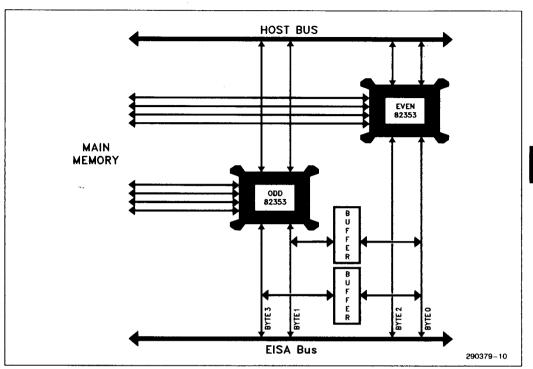

A single 82353 is a 16-bit data path slice which interfaces to 16-bit host and system data buses. The intent of the 82353 is for two 82353's to be connected in parallel, providing a 32-bit host and system data bus and 32, 64, or 128-bit wide two-way DRAM memory structure. In fact, any number of 82353s can be used in parallel to implement busses in 16-bit multiples.

The DRAM memory structure is very flexible allowing the designer to achieve the desired price/performance objectives. DRAM SIMMs of 64K, 256K, 1M, and 4M in address depth and speeds of 60, 70, 80, or 100 ns are supported in a "mix and match" arrangement, allowing memory expansion without discarding different size or speed memory devices.

#### 3.1 Pin Quick Reference

3.0 QUICK REFERENCE

| Signal Name        | 1/0 | Pin #  | Full Signal Name               |  |

|--------------------|-----|--------|--------------------------------|--|

| HOST BUS INTERFACE |     |        |                                |  |

| HD(15:0)           | 1/0 | Note A | Host Data                      |  |

| HPD(1:0)           | 1/0 | 40, 41 | Host Parity Data               |  |

| HAS#               |     | 73     | Host Address Strobe            |  |

| HARDY              | 0   | 75     | Host Asynchronous<br>Ready     |  |

| HBRDY#             | ı   | 67     | Host Burst Ready               |  |

| HCK1/2X#           | 1   | 69     | Host Clock Select              |  |

| HCLK               | 1   | 68     | Host Clock                     |  |

| HINTPAR            | 1   | 66     | Host Internal Parity<br>Select |  |

| HIOE#              | ı   | 71     | Host Internal Output<br>Enable |  |

| HRD#               | 1   | 63     | Host Read                      |  |

| HOE#               | 1   | 70     | Host Output Enable             |  |

| HRST               | ı   | 64     | Host Reset                     |  |

| HWLE#              | ļ   | 65     | Host Write Latch<br>Enable     |  |

| HWCLKEN#           | j   | 65     | Host Write Clock<br>Enable     |  |

| PERSTB#            | 0   | 74     | Parity Error Strobe            |  |

| BT/R#              | ı   | 71     | 82385 BT/R#                    |  |

| HLDSTB             | 1   | 63     | Host Local Data<br>Strobe      |  |

| DOE#               | 1   | 70     | Data Output Enable             |  |

#### 3.1 Pin Quick Reference (Continued)

| Signal Name          | 1/0 | Pin #  | Full Signal Name                                  |

|----------------------|-----|--------|---------------------------------------------------|

| SYSTEM BUS INTERFACE |     |        |                                                   |

| SD(15:0)             | 1/0 | Note B | System Data                                       |

| SPD(1:0)             | 1/0 | 14, 15 | System Parity Data                                |

| IDSDLE#              | I   | 5      | Internal Data to<br>System Data Latch<br>Enable   |

| SAS#                 | ١   | 4      | System Address<br>Strobe                          |

| SBRDY#               | 1   | 10     | System Burst Ready                                |

| SCLK                 | -   | 11     | System Clock                                      |

| SDIDLE#              | ı   | 9      | System to Internal<br>Data Latch Enable<br>(Word) |

| SDIDLE(1:0)#         | ı   | 14, 15 | System to Internal<br>Data Latch Enable<br>(Byte) |

| SDVLD                | 1   | 13     | System Data Valid<br>Strobe                       |

| SINTPAR              | ı   | 12     | System Internal<br>Parity Select                  |

| SOE#                 | ı   | 8      | System Output<br>Enable (Word)                    |

| SOE0#                | +   | 12     | System Output<br>Enable Byte 0                    |

| SOE1#                | 1   | 11     | System Output<br>Enable Byte 1                    |

| CPYEN#               | 1   | 10     | Copy Enable                                       |

| CPYUP                | 1   | 9      | Сору Uр                                           |

| SIOE#                | ı   | 8      | System Internal<br>Output Enable                  |

| RESIST               | ı   | 6      | Reference Resistor                                |

| Signal Name | 1/0                     | Pin #                       | Full Signal Name                 |  |  |

|-------------|-------------------------|-----------------------------|----------------------------------|--|--|

| MEMORY MO   | MEMORY MODULE INTERFACE |                             |                                  |  |  |

| MPD(7:0)    | 1/0                     | Note C                      | Memory Parity Data               |  |  |

| MD0D(15:0)  | 1/0                     | Note D                      | Memory Data 0                    |  |  |

| MD1D(15:0)  | 1/0                     | Note E                      | Memory Data 1                    |  |  |

| MD2D(15:0)  | 1/0                     | Note F                      | Memory Data 2                    |  |  |

| MD3D(15:0)  | 1/0                     | Note G                      | Memory Data 3                    |  |  |

| H/S#        | I                       | 2                           | Host/System Port<br>Select       |  |  |

| IF(1:0)     | 1                       | 80, 79                      | Interleave Factor                |  |  |

| MDS#        | 1                       | 76                          | Memory Data Strobe               |  |  |

| MIOE#       | 1                       | 1                           | Memory Internal<br>Output Enable |  |  |

| MWLS#       | ı                       | 164                         | Memory Write Latch<br>Select     |  |  |

| PER#        | 0                       | 3                           | Parity Error                     |  |  |

| SEL(1:0)    | ı                       | 78, 77                      | Selects                          |  |  |

| WE(3:0) #   | I                       | 145,<br>144,<br>104,<br>103 | Write Enables                    |  |  |

#### NOTES:

A. 42, 46, 48, 50, 52, 54, 58, 60, 43, 47, 49, 51, 53, 55, 59,

B. 16, 19, 23, 25, 29, 32, 35, 38, 17, 20, 24, 27, 30, 33, 37,

C. 162, 158, 161, 157, 160, 156, 159, 155.

D. 150, 140, 132, 123, 113, 105, 95, 86, 146, 136, 127, 118, 109, 99, 91, 82.

E. 151, 141, 133, 124, 114, 106, 96, 87, 147, 137, 128,

119, 110, 100, 92, 83. F. 152, 142, 134, 125, 115, 107, 97, 88, 148, 138, 129,

120, 111, 101, 93, 84. G. 153, 143, 135, 126, 116, 108, 98, 89, 149, 139, 130, 121, 112, 102, 94, 85.

#### 3.2 Multiplexed Pin Listing

Due to the large number of pins required by the 82353, and the fact that not all signals are used in every mode of operation, some of the pins are multiplexed. This means that a given pin may have more than one function dependent upon which mode of operation is selected.

The following tables show which 82353 signals are available in each of the three host modes and each of the two system modes. An "X" indicates that the corresponding signal name is used in that mode.

| Signal   | Host Interface Mode |            |       | Multiplexed |

|----------|---------------------|------------|-------|-------------|

| Name     | Transparent         | Clocked    | 82385 | Pin         |

| HD(15:0) | Х                   | Х          | Х     |             |

| HPD(1:0) | l x                 | X          | l x   |             |

| HAS#     | l x                 | X          | l x   |             |

| HARDY    | l x                 | X          | ×     |             |

| HBRDY#   | l x                 | , <b>X</b> | ×     |             |

| HCK1/2X# | X                   | ×          | ×     |             |

| HCLK     | l x                 | X          | ×     |             |

| HINTPAR  | x                   | ×          | ×     |             |

| PERSTB#  | X                   | X          | ×     |             |

| HRST     | X                   | X          | ×     |             |

| HIOE#    | X                   | X          |       | •           |

| HRD#     | X                   | X          |       | *           |

| HOE#     | l x                 | ×          |       | *           |

| HWLE#    | X                   |            |       | *           |

| HWCLKEN# |                     | x          |       | *           |

| BT/R#    |                     |            | ×     | *           |

| DOE#     |                     |            | ×     | *           |

| HLDSTB   |                     |            | ×     | •           |

<sup>&</sup>quot;x" indicates this pin is available in this mode of operation.

<sup>\*</sup>Pin provides a multiplexed signal dependent upon which one of three Host modes is selected.

| Multiplexed Host Signal Combinations |          |            |  |

|--------------------------------------|----------|------------|--|

| Transparent                          | Clocked  | 82385      |  |

| HIOE#                                | HIOE#    | BT/R#      |  |

| HRD#                                 | HRD#     | HLDSTB     |  |

| HOE#                                 | HOE#     | DOE#       |  |

| HWLE#                                | HWCLKEN# | (Reserved) |  |

| Signal<br>Name | Sys<br>Interfac | Multiplexed<br>Pin |      |

|----------------|-----------------|--------------------|------|

| Name           | Standard        | Buffered           | Fili |

| SD(15:0)       | Х               | Х                  |      |

| IDSDLE#        | ×               | ×                  |      |

| SDVLD          | ×               | ×                  |      |

| SIOE#          | X               |                    |      |

| CPYEN#         | ×               |                    | •    |

| CPYUP          | ×               |                    | *    |

| SDIDLE(1:0)#   | ×               |                    | *    |

| SOE(1:0)#      | ×               |                    | *    |

| SPD(1:0)       |                 | ×                  | *    |

| SAS#           |                 | ×                  | *    |

| SBRDY#         |                 | ×                  | *    |

| SCLK           |                 | ×                  | *    |

| SDIDLE#        |                 | ×                  | *    |

| SINTPAR        |                 | ×                  | *    |

| SOE#           |                 | X                  | *    |

| Multiplexed System Signal Combinations |               |  |  |

|----------------------------------------|---------------|--|--|

| Standard Mode                          | Buffered Mode |  |  |

| SDIDLE(1:0)#                           | SPD(1:0)      |  |  |

| CPYEN#                                 | SBRDY#        |  |  |

| SOE0# SINTPAR                          |               |  |  |

| SOE1# SCLK                             |               |  |  |

| CPYUP SDIDLE#                          |               |  |  |

| (Reserved) SAS#                        |               |  |  |

| SIOE#                                  | SOE#          |  |  |

## 4.0 82353 FUNCTIONAL DESCRIPTION

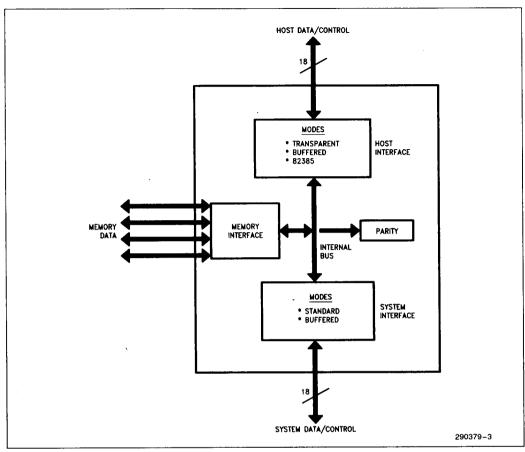

The internal structure of the 82353 consists of four functional blocks as shown in Figure 4.1. Three of these blocks interface the 82353 to the external host, system and memory busses. The fourth block's function is for parity checking.

Figure 4.1. 82353 Functional Blocks

These blocks are connected together through the 82353's internal bus. This bus is 18-bits wide and consists of 16 data bits and two parity bits. It is through this bus that data is transferred between the host, system and memory interfaces.

The host interface is responsible for transferring data between the 82353's internal bus and the host Bus. This interface has three modes of operation, each differing in the way data is latched off the host bus. These three modes, labeled "Transparent Mode", "Clocked Mode", and "82385 Mode", allow the 82353 to perform optimally for a wide variety of system designs.

The system interface is responsible for data transfers between the system and the internal bus. The 82353 has two modes of operation. The standard mode incorporates internal latches and swap buffers for byte assembly and disassembly operations. It also internally generates parity for system-to-memory or system-to-host data transfers. The incorporation of the assembly/disassembly and parity generation logic make this mode ideally suited for a direct connection to the EISA bus. The buffered mode disables the internal latches and swap buffers and incorporates a burst bus similar to the host interface. In the buffered mode, the 82353 also provides the option for parity to be generated internally or externally. This mode of operation is ideal for a custom-

ized system bus that supports high performance pe-

ripherals with a "i486-like" burst capability.

The memory interface is responsible for transferring data between the internal bus and the external DRAMS. It can support a 16, 32, or 64-bit memory data bus. This block also supports burst reads or writes of up to 16 words in length in zero wait states.

During memory accesses, the parity checking circuit monitors the word of data on the internal bus and its associated two parity bits (one parity bit per byte). All parity errors which occur are indicated to external circuitry via a synchronous and an asynchronous parity error signal.

#### 4.1 Host Interface

The host interface has three user selectable modes: Transparent Mode, Clocked Mode, and 82385 Mode. These three modes allow the system designer to have plenty of flexibility in designing the host subsection and allow the 82353 to achieve very high performance with various types of host CPUs.

The 82353 determines which mode to operate in by sampling HRD#//HLDSTB and HWCLKEN#// HWLE# pins on the falling edge of HRST (Host Reset). Table 4.1 lists the state of these pins at reset time to select the appropriate mode.

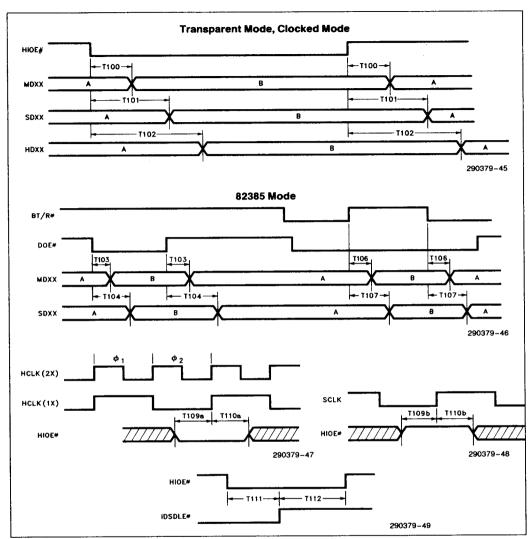

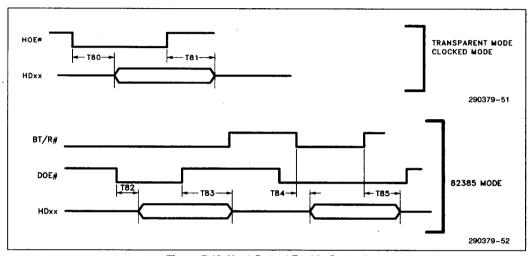

These three modes differ primarily in the way the 82353 transfers data to/from the host bus. Transparent Mode captures its data from the host bus on the rising edge of HWLE# and provides data to the host Bus when HOE# is low. Clocked Mode is very similar to transparent Mode and differs only in that it uses HWCLKEN# qualified by HCLK to latch data from the host bus. The 82385 Mode allows the 82353 to support systems utilizing the 82385 Cache Controller. In this mode, the 82385 signals BT/R#, LDSTB and DOE# control both the latching and driving of data to/from the host Bus. A full discussion and conceptual diagram of each of the three modes follows.

Although 82385 mode specifically interfaces to the 82385 Cache Controller, a variety of cache configurations are supported by using either clocked or transparent mode, including the 485Turbocache and 82395 DX Smart Cache Cache Controllers.

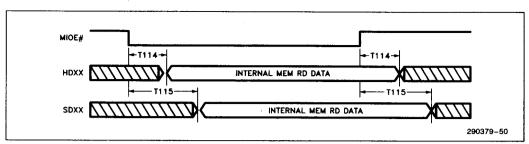

The host interface drives data onto the host bus under control of the HOE# signal. The source of this data is determined by the state of MIOE #. If MIOE # is asserted, data from the memory read latches will be driven; if de-asserted, data from the system interface will be driven.

Table 4-1. Selection of Host Interface Modes

| 1                | e at Falling<br>e of HRST | Mode             |  |

|------------------|---------------------------|------------------|--|

| HRD#//<br>HLDSTB | HWCLKEN#//<br>HWLE#       |                  |  |

| 1                | 0                         | Transparent Mode |  |

| 1                | 1                         | Clocked Mode     |  |

| 0                | ×                         | 82385 Mode       |  |

x = "Don't Care"

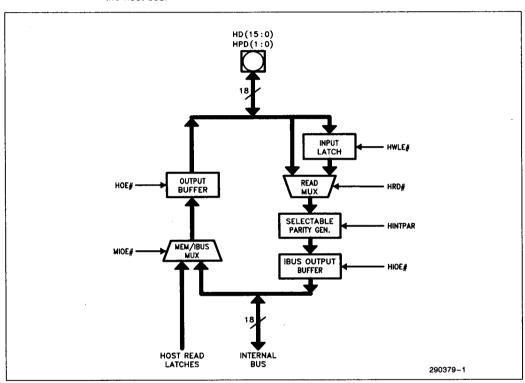

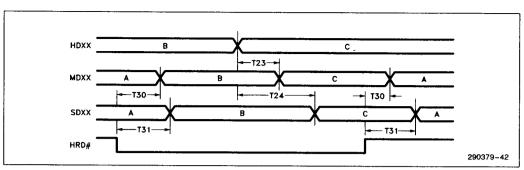

#### 4.1.1 HOST TRANSPARENT MODE

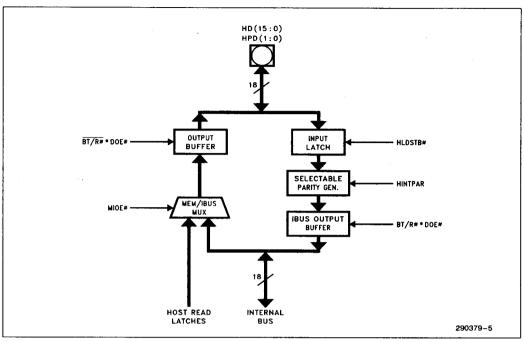

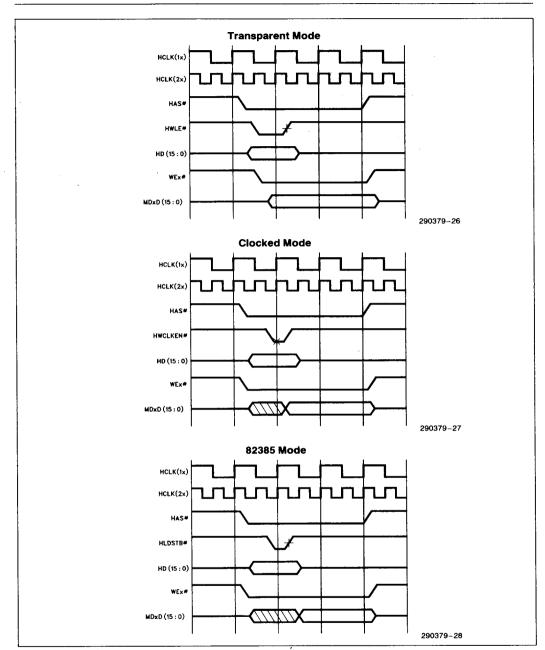

Figure 4.2 shows a conceptual diagram of the host interface in Transparent Mode. Transparent Mode differs from the other host modes in the way it latches data from the host bus. Data is latched into the host interface on the rising edge of HWLE# asynchronous to HCLK.

Host Input Latch

The Host Input Latch is used for capturing data from the host bus. This is closed on the

rising edge of HWLE#.

Host Read Mux

The Host Read Mux is used for selecting data from directly off the host bus or data from the Host Input Latch. Reading the Host bus directly is provided for designs which may incorporate slaves on the host bus

(typically not used).

#### **Selectable Parity** Generator

The Selectable Parity Generator provides parity generation for devices on the host bus which do not provide their own parity. If HINTPAR is asserted. the 82353 will internally generate parity for the host data and ignore any parity information on the host parity inputs (HPD(1:0)).

IBus Output Buffer The IBus (internal bus) Output Buffer controls the driving of host data onto the internal bus. Data and parity information from the host interface will be driven when HIOE# is assert-

Mem/IBus Mux

The Mem/IBus Mux selects between the memory interface and the internal bus for its source of data to be sent to the host bus.

Host Output Buffer The Host Output Buffer controls the driving of data onto the host bus. Data and parity information from the host Interface will be driven to the host bus when HOE# is asserted.

Figure 4.2. Host Transparent Mode

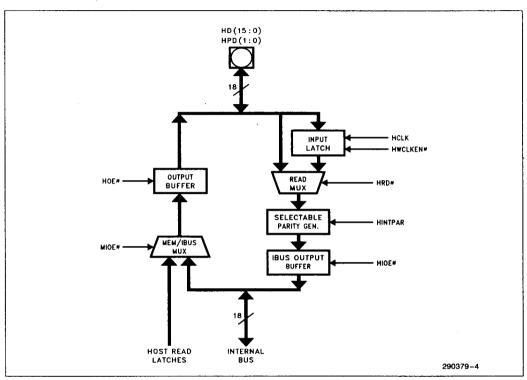

#### 4.1.2 HOST CLOCKED MODE

Clocked Mode is very similar to the Transparent Mode except for one point. In this mode, host data off the host bus will be latched into the 82353 on HCLK's rising edge qualified by HWCLKEN# (Host Write Clock Enable) asserted.

Host Read Mux, Selectable Parity Generator, IBus Output Buffer, Mem/IBus Mux, and Host Output Buffer function as in Transparent Mode.

Figure 4.3. Clocked Host Mode

#### 4.1.3 HOST 82385 MODE

Figure 4.4 shows a conceptual diagram of 82385 Mode of the host interface. The 82385 mode provides the optimum interface for systems utilizing the 82385 Cache Controller. In this mode, host data is latched off the host bus on the rising edge of HLDSTB#. (HLDSTB# should be connected directly to the 82385 LDSTB# signal.) The data is driven from the host interface onto the internal bus or host bus under control of BT/R# and DOE#, both of which should be connected to the 82385 signals of the same name.

**Host Input Latch**

The Host Input Latch is used for capturing data from the host bus. This latch is closed on the risina edae of HLDSTB#.

IBus Output Buffer The IBus Output Buffer con-

trols the driving of Host data onto the 82353's internal bus. Data and parity information from the host interface will be driven when the 82385 signal BT/R# is asserted (one) and DOE# is asserted.

Host Output Buffer The Host Output Buffer controls the driving of data onto the host bus. Data and parity information from the host interface will be driven to the host bus when BT/R# is deasserted (zero) and DOE# is asserted.

The Selectable Parity Generator and Mem/IBus MUX function exactly the same as Clocked and Transparent Mode.

#### 4.2 System Interface

The System Interface can take on one of two modes of operation: Standard Mode or Buffered Mode. The desired mode is selected at reset time by state of HINTPAR when HRST is asserted. The differences between the two modes are summarized in Table 4-2

Table 4-2. System Mode Differences

| Standard Mode                             | Buffered Mode                 |

|-------------------------------------------|-------------------------------|

| (HINTPAR = 0 at HRST)                     | (HINTPAR = 1 at HRST)         |

| System Master Can Not                     | System Master May             |

| Provide Parity                            | Provide Parity                |

| Parity Automatically                      | Parity Can Be Generated       |

| Generated                                 | "i486-Like" System Burst      |

| "i486-Like" System Burst<br>NOT Supported | Supported Word Output Enables |

| Byte Output Enables                       | Swap Buffers NOT              |

| Swap Buffers Provided                     | Provided                      |

Implementing two different modes, and the signals associated with these modes, requires that several of the system interface pins be multiplexed. These multiplex pins will have different signal names and functions dependent upon which system mode is selected. Table 4-3 lists the system signals which use a multiplexed pin.

Table 4-3. System Multiplexed Signals

| Buffered Mode |

|---------------|

| SPD(1:0)      |

| SBRDY#        |

| SINTPAR       |

| SCLK          |

| SDIDLE#       |

| SAS#          |

| SOE#          |

|               |

Figure 4.4. 82385 Host Mode

#### 4.2.1 BUFFERED MODE

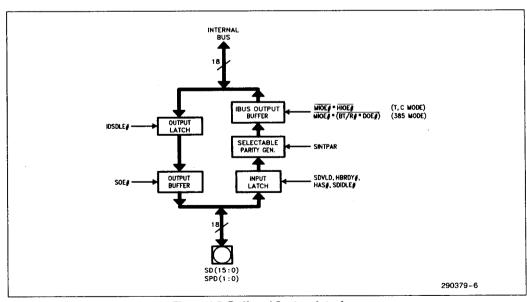

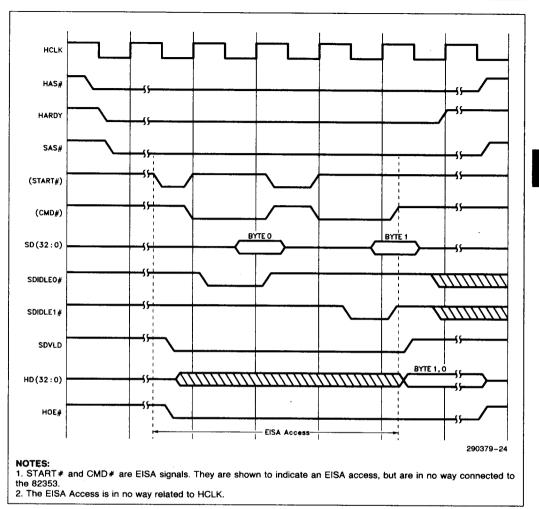

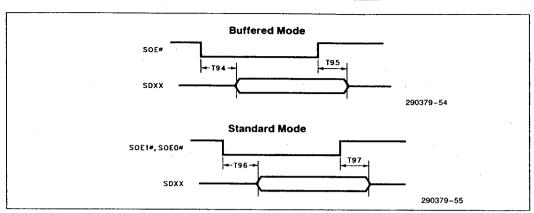

Figure 4.5 presents the conceptual block diagram of the Buffered Mode. The Buffered Mode is used when the system design implements a buffered bus separated from the EISA bus. This mode of operation provides the system designer with the choice of having parity generated by the 82353 or allowing the system device to provide its own parity. In addition, Buffered Mode supports the Buffered bus for "i486like" burst transfers. Since this bus is intended to be used with masters which are the same width as the bus, Buffered Mode does not support internal byte swapping.

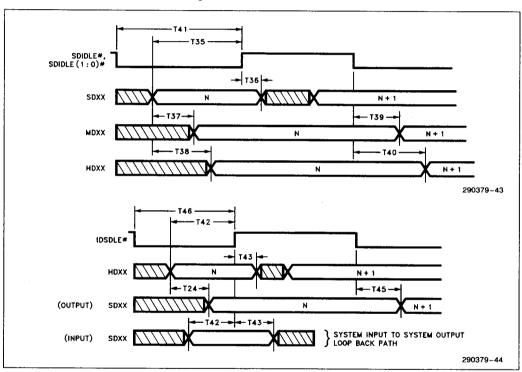

#### System Input Latch

The System Input Latch consists of one 16-bit latch under control of SDIDLE#. This provides for latching data into the 82353 from the system bus. SDVLD, HBRDY#, and HAS# are used during system-to-host transfers for holding system data in the System Input Latch until the host has had a chance to read

#### Selectable The Selectable Parity Generator will **Parity** Generator

generate parity for system devices which do not provide their own. If SINT-PAR is asserted, parity will be generated by the 82353 and any parity data provided by the system device will be ignored.

#### **IBus** Output Buffer

The IBus Output Buffer allows data from the system interface to be driven onto the 82353's internal bus. Data and parity information is driven when MIOE# and HIOE# are both de-assert-

#### System Output Latch

The System Output Latch is used for latching data bound for the system bus. The data is latched under control of IDSDLE#.

#### System Output Buffer

The System Output Buffer controls the re-driving of system data back to the system bus. Unlike Standard Mode, this buffer is 16-bits wide and is under control of SOE#.

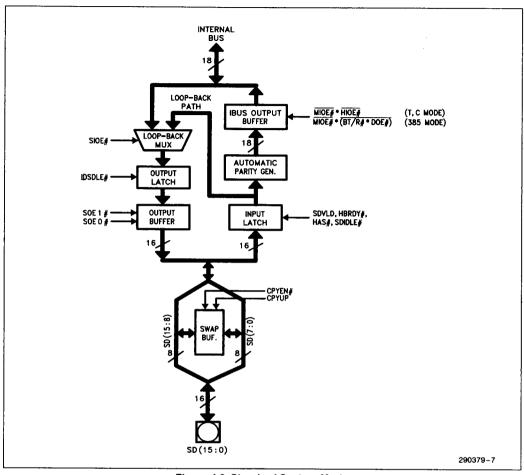

#### 4.2.2 STANDARD MODE

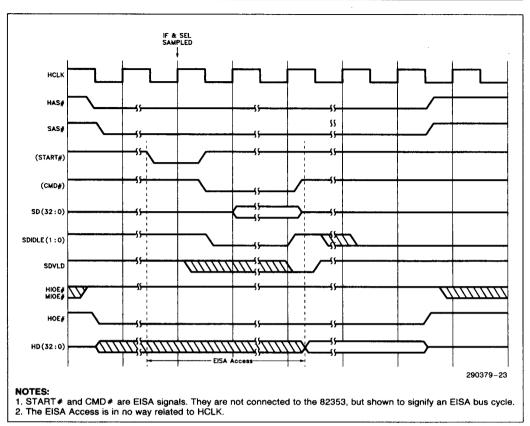

The Standard Mode conceptual diagram is shown in Figure 4.6. Standard Mode is used when the Buffered Bus is not implemented, and the system port is directly connected to the EISA bus. The Standard Mode incorporates internal swap buffers, byte-wide output enables, byte assembly, and automatic parity generation but does not support "i486-like" system port burst transfers (although EISA Burst transfers are supported.)

#### Swap Buffer

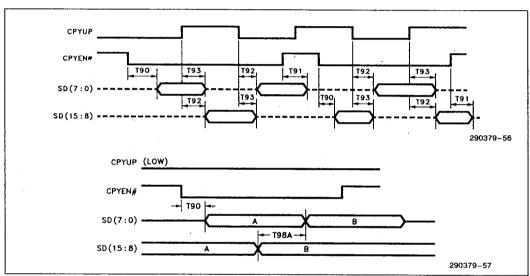

All transfers from the system port originate with the data entering the swap buffer structure and appearing at the System Input Latch. The swap buffer allows data appearing on either the high byte or the low byte of the system bus to be placed on the opposing byte's data lines. Swapping is enabled under control of CPYEN# and the direction of the swap is determined by the state of CPYUP. (The implementation of the 32-bit EISA bus requires that two 82353 devices be used and that external hardware be implemented to perform part of the byte swap logic. See Figure 4.9 for details.)

#### System Input Latch

The System Input Latch consists of two 8-bit latches, the upper under control of SDIDLE1# and the lower under control of SDIDLEO#. These provide for latching data into the 82353 from the system bus. Since each 8-bit latch has its own

control signal, these latches, along with the swap buffers, may be used for byte assembly. SDVLD. HBRDY#, and HAS# are used during system to host transfers for holding system data in the System Input Latch until the host has had a chance to read it.

#### **Parity** Generator

Automatic The Automatic Parity Generator will generate parity for all data bound for either main memory or the host bus. Unlike Buffered Mode, there is no provision for system devices to provide their own parity.

#### **IBus** Output **Buffer**

The IBus Output Buffer allows data from the system interface to be driven onto the 82353's internal bus. Data and parity information is driven when MIOE# and HIOE # are both de-asserted.

#### Loop-Back Mux

The System Loop-Back Mux selects either the loop-back path (used for byte assembly and re-drive) or the 82353's internal bus (main memory or host bus data) to supply data to be driven to the system bus.

#### System Output Latch

The System Output Latch is used for latching data bound for the system bus. The data is latched under control of IDSDLE#.

#### System Output Buffer

The System Output Buffers control driving data to the system bus. These buffers are each byte-wide and are under control of SOE1# and SOE0#.

Figure 4.5. Buffered System Interface

1-152

Figure 4.6. Standard System Mode

#### 4.3 Memory Interface

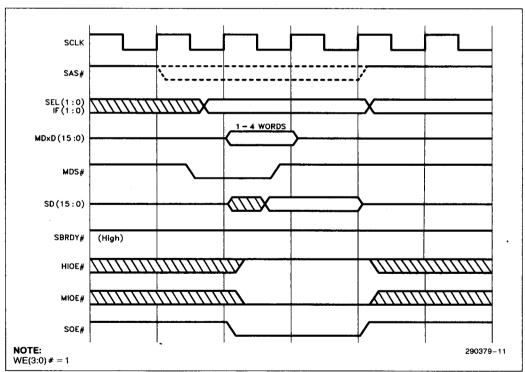

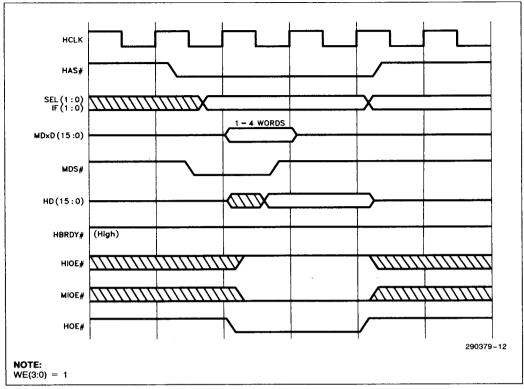

As shown in Figure 4.1, the memory interface is divided into two halves: the read interface and the write interface. The purpose of these interfaces is to route data between the internal bus and the DRAM data lines. The memory interface provides single cycle or burst, read and write capability to a one, two or four word-wide main memory bus.

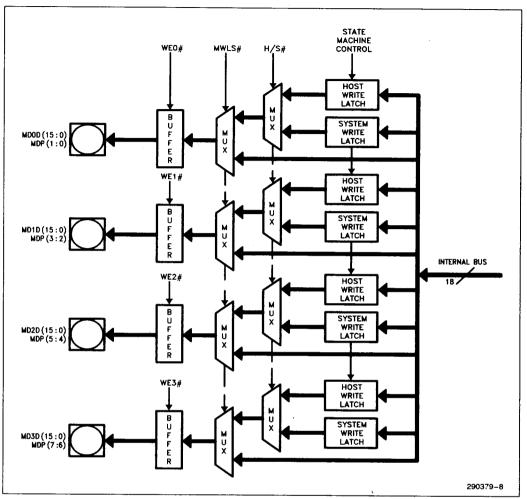

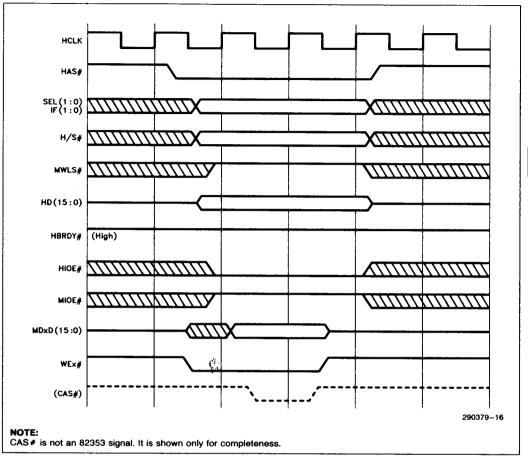

#### 4.3.1 MEMORY WRITE INTERFACE

The conceptual memory write interface is shown in Figure 4.7. The second level posted write latches can be seen at the right hand side. Separate write latches are provided for host and system words,

both receiving their data from the internal bus. These latches are under control of the internal state machines

Following the write latches are the H/S# muxes. These muxes are under control of the H/S# signal (from the 82359 DRAM Controller) and their purpose is to select either the host or system write latch.

The data selected by the H/S# mux enter a second level of muxes which selects data from the write latches or directly off the internal bus. The write latches are used only during burst writes; single cycle write data takes the faster route past the write latches and H/S# mux directly to the output buffers.

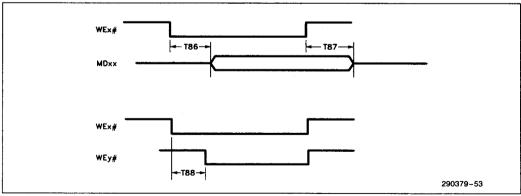

The write data is placed on the DRAM data lines by the write enable buffers. WE(3:0) #, asserted by the 82359, control which combination of data words are presented to the DRAM and when each will be driven.

#### 4.3.2 MEMORY READ INTERFACE

The conceptual Memory Read Interface is shown in Figure 4.8. The interface has separate read latches for system and host memory reads. Both Host and System Read Latch structures contain four sets of internal latches, a 16 word to 1 word mux, and a tri-state buffer. Each memory read latch is opened and closed under control of the internal state machines and each set contains four word latches; one for each of the four memory words (MD0D-MD3D). Both the Host Read Latch structure and the System Read Latch structure can hold 16 words of memory data at one time.

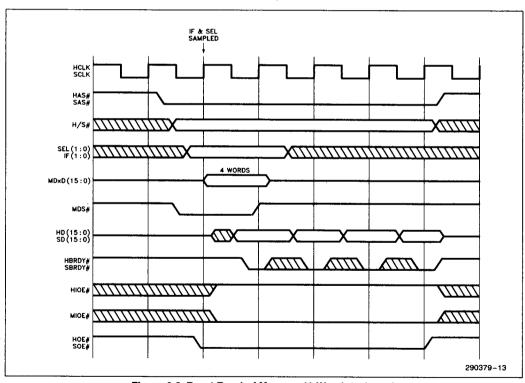

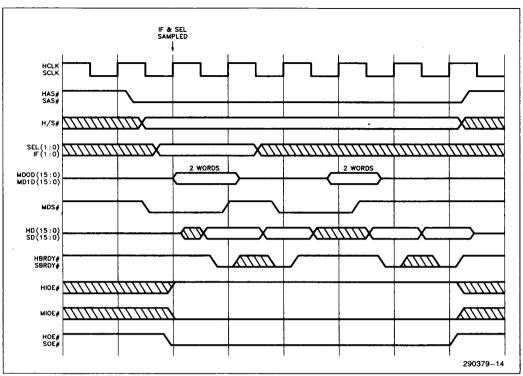

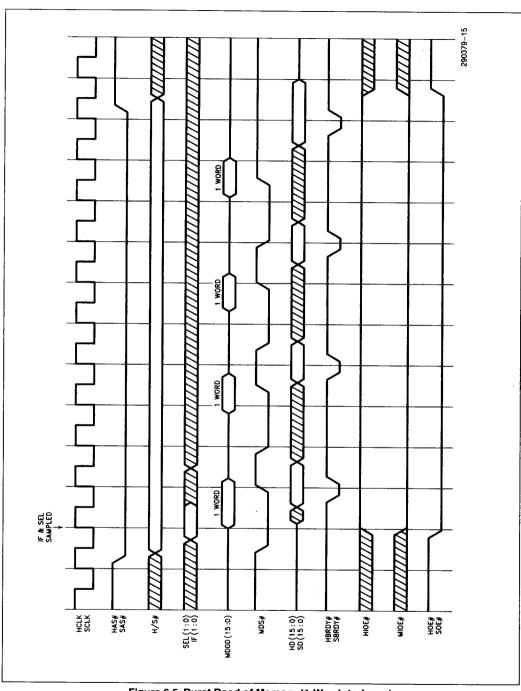

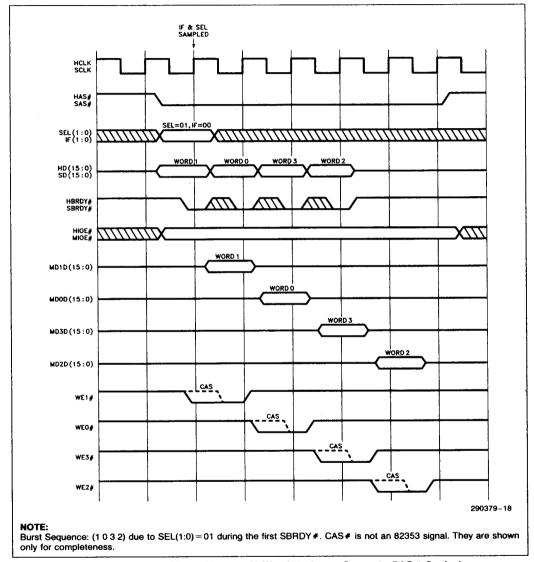

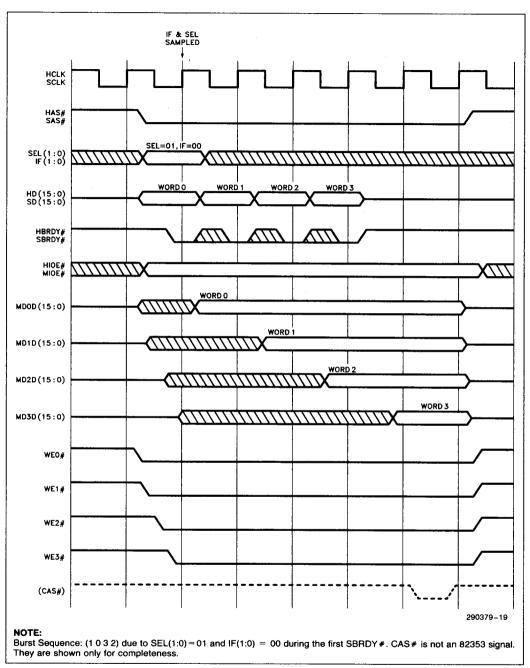

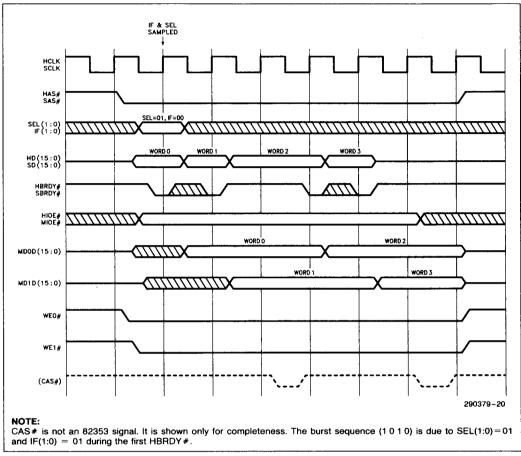

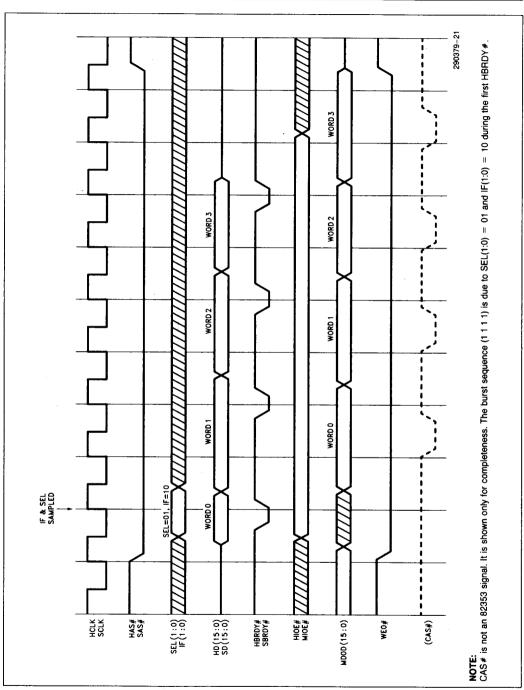

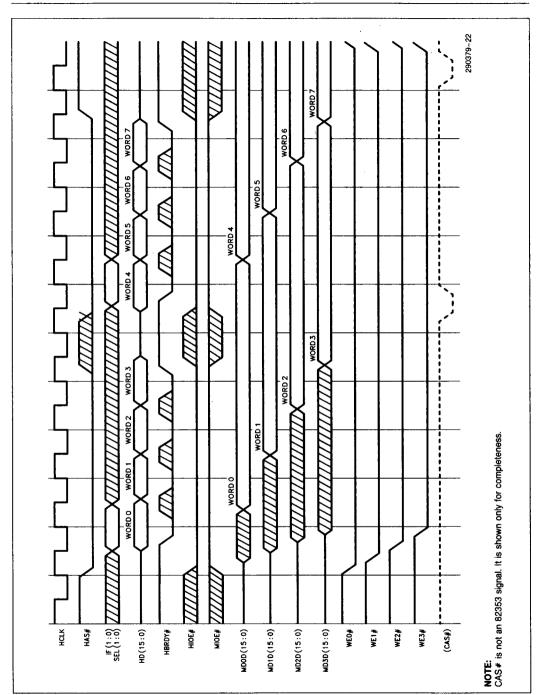

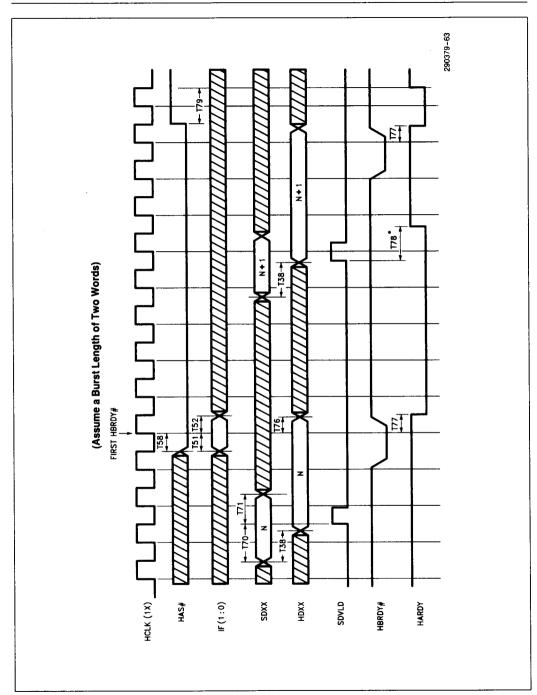

During burst reads, sequential memory data will be placed in either the Host or System Read Latches, dependent upon the state of H/S#. The four sets of 4-word-wide latches provide for a maximum burst read length of 16 words before the latches overflow. (Note that the 16 word burst requires 4 way word interleaved memory. Two and one way word interleaved memory structures can accommodate a maximum 8 and 4 word bursts respectively.)

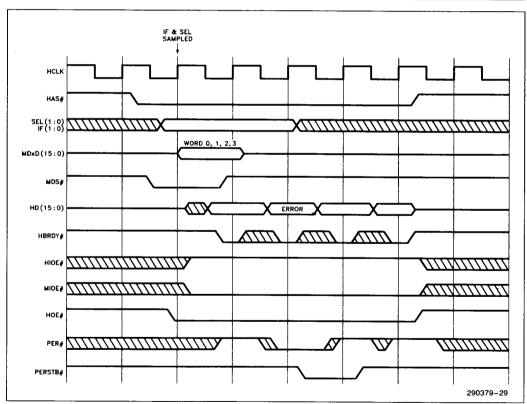

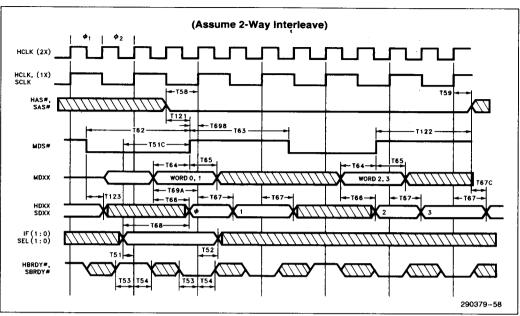

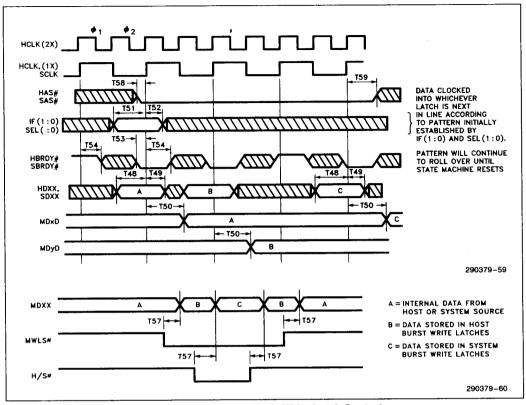

The outputs of the four sets of latches are routed to a 16 word to 1 word mux. This mux is also under control of the internal state machines and IF(1:0), SEL(1:0) which select one of the 16 words in the memory read latches to be routed towards the internal bus. During burst reads the controlling state machines sequence the mux through a series of words from the latches until the burst transfer is complete. The sequence of words in the burst is determined by the value of SEL(1:0) and IF(1:0) during the lead-off cycle.

A tri-state buffer under control of HIOE# and MIOE# drives System Read Latch data onto the internal bus. No buffer is required to route data to the Host Port since the read data bypasses the internal bus and goes directly to a mux in the Host Interface.

Figure 4.7. Memory Write Interface

Figure 4.8. Memory Read Interface

Figure 4.9. 32-Bit Data Bus Implementation Showing External Swap Buffers

#### 5.0 DETAILED PIN DESCRIPTIONS

The following sections describe each 82353 signal in detail. The signals have been broken into three groups according to which interface the signal belongs. These groups are (1) the Host Interface; (2) The System Interface, and; (3) the Memory Interface.

#### 5.1 Host Interface

#### 5.1.1 HOST PINS AVAILABLE TO ALL MODES

| Symbol   | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HD(15:0) | 1/0  | HOST DATA: Word-wide bi-directional host data bus. HD pins are tri-stated when the signal HOE# is high (Clocked, Transparent Mode), or DOE# is de-asserted (82385 Mode). Host data pins are driven when HOE# is asserted (Clocked, Transparent Mode), or when DOE# is asserted with BT/R# low.                                                                                                                                                                                                                                                                                                                                                             |

| HPD(1:0) | 1/0  | HOST PARITY DATA: HPD pins function as parity inputs during write cycles and parity outputs during read cycles. Even parity is supported and HPD signals follow the same timings as HD(15:0).                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HAS#     | ı    | HOST ADDRESS STROBE: This signal is used as a host cycle strobe. The falling edge of HAS# indicates the start of a host PST cycle and the rising edge indicates the end, resetting all host clock-driven state machines. HAS# should remain asserted throughout the entire host cycle.                                                                                                                                                                                                                                                                                                                                                                     |

| HARDY    | 0    | HOST ASYNCHRONOUS READY: HARDY is used during host-to-system burst read cycles to indicate to the host PST that valid data is available from the system with its rising edge. Note that the 82359 DRAM Controller also has its own HARDY signal. The 82353 HARDY and the 82359 HARDY are typically 'OR'ed together. The 82359's HARDY determines the state of HARDY for host-to-system single dword cycles and the lead-off access of a host-to-system burst cycles. The 82353 controls the state of HARDY for the subsequent cycles of the host-to-system burst.                                                                                          |

|          |      | In the lead-off cycle of a host burst read of the system, HARDY is controlled by the 82359 DRAM Controller. The DRAM Controller will de-assert HARDY in the lead-off cycle until it has ownership of the system bus and has completed the first fetch.                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |      | From this point, HARDY is controlled by the 82353. For each of the subsequent system reads in the burst sequence, SDVLD is asserted when the 82358DT Bus Controller has finished its EISA cycle. (SDVLD indicates that an EISA bus cycle has been completed and the data has been latched into the 82353.) Upon sampling the rising edge of SDVLD, the 82353 asserts HARDY to indicate to the host PST that the current word of the burst is ready for reading. When the host reads the data word as indicated by HBRDY #, HARDY becomes de-asserted until the next rising edge of SDVLD. This sequence is repeated until the burst transfer is completed. |

#### 5.1.1 HOST PINS AVAILABLE TO ALL MODES (Continued)

| Symbol    | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |                                                             |                                                                                    |                                                                                                      |                                           |  |  |  |  |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| HBRDY#    | -    | HOST BURST READY: HBRDY # is sampled by the 82353 on the rising edge of HCLK and indicates when the host is ready for the next word of a burst read cycle. During a burst read cycle, HBRDY # asserted indicates to the 82353 that the previous word of the burst has been read and the host is requesting the next word.  In a write cycle, HBRDY # asserted during the rising edge of HCLK indicates to the 82353 that a next word of the burst is valid on HD(15:0), at which time one of the 82353 write latches is closed. Which write latch is closed is determined by the combination of IF(1:0) and SEL(1:0) as sampled on the first active HBRDY #. |                                               |                                                             |                                                                                    |                                                                                                      |                                           |  |  |  |  |

|           |      | IF(1:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               | SEL(1:                                                      |                                                                                    | Vrite Latch<br>se Sequence                                                                           | ]                                         |  |  |  |  |

|           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 0                                           | 0 0<br>0 1<br>1 0<br>1 1<br>0 0                             |                                                                                    | 0-1-2-3<br>1-0-3-2<br>2-3-0-1<br>3-2-1-0<br>0-1-0-1                                                  |                                           |  |  |  |  |

|           |      | (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 0                                           | 0 1<br>1 0<br>1 1<br>0 0                                    |                                                                                    | 1-0-1-0<br>2-3-2-3<br>3-2-3-2                                                                        |                                           |  |  |  |  |

|           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 0                                           | 0 1<br>1 0<br>1 1                                           |                                                                                    | 0-0-0-0<br>1-1-1-1<br>2-2-2-2<br>3-3-3-3                                                             |                                           |  |  |  |  |

|           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 1                                           | X X                                                         | Syste                                                                              | em Port Access                                                                                       |                                           |  |  |  |  |

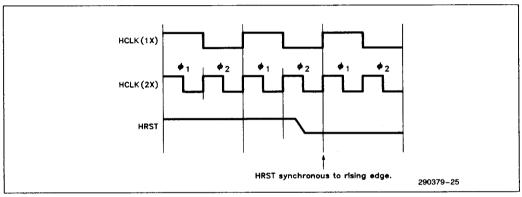

| HCLK1/2X# | I    | HOST CLOCK SELECT: used. The strapping of thi 1x 486-like clock. If strapp frequency of the 82353, Tasynchronous.  If strapped low, the HCLK internally, CMOS clock leter (The falling edge of HRST)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s pin :<br>ped hi<br>TL cl<br>input<br>vels a | selects b<br>gh, then<br>ock level<br>is divide<br>re expec | etween the e<br>the HCLK inp<br>s are expecte<br>ed by two by the<br>sted, and HRS | ither a 2x 386-like<br>out is 1x the operated, and the HRST in<br>the 82353 before be<br>the synchro | clock or a<br>ing<br>nput is<br>eing used |  |  |  |  |

| HCLK      | l    | HOST CLOCK: This is the of the 82353. HCLK can be the 82353, dependent up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e eith                                        | er 1x or                                                    | 2x of the inte                                                                     | rnal operating freq                                                                                  |                                           |  |  |  |  |

| HINTPAR   | ı    | HOST INTERNAL PARITY SELECT: HINTPAR specifies whether the 82353 or the host will be generating/checking parity for host port cycles. If HINTPAR is deasserted, host data parity is generated/checked by host masters and the PERSTB# signal is disabled for host read cycles. If HINTPAR is asserted, parity is generated/checked by the 82353 and PERSTB# is enabled to indicate parity errors.  At reset time, HINTPAR determines which system port mode (Buffered or Standard Mode) is desired by sampling the value of HINTPAR on the falling edge of HRST.                                                                                             |                                               |                                                             |                                                                                    |                                                                                                      |                                           |  |  |  |  |

|           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |                                                             | PAR at stem Mode                                                                   |                                                                                                      |                                           |  |  |  |  |

|           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                             | Star                                                        | ndard Mode<br>fered Mode                                                           |                                                                                                      |                                           |  |  |  |  |

#### 5.1.1 HOST PINS AVAILABLE TO ALL MODES (Continued)

| Symbol  | Type |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      | Name an                              | d Function                                   |        |  |  |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|--------|--|--|

| HRST    | I    | HOST RESET: HRST resets the 82353 internal state machines when asserted. The falling edge of HRST configures the host interface Mode and system interface mode as given in the following tables: |                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |                                              |        |  |  |

|         | 1    |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      | Host Interface                       | e Mode Selection                             |        |  |  |

|         |      |                                                                                                                                                                                                  | At HRS<br>HRD#//<br>HLDSTB                                                                                                                                                                                                                                                                                                                                                                           | T Falling Edge<br>HWCLKEN#/<br>HWLE# | / Host Interface Mode                        |        |  |  |

|         |      |                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                    | 0<br>1                               | Transparent Latch Mode<br>Clocked Latch Mode |        |  |  |

|         |      |                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                    | X                                    | 82385 Mode                                   |        |  |  |

|         |      |                                                                                                                                                                                                  | x = "Don't Ca                                                                                                                                                                                                                                                                                                                                                                                        | are"                                 |                                              |        |  |  |

|         |      |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      | e Mode Selection                     |                                              |        |  |  |

|         |      |                                                                                                                                                                                                  | At HRST Falling Edge<br>HINTPAR                                                                                                                                                                                                                                                                                                                                                                      |                                      | System Interface Mode                        |        |  |  |

|         |      |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      | 0<br>1                               | Standard Mode<br>Buffered Mode               |        |  |  |

|         |      | If HCK1/2X# is strapped for 2x, HRST falling edge must be synchronouphase 1 of the HCLK to set the 82353's internal clock phase. If HCLK1, strapped for 1X, HRST is asynchronous.                |                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |                                              |        |  |  |

| PERSTB# | ОС   | indicates PERSTB SINTPAR SBRDY#                                                                                                                                                                  | ERROR STROBE: PERSTB# is an open collector signal which to the host or system master that a parity error has occurred.  # is valid only when internal parity checking is enabled (HINTPAR = 1 or i = 1), the memory access is to main memory (IF(1:0) < > 11), and or HBRDY# is asserted. This is an active low, one SCLK or HCLK depulse (dependent on which port currently owns the internal bus). |                                      |                                              |        |  |  |

| RESIST  | I    | CURREN<br>GND.                                                                                                                                                                                   | IT DRIVE RE                                                                                                                                                                                                                                                                                                                                                                                          | GULATOR: Conr                        | nect through a 900 $\Omega$ $\pm 5\%$ resis  | tor to |  |  |

#### 5.1.2 TRANSPARENT MODE PINS

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| HIOE#  | l    | HOST INTERNAL OUTPUT ENABLE: This pin enables host data onto the 82353's internal data bus. HIOE# is controlled by the 82359 DRAM Controller. The assertion of HIOE# always overrides the setting of MIOE#. (See MIOE# for related information.)                      |  |  |  |  |  |  |

| HRD#   | ı    | HOST READ: Assertion of HRD# enables a data path from the host bus towards the internal bus, bypassing all write latches. HRD# is provided for designs which allow a system master to read a host bus slave. The typical system design would tie HRD# to logical "1". |  |  |  |  |  |  |

| HOE#   | ı    | <b>HOST OUTPUT ENABLE:</b> Enables data to be driven from the 82353's internal bus to the host bus.                                                                                                                                                                   |  |  |  |  |  |  |

| HWLE#  | ł    | HOST WRITE LATCH ENABLE: The host write latch is transparent when HWLE # is low and latches host data on its rising edge.                                                                                                                                             |  |  |  |  |  |  |

#### 5.1.3 CLOCKED MODE PINS

| Symbol   | Туре | Name and Function                                                                                                                                                                                                                                                     |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIOE#    | l    | HOST INTERNAL OUTPUT ENABLE: This pin enables host data onto the 82353's internal data bus. HIOE # is controlled by the 82359 DRAM Controller. The assertion of HIOE # always overrides the setting of MIOE #. (See MIOE # for related information.)                  |

| HRD#     | I    | HOST READ: Assertion of HRD# enables a data path from the host bus towards the internal bus, bypassing all write latches. HRD# is provided for designs which allow a system master to read a host bus slave. The typical system design would tie HRD# to logical "1". |

| HOE#     | 1    | <b>HOST OUTPUT ENABLE:</b> Enables data to be driven from the 82353's internal bus to the host bus.                                                                                                                                                                   |

| HWCLKEN# | -    | HOST WRITE CLOCK ENABLE: HWCLKEN# asserted enables the host write latch to capture host bus data on HCLK rising edge.                                                                                                                                                 |

#### 5.1.4 82385 MODE PINS

| Symbol | Type | Name and Function                                                                                                                                |                                                                                                                                                                      |       |                                    |  |  |  |  |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------|--|--|--|--|

| BT/R#  | I .  | 82385 BT/R#: This pin determines the direction of data flow in the host interface and should be connected to the BT/R# of the 82385. (See DOE#). |                                                                                                                                                                      |       |                                    |  |  |  |  |

| HLDSTB | l    |                                                                                                                                                  | HOST LOCAL DATA STROBE: The rising edge of this signal latches data into the posted write buffer inside the 82353. HLDSTB should be connected to LDSTB of the 82385. |       |                                    |  |  |  |  |

| DOE#   | I    | DATA OUTPUT El<br>pin, together with the<br>onto the host bus.                                                                                   |                                                                                                                                                                      |       |                                    |  |  |  |  |

|        | 1    | D                                                                                                                                                | OE#                                                                                                                                                                  | BT/R# | 82353 Action                       |  |  |  |  |

|        |      |                                                                                                                                                  | 0                                                                                                                                                                    | 0     | Host Interface drives Host Bus     |  |  |  |  |

|        |      |                                                                                                                                                  | 0                                                                                                                                                                    | 1     | Host Interface drives Internal Bus |  |  |  |  |

|        |      |                                                                                                                                                  |                                                                                                                                                                      | x     | Host and Internal Bus not driven   |  |  |  |  |

#### 5.2 System Interface

#### 5.2.1 SYSTEM PINS AVAILABLE IN BOTH MODES

| Symbol   | Type |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | Name and | Function    |          |                                        |  |  |

|----------|------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-------------|----------|----------------------------------------|--|--|

| SD(15:0) | 1/0  | stated whe                                                                   | <b>SYSTEM DATA:</b> Bi-directional system data bus. In Buffered Mode, SD pins are tristated when signal SOE# is high, and driven when SOE# is low. See SOE(1:0) for a description of the driving and tri-stating of the SD(15:0) pins in Standard Mode.                                                                                                                                                                                                                             |        |          |             |          |                                        |  |  |

| IDSDLE#  | -    | the bus cor<br>level poste<br>can come t<br>from either                      | INTERNAL DATA TO SYSTEM DATA LATCH ENABLE: IDSDLE # is generated by the bus controller for host-to-system write cycles to latch host data into a second level posted write buffer on the system port of the 82353. Data going into this latch can come from one of the two sources: (1) the 82353's internal bus (data coming from either host or memory ports), or; (2) data from the loop-back path in which an EISA master cycle requires byte assembly (in Standard Mode only). |        |          |             |          |                                        |  |  |

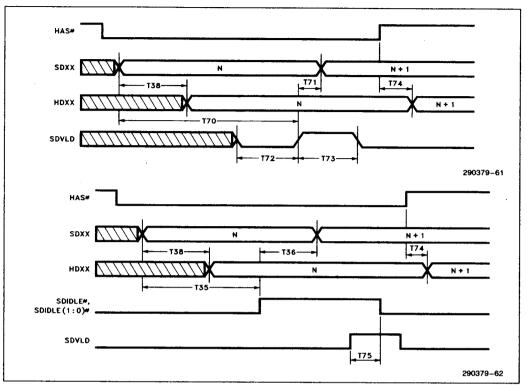

| SDVLD    | ١    | been latche ignore any                                                       | SYSTEM DATA VALID STROBE: Indicates to the 82353 that valid system data has been latched off the system bus. SDVLD's rising edge causes the system latch to ignore any further SDIDLE#'s until the host is finished reading the data (signified by either the rising edge of HAS# or HBRDY being sampled asserted).  Output Path                                                                                                                                                    |        |          |             |          |                                        |  |  |

|          |      |                                                                              | 82353 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nputs  |          | 82353 (     | Outputs  |                                        |  |  |

|          |      | CPYEN#                                                                       | CPYUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SOE1#  | SOE0#    | SD(15:8)    | SD(7:0)  | Transfer Type                          |  |  |

|          |      | 1                                                                            | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1      | 1        | HI-Z        | HI-Z     |                                        |  |  |

|          |      | 1                                                                            | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1      | 0        | HI-Z        | ID(7:0)  | H, M, L → SD                           |  |  |

| 1        |      | 1                                                                            | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | 1        | ID(15:8)    | HI-Z     | $H, M, L \rightarrow SD$               |  |  |

|          |      | 1                                                                            | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | 0        | ID(15:8)    | ID(7:0)  | H,M,L> SD                              |  |  |

|          |      | 0                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | 0        | *** Invalid |          |                                        |  |  |

|          |      | 0                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | 1        | ID(15:8)    | ID(15:8) | $\mid$ H, M, L $\rightarrow$ SD $\mid$ |  |  |

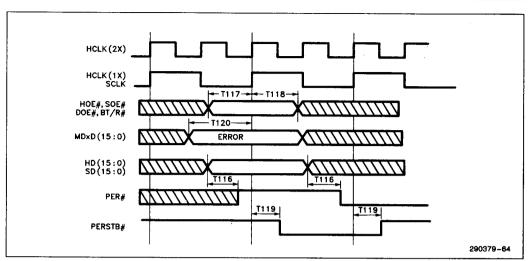

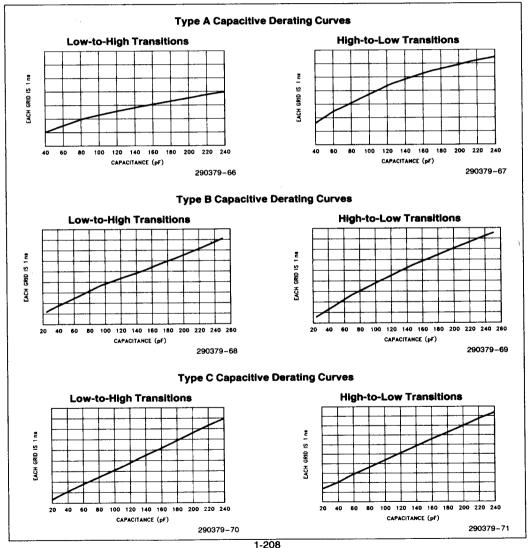

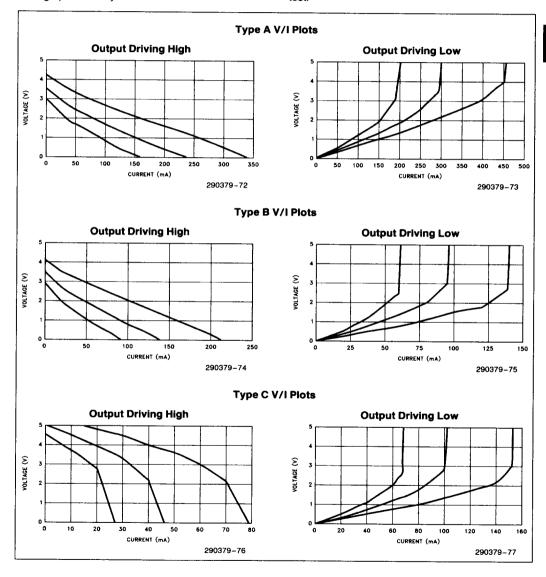

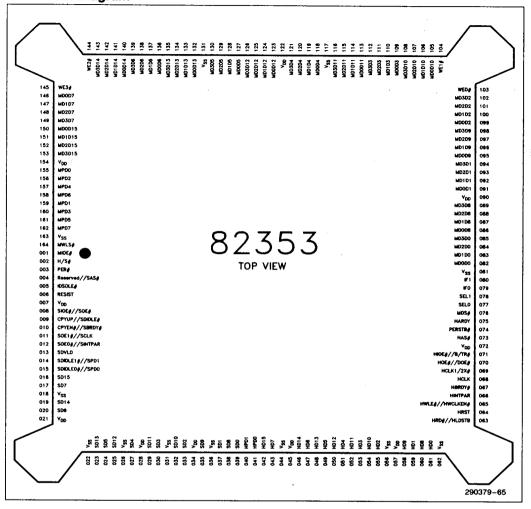

|          |      | 0                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1      | 0        | *** Invalid |          |                                        |  |  |