Data Sheet July 11, 2007 FN9100.5

#### **Power Distribution Controllers**

This family of fully featured hot swap power controllers targets applications in the +2.5V to +12V range. The ISL6115 is for +12V control, the ISL6116 for +5V, the ISL6117 for +3.3V and the ISL6120 for +2.5V control applications. Each has a hard wired undervoltage (UV) monitoring and reporting threshold level approximately 80% of the aforementioned voltage.

The ISL6115 has an integrated charge pump allowing control of up to +16V rails using an external N-Channel MOSFET whereas the other devices utilize the +12V bias voltage to fully enhance the N-channel pass FET. All ICs feature programmable overcurrent (OC) detection, current regulation (CR) with time delay to latch-off and soft-start.

The current regulation level is set by 2 external resistors;  $R_{ISET}$  sets the CR Vth and the other is a low ohmic sense element across, which the CR Vth is developed. The CR duration is set by an external capacitor on the CTIM pin, which is charged with a 20 $\mu$ A current once the CR Vth level is reached. If the voltage on the CTIM cap reaches 1.9V the IC then quickly pulls down the GATE output latching off the pass FET.

This family although designed for high side switch control the ISL6116, ISL6117, ISL6120 can also be used in a low side configuration for control of much higher voltage potentials.

## Ordering Information

| PART<br>NUMBER         | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE                | PKG.<br>DWG. # |  |  |

|------------------------|-----------------|---------------------|------------------------|----------------|--|--|

| ISL6115CB*             | ISL61 15CB      | 0 to +85            | 8 Ld SOIC              | M8.15          |  |  |

| ISL6116CB*             | ISL61 16CB      | 0 to +85            | 8 Ld SOIC              | M8.15          |  |  |

| ISL6117CB*             | ISL61 17CB      | 0 to +85            | 8 Ld SOIC              | M8.15          |  |  |

| ISL6120CB*             | ISL61 20CB      | 0 to +85            | 8 Ld SOIC              | M8.15          |  |  |

| ISL6115CBZA*<br>(Note) | 6115 CBZ        | 0 to +85            | 8 Ld SOIC<br>(Pb-free) | M8.15          |  |  |

| ISL6116CBZA*<br>(Note) | 6116 CBZ        | 0 to +85            | 8 Ld SOIC<br>(Pb-free) | M8.15          |  |  |

| ISL6117CBZA*<br>(Note) | 6117 CBZ        | 0 to +85            | 8 Ld SOIC<br>(Pb-free) | M8.15          |  |  |

| ISL6120CBZA*<br>(Note) | 6120 CBZ        | 0 to +85            | 8 Ld SOIC<br>(Pb-free) | M8.15          |  |  |

<sup>\*</sup>Add "-T" suffix for tape and reel.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

#### **Features**

- HOT SWAP Single Power Distribution Control (ISL6115 for +12V, ISL6116 for +5V, ISL6117 for +3.3V and ISL6120 for +2.5V)

- · Overcurrent Fault Isolation

- Programmable Current Regulation Level

- Programmable Current Regulation Time to Latch-Off

- Rail to Rail Common Mode Input Voltage Range (ISL6115)

- Internal Charge Pump Allows the use of N-Channel MOSFET for +12V control (ISL6115)

- Undervoltage and Overcurrent Latch Indicators

- Adjustable Turn-On Ramp

- · Protection During Turn On

- Two Levels of Overcurrent Detection Provide Fast Response to Varying Fault Conditions

- 1µs Response Time to Dead Short

- Pb-Free Plus Anneal Available (RoHS Compliant)

- · Tape and Reel Packing with '-T' Part Number Suffix

#### **Applications**

- Power Distribution Control

- · Hot Plug Components and Circuitry

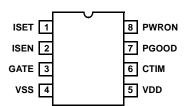

#### **Pinout**

ISL6115, ISL6116, ISL6117, ISL6120 (8 LD SOIC) TOP VIEW

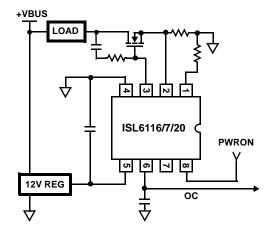

# Application One - High Side Controller

####

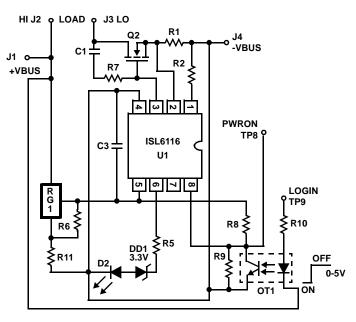

# Application Two - Low Side Controller

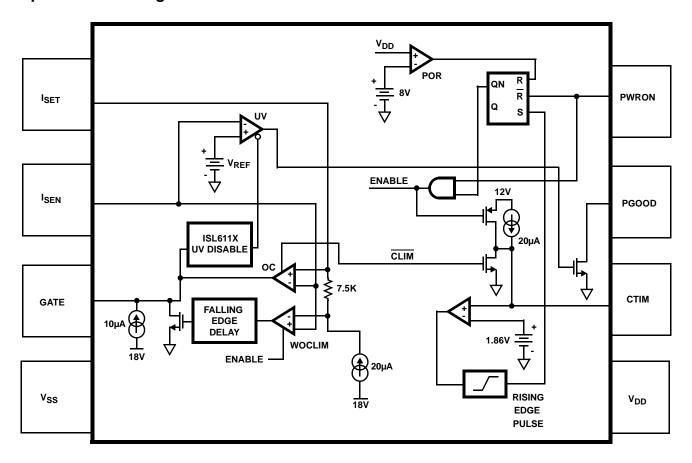

## Simplified Block Diagram

## Pin Descriptions

| PIN# | SYMBOL          | FUNCTION                          | DESCRIPTION                                                                                                                                                                                                                                                                                          |

|------|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ISET            | Current Set                       | Connect to the low side of the current sense resistor through the current limiting set resistor. This pin functions as the current limit programming pin.                                                                                                                                            |

| 2    | ISEN            | Current Sense                     | Connect to the more positive end of sense resistor to measure the voltage drop across this resistor.                                                                                                                                                                                                 |

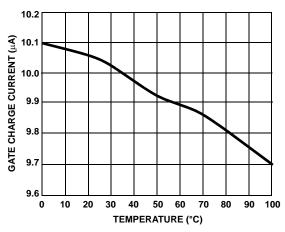

| 3    | GATE            | External FET Gate Drive<br>Pin    | Connect to the gate of the external N-Channel MOSFET. A capacitor from this node to ground sets the turn-on ramp. At turn-on this capacitor will be charged to $V_{DD}$ +5V (ISL6115) and to $V_{DD}$ (ISL6116, ISL6117, ISL6120) by a $10\mu$ A current source.                                     |

| 4    | VSS             | Chip Return                       |                                                                                                                                                                                                                                                                                                      |

| 5    | V <sub>DD</sub> | Chip Supply                       | 12V chip supply. This can be either connected directly to the +12V rail supplying the switched load voltage or to a dedicated $V_{SS}$ +12V supply.                                                                                                                                                  |

| 6    | CTIM            | Current Limit Timing<br>Capacitor | Connect a capacitor from this pin to ground. This capacitor determines the time delay between an overcurrent event and chip output shutdown (current limit time-out). The duration of current limit time-out is equal to $93 \text{k}\Omega \times \text{C}_{\text{TIM}}$ .                          |

| 7    | PGOOD           | Power Good Indicator              | Indicates that the voltage on the ISEN pin is satisfactory. PGOOD is driven by an open drain N-Channel MOSFET and is pulled low when the output voltage (VISEN) is less than the UV level for the particular IC.                                                                                     |

| 8    | PWRON           | Power ON                          | PWRON is used to control and reset the chip. The chip is enabled when PWRON pin is driven high to a maximum of 5V or is left open. Do not drive this input >5V. After a current limit time out, the chip is reset by a low level signal applied to this pin. This input has 20µA pull up capability. |

FN9100.5 intersil July 11, 2007

3

## ISL6115, ISL6116, ISL6117, ISL6120

## **Absolute Maximum Ratings** $T_A = +25$ °C

| V <sub>DD</sub> 0.3V to +16V                                 |

|--------------------------------------------------------------|

| GATE0.3V to V <sub>DD</sub> +8V                              |

| ISEN, PGOOD, PWRON, CTIM, ISET0.3V to V <sub>DD</sub> + 0.3V |

| FSD Classification 5kV                                       |

#### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range | +12V ±15%    |

|--------------------------------------|--------------|

| Temperature Range (T <sub>A</sub> )  | 0°C to +85°C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| SOIC Package                                     | 98                     |

| Maximum Junction Temperature (Plastic Package)   |                        |

| Maximum Storage Temperature Range65°             | C to +150°C            |

| Pb-free reflow profile                           | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. (See Tech Brief, #TB379.1 for

- 2. All voltages are relative to GND, unless otherwise specified

- 3. Limits established by characterization and are not production tested.

## **Electrical Specifications** $V_{DD} = 12V$ , $T_A = T_J = 0$ °C to +85°C, Unless Otherwise Specified

| PARAMETER                                | SYMBOL                  | TEST CONDITIONS                                                         | MIN                    | TYP                  | MAX  | UNITS |  |

|------------------------------------------|-------------------------|-------------------------------------------------------------------------|------------------------|----------------------|------|-------|--|

| CURRENT CONTROL                          |                         |                                                                         |                        |                      |      |       |  |

| ISET Current Source                      | I <sub>ISET_ft</sub>    |                                                                         | 18.5                   | 20                   | 21.5 | μΑ    |  |

| ISET Current Source                      | I <sub>ISET_pt</sub>    | $T_J = +15^{\circ}C \text{ to } +55^{\circ}C$                           | 19                     | 20                   | 21   | μΑ    |  |

| Current Limit Amp Offset Voltage         | Vio_ft                  | VISET - VISEN                                                           | -6                     | 0                    | 6    | mV    |  |

| Current Limit Amp Offset Voltage         | Vio_pt                  | V <sub>ISET</sub> - V <sub>ISEN</sub> , T <sub>J</sub> = +15°C to +55°C | -2                     | 0                    | 2    | mV    |  |

| GATE DRIVE                               | 1                       | ı                                                                       | I .                    | 1                    |      |       |  |

| GATE Response Time To Severe OC          | pd_woc_amp              | V <sub>GATE</sub> to 10.8V                                              | -                      | 100                  | -    | ns    |  |

| GATE Response Time to Overcurrent        | pd_oc_amp               | V <sub>GATE</sub> to 10.8V                                              | -                      | 600                  | -    | ns    |  |

| GATE Turn-On Current                     | I <sub>GATE</sub>       | V <sub>GATE</sub> to = 6V                                               | 8.4                    | 10                   | 11.6 | μА    |  |

| GATE Pull Down Current                   | OC_GATE_I_4V            | Overcurrent                                                             | 45                     | 75                   | -    | mA    |  |

| GATE Pull Down Current (Note 3)          | WOC_GATE_I_4V           | Severe Overcurrent                                                      | 0.5                    | 0.8                  | -    | Α     |  |

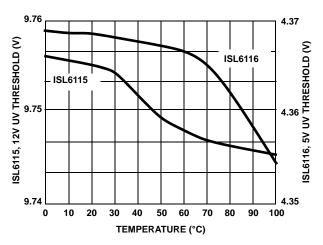

| ISL6115 Undervoltage Threshold           | 12V <sub>UV_VTH</sub>   |                                                                         | 9.2                    | 9.6                  | 10   | V     |  |

| ISL6115 GATE High Voltage                | 12VG                    | GATE Voltage                                                            | V <sub>DD</sub> + 4.5V | V <sub>DD</sub> + 5V | -    | V     |  |

| ISL6116 Undervoltage Threshold           | 5V <sub>UV_VTH</sub>    |                                                                         | 4.0                    | 4.35                 | 4.5  | V     |  |

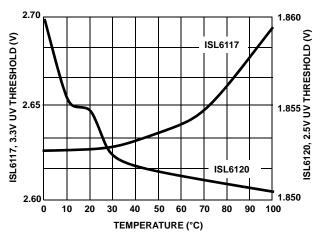

| ISL6117 Undervoltage Threshold           | 3V <sub>UV_VTH</sub>    |                                                                         | 2.4                    | 2.6                  | 2.8  | V     |  |

| ISL6120 Undervoltage Threshold           | 2V <sub>UV_VTH</sub>    |                                                                         | 1.8                    | 1.85                 | 1.9  | V     |  |

| ISL6116, 17, 20 GATE High Voltage        | VG                      | GATE Voltage                                                            | V <sub>DD</sub> - 1.5V | V <sub>DD</sub>      | -    | V     |  |

| BIAS                                     |                         |                                                                         | 11                     | I                    | •    |       |  |

| V <sub>DD</sub> Supply Current           | I <sub>VDD</sub>        |                                                                         | -                      | 3                    | 5    | mA    |  |

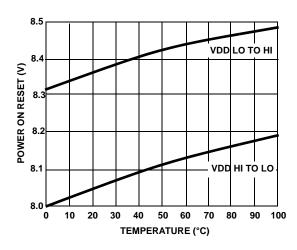

| V <sub>DD</sub> POR Rising Threshold     | V <sub>DD_POR_L2H</sub> | VDD Low to High                                                         | 7.8                    | 8.4                  | 9    | V     |  |

| V <sub>DD</sub> POR Falling Threshold    | V <sub>DD_POR_H2L</sub> | VDD High to Low                                                         | 7.5                    | 8.1                  | 8.7  | V     |  |

| V <sub>DD</sub> POR Threshold Hysteresis | V <sub>DD_POR_HYS</sub> | V <sub>DD_POR_L2H</sub> - V <sub>DD_POR_H2L</sub>                       | 0.1                    | 0.3                  | 0.6  | V     |  |

| Maximum PWRON Pull-Up Voltage            | PWRN_PUV                | Maximum External Pull-up Voltage                                        | -                      | 5                    | -    | V     |  |

| PWRON Pull-Up Voltage                    | PWRN_V                  | PWRON Pin Open                                                          | 2.7                    | 3.2                  | -    | V     |  |

| PWRON Rising Threshold                   | PWR_Vth                 |                                                                         | 1.4                    | 1.7                  | 2.0  | V     |  |

| PWRON Hysteresis                         | PWR_hys                 |                                                                         | 130                    | 170                  | 250  | mV    |  |

| PWRON Pull-Up Current                    | PWRN_I                  |                                                                         | 9                      | 17                   | 25   | μΑ    |  |

|                                          |                         |                                                                         |                        |                      |      |       |  |

Electrical Specifications V<sub>DD</sub> = 12V, T<sub>A</sub> = T<sub>J</sub> = 0°C to +85°C, Unless Otherwise Specified (Continued)

| PARAMETER                                       | SYMBOL                  | TEST CONDITIONS         | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|-------------------------|-------------------------|-----|-----|-----|-------|

| CURRENT REGULATION DURATION/POWER GOOD          |                         |                         |     |     |     |       |

| C <sub>TIM</sub> Charging Current               | C <sub>TIM</sub> _ichg0 | V <sub>CTIM</sub> = 0V  | 16  | 20  | 23  | μΑ    |

| C <sub>TIM</sub> Fault Pull-Up Current (Note 3) |                         |                         | -   | 20  | -   | mA    |

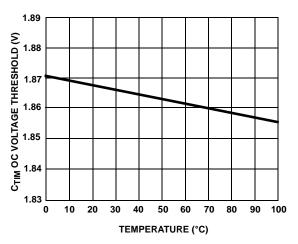

| Current Limit Time-Out Threshold Voltage        | C <sub>TIM</sub> _Vth   | CTIM Voltage            | 1.3 | 1.8 | 2.3 | V     |

| Power Good Pull Down Current                    | PG_lpd                  | V <sub>OUT</sub> = 0.5V | -   | 8   | -   | mA    |

## **Description and Operation**

The members of this family are single power supply distribution controllers for generic hot swap applications across the +2.5V to +12V supply range. The ISL6115 is targeted for +12V switching applications whereas the ISL6116 is targeted for +5V, the ISL6117 for +3.3V and the ISL6120 for +2.5V applications. Each IC has a hardwired undervoltage (UV) threshold level approximately 17% lower than the stated voltages.

These ICs feature a highly accurate programmable overcurrent (OC) detecting comparator, programmable current regulation (CR) with programmable time delay to latch off, and programmable soft-start turn-on ramp all set with a minimum of external passive components. The ICs also include severe OC protection that immediately shuts down the MOSFET switch should a rapid load current transient such as a near dead short cause the CR Vth to exceed the programmed level by 150mV. Additionally, the ICs have a UV indicator and an OC latch indicator. The functionality of the PGOOD feature is enabled once the IC is biased, monitoring and reporting any UV condition on the ISEN pin.

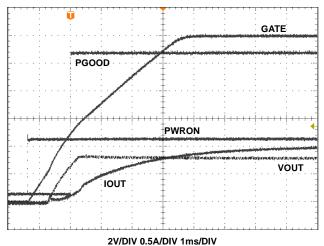

Upon initial power up, the IC can either isolate the voltage supply from the load by holding the external N-Channel MOSFET switch off or apply the supply rail voltage directly to the load for true hot swap capability. The PWRON pin must be pulled low for the device to isolate the power supply from the load by holding the external N-channel MOSFET off. With the PWRON pin held high or floating the IC will be in true hot swap mode. In both cases the IC turns on in a soft-start mode protecting the supply rail from sudden in-rush current.

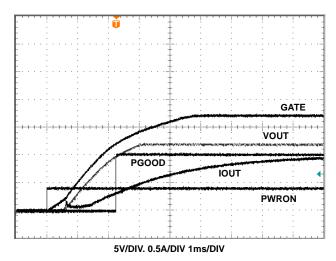

At turn-on, the external gate capacitor of the N-Channel MOSFET is charged with a  $10\mu\text{A}$  current source resulting in a programmable ramp (soft-start turn-on). The internal ISL6115 charge pump supplies the gate drive for the 12V supply switch driving that gate to  $\sim$ VDD +5V, for the other three ICs the gate drive voltage is limited to the chip bias voltage, VDD.

Load current passes through the external current sense resistor. When the voltage across the sense resistor exceeds the user programmed CR voltage threshold value, (see Table 1 for  $R_{\mbox{\scriptsize ISET}}$  programming resistor value and resulting nominal current regulation threshold voltage,  $V_{\mbox{\scriptsize CR}})$  the controller enters its current regulation mode. At this time, the

time-out capacitor, on  $C_{TIM}$  pin is charged with a  $20\mu A$  current source and the controller enters the current limit time to latch-off period. The length of the current limit time to latch-off duration is set by the value of a single external capacitor (see Table 2) for CTIM capacitor value and resulting nominal current limited time out to latch-off duration placed from the CTIM pin (pin 6) to ground. The programmed current level is held until either the OC event passes or the time out period expires. If the former is the case then the N-Channel MOSFET is fully enhanced and the  $C_{TIM}$  capacitor is discharged. Once CTIM charges to 1.87V, signaling that the time out period has expired an internal latch is set whereby the FET gate is quickly pulled to 0V turning off the N-Channel MOSFET switch, isolating the faulty load.

TABLE 1.

| R <sub>ISET</sub> RESISTOR | NOMINAL CR VTH |

|----------------------------|----------------|

| 10kΩ                       | 200mV          |

| 4.99kΩ                     | 100mV          |

| 2.5kΩ                      | 50mV           |

| 750Ω                       | 15mV           |

NOTE: Nominal Vth =  $R_{ISET} \times 20 \mu A$ .

TABLE 2.

| C <sub>TIM</sub> CAPACITOR | NOMINAL CURRENT LIMITED PERIOD |

|----------------------------|--------------------------------|

| 0.022μF                    | 2ms                            |

| 0.047μF                    | 4.4ms                          |

| 0.1μF                      | 9.3ms                          |

NOTE: Nominal time-out period =  $C_{TIM} \times 93k\Omega$ .

This IC responds to a severe overcurrent load (defined as a voltage across the sense resistor >150mV over the OC Vth set point) by immediately driving the N-Channel MOSFET gate to 0V in about  $10\mu s$ . The gate voltage is then slowly ramped up turning on the N-Channel MOSFET to the programmed current regulation level; this is the start of the time out period.

Upon a UV condition the PGOOD signal will pull low when tied high through a resistor to the logic or VDD supply. This pin is a UV fault indicator. For an OC latch off indication, monitor CTIM, pin 6. This pin will rise rapidly from 1.9V to VDD once the time out period expires.

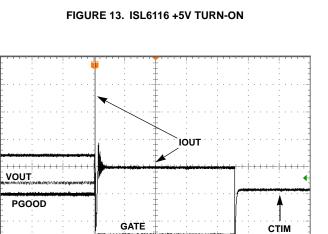

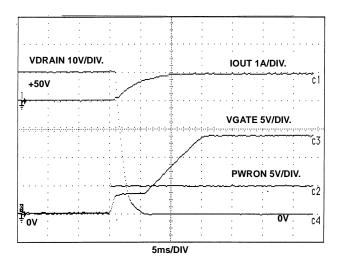

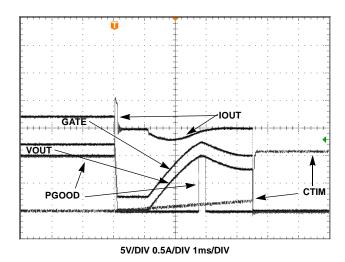

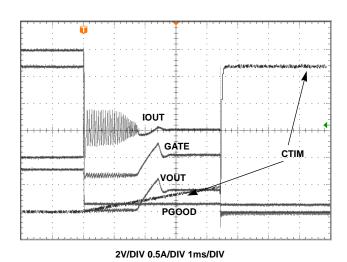

See Figures 12 to 16 for waveforms relevant to text.

The IC is reset after an OC latch-off condition by a low level on the PWRON pin and is turned on by the PWRON pin being driven high.

#### Application Considerations

Design applications where the CR Vth is set extremely low, 25mV or less there is a two fold risk to consider.

Firstly, there is the susceptibility to noise influencing the absolute CR Vth value. This can be addressed with a 100pF cap across the Rset resistor.

Secondly, due to common mode limitations of the overcurrent comparator, the voltage on the ISET pin must be 20mV above the IC ground either initially (from ISET \* RSET) or before CTIM reaches time-out (from gate charge-up). If this does not happen, the IC may incorrectly report overcurrent fault at startup when there is no fault. Circuits with high load capacitance and initially low load current are susceptible to this type of unexpected behavior.

Do not signal nor pull up the PWRON input to > 5V. Exceeding 6V on this pin will cause the internal charge pump to malfunction.

During the soft-start and the time-out delay duration with the IC in its current limit mode, the  $V_{GS}$  of the external N-Channel MOSFET is reduced driving the MOSFET switch into a (linear region) high  $r_{DS(ON)}$  state. Strike a balance between the CR limit and the timing requirements to avoid periods when the external N-Channel MOSFETs may be damaged or destroyed due to excessive internal power dissipation. Refer to the  ${\bf MOSFET}$  SOA information in the manufacturer's data sheet.

When driving particularly large capacitive loads a longer softstart time to prevent current regulation upon charging and a short CR time may offer the best application solution relative to reliability and FET MTF.

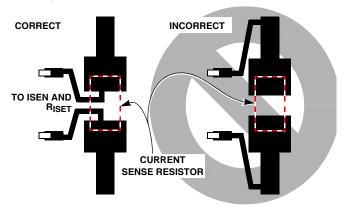

Physical layout of R<sub>SENSE</sub> resistor is critical to avoid the possibility of false overcurrent occurrences. Ideally, trace routing between the R<sub>SENSE</sub> resistors and the IC is as direct and as short as possible with zero current in the sense lines (See Figure 1).

FIGURE 1. SENSE RESISTOR PCB LAYOUT

6

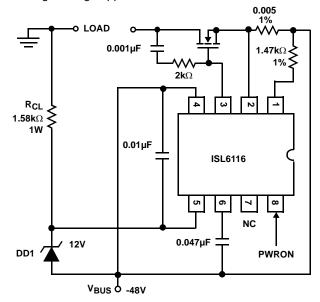

# Using the ISL6116 as a -48V Low Side Hot Swap Power Controller

To supply the required  $V_{DD}$ , it is necessary to maintain the chip supply 10 to 16V above the -48V bus. This may be accomplished with a suitable regulator between the voltage rail and pin 5 (VDD). By using a regulator, the designer may ignore the bus voltage variations. However, a low-cost alternative is to use a Zener diode (See Figure 2 for typical 5A load control); this option is detailed below.

Note that in this configuration the PGOOD feature (pin 7) is not operational as the  $I_{SEN}$  pin voltage is always < UV threshold.

See Figures 17 to 20 for waveforms relevant to -48V and other high voltage applications.

FIGURE 2.

## Biasing the ISL6116

Table 3 gives typical component values for biasing the ISL6116 in a  $\pm 48V$  application. The formulas and calculations deriving these values are also shown below.

TABLE 3. TYPICAL VALUES FOR A -48V HOT SWAP APPLICATION

| SYMBOL          | PARAMETER                             |  |  |  |

|-----------------|---------------------------------------|--|--|--|

| R <sub>CL</sub> | 1.58kΩ, 1W                            |  |  |  |

| DD1             | 12V Zener Diode, 50mA Reverse Current |  |  |  |

When using the ISL6116 to control -48V, a Zener diode may be used to provide the +12V bias to the chip. If a Zener is used then a current limit resistor should also be used. Several items must be taken into account when choosing

values for the current limit resistor ( $R_{CL}$ ) and Zener Diode (DD1):

- The variation of the V<sub>BUS</sub> (in this case, -48V nominal)

- The chip supply current needs for all functional conditions

- . The power rating of RCI.

- The current rating of DD1

#### **Formulas**

1. Sizing R<sub>CL</sub>:

$R_{CL} = (V_{BUS,MIN} - 12)/I_{CHIP}$

2. Power Rating of R<sub>CL</sub>:

$P_{RCL} = I_C(V_{BUS,MAX} - 12)$

3. DD1 Current Rating:

$I_{DD1} = (V_{BUS.MAX} - 12)/R_{CL}$

#### Example

A typical -48V supply may vary from -36 to -72V. Therefore,

$V_{BUS.MAX} = -72V$

$V_{BUS.MIN} = -36V$

$I_{CHIP} = 15mA (max)$

Sizing R<sub>CL</sub>:

$R_{CL} = (V_{BUS,MIN} - 12)/I_{C}$

$R_{CL} = (36 - 12)/0.015$

$R_{CL} = 1.6k\Omega$  [Typical Value =  $1.58k\Omega$ ]

Power Rating of R<sub>CI</sub>:

$P_{RCL} = I_C(V_{BUS,MAX} - 12)$

$P_{RCL} = (0.015)(72 - 12)$

P<sub>RCL</sub> = 0.9W [Typical Value = 1W]

DD1 Current Rating:

$I_{DD1} = (V_{BUS,MAX} - 12)/R_{CL}$

$I_{DD1} = (72 - 12)/1.58k\Omega$

I<sub>DD1</sub> = 38mA [Typical Value = 12V rating, 50mA reverse current]

## Typical Performance Curves

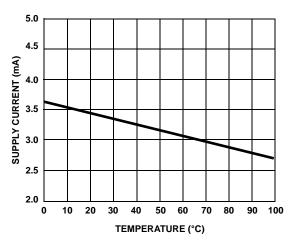

FIGURE 3. VDD BIAS CURRENT

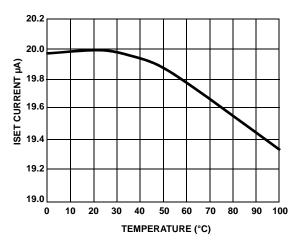

FIGURE 4. ISET SOURCE CURRENT

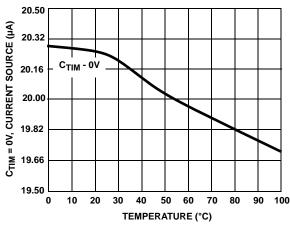

FIGURE 5. C<sub>TIM</sub> CURRENT SOURCE

FIGURE 6.  $C_{TIM}$  OC VOLTAGE THRESHOLD

FN910.5 July 11, 2007

## Typical Performance Curves (Continued)

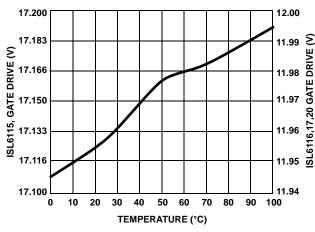

FIGURE 7. ISL6115, ISL6116 UV THRESHOLD

FIGURE 8. ISL6117, ISL6120 UV THRESHOLD

FIGURE 9. GATE CHARGE CURRENT

FIGURE 10. GATE DRIVE VOLTAGE, VDD = 12V

FIGURE 11. POWER ON RESET VOLTAGE THRESHOLD

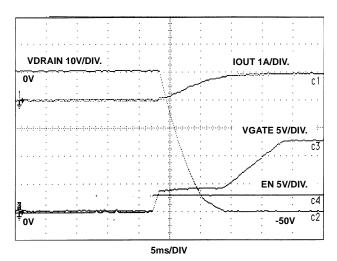

FIGURE 12. ISL6115 +12V TURN-ON

## Typical Performance Curves (Continued)

5V/DIV 0.5A/DIV 1ms/DIV

FIGURE 15. ISL6115 'HIGH' OVERCURRENT RESPONSE

FIGURE 17. +50V LOW SIDE SWITCHING CGATE = 100pF

FIGURE 14. ISL6115 'LOW' OVERCURRENT RESPONSE

FIGURE 16. ISL6116 'HIGH' OVERCURRENT RESPONSE

FIGURE 18. -50V LOW SIDE SWITCHING CGATE = 1000pF

FN9100.5 July 11, 2007

## Typical Performance Curves (Continued)

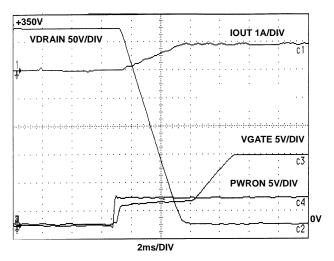

FIGURE 19. +350V LOW SIDE SWITCHING CGATE = 100pF

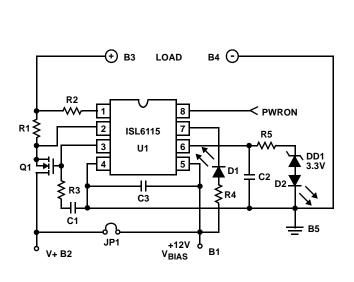

#### ISL6115EVAL1 Board

The ISL6115EVAL1 is configured as a +12V high side switch controller with the CR level set at ~1.5A. (See Figure 21 for ISL6115EVAL1 schematic and Table 4 for BOM). Bias and load connection points are provided along with test points for each IC pin.

With the chip to be biased from the +12V bus being switched, through B2, GND B5, the load connected between B3 and B4 and with jumper J1 installed the ISL6115 can be evaluated. PWRON pin pulls high enabling the ISL6115 if not driven low.

With R2 = 750 $\Omega$  the CR Vth is set to 15mV and with the 10m $\Omega$  sense resistor the ISL6115EVAL1 has a nominal CR level of 1.5A. The 0.047 $\mu$ F delay time to latch-off capacitors results in a nominal 4.4ms before latch-off of outputs after an OC event.

Also included with the ISL6115EVAL1 board are one each of the ISL6116, ISL6117 and ISL6120 for evaluation.

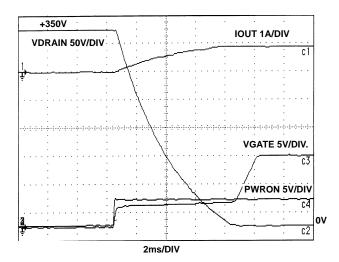

FIGURE 20. +350V LOW SIDE SWITCHING CGATE = 1000pF

#### ISL6116EVAL1 Board

The ISL6116EVAL1 is default configured as a negative voltage low side switch controller with a ~2.4A CR level. (See Figure 22 for ISL6116EVAL1 schematic and Table 4 for BOM and component description). This basic configuration is capable of controlling both larger positive or negative potential voltages with minimal changes.

Bias and load connection points are provided in addition to test points, TP1-8 for each IC pin. The terminals, J1 and J4 are for the bus voltage and return, respectively, with the more negative potential being connected to J4. With the load between terminals J2 and J3 the board is now configured for evaluation. The device is enabled through LOGIN, TP9 with a TTL signal. ISL6116EVAL1 includes a level shifting circuit with an opto-coupling device for the PWRON input so that standard TTL logic can be translated to the -V reference for chip control.

When controlling a positive voltage, PWRON can be accessed at TP8.

The ISL6116EVAL1 is provided with a high voltage linear regulator for convenience to provide chip bias from  $\pm 24$ V to  $\pm 350$ V. This can be removed and replaced with the zener & resistor bias scheme as discussed earlier. High voltage regulators and power discrete devices are no longer available from Intersil but can be purchased from other semiconductor manufacturers.

Reconfiguring the ISL6116EVAL1 board for a higher CR level can be done by changing the R<sub>SENSE</sub> and R<sub>ISET</sub> resistor values as the provided FET is 75A rated. If evaluation at >60V, an alternate FET must be chosen with an adequate  $BV_{DSS}$ .

FIGURE 21. ISL6115EVAL1 HIGH SIDE SWITCH APPLICATION

FIGURE 22. ISL6116EVAL1 NEGATIVE VOLTAGE LOW SIDE CONTROLLER

TABLE 4. BILL OF MATERIALS, ISL6115EVAL1, ISL6116EVAL1

| COMPONENT DESIGNATOR | COMPONENT NAME                             | COMPONENT DESCRIPTION                                                                                                                                      |

|----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q1                   | HUF76132SK8                                | 11.5mΩ, 30V, 11.5A Logic Level N-Channel Power MOSFET or equiv.                                                                                            |

| Q2                   | HUF7554S3S                                 | 10mΩ, 80V, 75A N-Channel Power MOSFET or equiv.                                                                                                            |

| R1                   | Load Current Sense Resistor                | Dale, WSL-2512 10mΩ 1W Metal Strip Resistor                                                                                                                |

| High Side R2         | Overcurrent Voltage Threshold Set Resistor | 750Ω 805 Chip Resistor (Vth = 15mV)                                                                                                                        |

| Low side R2          | Overcurrent Voltage Threshold Set Resistor | 1.21kΩ 805 Chip Resistor (Vth = 24mV)                                                                                                                      |

| C2                   | Time Delay Set Capacitor                   | 0.047μF 805 Chip Capacitor (4.5ms)                                                                                                                         |

| C1                   | Gate Timing Capacitor                      | 0.001μF 805 Chip Capacitor (<2ms)                                                                                                                          |

| C3                   | IC Decoupling Capacitor                    | 0.1μF 805 Chip Capacitor                                                                                                                                   |

| R3                   | Gate Stability Resistor                    | 20Ω 805 Chip Resistor                                                                                                                                      |

| R7                   | Gate to Drain Resistor                     | 2kΩ 805 Chip Resistor                                                                                                                                      |

| JP1                  | Bias Voltage Selection Jumper              | Install if switched rail voltage is = +12V ±15%. Remove and provide separate +12V bias voltage to U1 via TP5 if ISL6116, ISL6117, ISL6120 being evaluated. |

| R4, R5               | LED Series Resistors                       | 2.32kΩ 805 Chip Resistor                                                                                                                                   |

| D1, D2               | Fault Indicating LEDs                      | Low Current Red SMD LED                                                                                                                                    |

| DD1                  | Fault Voltage Dropping Diode               | 3.3V Zener Diode, SOT-23 SMD 350mW                                                                                                                         |

| OT1                  | PWRON Level Shifting Opto-Coupler          | PS2801-1 NEC                                                                                                                                               |

| R8                   | Level Shifting Bias Resistor               | 2.32kΩ 805 Chip Resistor                                                                                                                                   |

| R9                   | Level Shifting Bias Resistor               | 1.18kΩ 805 Chip Resistor                                                                                                                                   |

| R10                  | Level Shifting Bias Resistor               | 200Ω 805 Chip Resistor                                                                                                                                     |

| RG1                  | HIP5600IS                                  | High Voltage Linear Regulator                                                                                                                              |

| R6                   | Linear Regulator RF1                       | 1.78kΩ 805 Chip Resistor                                                                                                                                   |

| R11                  | Linear Regulator RF2                       | 15kΩ 805 Chip Resistor                                                                                                                                     |

| TP1-TP8              | Test Points for Device Pin Numbers 1-8     |                                                                                                                                                            |

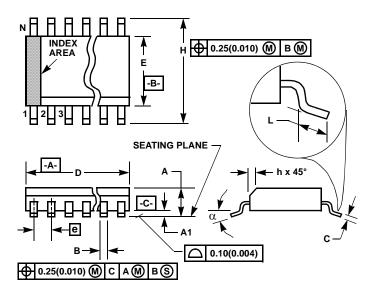

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C)

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES |        | MILLIMETERS |      |       |

|--------|--------|--------|-------------|------|-------|

| SYMBOL | MIN    | MAX    | MIN         | MAX  | NOTES |

| Α      | 0.0532 | 0.0688 | 1.35        | 1.75 | -     |

| A1     | 0.0040 | 0.0098 | 0.10        | 0.25 | -     |

| В      | 0.013  | 0.020  | 0.33        | 0.51 | 9     |

| С      | 0.0075 | 0.0098 | 0.19        | 0.25 | -     |

| D      | 0.1890 | 0.1968 | 4.80        | 5.00 | 3     |

| Е      | 0.1497 | 0.1574 | 3.80        | 4.00 | 4     |

| е      | 0.050  | BSC    | 1.27 BSC    |      | -     |

| Н      | 0.2284 | 0.2440 | 5.80        | 6.20 | -     |

| h      | 0.0099 | 0.0196 | 0.25        | 0.50 | 5     |

| L      | 0.016  | 0.050  | 0.40        | 1.27 | 6     |

| N      | 8      |        | 8           | 3    | 7     |

| а      | 0°     | 8°     | 0°          | 8°   | -     |

Rev. 1 6/05

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com