# Semiconductor Reliability Handbook

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other disputes involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawing, chart, program, algorithm, application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics products.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (space and undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. When using the Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat radiation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions or failure or accident arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please ensure to implement safety measures to guard them against the possibility of bodily injury, injury or damage caused by fire, and social damage in the event of failure or malfunction of Renesas Electronics products, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures by your own responsibility as warranty for your products/system. Because the evaluation of microcomputer software alone is very difficult and not practical, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please investigate applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive carefully and sufficiently and use Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall not use Renesas Electronics products or technologies for (1) any purpose relating to the development, design, manufacture, use, stockpiling, etc., of weapons of mass destruction, such as nuclear weapons, chemical weapons, or biological weapons, or missiles (including unmanned aerial vehicles (UAVs)) for delivering such weapons, (2) any purpose relating to the development, design, manufacture, or use of conventional weapons, or (3) any other purpose of disturbing international peace and security, and you shall not sell, export, lease, transfer, or release Renesas Electronics products or technologies to any third party whether directly or indirectly with knowledge or reason to know that the third party or any other party will engage in the activities described above. When exporting, selling, transferring, etc., Renesas Electronics products or technologies, you shall comply with any applicable export control laws and regulations promulgated and administered by the governments of the countries asserting jurisdiction over the parties or transactions.

- 10. Please acknowledge and agree that you shall bear all the losses and damages which are incurred from the misuse or violation of the terms and conditions described in this document, including this notice, and hold Renesas Electronics harmless, if such misuse or violation results from your resale or making Renesas Electronics products available any third party.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## Contents

| ~      | ality Assurance for Semiconductor Devices                                                        |    |

|--------|--------------------------------------------------------------------------------------------------|----|

| 1.1    | Basic Policy for Quality                                                                         |    |

| 1.2    | Quality Assurance System for Semiconductor Devices                                               |    |

| 1.3    | Quality Assurance at Development Stage                                                           |    |

| 1.4    | Quality Assurance at Mass Production Stage                                                       |    |

| 1.5    | Change Control                                                                                   |    |

| 1.6    | Failure After Shipping and Corrective Actions                                                    | 9  |

|        |                                                                                                  |    |

| 2. Re  | iability                                                                                         |    |

| 2.1    | Concept of Semiconductor Device Reliability                                                      |    |

| 2.2    | Dependencies of Failure Rate Function (Bathtub Curve)                                            |    |

| 2.2    |                                                                                                  | 13 |

| 2.2    |                                                                                                  | 13 |

| 2.2    | 3 Wear-out Failures                                                                              | 13 |

| 2.3    | Screening                                                                                        | 14 |

| 2.4    | Characteristics of Semiconductor Reliability                                                     | 15 |

| 2.5    | Reliability Criteria                                                                             | 16 |

| 2.5    | 1 Early Failure Period Criteria                                                                  | 16 |

| 2.5    | 2 Random Failure Period Criteria                                                                 | 16 |

| 2.6    | Probability Distribution Used for Reliability Analysis                                           | 20 |

| 2.7    | Reliability Testing                                                                              | 22 |

| 2.8    | Reliability Test Methods                                                                         | 23 |

| 2.9    | Accelerated Lifetime Test Methods                                                                | 23 |

| 2.9    | 1 Fundamental Failure Model                                                                      | 23 |

| 2.9    | 2 Method of Accelerated Life Testing                                                             | 27 |

| 2.10   | Reliability Prediction Based on the Failure Mechanism                                            | 29 |

| 2.1    | •                                                                                                |    |

| 2.1    |                                                                                                  |    |

|        | (Method of Estimating a Failure Rate at a 60% Confidence Level)                                  | 31 |

| 2.1    |                                                                                                  |    |

| 2.1    | •                                                                                                |    |

|        |                                                                                                  |    |

| 3. Fai | ure Mechanisms                                                                                   | 43 |

| 3.1    | Failure Classification                                                                           | 43 |

| 3.2    | Failure Mechanisms Related to the Wafer Process                                                  | 48 |

| 3.2    | 1 Time Dependent Dielectric Breakdown <sup>[1][2]</sup>                                          | 48 |

| 3.2    | 2 Hot Carrier                                                                                    | 50 |

| 3.2    | 3 NBTI (Negative Bias Temperature Instability)                                                   | 53 |

| 3.2    | 4 Electromigration                                                                               | 54 |

| 3.2    | 5 Stress Migration                                                                               | 55 |

| 3.2    | 6 Soft Error                                                                                     | 56 |

| 3.2    | 7 Reliability of Non-Volatile Memory                                                             | 59 |

| 3.3    | Failure Mechanisms Related to the Assembly Process                                               | 62 |

| 3.3    | 1 Wire Bonding Reliability (Au-Al Joint Reliability)                                             | 62 |

| 3.3    |                                                                                                  |    |

| 3.3    |                                                                                                  |    |

| 3.3    | -                                                                                                |    |

| 3.3    |                                                                                                  |    |

| 3.3    |                                                                                                  |    |

| 3.4    | Failure Mechanisms Related to the Mounting Process and During Practical Use                      |    |

| 3.4    |                                                                                                  |    |

| 3.5    | Failure Mechanisms Related to Electrostatic Breakdown, Electrical Overstress Breakdown, Latchup, |    |

| 2.5    | and Power Devices                                                                                |    |

| 3.5    | 1 Electrostatic Breakdown and Electrical Overstress Breakdown                                    | /9 |

| 3.5.2          | Latchup                                                                                      | 90  |

|----------------|----------------------------------------------------------------------------------------------|-----|

| 3.5.3          | Power MOS FET Damage                                                                         | 92  |

| 4 Failu        | to Analyzia                                                                                  | 101 |

|                | e Analysis                                                                                   |     |

|                | hy Failure Analysis Is Necessary?                                                            |     |

|                | hat Is Failure Analysis?                                                                     |     |

|                | ocedure of Failure Analysis                                                                  |     |

| 4.3.1<br>4.3.2 | Investigation and Clarification of Failure Circumstances                                     |     |

|                | Visual Inspection                                                                            |     |

| 4.3.3          | Evaluation for Electrical Characteristics                                                    |     |

| 4.3.4          | Internal Analysis of a Package                                                               |     |

| 4.3.5          | Fault Isolation                                                                              |     |

| 4.3.6          | Physical Analysis                                                                            |     |

| 4.3.7          | Impurity and Composition Analysis                                                            |     |

| 4.3.8          | Estimation of Failure Mechanism                                                              |     |

| 4.4 Fa         | ilure Analysis Methods                                                                       |     |

| 4.4.1          | SAT (Scanning Acoustic Tomography)                                                           |     |

| 4.4.2          | SEM (Scanning Electron Microscopy) and EPMA (Electron Probe Micro Analysis)                  |     |

| 4.4.3          | EB Tester (Electron Beam Tester)                                                             |     |

| 4.4.4          | Laser Voltage Probing (LVP) and Time Resolved Photo Emission Microscopy (TRE)                | 117 |

| 4.4.5          | Liquid Crystal Analysis                                                                      | 119 |

| 4.4.6          | Photoemission Microscopic Analysis                                                           | 121 |

| 4.4.7          | OBIRCH (Optical Beam Induced Resistance Change) Method                                       |     |

| 4.4.8          | Failure Analysis Techniques that Use IDDQ Abnormality Images                                 |     |

| 4.4.9          | AES (Auger Electron Spectroscopy)                                                            |     |

| 4.4.10         |                                                                                              |     |

| 4.4.11         |                                                                                              |     |

|                | ocessing Technology for Analysis                                                             |     |

| 4.5.1          | Introduction                                                                                 |     |

| 4.5.2          | FIB (Focused Ion Beam)                                                                       |     |

| 4.5.2          | Excimer Laser                                                                                |     |

|                |                                                                                              |     |

| 4.5.4          | RIE (Reactive Ion Etching)                                                                   |     |

| 4.5.5<br>4.6 A | FLB (Focused Laser Beam)                                                                     |     |

| -              |                                                                                              |     |

| 5. Basic       | Recommendations for Handling and Using Semiconductor Devices                                 | 155 |

|                | oduct Safety                                                                                 |     |

| 5.2 Se         | miconductor Device Selection                                                                 | 157 |

| 5.2.1          | Application-Related Cautions                                                                 | 157 |

| 5.2.2          | Maximum Ratings                                                                              | 157 |

| 5.2.3          | Derating                                                                                     | 158 |

| 5.2.4          | Safe Operating Area in Transistors                                                           | 163 |

| 5.2.5          | Using a Device with Equivalent Function                                                      |     |

| 5.2.6          | When a Device is Used in a Severe Environment                                                |     |

| 5.2.7          | Package Selection                                                                            |     |

|                | utions Concerning Design for Safety                                                          |     |

| 5.3.1          | What Is Design for Safety?                                                                   |     |

| 5.3.2          | System Safety Concepts                                                                       |     |

| 5.3.3          | Design for Safety Concerning Sets that Use Semiconductor Devices                             |     |

|                | ecautions in Circuit Design                                                                  |     |

|                |                                                                                              |     |

|                | nutions on Thermal Designing                                                                 |     |

|                | nutions on Use Environment                                                                   |     |

|                | otecting Semiconductor Devices from Electrical Damage                                        |     |

| 5.7.1          | ESD Damage                                                                                   |     |

| 5.7.2          | Excess Voltage Destruction                                                                   |     |

| 5.7.3          | Destruction due to External Surges                                                           |     |

| 5.7.4          | Notes on Destruction of Semiconductor Devices by Overvoltages Generated by the Device Itself | 188 |

| 5.7.5   | Latch-Up                                                               | 190 |

|---------|------------------------------------------------------------------------|-----|

| 5.7.6   | Destruction Induced by Over-Current                                    |     |

| 5.7.7   | Handling Unused Pins                                                   |     |

| 5.7.8   | Thermal Runaway                                                        | 191 |

| 5.7.9   | SOA Destruction                                                        | 191 |

| 5.7.1   |                                                                        |     |

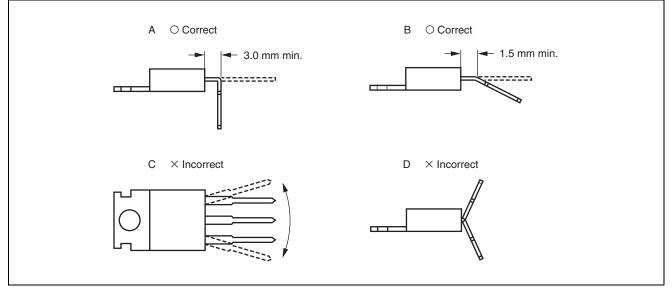

| 5.8 P   | Protecting Semiconductor Devices from Mechanical Damage                | 192 |

| 5.8.1   |                                                                        |     |

| 5.8.2   | Mounting on a Printed Circuit Board                                    | 195 |

| 5.8.3   | 6                                                                      |     |

| 5.8.4   |                                                                        |     |

| 5.9 P   | Protecting Semiconductor Devices from Thermal Damage                   |     |

| 5.9.1   | 6                                                                      |     |

| 5.9.2   |                                                                        |     |

| 5.9.3   | 6                                                                      |     |

|         | Protecting Semiconductor Devices from Malfunctions                     |     |

| 5.10.   | 8                                                                      |     |

| 5.10.   | e                                                                      |     |

| 5.10.   | 6                                                                      |     |

|         | Aeasurement-Related Cautions                                           |     |

| 5.11.   |                                                                        |     |

| 5.11.   |                                                                        |     |

|         | oftware Precautions                                                    |     |

|         | Being Prepared for Possible Malfunction                                |     |

|         | Cautions on Packing, Storage, Shipment and Handling                    |     |

| 5.14.   |                                                                        |     |

| 5.14.   |                                                                        |     |

| 5.14.   | 6                                                                      |     |

| 5.14.   | 1                                                                      |     |

| 5.15 E  | Examples of Other Categories of Problems                               |     |

| A. Sam  | pling Inspection                                                       |     |

|         | Vhat Is Sampling Inspection?                                           |     |

|         | AQL Sampling Table (MIL-STD-105)                                       |     |

|         | TPD Sampling Table (MIL-PRF-19500)                                     |     |

|         |                                                                        | 007 |

|         | ched Tables                                                            |     |

|         | Probability Density of Normal Distribution                             |     |

|         | Jpper Probability of Normal Distribution                               |     |

|         | Percent Points of Normal Distribution                                  |     |

|         | Poisson Distribution (Probability)                                     |     |

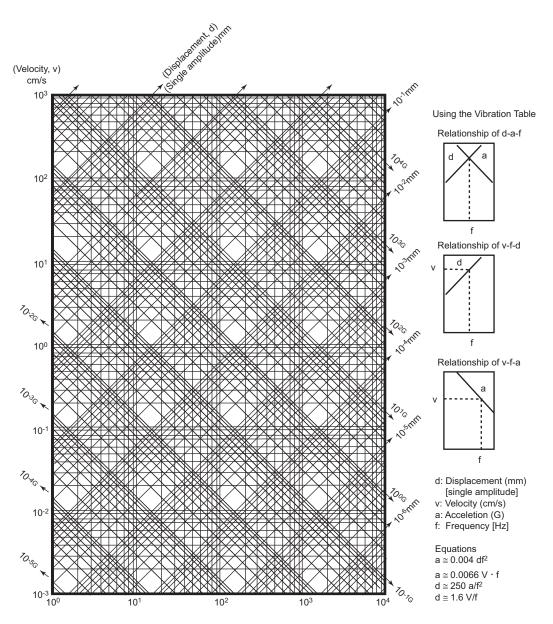

|         | Vibration Tables (Amplitude, Velocity, and Acceleration vs. Frequency) |     |

| B.6 V   | Vater Vapor Pressure Tables                                            |     |

| C. Reli | ability Theory                                                         |     |

|         | Reliability Criteria                                                   |     |

| C.1.1   | •                                                                      |     |

| C.1.2   | 5                                                                      |     |

|         | Reliability of Composite Devices                                       |     |

| C.2.1   |                                                                        |     |

| C.2.2   |                                                                        |     |

| C.2.3   | 11 1                                                                   |     |

|         | ailure Models for Accelerated Life Testing                             |     |

| C.3.1   | -                                                                      |     |

| C.3.2   | 5                                                                      |     |

| C.3.3   | , ,                                                                    |     |

| C.4 A   | Analysis of Test Results                                               |     |

|         |                                                                        |     |

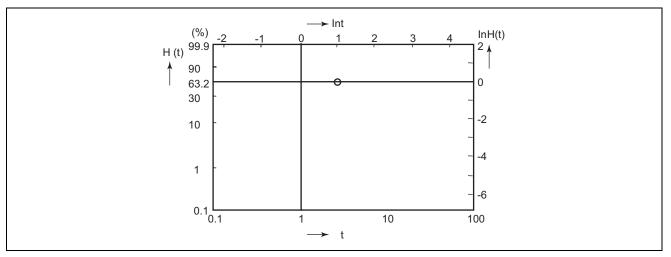

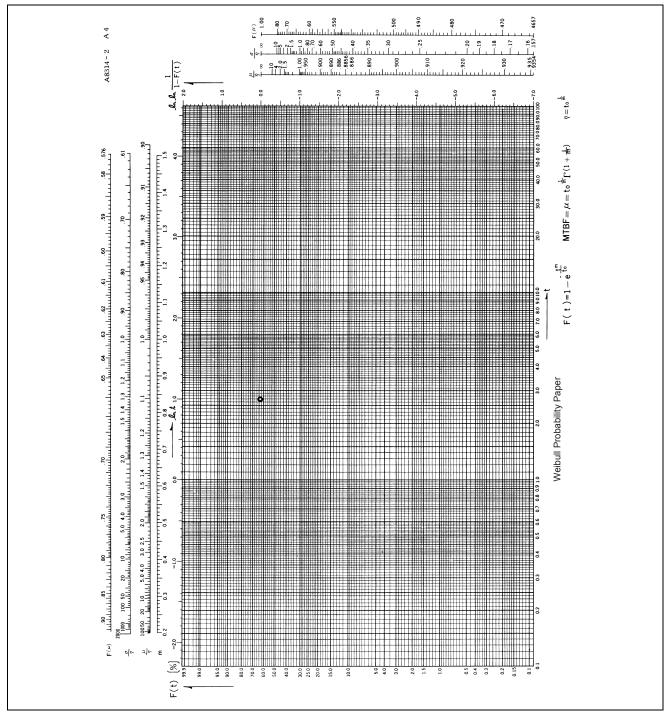

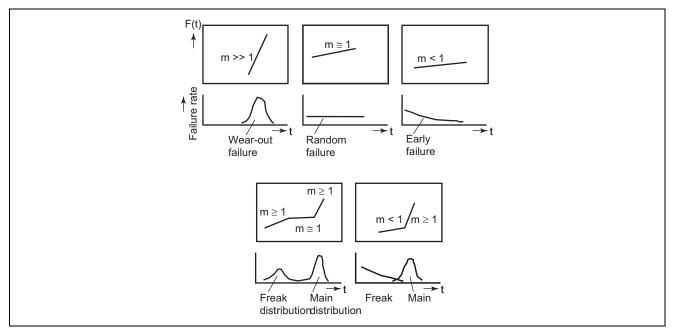

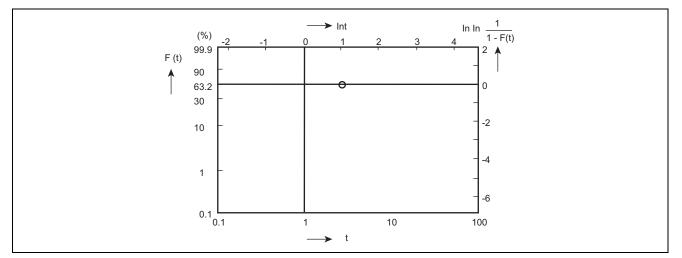

| С.4   | 4.1 Weibull Probability Paper                                                                |  |

|-------|----------------------------------------------------------------------------------------------|--|

| С.    | 4.2 Cumulative Hazard Paper                                                                  |  |

| C.4   | 4.3 Prediction Method from MIL-HDBK-217                                                      |  |

| D. Pr | obability Models Used in Reliability Analysis                                                |  |

| D.1   | Bernoulli Trial                                                                              |  |

| D.2   | Binomial Distribution: fBin(x, n, p)                                                         |  |

| D.3   | Negative Binomial Distribution: fneg – bin(x, n, p) and Multinomial Distribution: fmulti-bin |  |

|       | (x1, x2,, xm, n, p1, p2,, pm)                                                                |  |

| D.4   | Geometric Distribution: fGeo(n, p)                                                           |  |

| D.5   | Hypergeometric Distribution: fH – geo(N, R, n, x)                                            |  |

| D.6   | Exponential Distribution: fexp(t)                                                            |  |

| D.7   | Pascal Distribution: fPas(x, y, p)                                                           |  |

| D.8   | Gamma Distribution: $f\Gamma(t, \alpha, \beta)$                                              |  |

| D.9   | Poisson Distribution: fPois(x)                                                               |  |

| D.10  | Normal Distribution: fNorm(x)                                                                |  |

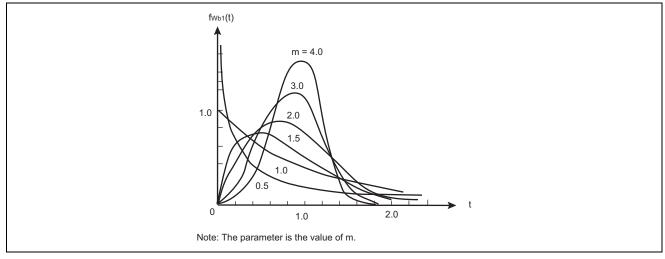

| D.11  | Weibull Distribution: fWbl(t)                                                                |  |

| D.12  | Double Exponential Distribution: fd-exp(x)                                                   |  |

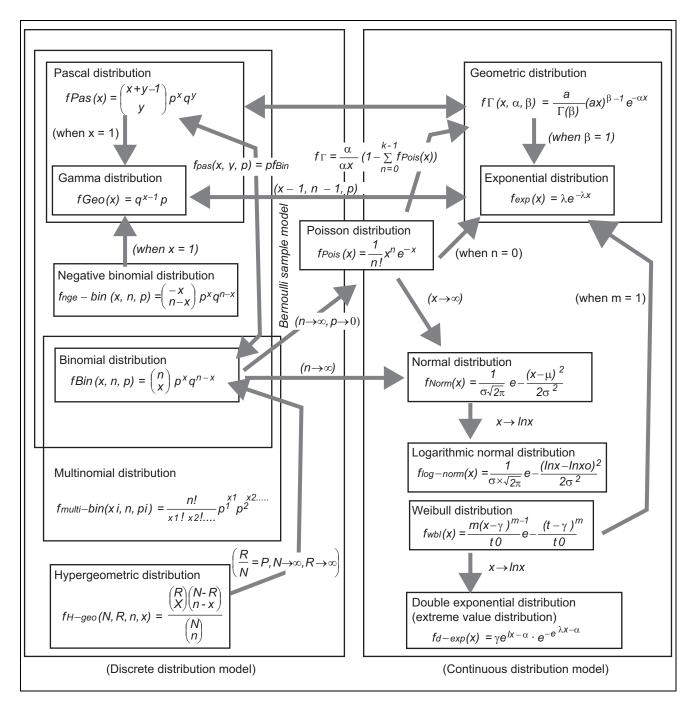

| E. Re | elations of Probability Distributions                                                        |  |

| F. Pr | obability Functions                                                                          |  |

## Figures

| 1. Quality A             | Assurance for Semiconductor Devices                                                      | 1  |

|--------------------------|------------------------------------------------------------------------------------------|----|

| Figure 1.1               | Renesas Electronics Quality Policy                                                       |    |

| Figure 1.2               | Renesas Quality Assurance System for Semiconductor Devices                               |    |

| Figure 1.3               | Quality Assurance Program Flowchart                                                      |    |

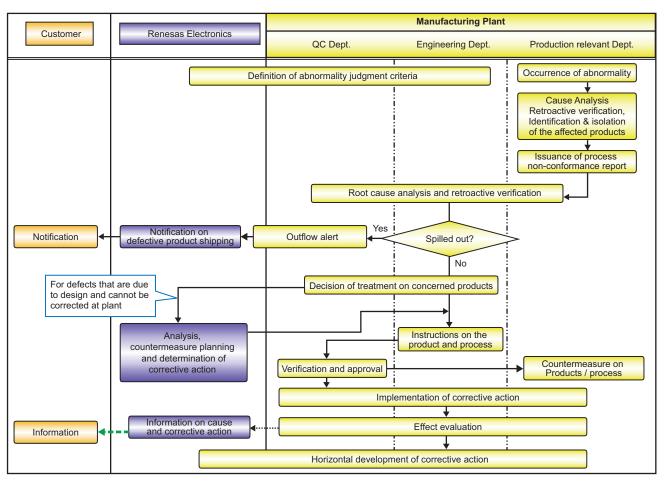

| Figure 1.4               | Flowchart of Corrective Action                                                           | 7  |

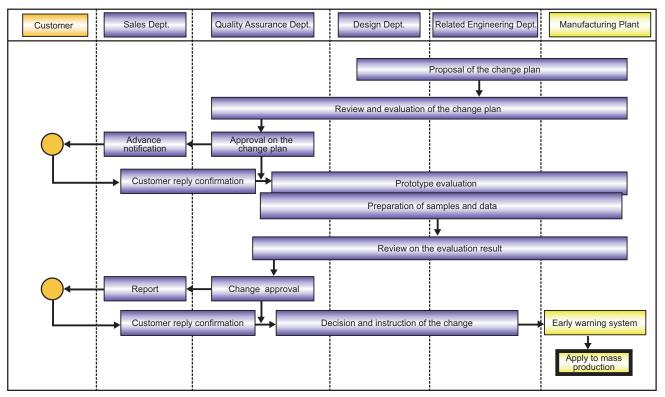

| Figure 1.5               | Change Control System                                                                    |    |

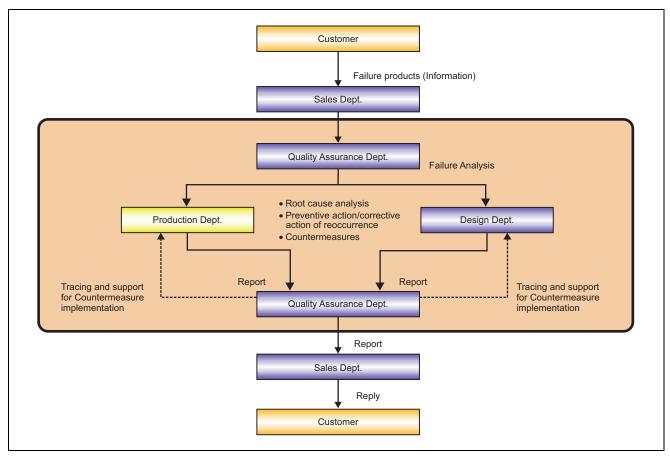

| Figure 1.6               | Flowchart of Customer Complaint Management                                               | 9  |

| 2 Raliahili              | ty                                                                                       | 11 |

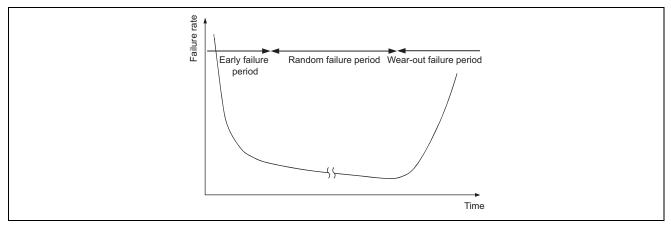

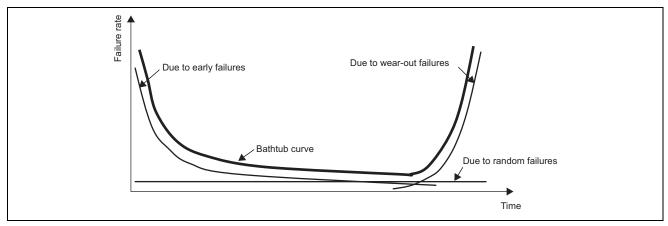

| Figure 2.1               | Failure Rate Curve (Bathtub Curve)                                                       |    |

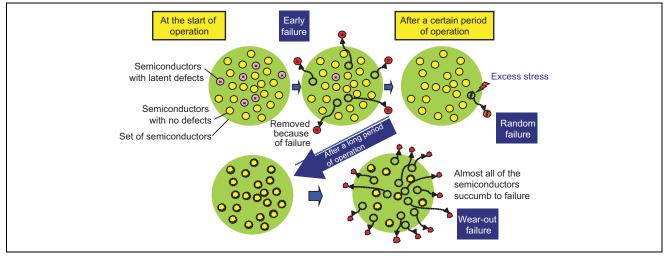

| Figure 2.1<br>Figure 2.2 | Image Showing Changes in the Semiconductor Failure Rate Results in a Bathtub Curve       |    |

| Figure 2.2<br>Figure 2.3 | Factors Creating the Bathtub Curve                                                       |    |

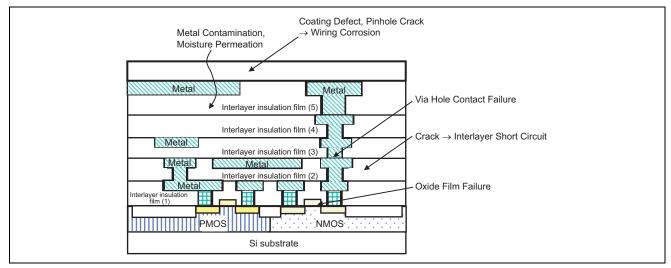

| Figure 2.3<br>Figure 2.4 | Semiconductor Device Cross-Section                                                       |    |

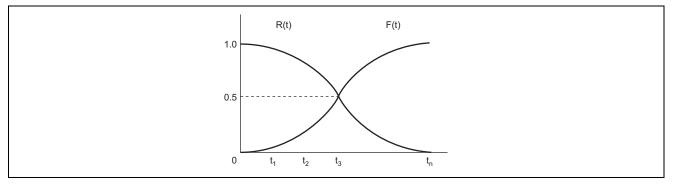

| Figure 2.4<br>Figure 2.5 | Relation of R(t) and F(t)                                                                |    |

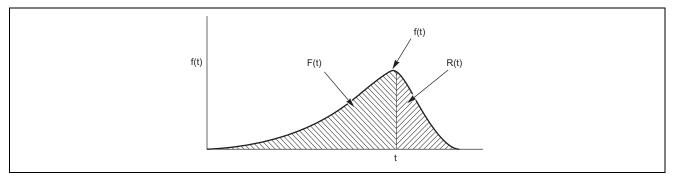

| Figure 2.6               | Schematic of f(t), R(t), F(t)                                                            |    |

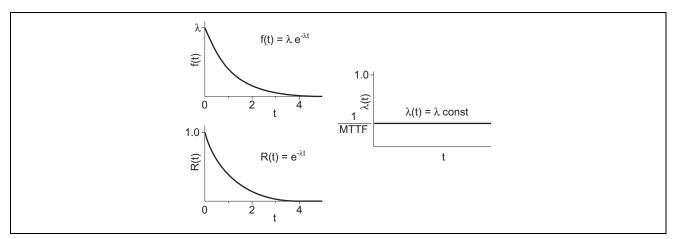

| Figure 2.7               | Exponential Distribution                                                                 |    |

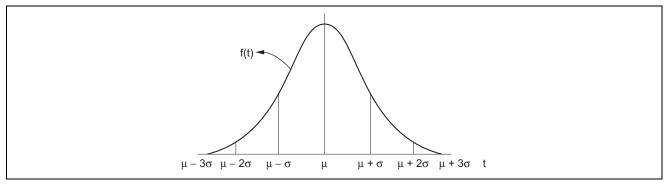

| Figure 2.8               | Normal Distribution                                                                      |    |

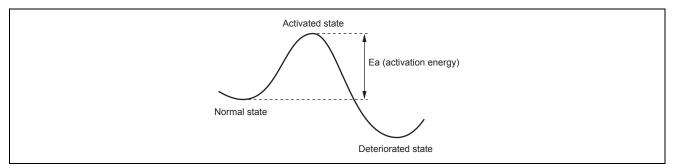

| Figure 2.9               | Activation Energy                                                                        |    |

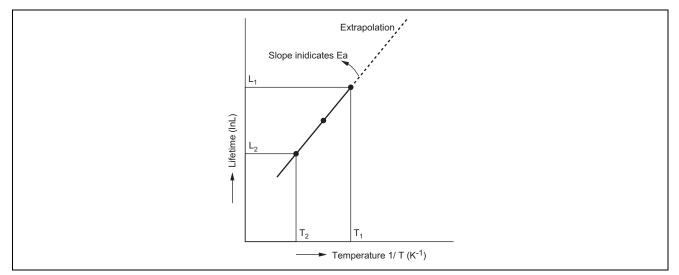

| Figure 2.10              | Schematic of the Arrhenius Model                                                         |    |

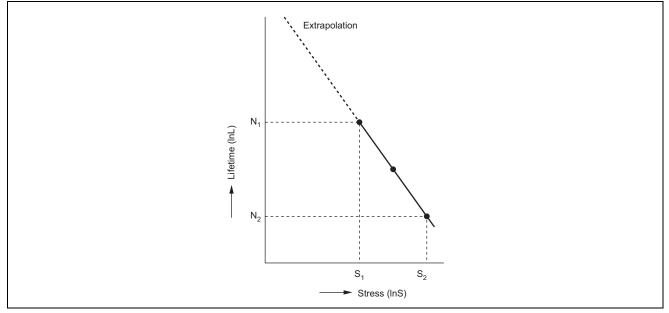

| Figure 2.10              | Schematic of the Eyring Model                                                            |    |

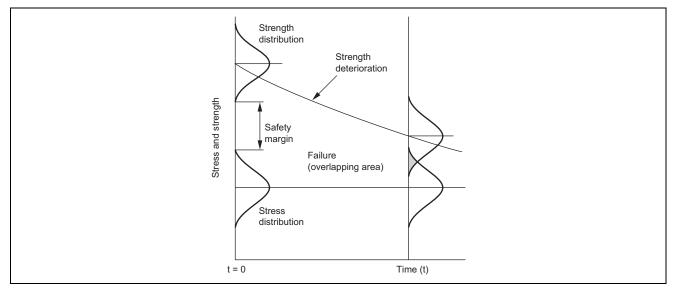

| Figure 2.12              | Stress Strength Model                                                                    |    |

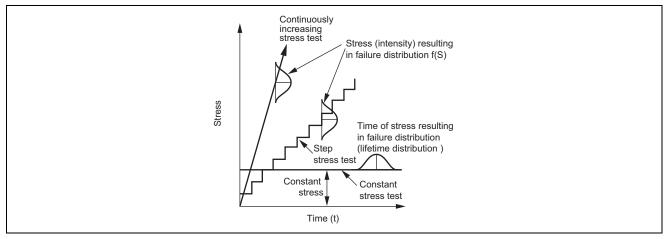

| Figure 2.12              | The Outline of Each Stress Tests                                                         |    |

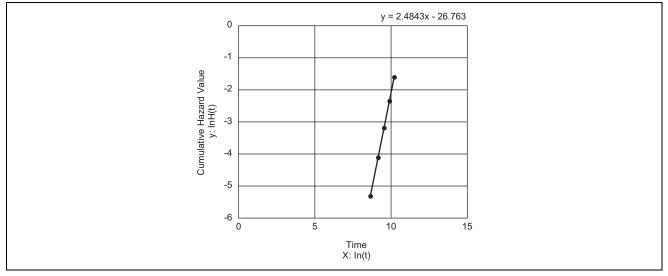

| Figure 2.14              | Life Prediction through Weibull Plotting                                                 |    |

| Figure 2.14              | Lifetime Distribution Plot on Weibull Cumulative Hazard Paper                            |    |

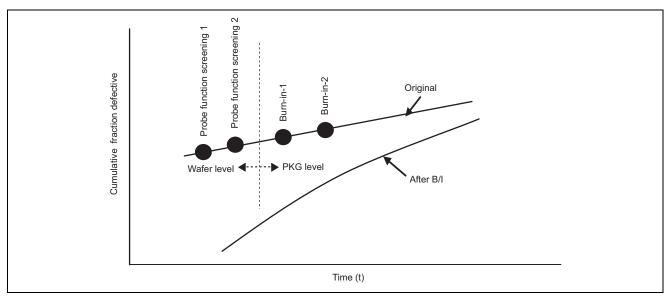

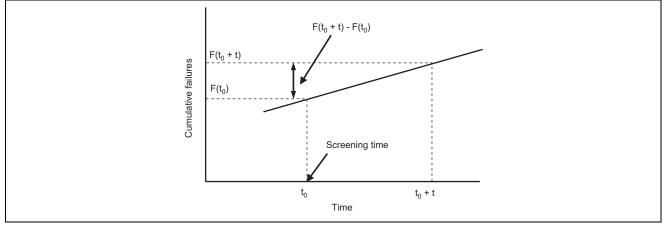

| Figure 2.16              | Post Screening (Future) Lifetime                                                         |    |

| 1 igure 2.10             | Tost Screening (Future) Elictime                                                         |    |

| 3. Failure N             | Mechanisms                                                                               |    |

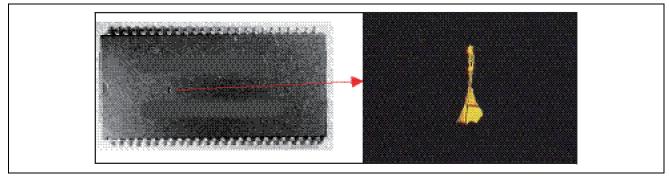

| Figure 3.1               | Gate Pinhole                                                                             |    |

| Figure 3.2               | Al Wiring Coverage Disconnection                                                         |    |

| Figure 3.3               | Crack                                                                                    |    |

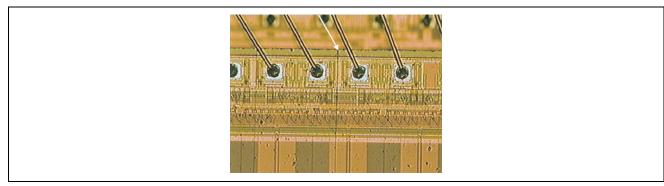

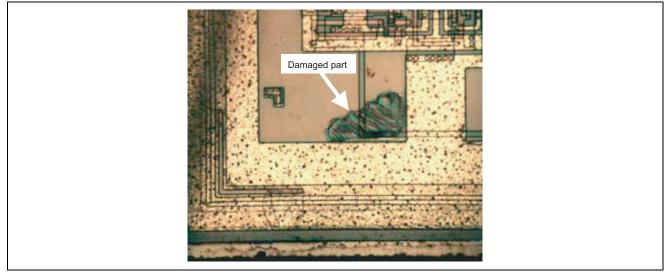

| Figure 3.4               | Damage under Bonding (Bottom View)                                                       |    |

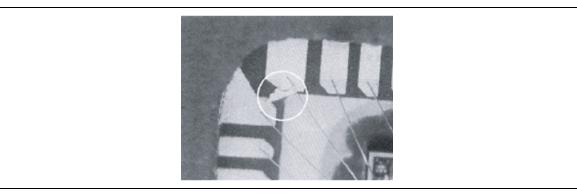

| Figure 3.5               | Damage on Wire Due to Ultrasonic Fatigue                                                 |    |

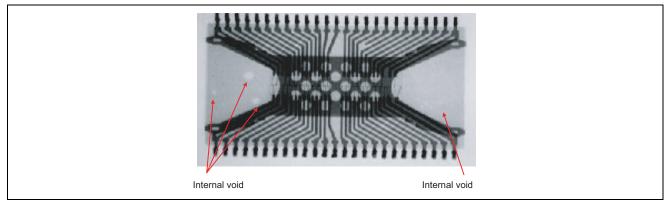

| Figure 3.6               | Internal Voids in Package                                                                |    |

| Figure 3.7               | No Molding Resin Injected                                                                |    |

| Figure 3.8               | Short Circuit Due to Conductive Particles in Package                                     |    |

| Figure 3.9               | Terminal Breakdown Due to Overvoltage                                                    |    |

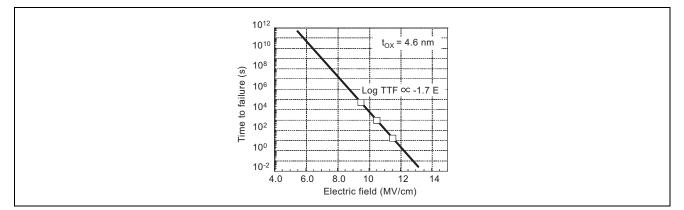

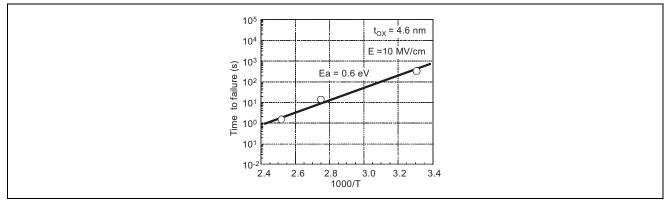

| Figure 3.10              | Electric Field Dependency of TDDB                                                        |    |

| Figure 3.11              | Temperature Dependency of TDDB                                                           | 49 |

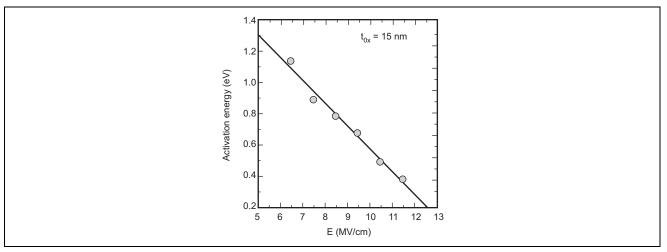

| Figure 3.12              | Electric-Field Dependency of Activation Energy                                           |    |

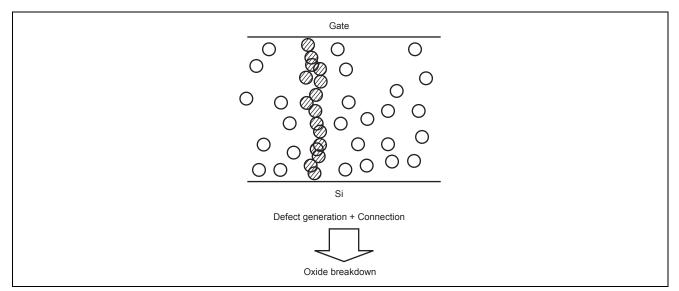

| Figure 3.13              | Dielectric Breakdown Mechanism                                                           | 50 |

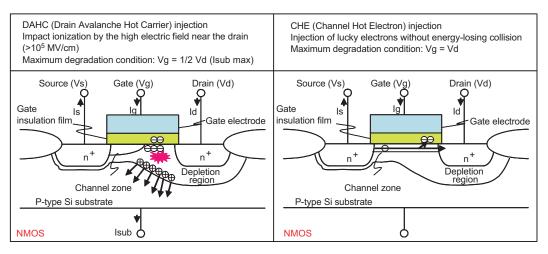

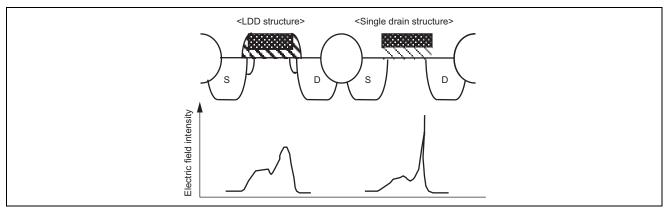

| Figure 3.14              | Major Mechanisms of Hot Carrier Injection                                                |    |

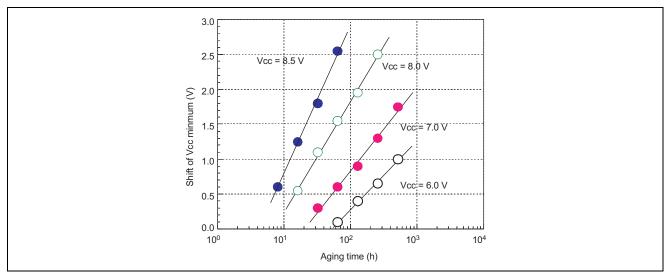

| Figure 3.15              | Supply Voltage (Drain Voltage) Dependency of Degradation                                 |    |

| Figure 3.16              | LDD Structure                                                                            |    |

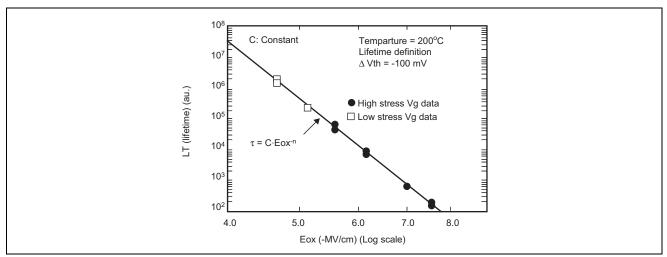

| Figure 3.17              | Electric field Dependency of Device Life                                                 |    |

| Figure 3.18              | Failure Mechanism                                                                        |    |

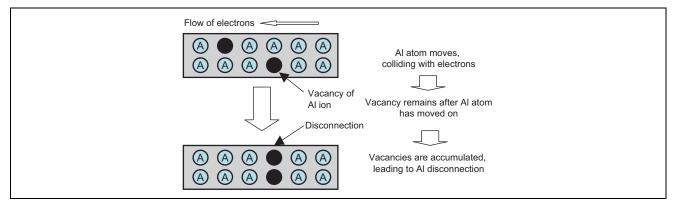

| Figure 3.19              | Electromigration of Al Wire                                                              |    |

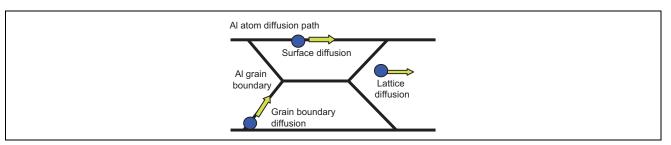

| Figure 3.20              | Lattice Diffusion, Grain Boundary Diffusion, and Surface Diffusion of Polycrystalline Al |    |

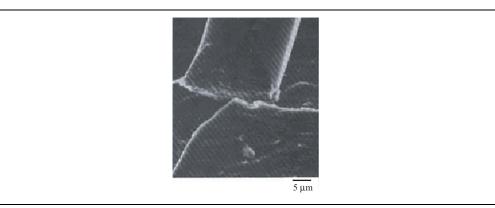

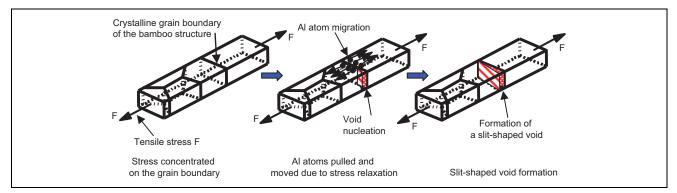

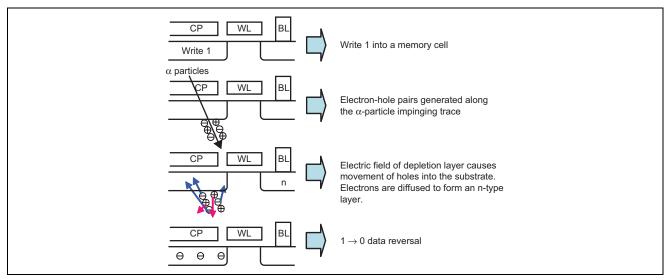

| Figure 3.21              | Mechanism of Slit-Shaped Void Formation                                                  |    |

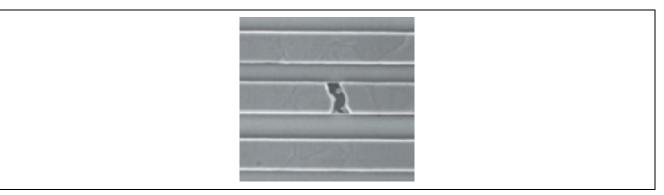

| Figure 3.22              | Slit-Shaped Void                                                                         |    |

| Figure 3.23              | Wedge-Shaped Void                                                                        |    |

| Figure 3.24              | Incorrect Operation in Memory Cell                                                       |    |

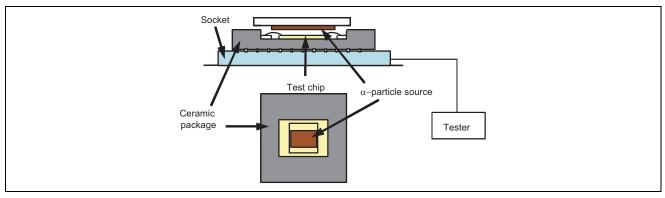

| Figure 3.25              | Accelerated Soft Error Evaluation System                                                 |    |

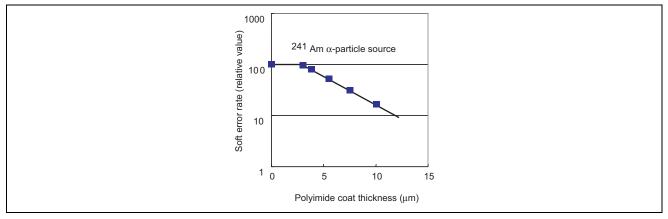

| Figure 3.26              | Soft Error Prevention Effect of Polyimide Coating                                        |    |

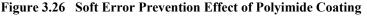

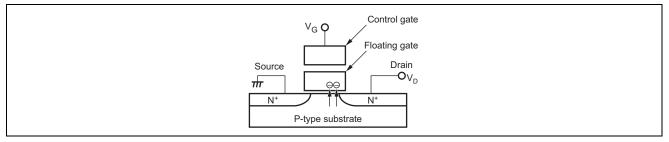

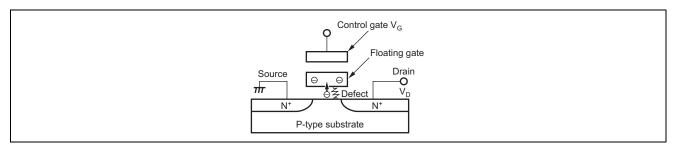

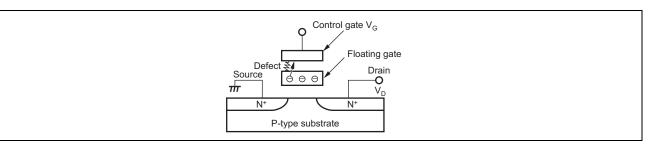

| Figure 3.27              | Stack Type Memory Cell Cross-section                                                     | 59 |

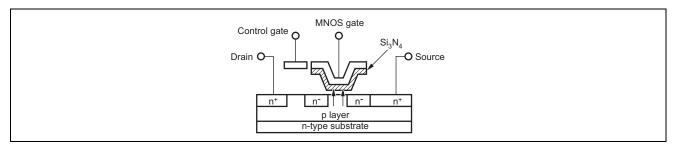

| Figure 3.28 | MNOS Memory Cell Cross-section                                                               | 59 |

|-------------|----------------------------------------------------------------------------------------------|----|

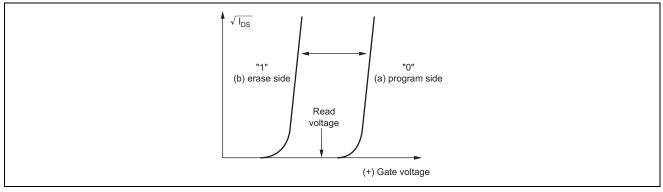

| Figure 3.29 | Stack-Type Memory Cell Vth Change                                                            |    |

| Figure 3.30 | Gate Oxide Defect Mode (Charge Gain)                                                         | 61 |

| Figure 3.31 | Interlayer Film Defect Mode (Charge Loss)                                                    | 61 |

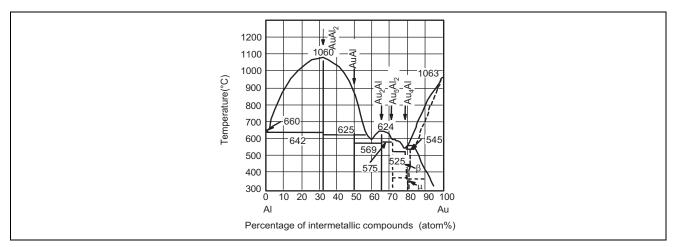

| Figure 3.32 | Phase Diagram for Au-Al Alloy                                                                | 62 |

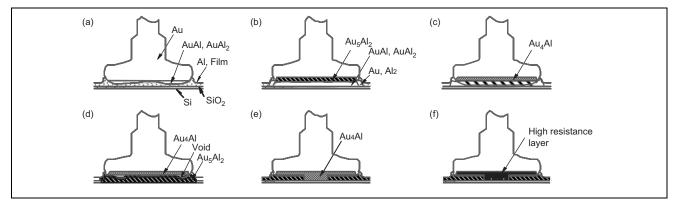

| Figure 3.33 | Au-Al Alloy State Chart                                                                      | 63 |

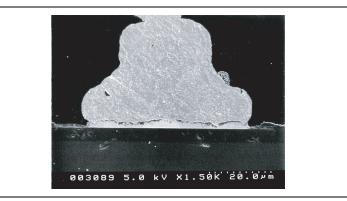

| Figure 3.34 | Cross-section of Au-ball Joint (SEM Image)                                                   | 64 |

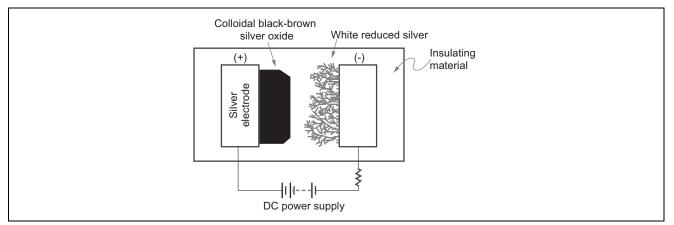

| Figure 3.35 | Generation of Silver Ion Migration                                                           | 65 |

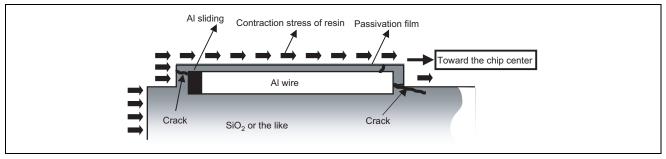

| Figure 3.36 | Example of Al Sliding                                                                        | 67 |

| Figure 3.37 | Chip Corner Al Wiring Cross Section                                                          | 67 |

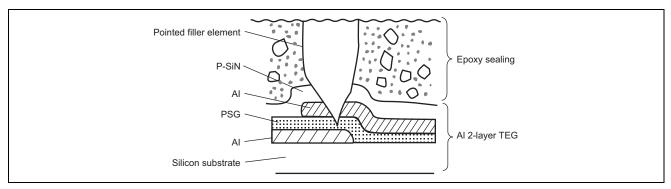

| Figure 3.38 | Cross Section of a Semiconductor Device in the Vicinity of the Chip Surface                  | 68 |

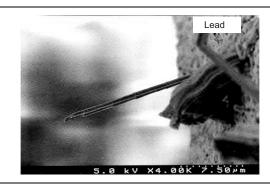

| Figure 3.39 | Example of Whisker Generation                                                                | 69 |

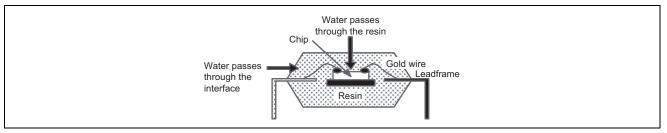

| Figure 3.40 | Water Penetration Path in a Plastic Mold Device                                              | 70 |

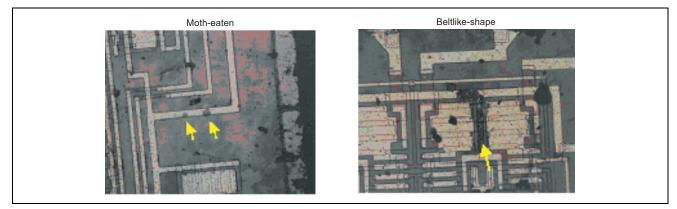

| Figure 3.41 | Al Corrosion During Storage with High Humidity and High Temperature                          | 71 |

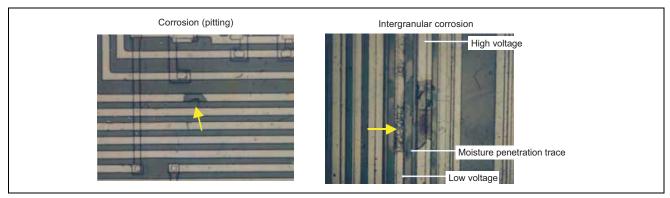

| Figure 3.42 | Al Corrosion on High Humidity and High Temperature Bias                                      | 71 |

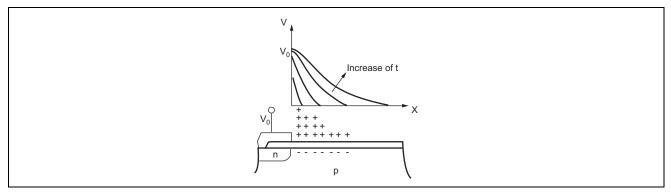

| Figure 3.43 | Surface Charge Expansion Phenomenon                                                          | 72 |

| Figure 3.44 | Example of Acceleration                                                                      | 73 |

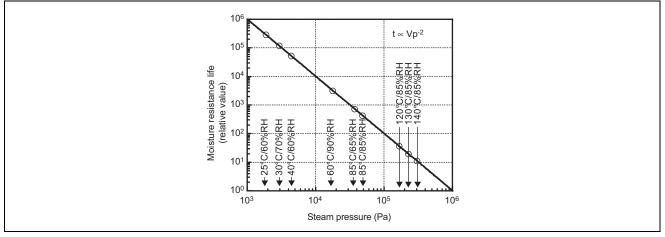

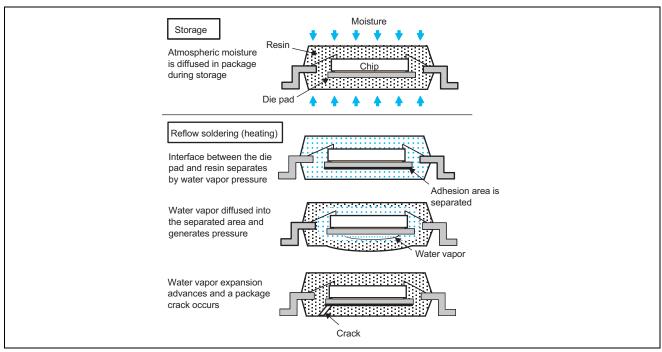

| Figure 3.45 | Model of Crack Generation in Reflow Soldering                                                | 76 |

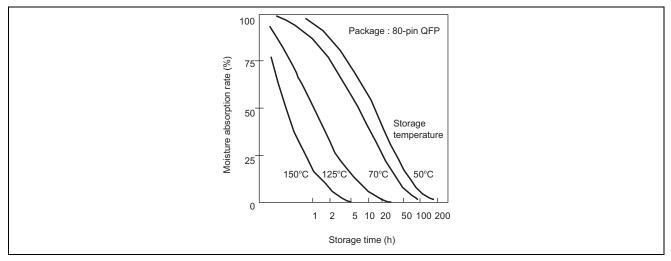

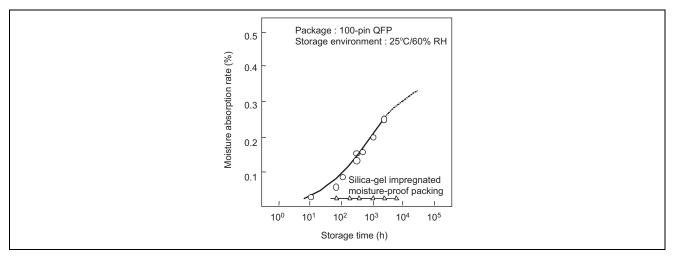

| Figure 3.46 | Dehumidification of Plastic Packages                                                         | 77 |

| Figure 3.47 | Effect of the Moisture-proof Pack                                                            | 77 |

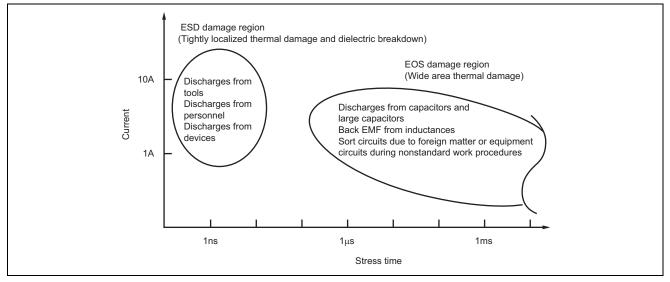

| Figure 3.48 | Differences Between the ESD and EOS Stress Regions                                           | 79 |

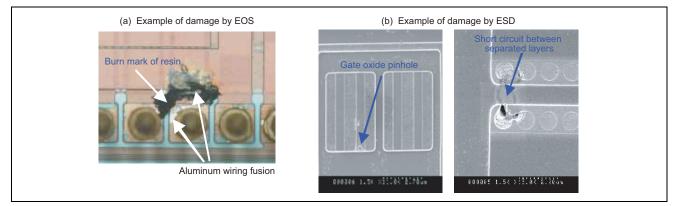

| Figure 3.49 | Example of Comparison between EOS Damage and ESD Damage                                      | 81 |

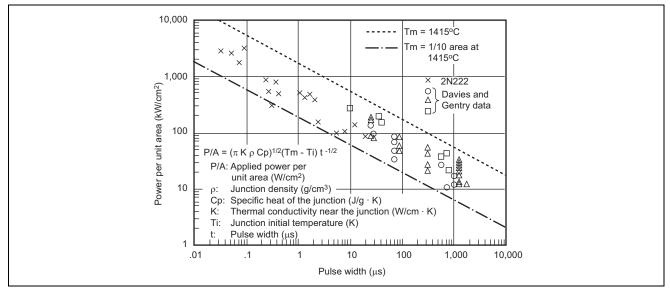

| Figure 3.50 | Wunsch & Bell Plot                                                                           | 82 |

| Figure 3.51 | Triboelectric Charging                                                                       | 83 |

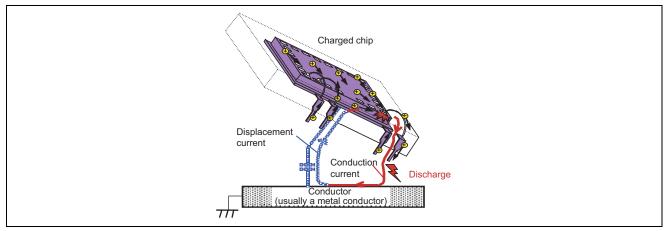

| Figure 3.52 | Discharge by Electrostatic Induction and Charging                                            | 83 |

| Figure 3.53 | Contact Charging and Discharging                                                             | 83 |

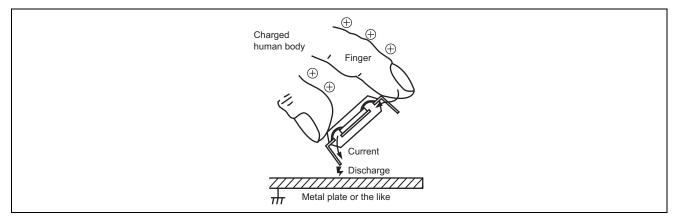

| Figure 3.54 | Discharge Model based on Human Body Model                                                    |    |

|             | (Model in which a Conduction Current Flows between Device Pins)                              | 84 |

| Figure 3.55 | Discharge Model based on Changed Device Model (Model in which an Conduction Current Flows to |    |

| -           | the Discharging Pin and a Displacement Current Flows to the Device Capacitance)              | 84 |

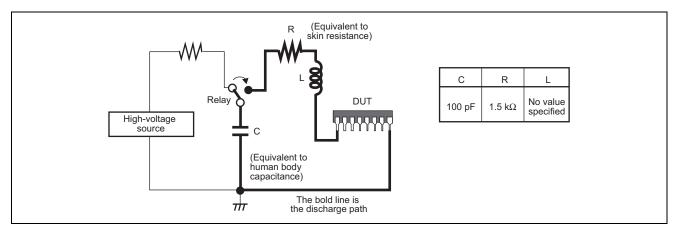

| Figure 3.56 | Test Circuit for Human Body Model                                                            | 85 |

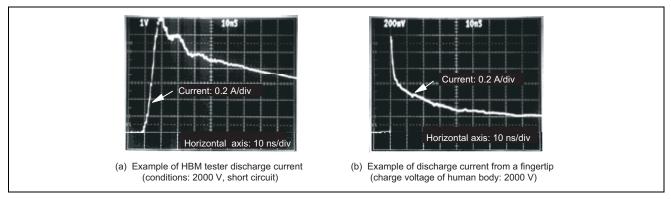

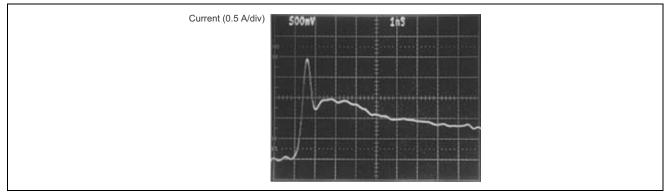

| Figure 3.57 | Comparison of Human Body and HBM Tester Discharge Currents                                   | 85 |

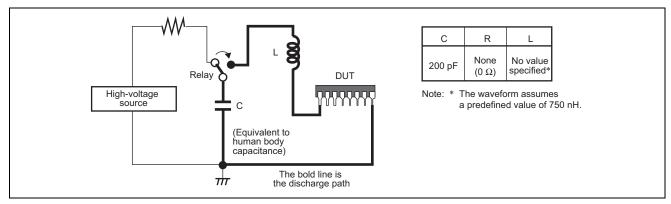

| Figure 3.58 | Machine Model Test Circuit                                                                   |    |

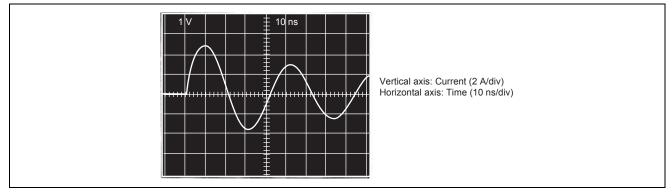

| Figure 3.59 | Discharge Waveform for Machine Model Test (Example with a Low Inductance L)                  |    |

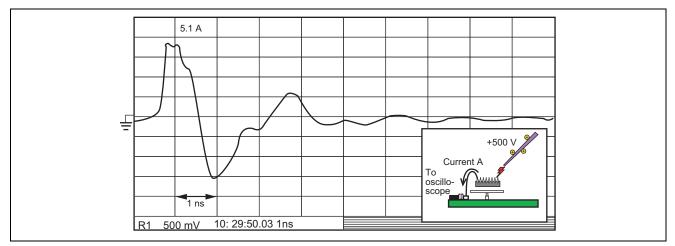

| Figure 3.60 | Discharge Waveform of Charged Metal Tweezers                                                 |    |

| C           | (Completely Different from That of the Machine Model)                                        | 87 |

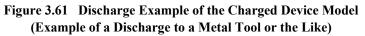

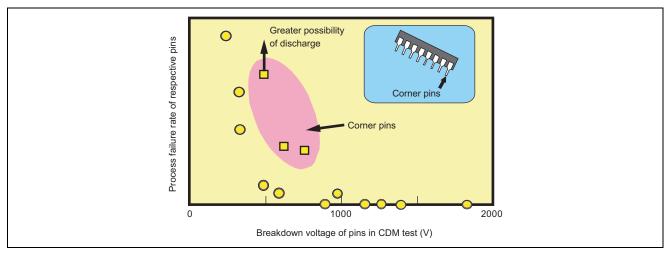

| Figure 3.61 | Discharge Example of the Charged Device Model                                                |    |

| U           | (Example of a Discharge to a Metal Tool or the Like)                                         | 87 |

| Figure 3.62 | Discharge Waveform for Charged Device Model (Measured with a 3.5-GHz Oscilloscope)           |    |

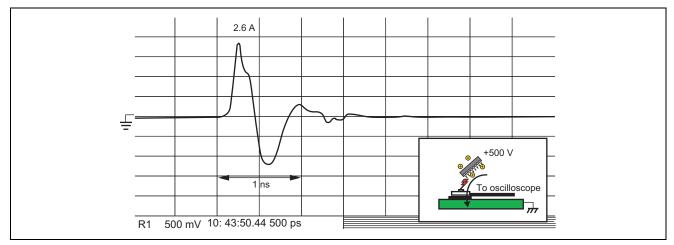

| Figure 3.63 | Example of CDM Test Circuit (Device is Charged from High-Voltage Source, Relay is Closed,    |    |

| C           | and Device is Discharged to a Ground Bar)                                                    | 88 |

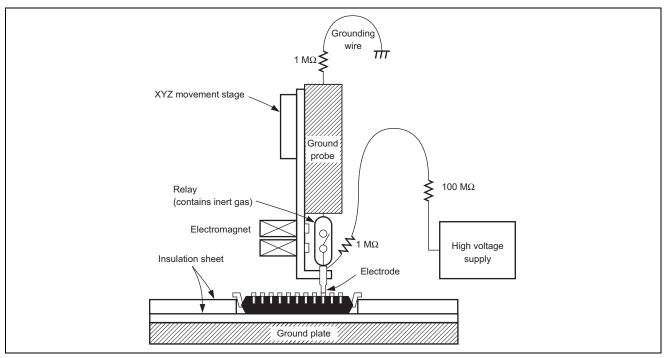

| Figure 3.64 | Relationship between Fraction Defective in Package Assembly Process and CDM Test Intensity   | 89 |

| Figure 3.65 | Example of Complex Discharge on HBM and CDM                                                  |    |

| Figure 3.66 | Example of Complex Discharge Current Waveform                                                | 90 |

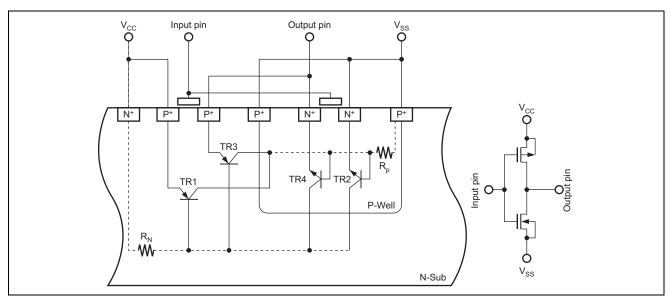

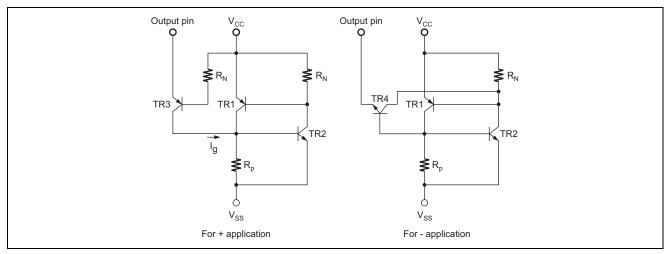

| Figure 3.67 | Cross Section of CMOS Inverter                                                               |    |

| Figure 3.68 | Parasitic Thyristor Equivalent Circuit                                                       |    |

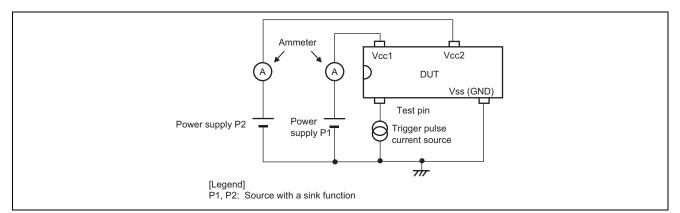

| Figure 3.69 | Latchup Test Circuit (Pulse Current Injection Method)                                        |    |

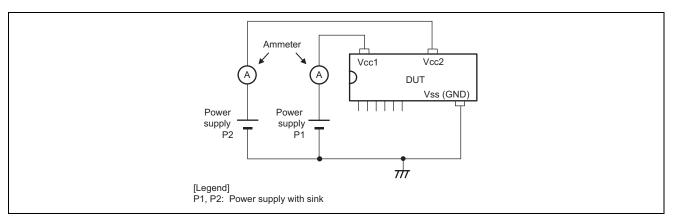

| Figure 3.70 | Latchup Test Circuit (Power Supply Over-Voltage Method)                                      |    |

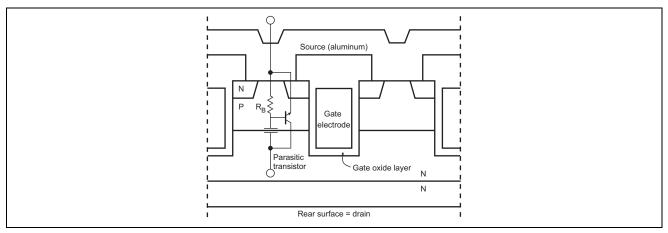

| Figure 3.71 | Section View of Power MOS FET                                                                |    |

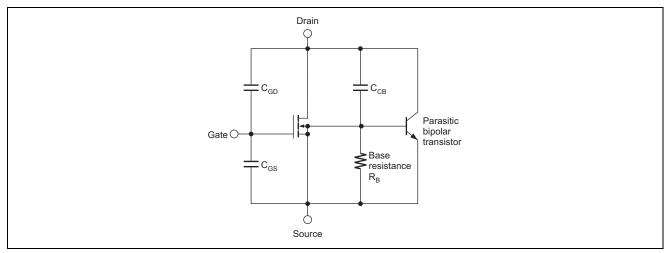

| Figure 3.72 | Equivalent Circuit of a Power MOS FET                                                        |    |

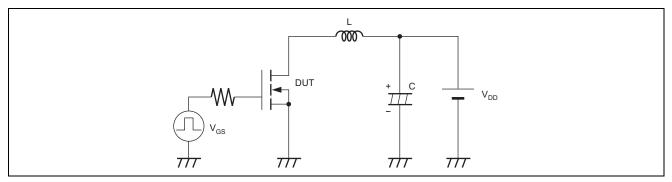

| Figure 3.73 | Avalanche Tolerance Evaluation Circuit Diagram                                               |    |

| Figure 3.74 | Avalanche Waveforms                                                                          |    |

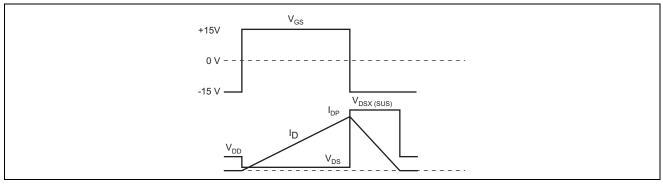

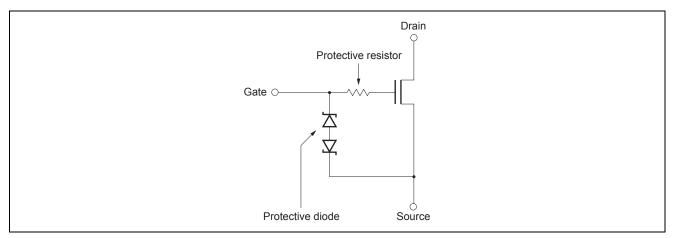

| Figure 3.75 | Gate Protection Circuit                                                                      |    |

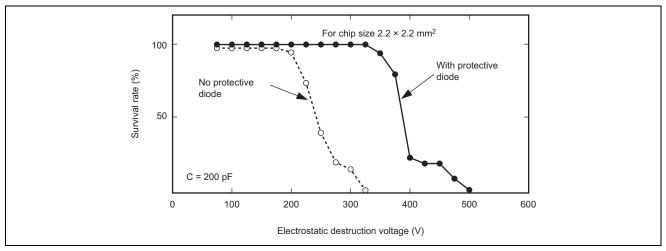

| Figure 3.76 | Electrostatic Discharge Strength of a Gate Oxide Film.                                       |    |

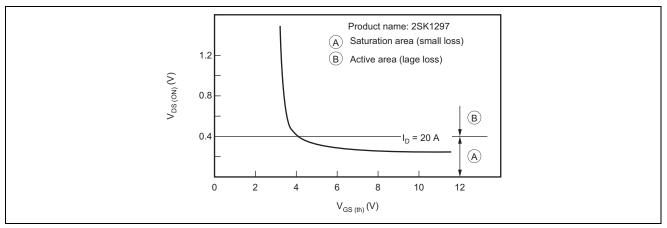

| Figure 3.77 | Vds(ON) - Vgs(th) Characteristics in Practical Use                                           |    |

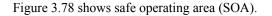

| Figure 3.78 | Safe Operating Area (SOA)                                                                    |    |

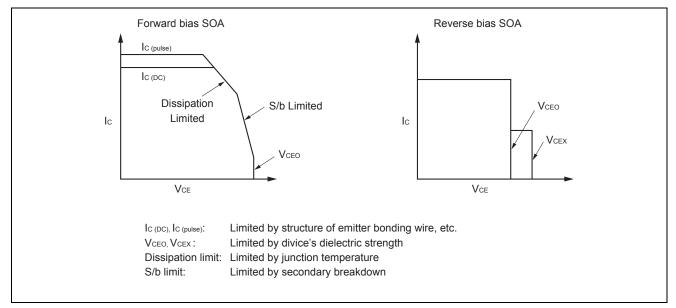

| Figure 3.79 | Safe Operating Area During Switching Operation                                               |    |

| Figure 3.80 | Breakdown Phenomena During Secondary Breakdowns                                     |     |

|-------------|-------------------------------------------------------------------------------------|-----|

| 4. Failure  | Analysis                                                                            |     |

| Figure 4.1  | General Failure Analysis Procedure                                                  |     |

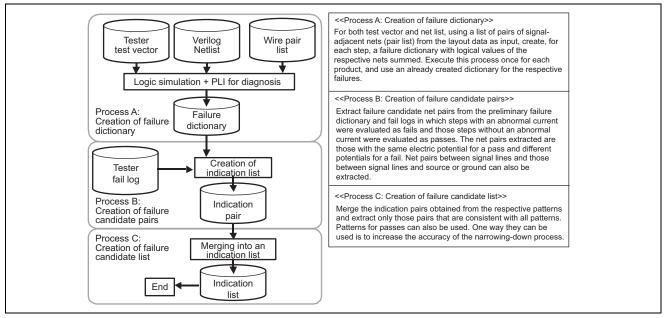

| Figure 4.2  | Analysis Flow with Failure Diagnosis                                                |     |

| Figure 4.3  | Function Test Failure Diagnosis Flow                                                |     |

| Figure 4.4  | Current System Test Failure Diagnosis Flow                                          |     |

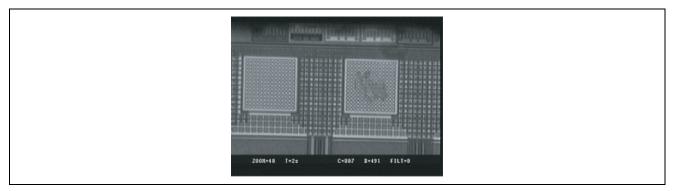

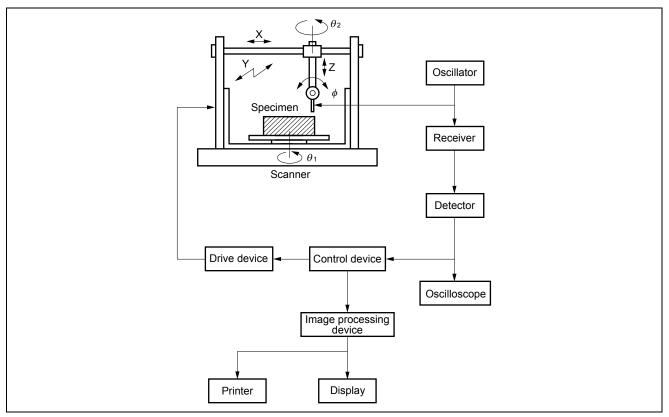

| Figure 4.5  | Configuration Diagram of SAT Device                                                 |     |

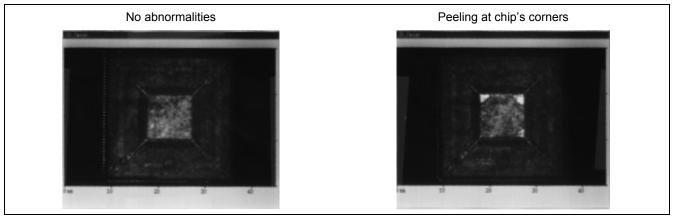

| Figure 4.6  | Observation Result of Adhesion Strength between Chip and Mold Resin                 |     |

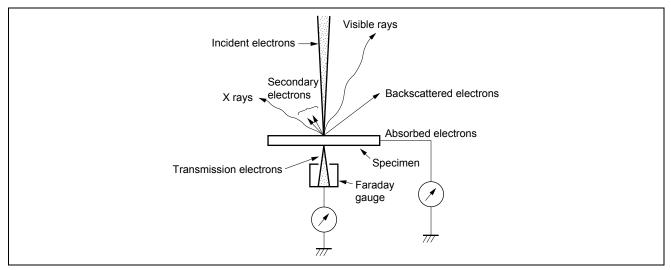

| Figure 4.7  | Electrons and X Rays Reflected from Surface of Specimen                             |     |

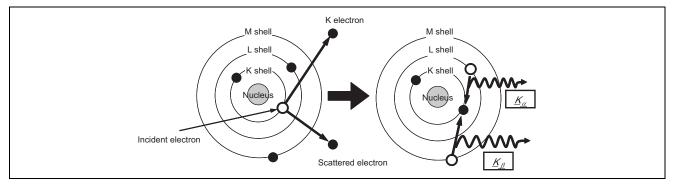

| Figure 4.8  | Characteristic X-Ray Generation Mechanism                                           |     |

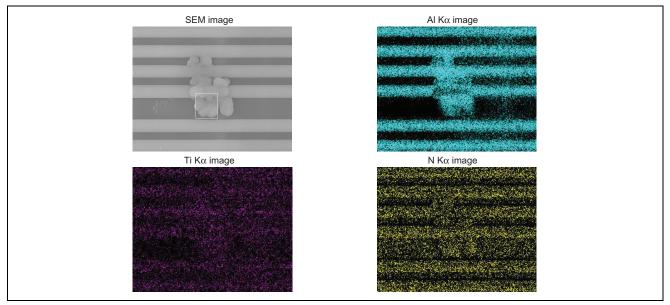

| Figure 4.9  | EPMA Analysis Results for an Al Wiring Pattern Defect                               |     |

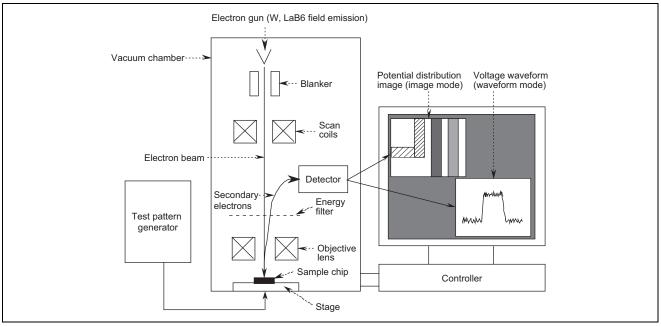

| Figure 4.10 | Outline Drawing of EB Tester                                                        |     |

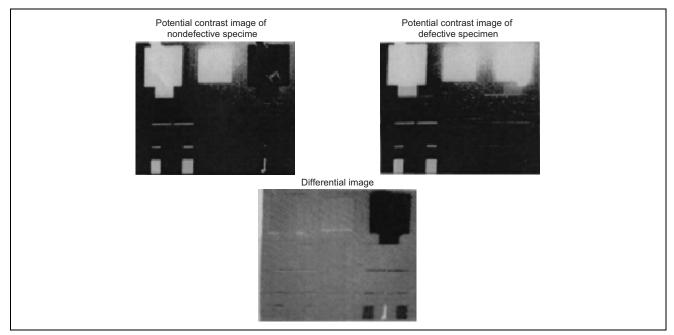

| Figure 4.11 | Potential Contrast Images                                                           |     |

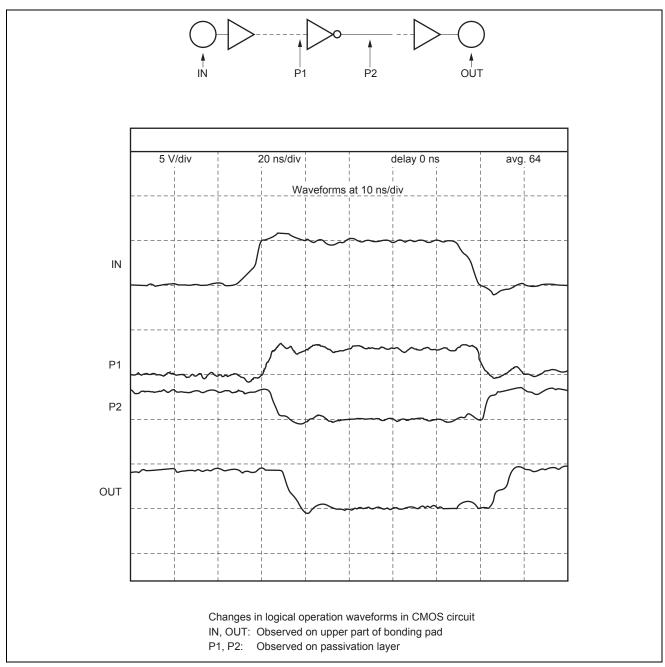

| Figure 4.12 | Logical Operation Waveforms                                                         |     |

| Figure 4.13 | AFI Image                                                                           |     |

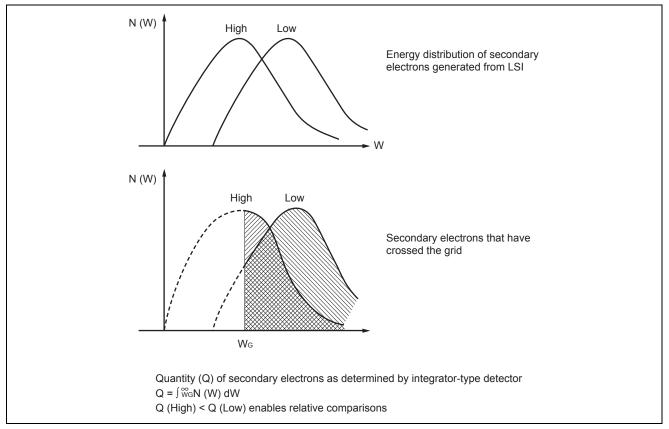

| Figure 4.14 | Energy Distribution of Secondary Electrons                                          |     |

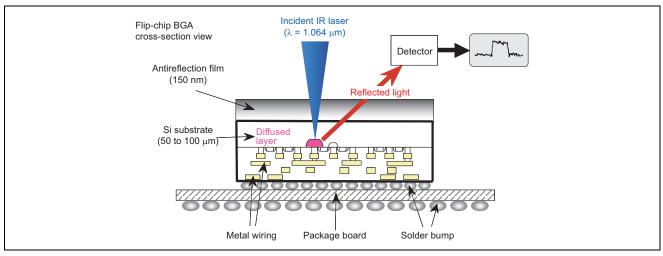

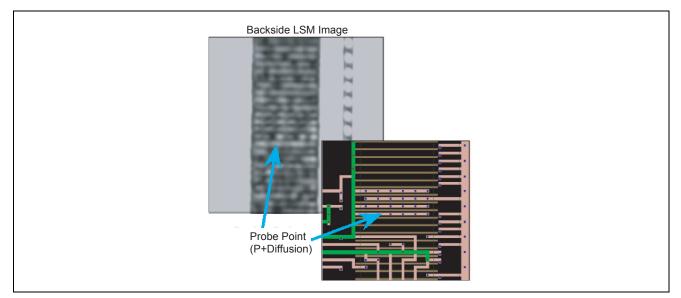

| Figure 4.15 | LVP Principle                                                                       |     |

| Figure 4.16 | Laser Scanned Image/Layout                                                          |     |

| Figure 4.17 | LVP Potential                                                                       |     |

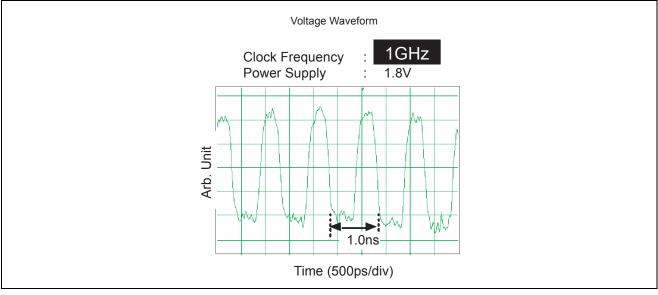

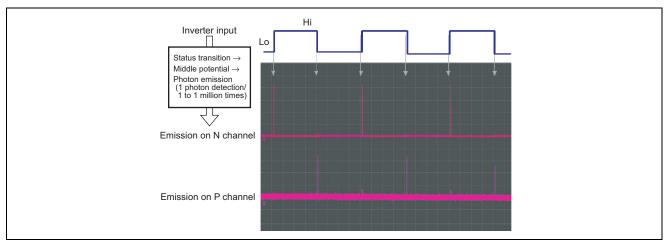

| Figure 4.18 | TRE Waveform for n-ch/p-ch Transistor                                               |     |

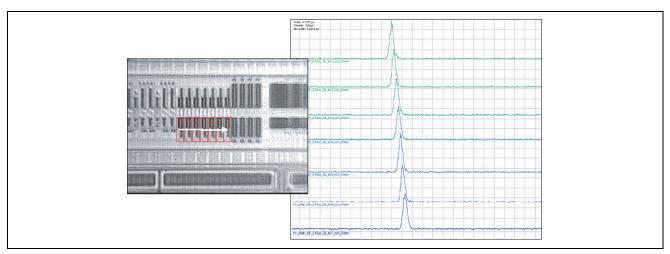

| Figure 4.19 | SIL-Employed Inverter Chain TRE Waveform Measurements                               |     |

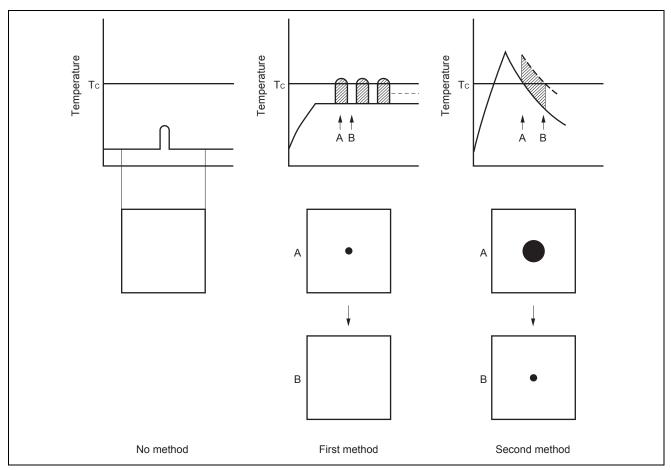

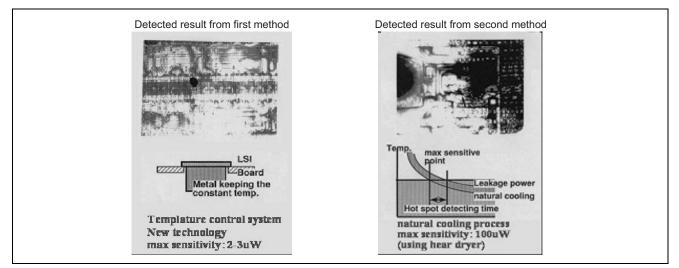

| Figure 4.20 | Method for Detection of Slight Hot Spots                                            |     |

| Figure 4.21 | Detected Result of Slight Hot Spots                                                 |     |

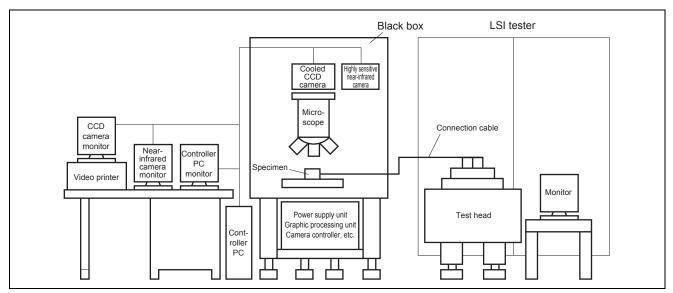

| Figure 4.22 | Outline Drawing of Photoemission Microscope System (When Linked to LSI Tester)      |     |

| Figure 4.23 | Emitted Photon Observation Examples                                                 |     |

| Figure 4.24 | Configuration Required to Implement OBIRCH.                                         |     |

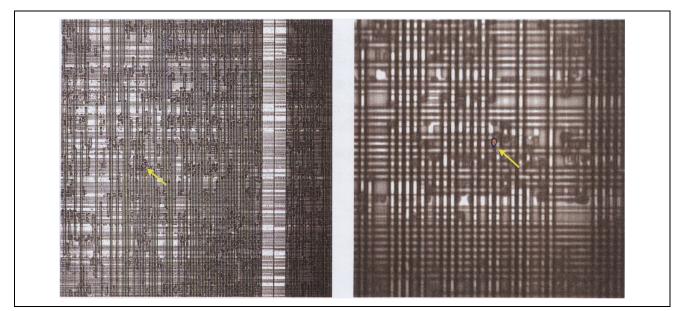

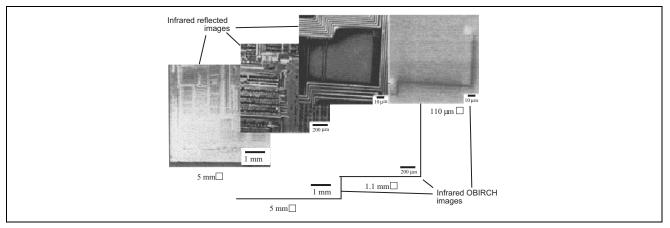

| Figure 4.25 | Current Path Observation Example                                                    |     |

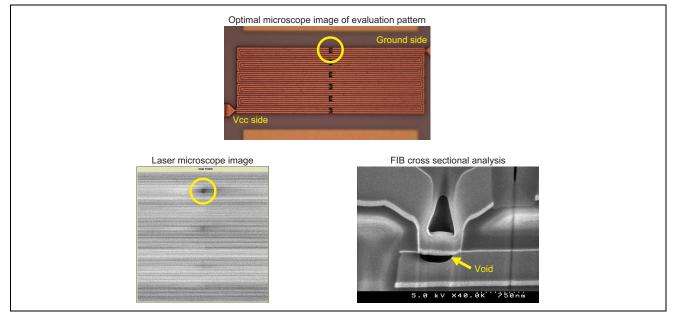

| Figure 4.26 | Example of Detected Voids in Via                                                    |     |

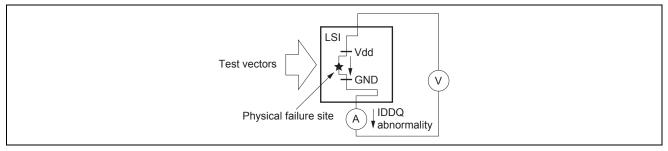

| Figure 4.27 | Penetration Current from VDD to GND Passing Through Physical Damage                 |     |

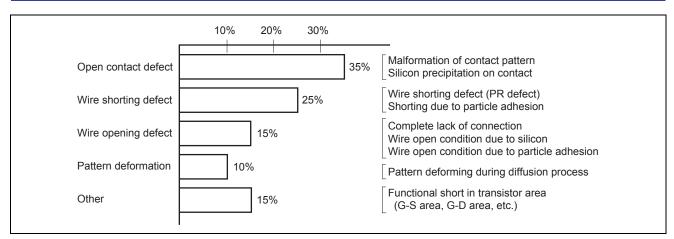

| Figure 4.28 | Graph of General Relation for Devices with Logical Operation Defects and Items      |     |

| 0           | with IDDQ Defects                                                                   | 127 |

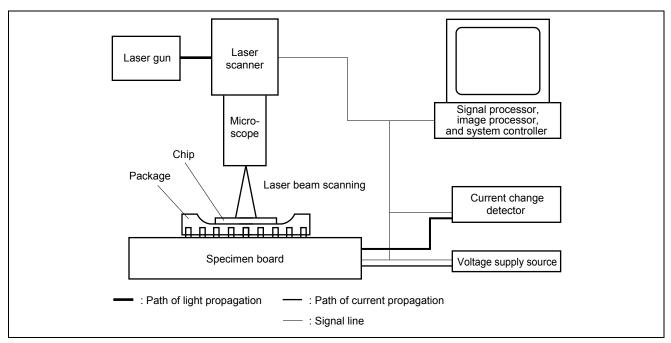

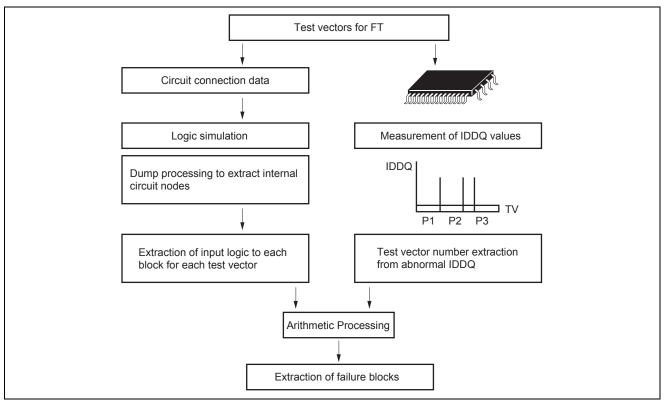

| Figure 4.29 | Failure Site Detection Method Using CAD Data and Test Vector Data for Abnormal IDDQ |     |

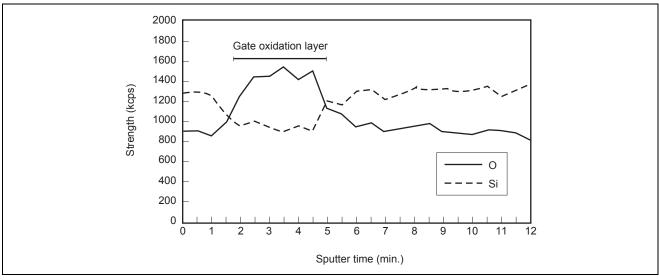

| Figure 4.30 | Depth Profile of Gate Oxide Layer                                                   |     |

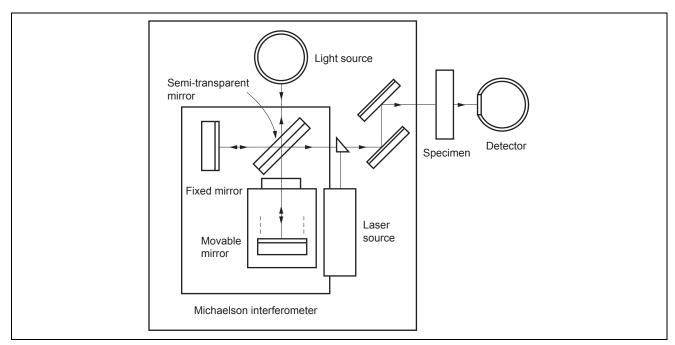

| Figure 4.31 | Configuration of FT-IR System                                                       |     |

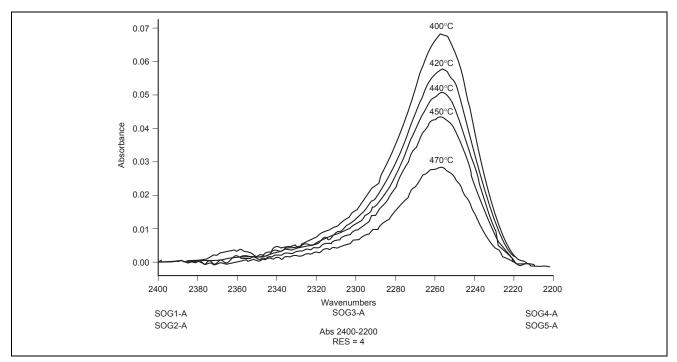

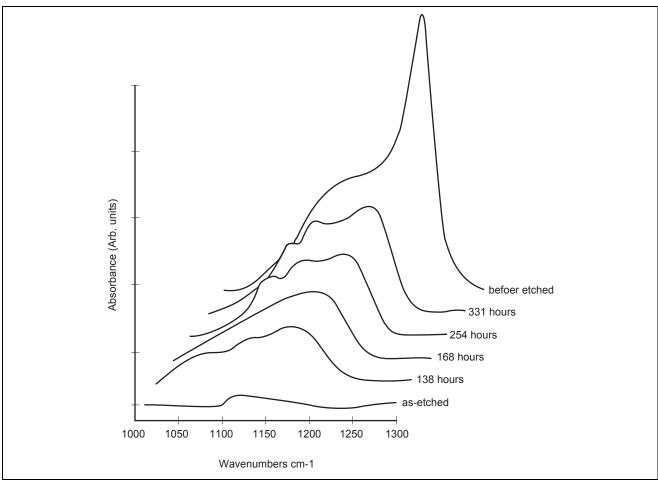

| Figure 4.32 | Temperature Changes at Peak Elasticity and Vibration Values for Si-H in SOG         |     |

| 8           | (Spin On Glass) Layer                                                               | 131 |

| Figure 4.33 | Growth Process of Silicon Native Oxide                                              |     |

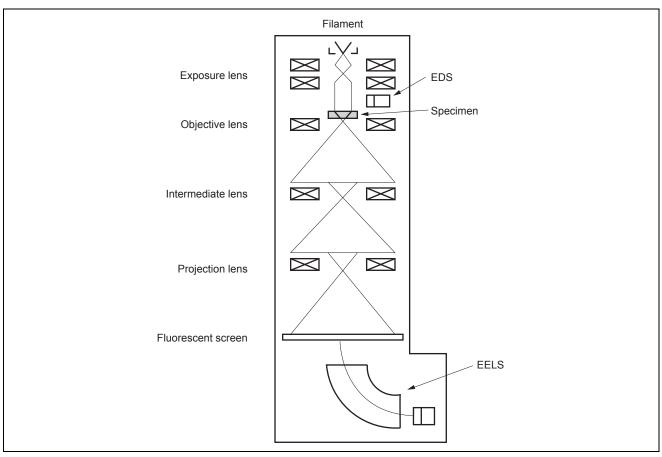

| Figure 4.34 | Outline of TEM System                                                               |     |

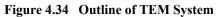

| Figure 4.35 | TEM Observation Example                                                             |     |

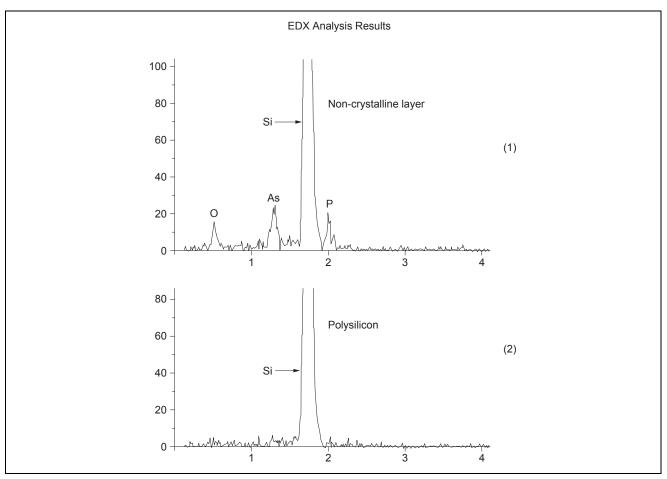

| Figure 4.36 | EDX Profile                                                                         |     |

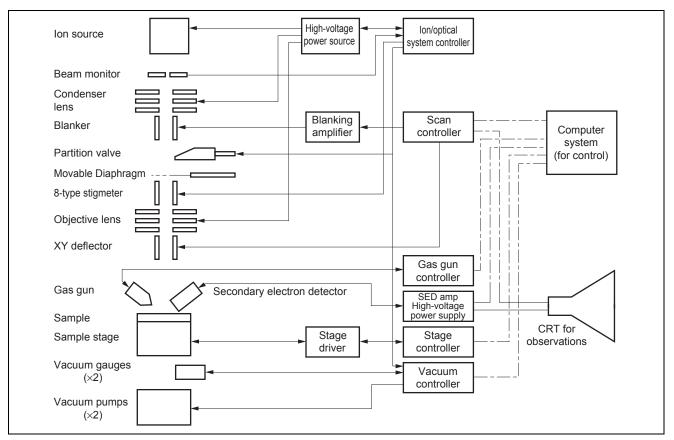

| Figure 4.37 | Outline of FIB System                                                               |     |

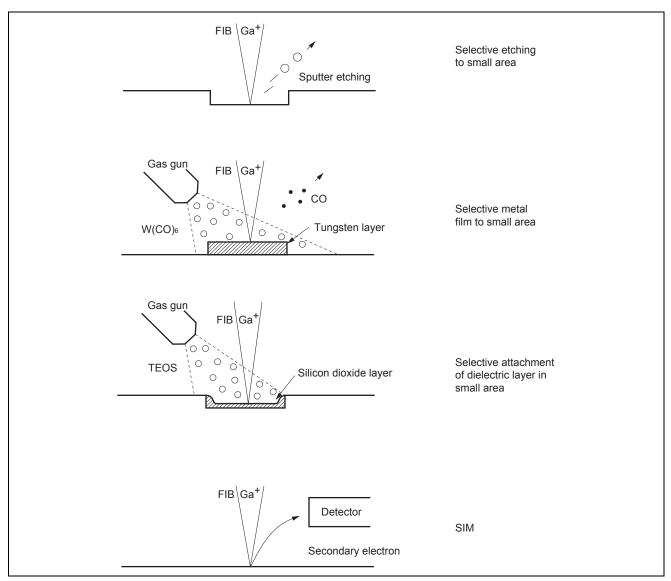

| Figure 4.38 | Four Functions of FIB                                                               |     |

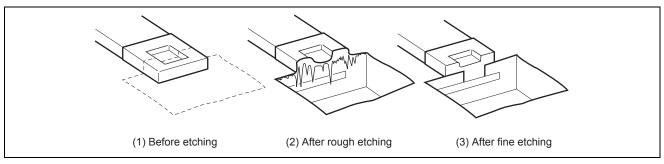

| Figure 4.39 | Cross-Sectioning Method Using FIB                                                   |     |

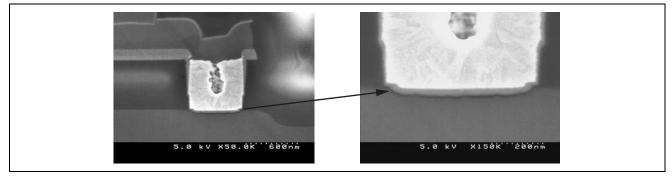

| Figure 4.40 | Cross Sectional Analysis Example 1 (poor contact)                                   |     |

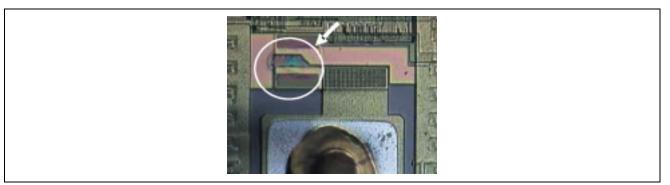

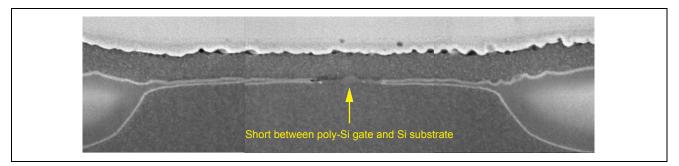

| Figure 4.41 | Cross Sectional Analysis Example 2 (gate oxide film destruction)                    |     |

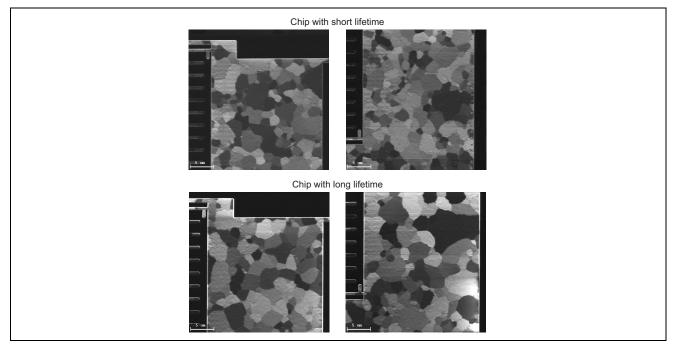

| Figure 4.42 | Al Grain Observation Using SIM Imaging                                              |     |

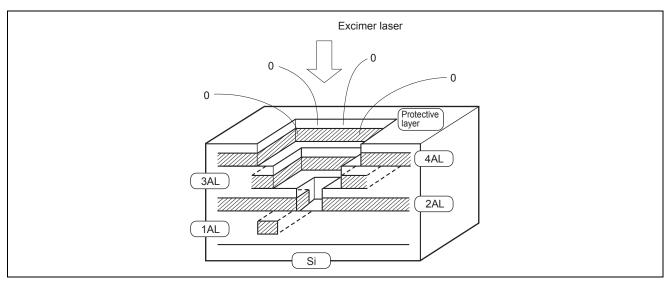

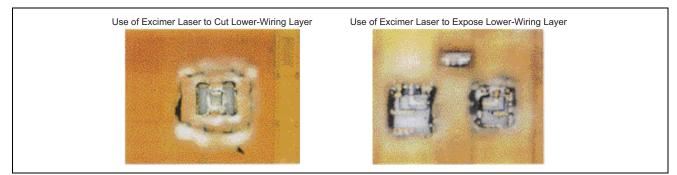

| Figure 4.43 | Use of Excimer Laser for Peeling Processing                                         |     |

| Figure 4.44 | Examples of Processing Using Excimer Laser                                          |     |

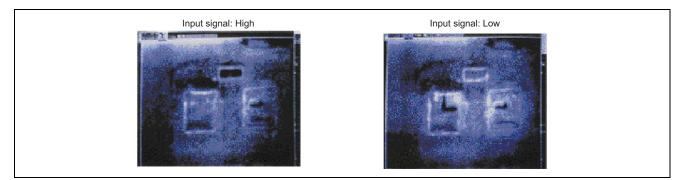

| Figure 4.45 | Use of EB Tester to Obtain Potential Contrast Image of Observed Lower-Wiring Layer  |     |

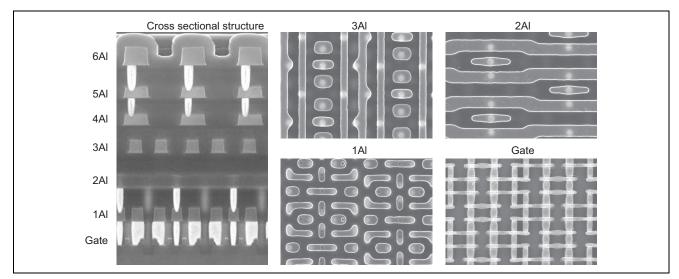

| Figure 4.46 | IC Chip Layer Removal Examples Using Polishing and RIE                              |     |

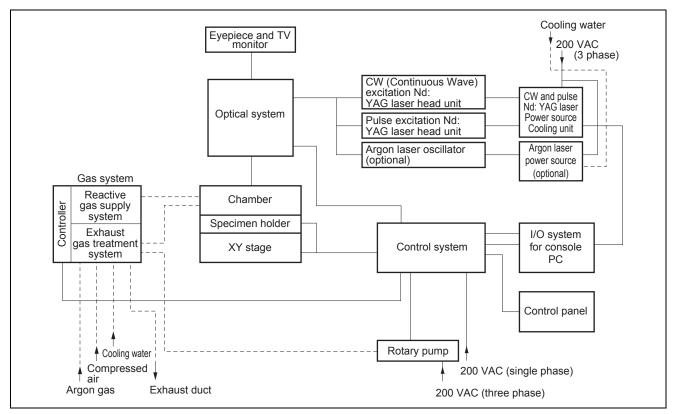

| Figure 4.47 | Outline of FLB System                                                               |     |

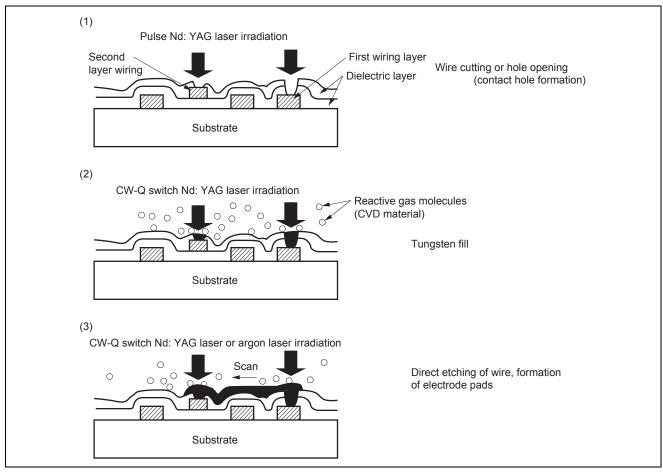

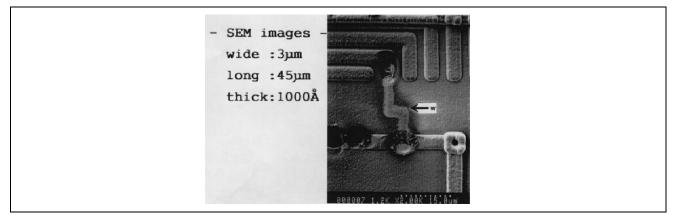

| Figure 4.48 | Microprocessing by FLB                                                              |     |

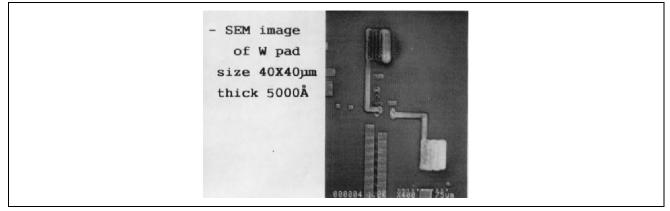

| Figure 4.49 | Bypass Formation Example                                                            |     |

| Figure 4.50 | Example of Probing Pad Formation                                                    |     |

| 5. Basic Re                | ecommendations for Handling and Using Semiconductor Devices                                                                       |     |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

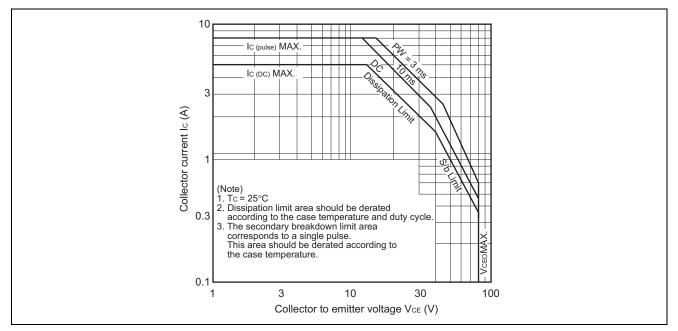

| Figure 5.1                 | Example of Safe Operating Area                                                                                                    | 163 |

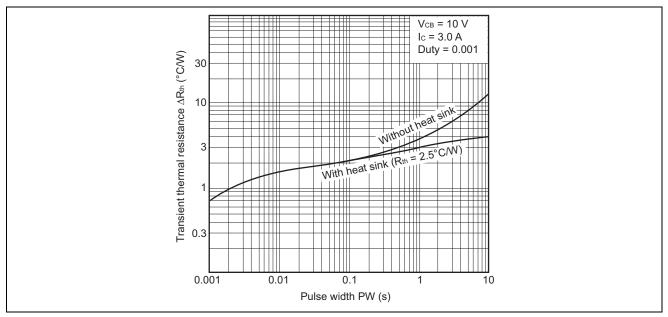

| Figure 5.2                 | Example of Transient Thermal Resistance                                                                                           |     |

| Figure 5.3                 | Example of LSI with Reset Signal Input Pin                                                                                        | 171 |

| Figure 5.4                 | Caution Concerning Load Driver                                                                                                    | 171 |

| Figure 5.5                 | Caution Concerning Load Driver                                                                                                    | 171 |

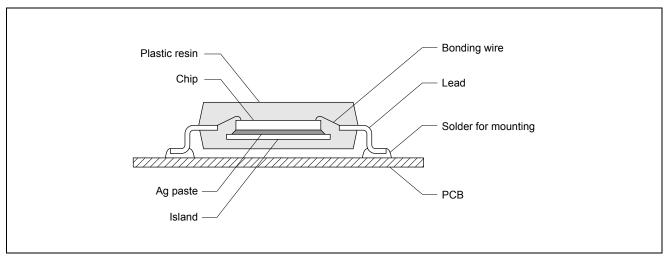

| Figure 5.6                 | Example of SMD Mounted on PCB                                                                                                     | 175 |

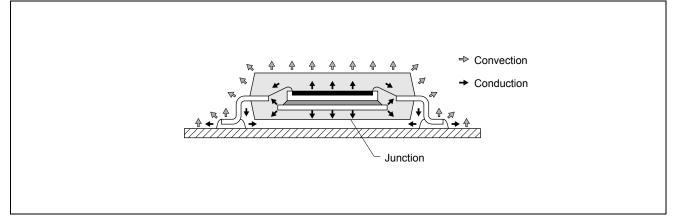

| Figure 5.7                 | Propagation of Heat in SMD                                                                                                        | 175 |

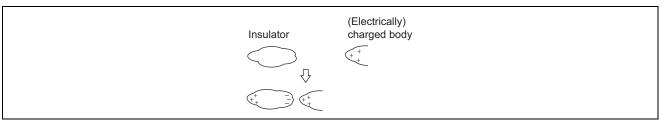

| Figure 5.8                 | Triboelectric Charging                                                                                                            |     |

| Figure 5.9                 | Electrostatic Induction                                                                                                           |     |

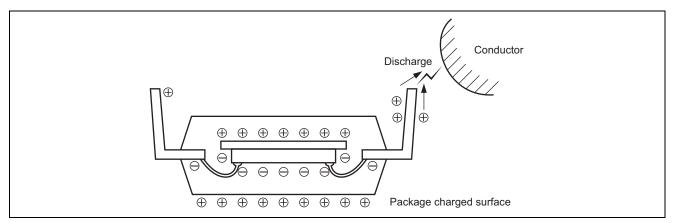

| Figure 5.10                | Internal Electrostatic Induction and Discharge when the Package Surface is Charged                                                | 181 |

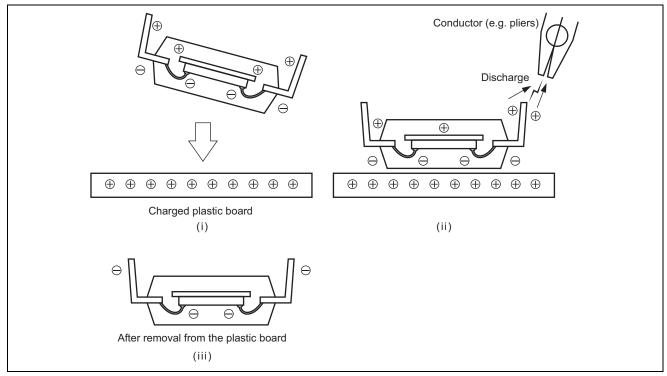

| Figure 5.11                | Process of Device Charging by Electrostatic Induction                                                                             | 181 |

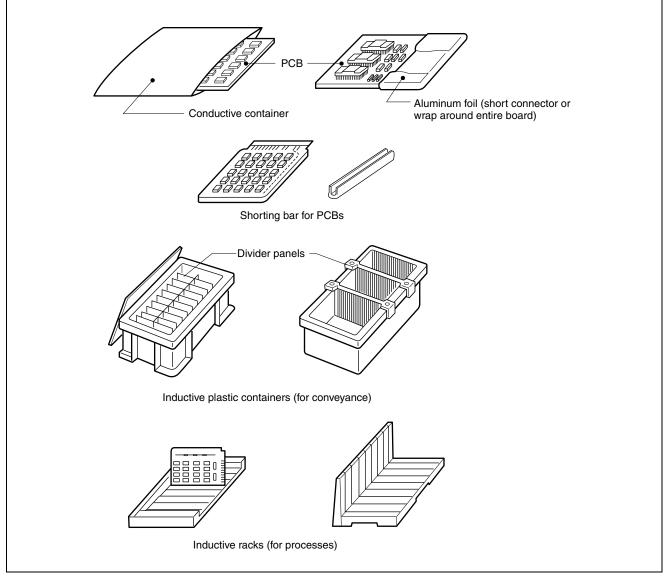

| Figure 5.12                | Example of Antistatic Protection Methods for PCBs                                                                                 |     |

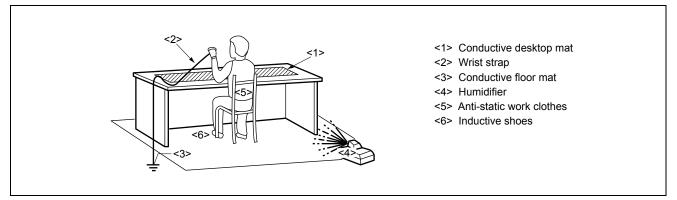

| Figure 5.13                | Anti-Static Measures for Work Area                                                                                                |     |

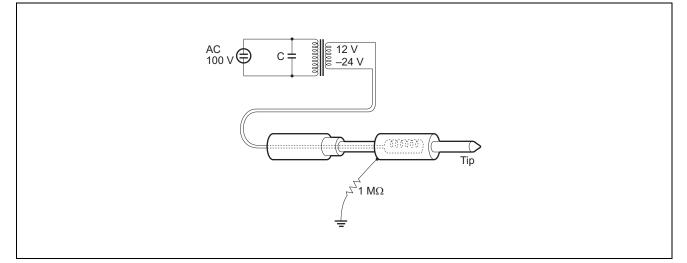

| Figure 5.14                | Grounding of Soldering Iron                                                                                                       |     |

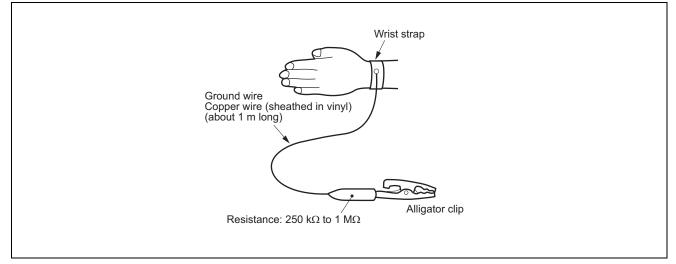

| Figure 5.15                | Body Grounding                                                                                                                    |     |

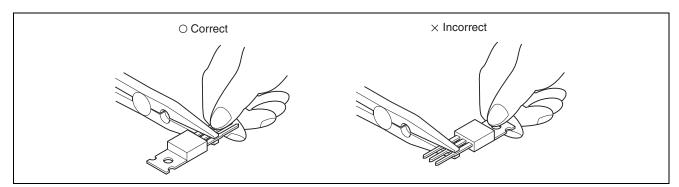

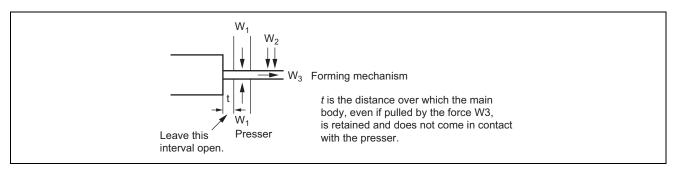

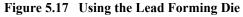

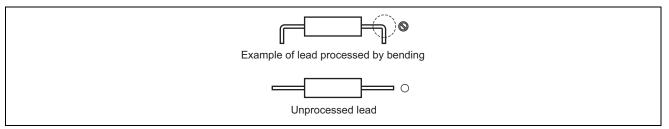

| Figure 5.16                | How to Bend Package Leads with Handling                                                                                           |     |

| Figure 5.17                | Using the Lead Forming Die                                                                                                        |     |

| Figure 5.18                | Locations and Directions for the Lead Forming of the Outer Lead                                                                   |     |

| Figure 5.19                | Methods of Mounting a Semiconductor Device on a Printed Circuit Board                                                             |     |

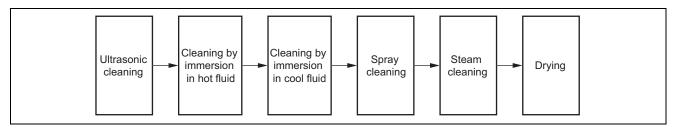

| Figure 5.20                | Normal Flow of Cleaning                                                                                                           |     |

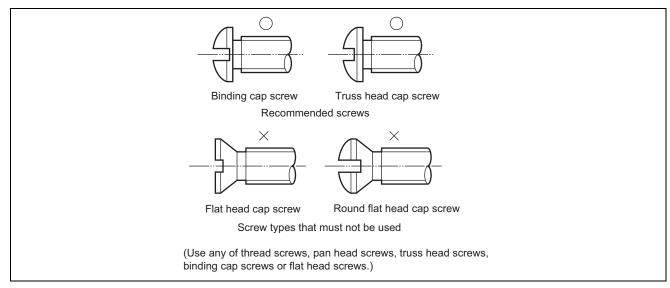

| Figure 5.21                | Types of Screws to be Recommended and not be Used                                                                                 |     |

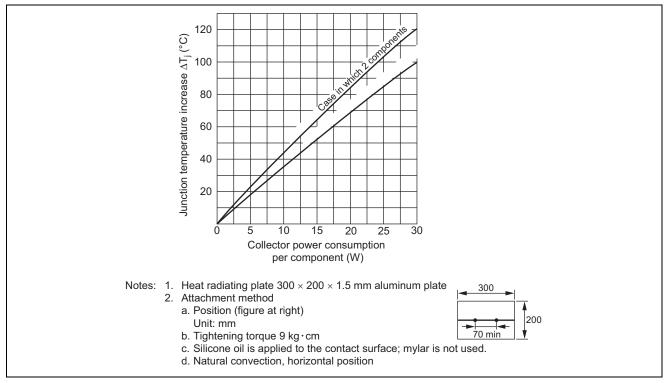

| Figure 5.22                | A Case in which Two Components are Attached to One Heat-Sink Plate                                                                |     |

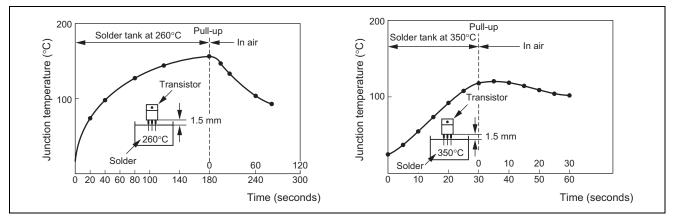

| Figure 5.23                | Junction Temperature during Soldering                                                                                             |     |

| Figure 5.24                | Grounding of the Tip of a Soldering Iron                                                                                          |     |

| Figure 5.25                | Warping of a Board in a Wave Solder Bath                                                                                          |     |

| Figure 5.26                | Example of Recommended Conditions                                                                                                 |     |

| Figure 5.27                | Structure of CMOS Input Protection Circuit                                                                                        |     |

| Figure 5.28                | I/O Switching Modes                                                                                                               |     |

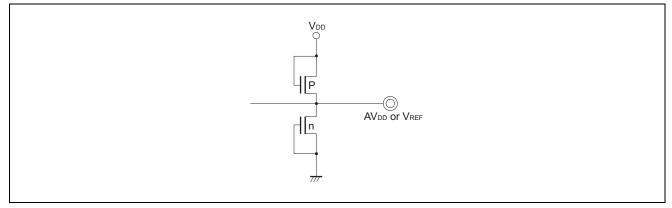

| Figure 5.29                | Example of Multiple Power Supply Sources                                                                                          |     |

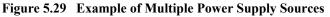

| Figure 5.30                | Example of Packaging                                                                                                              |     |

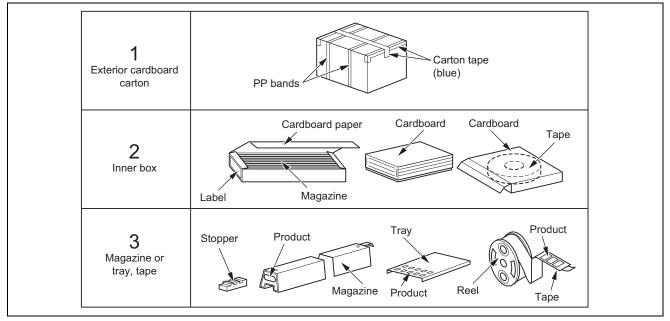

| Figure 5.31                | Example of Care Mark Labels Attached to Boxes                                                                                     |     |

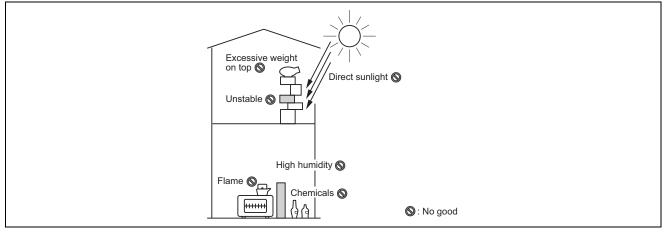

| Figure 5.32                | Examples of Poor Storage Locations and Practices                                                                                  |     |

| Figure 5.33                | Storage Condition                                                                                                                 |     |

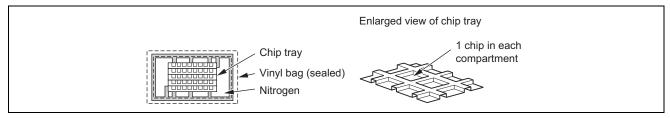

|                            | Examples of Chip Storage Containers                                                                                               |     |

| 116410 0.01                |                                                                                                                                   |     |

| A. Samplin                 | ng Inspection                                                                                                                     |     |

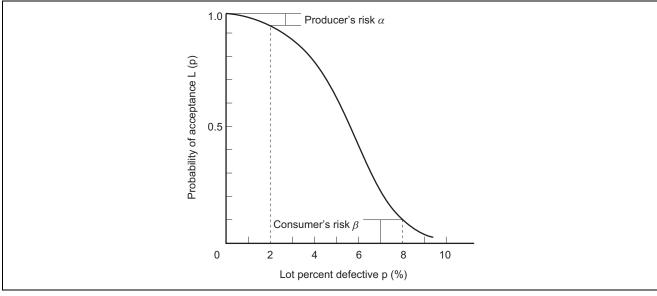

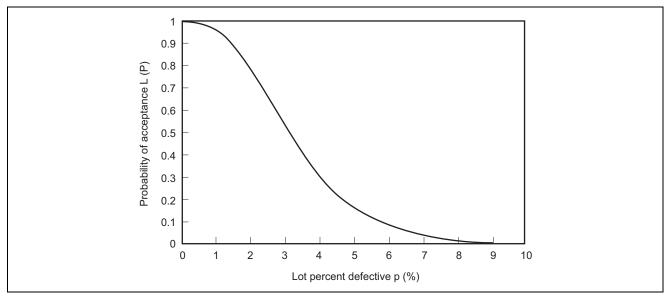

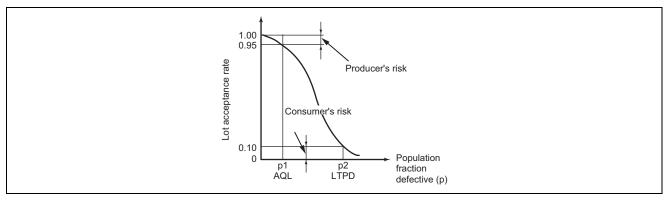

| Figure A.1                 | OC Curve                                                                                                                          | 227 |

| Figure A.2                 | OC Curve When $P0 = 1\%$ and $P1 = 5\%$                                                                                           | 228 |

|                            |                                                                                                                                   |     |

| B. Attache                 | d Tables                                                                                                                          |     |

| C Reliabil                 | ity Theory                                                                                                                        | 246 |

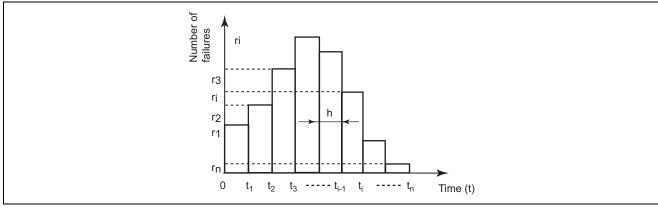

| Figure C.1                 | Discrete Failure Distribution                                                                                                     |     |

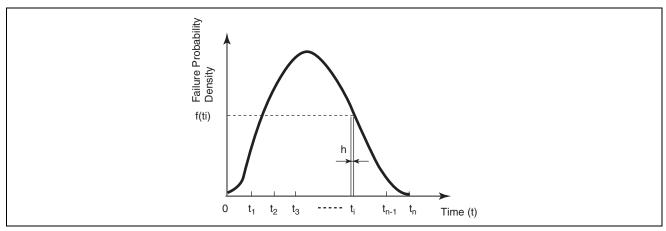

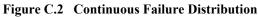

| Figure C.1<br>Figure C.2   | Continuous Failure Distribution                                                                                                   |     |

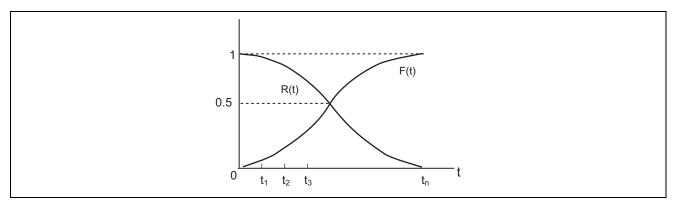

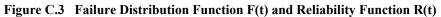

| Figure C.2<br>Figure C.3   | Failure Distribution Function F(t) and Reliability Function R(t)                                                                  |     |

| Figure C.3                 | Reliability Function for Series Model                                                                                             |     |

| -                          |                                                                                                                                   |     |

| Figure C.5                 | Reliability Function for Parallel Model                                                                                           |     |

| Figure C.6                 | Series Parallel Composite Model (2)                                                                                               |     |

| Figure C.7                 | Series-Parallel Composite Model (2)                                                                                               |     |

| Figure C.8                 | Stand-by Redundancy Model                                                                                                         |     |

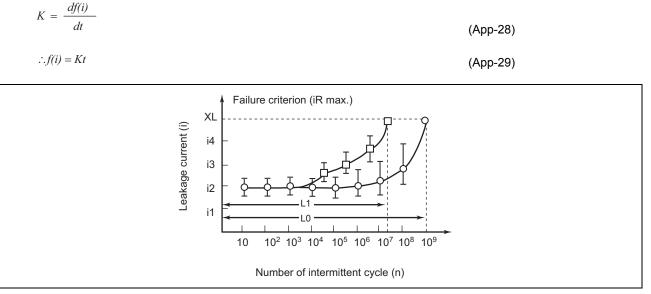

| Figure C.9                 | Data Example for Intermittent Operation Life Test                                                                                 |     |

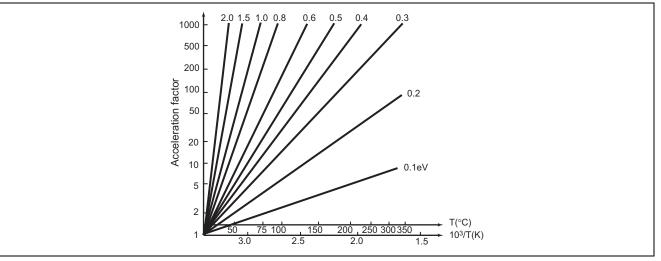

| Figure C.10                | Activation Energy Versus Acceleration Factor                                                                                      |     |

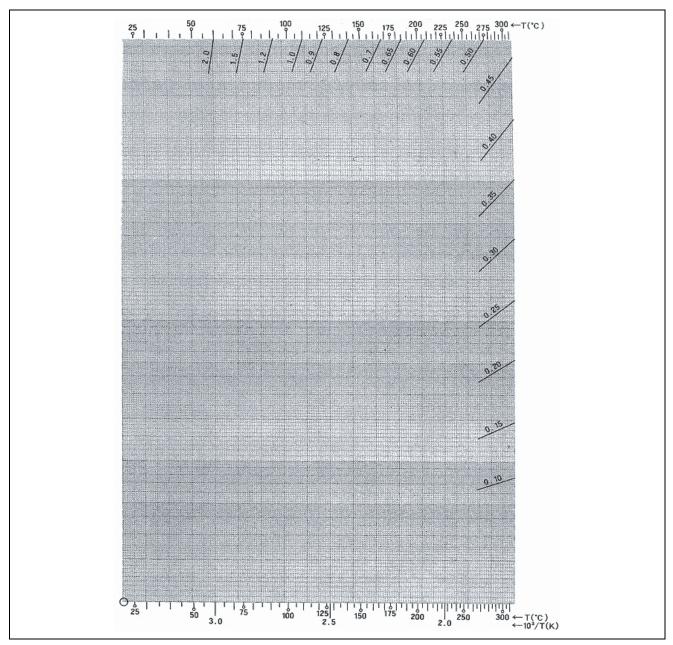

| Figure C.11<br>Figure C.12 | Basic Format of Weibull Probability Paper<br>Chart for Determining Relationship between Activation Energy and Acceleration Factor |     |

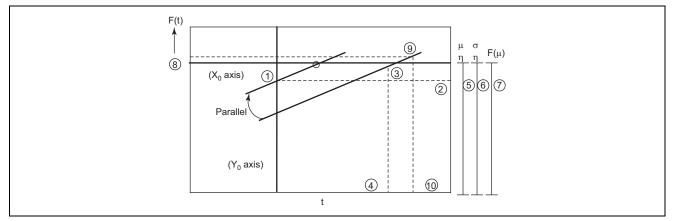

| Figure C.12<br>Figure C.13 | Example of Weibull Probability Paper                                                                                              |     |

| Figure C.13<br>Figure C.14 | Procedure for Use of Weibull Probability                                                                                          |     |

| riguit C.14                |                                                                                                                                   |     |

| Example of Weibull Probability Results                         |                                                                                                                                                                                 |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

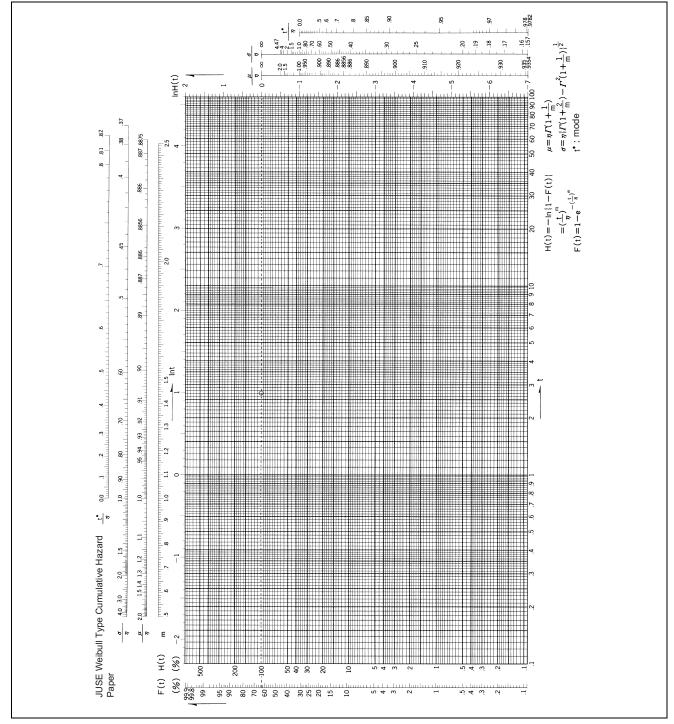

| Basic Format of Weibull Type Cumulative Hazard Paper           |                                                                                                                                                                                 |

| Example of Weibull Type Hazard Paper                           |                                                                                                                                                                                 |

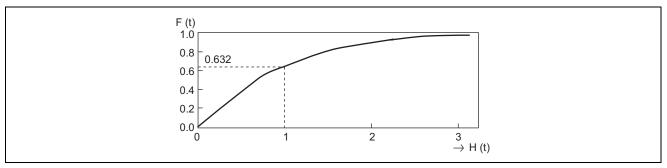

| Relationship between F(t) and H(t)                             |                                                                                                                                                                                 |

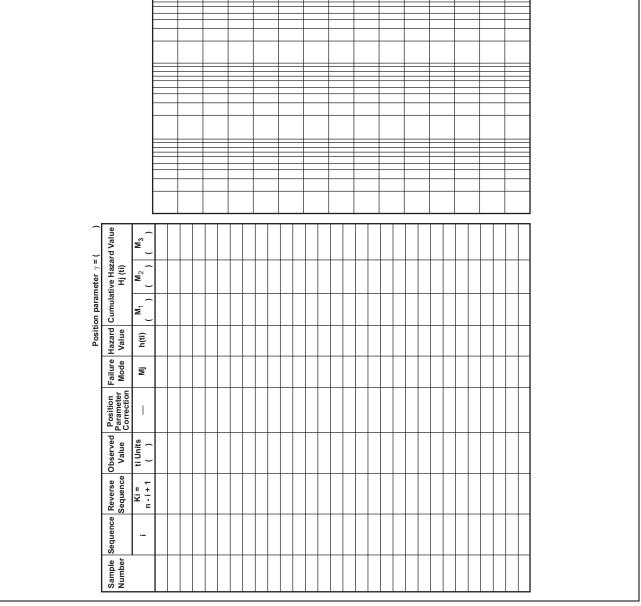

| Fill-in Example of Work Sheet                                  |                                                                                                                                                                                 |

| Example of Work Sheet Used for Data on Cumulative Hazard Paper |                                                                                                                                                                                 |

|                                                                |                                                                                                                                                                                 |

| lity Models Used in Reliability Analysis                       |                                                                                                                                                                                 |

| OC Curve                                                       |                                                                                                                                                                                 |

| Relation between Geometric and Exponential Distributions       |                                                                                                                                                                                 |

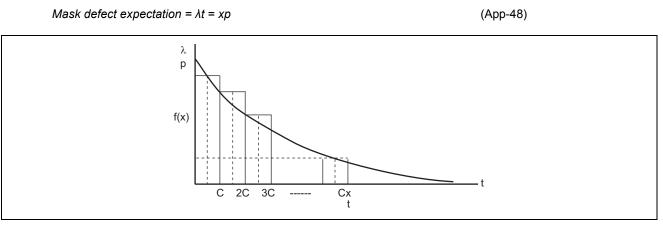

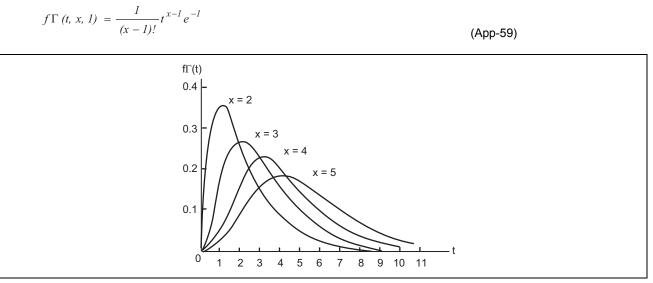

| Gamma Probability Density Functions $f\Gamma(t, x, 1)$         |                                                                                                                                                                                 |

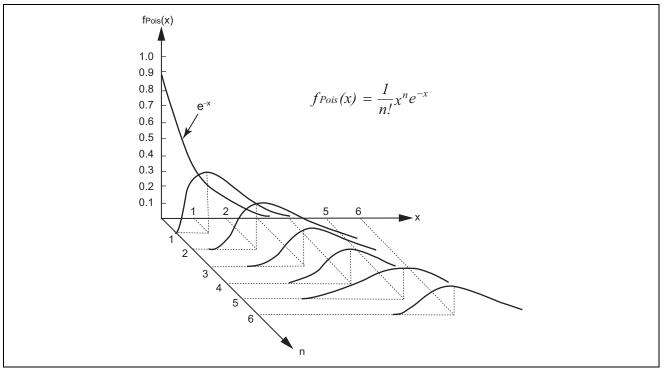

| Three-Dimensional Representation of Poisson Distributions      |                                                                                                                                                                                 |

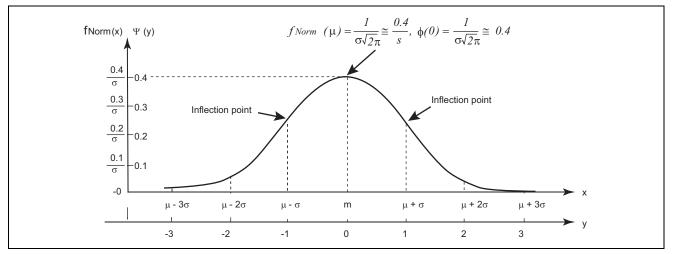

| Probability Density Function of Normal Distribution            | 276                                                                                                                                                                             |

| Trobuolity Density Tunetion of Normal Distribution             |                                                                                                                                                                                 |

|                                                                | Relation between Geometric and Exponential Distributions<br>Gamma Probability Density Functions $f\Gamma(t, x, 1)$<br>Three-Dimensional Representation of Poisson Distributions |

## Tables

| 1. Quality<br>Table 1.1 | Assurance for Semiconductor Devices<br>Quality Grades for Renesas Semiconductor Devices |     |

|-------------------------|-----------------------------------------------------------------------------------------|-----|

| 2. Reliabi              | lity                                                                                    |     |

| Table 2.1               | Typical Screening Methods                                                               |     |

| Table 2.2               | Examples of Reliability Testing Conducted When New Products are Developed               |     |

| Table 2.3               | Distribution of Representative Accelerated Lifetime Tests                               |     |

| Table 2.4               | Reliability Test Results for Microcontroller A                                          |     |

| Table 2.5               | Failure Data                                                                            |     |

| Table 2.6               | Cumulative Hazard Table                                                                 |     |

| 3. Failure              | Mechanisms                                                                              |     |

| Table 3.1               | Failure Factors, Mechanisms, and Modes                                                  |     |

| Table 3.2               | Au-Al Alloy Characteristics.                                                            |     |

| Table 3.3               | Major Methods for Evaluating the Moisture Resistance                                    |     |

| Table 3.4               | Package Cracking Types and Problems                                                     |     |

| Table 3.5               | MOS Device Failure Types from the Standpoint of Electric Stress Factors                 |     |

| 4. Failure              | Analysis                                                                                |     |

| Table 4.1               | Laser Types and Applications                                                            |     |

| 5 Basic F               | Recommendations for Handling and Using Semiconductor Devices                            | 155 |

| Table 5.1               | Principal Product Safety Measures                                                       |     |

| Table 5.2               | Documents Concerning Product Safety                                                     |     |

| Table 5.3               | Quality Grades for Renesas Semiconductor Devices                                        |     |

| Table 5.4               | Standard Examples of Derating Design                                                    |     |

| Table 5.5               | Temperature Characteristics of Derating (Example)                                       |     |

| Table 5.6               | Humidity Characteristics of Derating (Example)                                          |     |

| Table 5.7               | Power Transistor Power Cycle Characteristics of Derating (Example)                      |     |

| Table 5.8               | Examples of Typical Electrostatic Voltages (From DOD-HDBK-263)                          |     |

| Table 5.9               | Cleanliness Standards of a Printed Circuit Board                                        |     |

| Table 5.10              | Optimum Tightening Torque for Representative Packages                                   |     |

| A. Sampl                | ing Inspection                                                                          |     |

| Table A.1               | Sample Size Code Letters                                                                |     |

| Table A.2               | Single Sampling Plan for Normal Inspection (Master Table)                               |     |

| Table A.3               | Single Sampling Plan for Tightened Inspection (Master Table)                            |     |

| Table A.4               |                                                                                         |     |

|                         | Single Sampling Plan for Reduced Inspection (Master Table)                              |     |

| Table A.5               | Single Sampling Plan for Reduced Inspection (Master Table)<br>LTPD Sampling Table (1/2) |     |

## RENESAS

### Using this Semiconductor Reliability Handbook

- This document shows mainly three topics. Firstly, in Section 1, it shows Renesas' efforts at achieving reliability in its semiconductor products. Secondly, in Sections 2, 3, and 4, it shows fundamental information relating to reliability that supplements the reliability documentation Renesas provides for its semiconductor products. Finally, in Section 5, it presents some common precaution or instruction for using semiconductor products that our customers should understand and follow.

- The terms and conditions to be applied to individual sales of Renesas' semiconductor product, including without limitation, the various quality assurance liability and defect liability shall be specified in the sales contract and other related contracts concluded between the customer and either Renesas, its subsidiary or their distributor. In particular, this document neither adds to nor modifies those contracts. Furthermore, this document in no way constitute or is deemed to constitute any legal responsibilities of Renesas or its subsidiaries concerning Renesas semiconductor products.

- The content of this document is subject to change without notice. Therefore, when using this document, please check the Renesas web site for the latest information, or request the latest information from either Renesas sales window or distributors.

## RENESAS

## 1. Quality Assurance for Semiconductor Devices

#### 1.1 Basic Policy for Quality

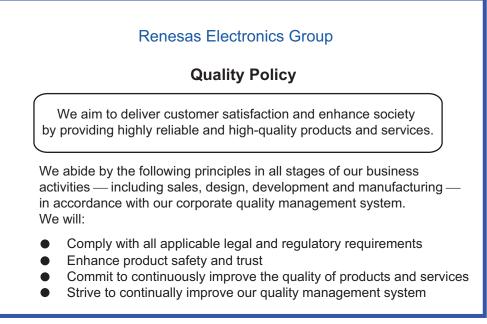

In accordance with the quality policy stated in Figure 1.1, Renesas Electronics has established a quality assurance system based on the ISO 9001 and ISO/TS 16949 standards. Renesas is developing consistent quality assurance and quality control across all stages from product planning to after-sales services, based on "built-in quality" that is backed up with reliability technologies.

Renesas has always placed great emphasis on maintaining and improving levels of quality and reliability. From the development to the delivery of a products, Renesas implements quality control and reliability verification from the three standpoints of "quality control and reliability verification in design", "quality control in production", and "quality assurance of product". All Renesas parties uphold the basic principle that quality comes first. To this end, they are concerned the achievement of quality levels that satisfy customer expectations.

Figure 1.1 Renesas Electronics Quality Policy

#### 1.2 Quality Assurance System for Semiconductor Devices

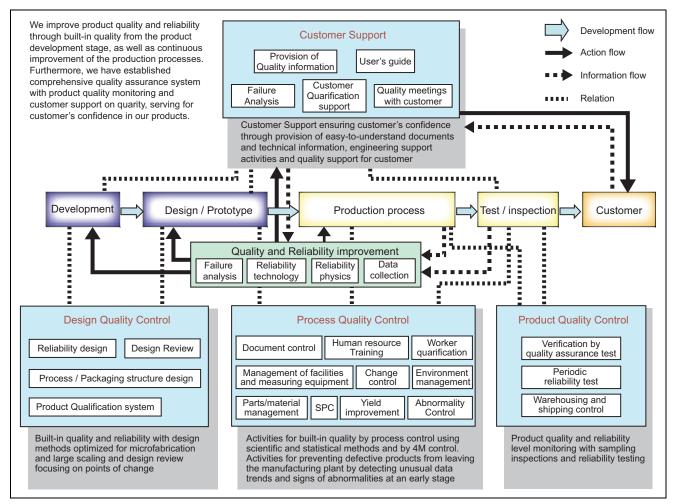

Figure 1.2 outlines our quality assurance system which covers all stages from product development to field use.

Figure 1.2 Renesas Quality Assurance System for Semiconductor Devices

Quality control in the design stage is the activity of built-in quality and reliability during design, and it concentrates on design review and the optimization of device structure, applicable materials, circuit design, packages, production process and so on. After verifying the electrical characteristics and reliability of prototypes for each product type, it moves to mass-production stage.

Quality control in mass-production stage is the activity of built-in quality during production process. This quality control is for equipment, tools, D.I. water, gasses and production conditions, and quality control of product performance. Using the EDP (Electronic Data Processing) system to control these quality control information, it is established the total quality control system.

Quality control in the finished product stage has two activities. The first activity is to check the completed products meet prescribed functionality and reliability target. These checks include the inspection of each device lot, or periodic in-house inspections and examinations. The second activity is to involve the customer support such as quality information service.

In this way, the quality information is fed backwards and forwards between all stages from the development and design to mass-production, shipping, and actual product operation. This system enable the implementation of more efficient product quality.

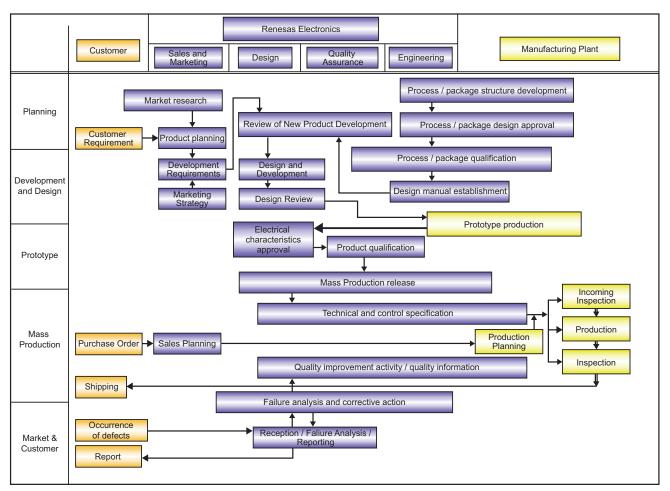

Figure 1.3 shows a flowchart of the quality assurance program.

Our quality control system has been built based on the ISO 9001 and ISO/TS 16949 standards.

#### Semiconductor Reliability Handbook

#### 1. Quality Assurance for Semiconductor Devices

Figure 1.3 Quality Assurance Program Flowchart

Not only have Renesas products been manufactured with high reliability and then improved for higher reliability by the quality assurance system illustrated in Figure 1.3, but they also have been specified from the product development stage for an appropriate degree of reliability based on the classification in Table 1.1.

| Table 1.1 | Quality Grades for Renesas Semiconductor Devices |

|-----------|--------------------------------------------------|

|-----------|--------------------------------------------------|

| Quality Grades | Representative Examples of Use Application                                                                                                                                                                           |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Quality   | Transportation equipment (automobiles, trains, ships, etc.), traffic control (signals), large-scale communication equipment, key financial terminal systems, safety control equipment, etc.                          |

| Standard       | Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment, industrial robots, etc. |

#### 1.3 Quality Assurance at Development Stage

The following procedure is used in product development to ensure the target quality and reliability. Using demand estimates for new products based on market research, we study to plan product development by investigating, at the product planning stage, first the required quality grade, functionality, and reliability of the new product, then issues related to product manufacture, and then issues related to cost. Based on the development plan, new theories, technologies, and concepts are actively adopted for design and technology development during the development of the new product.

The design is reviewed and then prototype is fabricated. Then the prototype undergoes a qualification test that checks whether their electrical characteristics, maximum ratings, and reliability meet the quality target.

Also at this stage, we provide the drawings and specifications required for mass production and at the same time as implementing education and training for the workers, we create a system for procuring the required materials and parts and provide the equipment and jigs required for manufacturing.

When the prototype has passed characteristics evaluation and reliability testing, we study issues related to design, manufacture, and quality, and once we have verified that there are no problems, we move on to the next step, the mass production stage.

These processes are set up for the various development levels and, to assure the desired quality and reliability, we implement quality approval at the device prototype period based on reliability design.

Product Quality Certification at Renesas is based on the following approach.

- 1. Use an objective viewpoint of the customers' stand point.

- 2. Incorporate examples of past failures and field use information.

- 3. Certify design modifications and operation alterations.

- 4. Certify parts, materials, and processes using stringent criteria.

- 5. Investigate the process capability and causes of deviation and verify the control items and points during massproduction.

The process of certification is divided into three steps:

- a. Certification of Parts and Materials

- b. Electrical Characteristics Approval

- c. Product Quality Certification

Design verification for parts and materials is performed during the Certification of Parts and Materials. Product design verification is covered in Electrical Characteristics Approval. Design validation is checked through the Product Quality Certification.

Renesas implements early warning system to verify the quality of the product at the initial stages of mass production. In early warning system, we set up a special management system for a fixed period after mass production starts, and under that system, we collect increased amounts of quality control information, quickly implement corrective measures for any problems found, and verify the results.

#### 1.4 Quality Assurance at Mass Production Stage

At the mass production stage, the device is put into production based on the production plan. The materials, parts, production processes, environments and equipment conditions, and products in plant are carefully controlled. In addition, in-process inspections and final inspection are carried out on both semi-manufactured and manufactured products to check quality levels.

Built-in-quality at this stage is very important for manufacturing to keep high quality and reliable products. To do this, the Manufacturing Department establishes production specifications and determines the items to be controlled for the main manufacturing conditions. Production is performed based on these production specifications, and, for manufacturing conditions that have a large effect on quality, quality is maintained and improved by implementing checklist based inspections and characteristics management.

Periodical maintenance and accuracy adjustments are regularly performed for early detection of abnormalities and for establishing/monitoring preventive maintenance schedules.

In the production process, Statistical Process Control, SPC, with continuous data and workmanship control are performed as in-process control.

To build in quality, SPC techniques are used at each stage. In particular, in the mass production stage, control chart is applied to critical work steps to monitor whether process variations are within acceptable ranges. Here, we have everyone involved with the manufacturing itself strive to minimize these process variations as much as possible by monitoring and managing various process parameters, such as the process capability index, Cp and Cpk, and the process performance index, Pp and Ppk.

The process capability index is used to obtain stability with respect to the process specifications from process data acquired over a fixed period and the values in the process control specification and are defined by the formulas shown below. We determine these process capability index and the process performance index periodically and use them to improve any dispersion in the process.

$$Cp = \frac{(Upper specification limit - Lower specification limit)}{6 \sigma}$$

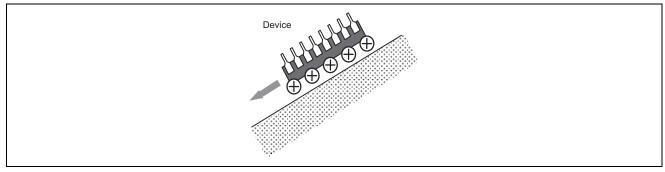

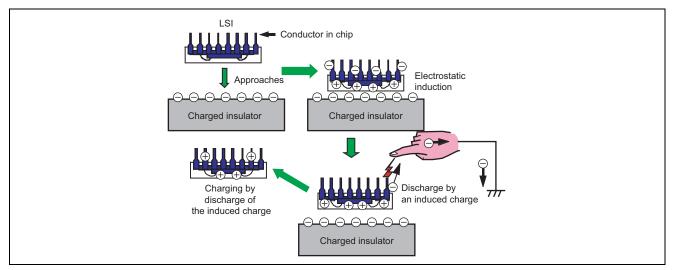

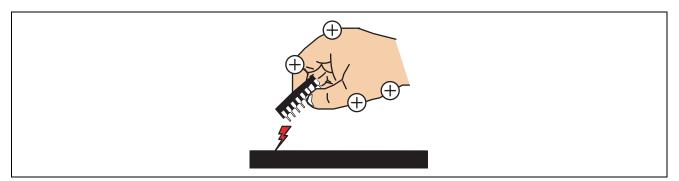

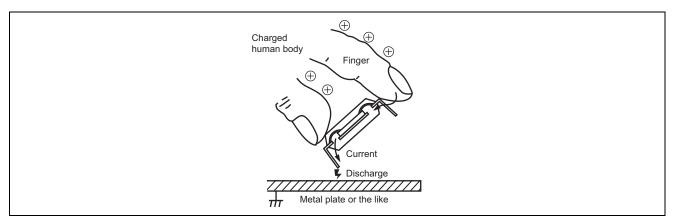

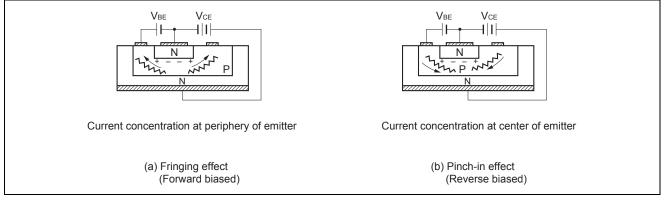

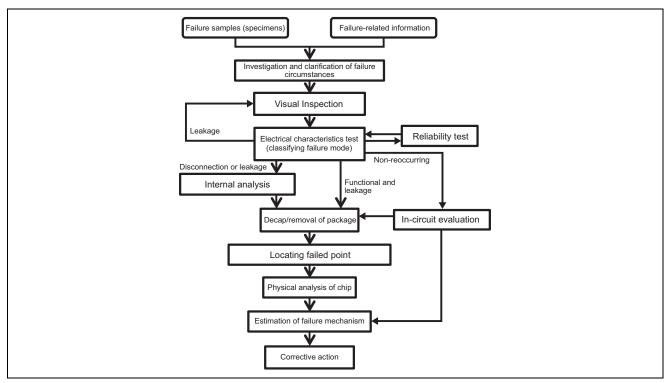

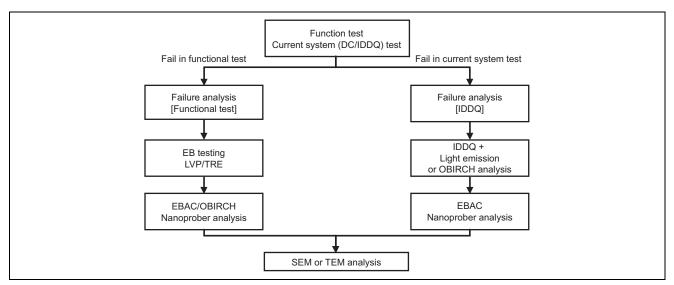

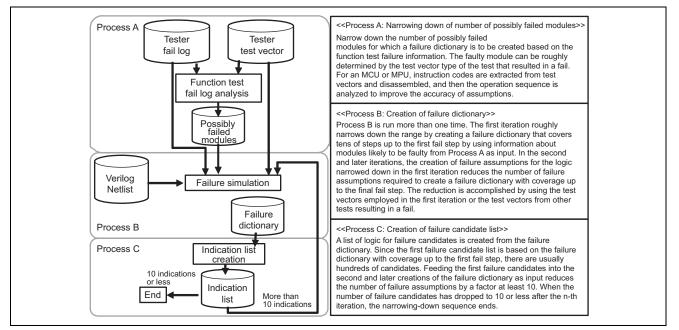

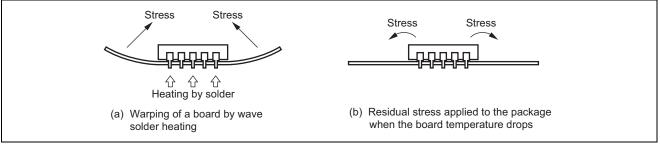

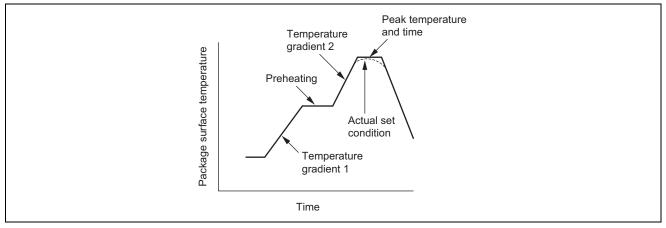

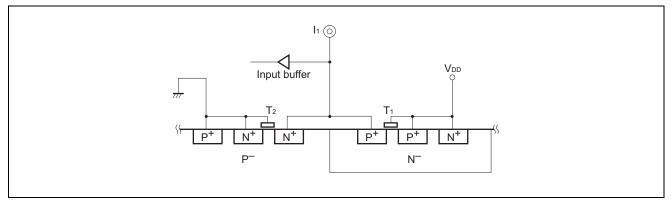

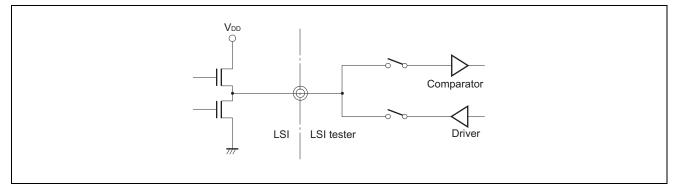

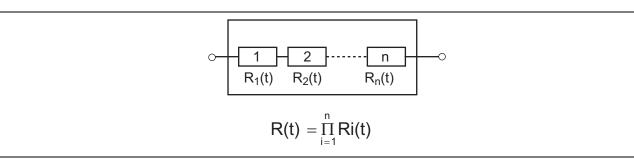

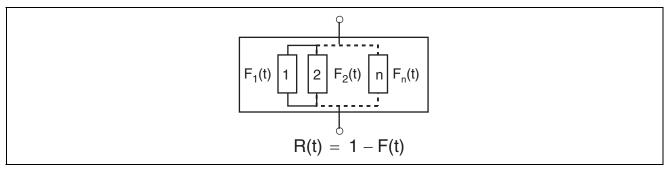

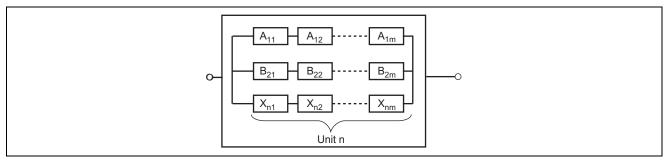

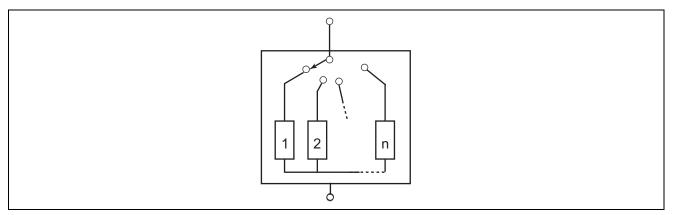

$$Cpk = \frac{|Specification limit close to the average|}{3 \sigma}$$