## M27256

## 256K (32K x 8) UV Erasable PROM

The Intel M27256 is a 5V only, 262, 144-bit ultraviolet Erasable and Electrically Programmable Read Only Memory (EPROM). Organized as 32K words by 8 bits, individual bytes are accessed in 200 ns. This is compatible with high performance microprocessors, such as the Intel 8 MHz M80186, allowing full speed operation without the addition of performance-degrading WAIT states. The M27256 is also directly compatible with Intel's M8051 family of microcontrollers.

The M27256 enables implementation of new, advanced systems with firmware intensive architectures. The combination of the M27256's high density, cost effective EPROM storage, and new advanced microprocessors having megabit addressing capability provides designers with opportunities to engineer user-friendly, high reliability, high-performance systems.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## M27256 256K (32K x 8) UV ERASABLE PROM

Military

- Military Temperature Range: -55°C to + 125°C (Tc)

- **Software Carrier Capability**

- 200, 250, 350 ns Access Times

- **Two-Line Control**

- inteligent Identifier™ Mode

- Automated Programming Operations

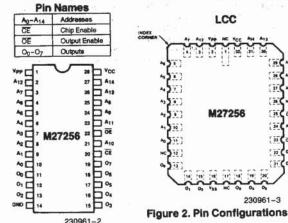

- Industry Standard Pinout . . . JEDEC Approved

- Low Power

- 125 mA max. Active

- 50 mA max. Standby

- inteligent Programming™ Algorithm - Fastest EPROM Programming

The Intel M27256 is a 5V only, 262, 144-bit ultraviolet Erasable and Electrically Programmable Read Only Memory (EPROM). Organized as 32K words by 8 bits, individual bytes are accessed in 200 ns. This is compatible with high performance microprocessors, such as the Intel 8 MHz M80186, allowing full speed operation without the addition of performance-degrading WAIT states. The M27256 is also directly compatible with Intel's M8051 family of microcontrollers.

The M27256 enables implementation of new, advanced systems with firmware intensive architectures. The combination of the M27256's high density, cost effective EPROM storage, and new advanced microprocessors having megabit addressing capability provides designers with opportunities to engineer user-friendly, high reliability, high-performance systems.

The M27256's large storage capability of 32K bytes enables it to function as a high density software carrier. Entire operating systems, diagnostics, high-level language programs and specialized application software can reside in a M27256 EPROM directly on a system's memory bus. This would permit immediate microprocessor access and execution of software and eliminate the need for time consuming disk accesses and downloads.

Several advanced features have been designed into the M27256 that allow for fast and reliable programming - the inteligent identifier™ mode and the inteligent Programming™ Algorithm. Programming equipment that takes advantage of these innovations will electronically identify the M27256 and then rapidly program it using an efficient programming method.

Two-line control and JEDEC-approved, 28-pin packaging are standard features of all Intel high-density EPROMS. This assures easy microprocessor interfacing and minimum design efforts when upgrading, adding, or choosing between nonvolatile memory alternatives.

The M27256 is manufactured using Intel's advanced HMOS\* II-E technology.

\*HMOS is a patented process of Intel Corporation.

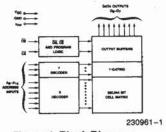

Figure 1. Block Diagram

230961-3

LCC

M27258

## intel

#### **ABSOLUTE MAXIMUM RATINGS\***

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### **Operating Conditions**

| Symbol         | Description                   | Min  | Max   | Units |

|----------------|-------------------------------|------|-------|-------|

| T <sub>C</sub> | Case Temperature (Instant On) | -55  | + 125 | °C    |

| Vcc            | Digital Supply Voltage        | 4.50 | 5.50  | ٧     |

#### **READ OPERATION**

#### D.C. CHARACTERISTICS (Over Specified Operating Conditions)

| Symbol                        | * B                                  |      | Limits   |                     | Units | 1.4.20.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0. |

|-------------------------------|--------------------------------------|------|----------|---------------------|-------|-------------------------------------------|

|                               | Parameter                            | Min  | Typ(3)   | Max                 |       | Comments                                  |

| lu                            | Input Load Current                   |      |          | 10                  | μΑ    | V <sub>IN</sub> = 5.5V                    |

| ILO                           | Output Leakage Current               |      |          | 10                  | μΑ    | V <sub>OUT</sub> = 5.5V                   |

| I <sub>PP1</sub> <sup>2</sup> | V <sub>PP</sub> Current Read/Standby |      | N. Carlo | 5                   | mA    | $V_{PP} = 5.5V$                           |

| l <sub>CC1</sub> <sup>2</sup> | V <sub>CC</sub> Current Standby      |      | 20       | 50                  | mA    | CE = VIH                                  |

| loc2 <sup>2</sup>             | V <sub>CC</sub> Current Active       |      | 45       | 125                 | mA    | $\overline{CE} = \overline{OE} = V_{IL}$  |

| V <sub>IL</sub> 5             | Input Low Voltage                    | -0.1 |          | +0.8                | V     |                                           |

| V <sub>IH</sub> 5             | Input High Voltage                   | 2.0  |          | V <sub>CC</sub> + 1 | ٧     |                                           |

| VOL                           | Output Low Voltage                   |      |          | 0.45                | V     | I <sub>OL</sub> = 2.1 mA                  |

| V <sub>OH</sub>               | Output High Voltage                  | 2.4  |          |                     | ٧     | I <sub>OH</sub> = -400 μA                 |

See notes on next page.

## intel

#### A.C. CHARACTERISTICS (Over Specified Operating Conditions)

| Symbol              | Parameter                                                           | M27256-20 |     | M27256-25 |     | M27256-35 |     | Units  | Comments      |  |

|---------------------|---------------------------------------------------------------------|-----------|-----|-----------|-----|-----------|-----|--------|---------------|--|

|                     |                                                                     | Min       | Max | Min       | Max | Min       | Max | Office | Comments      |  |

| tacc                | Address to Output Delay                                             |           | 200 |           | 250 |           | 350 | ns     | CE = OE = VIL |  |

| t <sub>CE</sub>     | CE to Output Delay                                                  |           | 200 |           | 250 | Speries   | 350 | ns     | OE = VIL      |  |

| t <sub>OE</sub>     | OE to Output Delay                                                  | 0         | 75  |           | 100 |           | 130 | ns     | CE = VIL      |  |

| t <sub>DF</sub> (4) | OE High to Output Float                                             | 0         | 55  | 0         | 60  | 0         | 110 | ns     | CE = VIL      |  |

| t <sub>OH</sub> (4) | Output Hold from<br>Addresses, CE or OE<br>Whichever Occurred First | 0         |     | 0         |     | 0         |     | ns     | CE = OE = VIL |  |

## NOTES:

- V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

V<sub>PP</sub> may be connected directly to V<sub>CC</sub> except during programming. The supply current would then be the sum of I<sub>CC</sub> and 1 pp1.

3. Typical values are for T<sub>C</sub> = +25°C and nominal supply voltages.

4. Output Float is defined as the point where data is no longer driven.

5. These values apply to D.C. test conditions only. The A.C. values are V<sub>IL</sub> = 0.45V max, V<sub>IH</sub> = 2.4V min.

#### CAPACITANCE T<sub>C</sub> = +25°C, f = 1 MHz

| Symbol | Parameter          | Typ(1) | Max | Units | Conditions            |

|--------|--------------------|--------|-----|-------|-----------------------|

| CIN    | Input Capacitance  | 4      | 6   | pF    | $V_{IN} = 0V$         |

| COUT   | Output Capacitance | 8      | 12  | pF    | V <sub>OUT</sub> = 0V |

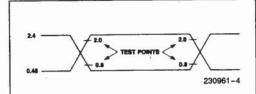

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. Testing: Inputs are Driven at 2.4V for a Logic "1" and 0.45V for a Logic "0". Timing Measurements are made at 2.0V for a Logic "1" and 0.8V for a Logic "0".

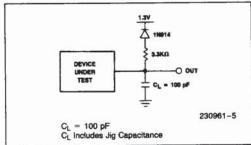

#### A.C. TESTING LOAD CIRCUIT

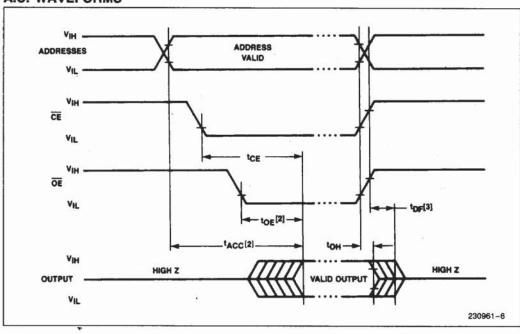

## A.C. WAVEFORMS

1. Typical values are for T<sub>C</sub> = 25°C and nominal supply voltages.

2. OE may be delayed up to t<sub>ACC</sub>-t<sub>OE</sub> after the falling edge of CE without impact on t<sub>ACC</sub>.

3. Output float is defined as the point where data is no longer driven.

## **DEVICE OPERATION**

The eight modes of operation of the M27256 are listed in Table 1. A single 5V power supply is required in the read mode. All inputs are TTL levels except for  $V_{PP}$  and 12V on A9 for int<sub>e</sub>ligent identifier mode.

**Table 1. Operating Modes**

| Table 1. Operating modes |            |            |                     |                     |                      |                           |  |  |

|--------------------------|------------|------------|---------------------|---------------------|----------------------|---------------------------|--|--|

| Pins<br>Mode             | CE<br>(20) | ŌĒ<br>(22) | A <sub>9</sub> (24) | V <sub>PP</sub> (1) | V <sub>CC</sub> (28) | Outputs<br>(11-13, 15-19) |  |  |

| Read                     | VIL        | VIL        | х                   | Vcc                 | Vcc                  | D <sub>OUT</sub>          |  |  |

| Output Disable           | VIL        | VIH        | Х                   | Vcc                 | Vcc                  | High Z                    |  |  |

| Standby                  | VIH        | Х          | Х                   | Vcc                 | Vcc                  | High Z                    |  |  |

| inteligent Programming   | VIL        | VIH        | Х                   | Vpp                 | Vcc                  | D <sub>IN</sub>           |  |  |

| Verify                   | VIH        | VIL        | Х                   | V <sub>PP</sub>     | Vcc                  | D <sub>OUT</sub>          |  |  |

| Optional Verify          | VIL        | VIL        | Х                   | Vpp                 | Vcc                  | D <sub>OUT</sub>          |  |  |

| Program Inhibit          | VIH        | VIH        | х                   | V <sub>PP</sub>     | Vcc                  | High Z                    |  |  |

| inteligent Identifier    | VIL        | VIL        | VH                  | Vcc                 | Vcc                  | Code                      |  |  |

#### NOTES:

1. X can be  $V_{IH}$  or  $V_{IL}$ 2.  $V_{H} = 12.0V \pm 0.5V$

#### **Read Mode**

The M27256 has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{\text{OE}}$ ) is the output control and should be used to gate data from the output pins, independent of device selection. Assuming that addresses are stable, the address access time ( $t_{ACC}$ ) is equal to the delay from  $\overline{\text{CE}}$  to output ( $t_{CE}$ ). Data is available at the outputs after a delay of  $t_{OE}$  from the falling edge of  $\overline{\text{OE}}$ , assuming that  $\overline{\text{CE}}$  has been low and addresses have been stable for at least  $t_{ACC}$ – $t_{OE}$ .

#### Standby Mode

The M27256 has a standby mode which reduces the maximum active current from 125 mA to 50. The M27256 is placed in the standby mode by applying a TTL-high signal to the  $\overline{\text{CE}}$  input. When in standby mode, the outputs are in a high impedance state, independent of the  $\overline{\text{OE}}$  input.

#### **Output OR-Tieing**

Because EPROMs are usually used in larger memory arrays, Intel has provided 2 control lines which accommodate this multiple memory connection. The two control lines allow for:

- a) the lowest possible memory power dissipation,

- b) complete assurance that output bus contention will not occur.

To use these two control lines most efficiently,  $\overline{\text{CE}}$  (pin 20) should be decoded and used as the primary device selecting function, while  $\overline{\text{OE}}$  (pin 22) should be made a common connection to all devices in the array connected to the  $\overline{\text{READ}}$  line from the system control bus. This assures that all deselected memory devices are in their low power standby mode and that the output pins are active only when data is desired from a particular memory device.

#### **System Considerations**

The power switching characteristics of HMOS\* II-E EPROMs require careful decoupling of the devices. The supply current, I<sub>CC</sub>, has three segments that are of interest to the system designer—the standby current level, the active current level, and the transient current peaks that are produced by the falling and rising edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitive and inductive loading of the de-

vice. The associated transient voltage peaks can be suppressed by complying with Intel's Two-Line Control and by properly selected decoupling capacitors. It is recommended that a 0.1  $\mu F$  ceramic capacitor be used on every device between  $V_{CC}$  and GND. This should be a high frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a 4.7  $\mu F$  bulk electrolytic capacitor should be used between  $V_{CC}$  and GND for every eight devices. The bulk capacitor should be located near where the power supply is connected to the array. The purpose of the bulk capacitor is to overcome the voltage droop caused by the inductive effects of PC board traces.

#### **Programming**

Caution: Exceeding 13.0V on pin 1 (Vpp) will permanently damage the M27256.

Initially, and after each erasure, all bits of the M27256 are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be present in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

The M27256 is in the programming mode when the V<sub>PP</sub> input is at 12.5V and ČE is at TTL-low. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.

## inteligent Programming™ Algorithm

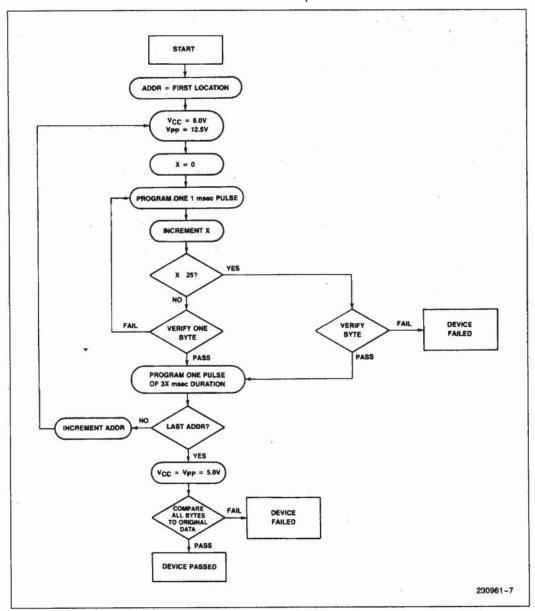

The M72756 inteligent Programming Algorithm rapidly programs Intel M27256 EPROMs using an efficient and reliable method particularly suited to the production programming environment. Typical programming times for individual devices are on the order of five minutes. Programming reliability is also ensured as the incremental program margin of each byte is continually monitored to determine when it has been successfully programmed. A flowchart of the M27256 inteligent Programming Algorithm is shown in Figure 3.

The inteligent Programming Algorithm utilizes two different pulse types: initial and overprogram. The duration of the initial  $\overline{\text{CE}}$  pulse(s) is one millisecond, which will then be followed by a longer overprogram pulse of length 3X msec. X is an iteration counter and is equal to the number of the initial one-millisecond pulses applied to a particular M27256 location, before a correct verify occurs. Up to 25 one-millisecond pulses per byte are provided for before the overprogram pulse is applied.

The entire sequence of program pulses and byte verifications is performed at  $V_{CC}=6.0V$  and  $V_{PP}=12.5V$ . When the intelligent Programming cycle has been completed, all bytes should be compared to the original data with  $V_{CC} = V_{PP} = 5.0V$ .

#### **Program Inhibit**

Programming of multiple M27256s in parallel with different data is easily accomplished by using the Program Inhibit mode. A high-level CE input inhibits the other M27256s from being programmed. Except for CE and OE, all like inputs of the parallel M27256s may be common. A TTL low-level pulse applied to the CE input with Vpp at 12.5V will program the selected M27256.

#### Verify

A verify should be performed on the programmed bits to determine that they have been correctly programmed. The verify is performed with OE at VIL, CE at VIH and Vpp at 12.5V.

## inteligent Identifier™ Mode

The inteligent Identifier Mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the 25°C ±5°C ambient temperature range that is required when programming the M27256.

To activate this mode, the programming equipment must force 11.5V to 12.5V on address line A9 (pin 24) of the M27256. Two identifier bytes may then be

sequenced from the device outputs by toggling address line A0 (pin 10) from VIL to VIH. All other address lines must be held at VIL during inteligent Identifier Mode.

Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code and byte 1 (A0 =  $V_{IH}$ ) the device identifier code. For the Intel M27256, these two identifier bytes are given in Table 2. All identifiers for manufacturer and device codes will possess odd parity, with the MSB (07) defined as the parity bit.

#### **ERASURE CHARACTERISTICS**

The erasure characteristics of the M27256 are such that erasure begins to occur upon exposure to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000 Å range. Data show that constant exposure to room level fluorescent lighting could erase the typical M27256 in approximately 3 years, while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the M27256 is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the M27256 window to prevent unintentional erasure.

The recommended erasure procedure for the M27256 is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity x exposure time) for erasure should be a minimum of 15 Wsec/cm2. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12000 µW/cm<sup>2</sup> power rating. The M27256 should be placed within 1 inch of the lamp tubes during erasure. The maximum integrated dose an M27256 can be exposed to without damage is 7258 Wsec/cm<sup>2</sup> (1 week @ 12000 μW/cm<sup>2</sup>). Exposure of the M27256 to high intensity UV light for long periods may cause permanent damage.

Table 2. M27256 Inteligent Identifier™ Bytes

| Pins<br>Identifier | A <sub>0</sub> (10) | O <sub>7</sub> (19) | O <sub>6</sub> (18) | O <sub>5</sub> (17) | O <sub>4</sub> (16) | O <sub>3</sub> (15) | O <sub>2</sub> (13) | O <sub>1</sub> (12) | O <sub>0</sub> (11) | Hex<br>Data |

|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------|

| Manufacturer Code  | V <sub>IL</sub>     | 1                   | 0                   | 0                   | 0                   | 1                   | 0                   | 0                   | 1                   | 89          |

| Device Code        | VIH                 | 0                   | 0                   | 0                   | 0                   | 0                   | 1                   | 0                   | 0                   | 04          |

#### NOTES:

1.  $A_9 = 12.0V \pm 0.5V$ 2.  $A_1 - A_8$ ,  $A_{10} - A_{13}$ ,  $\overline{CE}$ ,  $\overline{OE} = V_{|L}$ 3.  $A_{14} = V_{|H}$  or  $V_{|L}$

Figure 3. M27256 inteligent Programming™ Flowchart

## int<sub>e</sub>ligent Programming™ Algorithm

## D.C. PROGRAMMING CHARACTERISTICS

$T_C = 25 \pm 5$ °C,  $V_{CC} = 6.0 V \pm 0.25 V$ ,  $V_{PP} = 12.5 V \pm 0.3 V$

| Combal           | Parameter                                         |      | Limits              | Comments |                                      |

|------------------|---------------------------------------------------|------|---------------------|----------|--------------------------------------|

| Symbol           | Parameter                                         | Min  | Max                 | Unit     | (Note 1)                             |

| l <sub>IL</sub>  | Input Current (All Inputs)                        |      | 10                  | μΑ       | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |

| VIL              | Input Low Level (All Inputs)                      | -0.1 | 0.8                 | V        |                                      |

| VIH              | Input High Level                                  | 2.0  | V <sub>CC</sub> - 1 | ٧        |                                      |

| V <sub>OL</sub>  | Output Low Voltage During Verify                  |      | 0.45                | ٧        | I <sub>OL</sub> = 2.1 mA             |

| V <sub>OH</sub>  | Output High Voltage During Verify                 | 2.4  |                     | ٧        | $I_{OH} = -400 \mu$ A                |

| I <sub>CC2</sub> | V <sub>CC</sub> Supply Current (Program & Verify) |      | 100                 | mA       |                                      |

| I <sub>PP2</sub> | V <sub>PP</sub> Supply Current (Program)          |      | 50                  | mA       | CE = VIL                             |

| V <sub>ID</sub>  | A <sub>9</sub> inteligent Identifier Voltage      | 11.5 | 12.5                | V        | A32.0                                |

#### NOTE:

1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

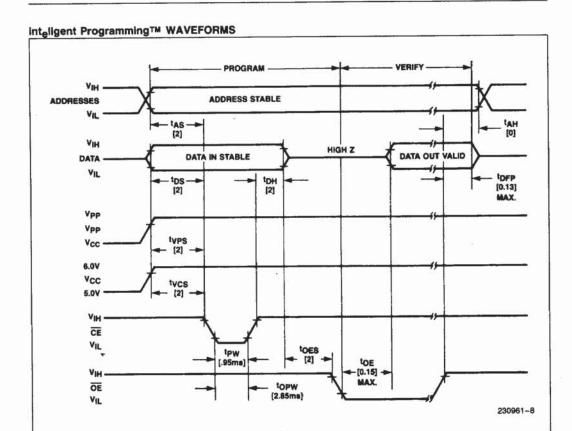

#### A.C. PROGRAMMING CHARACTERISTICS

$T_C = 25 \pm 5^{\circ}C_{1}V_{CC} = 6.0V \pm 0.25V, V_{PP} = 12.5V \pm 0.3V$

| Symbol               | Parameter                           |      | Comments |      |          |

|----------------------|-------------------------------------|------|----------|------|----------|

| Symbol               | Parameter                           | Min  | Max      | Unit | (Note 1) |

| tas                  | Address Setup Time                  | 2    |          | μs   |          |

| toes                 | OE Setup Time                       | 2    |          | μs   |          |

| t <sub>DS</sub>      | Data Setup Time                     | 2    |          | μs   |          |

| t <sub>AH</sub>      | Address Hold Time                   | 0    |          | μs   |          |

| t <sub>DH</sub>      | Data Hold Time                      | 2    |          | μs   |          |

| t <sub>DFP</sub> (4) | Output Enable to Output Float Delay | 0    | 130      | ns   |          |

| t <sub>VPS</sub>     | V <sub>PP</sub> Setup Time          | 2    |          | μs   |          |

| t <sub>VCS</sub>     | V <sub>CC</sub> Setup Time          | 2    |          | μs   |          |

| t <sub>PW</sub>      | CE Initial Program Pulse Width      | 0.95 | 1.05     | ms   | (Note 3) |

| topw                 | CE Overprogram Pulse Width          | 2.85 | 78.75    | ms   | (Note 2) |

| t <sub>OE</sub>      | Data Valid from OE                  |      | 150      | ns   |          |

#### \*A.C. CONDITIONS OF TEST

#### NOTES:

- 1.  $V_{CC}$  must be applied simultaneously or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

- The length of the overprogram pulse may vary from 2.85 ms to 78.75 ms as a function of the iteration counter value X.

- 3. Initial Program Pulse width tolerance is 1 ms  $\pm 5\%$ .

- 4. Output Float is defined as the point where data is no longer driven.

#### NOTES:

- NOTES:

1. All times shown in [] are minimum and in μs unless otherwise specified.

2. The input timing reference level is 0.8V for a V<sub>IL</sub> and 2V for a V<sub>IH</sub>.

3. t<sub>OE</sub> and t<sub>DFP</sub> are characteristics of the device but must be accommodated by the programmer.

4. When programming the M27256 a 0.1 μF capacitor is required across V<sub>PP</sub> and ground to suppress spurious voltage transients which can damage the device.