# Triple/Dual Phase-Equalized, Low-Pass Video Filter

### **GENERAL DESCRIPTION**

The ML6420 monolithic BiCMOS 6th-order filters provide fixed frequency low pass filtering for video applications. These triple output phase-equalized filters are designed for input anti-aliasing filtering.

Cut-off frequencies are either 3.0, 5.5, 8.0, or 9.3MHz. Each channel incorporates a 6th-order low-pass filter, a first order all-pass filter, and a 75W coax cable driver. A control pin (Range) is provided to allow the inputs to swing to ground by providing a 0.5V offset to the input.

The filters are powered from a single 5V supply, and can drive  $1V_{P-P}$  over 75W (0.5V to 1.5V), or  $2V_{P-P}$  over 150W (0.5V to 2.5V).

### **FEATURES**

- 3.0, 5.5, 8.0, or 9.3 MHz bandwidth

- 1X or 2X gain

- 6th-order filter with equalizer

- >40dB stopband rejection

- No external components or clocks

- ±10% maximum frequency accuracy over supply and temperature

- <2% differential gain, <2° differential phase

- <25ns group delay variation

- Drives  $1V_{P-P}$  into  $75\Omega$ , or  $2V_{P-P}$  into  $150\Omega$

- 5V ±10% operation

- ML6420 available with 6dB gain

- \* Some Packages Are End Of Life

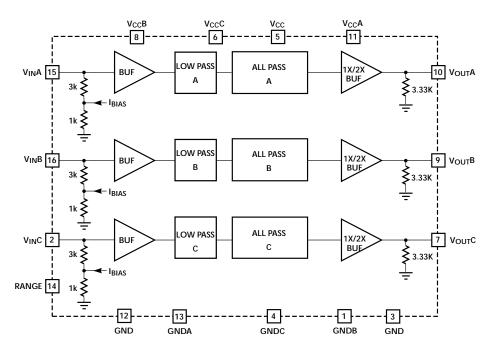

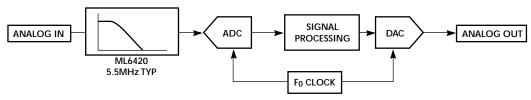

### ML 6420 BLOCK DIAGRAM

|          |          | 1X GAIN  |          | 2       | X GAIN     |

|----------|----------|----------|----------|---------|------------|

|          | ML6420-1 | ML6420-3 | ML6420-4 | ML6420- | 5 ML6420-7 |

| FILTER A | 5.5MHZ   | 8.0MHZ   | 8.0MHZ   | 5.5MHZ  | 9.3MHZ     |

| FILTER B | 5.5MHZ   | 8.0MHZ   | 3.0MHZ   | 2.5MHZ  | 9.3MHZ     |

| FILTER C | 5.5MHZ   | 8.0MHZ   | 3.0MHZ   | 2.5MHZ  | 9.3MHZ     |

Triple Input/Anti-aliasing Video Filter

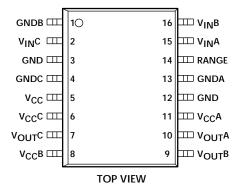

# PIN CONFIGURATION

### ML6420 16-Pin Wide SOIC (S16W)

# PIN DESCRIPTION

| PIN | NAME               | FUNCTION                                                                                                              | PIN | NAME              | FUNCTION                                                                                                                                                                                     |

|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GNDB               | Ground pin for filter B                                                                                               | 11  | $V_{CC}A$         | Power supply voltage for filter A.                                                                                                                                                           |

| 2   | $V_{IN}C$          | Signal input to filter C. Input impedance is $4k\Omega$ .                                                             | 12  | GND               | Power and logic ground.                                                                                                                                                                      |

| 3   | GND                | Power and logic ground                                                                                                | 13  | GNDA              | Ground pin for filter A.                                                                                                                                                                     |

| 4   | GNDC               | Ground pin for filter C.                                                                                              | 14  | RANGE             | Input signal range select. For -1 to -4; when RANGE is low (0), the input                                                                                                                    |

| 5   | $V_{CC}$           | Positive supply for bias circuit.                                                                                     |     |                   | signal range is 0.5V to 2.5V, with an output range of 0.5V to 2.5V. When                                                                                                                     |

| 6   | $V_{CC}C$          | Power supply voltage for filter C.                                                                                    |     |                   | RANGE is high (1) the input signal range is 0V to 2V, with an output range of 0.5V to 2.5V For 5 to 13; when                                                                                 |

| 7   | V <sub>OUT</sub> C | Output of filter C. Drive is $1V_{P-P}$ into $75\Omega$ (0.5V to 1.5V) or $2V_{P-P}$ into $150\Omega$ (0.5V to 2.5V). |     |                   | of 0.5V to 2.5V. For -5 to -12; when RANGE is low (0), the input signal range is 0.5V to 1.5V, with an output range of 0.5V to 2.5V. When RANGE is high (1) the input signal range is 0.V to |

| 8   | $V_{CC}B$          | Power supply voltage for filter B.                                                                                    |     |                   | high (1) the input signal range is 0V to 1V, with an output range of 0.5V to 2.5V.                                                                                                           |

| 9   | V <sub>OUT</sub> B | Output of filter B. Drive is $1V_{P-P}$ into $75\Omega$ (0.5V to 1.5V) or $2V_{P-P}$ into $150\Omega$ (0.5V to 2.5V). | 15  | $V_{IN}A$         | Signal input to filter A. Input impedance is $4k\Omega$ .                                                                                                                                    |

| 10  | V <sub>OUT</sub> A | Output of filter A. Drive is $1V_{P-P}$ into $75\Omega$ (0.5V to 1.5V) or $2V_{P-P}$ into $150\Omega$ (0.5V to 2.5V). | 16  | V <sub>IN</sub> B | Signal input to filter B. Input impedance is $4k\Omega$ .                                                                                                                                    |

# **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| Supply Voltage (V <sub>CC</sub> ) | 0.3 to 7V |

|-----------------------------------|-----------|

| GND                               |           |

| Logic Inputs                      |           |

| Input Current per Pin             | ±25mA     |

| Storage Temperature                   | −65° to 150°C |

|---------------------------------------|---------------|

| Package Dissipation at $T_A = 25$ °C  | 1W            |

| Lead Temperature (Soldering 10 sec)   |               |

| Thermal Resistance (q <sub>IA</sub> ) | 65°C/W        |

# **OPERATING CONDITIONS**

| Supply Voltage    | 5V $\pm$ 10% |

|-------------------|--------------|

| Temperature Range | 0°C to 70°C  |

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $V_{CC}$  = 5V  $\pm$  10%,  $T_A$  = Operating Temperature Range,  $R_L$  =75W or 150W,  $V_{OUT}$  = 2 $V_{P-P}$  for 150W Load and  $V_{OUT}$  = 1 $V_{P-P}$  for 75W Load (Notes 1-3)

| SYMBOL             | PARAMETER                       |                                             | CONDITIONS                                                | MIN  | TYP  | MAX | UNITS |

|--------------------|---------------------------------|---------------------------------------------|-----------------------------------------------------------|------|------|-----|-------|

| GENERAL            | I                               |                                             |                                                           | 1    | •    |     |       |

| R <sub>IN</sub>    | Input Impedan                   | ce                                          |                                                           | 3    | 4    | 5   | kΩ    |

| DR/R <sub>IN</sub> | Input R Matchi                  | ng                                          | Between filters A, B and C                                |      |      | ±2  | %     |

| I <sub>BIAS</sub>  | Input Current                   | ML6420 (-1 to -4)                           | V <sub>IN</sub> = 0.5V, range = low                       |      | -80  |     | μA    |

|                    |                                 |                                             | V <sub>IN</sub> = 0.0V, range = high                      |      | -125 |     | μA    |

|                    |                                 | ML6420                                      | V <sub>IN</sub> = 0.5V, range = low                       |      | 45   |     | μA    |

|                    |                                 | (-5 to-7)                                   | V <sub>IN</sub> = 0.0V, range = high                      |      | -210 |     | μA    |

|                    | Small Signal                    | ML6420 (-1 to -4)                           | $V_{IN} = 100 \text{mV}_{P-P} \text{ at } 100 \text{kHz}$ | -0.5 | 0    | 0.5 | dB    |

|                    | Gain                            | ML6420<br>(-5 to -7)                        | $V_{IN} = 100 \text{mV}_{P-P} \text{ at } 100 \text{kHz}$ | 5.5  | 6    | 6.5 | dB    |

|                    | Differential                    | ML6420 (-1 to -4)                           | $V_{IN} = 1.8V \pm 0.7V$ at 3.58 & 4.43 MHz               |      | 1    |     | %     |

|                    | Gain                            | ML6420<br>(-5 to -7)                        | $V_{1N} = 0.8V \text{ to } 1.5V$                          |      | 1    |     | %     |

|                    | Differential                    | ML6420 (-1 to -4)                           | $V_{IN} = 1.8V \pm 0.7V$ at 3.58 & 4.43 MHz               |      | 1    |     | deg   |

|                    | Phase                           | ML6420<br>(-5 to -7)                        | $V_{IN} = 0.8V \text{ to } 1.5V$                          |      | 1    |     | deg   |

| V <sub>IN</sub>    | Input Range                     | ML6420 (-1 to -4)                           | RANGE = 0, Ground                                         | 0.5  |      | 2.5 | V     |

|                    |                                 |                                             | RANGE = 1, $V_{CC}$                                       | 0.0  |      | 2.0 | V     |

|                    |                                 | ML6420                                      | RANGE = 0, Ground                                         | 0.5  |      | 1.5 | V     |

|                    |                                 | (-5 to -7)                                  | RANGE = 1, $V_{CC}$                                       | 0.0  |      | 1.0 | V     |

|                    | Peak Overshoo                   | t                                           | 2T, 0.7V <sub>P-P</sub> pulse                             |      | 2.0  |     | %     |

|                    | Crosstalk                       | ML6420 (-1 to -4)                           | $f_{IN} = 3.58$ , $f_{IN} = 4.43$ MHz                     | 50   |      |     | dB    |

|                    |                                 | ML6420<br>(-5 to -7)                        | $f_{IN} = 3.58, f_{IN} = 4.43 MHz$                        | 45   |      |     | dB    |

|                    | Channel to Cha<br>Group Delay M | annel<br>Matching (f <sub>C</sub> = 5.5MHz) | $f_{IN} = 100kHz$<br>Filters with identical $f_C$         |      | ±10  |     | ns    |

|                    | Channel to Cha                  | annel Gain Matching                         | f <sub>IN</sub> = 100kHz                                  |      | ±2   |     | %     |

# **ELECTRICAL CHARACTERISTICS** (Continued)

| SYMBOL    | P                | PARAMETER         | CONDITIONS                         | MIN  | TYP  | MAX  | UNITS             |

|-----------|------------------|-------------------|------------------------------------|------|------|------|-------------------|

| GENERAL   | (Continued)      |                   |                                    | '    |      | •    | · ·               |

|           | Output Current   |                   | $R_L = 0$ (short circuit)          |      | 75   |      | mA                |

| $C_L$     | Load Capacitan   | ice               |                                    |      |      | 35   | pF                |

|           | Composite        | ML6420 (-1 to -4) | $f_C = 5.5MHz$                     |      | ±10  |      | ns                |

|           | Chroma/Luma      |                   | $f_C = 8.0MHz$                     |      | ±8   |      | ns                |

|           | Delay At 3.58    | ML6420 (-5 to -7) | $f_C = 5.5MHz$                     |      | ±15  |      | ns                |

|           | & 4.43MHz        |                   | $f_C = 9.3MHz$                     |      | ±8   |      | ns                |

| 3.0/3.3MH | HZ FILTER – ML64 | 420               |                                    |      |      |      | •                 |

|           | Bandwidth (mo    | notonic passband) | -3dB (3.0MHz)                      | 2.7  | 3.0  | 3.3  | MHz               |

|           |                  |                   | -3dB (3.3MHz)                      | 3.0  | 3.3  | 3.6  | MHz               |

|           | Stopband Atten   | uation            | f <sub>IN</sub> = 9.82MHz (3.0MHz) | 30   | 33   |      | dB                |

|           |                  |                   | f <sub>IN</sub> = 9.82MHz (3.3MHz) | 35   | 40   |      | dB                |

|           |                  |                   | $f_{IN} = 60MHz$                   | 43   | 50   |      | dB                |

|           | Output Noise     |                   | BW = 30MHz                         |      |      | 490  | μV <sub>RMS</sub> |

|           | Group Delay      |                   |                                    |      | 225  |      | ns                |

| 5.50MHZ   | FILTER – ML6420  | )-1               |                                    | '    |      | •    | _                 |

|           | Bandwidth (mo    | notonic passband) | -3dB                               | 4.95 | 5.50 | 6.05 | MHz               |

|           | Stopband Atten   | uation            | f <sub>IN</sub> = 10MHz            | 16   | 18   |      | dB                |

|           |                  |                   | $f_{IN} = 50MHz$                   | 40   | 45   |      | dB                |

|           | Output Noise     |                   | BW = 30MHz                         |      |      | 700  | μV <sub>RMS</sub> |

|           | Group Delay      |                   |                                    |      | 145  |      | ns                |

| 8.0MHZ F  | ILTER – ML6420   |                   |                                    |      |      |      | •                 |

|           | Bandwidth (mo    | notonic passband) | -3dB                               | 7.2  | 8.0  | 8.8  | MHz               |

|           | Stopband Atten   | uation            | $f_{IN} = 17MHz$                   | 20   | 25   |      | dB                |

|           |                  |                   | $f_{IN} = 85MHz$                   | 40   | 42   |      |                   |

|           | Output Noise     |                   | BW = 30MHz                         |      |      | 700  | μV <sub>RMS</sub> |

|           | Group Delay      |                   |                                    |      | 120  |      | ns                |

# **ELECTRICAL CHARACTERISTICS** (Continued)

| SYMBOL          |                 | PARAMETER CONDI         |                                                                    | MIN                   | TYP  | MAX  | UNITS             |

|-----------------|-----------------|-------------------------|--------------------------------------------------------------------|-----------------------|------|------|-------------------|

| 5.50MHZ         | FILTER – ML642  | 20-5                    | <u>'</u>                                                           |                       |      | ı    | I.                |

|                 | Bandwidth (m    | onotonic passband)      | -3dB (Note 5)                                                      | 4.95                  | 5.50 | 6.05 | MHz               |

|                 | Attenuation     | $f_{IN} = 10MHz$        |                                                                    | 20                    | 25   |      | dB                |

|                 |                 | $f_{IN} = 50MHz$        |                                                                    | 45                    | 55   |      | dB                |

|                 | Output Noise    |                         | BW = 30MHz                                                         |                       |      | 1    | mV <sub>RMS</sub> |

|                 | Group Delay     |                         |                                                                    | 170                   |      | ns   |                   |

|                 | Small Signal C  | Gain                    | $V_{IN} = 100 \text{mV}_{P-P}$ at $100 \text{kHz}$ , Filter A or C | 5.5                   | 6    | 6.5  | dB                |

| CV              | Composite Sm    | nall Signal Gain        | $V_{IN}A$ , $C = 100 \text{mV}_{P-P}$ at $100 \text{kHz}$          | 11                    | 12   | 13   | dB                |

| 9.3MHZ F        | FILTER – ML6420 | )-7                     | ,                                                                  |                       |      |      | 1                 |

|                 | Bandwidth (m    | onotonic passband)      | -3dB (Note 5)                                                      | 8.4                   | 9.3  | 10.2 | MHz               |

|                 | Attenuation     | f <sub>IN</sub> = 17MHz |                                                                    | 20                    | 25   |      | dB                |

|                 |                 | $f_{IN} = 85MHz$        |                                                                    | 45                    | 55   |      | dB                |

|                 | Output Noise    |                         | BW = 30MHz                                                         |                       |      | 1    | mV <sub>RMS</sub> |

|                 | Group Delay     |                         |                                                                    | 100                   |      | ns   |                   |

| DIGITAL         | AND DC          |                         |                                                                    | '                     |      |      | •                 |

| V <sub>IL</sub> | Logic Input Lo  | )W                      | RANGE                                                              |                       |      | 0.8  | V                 |

| V <sub>IH</sub> | Logic Input Hi  | igh                     | RANGE                                                              | V <sub>CC</sub> - 0.8 |      |      | V                 |

| I <sub>IL</sub> | Logic Input Lo  | )W                      | V <sub>IN</sub> = GND                                              | -1                    |      |      | μA                |

| I <sub>IL</sub> | Logic Input Hi  | igh                     | $V_{IN} = V_{CC}$                                                  |                       |      | 1    | μA                |

| I <sub>CC</sub> | Supply Curren   | t $R_L = 75W$           | $V_{IN} = 0.5V \text{ (Note 4)}$                                   |                       | 110  | 135  | mA                |

|                 |                 |                         | V <sub>IN</sub> = 1.5V                                             |                       | 150  | 175  | mA                |

$<sup>\</sup>begin{array}{ll} \textbf{Note 1:} & \text{Limits are guaranteed by 100\% testing, sampling, or correlation with worst case test conditions.} \\ \textbf{Note 2:} & \text{Maximum resistance on the outputs is } 500\Omega \text{ in order to improve step response.} \\ \end{array}$

**Note 3:** Connect all ground pins to the ground plane via the shortest path.

**Note 4:** Power dissipation  $P_D = (I_{CC} \times V_{CC}) - [3 (V_{OUT}^2/R_L)]$

Note 5: The bandwidth is the -3dB frequency of the unboosted filter. This represents the attenuation that results from boosting the gain from -3dB point at the specified frequency.

### **FUNCTIONAL DESCRIPTION**

The ML6420 single-chip Dual/Triple Video Filter ICs are intended for low cost professional and consumer video applications. Each channel incorporates an input buffer amplifier, a sixth order lowpass filter, a first order allpass equalizer, and an output 1X or 2X gain amplifier capable of driving  $75\Omega$  to ground.

When RANGE is low the input and output signal range is 0.5V to 1.5V. When the input signal range is 0V to 1V, RANGE should be tied high. In this case, an offset is added to the input so that the output swing is kept between 0.5V to 1.5V. The output amplifier is capable of driving up to

24mA of peak current; therefore the output voltage should not exceed 1.8V when driving  $75\Omega$  to ground. The ML6420 can be driven by a DAC with swing down to 0V.

The summer output on the ML6422 is given by  $2x(V_{INA} + V_{INC}) - 2.5V$  when RANGE = 0 and  $2x(V_{INA} + V_{INC}) - 0.5V$  when RANGE is high. So,  $V_{INA}$  and  $V_{INC}$  should be such that this output does not go below 0.5V or above 2.5V for proper operation.

## **APPLICATION GUIDELINES**

#### **OUTPUT CONSIDERATIONS**

The triple filters have unity or 2X gain. The output circuit has unity or 2X gain (0dB) when connected to a  $150\Omega$  load, and a -6dB gain when driving a  $75\Omega$  load via a  $75\Omega$  series output resistor. The output may be either AC or DC coupled. For AC coupling (Figure 6), the -3dB point should be 5Hz or less. There must also be a DC path of  $\leq 500\Omega$  to ground for biasing.

The dual filters have 2X gain. The filter has 2X gain (6dB) when connected to a  $150\Omega$  load, and a 0dB gain when driving a  $75\Omega$  load via a  $75\Omega$  series output resistor. The output may be either AC or DC coupled. For AC coupling, the -3dB point should be 5Hz or less. There must also be a DC path of  $\le 500\Omega$  to ground for output biasing.

#### **INPUT CONSIDERATIONS**

The input resistance is  $4k\Omega$ . The input may be either DC or AC coupled. (Note that each input sources 80 to  $125\mu A$  of bias current).

### LAYOUT CONSIDERATIONS

In order to obtain full performance from these triple filters, layout is very important. Good high frequency decoupling is required between each power supply and ground. Otherwise, oscillations and/or excessive crosstalk may occur. A ground plane is recommended.

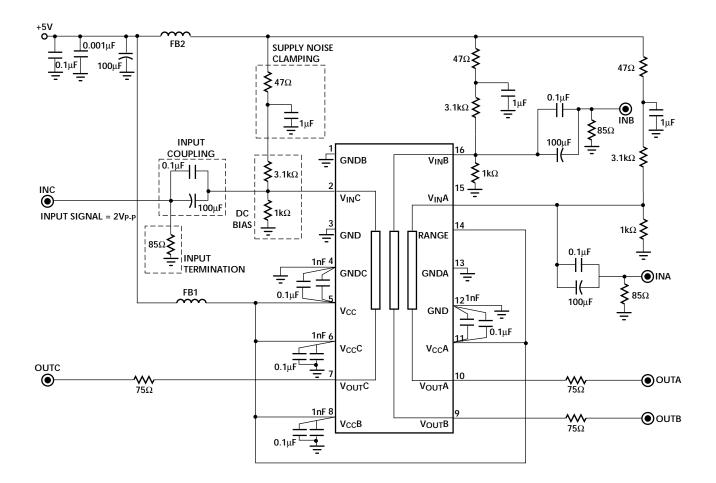

Each filter has its own supply and ground pins. In the test circuit,  $0.1\mu F$  capacitors are connected in parallel with  $0.001\mu F$  capacitors on pins  $V_{CC}$ ,  $V_{CC}A$ ,  $V_{CC}B$  and  $V_{CC}C$  for maximum noise rejection (Figure 6A and Figure 1G).

Further noise reduction is achieved by using series ferrite beads. In typical applications, this degree of bypassing may not be necessary.

Since there are three filters in one 16-pin SOIC package, space the signal leads away from each other as much as possible.

#### **POWER CONSIDERATIONS**

The ML6420 power dissipation follows the formula:

$$P_{D} = (I_{CC} \times V_{CC}) - \left(\frac{V_{OUT}^{2}}{R_{L}} \times 3\right)$$

This is a measure of the amount of current the part sinks (current in — current out to the load).

Under worst case conditions:

$$P_D = (0.175 \times 5.5) - \left(\frac{1.5^2}{75} \times 3\right) = 872.5 \text{mW}$$

Power consumption can be reduced by not suppling  $V_{CC}$  to unused filter sections. ( $V_{CC}A$ ,  $V_{CC}B$  or  $V_{CC}C$ )

#### **TEST CIRCUITS**

Figures 6A shows the test circuitn used for measuring the frequency and group delay. It is expected that actual customer circuits will be much simpler, since board bypasses already exist and DC coupling or clamping will be utilized at the inputs.

#### ML6420 VIDEO LOW PASS FILTER

**Filter Selection:** The ML6420 provides several choices in filter cut-off frequencies depending on the application.

**RGB:** When the bandwidth of each signal is the same, then the 5.5MHz or 8.0MHz/9.3MHz are appropriate depending on the sampling rate. (13.5MHz vs 27MHz)

**YUV:** When the luminance bandwidth is different from the color bandwidth, the ML6420-4 with the 8.0, 3.0 and 3.0MHz filters are more appropriate.

**S-Video:** For Y/C (S-video) and Y/C + CV (Composite Video) systems the ML6420 with 5.5MHz or 8.0MHz filters or ML6422 with 5.5MHZ and 9.3MHz filters are appropriate. In NTSC the C signal occupies the bandwidth from about 2.6MHz to about 4.6MHz, while in PAL the C signal occupies the bandwidth from about 3.4MHz to about 5.4MHz. In both cases, a 5.5MHz low pass filter provides adequate rejection for both sampling and reconstruction. In addition, using the same filter for both Y/C and CV maintains identical signal timing without adjustments.

**Composite:** When one or more composite signals need to be filtered, then the 5.50MHz, 8.0MHz, or 9.3MHz filters permit filtering of one, two or three composite signals.

**4X Over sampling:** While the ML6420 filters can eliminate the need for over sampling combined with digital filtering, there are times when over sampling is needed. For these situations, 8.0MHz or 9.3MHz is used in place of 5.5MHz, and 3.0MHz is used in place of 1.8MHz.

NTSC/PAL: A 5.50MHz cut-off frequency provides good

filtering for 4.2MHz, 5.0MHz.

Sinx/x: For digital video system with output D/A converters, there is a fall-off in response with frequency due to discrete sampling. The fall-off follows a sinx/x response. The ML6421 and ML6423 filters have a complementary boost to provide a flatter overall response. The boost is designed for 13.5MHz and 27MHz Y/C and CV sampling and 6.75MHz or 13.5MHz U/V sampling. The ML6421 has the same pin-out as the ML6420.

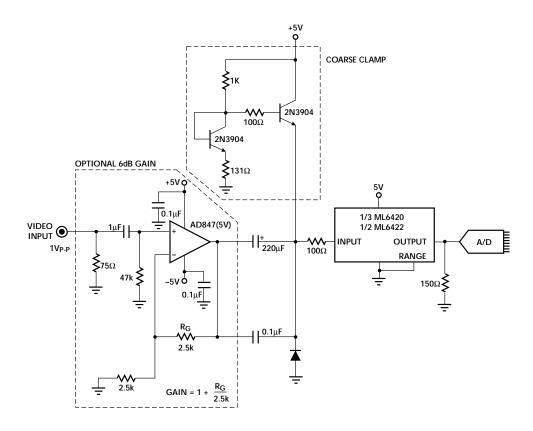

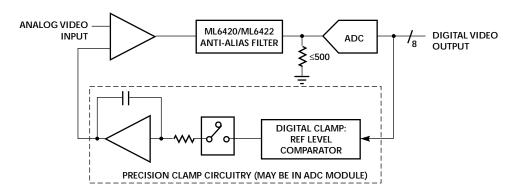

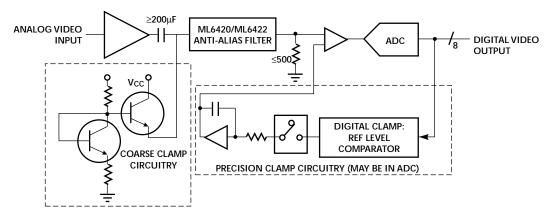

#### TYPICAL CLAMPING SCHEMES

Figures 8 and 9 show two typical applications of the ML6420 for anti-aliasing prior to A-to-D conversion. In Figure 8, a single precision digital feedback clamp circuit includes both the ADC and the ML6420. This establishes the proper DC operating point for the ML6420 (with RANGE input = 0V, 0.5V  $\leq$  V $_{IN}$   $\leq$  1.5V; with RANGE input = 5V, 0.0  $\leq$  V $_{IN}$   $\leq$  1.0V.) and the ADC. Figure 8 is typically used with ADC's that require external clamp circuitry. Figure 9 shows AC coupled application for ADC's with built-in clamps. In this case, the clamp is internal to the ADC and the ML6420 uses a simple coarse clamp at its input to establish the proper operating point.

#### USING VIDEO FILTERS

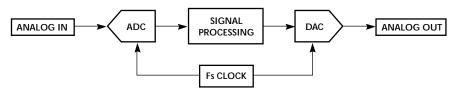

The ML6420 are monolithic, triple/dual lowpass filters intended for input anti-aliasing prior to analog to digital conversion in video systems.

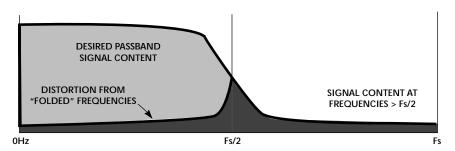

#### ALIASING: THE PROBLEM

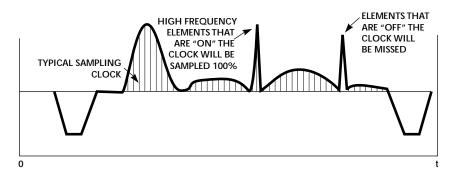

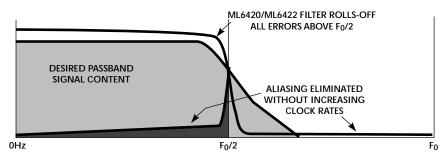

Aliasing is a signal distorting process that occurs when an analog signal is sampled. If the analog signal contains frequencies greater than half of the sampling rate, those frequencies will be altered and "folded back" in the frequency domain. These frequencies represent a distortion of the original signal as represented in the sampled domain, and cannot be corrected after sampling.

#### THE RESULT OF ALIASING IN A TV PICTURE

Aliasing causes several disturbing distortions to a picture. Since the folded spectrum adds to the original spectrum, it will sometimes be in phase, and sometimes out of phase causing ripples in response that depend on the position of the picture element relative to the clock. The net effect is that picture elements, edges, highlights, and details will "wink" in amplitude as they move across a picture if they have high frequency content above the Nyquist frequency of the sampler.

#### **ANTI-ALIASING**

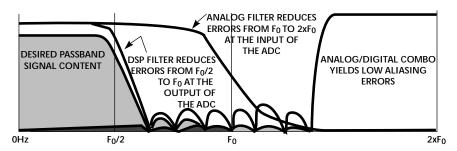

Anti-aliasing reduces the bandwidth of the signal to a value appropriate for the sample processing system. Some detail information is lost, but only the information that cannot be unambiguously displayed is removed. Assuming that the passband contains the "real" picture information, the only distortion that occurs is due to amplitude and phase variations of the anti-aliasing filter in the passband. The following section shows approaches using digital and analog filters in an oversampled system, and a monolithic analog filter as a lower cost alternative.

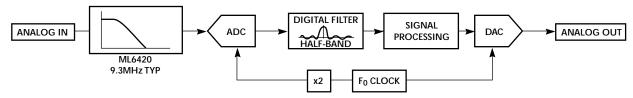

#### **OVERSAMPLING**

Aliasing cannot be removed once it occurs, it must be prevented at the signal sampler. Many current systems are choosing to prevent aliasing by increasing the clock rate of the sampler. This is known as "oversampling". Doubling the clock rate greatly reduces the burden on the analog anti-alias filter, but the increased data rate greatly increases the size, complexity and cost of the Digital Signal Processing (DSP) circuitry. Since the higher clock rate generates more samples than are necessary to represent the desired passband content, a digital filter may be used to decimate the signal back to a lower sample rate, saving size, complexity and power in the downstream circuitry. Since this digital filter itself is a complex digital block, this method cannot be considered the lowest cost approach to solving the anti-alias problem.

#### **NYQUIST SAMPLING**

In traditional systems, before the advent of higher speed ADCs, anti-aliasing filters were designed in the analog domain. The movement toward higher sampling rates was an attempt to circumvent the difficult challenge of designing a sharp roll-off, linear phase, non-distorting analog filter. The ML6420 series of filters solve this problem where it is best solved, in the analog domain. Since they are monolithic, their application is simple.

Since they have flat amplitude and linear phase, they are low distortion. And since the aliasing is removed at the analog input to the ADC, the clock rates are minimized, an expensive DSP half band filter is eliminated, and significant power is conserved.

#### Oversampling vs Nyquist sampling

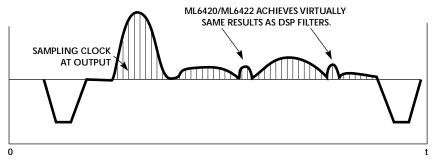

Clearly the purely analog monolithic solution versus the analog/digital solution using DSP filtering are different ways of solving the same problem. Other than costs (purely analog is many times less expensive) there are no real differences in performance for applications that require flatness specs of  $\pm 0.5 \, \text{db}$  to  $4.5 \, \text{MHz}$  for consumer and pro-sumer video applications. The ML6420/ML6422 are also phase corrected for flat group delay, a feature not found in typical low cost analog filters, and a characteristic often associated with digital filters alone. The following section highlights the importance of linear phase response in video applications.

# TIME DOMAIN RESPONSE: TRANSIENTS AND RINGING

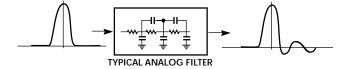

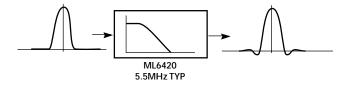

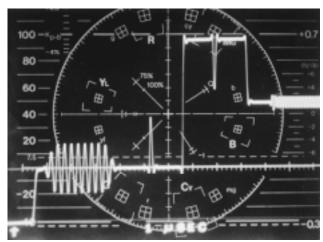

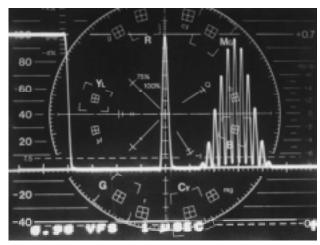

The phase response of filters is often ignored in applications where time domain waveforms are not relevant. But in video applications the time domain waveform is the signal that is finally presented on the screen to the viewer, and so time domain characteristics such as pulse response symmetry, pre-shoot, over-shoot and ringing are very important. Video applications are very demanding in that they require both sharp cutoff characteristics and linear phase. The application of DSP to the problem is based on the linear phase characteristic of a particular class of digital filters known as symmetrical FIR filters. Use of these filters guarantees the best possible time domain characteristics for a given amplitude characteristic. In the analog domain phase linearity is not automatic (except for special phase linear filters such as Bessel or Thomson filters, both of which have inadequate amplitude characteristics for most video anti-alias applications) and it is often assumed that linear phase is unachievable. This is not true. Similarly, in the digital domain it is often assumed that sharp cutoff amplitude characteristics can be achieved without overshoot and ringing. This is also not true. Phase linear filters whether digital or analog have symmetrical response to symmetrical inputs. High roll-off rate uncompensated filters (whether analog or digital) have ringing and overshoot. In the example below, the traditional 2T test pulse is applied to a traditional, non-phase linear analog filter, the ML6420 pure analog anti-alias filter (5.5MHz) and the combined analog/digital filters (9.3MHz analog filter and half-band digital filter.)

As seen in Figure 19c, the ML6420 filters provide a time domain response that is comparable to more complex and expensive filters.

#### Typical Passive Filter

# **USING VIDEO FILTERS (CONTINUIED)**

The output waveform is not symmetric. All ringing occurs after the main pulse. Result is visual smearing and fine ghosting to the right of every edge in the picture. See old Figure 19a.

### **Phase Corrected Analog Filter**

Output waveform is substantially symmetric. Ringing is greatly reduced. Result is increase in apparent resolution. No smearing or ghosting.

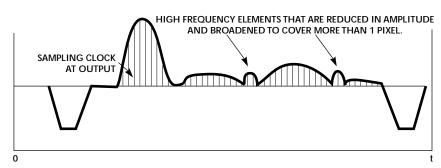

#### Analog Filtering in the Time Domain

Output waveform is symmetric. Ringing is about the same as ML6420 alone. Difference between purely analog and analog/digital approach is subtle and will only have a material effect on multi-pass video processing.

Figure 19a.

Figure 19b.

Figure 19c.

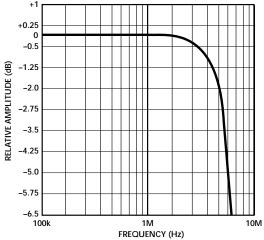

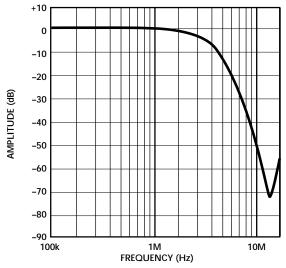

Figure 1A. Stop-Band Amplitude vs Frequency (f<sub>C</sub> = 5.5MHz). ML6420

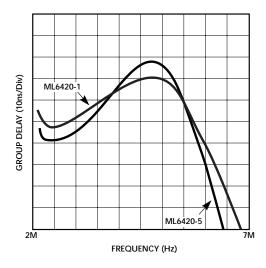

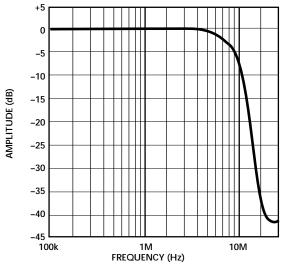

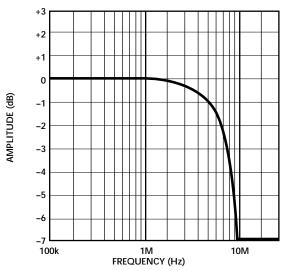

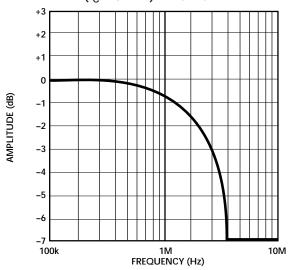

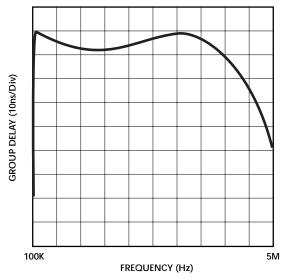

Note: Figure 1, 2 and 3 data was measured using the test circuit in Figure 6.

Figure 2A. Pass-Band Amplitude vs Frequency (f<sub>C</sub> = 5.5MHz). ML6420

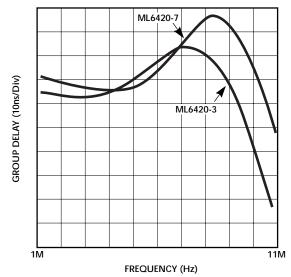

Figure 3A. Group Delay vs Frequency ( $f_C = 5.5MHz$ ). ML6420

Figure 1C. Stop-Band Amplitude vs Frequency  $(f_C = 9.3MHz)$ . ML6420

Figure 2C. Pass-Band Amplitude vs Frequency  $(f_C = 9.3MHz)$ . ML6420

Figure 3C. Group Delay vs Frequency ( $f_C = 9.3MHz$ ). ML6420

Figure 1D. Stop-Band Amplitude vs Frequency  $(f_C = 3MHz)$ . ML6420

Figure 2D. Pass-Band Amplitude vs Frequency  $(f_C = 3MHz)$ . ML6420

Figure 3D. Group Delay vs Frequency ( $f_C = 3MHz$ ). ML6420

Figure 1H. Cascading Filters for Sharper Cutoff

Figure 4. Burst with 100ns Pulse and Fast Transition at ML6420 Output Showing Symetrical Pulse Response

**Note:** Figure 4 and 5 data was measured using the test circuit in Figure 7.

Figure 5. Step with 2T and 12T Response at ML6420 Output Showing Accurate Pulse Response without Overshoot or Ringing

Figure 6A. ML6420 AC Coupled DC Bias Test Circuit

Figure 7. Video Clamp Prior to A/D Conversion

Figure 8. DC Coupled Video Digitizer for  $2V_{P-P}$  Video Signals

Figure 9. AC Coupled Video Digitizer for  $2V_{P-P}$  Video Signals

Figure 10. Simplified Digital Video Processing System

Figure 11. Aliasing in the Frequency Domain

Figure 12. Aliasing in the Time Domain

Figure 13. Oversampled Video Processing System with Analog LPF & Half-Band Digital Filter

Figure 14. Digital Filtering in the Frequency Domain

Figure 15. Digital Filtering in the Time Domain

Figure 16. Video Processing System with Monolithic Analog Anti-Alias Filter

Figure 17. Analog Filtering in the Frequency Domain

Figure 18. Analog Filtering in the Time Domain

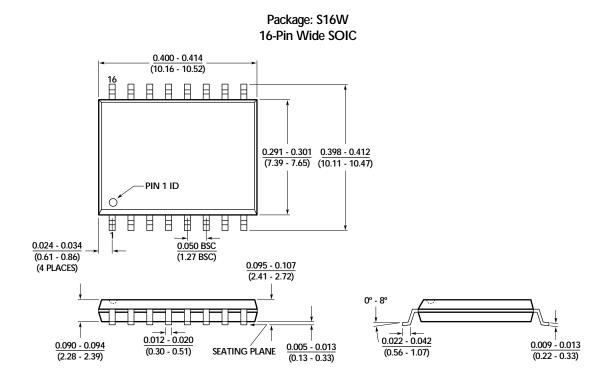

## PHYSICAL DIMENSIONS inches (millimeters)

### ORDERING INFORMATION

| PART NUMBER      | BW (MHZ)    | GAIN | TEMPERATURE RANGE | PACKAGE            |

|------------------|-------------|------|-------------------|--------------------|

| ML6420CS-1 (EOL) | 5.5/5.5/5.5 | 1X   | 0°C to 70°C       | 16-pin SOIC (S16W) |

| ML6420CS-3       | 8.0/8.0/8.0 | 1X   | 0°C to 70°C       | 16-pin SOIC (S16W) |

| ML6420CS-4 (EOL) | 8.0/3.0/3.0 | 1X   | 0°C to 70°C       | 16-pin SOIC (S16W) |

| ML6420CS-5 (EOL) | 5.0/5.0/5.0 | 2X   | 0°C to 70°C       | 16-pin SOIC (S16W) |

| ML6420CS-7 (EOL) | 9.3/9.3/9.3 | 2X   | 0°C to 70°C       | 16-pin SOIC (S16W) |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

© 2000 Fairchild Semiconductor Corporation

20 REV. 1.0 100/\$2420000