### **General Description**

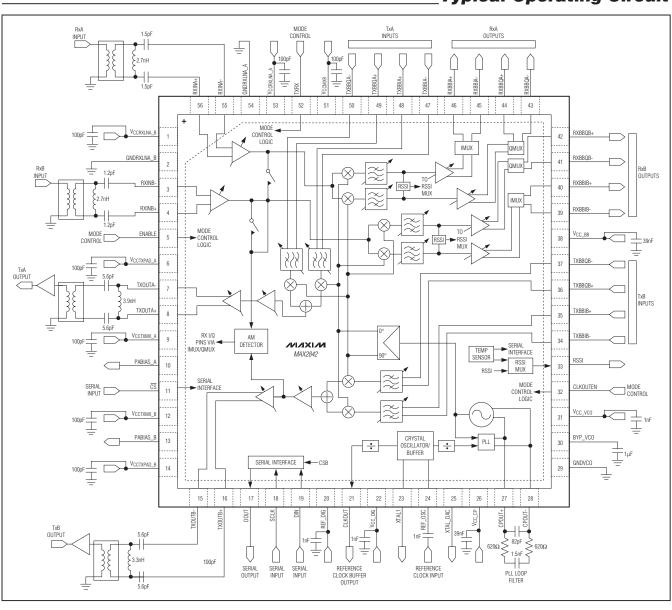

The MAX2842 single-chip, direct-conversion, zero-IF RF transceiver IC is designed for 3GHz NLOS wireless broadband MIMO systems. It has two transmitters and two receivers, with differential  $100\Omega$  RF inputs and outputs. The IC includes all circuitry required to implement the complete RF transceiver function, providing fully integrated receive paths, transmit path, VCO and tank, frequency synthesis, and baseband/control interface. It includes a fast-settling sigma-delta RF fractional synthesizer with ~25Hz frequency step size. The IC also integrates an on-chip AM detector for measuring transmitter I/Q imbalance and LO leakage. An internal transmit-toreceive loopback mode allows for receiver I/Q imbalance calibration. The IC supports full duplex mode of operation for external loopback.

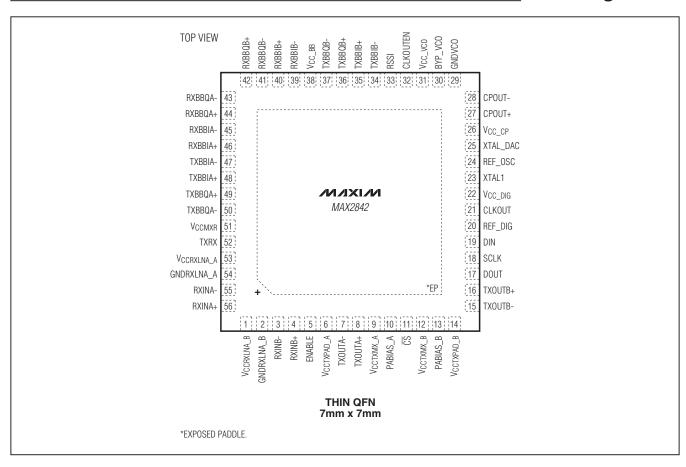

The MAX2842 completely eliminates the need for external SAW filters by implementing on-chip programmable monolithic filters for both receiver and transmitter, for channel bandwidths from 3.5MHz to 10MHz. The baseband filtering Rx and Tx signal paths are optimized to meet stringent noise figure and linearity requirements. The transceiver is housed in a small 56-pin TQFN, 7mm x 7mm, leadless plastic package with exposed paddle.

### **Applications**

3GHz 16d and 16e MIMO WiMAX

#### **Features**

- ♦ 3.3GHz to 3.9GHz Operation

- **♦** Complete RF Transceiver with PA Driver 0dBm Linear OFDMA Transmit Power, 64-QAM, -65dB Relative Spectral Emission Mask

- 3.8dB Receiver Noise Figure

Automatic On-Chip Receiver I/Q DC Cancellation On-Chip Tx I/Q Gain/Phase Error and LO

Leakage Detection

Monolithic Low-Noise VCO with -38dBc **Integrated Phase Noise**

Fully Integrated Programmable I/Q Lowpass Rx Channel Filters for 3.5MHz, 5MHz, 7MHz, and 10MHz Channels

Programmable Tx I/Q Lowpass Reconstruction **Filters**

Fractional PLL with 50µs Channel Hopping Time (Settling to 50Hz)

4-Wire Bidirectional SPI™ Interface

60dB Transmit Power Control Range, Digitally Controlled by SPI

71dB Receive Gain Control Range, Digitally Controlled by SPI

**RSSI** with 60dB Dynamic Range

Digital Control for Tx, Rx, Shutdown, and Standby Modes

On-Chip Crystal Oscillator with Digital Tuning **Programable Logic Interface Voltages Both Automatic and Modem-Assisted Receiver**

I/Q DC Offset Correction

- ♦ Single +2.7V to +3.6V Supply

- **♦ Low Shutdown Mode Current**

- ◆ Small 56-Pin TQFN Package (7mm x 7mm)

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |  |  |

|--------------|----------------|-------------|--|--|

| MAX2842ETN+T | -40°C to +85°C | 56 TQFN-EP* |  |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Typical Operating Circuit appears at end of data sheet.

SPI is a trademark of Motorola, Inc.

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> _ Pins to GND0.3V to +3.9V                                |

|---------------------------------------------------------------------------|

| RF Inputs: Maximum Current at RXINA+,<br>RXINA-, RXINB+, RXINB1mA to +1mA |

| RF Outputs: TXOUTA+, TXOUTA-, TXOUTB+,                                    |

| TXOUTB- to GND0.3V to +3.9V                                               |

| Analog Inputs: TXBBIA+, TXBBIA-,                                          |

| TXBBQA+, TXBBQA-, TXBBIB+, TXBBIB-,                                       |

| TXBBQB+, TXBBQB-, REF_DIG to GND0.3V to +3.9V                             |

| Analog Input: XTAL1, REF_OSCAC-Coupled Only                               |

| Analog Outputs: Maximum Current at                                        |

| RXBBIA+, RXBBIA-, RXBBQA+, RXBBQA-,                                       |

| RXBBIB+, RXBBIB-, RXBBQB+,                                                |

| RXBBQB-, CPOUT+, CPOUT1mA to +1mA                                         |

| Analog Outputs: Maximum Current at                                        |

| PABIAS_A, PABIAS_B100mA to +100mA                                         |

| Digital Inputs: TXRX, CS, SCLK, DIN,                  |                 |

|-------------------------------------------------------|-----------------|

| ENABLE, CLKOUTEN to GND                               | 0.3V to +3.9V   |

| Digital Outputs: DOUT, CLKOUT                         | 0.3V to +3.9V   |

| Bias Voltages: BYP_VCO                                | 0.3V to +3.9V   |

| Short-Circuit Duration on All Output Pins             | 10s             |

| RF Input Power: All RXIN                              | +10dBm          |

| RF Output Differential Load VSWR: All TXOUT           | 6:1             |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C) |                 |

| 56-Pin TQFN (derate 27.8mW/°C above +70°              | C)< 2222mW      |

| Operating Temperature Range                           | 40°C to +85°C   |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | -65°C to +160°C |

| Lead Temperature (soldering, 10s)                     |                 |

| Soldering Temperature (reflow)                        | +260°C          |

|                                                       |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS TABLE

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = -40°C to +85°C, Rx set to the maximum gain. ENABLE and TXRX are set according to operating mode,  $\overline{CS}$  = high, SCLK = DIN = low, no input signal at RF inputs, all RF inputs and outputs terminated into  $50\Omega$ , receiver baseband outputs are open.  $90\text{mV}_{RMS}$  differential I and Q signals (1MHz) applied to I and Q baseband inputs of transmitter in transmit mode, all registers set to recommended settings and corresponding test mode, unless otherwise noted. Typical values are at  $V_{CC}$  = 2.8V,  $f_{LO}$  = 3.6GHz, and  $T_A$  = +25°C, unless otherwise noted. LOGIC\_VREF =  $V_{CC}$ .) (Note 1)

| PARAMETER                            | COI                                               | NDITIONS                                 | MIN | TYP | MAX  | UNITS |

|--------------------------------------|---------------------------------------------------|------------------------------------------|-----|-----|------|-------|

| Supply Voltage, VCC                  |                                                   |                                          | 2.7 |     | 3.6  | V     |

|                                      | Shutdown mode                                     |                                          |     | 10  |      | μΑ    |

|                                      | Shutdown mode with 44                             | .8MHz reference clock output             |     | 1.9 | 3.6  |       |

|                                      | Shutdown mode with cry<br>44.8MHz reference clock | vstal oscillator enabled and<br>k output |     | 2.9 | 5.0  |       |

|                                      | Standby mode                                      |                                          |     | 35  | 50   |       |

|                                      | Rx mode                                           | One receiver on                          |     | 77  | 96   | mA    |

| Supply Current                       | nx mode                                           | Both receivers on                        |     | 115 | 142  |       |

|                                      | Tx mode                                           | One transmitter on                       |     | 152 | 190  |       |

|                                      |                                                   | Both transmitters on                     |     | 246 | 320  |       |

|                                      | Receiver loopback I/Q                             | One receiver on                          |     | 125 | 155  |       |

|                                      | calibration                                       | Both receivers on                        |     | 154 | 190  |       |

|                                      | Transmitter calibration                           | One transmitter on                       |     | 119 | 148  |       |

|                                      | with AM detector                                  | Both transmitters on                     |     | 181 | 230  |       |

| Rx I/Q Output Common-Mode<br>Voltage | D5:D4 = 00 in Local add                           | dress 8                                  |     | 1.0 |      |       |

|                                      | D5:D4 = 01 in Local add                           | D5:D4 = 01 in Local address 8            |     | 1.1 | 1.32 | V     |

|                                      | D5:D4 = 10 in Local add                           | D5:D4 = 10 in Local address 8            |     | 1.2 |      | ] v   |

|                                      | D5:D4 = 11 in Local add                           | D5:D4 = 11 in Local address 8            |     | 1.3 |      |       |

### DC ELECTRICAL CHARACTERISTICS TABLE (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = -40°C to +85°C, Rx set to the maximum gain. ENABLE and TXRX are set according to operating mode,  $\overline{CS}$  = high, SCLK = DIN = low, no input signal at RF inputs, all RF inputs and outputs terminated into 50Ω, receiver baseband outputs are open. 90mV<sub>RMS</sub> differential I and Q signals (1MHz) applied to I and Q baseband inputs of transmitter in transmit mode, all registers set to recommended settings and corresponding test mode, unless otherwise noted. Typical values are at  $V_{CC}$  = 2.8V,  $f_{LO}$  = 3.6GHz, and  $T_A$  = +25°C, unless otherwise noted. LOGIC\_VREF =  $V_{CC}$ .) (Note 1)

| PARAMETER                                             | CONDITIONS                                                                 | MIN                     | TYP | MAX | UNITS |

|-------------------------------------------------------|----------------------------------------------------------------------------|-------------------------|-----|-----|-------|

| Tx Baseband Input Common-Mode Voltage Operating Range | To achieve at least +4dBm Tx output P - 1dB with maximum -3dB gain setting | 0.5                     |     | 1.2 | V     |

| Tx Baseband Input Bias Current                        | Source current                                                             |                         | 10  | 25  | μΑ    |

| LOGIC INPUTS: TXRX, ENABLE, S                         | SCLK, DIN, CS, CLKOUTEN                                                    |                         |     |     |       |

| Digital Input-Voltage High, V <sub>IH</sub>           |                                                                            | V <sub>C</sub> C - 0.4V |     |     | V     |

| Digital Input-Voltage Low, VIL                        |                                                                            |                         |     | 0.4 | V     |

| Digital Input-Current High, I <sub>IH</sub>           |                                                                            | -1                      |     | +1  | μΑ    |

| Digital Input-Current Low, I <sub>I</sub> L           |                                                                            | -1                      |     | +1  | μΑ    |

| LOGIC OUTPUTS: DOUT, CLKOUT                           | Т                                                                          |                         |     |     |       |

| Digital Output-Voltage High, VOH                      | Sourcing 100µA                                                             | VCC -<br>0.4V           |     |     | V     |

| Digital Output-Voltage Low, VOL                       | Sinking 100µA                                                              |                         |     | 0.4 | V     |

| DOUT Voltage in Shutdown Mode or Disabled Mode        | D7:D5 = 000 in Main address 22                                             |                         | VoL |     | V     |

| CLKOUT Voltage When Disabled                          |                                                                            |                         | Vol |     | V     |

#### AC ELECTRICAL CHARACTERISTICS TABLE—Rx Mode

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  =  $\pm 25^{\circ}$ C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, baseband output signal frequency = 1MHz, receiver baseband I/Q output at 90mV<sub>RMS</sub>, REF\_OSC frequency = 44.8MHz, ENABLE = TXRX =  $\overline{CS}$  = high, SCLK = DIN = low. Lowpass filter is set to 10MHz RF channel BW, with power matching for the differential RF pins using the *Typical Operating Circuit*. RXBB\_ pins are loaded with differential  $10k\Omega$  resistor and 10pF capacitance in parallel. Registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications that normally apply over the entire operating conditions, unless otherwise indicated.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                               |                                                                                     | MIN | TYP | MAX | UNITS |  |

|-----------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| RECEIVER SYSTEM: RF INPUT TO I/Q BASEBAND LOADED OUTPUT   |                                                          |                                                                                     |     |     |     |       |  |

| RF Input Frequency Range                                  |                                                          |                                                                                     | 3.3 |     | 3.9 | GHz   |  |

| Peak-to-Peak Gain Variation Over RF Input Frequency Range | Tested at band edges and band center; at one temperature |                                                                                     |     | 3   |     | dB    |  |

| S11 of RF Input Port                                      | All RF gains                                             |                                                                                     |     | -10 |     | dB    |  |

| Total Voltage Gain                                        | $T_A = -40^{\circ}C$ to                                  | Maximum gain; D7:D0 = 11111000 in Main address 2 for Rx1, in Main address 3 for Rx2 | 70  | 77  |     | dB    |  |

|                                                           | +85°C                                                    | Minimum gain; D7:D0 = 00000111 in Main address 2 for Rx1, in Main address 3 for Rx2 |     | 6   | 14  | uB    |  |

### AC ELECTRICAL CHARACTERISTICS TABLE—Rx Mode (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, baseband output signal frequency = 1MHz, receiver baseband I/Q output at 90mV<sub>RMS</sub>, REF\_OSC frequency = 44.8MHz, ENABLE = TXRX =  $\overline{CS}$  = high, SCLK = DIN = low. Lowpass filter is set to 10MHz RF channel BW, with power matching for the differential RF pins using the *Typical Operating Circuit*. RXBB\_ pins are loaded with differential 10k $\Omega$  resistor and 10pF capacitance in parallel. Registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications that normally apply over the entire operating conditions, unless otherwise indicated.) (Note 1)

| PARAMETER                 | CONDITIONS                                                                                                                                                                           | MIN                                                   | TYP | MAX | UNITS |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|-----|-------|--|

|                           | From maximum RF gain to maximum RF gain - 8dB (D2:0 = 001 in Main address 2 for Rx1, in Main address 3 for Rx2)                                                                      |                                                       | 8   |     |       |  |

|                           | From maximum RF gain to maximum RF gain - 16dB (D2:0 = 010 in Main address 2 for Rx1, in Main address 3 for Rx2)                                                                     | D2:0 = 010 in Main address 2 for Rx1, in Main address |     |     |       |  |

| RF Gain Steps             | From maximum RF gain to maximum RF gain - 24dB (D2:0 = 011 in Main address 2 for Rx1, in Main address 3 for Rx2)                                                                     |                                                       | 24  |     | dB    |  |

|                           | From maximum RF gain to maximum RF gain - 32dB (D2:0 = 110 in Main address 2 for Rx1, in Main address 3 for Rx2)                                                                     |                                                       | 32  |     |       |  |

|                           | From maximum RF gain to maximum RF gain - 40dB (D2:0 = 111 in Main address 2 for Rx1, in Main address 3 for Rx2)                                                                     |                                                       | 40  |     |       |  |

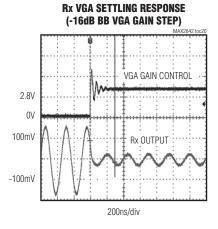

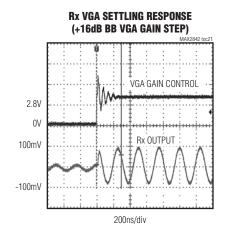

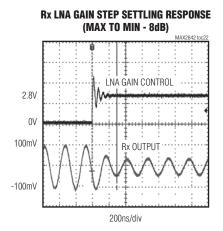

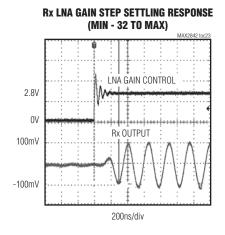

| Gain Changa Sattling Time | Any RF or baseband gain change; signal amplitude settling to ±0.5dB of steady state, excludes I/Q path DC offset settling                                                            |                                                       | 300 |     | 20    |  |

| Gain Change Settling Time | Any RF or baseband gain change; signal amplitude settling to ±0.1dB of steady state, excludes I/Q path DC offset settling                                                            |                                                       | 500 |     | ns    |  |

| Baseband Gain Range       | From maximum baseband gain (D7:D3 = 00000 in Main address 2 for Rx1, in Main address 3 for Rx2) to minimum gain (D7:D3 = 11111 in Main address 2 for Rx1, in Main address 3 for Rx2) | 28                                                    | 31  | 34  | dB    |  |

| Baseband Gain Step Size   |                                                                                                                                                                                      |                                                       | 1   |     | dB    |  |

MIXIM

### AC ELECTRICAL CHARACTERISTICS TABLE—Rx Mode (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, baseband output signal frequency = 1MHz, receiver baseband I/Q output at 90mV<sub>RMS</sub>, REF\_OSC frequency = 44.8MHz, ENABLE = TXRX =  $\overline{CS}$  = high, SCLK = DIN = low. Lowpass filter is set to 10MHz RF channel BW, with power matching for the differential RF pins using the *Typical Operating Circuit*. RXBB\_ pins are loaded with differential 10k $\Omega$  resistor and 10pF capacitance in parallel. Registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications that normally apply over the entire operating conditions, unless otherwise indicated.) (Note 1)

| PARAMETER             | CONDITIONS                                                                  |                                                                                                                                 | MIN | TYP  | MAX | UNITS |

|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| DSB Noise Figure      |                                                                             | Voltage gain ≥ 65dB with maximum RF gain (D7:0 = 10111000 in Main address 2 for Rx1, in Main address 3 for Rx2)                 | 3.8 |      |     |       |

|                       | Balun input                                                                 | Voltage gain = 50dB with maximum RF gain - 8dB (D7:0 = 10000001 in Main address 2 for Rx1, in Main address 3 for Rx2)           |     | 7.1  |     | dB    |

|                       | referred                                                                    | Voltage gain = 45dB with maximum RF gain - 16dB (D7:0 = 10011010 in Main address 2 for Rx1, in Main address 3 for Rx2)          |     | 13.3 |     | αь    |

|                       |                                                                             | Voltage gain = 15dB with maximum RF gain - 32dB (D7:0 = 00101110 in Main address 2 for Rx1, in Main address 3 for Rx2)          |     | 28.2 |     |       |

| Out-of-Band Input IP3 | Two tones at +20MHz and +39MHz offsets, at -35dBm each; measure IM3 at 1MHz | AGC set for -65dBm wanted signal, maximum RF gain (D7:0 = xxxxx000 in Main address 2 for Rx1, in Main address 3 for Rx2)        |     | -15  |     |       |

|                       |                                                                             | AGC set for -55dBm wanted signal, maximum RF gain - 8dB (D7:0 = xxxxx001 in Main address 2 for Rx1, in Main address 3 for Rx2)  |     | -9   |     | alD   |

|                       |                                                                             | AGC set for -40dBm wanted signal, maximum RF gain - 16dB (D7:0 = xxxxx010 in Main address 2 for Rx1, in Main address 3 for Rx2) |     | -6   |     | dBm   |

|                       |                                                                             | AGC set for -30dBm wanted signal, maximum RF gain - 32dB (D7:0 = xxxxx110 in Main address 2 for Rx1, in Main address 3 for Rx2) |     | 0    |     |       |

### AC ELECTRICAL CHARACTERISTICS TABLE—Rx Mode (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, baseband output signal frequency = 1MHz, receiver baseband I/Q output at 90mV<sub>RMS</sub>, REF\_OSC frequency = 44.8MHz, ENABLE = TXRX =  $\overline{CS}$  = high, SCLK = DIN = low. Lowpass filter is set to 10MHz RF channel BW, with power matching for the differential RF pins using the *Typical Operating Circuit*. RXBB\_ pins are loaded with differential 10k $\Omega$  resistor and 10pF capacitance in parallel. Registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications that normally apply over the entire operating conditions, unless otherwise indicated.) (Note 1)

| PARAMETER                                       |                                                                                            | CONDITIONS                                                                                                                                                                                                                                                      | MIN | TYP  | MAX | UNITS            |  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------------------|--|

| Out-of-Band Input IP2                           | Two tones at<br>+50MHz and<br>+51MHz offsets,<br>at -40dBm each;<br>measure IM2 at<br>1MHz | AGC set for -65dBm wanted signal, maximum RF gain (D7:0 = xxxxx000 in Main address 2 for Rx1, in Main address 3 for Rx2)                                                                                                                                        |     | 30   |     | dBm              |  |

|                                                 | Maximum RF gain<br>Rx1, in Main addr                                                       | (D2:0 = 000 in Main address 2 for ess 3 for Rx2)                                                                                                                                                                                                                |     | -41  |     |                  |  |

| In David Invest D 44D                           | Maximum RF gain for Rx1, in Main a                                                         | - 8dB (D2:0 = 001 in Main address 2 ddress 3 for Rx2)                                                                                                                                                                                                           |     | -32  |     | ,<br>,<br>,      |  |

| In-Band Input P-1dB                             | Maximum RF gain for Rx1, in Main a                                                         | - 16dB (D2:0 = 010 in Main address 2 ddress 3 for Rx2)                                                                                                                                                                                                          |     | -24  |     | dBm              |  |

|                                                 | Maximum RF gain for Rx1, in Main a                                                         | - 32dB (D2:0 = 110 in Main address 2 ddress 3 for Rx2)                                                                                                                                                                                                          |     | -8   |     |                  |  |

| Output P-1dB Compression                        | Over passband from                                                                         | equency range, at minimum VGA gain                                                                                                                                                                                                                              |     | 1.5  |     | V <sub>P-P</sub> |  |

| I/Q Gain Imbalance                              | 1MHz I/Q baseba                                                                            | 1MHz I/Q baseband output, 1σ variation                                                                                                                                                                                                                          |     | 0.05 |     | dB               |  |

| I/Q Phase Error                                 | 1MHz I/Q baseba                                                                            | nd output, 1σ variation                                                                                                                                                                                                                                         |     | 0.5  |     | Degrees          |  |

| Loopback Gain (for Receiver I/Q<br>Calibration) | gain at maximum 25), receiver base 10101 in Main add                                       | Transmitter I/Q input to receiver I/Q output; transmitter gain at maximum - 6dB (D5:0 = 000110 in Main address 25), receiver baseband gain = maximum - 10dB (D7:3 = 10101 in Main address 2 for Rx1, in Main address 3 for Rx2) programmed through SPI (Note 2) |     | 9    | 17  | dB               |  |

| I/Q DC Error After Receive<br>Enable            | Using one-shot me                                                                          | ode, 7µs after receive enable                                                                                                                                                                                                                                   |     | ±15  |     | mV               |  |

| I/Q Output DC Droop                             |                                                                                            | er 10μs, 5μs to 10ms after any gain<br>enable DC convergence, 1σ variation                                                                                                                                                                                      |     | ±100 |     | μV/ms            |  |

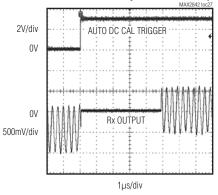

| Isolation Between Rx Channel A and Rx Channel B |                                                                                            |                                                                                                                                                                                                                                                                 |     | 25   |     | dB               |  |

| RECEIVER BASEBAND FILTERS                       | S                                                                                          |                                                                                                                                                                                                                                                                 |     |      |     |                  |  |

| RF Channel BW Supported by BB Filter            | Main address 0, s                                                                          | erial bits D2:D1 = 00                                                                                                                                                                                                                                           | 3.5 |      |     |                  |  |

|                                                 | Main address 0, s                                                                          | Main address 0, serial bits D2:D1 = 01                                                                                                                                                                                                                          |     | 5    |     | MHz              |  |

|                                                 | Main address 0, s                                                                          | erial bits D2:D1 = 10                                                                                                                                                                                                                                           |     | 7    |     | IVIHZ            |  |

|                                                 | Main address 0, serial bits D2:D1 =                                                        |                                                                                                                                                                                                                                                                 |     | 10   |     |                  |  |

| Baseband Gain Ripple                            | 0 to 4.6MHz for BW = 10MHz                                                                 |                                                                                                                                                                                                                                                                 |     | 1.7  |     | dBp-p            |  |

| Baseband Group Delay Ripple                     | 0 to 4.6MHz for B                                                                          | W = 10MHz                                                                                                                                                                                                                                                       |     | 42   |     | nsp-p            |  |

N/IXI/W

### AC ELECTRICAL CHARACTERISTICS TABLE—Rx Mode (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, baseband output signal frequency = 1MHz, receiver baseband I/Q output at 90mV<sub>RMS</sub>, REF\_OSC frequency = 44.8MHz, ENABLE = TXRX =  $\overline{CS}$  = high, SCLK = DIN = low. Lowpass filter is set to 10MHz RF channel BW, with power matching for the differential RF pins using the *Typical Operating Circuit*. RXBB\_ pins are loaded with differential 10k $\Omega$  resistor and 10pF capacitance in parallel. Registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications that normally apply over the entire operating conditions, unless otherwise indicated.) (Note 1)

| PARAMETER                   | CONDITIO                      | DNS               | MIN T | YP MAX | UNITS |  |

|-----------------------------|-------------------------------|-------------------|-------|--------|-------|--|

|                             |                               | 1.6MHz            | 0.5   |        |       |  |

|                             | 3.5MHz channel bandwidth      | 2.3MHz            | Ę     | 5.5    |       |  |

|                             |                               | 14.25MHz          |       | 60     |       |  |

|                             |                               | 2.3MHz            | (     | ).5    |       |  |

|                             | 5MHz channel bandwidth        | 3.3MHz            | Ę     | 5.5    |       |  |

| Baseband Filter Stop Band   |                               | 21MHz             | (     | 60     | -10   |  |

| Rejection                   | 7MHz channel bandwidth        | 3.2MHz            | (     | ).5    | dB    |  |

|                             |                               | 4.7MHz            | Ę     | 5.5    |       |  |

|                             |                               | 29MHz             | (     | 60     |       |  |

|                             | 10MHz channel bandwidth       | 4.6MHz            | (     | ).5    |       |  |

|                             |                               | 6.7MHz            | Ę     | 5.5    |       |  |

|                             |                               | 41.6MHz           |       | 60     |       |  |

| RSSI                        |                               |                   | •     |        |       |  |

| RSSI Minimum Output Voltage | $R_{LOAD} = 10k\Omega$        |                   | (     | ).5    | V     |  |

| RSSI Maximum Output Voltage | $R_{LOAD} = 10k\Omega$        |                   | 2     | 2.2    | V     |  |

| RSSI Slope                  |                               |                   | ;     | 30     | mV/dB |  |

| DCCI Output Cottling Time   | To within 2dD of stoody state | +32dB signal step | 4     | 100    |       |  |

| RSSI Output Settling Time   | To within 3dB of steady state | -32dB signal step | 1     | 100    | ns    |  |

#### AC ELECTRICAL CHARACTERISTICS TABLE—Tx Mode

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, REF\_OSC frequency = 44.8MHz, ENABLE =  $\overline{CS}$  = high, TXRX = SCLK = DIN = low. Power matching at RF outputs using the *Typical Operating Circuit*. Lowpass filter is set to 10MHz RF channel BW; 90mV<sub>RMS</sub>, 1MHz sine and cosine signal applied to I and Q baseband inputs of transmitter (differential DC-coupled). Registers set to default settings and corresponding test mode, unless otherwise noted.) (Note 1)

| PARAMETER                                              | CONDITIONS                                                                                                                 | MIN | TYP | MAX | UNITS |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|--|--|

| TRANSMIT SECTION: Tx BASEBAND I/Q INPUTS TO RF OUTPUTS |                                                                                                                            |     |     |     |       |  |  |  |

| RF Output Frequency Range                              |                                                                                                                            | 3.3 |     | 3.9 | GHz   |  |  |  |

| Peak-to-Peak Gain Variation Over RF Band               | Single matching for entire band, at one temperature                                                                        |     | 2.2 |     | dB    |  |  |  |

| Total Voltage Gain                                     | At unbalanced $50\Omega$ matched output                                                                                    |     | 5   |     | dB    |  |  |  |

| Maximum Output Power                                   | OFDMA signal, gain adjusted over maximum gain and maximum gain - 6dB; single matching for entire band; 64-QAM, EVM = -36dB |     | 0   |     | dBm   |  |  |  |

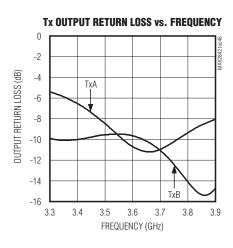

| RF Output Return Loss                                  | All gain settings                                                                                                          |     | 6   |     | dB    |  |  |  |

| Output P-1dB                                           | Maximum gain setting                                                                                                       |     | 10  |     | dBm   |  |  |  |

### AC ELECTRICAL CHARACTERISTICS TABLE—Tx Mode (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz, REF\_OSC frequency = 44.8MHz, ENABLE =  $\overline{CS}$  = high, TXRX = SCLK = DIN = low. Power matching at RF outputs using the *Typical Operating Circuit*. Lowpass filter is set to 10MHz RF channel BW; 90mV<sub>RMS</sub>, 1MHz sine and cosine signal applied to I and Q baseband inputs of transmitter (differential DC-coupled). Registers set to default settings and corresponding test mode, unless otherwise noted.) (Note 1)

| PARAMETER                                                                           | CONDITIONS                                                                                        |                      | MIN     | TYP     | MAX    | UNITS |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------|---------|---------|--------|-------|

| RF Gain Control Range                                                               | From maximum Tx gain (D5:D0 = 00 address 25 for Tx1, in Main address mum Tx gain (B6:B1 = 111111) |                      |         | 60      |        | dB    |

| Unwanted Sideband Suppression                                                       | Without calibration by modem, and excludes modem I/Q imbalance;                                   | Maximum Tx gain      |         | 45      |        | dB    |

| onwanted oldeband ouppression                                                       | sine and cosine signal applied to the I/Q baseband inputs                                         | Minimum Tx gain      |         | 38      |        | αВ    |

|                                                                                     | D0 in Main address 25 for Tx1, in Mai                                                             | n address 24 for Tx2 |         | 1       |        |       |

|                                                                                     | D1 in Main address 25 for Tx1, in Mai                                                             | n address 24 for Tx2 |         | 2       |        |       |

| RF Gain Control Binary Weights                                                      | D2 in Main address 25 for Tx1, in Mai                                                             | n address 24 for Tx2 |         | 4       |        | dB    |

| The Gain Control Binary Weights                                                     | D3 in Main address 25 for Tx1, in Mai                                                             | n address 24 for Tx2 |         | 8       |        | QD.   |

|                                                                                     | D4 in Main address 25 for Tx1, in Mai                                                             | n address 24 for Tx2 |         | 16      |        |       |

|                                                                                     | D5 in Main address 25 for Tx1, in Mai                                                             | n address 24 for Tx2 |         | 32      |        |       |

| Carrier Leakage                                                                     | Relative to -3dBm output power; wit modem sine and cosine signal appl band inputs                 |                      |         | -40     |        | dBc   |

| Ty I/O Input Impodence (PIIC)                                                       | Differential resistance                                                                           |                      |         | 25      |        | kΩ    |

| Tx I/Q Input Impedance (RIIC)                                                       | Differential capacitance                                                                          |                      |         | 1       |        | рF    |

|                                                                                     | 3.5MHz channel bandwidth                                                                          | 2.33MHz              |         | 0.5     |        |       |

|                                                                                     | 3.5IVII IZ CHAFILIEI DAHUWIUUT                                                                    | 6.62MHz              |         | 45      |        |       |

|                                                                                     | 5MHz channel bandwidth                                                                            | 3.33MHz              |         | 0.5     |        |       |

| Baseband Filter Rejection                                                           | Sivil 12 Chariner Dandwidth                                                                       | 9.45MHz              |         | 45      |        | dB    |

| Baseband Filler nejection                                                           | 7MHz channel bandwidth                                                                            | 4.67MHz              |         | 0.5     |        | J GB  |

|                                                                                     |                                                                                                   | 13.23MHz             |         | 45      |        |       |

|                                                                                     | 40141                                                                                             | 6.67MHz              |         | 0.5     |        |       |

|                                                                                     | 10MHz channel bandwidth                                                                           | 18.9MHz              |         | 45      |        |       |

| Baseband Group Delay Ripple                                                         | 0 to 4.6MHz (BW = 10MHz)                                                                          |                      |         | 10      |        | ns    |

| Baseband Input 1dB Gain Compression or Expansion                                    | Sine and cosine signal applied to the inputs, 5MHz I/Q inputs                                     | e I/Q baseband       |         | 0.5     |        | VPEAK |

| Isolation Between Tx Channel A and Tx Channel B                                     |                                                                                                   |                      |         | 45      |        | dB    |

| Maximum Gain Mismatch<br>Between Tx Channel A and Tx<br>Channel B over RF Frequency | 3.3GHz to 3.9GHz, single matching                                                                 | for entire band      |         | ±2      |        | dB    |

| TRANSMITTER LO LEAKAGE AN RECEIVER I-CHANNEL MULTIPL                                | ND I/Q CALIBRATION USING POWE<br>EXED OUTPUT                                                      | R DETECTOR: Tx I/    | Q BASEB | AND INI | PUT TO |       |

| Output AC-Coupling, -3dB<br>Frequency                                               |                                                                                                   |                      |         | 750     |        | kHz   |

| Baseband AC Amplifier Gain Range                                                    | Measure from minimum gain (D5:D4 address 21) to maximum gain (D5:D4 address 21)                   |                      |         | 30      |        | dB    |

### AC ELECTRICAL CHARACTERISTICS TABLE—Tx Mode (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{RF}$  = 3.601GHz,  $f_{LO}$  = 3.6GHz,  $f_{RF}$  OSC frequency = 44.8MHz, ENABLE =  $\overline{CS}$  = high, TXRX = SCLK = DIN = low. Power matching at RF outputs using the *Typical Operating Circuit*. Lowpass filter is set to 10MHz RF channel BW; 90mV<sub>RMS</sub>, 1MHz sine and cosine signal applied to I and Q baseband inputs of transmitter (differential DC-coupled). Registers set to default settings and corresponding test mode, unless otherwise noted.) (Note 1)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                            | MIN | TYP | MAX | UNITS |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Ftone or 2Ftone Level at Output | Maximum - 2dB Tx gain (D5:D0 = 000010 in Main address 25 for Tx1, in Main address 24 for Tx2), -25dBc LO leakage, Ftone = 2MHz, and minimum AM detector gain (D5:D4 = 00 in Main address 21) (Note 3) |     | -17 |     | dBm   |

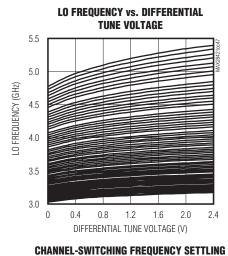

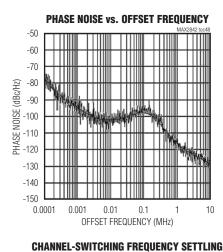

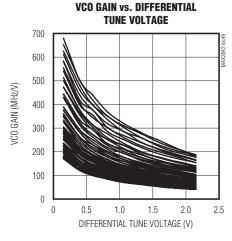

### AC ELECTRICAL CHARACTERISTICS TABLE—Frequency Synthesis

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{LO}$  = 3.6GHz, REF\_OSC frequency = 44.8MHz,  $\overline{CS}$  = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, PLL loop bandwidth = 180kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                              | CONDITIONS                                                                                                                           | MIN | TYP                | MAX | UNITS |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|

| MAIN FREQUENCY SYNTHESIZE                              | ER .                                                                                                                                 |     |                    |     |       |

| RF Channel Center Frequency Range                      |                                                                                                                                      | 3.3 |                    | 3.9 | GHz   |

| Channel Center Frequency Programming Minimum Step Size |                                                                                                                                      |     | 25                 |     | Hz    |

| Charge-Pump Comparison Frequency                       |                                                                                                                                      | 19  | 44.8               |     | MHz   |

| Reference Frequency Range                              |                                                                                                                                      | 19  | 44.8               | 80  | MHz   |

| Reference Frequency Input<br>Levels                    | AC-coupled to REF_OSC pin                                                                                                            | 0.8 |                    |     | VP-P  |

| Reference Frequency Input                              | Resistance (REF_OSC pin)                                                                                                             |     | 10                 |     | kΩ    |

| Impedance (RIIC)                                       | Capacitance (REF_OSC pin)                                                                                                            |     | 1                  |     | рF    |

| Dragrammable Deference Divide                          | D1:D0 = 00 in Local address 15                                                                                                       |     | 1                  |     |       |

| Programmable Reference Divider Values                  | D1:D0 = 01 in Local address 15                                                                                                       |     | 2                  |     |       |

| values                                                 | D1:D0 = 10 in Local address 15                                                                                                       |     | 4                  |     |       |

| Closed-Loop Integrated Phase Noise                     | Integrated phase noise from 200Hz to 5MHz                                                                                            |     | -38                |     | dBc   |

| Charge-Pump Output Current                             | On each differential side                                                                                                            |     | 0.8                |     | mA    |

| Spur Level                                             | foffset = 0 to 1.8MHz                                                                                                                |     | -40                |     | dBc   |

| Spui Levei                                             | foffset = 44.8MHz                                                                                                                    |     | -77                |     | ивс   |

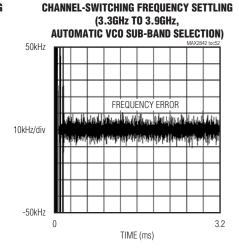

| Turnaround LO Frequency Error                          | Relative to steady state; measured 35µs after Tx-Rx or Rx-Tx switching instant, and 4µs after any receiver gain changes              |     | ±50                |     | Hz    |

| Temperature Range over Which VCO Maintains Lock        | Relative to the ambient temperature T <sub>A</sub> , as long as the VCO lock temperature range is within operating temperature range |     | T <sub>A</sub> ±40 |     | °C    |

| CLKOUT Divider Values                                  | TXRX = 0 at the CLKOUTEN rising edge                                                                                                 |     | 1                  |     |       |

| CLICOT DIVIDE Values                                   | TXRX = 1 at the CLKOUTEN rising edge                                                                                                 |     | 2                  |     |       |

### AC ELECTRICAL CHARACTERISTICS TABLE—Frequency Synthesis (continued)

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{LO}$  = 3.6GHz, REF\_OSC frequency = 44.8MHz,  $\overline{CS}$  = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, PLL loop bandwidth = 180kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER           |             | CONDITIONS                                             | MIN  | TYP  | MAX | UNITS  |

|---------------------|-------------|--------------------------------------------------------|------|------|-----|--------|

| CLKOUT Output Swing | R= 10kΩ,    | D7:6 = 00 in Local address 9 with 44.8MHz clock output | 2.56 |      |     | \/p. p |

|                     | CLOAD = 5pF | D7:6 = 11 in Local address 9 with 22.4MHz clock output |      | 2.66 |     | VP-P   |

#### AC ELECTRICAL CHARACTERISTICS TABLE—Miscellaneous Blocks

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V, REF\_OSC frequency = 44.8MHz,  $\overline{CS}$  = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER              | CO                               | NDITIONS                          | MIN | TYP                   | MAX  | UNITS |

|------------------------|----------------------------------|-----------------------------------|-----|-----------------------|------|-------|

| PA BIAS VOLTAGE        |                                  |                                   |     |                       |      |       |

| Output High Level      | 10mA source current              |                                   |     | V <sub>CC</sub> - 0.2 |      | V     |

| Output Low Level       | 10mA sink current                |                                   |     | 0.2                   |      | V     |

| Turn-On Time           | Excludes programmable 0.45µs     | delay of 0 to 6.3µs in steps of   |     | 200                   |      | ns    |

| VCTCXO DAC             |                                  |                                   |     |                       |      |       |

| Outrast Oursell        | 0                                | D5:D0 = 000000 in Main address 29 | 0   |                       |      |       |

| Output Current         | Source current                   | D5:D0 = 111111 in Main address 29 |     | 315                   | - μΑ |       |

| Maximum Output Voltage |                                  |                                   |     | 2.4                   |      | V     |

| Step Size              |                                  |                                   |     | 5                     |      | μΑ    |

| ON-CHIP TEMPERATURE SE | ENSOR                            |                                   |     |                       |      |       |

|                        | Decelorate DOUT win              | T <sub>A</sub> = +25°C            |     | 10001                 |      |       |

| Digital Output Code    | Read-out at DOUT pin through SPI | T <sub>A</sub> = +85°C            |     | 11010                 |      |       |

|                        | ti i ougii oi i                  | TA = $-40^{\circ}$ C              |     |                       |      |       |

| Temperature Step Size  |                                  |                                   |     | 5                     |      | °C    |

## AC ELECTRICAL CHARACTERISTICS TABLE—Timing

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{LO}$  = 3.6GHz, REF\_OSC frequency = 44.8MHz,  $\overline{CS}$  = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, PLL loop bandwidth = 180kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER              | SYMBOL | CONDIT                  | TONS                             | MIN | TYP | MAX | UNITS |

|------------------------|--------|-------------------------|----------------------------------|-----|-----|-----|-------|

| SYSTEM TIMING          |        |                         |                                  |     |     |     |       |

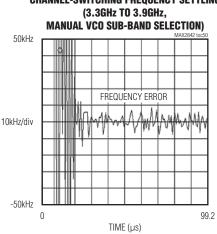

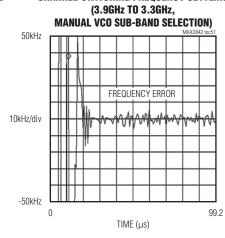

| Channel Switching Time |        | Frequency error settles | Automatic VCO sub-band selection |     | 2   |     | ms    |

|                        |        | to ±50Hz                | Manual VCO sub-band selection    |     | 56  |     | μs    |

### **AC ELECTRICAL CHARACTERISTICS TABLE—Timing (continued)**

(MAX2842 Evaluation Kit,  $V_{CC}$  = 2.7V to 3.6V,  $T_A$  = +25°C,  $f_{LO}$  = 3.6GHz, REF\_OSC frequency = 44.8MHz,  $\overline{CS}$  = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, PLL loop bandwidth = 180kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                              | SYMBOL         | CONDIT                                                               | TONS     | MIN TYP MAX L |     |    | UNITS |  |

|----------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------|----------|---------------|-----|----|-------|--|

| Turnaround Time                                                                        |                | Measured from TXRX rising or falling edge; signal settling to within | Rx to Tx | :             | 2   |    | μs    |  |

|                                                                                        |                | 0.5dB of steady state                                                | Tx to Rx | 2             |     |    |       |  |

| Tx Turn-On Time (From Standby Mode)                                                    |                | Measured from ENABLE settling to within 0.5dB                        | 0 0      | 2             |     |    | μs    |  |

| Tx Turn-Off Time (To Standby Mode)                                                     |                | From ENABLE falling ec                                               | lge      | 1             |     |    | μs    |  |

| Rx Turn-On Time (From Standby Mode)                                                    |                | Measured from ENABLE settling to within 0.5dB                        |          | 2             |     |    | μs    |  |

| Rx Turn-Off Time (To Standby Mode)                                                     |                | From ENABLE falling ec                                               | lge      |               | 1   |    | μs    |  |

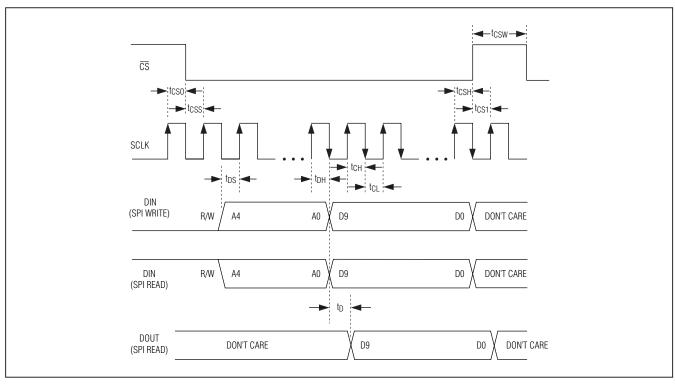

| 4-WIRE SERIAL PARALLEL INT                                                             | ERFACE T       | MING (See Figure 1)                                                  |          |               |     |    |       |  |

| SCLK Rising Edge to CS Falling Edge Wait Time                                          | tcso           |                                                                      |          | (             | 6   |    | ns    |  |

| Falling Edge of CS to Rising Edge of First SCLK Time                                   | tcss           |                                                                      |          | (             | 6   |    | ns    |  |

| DIN to SCLK Setup Time                                                                 | tDS            |                                                                      |          | (             | 6   |    | ns    |  |

| DIN to SCLK Hold Time                                                                  | tDH            |                                                                      |          | (             | 6   |    | ns    |  |

| SCLK Pulse-Width High                                                                  | tch            |                                                                      |          | (             | 6   |    | ns    |  |

| SCLK Pulse-Width Low                                                                   | tCL            |                                                                      |          | (             | 6   |    | ns    |  |

| Last Rising Edge of SCLK to<br>Rising Edge of CS or Clock to<br>Load Enable Setup Time | tcsh           |                                                                      |          | (             | 6   |    | ns    |  |

| CS High Pulse Width                                                                    | tcsw           |                                                                      |          | 4             | 15  |    | ns    |  |

| Time Between Rising Edge of CS and the Next Rising Edge of SCLK                        | tCS1           |                                                                      |          | (             | 6   |    | ns    |  |

| Clock Frequency                                                                        | fCLK           |                                                                      |          |               | 4.  | 5  | MHz   |  |

| Rise Time                                                                              | t <sub>R</sub> |                                                                      | fCLK/10  |               |     | ns |       |  |

| Fall Time                                                                              | tϝ             | fCLK/10                                                              |          |               |     |    | ns    |  |

| SCLK Falling Edge to Valid DOUT                                                        | tD             |                                                                      |          | 12            | 2.5 |    | ns    |  |

- Note 1: MAX2842 ICs are production tested at T<sub>A</sub> = +25°C. Min/max limits at T<sub>A</sub> = -40°C and T<sub>A</sub> = +85°C are guaranteed by design and characterization. There is **no** power-on register settings self-reset. Recommended register settings must be loaded after V<sub>CC</sub> is applied.

- **Note 2:** Loopback gain is production tested at V<sub>CC</sub> = 2.7V. Min/max limits over the supply voltage range are guaranteed by design and characterization.

- Note 3: The LO leakage produces Ftone, while the I/Q imbalance produces 2Ftone at the baseband output of the power detector. The output Ftone increases by 1dB for 1dB increase of the LO leakage, provided that the output power remains constant. The same relationship applies for the sideband leakage (due to I/Q imbalance) and 2Ftone.

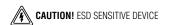

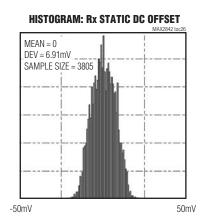

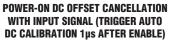

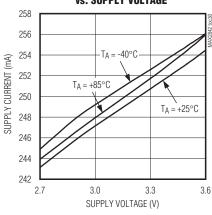

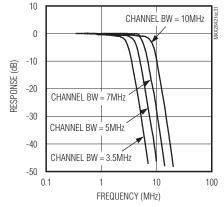

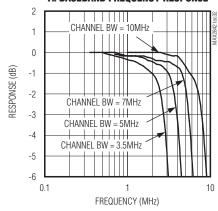

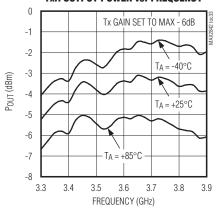

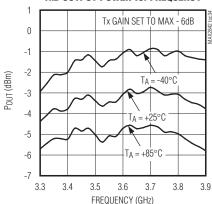

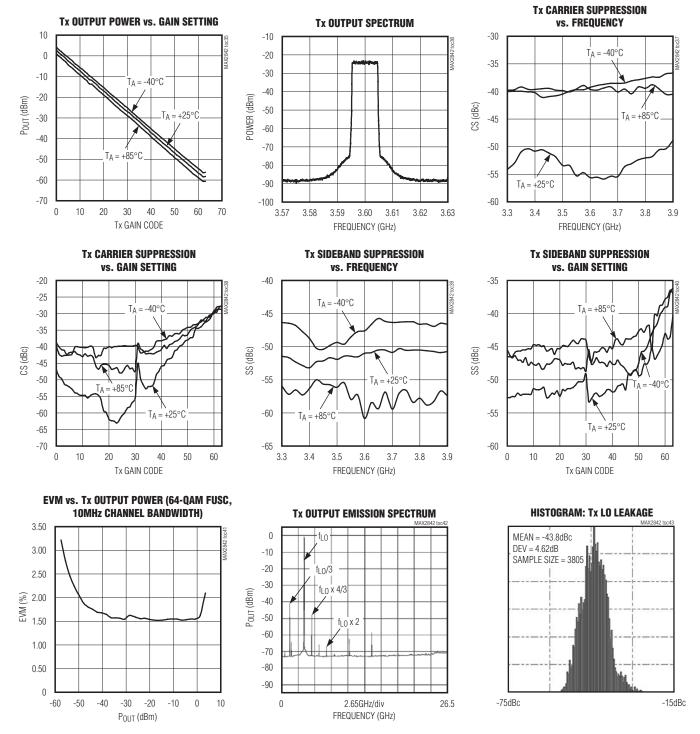

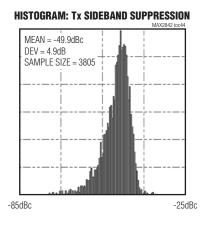

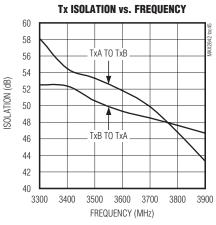

### Typical Operating Characteristics

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at 50<math>\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

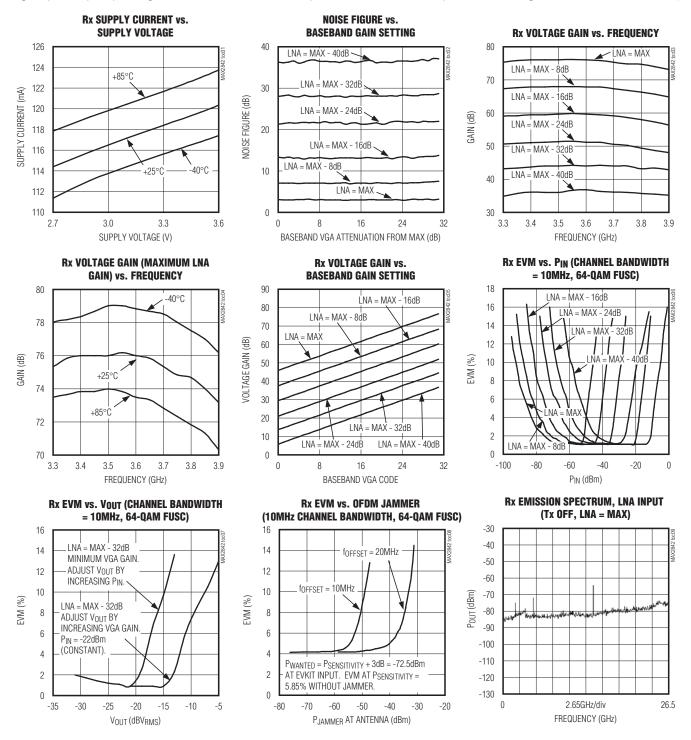

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF\_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at <math>50\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at 50<math>\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

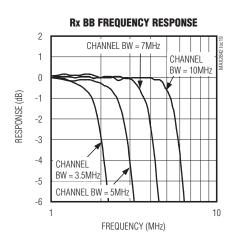

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF\_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at <math>50\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

#### POWER-ON DC OFFSET CANCELLATION WITHOUT INPUT SIGNAL (TRIGGER AUTO DC CALIBRATION 1µS AFTER ENABLE)

Rx ISOLATION vs. FREQUENCY

Tx SUPPLY CURRENT vs. SUPPLY VOLTAGE

Tx BASEBAND FREQUENCY RESPONSE

Tx BASEBAND FREQUENCY RESPONSE

TXA OUTPUT POWER vs. FREQUENCY

TxB OUTPUT POWER vs. FREQUENCY

### Typical Operating Characteristics (continued)

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at 50<math>\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

### Typical Operating Characteristics (continued)

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF\_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at <math>50\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

### Typical Operating Characteristics (continued)

$(V_{CC} = 2.8V, T_A = +25^{\circ}C, f_{LO} = 3.6GHz, f_{REF} = REF\_OSC frequency = 44.8MHz, \overline{CS} = high, SCLK = DIN = low, ENABLE and TXRX logic inputs as per operating mode, RF BW = 10MHz, Tx output at <math>50\Omega$  unbalanced output of balun, using the MAX2842 Evaluation Kit.)

**Pin Configuration**

## Pin Description

| PIN | NAME       | FUNCTION                                                                                                                                                                               |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCCRXLNA_B | Receiver B LNA Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                                |

| 2   | GNDRXLNA_B | Receiver B LNA Ground                                                                                                                                                                  |

| 3   | RXINB-     | Receiver B LNA Differential Input. Inputs are internally DC-coupled. Two external series capacitors                                                                                    |

| 4   | RXINB+     | and one shunt inductor match the inputs to $100\Omega$ differential.                                                                                                                   |

| 5   | ENABLE     | Mode Control Logic Input. See Table 1 for operating modes.                                                                                                                             |

| 6   | VCCTXPAD_A | Transmitter A Supply Voltage for Transmitter Power-Amplifier Driver. Bypass with a capacitor as close as possible to the pin.                                                          |

| 7   | TXOUTA-    | Transmitter A Power-Amplifier Driver Differential Output. The pins are internally DC-coupled. Two                                                                                      |

| 8   | TXOUTA+    | external series capacitors and one shunt inductor match the outputs to $100\Omega$ differential.                                                                                       |

| 9   | VCCTXMX_A  | Transmitter A Upconverter Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                     |

| 10  | PABIAS_A   | Transmit A External PA Bias Voltage Output                                                                                                                                             |

| 11  | CS         | Chip-Select Logic Input of 4-Wire Serial Interface (See Figure 1)                                                                                                                      |

| 12  | VCCTXMX_B  | Transmitter B Upconverter Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                     |

| 13  | PABIAS_B   | Transmit B External PA Bias Voltage Output                                                                                                                                             |

| 14  | VCCTXPAD_B | Transmitter B Supply Voltage for Transmitter Power-Amplifier Driver. Bypass with a capacitor as close as possible to the pin.                                                          |

| 15  | TXOUTB-    | Transmitter B Power-Amplifier Driver Differential Output. The pins are internally DC-coupled. Two                                                                                      |

| 16  | TXOUTB+    | external series capacitors and one shunt inductor match the outputs to 100 $\Omega$ differential.                                                                                      |

| 17  | DOUT       | Data Logic Output of 4-Wire Serial Interface (See Figure 1)                                                                                                                            |

| 18  | SCLK       | Serial-Clock Logic Input of 4-Wire Serial Interface (See Figure 1)                                                                                                                     |

| 19  | DIN        | Data Logic Input of 4-Wire Serial Interface (See Figure 1)                                                                                                                             |

| 20  | REF_DIG    | CMOS Logic Supply-Voltage Reference Input. Bypass with a capacitor as close as possible to the pin. It is tested at 2.7V and 3.6V. For 1.8V voltage support, contact the manufacturer. |

| 21  | CLKOUT     | Divided Reference Clock Output                                                                                                                                                         |

| 22  | Vcc_dig    | Digital Blocks Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                                |

| 23  | XTAL1      | Crystal Connection. (If the on-chip crystal oscillator is not used, leave this input unconnected.)                                                                                     |

| 24  | REF_OSC    | 44.8MHz Reference Clock Input or Crystal Connection. AC-couple a crystal or a reference clock to this analog input.                                                                    |

| 25  | XTAL_DAC   | Source Current DAC Output for VCTCXO                                                                                                                                                   |

| 26  | VCC_CP     | PLL Charge-Pump Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                               |

| 27  | CPOUT+     | Differential Charge-Pump Output. Connect the frequency synthesizer's loop filter between CPOUT+                                                                                        |

| 28  | CPOUT-     | and CPOUT- (see the Typical Operating Circuit).                                                                                                                                        |

| 29  | GNDVCO     | VCO Ground                                                                                                                                                                             |

| 30  | BYP_VCO    | On-Chip VCO Regulator Output Bypass. Bypass with a 1µF capacitor to GND. Do not connect other circuitry to this point.                                                                 |

| 31  | Vcc_vco    | VCO Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                                           |

| 32  | CLKOUTEN   | Logic Input to Enable CLKOUT                                                                                                                                                           |

| 33  | RSSI       | RSSI or Temperature Sensor Multiplexed Analog Output                                                                                                                                   |

| 34  | TXBBIB-    |                                                                                                                                                                                        |

| 35  | TXBBIB+    | Transmitter B Baseband I-Channel Differential Inputs                                                                                                                                   |

| 36  | TXBBQB+    | T                                                                                                                                                                                      |

| 37  | TXBBQB-    | Transmitter B Baseband Q-Channel Differential Inputs                                                                                                                                   |

# Pin Description (continued)

|     |            | FUNCTION                                                                                                                                                                                                               |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME       | FUNCTION                                                                                                                                                                                                               |

| 38  | VCC_BB     | Receiver Baseband Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                                                             |

| 39  | RXBBIB-    | Receiver B Baseband I-Channel Differential Outputs. In Tx calibration mode, these pins are the LO                                                                                                                      |

| 40  | RXBBIB+    | leakage and sideband detector outputs.                                                                                                                                                                                 |

| 41  | RXBBQB-    | Receiver B Baseband Q-Channel Differential Outputs. In Tx calibration mode, these pins are the LO                                                                                                                      |

| 42  | RXBBQB+    | leakage and sideband detector outputs.                                                                                                                                                                                 |

| 43  | RXBBQA-    | Receiver A Baseband Q-Channel Differential Outputs. In Tx calibration mode, these pins are the LO                                                                                                                      |

| 44  | RXBBQA+    | leakage and sideband detector outputs.                                                                                                                                                                                 |

| 45  | RXBBIA-    | Receiver A Baseband I-Channel Differential Outputs. In Tx calibration mode, these pins are the LO                                                                                                                      |

| 46  | RXBBIA+    | leakage and sideband detector outputs.                                                                                                                                                                                 |

| 47  | TXBBIA-    | Transmitter A December of I Channel Differential Inquite                                                                                                                                                               |