**Benefits and Features**

### **MAX2551**

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **General Description**

### ♦ Single-Chip Femtocell Radio Transceiver ♦ WCDMA/HSPA+ Band II and V Operation

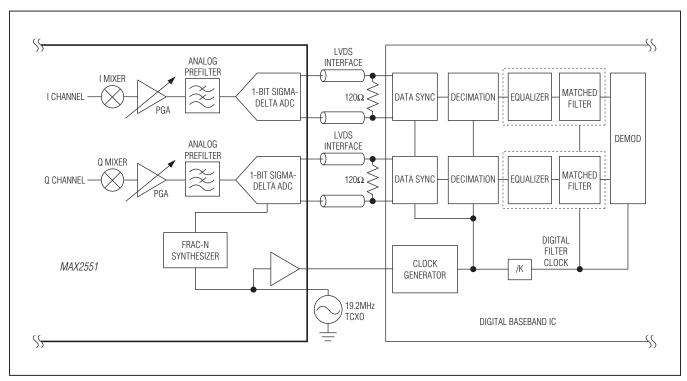

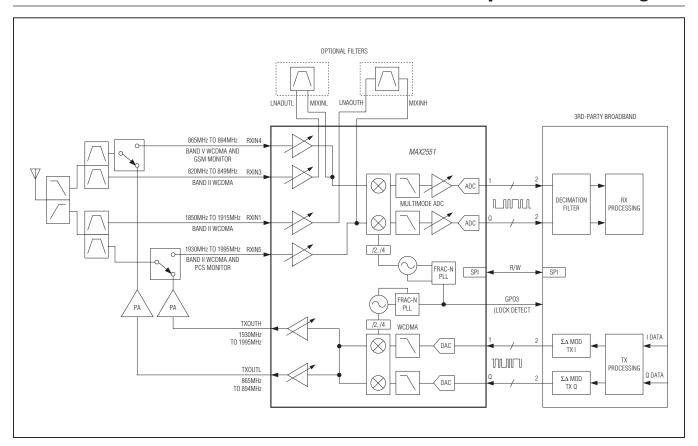

The MAX2551 is a complete single-chip RF-to-bits and bits-to-RF radio transceiver. This device is in compliance with the 3GPP TS25.104 femtocell standard for Band II and V. It's equipped with multiple receive inputs and transmit outputs for low band, high band, and macro-cell monitoring (Table 1).

This fully integrated transceiver facilitates compact radio designs for dongle and standalone femtocell products by minimizing external component count. Maxim's MAX-PHY serial interface is used to drastically reduce IC pin count. while worldwide field-proven architecture accelerates time to product deployment.

The device features unparalleled receive blocker performance and the industry's lowest noise figure for higher data rates and range. Low-power operational modes are available to minimize power consumption. The transmitter is designed to deliver EVM far exceeding the standard requirement at 0dBm.

The MAX2550-MAX2553 is a family of pin-compatible transceivers to cover all major WCDMA and cdma2000® bands. All parts are controlled by a 4-wire interface.

The MAX2551 is packaged in a compact 7mm x 7mm TQFN and specified over the -40°C to +85°C extended temperature range. A complete radio reference design is available to facilitate custom designs.

#### **Applications**

WCDMA Band II and V Femtocells

Simplified Block Diagram appears at end of data sheet.

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maxim-ic.com/MAX2551.related.

- **♦ TS25.104 Standard Compliant**

- ♦ Multiple LNA Inputs for WCDMA, PCS, and GSM **Macrocell Monitoring**

- ♦ High Level of Integration

- ♦ On-Chip Fractional-N Frequency Synthesizers for LO Generation

- ♦ No Tx SAW Filters Required

- ♦ Integrated PA Drivers for Lower-Cost Power **Amplifier Designs**

- ♦ 12-Bit AFC DAC to Control TCXO

- ♦ On-Chip Temperature Sensor

- ♦ Three General-Purpose Outputs

- ♦ Reference Clock with Selectable CMOS and Low **Swing Output**

- ♦ PLL Lock-Detect Output Through GPO3

- **♦ Optimized Receiver Performance**

- ♦ High Dynamic Range Sigma-Delta ADCs Allow Simple AGC Implementation with Switched Gain States

- **♦ Optimized Transmitter Performance**

- ♦ Factory Calibrated for Gain, Carrier Leakage, and Sideband Suppression

- ♦ 10-Bit Gain Control Resolution for Better Power Accuracy

- ♦ 60dB Gain Control Range

- ♦ Loopback Operating Mode from Tx Baseband Input to Rx Baseband Output

- **♦ MAX-PHY Serial Digital Interface**

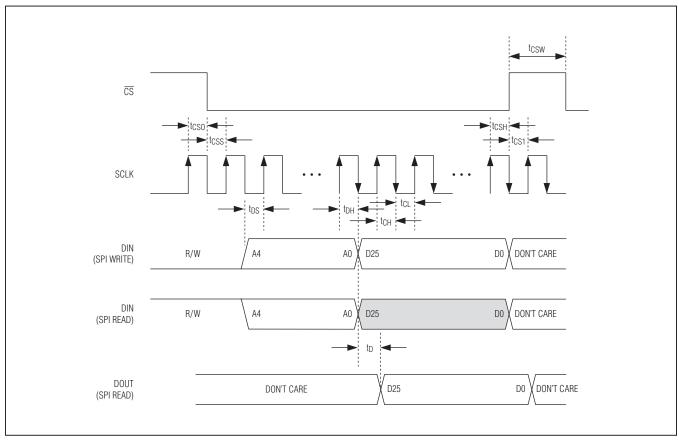

- ♦ SPI Read/Write Functionality

- ♦ Operation Controlled by 4-Wire Serial Interface

- ♦ Low-Cost 7mm x 7mm TQFN Package

cdma2000 is a registered service mark of Telecommunications Industry Association.

## Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **ABSOLUTE MAXIMUM RATINGS**

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | Operating Temperature Range -40°C to +85°C Storage Temperature Range -65°C to +150°C Lead Temperature (soldering, 10s) +300°C Soldering Temperature (reflow) +260°C |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (derate 40mW/°C above +70°C)3.2\                     |                                                                                                                                                                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

**TOFN**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )........25°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )..............1°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC_-} = 3.0 \text{V to } 3.6 \text{V}, T_A = -40 \text{ to } +85 ^{\circ}\text{C}, 50 \Omega \text{ system, } f_{REFIN} = 19.2 \text{MHz}, \text{ typical values are at } V_{CC_-} = 3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Register settings as defined in tables following the specification tables.) (Note 2)

| SPEC NO. | PARAMETER                                         | SYMBOL            | CONDITIONS                                                  | MIN | TYP | MAX  | UNITS |

|----------|---------------------------------------------------|-------------------|-------------------------------------------------------------|-----|-----|------|-------|

| DC1a     | Supply Voltage                                    | V <sub>CC</sub> _ |                                                             | 3.0 | 3.3 | 3.6  | V     |

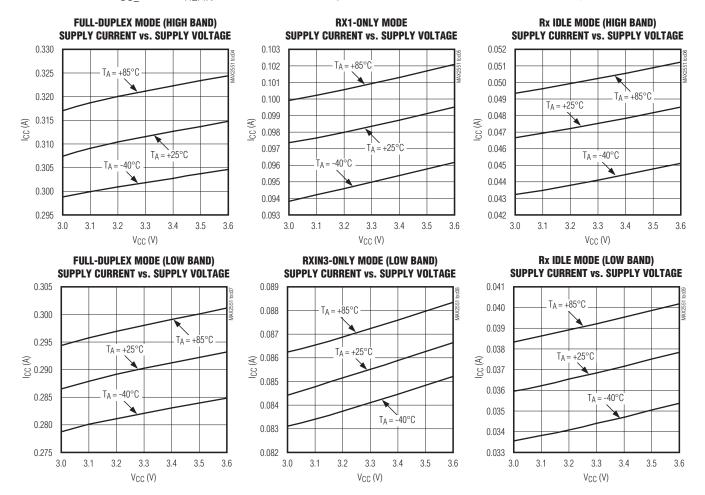

| DC19     |                                                   |                   | Full-duplex high band                                       |     | 312 | 410  |       |

| DC20     |                                                   |                   | Full-duplex low band                                        |     | 290 | 400  |       |

| DC21     |                                                   |                   | RXIN4 monitor                                               |     | 75  | 100  |       |

| DC22     | Operating Supply Current                          | laa               | RXIN5 monitor                                               |     | 88  | 120  | mA    |

| DC23     | WCDMA                                             | ICC_              | Tx only high band                                           |     | 227 | 315  | IIIA  |

| DC24     |                                                   |                   | Tx only low band                                            |     | 218 | 315  |       |

| DC25     |                                                   |                   | Idle Rx                                                     |     | 48  |      |       |

| DC26     |                                                   |                   | Idle Tx                                                     |     | 48  |      |       |

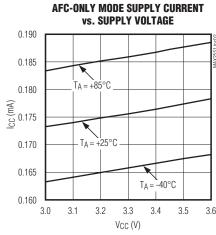

| DC3      | Operating Supply Current<br>AFC-Only Mode         | I <sub>CC</sub> _ | AFC DAC and SPI only                                        |     | 175 | 1000 | μΑ    |

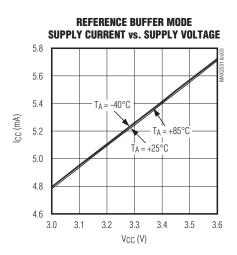

| DC5      | Operating Supply Current<br>Reference Buffer Mode | I <sub>CC</sub> _ | REFOUT = $500\Omega$ II 22pF, all else = off                |     | 5.3 | 7.5  | mA    |

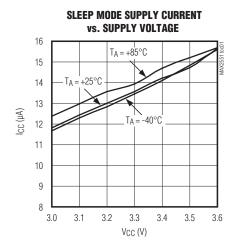

| DC6      | Operating Supply Current<br>Sleep Mode            | I <sub>CC</sub> _ | All functions off                                           |     | 14  | 1000 | μА    |

| DC11     | Digital Input Logic-High                          |                   |                                                             | 1.3 |     |      | V     |

| DC12     | Digital Input Logic-Low                           |                   |                                                             |     |     | 0.4  | V     |

| DC13     | Input Current for Digital<br>Control Pins         |                   |                                                             |     |     | 10   | lμAl  |

| DC16     | GPO Sink Current                                  |                   | $V_{OUT} = 0.35V$ , DOUT_DRV = 01                           | 1.0 | 1.8 |      | mA    |

| DC17     | GPO Source Current                                |                   | V <sub>OUT</sub> = V <sub>CC</sub> - 0.3V,<br>DOUT_DRV = 01 | 1.0 | 1.9 |      | mA    |

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### **Band II Duplexer Specifications**

(Diplexer between antenna and duplexer loss: 0.3dB (applies to all Rx modes).)

#### Antenna—Uplink Port (Applies to Uplink WCDMA Rx Mode on RXIN1)

| BAND (MHz)        | Uplink<br>1850 to 1910 | 1 to 1800      | 1930 to<br>1995 | 1980 to<br>2020 | 2020 to<br>2200 | 2300 to<br>2500 | 2500 to<br>4500 | 4500 to<br>12750 |

|-------------------|------------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| ATTENUATION       | Attenuation            |                |                 | Min             | imum Attenu     | ation           |                 |                  |

| (dB)              | 2                      | 35             | 30              | 35              | 37              | 27              | 25              | 15               |

| Rx SAW FILTER RES | SPONSE                 |                |                 |                 |                 |                 |                 |                  |

| BAND (MHz)        | Out of Band            |                |                 |                 |                 |                 |                 |                  |

| ATTENUATION       | Required minim         | um attenuation | on relative to  | in-band         |                 |                 |                 |                  |

| (dB)              | 25                     |                |                 |                 |                 |                 |                 |                  |

#### Band II Uplink WCDMA Rx Mode on RXIN1 (Full Duplex)

| SPEC NO. | PARAMETER                                     | CONDITIONS                                                                                                                                                                                                                                                                                                                                             | MIN    | TYP  | MAX    | UNITS |

|----------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|-------|

| Wb2fu-0  | Frequency Band                                | WCDMA FDD Band II uplink (lowest to highest channel center frequency)                                                                                                                                                                                                                                                                                  | 1852.4 |      | 1912.6 | MHz   |

| Wb2fu-1  | Sensitivity<br>3GPP TS25.104<br>Section 7.2.1 | Tx on at -27dBm, LNA gain mid gain, PGA gain register set to 9, assumed SNDR > -17.5dB at sensitivity, using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT, LNA linearity set to 0dBm (Note 3) |        | -118 | -107   | dBm   |

| Wb2fu-1a | Sensitivity with LNA in<br>High-Gain Mode     | Tx on at -27dBm, LNA gain high, PGA gain register set to 6, assumed SNDR > -17.5dB at sensitivity, using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT, LNA linearity set to high              |        | -121 | -107   | dBm   |

| Wb2fu-3  | High-Level EVM WCDMA                          | P <sub>IN</sub> = -20dBm, LNA gain low, PGA gain register set to 1                                                                                                                                                                                                                                                                                     |        | 4.5  |        | %     |

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### Band II Uplink WCDMA Rx Mode on RXIN1 (Full Duplex) (continued)

| SPEC NO. | PARAMETER                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MIN | TYP  | MAX  | UNITS |

|----------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Wb2fu-4  | Sensitivity with Adjacent<br>Channel Interference<br>3GPP TS25.104<br>Section 7.4.1 | Tx on at -27dBm; LNA gain high; PGA gain register set to 3; assumed SNDR > -17.5dB at sensitivity; interfering signals at front-end input -28dBm, at 5MHz offset and -5MHz offset and modulated as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; SNDR at MAX-PHY filter output established with FFT (Note 3)                                                                                                    |     | -107 | -91  | dBm   |

| Wb2fu-5  | Sensitivity with In-Band<br>Blocking Interference<br>3GPP TS25.104 Section 7.5      | Tx on at -27dBm; LNA gain high; PGA gain register set to 6; assumed SNDR > -17.5dB at sensitivity; interfering signal at front-end input -30dBm at 1900MHz to 2000MHz min, 10MHz offset modulated as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; (test only worst case in production); SNDR at MAX-PHY filter output established with FFT (Note 3)                                                            |     | -120 | -101 | dBm   |

| Wb2fu-6  | Sensitivity with Out-of-Band Blocking Interference 3GPP TS25.104 Section 7.5.1      | Front-end assumed response as above, Tx on at -27dBm, LNA high gain, PGA gain register set to 6, assumed SNDR > -17.5dB at sensitivity, interfering signal at front-end input -15dBm CW, 1MHz to 1830MHz and 1930MHz to 2750MHz with 1 MHz steps, no exceptions allowed, (test only worst case in production), using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT (Note 3) |     | -116 | -101 | dBm   |

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### Band II Uplink WCDMA Rx Mode on RXIN1 (Full Duplex) (continued)

| SPEC NO. | PARAMETER                                                                 | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                           | MIN   | TYP  | MAX  | UNITS |

|----------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| Wb2fu-8  | Sensitivity with Intermodulation Interference 3GPP TS25.104 Section 7.6.1 | Tx on at -27dBm; LNA gain high; PGA gain register set to 6; assumed SNDR > -17.5dB at sensitivity; interfering signals at front-end input -38dBm, at 10MHz offset (CW) and 20MHz offset (modulated) as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; SNDR at MAX-PHY filter output established with FFT (Note 3) |       | -118 | -101 | dBm   |

|          |                                                                           | 30MHz to 1GHz, measured in 100kHz BW                                                                                                                                                                                                                                                                                                                                                                                                 |       | -100 | -60  |       |

| Wb2fu-10 | Spurious Emissions Out-of-Band 3GPP TS25.104 Section 7.7.1                | 1GHz to 12.75GHz, measured in 1MHz BW, with the exception of frequencies between 12.5MHz below the first carrier frequency and 12.5MHz above the last carrier frequency used by the BS (Note 3)                                                                                                                                                                                                                                      |       | -100 | -50  | dBm   |

| Wb2fu-11 | Spurious Emissions<br>in Receive Bands<br>3GPP TS25.104<br>Section 7.9.2  | Front-end assumed response as above, 1850MHz to 1910MHz (Note 3)                                                                                                                                                                                                                                                                                                                                                                     |       | -95  | -80  | dBm   |

| Wb2fu-12 | Conversion Gain<br>High LNA Gain                                          | LNA high gain; PGA gain register set to 6; tested on CW input signal at -90dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                                                        | 23    | 32   | 39   | dB    |

| Wb2fu-13 | Conversion Gain<br>Mid LNA Gain                                           | LNA mid gain; PGA gain register set to 9; tested on CW input signal at -90dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                                                         | 22    | 30.5 | 37   | dB    |

| Wb2fu-14 | Conversion Gain<br>Low LNA Gain                                           | LNA gain low; PGA gain register set to 1; tested on CW input signal at -20dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                                                         | -13.5 | -6.5 | -3   | dB    |

## Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

### Antenna—Downlink Port (Applies to Downlink WCDMA Rx Mode on RXIN5)

| BAND (MHz)   | Downlink<br>1930 to 1990 | 1 to 1910                | 1850 to 1910 | 2050 to 3000 | 2255 to 12750 |  |  |

|--------------|--------------------------|--------------------------|--------------|--------------|---------------|--|--|

| ATTENTUATION | Attenuation:             | Minimum Attenuation (dB) |              |              |               |  |  |

| (dB)         | 3.5                      | 15                       | 52           | 25           | 15            |  |  |

#### **Band II Downlink WCDMA Rx MODE on RXIN5 (Monitor)**

| SPEC NO. | PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                    | MIN    | TYP   | MAX      | UNITS |

|----------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------|-------|

| Wb2fd-0  | Frequency Band                                                           |                                                                                                                                                                                                                                                                                                                                                                                               | 1932.4 |       | 1992.6   | MHz   |

| Wb2fd-1  | Sensitivity<br>3GPP TS25.101<br>Section 7.3.1                            | LNA gain high, PGA gain register set to 11, assumed SNDR > -7dB at sensitivity, using UL reference measurement channel, (12.2kbps) as specified in C.3.1 3GPP 25.101, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT, LNA linearity set to 0dBm, specified data is for a manual built fcLGA using 2.7pF filter caps |        | -110  |          | dBm   |

| Wb2fd-8  | Spurious Emissions Out-of-Band                                           | 30MHz to 1000MHz in 100kHz bandwidth (Note 3)                                                                                                                                                                                                                                                                                                                                                 |        | -100  | -100 -60 | dBm   |

| VVD21U-0 | 3GPP TS25.101<br>Section 7.9.1                                           | 1000MHz to 12750MHz in 1MHz bandwidth (Note 3)                                                                                                                                                                                                                                                                                                                                                |        | -96   | -50      | UDITI |

| Wb2fd-9  | Spurious Emissions<br>in Receive Bands<br>3GPP TS25.101<br>section 7.9.2 | Front-end assumed response as above, 1850MHz to 1910MHz and 1930MHz to 1990MHz (Note 3)                                                                                                                                                                                                                                                                                                       |        | -97   | -80      | dBm   |

| Wb2fd-10 | Conversion Gain<br>High LNA Gain                                         | LNA gain high; PGA gain register set to 11; tested on CW input signal at -90dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                | 37     | 44.5  | 49       | dB    |

| Wb2fd-11 | Conversion Gain<br>Low LNA Gain                                          | LNA gain low; PGA gain register set to 0; tested on CW input signal at -20dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                  | -18    | -12.7 | -7.5     | dB    |

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2$ MHz, all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### **PCS Band GMSK Rx Mode**

The signal shares the same path as WCDMA Band II downlink. Losses applied are:

1) Diplexer: 0.3dB

2) Band II duplexer, antenna to downlink port (same as WCDMA table)

3) SPDT: 0.3dB

#### PCS Band Rx Mode on RXIN5

| SPEC NO. | PARAMETER                                    | CONDITIONS                                                                                                                                                                                                                                                         | MIN    | TYP  | MAX    | UNITS |

|----------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|-------|

| pcs-0    | RF Frequency                                 |                                                                                                                                                                                                                                                                    | 1930.2 |      | 1994.8 | MHz   |

| pcs-1    | Sensitivity<br>3GPP TS100.910<br>Section 6.2 | LNA gain high, PGA gain register set to 12, assumed SNDR > 7dB at sensitivity, using static E-TCH/F as specified in 3GPP TS 100.910, tested by measurement of SNDR at ADC output on CW input signal at -102dBm, SNDR at MAX-PHY filter output established with FFT |        | -108 |        | dBm   |

#### **Band V Duplexer Specifications**

#### Antenna—Uplink Port (Applies to Uplink WCDMA Rx Mode on RXIN3)

| BAND (MHz)            | Uplink<br>824 to 849 | 1 to 804                             | 869 to 894         | 894 to 2500 | 2500 to 3000 | 3000 to 6000 |

|-----------------------|----------------------|--------------------------------------|--------------------|-------------|--------------|--------------|

| ATTENUATION (JB)      |                      | Attenuation Minimum Attenuation (dB) |                    |             |              |              |

| ATTENUATION (dB)      | 2                    | 32                                   | 43                 | 32          | 22           | 15           |

| Rx SAW FILTER RESPONS | SE                   |                                      |                    |             |              |              |

| BAND (MHz)            | Out-of-Band          |                                      |                    |             |              |              |

|                       | Required minim       | um attenuation re                    | elative to in-band | ·           |              |              |

| ATTENUATION (dB)      | 25                   |                                      |                    |             |              |              |

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### Band V Uplink WCDMA Rx Mode on RXIN3 (Full Duplex)

| SPEC NO. | PARAMETER                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MIN   | TYP  | MAX   | UNITS |

|----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Wb5fu-0  | Frequency Band                                                                      | WCDMA FDD Band V uplink (lowest to highest channel center frequency)                                                                                                                                                                                                                                                                                                                                                                                                     | 821.4 |      | 846.6 | MHz   |

| Wb5fu-1  | Sensitivity<br>3GPP TS25.104<br>Section 7.2.1                                       | Tx on at -27dBm, LNA gain mid gain, PGA gain register set to 9, assumed SNDR > -17.5dB at sensitivity, using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT, LNA linearity set to 0dBm (Note 3)                                                                                                                   |       | -118 | -107  | dBm   |

| Wb5fu-2  | Sensitivity with LNA in<br>High-Gain Mode                                           | Tx on at -27dBm, LNA gain high, PGA gain register set to 6, assumed SNDR > -17.5dB at sensitivity, using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT, LNA linearity set to high                                                                                                                                |       | -121 | -107  | dBm   |

| Wb5fu-3  | High-Level EVM WCDMA                                                                | P <sub>IN</sub> = -20 dBm, LNA gain low, PGA gain register set to 1                                                                                                                                                                                                                                                                                                                                                                                                      |       | 4.0  |       | %     |

| Wb5fu-4  | Sensitivity with Adjacent<br>Channel Interference<br>3GPP TS25.104 Section<br>7.4.1 | Tx on at -27dBm; LNA gain high; PGA gain register set to 3; assumed SNDR > -17.5dB at sensitivity; interfering signals at front-end input -28dBm, at 5MHz offset and -5MHz offset and modulated as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; SNDR at MAX-PHY filter output established with FFT (Note 3)                                         |       | -104 | -91   | dBm   |

| Wb5fu-5  | Sensitivity with In-Band<br>Blocking Interference<br>3GPP TS25.104 Section<br>7.5.1 | Tx on at -27dBm; LNA gain high; PGA gain register set to 6; assumed SNDR > -17.5dB at sensitivity; interfering signal at front-end input -30dBm at 1900MHz to 2000MHz min, 10MHz offset modulated as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; (test only worst case in production); SNDR at MAX-PHY filter output established with FFT (Note 3) |       | -120 | -101  | dBm   |

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### Band V Uplink WCDMA Rx Mode on RXIN3 (Full Duplex) (continued)

| SPEC NO. | PARAMETER                                                                      | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN  | TYP  | MAX  | UNITS |

|----------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Wb5fu-6  | Sensitivity with Out-of-Band Blocking Interference 3GPP TS25.104 Section 7.5.1 | Front-end assumed response as above; Tx on at -27dBm; LNA gain high; PGA gain register set to 6; assumed SNDR > -17.5dB at sensitivity; interfering signal at Front-end input -15dBm CW; 1MHz to 804MHz and 869MHz to 12750MHz with 1 MHz steps; no exceptions allowed; (test only worst case in production); using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; SNDR at MAX-PHY filter output established with FFT (Note 3) |      | -118 | -101 | dBm   |

| Wb5fu-7  | Sensitivity with Intermodulation Interference 3GPP TS25.104 Section 7.6.1      | Tx on at -27dBm; LNA gain high; PGA gain register set to 6; assumed SNDR > -17.5dB at sensitivity; interfering signals at front-end input -38dBm, at 10MHz offset (CW) and 20MHz offset (modulated) as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in A.2 3GPP 25.104; tested by measurement of SNDR at output on CW input signal at -90dBm; SNDR at MAX-PHY filter output established with FFT (Note 3)                                                                                               |      | -117 | -101 | dBm   |

|          |                                                                                | 30MHz to 1GHz, measured in 100kHz BW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | -100 | -60  |       |

| Wb5fu-8  | Spurious Emissions<br>Out-of-Band<br>3GPP TS25.104<br>Section 7.7.1            | 1GHz to 12.75GHz, measured in 1MHz BW, with the exception of frequencies between 12.5MHz below the first carrier frequency and 12.5MHz above the last carrier frequency used by the BS (Note 3)                                                                                                                                                                                                                                                                                                                                    |      | -84  | -50  | dBm   |

| Wb5fu-10 | Conversion Gain<br>High LNA Gain                                               | LNA high gain; PGA gain register set to 6; tested on CW input signal at -90dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                                                                                                                                                      | 25   | 32.5 | 37   | dB    |

| Wb5fu-11 | Conversion Gain<br>Mid LNA Gain                                                | LNA mid gain; PGA gain register set to 9; tested on CW input signal at -90dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output                                                                                                                                                                                                                                                                                       | 23.5 | 30   | 35   | dB    |

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2$ MHz, all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### Band V Uplink WCDMA Rx Mode on RXIN3 (Full Duplex) (continued)

| SPEC NO. | PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                   | MIN   | TYP | MAX | UNITS |

|----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-------|

| Wb5fu-12 | Conversion Gain<br>Low LNA Gain | LNA gain low; PGA gain register set to 1; tested on CW input signal at -20dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output | -14.5 | -8  | -4  | dB    |

#### Antenna—Downlink Port (Applies to Downlink WCDMA Rx Mode on RXIN4)

| BAND (MHz)       | Downlink<br>869 to 894 | 1 to 804                 | 824 to 849 | 914 to 3000 | 3000 to 6000 |  |

|------------------|------------------------|--------------------------|------------|-------------|--------------|--|

| ATTENUATION (dB) | Attenuation:           | Minimum Attenuation (dB) |            |             |              |  |

| ATTENUATION (UB) | 3                      | 37                       | 51         | 35          | 20           |  |

#### Band V Downlink WCDMA Rx Mode on RXIN4 (Monitor)

| SPEC NO. | PARAMETER                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                             | MIN   | TYP    | MAX    | UNITS |

|----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|--------|-------|

| Wb5fd-0  | Frequency Band                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        | 867.4 |        | 891.6  | MHz   |

| Wb5fd-1  | Sensitivity<br>3GPP TS25.101<br>Section 7.3.1                                       | LNA gain high, PGA gain register set to 11, assumed SNDR > -7dB at sensitivity, using UL reference measurement channel (12.2kbps) as specified in C.3.1 3GPP 25.101, tested by measurement of SNDR at output on CW input signal at -90dBm, SNDR at MAX-PHY filter output established with FFT, LNA linearity set to 0dBm, specified data is for a manual built fcLGA using 2.7pF filter caps           |       | -111.5 | -104.7 | dBm   |

| Wb5fd-4  | Sensitivity with Adjacent<br>Channel Interference<br>3GPP TS25.101 Section<br>7.5.1 | LNA gain high; PGA gain register set to 11; assumed SNDR > -7dB at sensitivity; interfering signals at front-end input -52dBm, at 5MHz offset and -5MHz offset and modulated as in 3GPP; using UL reference measurement channel (12.2kbps) as specified in C.3.1 3GPP 25.101; tested by measurement of SNDR at output on CW input signal at -90dBm; SNDR at MAX-PHY filter output established with FFT |       | -111   |        | dBm   |

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , registers set as described in Tables 20–51,  $V_{CC} = 3.0V$  to 3.6V,  $f_{REFIN} = 19.2MHz$ , all sensitivity levels and blocker levels are antenna referred. Typical values are at  $T_A = +25^{\circ}\text{C}$  and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

#### Band V Downlink WCDMA Rx Mode on RXIN4 (Monitor) (continued)

| SPEC NO. | PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                                                     | MIN   | TYP   | MAX  | UNITS |

|----------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|-------|

| Wb5fd-9  | Spurious Emissions<br>Out-of-Band                                        | 30MHz to 1000MHz, 100kHz bandwidth                                                                                                                                                                                                             |       | -100  | -60  | dBm   |

| VVD3IG-9 | 3GPP TS25.101<br>Section 7.9.1 (Note 3)                                  | 1000MHz to 12750MHz, 1MHz bandwidth                                                                                                                                                                                                            |       | -98   | -50  | UDITI |

| Wb5fd-10 | Spurious Emissions<br>in Receive Bands<br>3GPP TS25.101<br>Section 7.9.2 | Front-end assumed response as above, 824MHz to 849MHz and 869MHz to 894MHz (Note 3)                                                                                                                                                            |       | -95   | -80  | dBm   |

| Wb5fd-11 | Conversion Gain<br>High LNA Gain                                         | LNA gain high; PGA gain register set to 11; tested on CW input signal at -90dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the 16-bit output | 40    | 45    | 48   | dB    |

| Wb5fd-12 | Conversion Gain<br>Low LNA Gain                                          | LNA gain low; PGA gain register set to 0; tested on CW input signal at -20dBm; calculated by subtracting the FE input signal in dBm from the ADC output signal in dBFS at digital filter outputs, includes digital gain to the16-bit output    | -17.5 | -13.5 | -8.5 | dB    |

#### **GSM850 Band Rx Mode**

The signal shares the same path as WCDMA Band V downlink. Losses applied are:

1) Diplexer: 0.3dB

2) Band V duplexer, antenna to downlink port (same as WCDMA table)

3) SPDT: 0.3dB

#### **GSM850 Band GMSK Monitor on RXIN4**

| SPEC NO. | PARAMETER                                    | CONDITIONS                                                                                                                                                                                                                                                           | MIN   | TYP  | MAX   | UNITS |

|----------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| G850-0   | RF Frequency                                 |                                                                                                                                                                                                                                                                      | 865.2 |      | 893.8 | MHz   |

| G850-1   | Sensitivity<br>3GPP TS100.910<br>Section 6.2 | LNA gain high, PGA gain register set to 12, assumed SNDR > 7dB at sensitivity (GSM), using static E-TCH/F as specified in 3GPP TS 100.910, tested by measurement of SNDR at output on CW input signal at -102dBm, SNDR at MAX-PHY filter output established with FFT |       | -110 | -104  | dBm   |

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

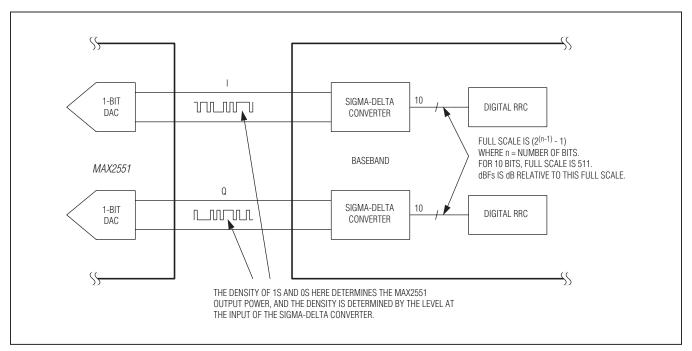

#### Tx MODE AC ELECTRICAL CHARACTERISTICS

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A$  = -40°C to +85°C, WCDMA downlink TM1 16 channels with -14dBFs peak level into sigma-delta modulator inside baseband chip (see the *Baseband Input Level* section), registers set as described in Tables 20–51,  $V_{CC_{-}}$  = 3.0V to 3.6V,  $f_{REFIN}$  = 19.2MHz, typical values are at  $T_A$  = +25°C,  $V_{CC_{-}}$  = 3.3V, and mid-band, unless otherwise noted. Tx specifications are referred to the output pin of the chip.) (Note 2)

| SPEC NO. | PARAMETER                                   | CONDITIONS                                                                                                                                                                                                                              | MIN    | TYP   | MAX    | UNITS  |

|----------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|--------|

| W1       | RF Frequency Range                          | Center of the WCDMA signal, Band II output (TXOUTH)                                                                                                                                                                                     | 1932.4 |       | 1992.6 | MHz    |

| W1a      |                                             | Band V output (TXOUTL)                                                                                                                                                                                                                  | 867.4  |       | 891.6  | MHz    |

| W2       | Linear Output Power                         | TX_GAIN = 1023                                                                                                                                                                                                                          | 0      |       |        | dBm    |

| W3       | Adjacent Channel Power<br>Ratio             | Offset frequency = ±5MHz in 3.84MHz BW, POUT = 0dBm (Note 3)                                                                                                                                                                            |        | -55   | -50    | dBc    |

| W4       | Alternate Channel Power Ratio               | Offset frequency = ±10MHz in 3.84MHz BW, POUT = 0dBm (Note 3)                                                                                                                                                                           |        | -70   | -60    | dBc    |

| W5       | Rx Band Noise Power,                        | Noise measured at -80MHz offset in 3.84MHz<br>BW, then convert to per Hz, Band II output                                                                                                                                                |        | -153  | -142   | dBm/Hz |

| W5a      | P <sub>OUT</sub> ≤ 0dBm                     | Noise measured at -45MHz offset in 3.84MHz<br>BW, then convert to per Hz, Band V output                                                                                                                                                 |        | -152  | -142   | dBm/Hz |

| W6       | EVM                                         | P <sub>OUT</sub> = 0dBm                                                                                                                                                                                                                 |        | 3.3   |        | %      |

| W6a      | RCDE                                        | TM6, 8 channels at 0dBm                                                                                                                                                                                                                 |        | -28   |        | dB     |

| W7       | Minimum Output Power                        | TX_GAIN = 0                                                                                                                                                                                                                             |        | -61   | -50    | dBm    |

| W8       | Output Power Deviation                      | TX_GAIN = 1023, high band                                                                                                                                                                                                               | -0.5   | +2    | +3.5   | dB     |

| VVO      | from $T_A = +25^{\circ}C$ to $-40^{\circ}C$ | Low band                                                                                                                                                                                                                                | -1     | +0.5  | +2.5   | иь     |

| W9       | Output Power Deviation                      | TX_GAIN = 1023, high band                                                                                                                                                                                                               | -4     | -2    | -1     | dB     |

| VV9      | from $T_A = +25^{\circ}C$ to $+85^{\circ}C$ | Low band                                                                                                                                                                                                                                | -2.5   | -1    | 0      | иь     |

| W10      | Power Control Step Size<br>Accuracy         | Five calibration points over the power control range to create four linear regions, any linearly interpolated 1dB TX_GAIN step over the specified power range (W2 and W7) will produce 1dB output power step within this error range.   |        | ±0.25 |        | dB     |

| W11      | Power Control Step Size<br>Accuracy         | Five calibration points over the power control range to create four linear regions, any linearly interpolated 10dB TX_GAIN step over the specified power range (W2 and W7) will produce 10dB output power step within this error range. | ±0.75  |       | dB     |        |

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **AC ELECTRICAL CHARACTERISTICS: General**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A$  = -40°C to +85°C, registers set as described in Tables 20–51,  $V_{CC_{-}}$  = 3.0V to 3.6V,  $f_{REFIN}$  = 19.2MHz, all sensitivity levels and blocker levels are antenna referred, typical values are at  $T_A$  = +25°C, unless otherwise noted.) (Note 2)

| SPEC NO.   | PARAMETER                                                 | CONDITIONS                                                             | MIN         | TYP   | MAX   | UNITS              |

|------------|-----------------------------------------------------------|------------------------------------------------------------------------|-------------|-------|-------|--------------------|

| REFERENC   | E FREQUENCY INPUT                                         |                                                                        |             |       |       |                    |

| R1         | Input Level                                               | Test condition                                                         | 125         |       | 600   | mV <sub>P-P</sub>  |

| R2         | Input Frequency                                           | Reference divider set to divide-by-2 for frequencies higher than 26MHz | 13          | 19.2  | 40    | MHz                |

| REFERENC   | E FREQUENCY OUTPUT                                        |                                                                        |             |       |       |                    |

| RO1a       | REFOUT Output Level, AC                                   | $500$ Ω II 22pF load, REFOUT_LV_CMOS_SEL = 1                           | 110         | 320   | 500   | mV <sub>P-P</sub>  |

| RO1b       | REFOUT Output Level, DC                                   |                                                                        |             | 0.8   |       | V                  |

| RO2        | REFOUT Output Amplitude                                   | $500$ Ω II 22pF load, REFOUT_LV_CMOS_SEL = 0                           | 2.4         | 2.7   |       | V <sub>P-P</sub>   |

| RO4        | REFOUT Output<br>Frequency                                | Matches REFIN frequency (FREF)                                         | 13          | 19.2  | 40    | MHz                |

| Rx DIGITAL | LOW-VOLTAGE DIFFEREN                                      | ITIAL SIGNALING OUTPUT INTERFACE                                       |             |       |       | ,                  |

| LV0        | Output Bit Rate on Each I and Q                           | Test condition                                                         |             | 153.6 |       | Mbps               |

| LV1        | Output Common Mode                                        |                                                                        |             | 1.2   |       | V                  |

| LV3        | Output Differential Swing on Load                         | 120 $\Omega$ differential output load (Note 3)                         | 100 140 220 |       | 220   | mV <sub>PEAK</sub> |

| LV4        | Differential Output<br>Resistance                         |                                                                        | 670         |       |       | Ω                  |

| Tx BASEBA  | ND INTERFACE                                              |                                                                        | -           |       |       | Į                  |

| Bb1        | Input Bit Rate, on Each I and Q                           | Test condition                                                         |             | 153.6 |       | Mbps               |

| Bb8        | Common Mode Input<br>Voltage                              |                                                                        |             | 1.25  |       | V                  |

| Bb9        | Differential Input Swing                                  |                                                                        | 112         | 140   | 500   | mV <sub>P-P</sub>  |

| bb10       | Differential Input                                        | Bit TXINDACZI = 1                                                      | 55          | 100   | 140   | 0                  |

| bb11       | Resistance (Note 3)                                       | Bit TXINDACZI = 0                                                      | 140         | 220   | 340   | Ω                  |

| Rx RF PLL  |                                                           |                                                                        |             |       |       |                    |

| RS1        | Valid RF Main Division<br>Ratio Range                     |                                                                        | 62          |       | 147   |                    |

| RS3        | Valid Main Fractional<br>Divider Programming<br>Value     | 20-bit resolution                                                      | 00000       |       | FFFFF | hex                |

| RS5        | Charge-Pump Current Gain  Using 800µA setting  0.5 0.82 1 |                                                                        | 1.0         | mA    |       |                    |

| RS6a       | V00 T : 0 :                                               | RXVCO, high band                                                       | 21          | 65    | 111   | N 41 1 2 2         |

| RS6b       | VCO Tuning Gain                                           | RXVCO, low band                                                        | 38          | 127   | 216   | MHz/V              |

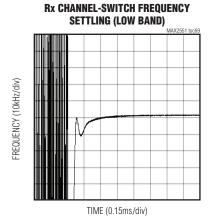

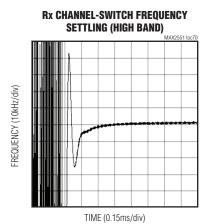

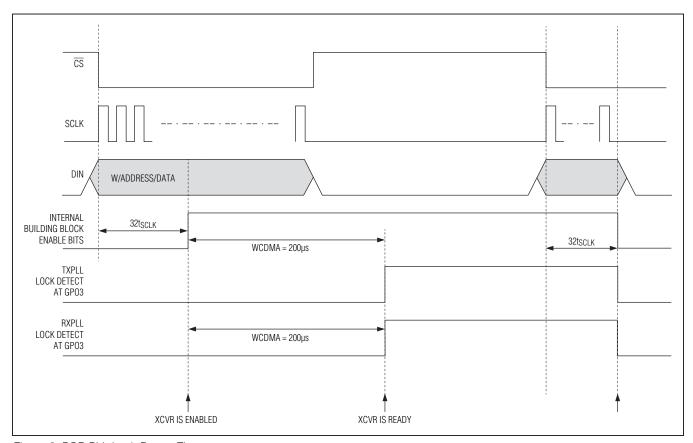

| RS9        | PLL Settling Time                                         | 50kHz loop bandwidth                                                   | 200         |       | μs    |                    |

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **AC ELECTRICAL CHARACTERISTICS: General (continued)**

(MAX2551 MAX-PHY FPGA evaluation platform,  $T_A$  = -40°C to +85°C, registers set as described in Tables 20–51,  $V_{CC_-}$  = 3.0V to 3.6V,  $f_{REFIN}$  = 19.2MHz, all sensitivity levels and blocker levels are antenna referred, typical values are at  $T_A$  = +25°C, unless otherwise noted.) (Note 2)

| SPEC NO.   | PARAMETER                                             | CONDITIONS                                                 | MIN   | TYP  | MAX   | UNITS   |

|------------|-------------------------------------------------------|------------------------------------------------------------|-------|------|-------|---------|

| Tx RF PLL  |                                                       |                                                            |       |      |       |         |

| TS2        | Valid RF Main Division<br>Ratio Range                 |                                                            | 66    |      | 153   |         |

| TS3        | Valid Reference Division<br>Ratios                    | Division ratios are 1 or 2                                 | 1     |      | 2     |         |

| TS4        | Valid Main Fractional<br>Divider Programming<br>Value | 20-bit resolution                                          | 00000 |      | FFFFF | hex     |

| TS5        | Charge-Pump Current CP                                | 800μΑ                                                      | 0.5   | 0.82 | 1.0   | mA      |

| TS9        | PLL Settling Time                                     | 50kHz loop bandwidth                                       |       | 200  |       | μs      |

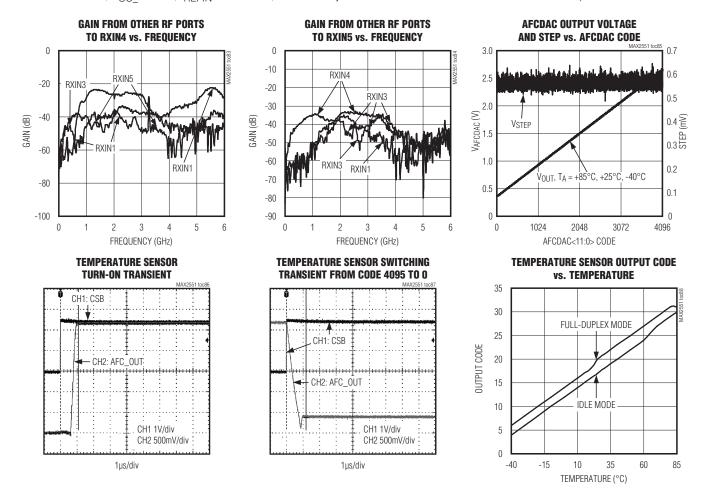

| DAC1       | Resolution                                            | Monotonicity is production tested                          |       | 12   |       | Bits    |

| AFC DAC    |                                                       |                                                            |       |      |       |         |

| DAC3       | Output-Voltage High                                   | Load > $200k\Omega$ to GND, AFCDAC = all 1                 | 2.55  | 2.68 |       | V       |

| DAC4       | Output-Voltage Low                                    | Load > 200k $\Omega$ to V <sub>CC_</sub> , AFCDAC = all 0  |       | 0.37 | 0.45  | V       |

| DAC5       | Output Noise                                          | Any code within 0.5V to 2.5V output level, 100Hz to 20kHz  |       | 6    |       | μV/rtHz |

| DAC6       | Settling Time                                         | Step from 0.6V to 2V, settling to ±10mV                    |       |      |       | μs      |

| DIGITAL TE | MPERATURE SENSOR                                      |                                                            |       |      |       |         |

| T1         | 0 0                                                   | $T_A = -40$ °C                                             |       | 5    |       |         |

| T2         | Output Code vs. Temperature                           | $T_A = +25$ °C                                             |       | 17   |       | 0/1     |

| T3         | remperature                                           | $T_A = +85^{\circ}C$                                       |       | 27   |       | °/code  |

| T5         | Code Slope                                            | $T_A = -20$ °C to $+70$ °C                                 | 5     |      |       |         |

| ISOLATION  |                                                       |                                                            |       |      |       |         |

| M1         | RXIN_ Pin-to-Pin Isolation                            | Between any RXIN_ pins, with one of the two ports disabled | 30    |      | dB    |         |

| M2         | TXOUT_ to RXIN_ Isolation                             | Between any TXOUT and RXIN_, with both ports on            |       | 60   |       | dB      |

**Note 2:** Production tested at  $T_A = +25$ °C. Cold and hot are guaranteed by design and characterization.

Note 3: Guaranteed by design and characterization.

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **General Comments**

#### **MAX-PHY**

MAX-PHY is Maxim's solution for the digital interface system between the radio IC and the baseband/DSP. It is a multimode, software programmable, digital signal post-processing engine that processes the data out of the radio IC and produces the digital filtered outputs for use in the DSP. It enables multimode operation of the radio through software control. Maxim offers an evaluation kit for the MAX2551 along with an FPGA-based MAX-PHY evaluation platform. The FPGA includes the recommended digital channel-selection filters. The Verilog code for these filters is also available for integration into the DSP. Contact Maxim for further information.

#### **Additional Information**

The specifications in the following pages calculate sensitivity with a specified front-end loss from a measured signal-to-noise and distortion ratio (SNDR) and an assumed minimum output SNDR<sub>SENS</sub> needed for demodulation at sensitivity. The sensitivity values can be related to noise figure by the formula:

Noise Figure of MAX2551 (dB) = Sensitivity (dBm) - Front-End Loss (dB) - SNDR<sub>SENS</sub> (dB) + 174dBm/Hz - 10 x LOG(bandwidth in Hz)

Low-noise amplifier (LNA) and programmable-gain amplifier (PGA) gain are set according to the Conditions column in the *Electrical Characteristics* table. The output SNDR is measured using MAX-PHY and the bandwidth of the measurement is defined by the digital filters in MAX-PHY. DC at the output is excluded from the SNDR measurement. SNDR is calculated using an FFT of the output bytes with a typical FFT length of 2<sup>14</sup> output samples.

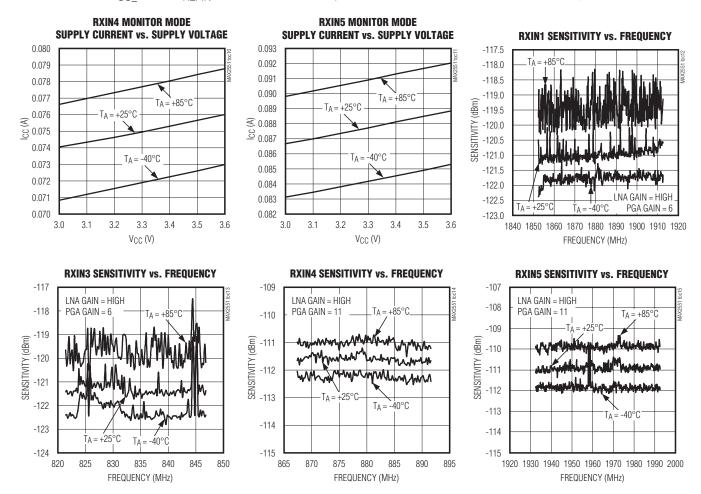

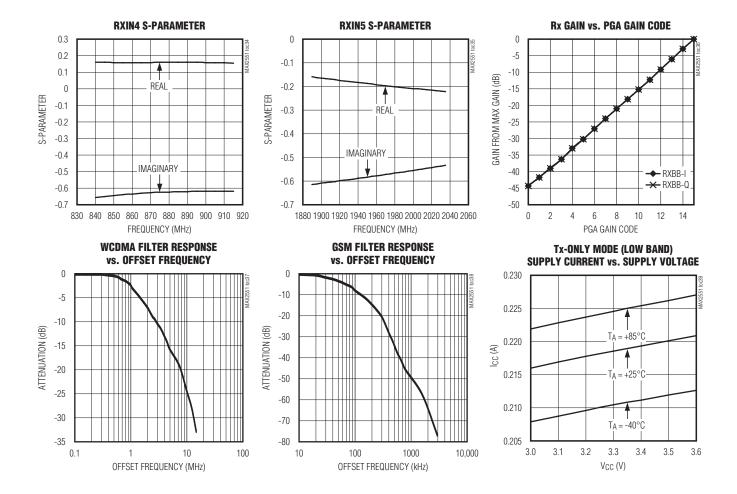

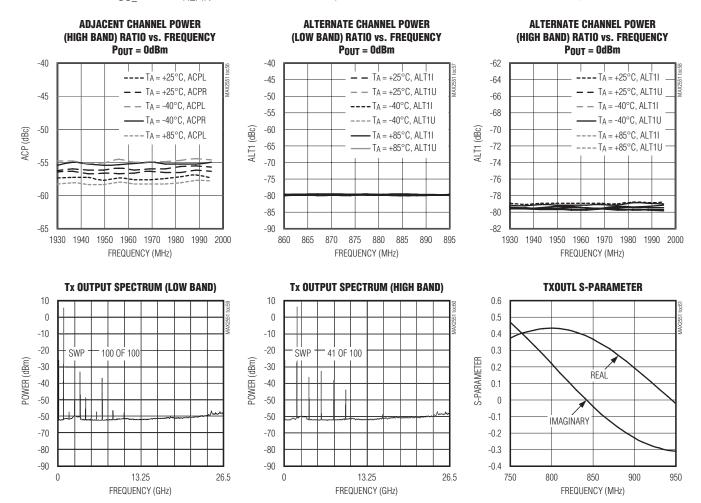

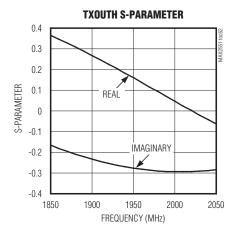

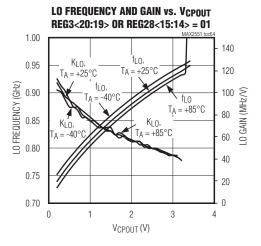

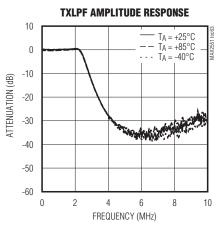

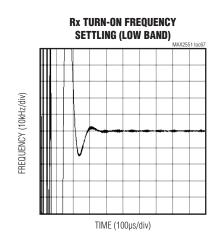

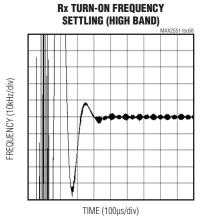

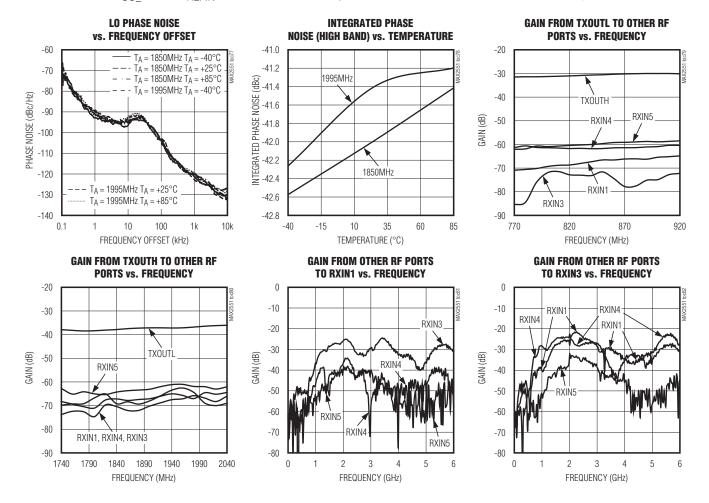

## **Typical Operating Characteristics**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

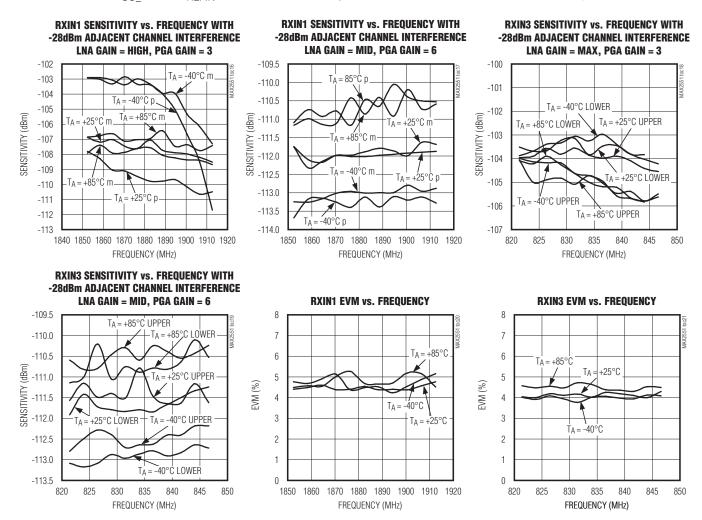

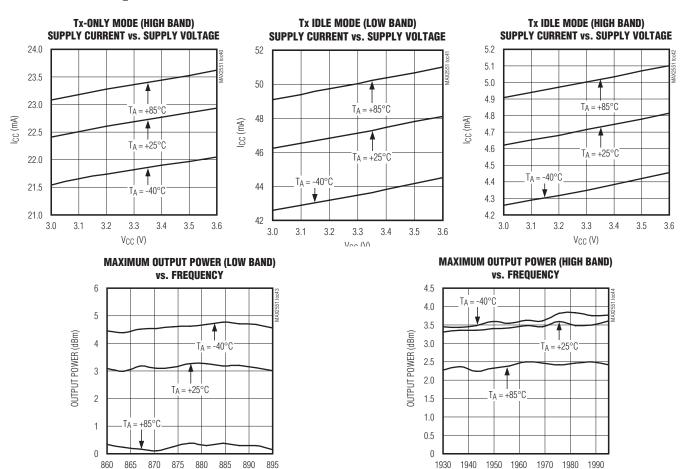

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

## Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

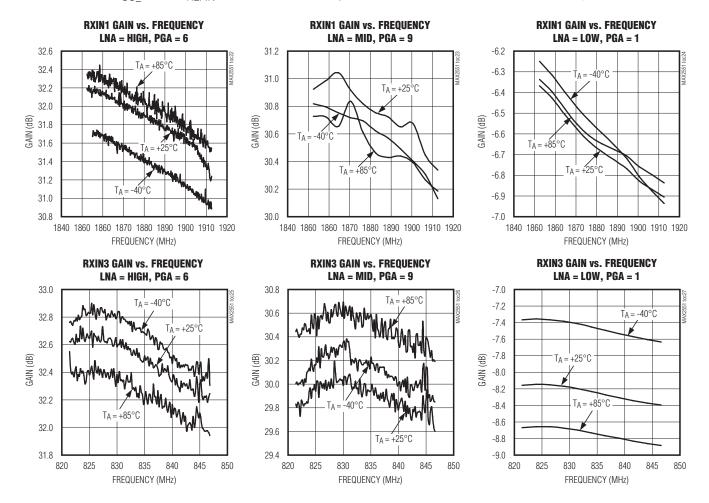

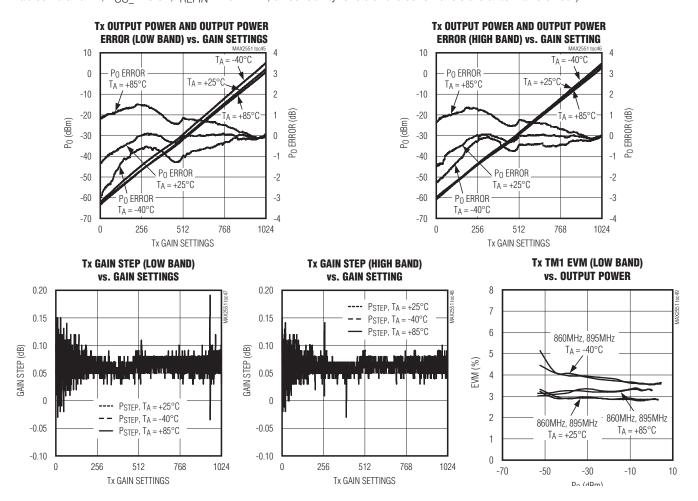

#### Typical Operating Characteristics (continued)

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

## **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

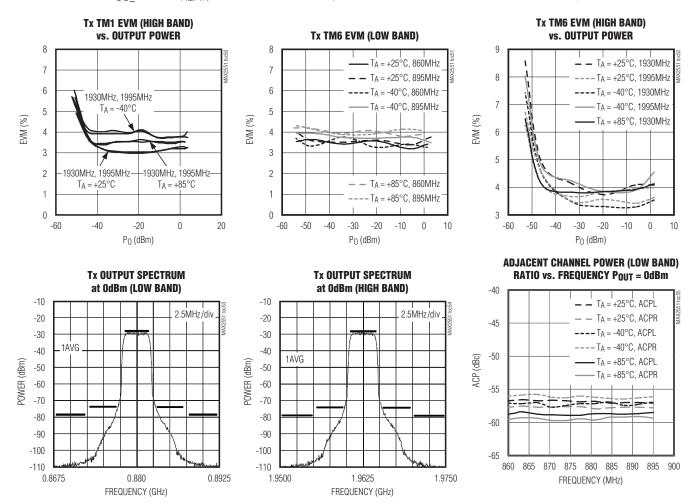

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

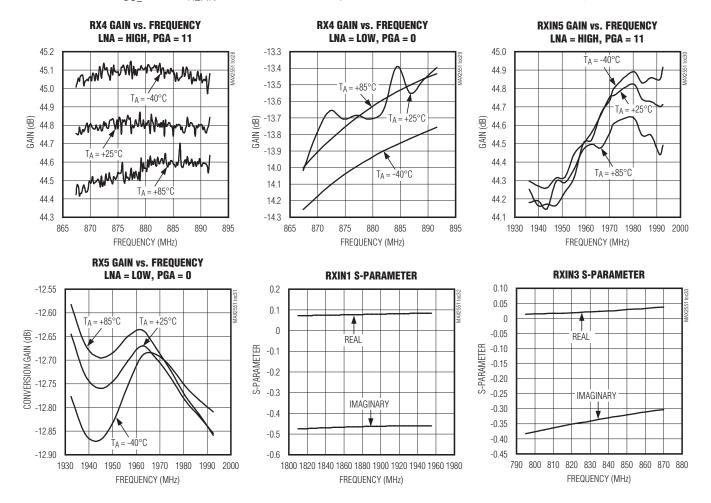

## **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

## **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC_{-}} = 3.3V$ ,  $f_{REFIN} = 19.2 \text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

FREQUENCY (MHz)

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2MHz$ , all sensitivity levels and blocker levels are antenna referred.)

FREQUENCY (MHz)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2MHz$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### Typical Operating Characteristics (continued)

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{\text{CC}} = 3.3\text{V}$ ,  $f_{\text{REFIN}} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

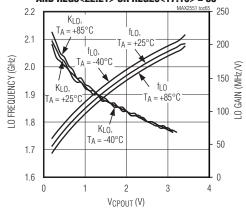

LO FREQUENCY AND GAIN vs. V<sub>CPOUT</sub> REG3<20:19> OR REG28<15:14> = 10, AND REG3<22:21> OR REG28<17:16> = 00

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

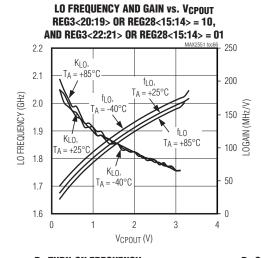

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}C$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC_{-}} = 3.3V$ ,  $f_{REFIN} = 19.2MHz$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC} = 3.3V$ ,  $f_{REFIN} = 19.2\text{MHz}$ , all sensitivity levels and blocker levels are antenna referred.)

# **Band II and V WCDMA Femtocell Transceiver with GSM Monitoring**

#### **Typical Operating Characteristics (continued)**

(MAX2551 EV kit and MAX-PHY FPGA evaluation platform,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Registers set as described in Tables 20 and 21,  $V_{CC_{-}} = 3.3V$ ,  $f_{REFIN} = 19.2MHz$ , all sensitivity levels and blocker levels are antenna referred.)

# Band II and V WCDMA Femtocell Transceiver with GSM Monitoring

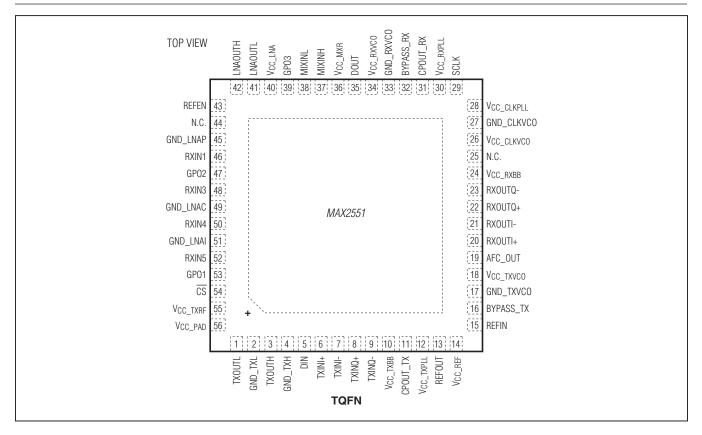

### **Pin Configuration**

## **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                         |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TXOUTL  | Low-Band TXRF Output. Internally matched to $50\Omega$ over the band of operation.                                                               |

| 2   | GND_TXL | Tx Ground. Connect directly to ground plane.                                                                                                     |