# GX414A Monolithic 4x1 Video Multiplexer

# DATA SHEET

#### FEATURES

- low disabled power consumption: 5.2 mW

- low differential gain: 0.03% typ. at 4.43 MHz

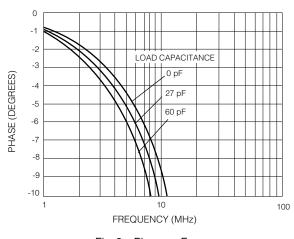

- low differential phase: 0.012° typ. at 4.43 MHz

- bandwidth (-3dB) 100 MHz with 30 pF load

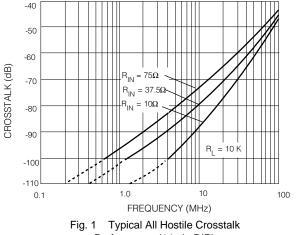

- all hostile crosstalk at 5 MHz -97dB typ.

- low insertion loss 0.05 dB max at 100 kHz

- off-isolation 110 dB at 10 MHz

- fast make before break switching: 200 ns typ.

- TTL and 5 volt CMOS compatible logic inputs

- for NTSC, PAL and SECAM applications

- low cost 14 pin DIP and16 pin SOIC packages

#### **CIRCUIT DESCRIPTION**

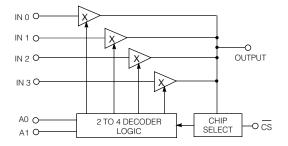

The GX414A is high performance low cost monolithic 4x1 video multiplexer incorporating four analog video switches and a 2 to 4 address decoder. An enabled input allows paralleled GX414As to be operated in a switching matrix with multiple inputs and a common output. Unlike similar devices using MOS bilateral switching elements, the GX414A represents a fully buffered unilateral trans-mission path when enabled. The GX414A requires  $\pm 8V$  and is designed for use in video switching applications. Logic inputs are TTL and 5V CMOS compatible, providing input select and output enable functions.

## APPLICATIONS

Glitch free analog switching for...

- High quality video routing

- A/D input multiplexing

- Sample and hold circuits

- TV/ CATV/ monitor switching

- Instrumentation and communication equipment

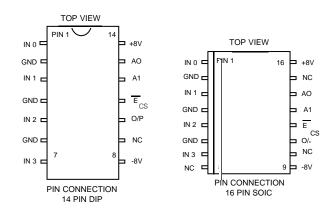

# **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| Part Number  | Package Type     | Temperature Range |  |  |

|--------------|------------------|-------------------|--|--|

| GX414 - ACDB | 14 Pin DIP       | 0° to 70° C       |  |  |

| GX414 - ACKC | 16 Pin SOIC      | 0° to 70° C       |  |  |

| GX414 - ACTC | Tape 16 Pin SOIC | 0° to 70° C       |  |  |

## FUNCTIONAL SCHEMATIC

#### TRUTH TABLE

| ĊŚ     | A1        | A0        | OUTPUT   |  |  |

|--------|-----------|-----------|----------|--|--|

| 0      | 0         | 0         | IN 0     |  |  |

| 0      | 0         | 1         | IN 1     |  |  |

| 0      | 1         | 0         | IN 2     |  |  |

| 0      | 1         | 1         | IN 3     |  |  |

| 1      | х         | х         | HI - Z   |  |  |

| X = D( | I<br>ON'T | I<br>CARE | <u> </u> |  |  |

# ABSOLUTE MAXIMUM RATINGS

| Parameter                            | Value                                  | Parameter            | Value                      |

|--------------------------------------|----------------------------------------|----------------------|----------------------------|

| Supply Voltage                       | ±13.5V                                 | Analog Input Voltage | $-4V \le V_{IN} \le +2.4V$ |

| Operating Temperature Range          | $0^{\circ}C \le T_{A} \le 70^{\circ}C$ | Analog Input Current | 50μA AVG, 10 mA peak       |

| Storage Temperature Range            | -65°C ≤ T <sub>S</sub> ≤ 150° C        | Logic Input Voltage  | $-4V \le V_1 \le +5.5V$    |

| Lead Temperature (Soldering, 10 Sec) | 260° C                                 |                      | _                          |

# **ELECTRICAL CHARACTERISTICS** (V<sub>S</sub> = ±8V DC, 0°C < T<sub>A</sub> < 70°C, R<sub>L</sub> = 10K, C<sub>L</sub> = 30 pF, unless otherwise shown.)

| PARAMETER                       | CONDITIONS                                                                                |                            | MIN              | TYP                       | MAX                       | UNITS                |

|---------------------------------|-------------------------------------------------------------------------------------------|----------------------------|------------------|---------------------------|---------------------------|----------------------|

| Supply Current                  | CS = 0 V+<br>V-<br>CS = 1 V+<br>V-                                                        |                            | -<br>-<br>-<br>- | 11<br>10.5<br>0.4<br>0.25 | 14<br>14<br>0.58<br>0.38  | mA                   |

| Analog Output Voltage<br>Swing  | Extremes before clipping occurs                                                           |                            | -                | +2.0<br>-1.2              | -                         | V                    |

| Output Offset voltage           | 75 $\Omega$ on each input grou                                                            | nd                         | -2               | 5                         | 12                        | mV                   |

| Output Offset Drift             | $\Delta$ V <sub>OSC</sub> / $\Delta$ T                                                    |                            | -                | +50                       | +200                      | μV / °C              |

| Address Logic Delay             | Control input to appearance<br>of signal on output                                        |                            | 130              | 200                       | 270                       | ns                   |

| Chip Selection Delay            | Control input to appearance<br>of signal on output                                        |                            | 200              | 300                       | 400                       | ns                   |

| Logic Input Threshold           | 1<br>0                                                                                    |                            | - 2              | -                         | 1.1<br>-                  | V<br>V               |

| Logic Input Current             | A0, A1 = 1<br>A0, A1 = 0<br>$\frac{\overline{CS}}{\overline{CS}} = 1$ $\overline{CS} = 0$ |                            | -<br>-<br>-      |                           | 5.0<br>0.1<br>1.0<br>30.0 | μA<br>nA<br>nA<br>μA |

| Insertion Loss                  | 1V p-p sine or sq.wave at 100 kHz                                                         |                            | 0.02             | 0.03                      | 0.05                      | dB                   |

| Gain Spread at 8 MHz            |                                                                                           |                            | -                | -                         | ±0.25                     | dB                   |

| Bandwidth ( -3dB )              |                                                                                           |                            | 90               | 100                       | -                         | MHz                  |

| Differential Gain               | at 3.58 or 4.43 MHz                                                                       |                            | -                | 0.03                      | 0.05                      | %                    |

| Differential Phase              | at 3.58 or 4.43 MHz                                                                       |                            | -                | 0.012                     | 0.025                     | degrees              |

| Matching (chip-chip) at 3.57954 | $75\Omega$ source impedance                                                               |                            | -                | -                         | ±0.6                      | degrees              |

|                                 |                                                                                           | Full temp.                 | -                | -                         | ±1.0                      | degrees              |

| All Hostile Crosstalk           | Sweep on 3 inputs 1V p-p 4th input 10 $\Omega$ to gnd at 5 MHz                            |                            | 94               | 97                        | -                         | dB                   |

| Chip Disabled Crosstalk         | 14 $\Omega$ on output to gnd at 10 MHz                                                    |                            | 100              | 110                       | -                         | dB                   |

| Input Resistance                | $\overline{CS} = 0$                                                                       |                            | -                | 960                       | -                         | kΩ                   |

| Input Capacitance               | $\frac{\overline{CS}}{\overline{CS}} = 0$<br>$\overline{CS} = 1$                          |                            | -                | 2.0<br>2.4                | -                         | pF<br>pF             |

| Output Resistance               |                                                                                           | $\overline{CS} = 0$        | -                | 14                        | -                         | Ω                    |

| Output Capacitance              |                                                                                           | $\overline{\text{CS}} = 1$ | -                | 15                        | -                         | pF                   |

| Slew Rate                       | V <sub>IN</sub> = 3V p-p (C <sub>L</sub> = 0 pF                                           | +SR<br>-) -SR              | -                | 40<br>40                  | -                         | V/μs<br>V/μs         |

Performance (14 pin DIP)

Fig. 2 Phase vs Frequency

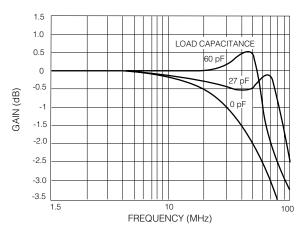

Fig. 3 Gain vs Frequency

10 mV/div

0.1 V/div

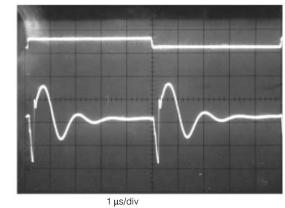

Fig. 4 Switching Transient (crosspoint-to-crosspoint)

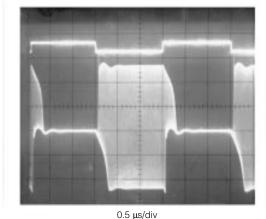

Fig. 5 Switching Envelope (crosspoint-to-crosspoint)

## **APPLICATION INFORMATION**

As expected with any wide bandwidth circuit, the layout is critical. Good power supply regulation and bypassing are necessary, along with good high frequency design practice. Proper lead dress, component placement and PC board layout must be exercised for optimum performance.

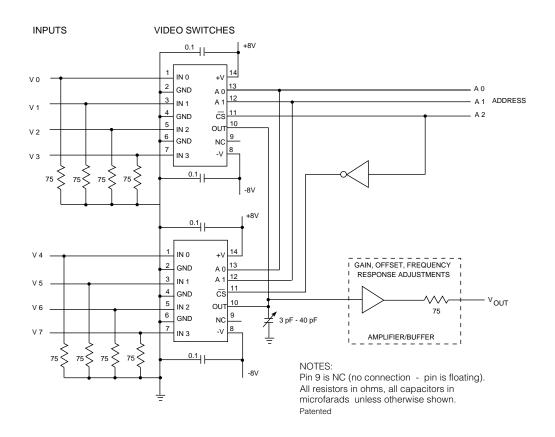

The GX414A is non-inverting. Frequency peaking is compensated on-chip and optimised for a 60 pF load. The inputs are buffered and require  $75\Omega$  line terminating resistors when driven from  $75\Omega$  cable. The output must be buffered to drive  $75\Omega$  lines. The addition of an amplifier/buffer also allows adjustments to be made to the gain, offset and frequency response of the circuit. By reducing the load capacitance from 60 pF, the GX414A can be used to compensate for the frequency peaking of the buffer.

A typical application is shown in Figure 6 on the next page . Two GX414A devices are paralleled to form an 8x1 multiplexer switch. The three address lines make use of the A0, A1 and  $\overline{CS}$  inputs. If more than two devices are used in parallel, a decoder will be necessary to generate the extra address inputs. Depending on the application and the speed of the logic family employed, latches may be required for synchronization where timing and delays are important.

The active switching circuitry of the GX414A will ensure low crosstalk and high performance over an input voltage range of -1.2 V to +2.0 V.

Fig. 6 Video Multiplexer Incorporating Two GX414As

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.