SLLS407 - FEBRUARY 2000

- Flatlink™ Interface Utilizes Low Power Differential Signalling(LVDS)

- Suitable for Notebook Application

- XGA Resolution

- Six Bit System Interface

- Support Mainstream Data and Gate Drivers

- Optional Configurable Pins

- Low Voltage CMOS 3.3 V Technology

- 65 MHz Phase-Lock Input

- 100-pin TQFP Package for Compact LCD Module

- Tolerates 4 kV HBM ESD for LVDS Pins and 2 kV HBM for Others

- Improved Jitter Tolerance

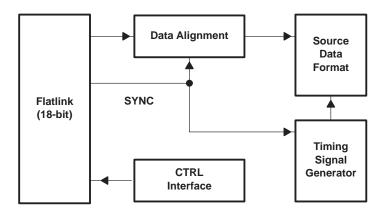

## description

The SN75LVDS88B (LVDS panel timing controller) integrates a Flatlink™ signal interface with a TFT LCD timing controller. It resides in the LCD panel and provides interface between the graphic controller and a TFT LCD panel.

The SN75LVDS88B accepts host data through 3 pairs of inputs (18-bits) making up the LVDS bus, which is a low-EMI high-throughput interface. SN75LVDS88B then reformats the received image data into a specific data format and synchronous timing suitable for driving LCD panel column and row drivers. This device supports XGA resolution.

The SN75LVDS88B is easily configured by several selection terminals and is equipped with default timing specifications to support mainstream gate and source drivers on the market.

## block diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Flatlink is a trademark of Texas Instruments Incorporated.

SLLS407 - FEBRUARY 2000

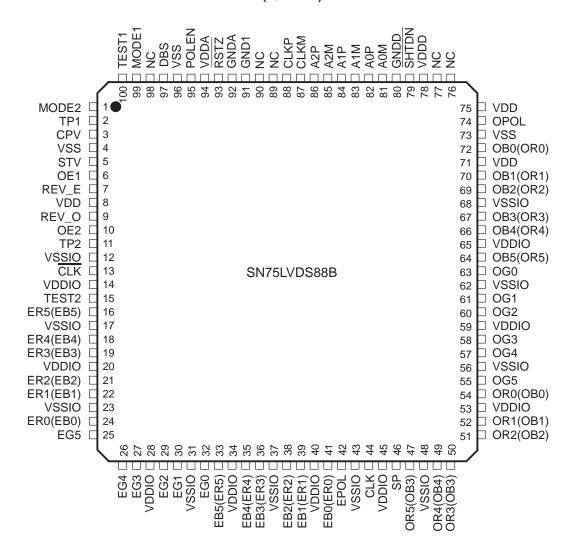

## pin assignment

#### TQFP PACKAGE (TOP VIEW)

# **Terminal Functions**

| TERMINAL             |                                              |     |                                                                    |

|----------------------|----------------------------------------------|-----|--------------------------------------------------------------------|

| NAME                 | NO.                                          | 1/0 | DESCRIPTION                                                        |

| A0M/A0P              | 81,82                                        | I   | Flatlink 1 <sup>st</sup> data pair                                 |

| A1M/A1P              | 83, 84                                       | I   | Flatlink 2 <sup>nd</sup> data pair                                 |

| A2M/A2P              | 85, 86                                       | I   | Flatlink 3 <sup>rd</sup> data pair                                 |

| CLK                  | 44                                           | 0   | CD bus clock                                                       |

| CLK                  | 13                                           | 0   | CD bus clock (180 degree out of phase)                             |

| CLKM/CLKP            | 87, 88                                       | Ι   | Flatlink clock pair                                                |

| CPV                  | 3                                            | 0   | Gate driver clock                                                  |

| DBS                  | 97                                           | Т   | Data bus sequence                                                  |

| EPOL                 | 42                                           | 0   | Even RGB data stream polarity indicator                            |

| ER0ER5<br>(EB0)(EB5) | 24, 22, 21,<br>19, 18, 16                    | 0   | Even red (blue) data bus, controlled by DBS Pin, 0 = red, 1 = blue |

| (ER0)(ER5)<br>EB0EB5 | 41,39,38<br>36,35,33                         | 0   | Even blue (red) data bus, controlled by DBS Pin, 0 = blue, 1 = red |

| GND1                 | 91                                           | Р   | PLL ground for LVDS                                                |

| MODE1                | 99                                           | ı   | Default timing selection pin 1                                     |

| MODE2                | 1                                            | ı   | Default timing selection pin 2                                     |

| NC                   | 76, 77, 89, 90, 98                           | NC  | NC terminals <sup>†</sup>                                          |

| OE1, OE2             | 6, 10                                        | 0   | Gate driver output enable                                          |

| OG0OG5               | 63, 61, 60,<br>58, 57, 55                    | 0   | Odd green data bus                                                 |

| OPOL                 | 74                                           | 0   | Odd RGB data stream polarity indicator                             |

| OR0OR5<br>(OB0)(OB5) | 54, 52, 51,<br>50, 49, 47                    | 0   | Odd red (blue) data bus, controlled by DBS Pin, 0 = red, 1 = blue  |

| (OR0)(OR5)<br>OB0OB5 | 72, 70, 69<br>67, 66, 64                     | 0   | Odd blue (red) data bus, controlled by DBS Pin, 0 = blue, 1 = red  |

| POLEN                | 95                                           | ı   | Output data polarity control enable /disable                       |

| REV_E                | 7                                            | 0   | CD line/dot inversion control signal                               |

| REV_O                | 9                                            | 0   | CD line/dot inversion control signal (180 degree of phase)         |

| RSTZ                 | 93                                           | ı   | Reset, active low                                                  |

| SHTDN                | 79                                           | ı   | System shutdown control, active low                                |

| SP                   | 46                                           | 0   | Data bus starting pulse                                            |

| STV                  | 5                                            | 0   | Gate driver starting pulse                                         |

| TEST1, TEST2         | 100, 15                                      | ı   | Test points <sup>†</sup>                                           |

| TP1, TP2             | 2, 11                                        | 0   | CD output control signal                                           |

| VDDA                 | 94                                           | Р   | PLL power for LVDS                                                 |

| GNDA                 | 92                                           | Р   | Analog ground for LVDS                                             |

| VDDD                 | 78                                           | Р   | Digital power supply for LVDS                                      |

| GNDD                 | 80                                           | Р   | Digital power ground for LVDS                                      |

| VDD                  | 8,71,75                                      | Р   | Digital power                                                      |

| VSS                  | 4,73,96                                      | Р   | Digital ground                                                     |

| VDDIO                | 14, 20, 28, 34,<br>40, 45, 53, 59, 65        | Р   | I/O power                                                          |

| VSSIO                | 12, 17, 23, 31,<br>37, 43, 48, 56,<br>62, 68 | Р   | I/O ground                                                         |

<sup>†</sup> Terminals must be connected to ground.

# SN75LVDS88B TFT LCD PANEL TIMING CONTROLLER WITH LVDS INTERFACE

SLLS407 – FEBRUARY 2000

## options

## output control

| PIN NAME       | PIN NO. | INTERNAL CONNECTION |           | DESCRIPTION                                                       |

|----------------|---------|---------------------|-----------|-------------------------------------------------------------------|

| PIN NAME       |         | REQUIRED            | SUGGESTED | DESCRIPTION                                                       |

| MODE1<br>MODE2 | 99<br>1 | Pullup<br>Pulldown  |           | Default timing selection pin 1 Default timing selection pin 2     |

| POLEN          |         | Pulldown            |           | 0 = Output data reverse disable<br>1 = Output data reverse enable |

| DBS            | 97      | Pulldown            |           | Data bus sequence<br>0 = normal (RGB)<br>1 = reverse (BGR)        |

NOTE: NC pin 76 is internally pulldown and NC pins 77 and 98 are internally pullup.

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> <sup>‡</sup>           | 0.5 V to 4 V                 |

|--------------------------------------------------------------|------------------------------|

| Voltage range at any terminal                                |                              |

| Continuous power dissipation                                 | See Dissipation Rating Table |

| Storage temperature range, T <sub>stg</sub>                  |                              |

| Electrostatic discharge: Class 3 A                           | 4 kV                         |

| Class 2 B                                                    | 200 V                        |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | OPERATING FACTOR§ ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|----------------------------------------------------|-----------------------------------------------|---------------------------------------|

| PFD     | 1.548 W                                            | 12 mW                                         | 1.012 W                               |

<sup>§</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

<sup>‡</sup> All voltage values are with respect to the GND terminals unless otherwise noted.

SLLS407 - FEBRUARY 2000

# recommended operating conditions

|                                              |                      |  | NOM                        | MAX | UNIT |

|----------------------------------------------|----------------------|--|----------------------------|-----|------|

| Supply voltage, V <sub>CC</sub>              |                      |  |                            | 3.6 | V    |

| High-level input voltage, VIH                |                      |  | 2                          |     | V    |

| Low-level input voltage, V <sub>IL</sub>     | SHTDN                |  |                            | 0.8 | V    |

| Magnitude of differential input voltage, VID | 0.1                  |  | 0.6                        | V   |      |

| Common-mode input voltage, V <sub>IC</sub>   | $\frac{ V_{ID} }{2}$ |  | $2.4 - \frac{ V_{ID} }{2}$ | V   |      |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                           | TEST CONDITIONS                                                                 | MIN  | TYP <sup>†</sup> | MAX | UNIT |

|-------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|------|------------------|-----|------|

| V <sub>IT+</sub>  | Positive-going differential input voltage threshold |                                                                                 |      |                  | 100 | mV   |

| V <sub>IT</sub> _ | Negative-going differential input voltage threshold |                                                                                 | -100 |                  |     | mV   |

| Icc               |                                                     | Disabled, all inputs to ground                                                  |      |                  | 360 | μΑ   |

|                   | Quiescent current (average)                         | Enabled, AnP at 1 V and AnM at 1.4 V, t <sub>C</sub> = 15.38 ns                 |      | 80               |     |      |

|                   |                                                     | Enabled, $C_L = 8 \text{ pF}$ ,<br>Grayscale pattern , $t_C = 15.38 \text{ ns}$ |      | 100              |     | mA   |

|                   |                                                     | Enabled, $C_L = 8 \text{ pF}$ ,<br>Worst-case pattern, $t_C = 15.38 \text{ ns}$ |      | 120              |     |      |

| lіН               | High-level input current (SHTDN)                    | V <sub>IH</sub> = V <sub>CC</sub>                                               |      |                  | ±20 | μΑ   |

| IJЦ               | Low-level input current (SHTDN)                     | V <sub>IL</sub> = 0 V                                                           |      |                  | ±20 | μΑ   |

| I <sub>IN</sub>   | Input current (A inputs)                            | 0 V ≤ V <sub>I</sub> ≤ 2.4 V                                                    |      |                  | ±20 | μΑ   |

| loz               | High-impendance output current                      | $V_O = 0 \text{ V or } V_{CC}$                                                  |      |                  | ±10 | μΑ   |

# timing requirements

|                                 |                           | MIN  | TYP | MAX   | UNIT |

|---------------------------------|---------------------------|------|-----|-------|------|

| t <sub>C</sub> §                | Input clock period        | 14.7 |     | 31.25 | ns   |

| t <sub>su</sub> /t <sub>h</sub> | Input set up or hold time | 550  |     |       | ps   |

<sup>§</sup> t<sub>C</sub> is defined as the mean duration of a minimum of 32,000 clock periods.

# output buffer rating

|                                | MIN | TYP | MAX | UNIT |

|--------------------------------|-----|-----|-----|------|

| STV, SP                        |     | 4   |     | mA   |

| CLK, CLK                       |     | 8   |     | mA   |

| Data bus and remaining outputs |     | 4   |     | mA   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C. ‡ The algebraic convention, in which the less-positive (more-negative) limit is designated minimum, is used in this data sheet for the negative-going input voltage threshold only.

SLLS407 – FEBRUARY 2000

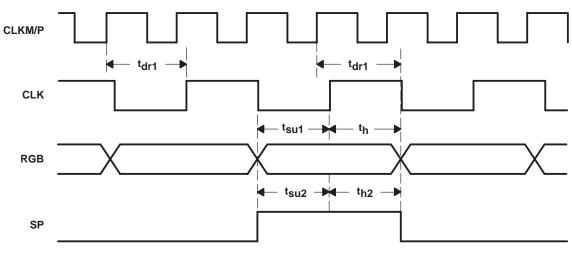

# switching characteristics

|                  | PARAMETER                                        | TEST CONDITIONS                                                                     | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| <sup>t</sup> dr1 | Input clock rising to output clock rising delay  | C <sub>L</sub> = 80 pF                                                              | 10  |     | 40  | ns   |

| <sup>t</sup> df1 | Input clock rising to output clock falling delay |                                                                                     | 10  |     | 40  | ns   |

| t <sub>su1</sub> | Data setup time, E/O RGB to CLK↑                 | C <sub>L</sub> = 80 pF                                                              | 10  |     | 20  | ns   |

| t <sub>h1</sub>  | Data hold time, CLK↑ to E/O RGB                  |                                                                                     | 10  |     | 20  | ns   |

| t(RSKM)          | Receiver input skew margin, See Note 1           | $t_C = 15.38 \text{ ns } (\pm 0.2\%),$<br> Input clock jitter   < 50 ps, See Note 2 | 550 | 700 |     | ps   |

| t <sub>en</sub>  | Enable time, SHTDN to phase lock                 |                                                                                     |     | 1   |     | ms   |

| <sup>t</sup> dis | Disable time, SHTDN to off state                 |                                                                                     |     | 250 |     | ns   |

| t <sub>su2</sub> | SP setup time                                    | C - 10 pF                                                                           | 10  |     | 20  | ns   |

| t <sub>h2</sub>  | SP pulse hold time                               | $C_{SP} = 10 \text{ pF}$                                                            | 10  |     | 20  | ns   |

- NOTES: 1.  $t_{RSKM}$  is the timing margin available to allocate to the transmitter and interconnection skews and clock jitter. The value of this parameter at clock periods other than 15.38 ns can be calculated from  $t_{RSKM} = \frac{t_c}{14}$ -300 ps.

- 2. |Input clock jitter| is the magnitude of the change in the input clock period.

## PARAMETER MEASUREMENT INFORMATION

Figure 1. Output Setup and Hold Time

## PARAMETER MEASUREMENT INFORMATION

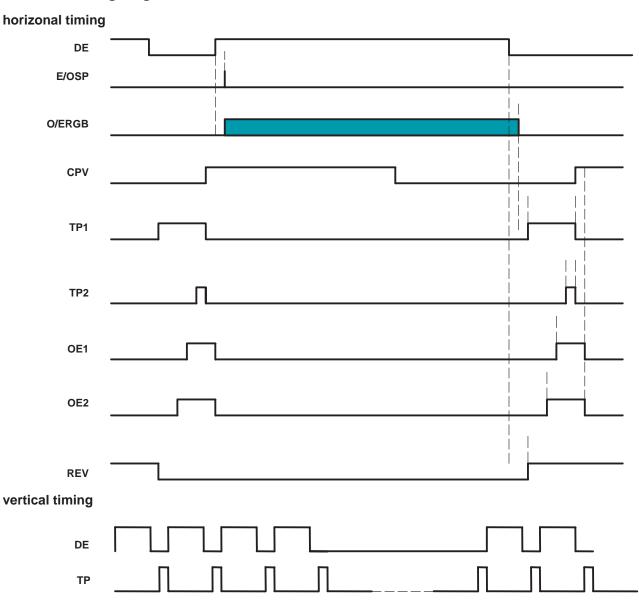

# reference timing diagrams

**Figure 2. Typical Output Waveform**

# SN75LVDS88B TFT LCD PANEL TIMING CONTROLLER WITH LVDS INTERFACE

SLLS407 - FEBRUARY 2000

#### PARAMETER MEASUREMENT INFORMATION

### functional description

#### **Flatlink**

The core of the Flatlink is TIs original 86A LVDS receiver, which has three data channels for the 18-bit color plus one clock channel.

### data alignment

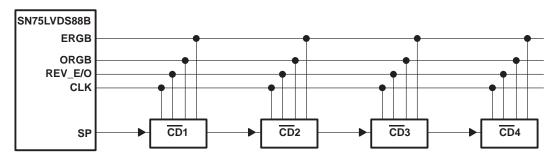

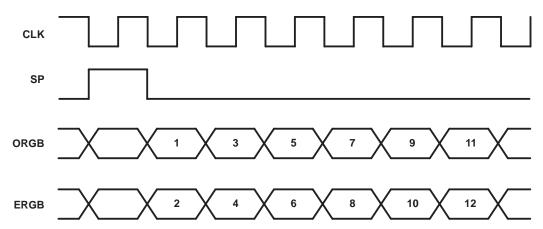

The data alignment block supports dual bus, dual port column driver configuration. When interfacing a 2-port column driver, the controller arranges pixels in odd and even order, then distributes them to odd and even buses and each connects to either of the driver ports. Under this setup, the controller outputs one clock, one or two data polarities (depends on driver), and one inverse ( support line inversion) signal to the drivers.

## output formatting

The output formatting provides several functions to reduce EMI, noise, and timing delay arrangement. These functions are controllable through some optional pins. See the registers and options section for reference.

#### Reverse Polarity Generation

When enabled this function generates polarity indication signals. This occurs when the number of transitions in the output data bus exceeds 18-bits compared to the previous output under normal polarity. The polarity signal will be active and the output will be the opposite polarity to reduce transition.

#### Line Inversion

When enabled, the REV\_O and REV\_E terminals will output the same line inversion control signals but in opposite polarities.

#### timing control

#### Horizontal Starting pulses

ESP and OSP terminals are used as the horizontal starting pulses output pins. Their outputs are one HCLK period ahead of the RGB data stream

#### Horizontal Clock

ECLK and OCLK terminals are responsible for the clock pulses, based on the XGA resolution when its frequency is at 32.5 MHz.

#### CD Data Latch Pulse

TP1 and TP2 provide the column driver input latch and output enable signals.

### Gate Driver Clock

The CPV terminal output the clock pulses to the gate drivers as the horizontal sync timing in its CRT counter part.

## Gate Driver Starting Pulse

The vertical starting pulse automatically generates at the start of every frame.

#### Gate Driver Output Enable

The OE1 and OE2 terminals provide the gate output enabale signals.

#### PARAMETER MEASUREMENT INFORMATION

## functional description (continued)

## vertical/horizontal reference generator

This block provides vertical and horizontal reference points for timing control. Vsync, Hsync, and ENAB signals, along with the auto detection function, determine when the video from the host is valid.

### power-up procedure

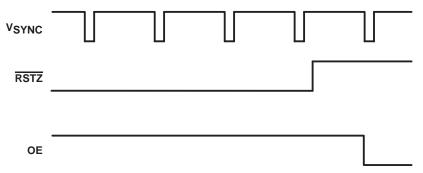

Due to the uncertainty of registers and counters in the driver, SN75LVDS88B combines the input from both reset and Vsync to blank the output and simultaneously resets the content of drivers (see Figure 3).

Figure 3. Reset Waveform

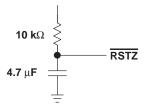

It is recommended that the following circuit be used to ensure the device is reset for more than 5 ms after power up.

## **APPLICATION INFORMATION**

Figure 4. Application Block Diagram

Figure 5. Data Output Format

SLLS407 – FEBRUARY 2000

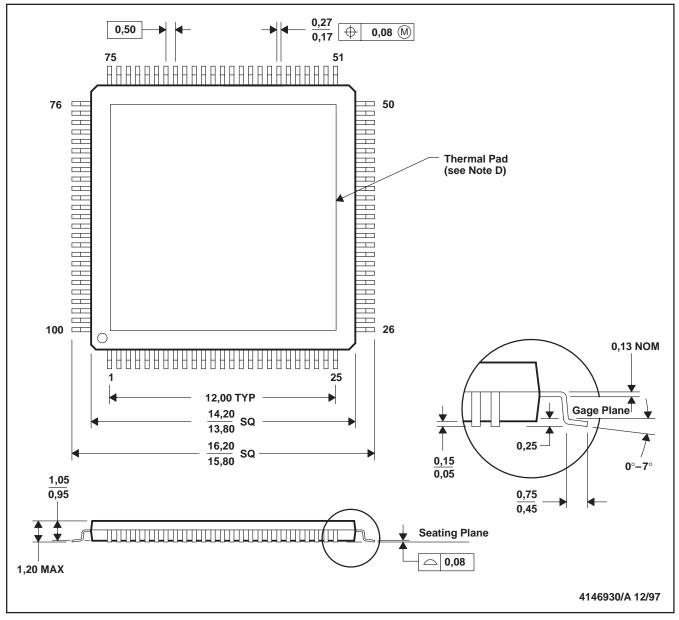

# **MECHANICAL DATA**

## PFD (S-PQFP-G100)

# PowerPAD™ PLASTIC QUAD FLATPACK (DIE DOWN)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. The package thermal performance may be enhanced by attaching an external heatsink to the thermal pad. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated