April 2012

## FSAR001 AC-DC Linear Regulator

#### **Features**

High Output Voltage Accuracy: 2%

Output Voltage: 5V

Low Ground Current: < 2.0mA</p>

Ultra-Fast Line and Load Transient Response

Hysteretic Thermal and Current-Limit Protections

Over-Voltage and Under-Voltage Protections

Ultra-Low Power Dissipation with No Load

Universal Input Range: 80~265V<sub>RMS</sub>

No Inductor Required

Low Components and Cost

## **Applications**

- Non-Isolation AC/DC Converter

- Home Appliance

## Description

FSAR001 is designed to replace capacitor-fed ("cap dropper") non-isolated power supplies, offering better high-power conversion performance and high-energy efficiency than a cap dropper solution. The appliance needs no inductor, uses few components, and offers lower cost.

FSAR001 integrates a 600V high-power device, startup controller, voltage control circuit, synchronous circuit, low dropout regulator, over-temperature protector, over-voltage protector, under-voltage protector, and current-limit circuit onto a monolithic IC.

## **Ordering Information**

| Part<br>Number | 3               |    | Maximum<br>Load | Package | Packing Method |

|----------------|-----------------|----|-----------------|---------|----------------|

| FSAR001BNY     | -40°C to +105°C | 5V | 35mA            | DIP-8   | Tube           |

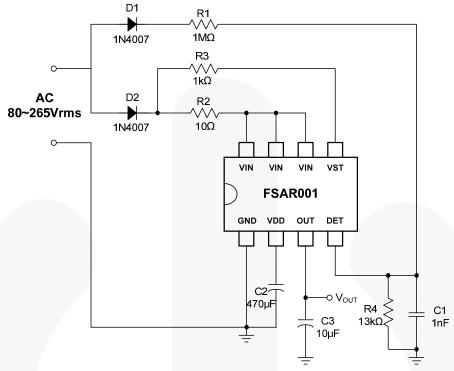

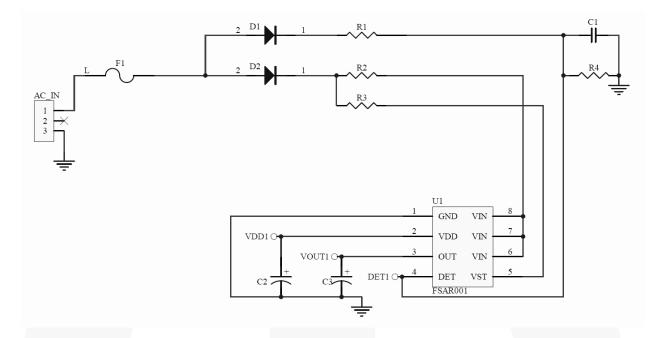

## **Application Diagram**

Figure 1. Typical Application

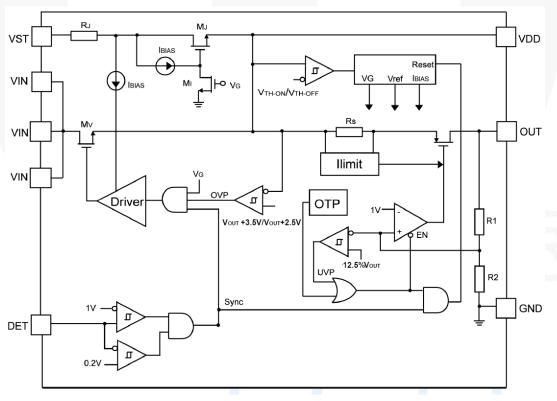

## **Internal Block Diagram**

Figure 2. Functional Block Diagram

## **Marking Information**

- F Fairchild Logo

- Z Plant Code

- X 1-Digit Year Code

- Y 1-Digit Week Code TT 2-Digit Die Run Code

- S: B: 5V V<sub>OUT</sub>

T: Package Type (N=DIP)

P Y: Green Package

- M Manufacture Flow Code

Figure 3. **Top Mark**

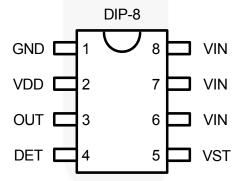

## **Pin Configuration**

Figure 4. **DIP-8 Pin Configuration**

## **Pin Definitions**

| Name | Pin# | Туре         | Description                                                                                                              |

|------|------|--------------|--------------------------------------------------------------------------------------------------------------------------|

| VDD  | 2    | Power Supply | Connect a 470µF external capacitor to ground for generated $V_{OUT}\text{+}2.5V\sim V_{OUT}\text{+}3.5V$ supply voltage. |

| GND  | 1    | Ground       | Ground                                                                                                                   |

| OUT  | 3    | Output       | Regulator output; fixed 5V output voltage                                                                                |

| DET  | 4    | Detect       | Sin waveforms input connection. Connects to full-bridge output and provides synchronous signal.                          |

| VST  | 5    | HV Start     | 500V power device startup connection.                                                                                    |

|      | 6    |              |                                                                                                                          |

| VIN  | 7    | 600V Input   | 600V power device input connection                                                                                       |

|      | 8    |              |                                                                                                                          |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                                                 | Min.                                                    | Max.             | Unit |      |

|------------------|---------------------------------------------------------------------------|---------------------------------------------------------|------------------|------|------|

| V <sub>IN</sub>  | Input Voltage of VIN Pin                                                  |                                                         |                  | 600  | V    |

| V <sub>ST</sub>  | Input Voltage of VST Pin                                                  |                                                         |                  | 500  | V    |

| $V_{DET}$        | Input Voltage of DET Pin                                                  |                                                         |                  | 7    | V    |

| V <sub>DD</sub>  | Input Voltage of VDD Pin                                                  |                                                         | 30               | V    |      |

| V <sub>OUT</sub> | Input Voltage of OUT Pin                                                  |                                                         | 30               | V    |      |

| P <sub>D</sub>   | Power Dissipation ( $T_A \le 50^{\circ}C$ )                               |                                                         |                  | 1.15 | W    |

| $\Theta_{JA}$    | Thermal Resistance (Junction to Air)                                      |                                                         |                  | 95   | °C/W |

| TJ               | Operating Junction Temperature                                            | -40                                                     | +125             | °C   |      |

| T <sub>STG</sub> | Storage Temperature Range                                                 | -55                                                     | +150             | °C   |      |

| TL               | Lead Temperature (Wave Soldering or IR, 10 Seconds)                       |                                                         |                  | 260  | °C   |

| ESD              | Human Body Model, JEDEC:JESD22-A114 All Pins Except HV Pin <sup>(3)</sup> |                                                         | n <sup>(3)</sup> | 6    | KV   |

| ESD              | Charged Device Model, JEDEC:JESD22-C101                                   | JEDEC:JESD22-C101 All Pins Except HV Pin <sup>(3)</sup> |                  | 2    | IVV  |

#### Notes:

- 1. All voltage values, except differential voltages, are given with respect to the network ground terminal.

- 2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

- 3. ESD with HV pin CDM=1000V and HBM=500V.

## **Recommended Operating Conditions**

| Symbol         | Parameter                     | Min. | Max. | Unit |

|----------------|-------------------------------|------|------|------|

| $V_{IN}$       | 600V High-Voltage Input       |      | 600  | V    |

| $V_{ST}$       | 500V High-Voltage Startup     |      | 500  | V    |

| T <sub>A</sub> | Operating Ambient Temperature | -40  | +105 | °C   |

#### Note:

4. For proper operation.

## **Electrical Characteristics**

$V_{IN}\text{-}open,\ V_{DD}\text{-}V_{OUT}\text{+}1\ V,\ C_{VDD}\text{-}470\ \mu\text{F}/\ 25\ V,\ C_{OUT}\text{-}10\ \mu\text{F}/\ 16\ V,\ I_{OUT}\text{-}1\ mA,\ T_{A}\text{-}25^{\circ}C,\ unless\ otherwise\ noted.}$

| Symbol                  | Parameter                                                                              | Conditions                                                 | Min.                  | Тур.                  | Max.                  | Uni<br>t |

|-------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------|

| VDD Section             | n                                                                                      |                                                            | 1                     | l                     |                       |          |

| $V_{\text{TH-ON}}$      | Turn-On Threshold Voltage (V <sub>OUT</sub> =5V)                                       | VDD Pin                                                    | 9                     | 10                    | 11                    | ٧        |

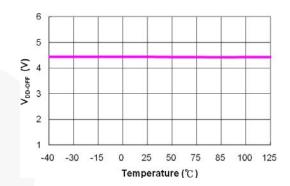

| $V_{\text{TH-OFF}}$     | Turn-off Voltage (V <sub>OUT</sub> =5V)                                                | VDD Pin                                                    | 3                     | 4                     | 5                     | V        |

| I <sub>DD-ST</sub>      | Startup Current of VDD Pin                                                             | VDD Pin                                                    |                       | 10                    | 30                    | μΑ       |

| I <sub>DD-OP</sub>      | Operating Supply Current                                                               | I <sub>OUT</sub> =1mA                                      | 1.0                   | 1.5                   | 2.0                   | mA       |

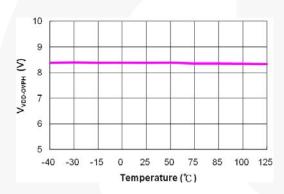

| $V_{\text{DD-OVP}}$     | Threshold of V <sub>DD</sub> OVP                                                       |                                                            | V <sub>OUT</sub> +3.0 | V <sub>OUT</sub> +3.5 | V <sub>OUT</sub> +4.0 | V        |

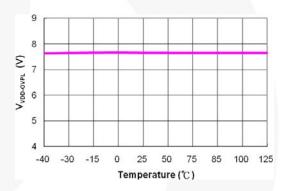

| $V_{\text{DD-OVPHYS}}$  | Threshold of V <sub>DD</sub> OVP Hysteresis                                            |                                                            | 0.8                   | 1.0                   | 1.2                   | V        |

| $tV_{DD-OVP}$           | Time Delay of V <sub>DD</sub> OVP                                                      |                                                            |                       | 1.5                   |                       | μs       |

| VIN Section             | 1                                                                                      |                                                            |                       |                       |                       |          |

| $V_{VIN}$               | Supply Voltage                                                                         |                                                            |                       |                       | 600                   | V        |

| <b>VST Sectio</b>       | n                                                                                      |                                                            |                       |                       |                       |          |

| I <sub>ST</sub>         | Supply Current from VST Pin                                                            | $V_{AC}$ =90V ( $V_{DC}$ =120V), $V_{DD}$ =10 $\mu$ F      | 2.50                  | 3.75                  | 5.00                  | mA       |

| I <sub>ST-LC</sub>      | Supply Current After Startup                                                           | $HV=500V$ , $V_{DD}=V_{DD-}$<br>OFF+1V                     |                       | 1                     | 20                    | μΑ       |

| <b>DET Sectio</b>       | n                                                                                      |                                                            |                       |                       |                       |          |

| $V_{DET\_MAX}$          | Turn-Off Synchronous Voltage                                                           |                                                            | 0.90                  | 0.95                  | 1.00                  | V        |

| V <sub>DET_MAXHYS</sub> | Turn-Off Synchronous Voltage Hy                                                        | 0.08                                                       | 0.10                  | 0.12                  | V                     |          |

| $V_{DET\_MIN}$          | Turn-On Synchronous Voltage                                                            |                                                            | 0.08                  | 0.14                  | 0.20                  | V        |

| V <sub>DET MINHYS</sub> | Turn-Off Synchronous Voltage Hysteresis                                                |                                                            | 0.08                  | 0.14                  | 0.20                  | V        |

| I <sub>DET</sub>        | DET Current                                                                            |                                                            |                       | 0.1                   |                       | μΑ       |

| VOUT Secti              | ion                                                                                    |                                                            | <u>I</u>              |                       |                       |          |

| UVP <sub>Vout</sub>     | Output Pin Under-Voltage Protecti                                                      | -10.0                                                      | -12.5                 | -15.0                 | %                     |          |

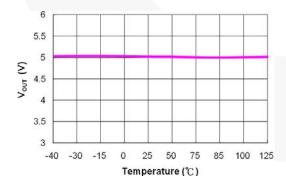

| V <sub>ACC</sub>        | Output Voltage Accuracy                                                                |                                                            | -2                    |                       | 2                     | %        |

| LR                      | Load Regulation                                                                        | I <sub>OUT</sub> =1mA to Maximum                           | -2                    |                       | 2                     | %        |

| ΔV <sub>OUT (VIN)</sub> | Line Regulation dV <sub>OUT</sub> /dV <sub>IN</sub>                                    |                                                            | -0.2                  |                       | 0.2                   | %/V      |

| ILIM                    | Current Limit                                                                          | V <sub>DD</sub> =V <sub>OUT</sub> +3V                      | 110                   | 140                   | 170                   | mA       |

| $V_{Drop}$              | Dropout Voltage (V <sub>OUT</sub> =5V)                                                 | I <sub>OUT</sub> =35mA                                     | 0.3                   | 0.4                   | 0.5                   | V        |

| I <sub>G</sub>          | Ground Pin Current <sup>(5)</sup>                                                      | Output Current = Maximum Load                              |                       | 1.5                   | 2.0                   | mA       |

| tD <sub>OUT-ST</sub>    | Output Voltage Rising Time (V <sub>OUT</sub> =12V) V <sub>DD</sub> to V <sub>OUT</sub> | V <sub>OUT</sub> =0%~90%<br>C <sub>OUT</sub> =1µF          | 40                    | 50                    | 60                    | μs       |

| PSRR                    | Ripple Rejection <sup>(6)</sup>                                                        | f= 50Hz, C <sub>OUT</sub> =10μF,<br>I <sub>OUT</sub> =35mA |                       | 60                    |                       | dB       |

| . 5141                  | f =100Hz, C <sub>OUT</sub> =<br>I <sub>OUT</sub> =35mA                                 |                                                            |                       |                       |                       |          |

| $T_{OTP}$               |                                                                                        | Protection Junction Temperature <sup>(6)</sup>             |                       | 150                   |                       | °C       |

| $T_{HYS}$               | Restart Junction Temperature <sup>(6)</sup>                                            |                                                            |                       | T <sub>OTP</sub> -40  |                       | °C       |

## Notes:

- 5. For  $V_{Drop}$ =1V of  $V_{OUT}$ =3.3V version, the test condition is modified to  $V_{DD}$ = $V_{OUT}$ +1.5V.

- 6. Guaranteed by design.

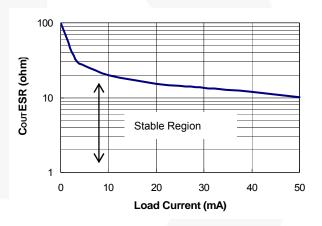

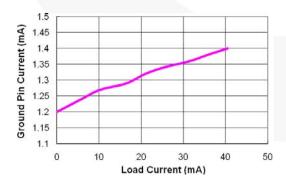

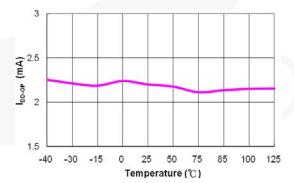

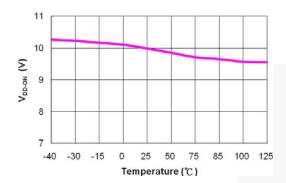

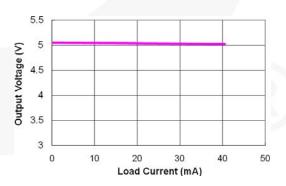

## **Typical Performance Characteristics**

$V_{\text{AC}} = 264\text{V}/50\text{Hz}, \ V_{\text{OUT}} = 5\text{V}, \ I_{\text{OUT}} = 35\text{mA} \sim 40\text{mA}, \ C_{\text{VDD}} = 470\mu\text{F}, \ C_{\text{OUT}} = 10\mu\text{F}, \ T_{\text{A}} = 25^{\circ}\text{C}, \ \text{unless otherwise noted}.$

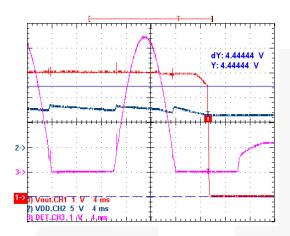

Figure 5. V<sub>OUT</sub> Pin Under-Voltage Protection

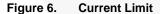

Figure 7. Load Transient

Figure 8. Region of Stable C<sub>OUT</sub> ESR vs. Load Curre

Figure 9. Ground Pin Current vs. Load Current

Figure 10. Operating Supply Current vs. Temperature

## **Typical Performance Characteristics** (Continued)

Figure 11. Turn-On Threshold Voltage vs. Temperature

Figure 12. Turn-Off Threshold Voltage vs. Temperature

Figure 13. Threshold of  $V_{DD}$  OVP HIGH vs. Temperature

Figure 14. Threshold of V<sub>DD</sub> OVP LOW vs. Temperature

Figure 15. Output Voltage vs. Temperature

Figure 16. Output Voltage vs. Output Load

### **Functional Description**

The FSAR001 is a compact, inductor-free, and highly monolithic AC/DC linear converter housed in 8-lead DIP packages and designed for non-isolated AC/DC converter and home appliances. The FSAR001 provides universal AC voltage input from  $80V_{RMS}$  to  $265V_{RMS}$  and fixed-DC output voltage with current limiter for the non-isolated AC/DC converter operating safety and stability. The FSAR001 integrates many protection functions, including output current limiter ( $I_{LIMIT}$ ), output undervoltage protection (UVP), over-temperature protector (OTP),  $V_{DD}$  over-voltage protection (OVP), and AC synchronous signal detect function ( $V_{DET}$ ).

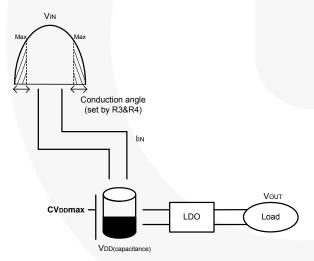

As the FSAR001 operates in a typical application, the startup current flows through the startup pin (V<sub>ST</sub>) and charges V<sub>DD</sub> capacitor. When the voltage of V<sub>DD</sub> is larger than V<sub>TH ON</sub>, the FSAR001 is turned on. After one AC synchronous signal, the LDO is turned on and creates output voltage (V<sub>OUT</sub>). At steady state, the energy of V<sub>DD</sub> capacitor decreases because of the chip operation and load power dissipation. The behavior is shown in Figure 17 and the energy is recharged during conduction angle interval (settled by R3 and R4) and under OVP function limitation (V<sub>DD-OVPH</sub>). With a view to increasing LDO efficiency and system stability, FSAR001 sets the V<sub>DD</sub> OVP voltage at 8.5V for 5V LDO regulator. The  $V_{\text{DD}}$ capacitor recovery angle controls below  $50V_{\text{RMS}}$  settled by AC synchronous signal (DET sense voltage), detailed in the following sections.

Figure 17. Operating Principle

#### **Startup Current**

During FSAR001 startup, the startup current through the rectifier and  $V_{\text{ST}}$  pin charges the  $V_{\text{DD}}$  capacitor with maximum start current of  $V_{\text{ST}}$  pin of 3.75mA and the synchronous current controlled by R3 (1M $\Omega$ ) and R4 (13k $\Omega$ ), shown in Figure 1. The FSAR001 remains off until the  $V_{\text{DD}}$  voltage is larger than  $V_{\text{TH-ON}}$  and the output voltage is created at the same time. After the FSAR001 turns on, the  $V_{\text{ST}}$  function is disabled by the control loop. The major energy path changes from  $V_{\text{ST}}$  pin from the inner power MOSFET MV ( $V_{\text{IN}}$ ).

#### **OUT Pin Under-Voltage Protection**

When the output power is larger than the maximum handling power of FSAR001, the condition causes the output voltage to drop. Until the output voltage is less than output nominal voltage -12% (5V - 0.625V = 4.375V), the UVP function disables the LDO stage and waits until the next AC synchronous signal to restart the FSAR001 automatically.

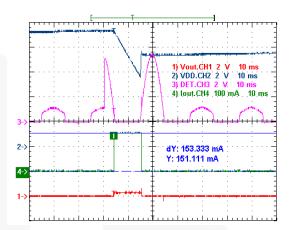

#### **Current Limit**

The FSAR001 includes a current limiter (ILIMIT) for safe LDO operation. The limiter monitors the loading current and directly controls the output delivery current of LDO. The typical limited current set is 140mA to avoid the output shorted to ground for an indefinite amount of time without damaging the part. At over-current operation, the I<sub>LIMIT</sub> function limits the maximum output current and causes the unregulated output voltage to drop until the UVP function occurs.

#### **Over-Temperature Protection**

The FSAR001 operates in highly converting ratio. The thermal energy of FSAR001 is generated by the inner converting power of the MOSFET. When the junction temperature ( $T_J$ ) exceeds 150°C, the OTP function disables LDO stage and waits for the next AC synchronous signal to restart. The over-temperature hysteresis range is 40°C. After startup, the OTP function monitors the junction temperature. When junction temperature decreases to the ( $T_{OTP-THYS}$ ), the OTP function enables the signal and allows LDO turn on. If not, OTP function keeps the output function disabled and continuously monitors the junction temperature. The OTP function is designed to protect against abnormal conditions and over-power operation.

#### **DET Pin Selection**

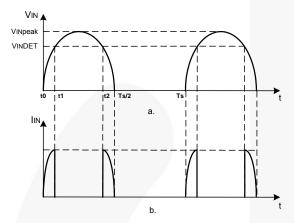

The DET pin connects to the commutated AC bus. It sinks commutated AC voltage waveform used to provide the AC synchronous signal and to set the V<sub>DD</sub> capacitor recovery conduction angle. For synchronous signal function, the AC synchronous signal used to enable output voltage of the LDO and to trigger the output stage protection with UVP and OTP. To limit the recoveryconduction angle of the  $V_{\text{\tiny DD}}$  capacitor, the DET pin sense voltage ( $V_{DET}$ ) is set between 0.14V ~0.95V. During the sense-voltage range of the DET pin, the V<sub>DD</sub> capacitor can be charged by the power MOSFET until the OVP function is operating in every synchronous cycle. As shown in Figure 18, the DET pin sense voltage limits the charge time of t0~t1 and t2~ts/2 settled by R3 and R4. The maximum commutated input voltage of FSAR001 can be determined by the following equation with the maximum DET sense voltage defined:

### Functional Description (Continued)

$$V_{DET,max} = \frac{R4}{R3 + R4} \times V_{ac}$$

$$V_{DET,min} = \frac{R4}{R3 + R4} \times V_{ac}$$

EQ 1

Figure 18. Typical Waveforms

#### **VDD Pin Over-Voltage Protection**

After startup, FSAR001 turns on the OVP function. During conduction angle interval, the  $V_{\text{DD}}$  voltage has two kinds of behavior. One is that if the  $V_{\text{DD}}$  capacitor recharges to OVP trigger point (8.5V for 5V version), the FSAR001 turns off the power MOSFET to limit the maximum  $V_{\text{DD}}$  voltage. The other is that if the voltage of  $V_{\text{DD}}$  cannot recharge to the OVP level during the conduction interval, the power MOSFET is turned off by AC synchronous signal and continuously recharges  $V_{\text{DD}}$  capacitor at next duration. Using this technique, energy is drawn from the AC mains only during the low-voltage portions of each positive half cycle, reducing the

dissipation in the first stage. During the power MOSFET turn-on, the current provided by the commutated AC voltage is used to supply the loads and to charge the  $V_{DD}$  capacitor. In this way, when the power MOSFET switches off, the loads receive the required currents by the capacitor discharge. For this reason, it is important to properly set the conduction angle.

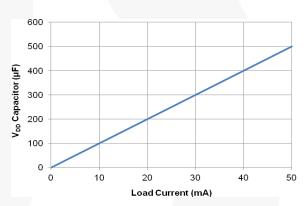

For the  $V_{DD}$  capacitor selection, during conduction angle interval; the energy is drawn from commutated AC bus, which not only provides the output requirement but also recharges the  $V_{DD}$  capacitor to OVP level. Outside of conduction angle, the  $V_{DD}$  capacitor supplies the whole system requirement. The  $V_{DD}$  capacitor can be reduced by maximum loading power. The capacitor is evaluated by Equation 2; the selection chart is shown in Figure 19.

$$C_{VDD} = \frac{I_{LOAD} \times 10m}{1}, (unit = F)$$

EQ 2

Figure 19. V<sub>DD</sub> Capacitor vs. Output Current

## **Applications Information**

Figure 20. Application Circuit

## **Bill of Materials (BOM)**

| Designator | Part Type    | Designator | Part Type |

|------------|--------------|------------|-----------|

| F1         | FUSE 3A/250V | D2         | 1N4007    |

| C1         | 1nF/50V      | R1         | 1MΩ 1/4W  |

| C2         | 470μF/25V    | R2         | 10Ω 2W    |

| C3         | 10μF/50V     | R3         | 1KΩ 1/2W  |

| D1         | 1N4007       | R4         | 13KΩ 1/4W |

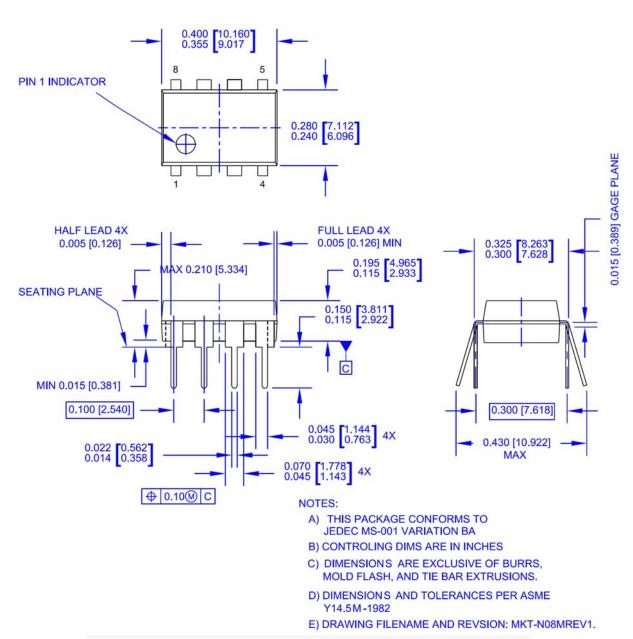

# Physical Dimensions

Figure 21. 8-Pin, DIP-8 Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™ AccuPower™ AX-CAP™\* BitSiC™ Build it Now™ CorePLUS™ CorePOWER™

CROSSVOLT™ CTL™ Current Transfer Logic™ DEUXPEED<sup>1</sup>

Dual Cool™ EcoSPARK® EfficientMax™ ESBC™ F

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT FAST® FastvCore™ FETBench™

FlashWriter®\* FPSTW

F-PFS™ FRFET®

Global Power Resource<sup>SM</sup> GreenBridge™

Green FPS™ Green FPS™ e-Series™ Gmax™

GTO\*\* IntelliMAX™ ISOPLANAR™

Making Small Speakers Sound Louder

and Better MegaBuck™ MICROCOUPLER™ MicroFET\*\* MicroPak™ MicroPak2™ Miller Drive™

Motion Max™ Motion-SPM™ mWSaver™ OntoHiT™ OPTOLOGIC® OPTOPLANAR® PowerTrench® PowerXS™

Programmable Active Droop™

**QFET** QSTM Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise<sup>T</sup> SmartMax™ SMART START™

Solutions for Your Success™

SPM® STEALTH™ SuperFET<sup>®</sup> SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET\*\* Sync-Lock™ SYSTEM GENERAL®\* The Power Franchise®

wer franchis TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinvPWM™ TinyWire™ Tran SiC™

TriFault Detect™

TRUECURRENT®\*

UHC Ultra FRFET™ UniFET™ VCX™ VisualMax™ VoltagePlus™

XST

μSerDes™

Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Deliminon of Terms       |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.  The datasheet is for reference information only.                                                   |

**Rev 161**