### **General Description**

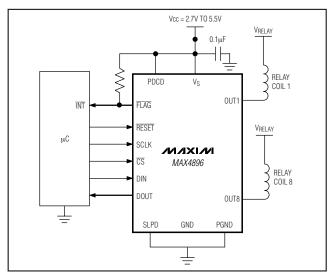

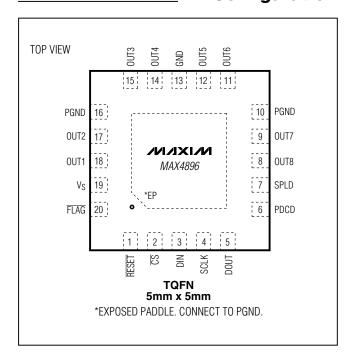

The MAX4896 8-channel relay and load driver is designed for medium voltage applications up to 50V. This device is offered in a 20-pin, 5mm x 5mm TQFN package, resulting in substantial board space savings.

The MAX4896 8-channel relay driver offers built-in inductive kickback protection, drive for latching/ nonlatching or dual-coil relays, and open-load and short-circuit fault detection. The MAX4896 also protects against overcurrent conditions. Each independent open-drain output features a  $3\Omega$  (typ) on-resistance, and is guaranteed to sink 200mA of load current  $(V_S \ge 4.5V)$ .

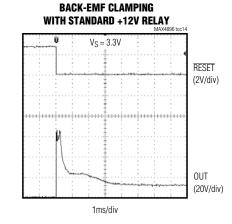

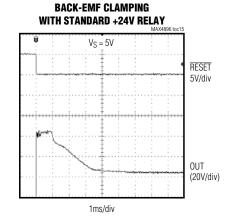

A built-in overvoltage protection clamp handles kickback-voltage transients, which are common when driving inductive loads. Thermal-shutdown circuitry shuts off all outputs (OUT\_) when the junction temperature exceeds +160°C. The MAX4896 employs a reset input that allows the user to turn off all outputs simultaneously with a single control line.

The MAX4896 includes a 10MHz SPI™-/QSPI™-/ MICROWIRE™-compatible serial interface. The serial interface is compatible with TTL-/CMOS-logic voltage levels and operates with a single +2.7V to +5.5V supply. In addition, the SPI output data can be used for diagnostics purposes including open-load and shortcircuit fault detection.

The MAX4896 is offered in the extended (-40°C to +85°C) and automotive (-40°C to +125°C) operating temperature ranges.

## Typical Operating Circuit

Pin Configuration appears at end of data sheet.

### Features

- ♦ Supports Up to 50V Continuous Drain-to-Source Voltage

- **♦** Guaranteed Drive Current:

- ♦ Vs ≥ 4.5V 200mA (All Channels On) 410mA (Individual Channels)

- Vs ≤ 3.6V 100mA

- ♦ Built-In Output Clamp Protects Against Inductive **Kickback**

- ♦ +2.7V to +5.5V Logic Supply Voltage

- **♦ RESET Input Turns Off All Outputs** Simultaneously

- ♦ Built-in Power-On Reset

- ♦ Automotive Temperature Range (-40°C to +125°C)

- ♦ SPI-/QSPI-/MICROWIRE-Compatible Serial

- ♦ Serial Digital Output for Daisy Chaining and **Diagnostics**

- ♦ FLAG Output for μP Interrupt

- ♦ Open-Load and Short-Circuit Detection and **Protection**

- Thermal Shutdown

- ♦ Low 100µA (max) Quiescent Supply Current

- ♦ Space-Saving, 5mm x 5mm, 20-Pin TQFN Package

### **Applications**

Industrial Equipment

Automotive Relay Control

White Goods

**ATE**

Power-Grid Monitoring and Protection Equipment

## **Ordering Information**

| PART        | TEMP<br>RANGE      | PIN-<br>PACKAGE        | PACKAGE<br>CODE |

|-------------|--------------------|------------------------|-----------------|

| MAX4896ETP  | -40°C to<br>+85°C  | 20 TQFN<br>(5mm x 5mm) | T2055-5         |

| MAX4896ATP* | -40°C to<br>+125°C | 20 TQFN<br>(5mm x 5mm) | T2055-5         |

<sup>\*</sup>Future product—contact factory for availability.

SPI and QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)       |                        |

|-----------------------------------------|------------------------|

| V <sub>S</sub>                          | 0.3V to +7.0V          |

| OUT                                     | (-0.3V to +50V)        |

| Continuous OUT_ Voltage                 |                        |

| CS, SCLK, DIN, RESET, SPLD, PDCD        | 0.3V to +7.0V          |

| DOUT                                    | 0.3V to $(V_S + 0.3V)$ |

| PGND to GND                             | (-0.3V to +0.3V)       |

| Continuous OUT_ Current, TA = +25°C (No | ote 1)                 |

| All Outputs On                          | 210mA                  |

| Single Output On                        | 420mA                  |

|                                         |                        |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 20-Pin TQFN (derate 21.3mW/°C above +70°C)1702mW      |

| θJA+47°C/W                                            |

| Maximum Output Clamp Energy (EOUT_)30mJ               |

| Operating Temperature Range40°C to +125°C             |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

|                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 1:** Maximum continuous current at a given temperature must be calculated such that the maximum continuous power dissipation for the package is not exceeded.

### **ELECTRICAL CHARACTERISTICS**

$(V_S = +2.7 V \text{ to } +5.5 V, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_{A=} +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                            | SYMBOL                                | CONDITI                                                                                  | ONS                 | MIN | TYP  | MAX | UNITS |  |

|--------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------|---------------------|-----|------|-----|-------|--|

| Operating Voltage                    | Vs                                    |                                                                                          |                     | 2.7 |      | 5.5 | V     |  |

| Quiescent Current                    | loo                                   | I <sub>OUT</sub> = 0, logic inputs                                                       | $=$ $V_S = 3.6V$    |     | 5    | 70  |       |  |

| Quiescent Current                    | Icc                                   | 0 or $V_S$ , $\overline{RESET} = low$                                                    | V <sub>S</sub> = 5V |     | 10   | 100 | μΑ    |  |

| Dynamic Average Supply<br>Current    | IS                                    | $S_{SCLK} = 10MHz$ , $f_{DIN} = 0.5 \times f_{CLK}$ ,<br>$C_{OUT} = 50pF$ , $V_S = 5.5V$ |                     |     |      | 6   | mA    |  |

| Thermal Shutdown                     | T <sub>SHD</sub>                      |                                                                                          |                     |     | +160 |     | °C    |  |

| Thermal-Shutdown Hysteresis          | TSHDH                                 |                                                                                          |                     |     | 20   |     | °C    |  |

| Power-On Reset                       | V <sub>RST</sub>                      | V <sub>S</sub> falling                                                                   |                     | 1.8 | 2.05 | 2.3 | V     |  |

| Power-On-Reset Hysteresis            | V <sub>RSTH</sub>                     |                                                                                          |                     |     | 140  |     | mV    |  |

| DIGITAL INPUTS (SCLK, DIN,           | CS, RESET,                            | PDCD, SPLD)                                                                              |                     |     |      |     |       |  |

| Input Logic-High Voltage             | \/                                    | V <sub>S</sub> = 2.7V to 3.6V                                                            |                     | 2.0 |      |     | V     |  |

|                                      | V <sub>IH</sub>                       | V <sub>S</sub> = 4.5V to 5.5V                                                            |                     | 2.4 |      |     | V     |  |

| land the sign bout Valtages          | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | $V_S = 2.7V \text{ to } 3.6V$                                                            |                     |     |      | 0.6 | V     |  |

| Input Logic-Low Voltage              | VIL                                   | V <sub>S</sub> = 4.5V to 5.5V                                                            |                     |     |      | 0.8 | V     |  |

| Input Logic Hysteresis               | V <sub>H</sub> YST                    |                                                                                          |                     |     | 230  |     | mV    |  |

| Input Leakage Currents               | ILEAK                                 | Input voltages = 0 or +5                                                                 | 5.5V                | -1  |      | +1  | μΑ    |  |

| Input Capacitance                    | CIN                                   |                                                                                          |                     |     | 10   |     | рF    |  |

| RELAY OUTPUT DRIVERS (O              | UT1–OUT8)                             |                                                                                          |                     |     |      |     |       |  |

|                                      |                                       | T                                                                                        | J = +25°C           |     | 5    | 6   |       |  |

|                                      |                                       | $I_{OUT} = 50$ mA,<br>$V_{S} = 2.7$ V                                                    | J = +125°C          |     |      | 11  |       |  |

| OLIT ON Posistance                   | Dov                                   |                                                                                          | J = +150°C          |     |      | 12  | Ω     |  |

| OUT_ ON Resistance                   | Ron                                   |                                                                                          | J = +25°C           |     | 3    | 4   |       |  |

|                                      |                                       | $I_{OUT} = 100 \text{mA},$<br>$V_{S} = 4.5 \text{V}$                                     | J = +125°C          |     |      | 7   |       |  |

|                                      |                                       | T                                                                                        | J = +150°C          |     |      | 8   |       |  |

| I <sub>OUT</sub> Off-Leakage Current | ILEAK                                 | PDCD = high or RESET off                                                                 | = low, all outputs  | -1  |      | +1  | μΑ    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_S = +2.7 V \text{ to } +5.5 V, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                            | SYMBOL                 | CONDITIONS                                                                                                                                                                            | MIN      | TYP | MAX  | UNITS |  |

|------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|------|-------|--|

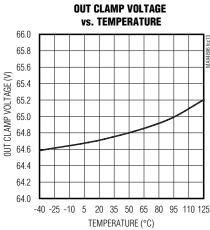

| OUT Clamping Voltage                                 | VCLAMP                 | (Note 3)                                                                                                                                                                              | 50       |     | 75   | V     |  |

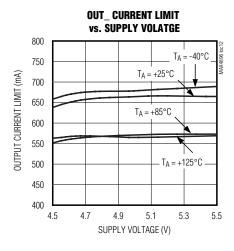

| OUT Current-Limit Threshold                          | I <sub>LIM</sub>       | V <sub>S</sub> ≥ 4.5V                                                                                                                                                                 | 400      |     | 960  | mA    |  |

| OUT Capacitance                                      |                        | $V_{OUT} = 16V, f = 1MHz$                                                                                                                                                             |          | 30  |      | pF    |  |

| DIAGNOSTIC                                           |                        |                                                                                                                                                                                       |          |     |      |       |  |

| Open-Load Detection Voltage<br>Threshold             | V <sub>DS(OL)</sub>    | OUT_ falling                                                                                                                                                                          | 0.75     | 1   | 1.15 | V     |  |

| Open-Load Detection-Voltage-<br>Threshold Hysteresis | V <sub>DS</sub> (OLH)  |                                                                                                                                                                                       |          | 40  |      | mV    |  |

| OUT_ Pulldown Current                                | IPD(OL)                | PDCD = low                                                                                                                                                                            | 150      | 300 | 500  | μΑ    |  |

| Fault Delay/Filtering Time                           | t <sub>D</sub> (FAULT) | From rising edge at $\overline{\text{CS}}$ at 50% to valid diagnostic data                                                                                                            | 30       | 90  | 280  | μs    |  |

| DIGITAL OUTPUT (DOUT, FLA                            | G)                     |                                                                                                                                                                                       | •        |     |      |       |  |

| DOUT Low Voltage                                     | Voi                    | 2.7V ≤ V <sub>S</sub> ≤ 3.6V, I <sub>SINK</sub> = 0.3mA                                                                                                                               |          |     |      | V     |  |

| DOOT Low voitage                                     | VoL                    | 4.5V ≤ V <sub>S</sub> ≤ 5.5V, I <sub>SINK</sub> = 0.5mA                                                                                                                               | 0.4      |     |      | V     |  |

| DOUT High Voltage                                    | Vall                   | 2.7V ≤ V <sub>S</sub> ≤ 3.6V, I <sub>SOURCE</sub> = 0.25mA V <sub>S</sub> - 0                                                                                                         |          |     |      | V     |  |

| DOUT High Voltage                                    | VoH                    | $4.5V \le V_S \le 5.5V$ , $I_{SOURCE} = 0.4mA$                                                                                                                                        | Vs - 0.5 |     |      | V     |  |

| FLAG Low Voltage                                     |                        | I <sub>SINK</sub> = 0.5mA                                                                                                                                                             |          |     | 0.4  | V     |  |

| FLAG Off-Leakage Current                             |                        | 4.5V ≤ V <sub>S</sub> ≤ 5.5V, V <sub>FLAG</sub> = 5.5V                                                                                                                                | -1       |     | +1   | μΑ    |  |

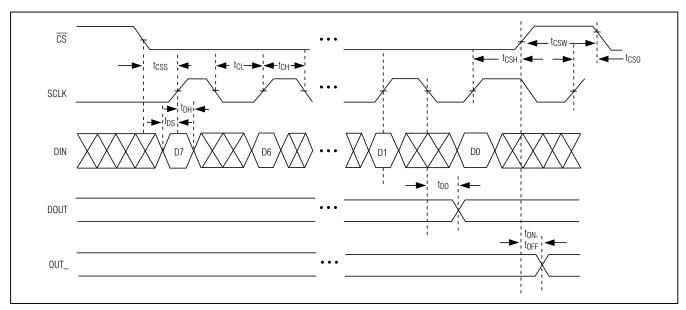

| TIMING                                               |                        |                                                                                                                                                                                       |          |     |      |       |  |

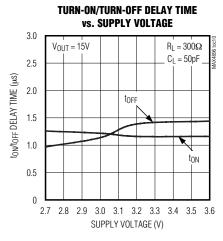

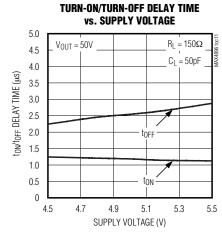

| T O. Tiere (OUT.)                                    |                        | From rising edge of $\overline{\text{CS}}$ at 50% to V <sub>OUT</sub> = 90%VP, VP = 15V, R <sub>L</sub> = 300 $\Omega$ , C <sub>L</sub> = 50pF, 2.7V $\leq$ V <sub>S</sub> $<$ 3.6V   |          |     | 20   |       |  |

| Turn-On Time (OUT_)                                  | ton                    | From rising edge of $\overline{\text{CS}}$ at 50% to V <sub>OUT</sub> = 90%VP, VP =16V, R <sub>L</sub> = 150 $\Omega$ , C <sub>L</sub> = 50pF, 4.5V $\leq$ V <sub>S</sub> $\leq$ 5.5V |          | 10  |      | μs    |  |

| Turn Off Time (OLIT.)                                | to                     | From rising edge of $\overline{\text{CS}}$ at 50% to V <sub>OUT</sub> = 10%VP, VP = 15V, R <sub>L</sub> = 300 $\Omega$ , C <sub>L</sub> = 50pF, 2.7V $\leq$ V <sub>S</sub> $<$ 3.6V   |          |     | 15   |       |  |

| Turn-Off Time (OUT_)                                 | tOFF                   | From rising edge of $\overline{\text{CS}}$ at 50% to V <sub>OUT</sub> = 90%VP, VP = 16V, R <sub>L</sub> = 150 $\Omega$ , C <sub>L</sub> = 50pF, 4.5V < V <sub>S</sub> $\leq$ 5.5V     |          |     | 10   | μs    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_S = +2.7 V \text{ to } +5.5 V, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                  | SYMBOL          | CONI                                                                            | MIN                          | TYP | MAX | UNITS |         |  |

|----------------------------|-----------------|---------------------------------------------------------------------------------|------------------------------|-----|-----|-------|---------|--|

|                            |                 | T050C                                                                           | 2.7V ≤ V <sub>S</sub> < 3.6V | 0   |     | 6     |         |  |

| CCLI/ Fraguenay            | f               | $T_A = +85^{\circ}C$                                                            | $4.5V \le V_S \le 5.5V$      |     |     | 11    | N AL I— |  |

| SCLK Frequency             | fsclk           | T .1050C                                                                        | 2.7V ≤ V <sub>S</sub> ≤ 3.6V | 0   |     | 5     | MHz     |  |

|                            |                 | $T_A = +125^{\circ}C$                                                           | $4.5V \le V_S \le 5.5V$      |     |     | 10    |         |  |

| Cycle Time                 | tour tou        | $2.7V \le V_S \le 3.6V$                                                         |                              | 200 |     |       | 20      |  |

| Cycle Time                 | tch + tcl       | $4.5V \le V_S \le 5.5V$                                                         |                              | 100 |     |       | ns      |  |

| CS Fall-to-SCLK Rise Setup | tono            | $2.7V \le V_S \le 3.6V$                                                         |                              | 100 |     |       | no      |  |

| C3 Fail-10-30LK hise 3etup | tcss            | $4.5V \le V_S \le 5.5V$                                                         |                              | 50  |     |       | ns      |  |

| CS Rise-to-SCLK Hold       | toou            | $2.7V \le V_S \le 3.6V$                                                         |                              | 100 |     |       | 20      |  |

| CS RISE-10-SCLN HOID       | tcsh            | $4.5V \le V_S \le 5.5V$                                                         |                              | 50  |     |       | ns      |  |

| CCLI/ High Time            | tou             | $2.7V \le V_S \le 3.6V$                                                         |                              | 80  |     |       | 20      |  |

| SCLK High Time             | tCH             | $4.5V \le V_S \le 5.5V$                                                         |                              | 40  |     |       | ns      |  |

| SCLK Low Time              | +01             | $2.7V \le V_S \le 3.6V$                                                         | 80                           |     |     |       |         |  |

|                            | tCL             | $4.5V \le V_S \le 5.5V$                                                         | 40                           |     |     | ns    |         |  |

| Data Catura Tima           | 1               | $2.7V \le V_S \le 3.6V$                                                         | 40                           |     |     |       |         |  |

| Data Setup Time            | t <sub>DS</sub> | $4.5V \le V_S \le 5.5V$                                                         |                              | 20  |     |       | ns      |  |

| Data Hald Time             | 4               | $2.7V \le V_S \le 3.6V$                                                         |                              | 5   |     |       |         |  |

| Data Hold Time             | tDH             | $4.5V \le V_S \le 5.5V$                                                         |                              | 0   |     |       | ns      |  |

| SCLK Fall-to-DOUT Valid    | +==             | 50% of SCLK to<br>20% of V <sub>S</sub> falling<br>edge, C <sub>L</sub> = 50pF, | $2.7V \le V_S \le 3.6V$      |     |     | 70    | 20      |  |

| SCEN Fall-10-DOOT Valld    | tDO             | 50% at SCLK to<br>80% of Vs rising<br>edge                                      | $4.5V \le V_{S} \le 5.5V$    |     |     | 30    | ns      |  |

| Rise Time (DIN, SCLK, CS,  |                 | 20% of V <sub>S</sub> to 70%                                                    | $2.7V \le V_S \le 3.6V$      |     |     | 2     |         |  |

| RESET)                     | tscr            | of $V_S$ , $C_L = 50pF$<br>(Note 4)                                             | 4.5V ≤ V <sub>S</sub> ≤ 5.5V |     |     | 2     | μs      |  |

| Fall Time (DIN, SCLK, CS,  |                 | 20% of V <sub>S</sub> to 70%                                                    | $2.7V \le V_S \le 3.6V$      |     |     | 2     |         |  |

| RESET)                     | tscf            | of $V_S$ , $C_L = 50pF$<br>(Note 4)                                             | $4.5V \le V_S \le 5.5V$      |     |     | 2     | μs      |  |

| RESET Min Pulse Width      | t <sub>RW</sub> |                                                                                 |                              | 70  |     |       | ns      |  |

**Note 2:** Specifications at -40°C are guaranteed by design and not production tested.

**Note 3:** The output stages are compliant with the transient immunity requirements, as specified in ISO 7637 Part 3 with test pulses 1, 2, 3a, and 3b.

Note 4: Guaranteed by design.

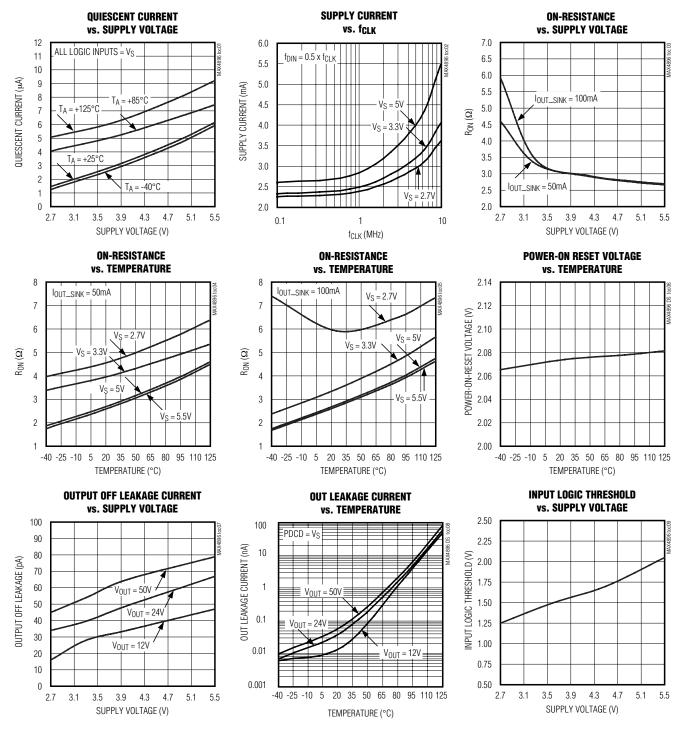

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Pin Description

| PIN    | NAME  | FUNCTION                                                                                                                                                                                                                                                           |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | RESET | Reset Input. Drive RESET low to clear all latches and registers (all outputs are turned off). All OUT pulldown currents are disabled when RESET = low.                                                                                                             |

| 2      | CS    | Chip Select Input. Drive $\overline{CS}$ low to select the device. When $\overline{CS}$ is low, data at DIN is clocked into the 8-bit shift register on SCLK's rising edge. Drive $\overline{CS}$ from low to high to latch the data to the registers.             |

| 3      | DIN   | Serial Data Input                                                                                                                                                                                                                                                  |

| 4      | SCLK  | Serial Clock Input                                                                                                                                                                                                                                                 |

| 5      | DOUT  | Serial Data Output. DOUT is the output of the 8-bit shift register. This output can be used to daisy chain multiple MAX4896s. The data at DOUT appears synchronous to SCLK's falling edge.                                                                         |

| 6      | PDCD  | Pulldown Current Disable. Drive PDCD high to disable OUT's pulldown current source. Drive PDCD low to enable OUT_ pulldown current source. PDCD must be low to detect an open-load fault.                                                                          |

| 7      | SPLD  | Short-Protection Latch-Off Disable Input. Drive SPLD high to disable the built-in short-circuit protection latch-off feature. When SPLD is low, an overloaded channel is turned off immediately. See the Output Short-Circuit/Current-Limiting Protection section. |

| 8      | OUT8  | Open-Drain Output 8. Connect OUT8 to the low side of a relay coil. OUT8 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 9      | OUT7  | Open-Drain Output 7. Connect OUT7 to the low side of a relay coil. OUT7 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 10, 16 | PGND  | Power Ground. PGND is the ground return path for the output sinks. Connect PGND pins together and to GND.                                                                                                                                                          |

| 11     | OUT6  | Open-Drain Output 6. Connect OUT6 to the low side of a relay coil. OUT6 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 12     | OUT5  | Open-Drain Output 5. Connect OUT5 to the low side of a relay coil. OUT5 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 13     | GND   | Ground                                                                                                                                                                                                                                                             |

| 14     | OUT4  | Open-Drain Output 4. Connect OUT4 to the low side of a relay coil. OUT4 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 15     | OUT3  | Open-Drain Output 3. Connect OUT3 to the low side of a relay coil. OUT3 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 17     | OUT2  | Open-Drain Output 2. Connect OUT2 to the low side of a relay coil. OUT2 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 18     | OUT1  | Open-Drain Output 1. Connect OUT1 to the low side of a relay coil. OUT1 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                          |

| 19     | Vs    | Input Supply Voltage. Bypass V <sub>S</sub> to GND with a 0.1µF capacitor.                                                                                                                                                                                         |

| 20     | FLAG  | Open-Drain Fault Output. FLAG asserts low when a fault occurs at OUT1-OUT8.                                                                                                                                                                                        |

|        | EP    | Exposed Paddle. Connect EP to ground plane.                                                                                                                                                                                                                        |

|        |       |                                                                                                                                                                                                                                                                    |

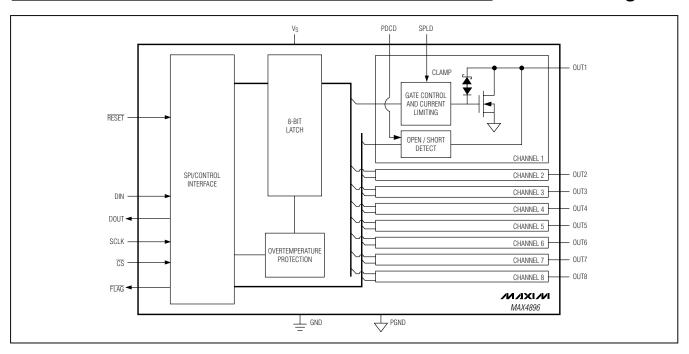

### **Detail Description**

The MAX4896 is an 8-channel relay and load driver for medium voltage applications up to 50V. The MAX4896 features built-in inductive kickback protection, drive for latching/nonlatching, or dual-coil relays and an internal register for detecting open-load and short-circuit faults. Each independent open-drain output features a 3 $\Omega$  onresistance and is guaranteed to sink 400mA at V<sub>S</sub>  $\geq$  4.5V, and 100mA at V<sub>S</sub>  $\leq$  3.6V.

The MAX4896 also incorporates a logic input (PDCD) that allows the device to continue operating when an overcurrent condition lasts longer than the 280µs (max) fault delay time. A built-in overvoltage protection clamp handles kickback voltage transients, which are common when driving inductive loads. Thermal-shutdown circuitry shuts off all outputs (OUT\_) when the junction temperature exceeds +160°C.

The MAX4896 employs a reset input that allows the user to turn off all outputs simultaneously with a single control line.

The MAX4896 includes a 10MHz SPI-/QSPI-/MICROWIRE-compatible serial interface. The serial interface is compatible with TTL-/CMOS-logic voltage levels and operates with a single +2.7V to +5.5V supply.

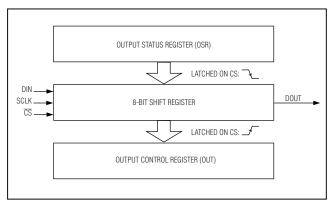

#### Serial Interface

The serial interface consists of an 8-bit input shift register, a parallel latch (output control register) controlled by SCLK and  $\overline{CS}$ , and an output status register containing diagnostics information. The input to the shift register is an 8-bit word. Each data bit controls one of the eight outputs, with the most significant bit (D7) corresponding to OUT8, and the least significant bit (D0) corresponding to OUT1 (see Table 1). When  $\overline{CS}$  is low, data at DIN is clocked into the shift register synchronously with SCLK's rising edge. Driving  $\overline{CS}$  from low to

Figure 1. Serial Interface

high latches the data in the shift register to the output control register.

DOUT is the output of the internal output status register for diagnostics purposes (see Figure 2 and Tables 2 and 3). Status data for each channel is transferred to the shift register at the falling edge of  $\overline{\text{CS}}$ . The data bits contained in the shift register are then transferred to the DOUT output synchronously with SCLK's falling edge.

While  $\overline{CS}$  is low, the <u>switches</u> always remain in their previous states. Drive  $\overline{CS}$  high after 8 bits of data have been shifted in to update the output state, and to further inhibit data from entering the shift register. When  $\overline{CS}$  is high, transitions at DIN and SCLK have no effect on the output, and the first input bit (D7) is present at DOUT.

If the number of data bits entered while  $\overline{CS}$  is low is greater or less than 8, the shift register contains only the last 8 data bits, regardless of when they were entered.

The 3-wire serial interface is compatible with SPI, QSPI, and MICROWIRE standards. The latch that drives the analog output stages is updated on the rising edge of  $\overline{\text{CS}}$ , regardless of SCLK's state.

### **Diagnostic Information**

The MAX4896 contains an internal output status register used for diagnostics information for each output (see Tables 1, 2, and 3). When a fault condition is detected at any channel for longer than the minimum fault-filtering time (tD(FAULT)\_min), the fault information is latched into the corresponding position in the output status register (see Table 2), and the FLAG asserts. Status/diagnostics data for each channel in the output status register is transferred to the output shift register at the falling edge of CS. While CS is low, the diagnostics bits are then transferred to DOUT synchronously with SCLK's falling edge. A rising edge at CS resets the output status register data. During normal operation, the output status bit is the same as the DIN bit (DO1 = D1, DO2 = D2). When the MAX4896 is operating with a fault condition, the output status bit is the inverse of the DIN bit (DO1 = 0, D1 = 1).

**Table 1. Serial-Input Address**

| DIN  | D0   | D1   | D2   | D3   | D4   | D5   | D6   | D7   |

|------|------|------|------|------|------|------|------|------|

| OUT_ | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8 |

## **Table 2. Serial-Output Address**

| DOUT | DO0  | DO1  | DO2  | DO3  | DO4  | DO5  | DO6  | D07  |

|------|------|------|------|------|------|------|------|------|

| OUT_ | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8 |

**Table 3. Status-Register Output Diagnostic**

| OUTPUT<br>STATUS | DO_<br>STATUS BIT | DIAGNOSTIC                                               |

|------------------|-------------------|----------------------------------------------------------|

| Off              | Low               | Normal operation.                                        |

| Off              | High              | Fault condtion. Output open or short circuit.            |

| On               | Low               | Fault condition. Short circuit to positive load voltage. |

| On               | High              | Normal operation.                                        |

Figure 2. 3-Wire Serial-Interface Timing

The minimum fault-filtering time helps mask short-duration fault conditions, such as driving highly capacitive loads.

The typical diagnostics software routine works as follows:

- Write data to the MAX4896

- Wait for tD(FAULT) maximum to ensure diagnostics data is ready and valid

- Write same data to the MAX4896 and read out the diagnostics data from the shift register

Use Table 3 to diagnose the output state.

To reduce processor overhead, an interrupt-based diagnostics routine is possible. The diagnostics routine will analyze diagnostics data only when the FLAG output triggers an interrupt.

### Output Short-Circuit/Current-Limiting Protection

The MAX4896 channels (OUT\_) are protected against short-circuits conditions. When the channel's output current exceeds the current-limit threshold (ILIM) for longer than the minimum fault-filtering time (tD(FAULT) min), the short-circuit protection is activated. The short-circuit protection behavior is determined by the logic level at SPLD. When SPLD = high, an overloaded channel remains in a current-limited state until the short-circuit condition is removed or thermal shutdown is reached. This allows the operation of loads where the inrush currents may exceed the MAX4896 internal current limit.

When SPLD = low, an overloaded channel immediately turns off (latched-off). When a shorted output is latched off, the channel can be turned back on after the next serial input data is latched into the MAX4896.

#### Open-Load Detection

The MAX4896 features an output pulldown current source, along with a voltage comparator, to detect an open-load fault condition. To enable the open-load detection function, PDCD must be low. The voltage at OUT\_ is compared with the diagnostics threshold voltage (VDS(OL)) to determine whether a open-load fault condition exists.

#### **Thermal Shutdown**

If the junction temperature exceeds  $+160^{\circ}$ C, all outputs are switched off immediately (no filtering time) and  $\overline{\text{FLAG}}$  asserts. The hysteresis is approximately  $+20^{\circ}$ C, disabling thermal shutdown once the temperature drops below  $+140^{\circ}$ C.

#### RESET

The MAX4896 features an asynchronous reset input that allows the user to simultaneously turn all outputs off using a single control line. Drive RESET low to clear all latches and registers, and to turn off all outputs. While RESET is low, the OUT pulldown currents are disabled, regardless of the state of PDCD.

### **FLAG** Output

$\overline{\text{FLAG}}$  is an open-drain latched output that can be connected to a  $\mu P$  interrupt and pulls low whenever a fault condition (short-circuit and/or open-load) is detected in any of the eight outputs for longer than the minimum fault-filtering time (tD(FAULT) min). FLAG asserts immediately, (no filtering time), when a thermal-shutdown fault condition is detected. The latch  $\overline{\text{FLAG}}$  deasserts on  $\overline{\text{CS}}$  rising edge.

## \_Applications Information

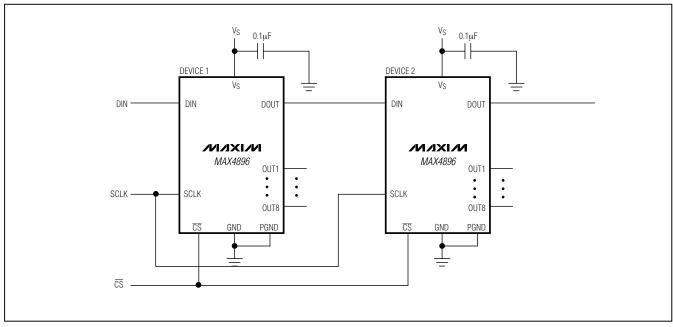

### **Daisy Chaining**

The MAX4896 features a digital output (DOUT) that provides a simple way to daisy chain multiple devices. This feature allows the user to drive large banks of relays using only a single serial interface. To daisy chain multiple devices, connect all  $\overline{\text{CS}}$  inputs together and connect the DOUT of one device to the DIN of another device (see Figure 3). During operation, a stream of serial data is shifted through all the MAX4896s in series.

### **Inductive Kickback Protection**

Each output features an output protection clamp, limiting the OUT voltage to 65V (typ). The clamp protects against voltage transient when driving inductive loads.

Figure 3. Daisy-Chain Configuration

## **Functional Diagram**

## Pin Configuration

\_Chip Information

PROCESS: BICMOS

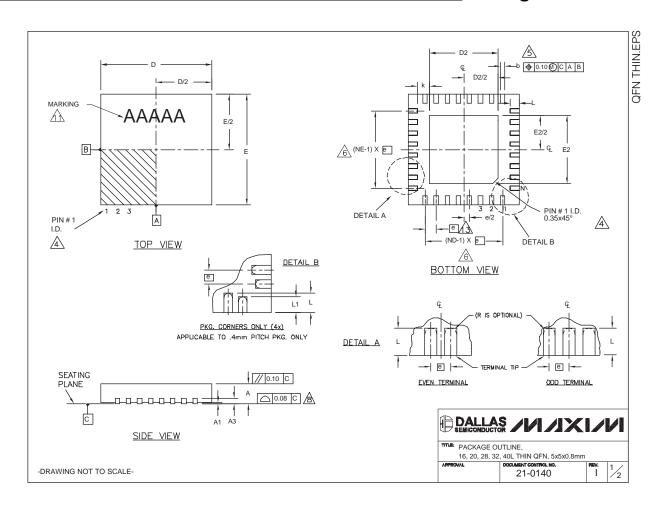

### **Package Information**

### Package Information (continued)

|        | COMMON DIMENSIONS |        |      |           |       |               |        |       |               |       |        |               |         |       |      |

|--------|-------------------|--------|------|-----------|-------|---------------|--------|-------|---------------|-------|--------|---------------|---------|-------|------|

| PKG.   | 1                 | 6L 5x  | 5    | 2         | OL 5> | <b>&lt;</b> 5 | 2      | 8L 5> | <b>&lt;</b> 5 | 3     | 32L 5> | <b>&lt;</b> 5 | 40L 5x5 |       | (5   |

| SYMBOL | MIN.              | NOM.   | MAX. | MIN.      | NOM.  | MAX.          | MIN.   | NOM.  | MAX.          | MIN.  | NOM.   | MAX.          | MIN.    | NOM.  | MAX. |

| Α      | 0.70              | 0.75   | 0.80 | 0.70      | 0.75  | 0.80          | 0.70   | 0.75  | 0.80          | 0.70  | 0.75   | 0.80          | 0.70    | 0.75  | 0.80 |

| A1     | 0                 | 0.02   | 0.05 | 0         | 0.02  | 0.05          | 0      | 0.02  | 0.05          | 0     | 0.02   | 0.05          | 0       | 0.02  | 0.05 |

| A3     | 0.                | 20 RE  | F.   | 0.        | 20 RE | F.            | 0.     | 20 RE | F.            | 0.    | 20 RE  | F.            | 0.      | 20 RE | F.   |

| b      | 0.25              | 0.30   | 0.35 | 0.25      | 0.30  | 0.35          | 0.20   | 0.25  | 0.30          | 0.20  | 0.25   | 0.30          | 0.15    | 0.20  | 0.25 |

| D      | 4.90              | 5.00   | 5.10 | 4.90      | 5.00  | 5.10          | 4.90   | 5.00  | 5.10          | 4.90  | 5.00   | 5.10          | 4.90    | 5.00  | 5.10 |

| E      | 4.90              | 5.00   | 5.10 | 4.90      | 5.00  | 5.10          | 4.90   | 5.00  | 5.10          | 4.90  | 5.00   | 5.10          | 4.90    | 5.00  | 5.10 |

| е      | 0                 | .80 BS | SC.  | 0.65 BSC. |       | 0             | .50 BS | SC.   | 0             | .50 B | SC.    | 0             | .40 B   | SC.   |      |

| k      | 0.25              | -      | -    | 0.25      | -     | -             | 0.25   | -     | -             | 0.25  | -      | -             | 0.25    | 0.35  | 0.45 |

| L      | 0.30              | 0.40   | 0.50 | 0.45      | 0.55  | 0.65          | 0.45   | 0.55  | 0.65          | 0.30  | 0.40   | 0.50          | 0.40    | 0.50  | 0.60 |

| L1     | -                 | -      | -    | -         | -     | -             | -      | -     | -             | -     | -      | -             | 0.30    | 0.40  | 0.50 |

| N      |                   | 16 20  |      |           |       | 28            |        | 32    |               |       | 40     |               |         |       |      |

| ND     | 4                 |        |      | 5         |       |               | 7      |       | 8             |       |        | 10            |         |       |      |

| NE     |                   | 4      |      |           | 5     |               |        | 7     |               | 8     |        |               | 10      |       |      |

| JEDEC  |                   | WHHE   | 3    | -         | WHH   | 0             | WHHD-1 |       |               | Ιv    | VHHD   | 1-2           |         |       |      |

| N١ | 0 | т | ⊏ | C |  |

|----|---|---|---|---|--|

|    |   |   |   |   |  |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

A THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

⚠ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

M AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

▲ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR T2855-3 AND T2855-6.

WARPAGE SHALL NOT EXCEED 0.10 mm.

11. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

12. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |      |      |      |              |      |      |            |         |  |  |

|------------------------|------|------|------|--------------|------|------|------------|---------|--|--|

| PKG.                   | D2   |      |      | E2           |      |      | exceptions | DOWN    |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN.         | NOM. | MAX. | ±0.15      | ALLOWED |  |  |

| T1655-2                | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | YES     |  |  |

| T1655-3                | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | NO      |  |  |

| T1655N-1               | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | NO      |  |  |

| T2055-3                | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | YES     |  |  |

| T2055-4                | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | NO      |  |  |

| T2055-5                | 3.15 | 3.25 | 3.35 | 3.15         | 3.25 | 3.35 | 0.40       | YES     |  |  |

| T2855-3                | 3.15 | 3.25 | 3.35 | 3.15         | 3.25 | 3.35 | **         | YES     |  |  |

| T2855-4                | 2.60 | 2.70 | 2.80 | 2.60         | 2.70 | 2.80 | **         | YES     |  |  |

| T2855-5                | 2.60 | 2.70 | 2.80 | 2.60         | 2.70 | 2.80 | **         | NO      |  |  |

| T2855-6                | 3.15 | 3.25 | 3.35 | 3.15         | 3.25 | 3.35 | **         | NO      |  |  |

| T2855-7                | 2.60 | 2.70 | 2.80 | 2.60         | 2.70 | 2.80 | **         | YES     |  |  |

| T2855-8                | 3.15 | 3.25 | 3.35 | 3.15         | 3.25 | 3.35 | 0.40       | YES     |  |  |

| T2855N-1               | 3.15 | 3.25 | 3.35 | 3.15         | 3.25 | 3.35 | **         | NO      |  |  |

| T3255-3                | 3.00 | 3.10 | 3.20 | <b>3</b> .00 | 3.10 | 3.20 | **         | YES     |  |  |

| T3255-4                | 3.00 | 3.10 | 3.20 | <b>3</b> .00 | 3.10 | 3.20 | **         | NO      |  |  |

| T3255-5                | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | YES     |  |  |

| T3255N-1               | 3.00 | 3.10 | 3.20 | 3.00         | 3.10 | 3.20 | **         | NO      |  |  |

| T4055-1                | 3.20 | 3.30 | 3.40 | 3.20         | 3.30 | 3.40 | **         | YES     |  |  |

\*\* SEE COMMON DIMENSIONS TABLE

PACKAGE OUTLINE, 16, 20, 28, 32, 40L THIN QFN, 5x5x0.8mm

21-0140

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

SITE SEARCH SEARCH

WHAT'S NEW PRODUCTS SOLUTIONS

DESIGN

APPNOTES SUPPORT

BUY

COMPANY

**MEMBERS**

### **MAX4896**

### **Part Number Table**

#### Notes:

- 1. See the MAX4896 QuickView Data Sheet for further information on this product family or download the MAX4896 full data sheet (PDF, 212kB).

- 2. Other options and links for purchasing parts are listed at: http://www.maxim-ic.com/sales.

- 3. Didn't Find What You Need? Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; + = RoHS/lead-free; # = RoHS/lead-exempt. More: See full data sheet or Part Naming Conventions.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number  | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE DRAWING CODE/VAR *                                          | Temp            | RoHS/Lead-Free?<br>Materials Analysis   |

|--------------|----------------|---------------|-------------------------------------------------------------------------------------|-----------------|-----------------------------------------|

| MAX4896ATP+T |                | Buy           | THIN QFN;20 pin;5x5x0.8mm<br>Dwg: 21-0140K (PDF)<br>Use pkgcode/variation: T2055+5* | -40°C to +125°C | RoHS/Lead-Free: Yes Materials Analysis  |

| MAX4896ATP+  | Sample         | Buy           | THIN QFN;20 pin;5x5x0.8mm<br>Dwg: 21-0140K (PDF)<br>Use pkgcode/variation: T2055+5* | -40°C to +125°C | RoHS/Lead-Free: Yes Materials Analysis  |

| MAX4896ETP+  | Sample         | Buy           | THIN QFN;20 pin;5x5x0.8mm<br>Dwg: 21-0140K (PDF)<br>Use pkgcode/variation: T2055+5* | -40°C to +85°C  | RoHS/Lead-Free: Yes  Materials Analysis |

| MAX4896ETP+T |                | Buy           | THIN QFN;20 pin;5x5x0.8mm<br>Dwg: 21-0140K (PDF)<br>Use pkgcode/variation: T2055+5* | -40°C to +85°C  | RoHS/Lead-Free: Yes Materials Analysis  |

Didn't Find What You Need?

Copyright © 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy