National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

MH6321 300 mA High Speed Buffer with Adjustable Current Limit

# LMH6321 300 mA High Speed Buffer with Adjustable Current Limit

## **General Description**

The LMH6321 is a high speed unity gain buffer that slews at 1800 V/µs and has a small signal bandwidth of 110 MHz while driving a 50 $\Omega$  load. It can drive ±300 mA continuously and will not oscillate while driving large capacitive loads.

The LMH6321 features an adjustable current limit. The current limit is continuously adjustable from 10 mA to 300 ma with a ±5 mA ±5% accuracy. The current limit is set by adjusting an external reference current with a resistor. The current can be easily and instantly adjusted, as needed by connecting the resistor to a DAC to form the reference current. The sourcing and sinking currents share the same current limit.

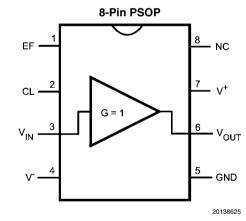

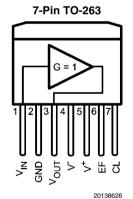

The LMH6321 is available in a space saving 8-pin PSOP or a 7-pin TO-263 power package. The PSOP package features an exposed pad on the bottom of the package to increase its heat sinking capability. The LMH6321 can be used within the feedback loop of an operational amplifier to boost the current output or as a stand alone buffer.

### **Features**

- 1800 V/µs High slew rate Wide bandwidth 110 MHz Continuous output current ±300 mA ±5 mA ±5% Output current limit tolerance Wide supply voltage range 5V to ±15V -40°C to +125°C

- Wide temperature range

- Adjustable current limit

- High capacitive load drive

- Thermal shutdown error flag

## **Applications**

- Line driver

- -Pin driver

- Sonar driver

- Motor control

Note: V- pin is connected to tab on back of each package

**Connection Diagrams**

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 2)                    |                  |

|-------------------------------------------|------------------|

| Human Body Model                          | 2.5 kV           |

| Machine Model                             | 250V             |

| Supply Voltage                            | 36V (±18V)       |

| Input to Output Voltage (Note 3)          | ±5V              |

| Input Voltage                             | $\pm V_{SUPPLY}$ |

| Output Short-Circuit to GND (Note 4)      | Continuous       |

| Storage Temperature Range                 | -65°C to +150°C  |

| Junction Temperature (T <sub>JMAX</sub> ) | +150°C           |

| Lead Temperature                          |                  |

| (Soldering, 10 seconds)               | 260°C           |

|---------------------------------------|-----------------|

| Power Dissipation                     | (Note 8)        |

| C <sub>L</sub> Pin to GND Voltage     | ±1.2V           |

| <b>Operating Ratings</b>              |                 |

| Operating Temperature Range           | -40°C to +125°C |

| Operating Supply Range                | 5V to ±16V      |

| Thermal Resistance $(\theta_{JA})$ ,  |                 |

| PSOP Package (Note 6)                 | 180°C/W         |

| Thermal Resistance (θ <sub>JC</sub> ) |                 |

| TO-263 Package                        | 4°C/W           |

| Thermal Resistance (θ <sub>JA</sub> ) |                 |

| TO-263 Package                        | 80°C/W          |

# ±15V Electrical Characteristics

The following specifications apply for Supply Voltage = ±15V,  $V_{CM} = 0$ ,  $R_L \ge 100 \text{ k}\Omega$  and  $R_S = 50\Omega$ ,  $C_L$  open, unless otherwise noted. **Boldface** limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol           | Parameter                    | Condition                                                                                | IS                                           | Min                 | Тур   | Max                   | Units |  |

|------------------|------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|---------------------|-------|-----------------------|-------|--|

| A <sub>V</sub>   | Voltage Gain                 | $R_L = 1 \ k\Omega, \ V_{IN} = \pm 10V$                                                  |                                              | 0.99<br><b>0.98</b> | 0.995 |                       | V/V   |  |

|                  |                              | $R_L = 50\Omega, V_{IN} = \pm 10V$                                                       |                                              | 0.86<br><b>0.84</b> | 0.92  |                       | V/V   |  |

| V <sub>OS</sub>  | Input Offset Voltage         | $R_L = 1 k\Omega, R_S = 0V$                                                              |                                              |                     | ±4    | ±35<br><b>±52</b>     | mV    |  |

| I <sub>B</sub>   | Input Bias Current           | $V_{IN} = 0V, R_L = 1 \ k\Omega, R_S =$                                                  | 0V                                           |                     | ±2    | ±15<br><b>±17</b>     | μA    |  |

| R. <sub>IN</sub> | Input Resistance             | R. <sub>L</sub> = 50Ω                                                                    |                                              |                     | 250   |                       | kΩ    |  |

| C <sub>IN</sub>  | Input Capacitance            |                                                                                          |                                              |                     | 3.5   |                       | pF    |  |

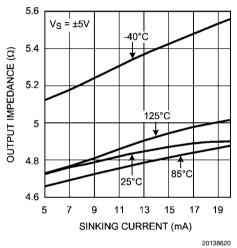

| R <sub>o</sub>   | Output Resistance            | $I_0 = \pm 10 \text{ mA}$                                                                |                                              |                     | 5     |                       | Ω     |  |

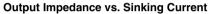

| I <sub>S</sub>   | Power Supply Current         | $R_L = \infty, V_{IN} = 0$                                                               |                                              |                     | 11    | 14.5<br><b>16.5</b>   | mA    |  |

|                  |                              |                                                                                          | 750 μA into<br>C <sub>L</sub> Pin            |                     | 14.9  | 18.5<br><b>20.5</b>   |       |  |

| V <sub>O</sub> 1 | Positive Output Swing        | $I_{O} = 300 \text{ mA}, \text{ R}_{S} = 0 \text{V}, \text{ V}_{IN}$                     | $=\pm V_S$                                   | 11.2<br><b>10.8</b> | 11.9  |                       |       |  |

|                  | Negative Output Swing        | $I_0 = 300 \text{ mA}, \text{ R}_S = 0 \text{V}, \text{ V}_{\text{IN}} = \pm \text{V}_S$ |                                              |                     | -11.3 | -10.3<br><b>-9.8</b>  | V     |  |

| V <sub>O</sub> 2 | Positive Output Swing        | $R_L = 1 \text{ k}\Omega, R_S = 0V, V_{IN} = \pm V_S$                                    |                                              | 13.1<br><b>12.9</b> | 13.4  |                       |       |  |

|                  | Negative Output Swing        | $R_L = 1 \text{ k}\Omega, R_S = 0V, V_{IN} =$                                            | ±V <sub>S</sub>                              |                     | -13.4 | -12.9<br><b>-12.6</b> | V     |  |

| V <sub>O</sub> 3 | Positive Output Swing        | $R_L = 50\Omega, R_S = 0V, V_{IN} = 1$                                                   | ±V <sub>S</sub>                              | 11.6<br><b>11.2</b> | 12.2  |                       |       |  |

|                  | Negative Output Swing        | $R_L$ = 50 $\Omega$ , $R_S$ = 0V, $V_{IN}$ =                                             | $R_L = 50\Omega, R_S = 0V, V_{IN} = \pm V_S$ |                     | -11.9 | -10.9<br><b>-10.6</b> | V     |  |

| V <sub>EF</sub>  | Error Flag Output Voltage    | $R_{L} = \infty, V_{IN} = 0,$                                                            | Normal                                       |                     | 5.00  |                       |       |  |

|                  |                              | EF pulled up with 5 k $\Omega$ to +5V                                                    | During<br>Thermal<br>Shutdown                |                     | 0.25  |                       | V     |  |

| Т <sub>SH</sub>  | Thermal Shutdown Temperature | Measure Quantity is Die (Junction)<br>Temperature                                        |                                              |                     | 168   |                       | °C    |  |

|                  |                              | Hysteresis                                                                               |                                              |                     | 10    |                       |       |  |

| Symbol            | Parameter                                    | Conditions                                                            |                                   | Min                 | Тур  | Max               | Units  |  |

|-------------------|----------------------------------------------|-----------------------------------------------------------------------|-----------------------------------|---------------------|------|-------------------|--------|--|

| I <sub>SH</sub>   | Supply Current at Thermal Shutdown           | EF pulled up with 5 k $\Omega$ to +5V                                 |                                   |                     | 3    |                   | mA     |  |

| PSSR              | Power Supply Rejection Ratio                 | $R_L = 1 k\Omega, V_{IN} = 0V,$<br>V <sub>S</sub> = ±5V to ±15V       | Positive                          | 58<br><b>54</b>     | 66   |                   | 5      |  |

|                   |                                              | 5                                                                     | Negative                          | 58<br><b>54</b>     | 64   |                   | - dB   |  |

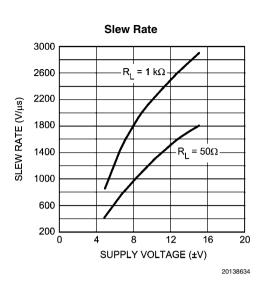

| SR                | Slew Rate                                    | $V_{IN} = \pm 11V, R_L = 1 k\Omega$                                   | e.                                |                     | 2900 |                   |        |  |

|                   |                                              | $V_{IN} = \pm 11V, R_{L} = 50\Omega$                                  |                                   |                     | 1800 |                   | - V/μs |  |

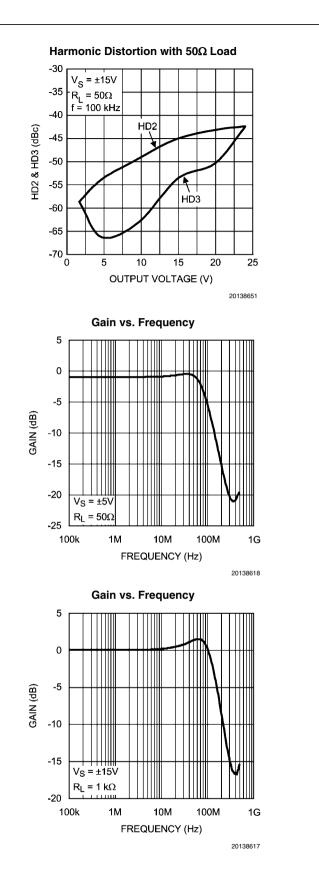

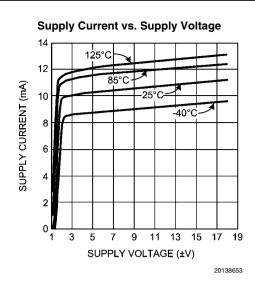

| BW                | -3 dB Bandwidth                              | $V_{IN} = \pm 20 \text{ mV}_{PP}, \text{ R}_{L} = 50\Omega$           |                                   |                     | 110  |                   | MHz    |  |

| LSBW              | Large Signal Bandwidth                       | $V_{IN} = 2 V_{PP}, R_{L} = 50\Omega$                                 |                                   |                     | 48   |                   | MHz    |  |

| HD2               | 2nd Harmonic Distortion                      | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 100 kHz                      | R <sub>L</sub> = 50Ω              |                     | -59  |                   |        |  |

|                   |                                              |                                                                       | R <sub>L</sub> = 100Ω             |                     | -70  |                   |        |  |

|                   |                                              | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 1 MHz                        | R <sub>L</sub> = 50Ω              |                     | -57  |                   | dBc    |  |

|                   |                                              |                                                                       | R <sub>L</sub> = 100Ω             |                     | -68  |                   |        |  |

| HD3               | 3rd Harmonic Distortion                      | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 100 kHz                      | R <sub>L</sub> = 50Ω              |                     | -59  |                   | 1      |  |

|                   |                                              |                                                                       | R <sub>L</sub> = 100Ω             |                     | -70  |                   | dBc    |  |

|                   |                                              | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 1 MHz                        | $R_L = 50\Omega$                  |                     | -62  |                   |        |  |

|                   |                                              |                                                                       | $R_1 = 100\Omega$                 |                     | -73  |                   |        |  |

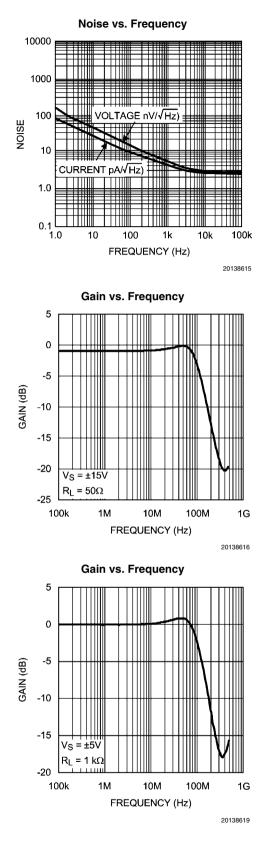

| e <sub>n</sub>    | Input Voltage Noise                          | f ≥ 10 kHz                                                            |                                   |                     | 2.8  |                   | nV/√Hz |  |

| i <sub>n</sub>    | Input Current Noise                          | f ≥ 10 kHz                                                            |                                   |                     | 2.4  |                   | pA/√Hz |  |

| I <sub>sc</sub> 1 | Output Short Circuit Current                 | $V_{O} = 0V,$                                                         | Sourcing                          | 4.5                 | 10   | 15.5              |        |  |

|                   | Source (Note 7)                              | Program Current                                                       | $V_{IN} = +3V$                    | 4.5                 |      | 15.5              | - mA   |  |

|                   |                                              | into C <sub>L</sub> = 25 μA                                           | Sinking                           | 4.5                 | 10   | 15.5              |        |  |

|                   |                                              |                                                                       | $V_{IN} = -3V$                    | 4.5                 |      | 15.5              |        |  |

|                   |                                              | V <sub>O</sub> = 0V<br>Program Current                                | Sourcing<br>V <sub>IN</sub> = +3V | 280<br>273          | 295  | 308<br><b>325</b> |        |  |

|                   |                                              | into $C_L = 750 \ \mu A$                                              | Sinking                           | 280                 | 295  | 310               | - mA   |  |

|                   |                                              |                                                                       | $V_{IN} = -3V$                    | 275                 |      | 325               |        |  |

| I <sub>SC</sub> 2 | Output Short Circuit Current                 | $R_{S} = 0V, V_{IN} = +3V$                                            |                                   | 320                 | 570  | 750               |        |  |

|                   | Source                                       | (Notes 5, 7)                                                          |                                   | 300                 |      | 920               | - mA   |  |

|                   | Output Short Circuit Current Sink            |                                                                       |                                   | 300                 | 515  | 750               |        |  |

| V/I Sectio        | n                                            | (Notes 5, 7)                                                          |                                   | 305                 |      | 910               |        |  |

| CLV <sub>os</sub> | Current Limit Input Offset Voltage           | $B = 1 k \Omega G N D = 0 V$                                          |                                   | 1                   | ±0.5 | ±4.0              | 1      |  |

| •0s               |                                              | $ 1 _{1} = 1.132, 0.100 = 0.0$                                        |                                   |                     |      | ±4.0              | mV     |  |

| CLI <sub>B</sub>  | Current Limit Input Bias Current             | $R_L = 1 k\Omega$                                                     |                                   | -0.5<br><b>-0.8</b> | -0.2 |                   | μA     |  |

| CL<br>CMRR        | Current Limit Common Mode<br>Rejection Ratio | $R_L = 1 \text{ k}\Omega, \text{ GND} = -13 \text{ to } +14 \text{V}$ |                                   | 60<br><b>56</b>     | 69   |                   | dB     |  |

# ±5V Electrical Characteristics

The following specifications apply for Supply Voltage =  $\pm 5V$ ,  $V_{CM} = 0$ ,  $R_L \ge 100 \text{ k}\Omega$  and  $R_S = 50\Omega$ ,  $C_L$  Open, unless otherwise noted. **Boldface** limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol            | Parameter                         | Conditio                                                       | ons                               | Min                 | Тур   | Max                 | Units |  |

|-------------------|-----------------------------------|----------------------------------------------------------------|-----------------------------------|---------------------|-------|---------------------|-------|--|

| A <sub>V</sub>    | Voltage Gain                      | $R_L = 1 \ k\Omega, \ V_{IN} = \pm 3V$                         |                                   | 0.99<br><b>0.98</b> | 0.994 |                     |       |  |

|                   |                                   |                                                                |                                   |                     | 0.00  |                     | V/V   |  |

|                   |                                   |                                                                |                                   | 0.86<br><b>0.84</b> | 0.92  |                     |       |  |

| V <sub>os</sub>   | Offset Voltage                    | R <sub>L</sub> = 1 kΩ, R <sub>S</sub> = 0V                     |                                   |                     | ±2.5  | ±35                 |       |  |

| 00                |                                   |                                                                |                                   |                     |       | ±50                 | mV    |  |

| I <sub>B</sub>    | Input Bias Current                | $V_{IN} = 0V, R_L = 1 k\Omega, R_S =$                          | 0V                                |                     | ±2    | ±15<br><b>±17</b>   | μA    |  |

| R <sub>IN</sub>   | Input Resistance                  | R <sub>L</sub> = 50Ω                                           |                                   |                     | 250   |                     | kΩ    |  |

| C <sub>IN</sub>   | Input Capacitance                 |                                                                |                                   |                     | 3.5   |                     | pF    |  |

| R <sub>o</sub>    | Output Resistance                 | I <sub>OUT</sub> = ±10 mA                                      |                                   |                     | 5     |                     | Ω     |  |

| s                 | Power Supply Current              | $R_L = \infty, V_{IN} = 0V$                                    |                                   |                     | 10    | 13.5<br><b>14.7</b> |       |  |

|                   |                                   |                                                                | 750 μA into CL Pin                |                     | 14    | 17.5<br><b>19.5</b> |       |  |

| V <sub>O</sub> 1  | Positive Output Swing             | $I_{O}$ = 300 mA, $R_{S}$ = 0V, $V_{IN}$                       | =±V <sub>S</sub>                  | 1.3<br><b>0.9</b>   | 1.9   |                     |       |  |

|                   | Negative Output Swing             | $I_{O}$ = 300 mA, $R_{S}$ = 0V, $V_{IN}$                       | =±V <sub>S</sub>                  |                     | -1.3  | -0.5<br><b>-0.1</b> |       |  |

| V <sub>O</sub> 2  | Positive Output Swing             | $R_L = 1 \text{ k}\Omega, R_S = 0V, V_{IN} = \pm V_S$          |                                   | 3.2<br><b>2.9</b>   | 3.5   |                     | v     |  |

|                   | Negative Output Swing             | $R_L = 1 k\Omega, R_S = 0V, V_{IN} = \pm V_S$                  |                                   |                     | -3.5  | –3.1<br><b>–2.9</b> | v     |  |

| V <sub>O</sub> 3  | Positive Output Swing             | $R_L = 50\Omega, R_S = 0V, V_{IN} = \pm V_S$                   |                                   | 2.8<br><b>2.5</b>   | 3.1   |                     | V     |  |

|                   | Negative Output Swing             | $R_L = 50\Omega, R_S = 0V, V_{IN} = \pm V_S$                   |                                   |                     | -3.0  | -2.6<br><b>-2.4</b> | v     |  |

| PSSR              | Power Supply Rejection Ratio      | $R_L = 1 k\Omega, V_{IN} = 0,$<br>V <sub>S</sub> = ±5V to ±15V | Positive                          | 58<br><b>54</b>     | 66    |                     |       |  |

|                   |                                   |                                                                | Negative                          | 58<br><b>54</b>     | 64    |                     | dB    |  |

| I <sub>sc</sub> 1 | Output Short Circuit Current      | $V_{O} = 0V$ , Program Current                                 | Sourcing                          | 4.5                 | 9     | 14.0                |       |  |

|                   |                                   | into C <sub>L</sub> = 25 μA                                    | V <sub>IN</sub> = +3V             | 4.5                 |       | 15.5                |       |  |

|                   |                                   |                                                                | Sinking                           | 4.5<br><b>4.5</b>   | 9     | 14.0<br><b>15.5</b> |       |  |

|                   |                                   |                                                                | $V_{IN} = -3V$                    |                     |       |                     | mA    |  |

|                   |                                   | $V_O = 0V$ , Program Current<br>into C <sub>1</sub> = 750 µA   | Sourcing<br>V <sub>IN</sub> = +3V | 275<br><b>270</b>   | 290   | 305<br><b>320</b>   |       |  |

|                   |                                   | into C <sub>L</sub> = 750 μΑ                                   | Sinking                           | 275                 | 290   | 310                 |       |  |

|                   |                                   |                                                                | $V_{IN} = -3V$                    | 273<br>270          | 230   | 320                 |       |  |

| I <sub>sc</sub> 2 | Output Short Circuit Current      | $R_{S} = 0V, V_{IN} = +3V$                                     |                                   | 300                 | 470   |                     |       |  |

|                   | Source                            | (Notes 5, 7)                                                   |                                   |                     |       |                     | mA    |  |

|                   | Output Short Circuit Current Sink | R <sub>S</sub> = 0V, V <sub>IN</sub> = -3V<br>(Notes 5, 7)     |                                   | 300                 | 400   |                     |       |  |

| SR                | Slew Rate                         | $V_{IN} = \pm 2 V_{PP}, R_L = 1 k\Omega$                       |                                   |                     | 450   |                     |       |  |

|                   |                                   | $V_{IN} = \pm 2 V_{PP}, R_L = 50\Omega$                        |                                   |                     | 210   |                     | V/µs  |  |

| BW                | -3 dB Bandwidth                   | $V_{IN} = \pm 20 \text{ mV}_{PP}, \text{ R}_{L} = 50\Omega$    | 2                                 |                     | 90    |                     | MHz   |  |

| LSBW              | Large Signal Bandwidth            | $V_{IN} = 2 V_{PP}, R_L = 50\Omega$                            |                                   |                     | 39    |                     | MHz   |  |

| Symbol            | Parameter                        | Conditions                           | Min  | Тур  | Max  | Units |

|-------------------|----------------------------------|--------------------------------------|------|------|------|-------|

| T <sub>SD</sub>   | Thermal Shutdown                 | Temperature                          |      | 170  |      | °C    |

|                   |                                  | Hysteresis                           |      | 10   |      |       |

| V/I Sectio        | 'n                               |                                      | •    |      |      | -     |

| CLV <sub>OS</sub> | Current Limit Input Offset       | R <sub>1</sub> = 1 kΩ, GND = 0V      |      | 2.7  | +5   | mV    |

|                   | Voltage                          | -                                    |      |      | ±5.0 | mv    |

| CLIB              | Current Limit Input Bias Current | $R_{1} = 1 k\Omega, C_{1} = 0V$      | -0.5 | -0.2 |      |       |

|                   |                                  |                                      | -0.6 |      |      | μΑ    |

| CL                | Current Limit Common Mode        | $R_1 = 1 k\Omega$ , GND = -3V to +4V | 60   | 65   |      | dB    |

| CMRR              | Rejection Ratio                  | -                                    | 56   |      |      | uВ    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics Table.

Note 2: Human Body Model is 1.5 k $\Omega$  in series with 100 pF. Machine Model is  $0\Omega$  in series with 200 pF.

**Note 3:** If the input-output voltage differential exceeds  $\pm$ 5V, internal clamping diodes will turn on. The current through these diodes should be limited to 5 mA max. Thus for an input voltage of  $\pm$ 15V and the output shorted to ground, a minimum of 2 k $\Omega$  should be placed in series with the input.

Note 4: The maximum continuous current must be limited to 300 mA. See the Application section for more details.

Note 5: For the condition where the C<sub>L</sub> pin is left open the output current should not be continuous, but instead, should be limited to low duty cycle pulse mode such that the RMS output current is less than or equal to 300 mA.

Note 6: Soldered to PC board with copper foot print equal to DAP size. Natural convection (no air flow). Board material is FR-4.

**Note 7:**  $V_{IN} = + \text{ or } -4V \text{ at } T_J = -40^{\circ}\text{C}.$

**Note 8:** The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = T_{J(MAX)} - T_A / \theta_{JA}$ . See Thermal Management section of the Application Hints.

# **Ordering Information**

| Package       | Part Number | Package Marking | Transport Media          | NSC Drawing |

|---------------|-------------|-----------------|--------------------------|-------------|

| 8-Pin PSOP    | LMH6321MR   | LMH6321MR       | 95 Units/Rail            | MRA08A      |

| 0-PIII P30P   | LMH6321MRX  |                 | 2.5k Units Tape and Reel | MINAUOA     |

| 7-Pin TO-263  | LMH6321TS   | LMH6321TS       | 45 Units/Rail            | TS7B        |

| 7-Pill 10-203 | LMH6321TSX  |                 | 500 Units Tape and Reel  | 13/6        |

# LMH6321

# **Typical Performance Characteristics**

# 60 UNDERSHOOT

20138665

20138635

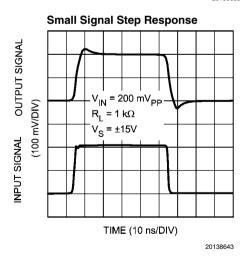

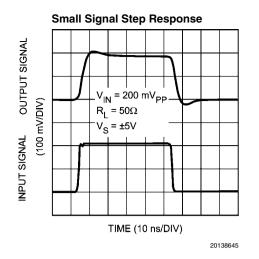

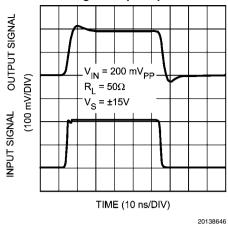

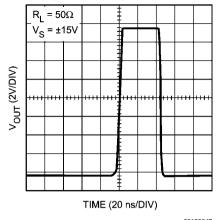

**Small Signal Step Response**

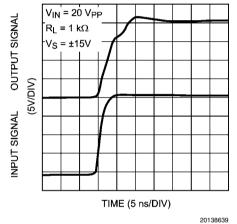

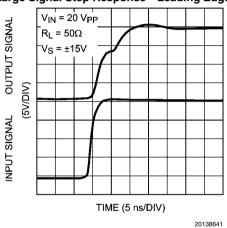

#### Large Signal Step Response—Leading Edge

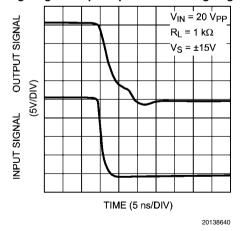

Large Signal Step Response — Trailing Edge

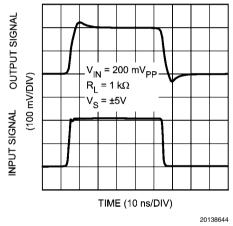

**Small Signal Step Response**

Large Signal Step Response—Leading Edge

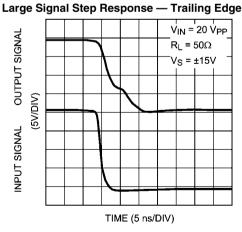

Large Signal Step Response

20138647

Large Signal Step Response

20138650

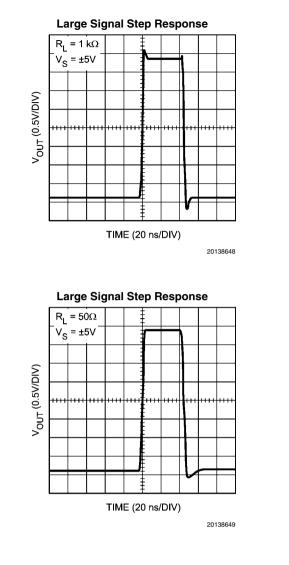

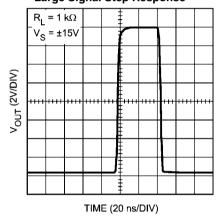

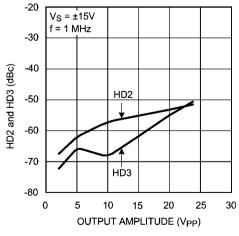

Harmonic Distortion with  $100\Omega$  Load

20138637

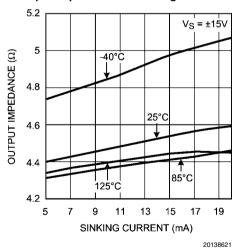

**Output Impedance vs. Sinking Current**

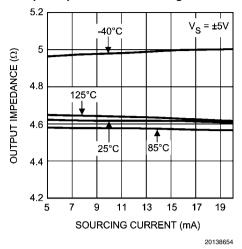

**Output Impedance vs. Sourcing Current**

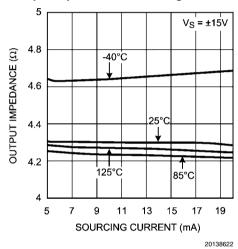

**Output Impedance vs. Sourcing Current**

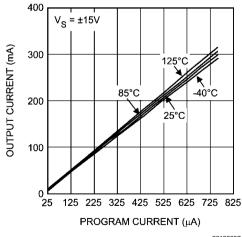

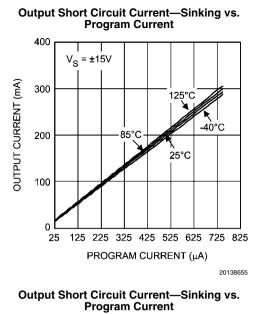

Output Short Circuit Current—Sourcing vs. Program Current

20138657

LMH6321

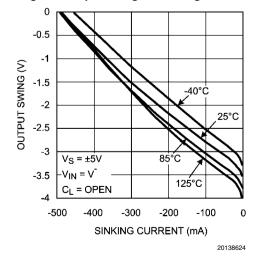

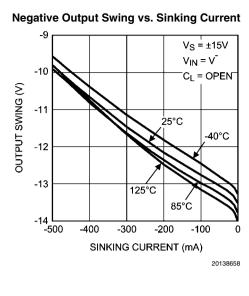

Negative Output Swing vs. Sinking Current

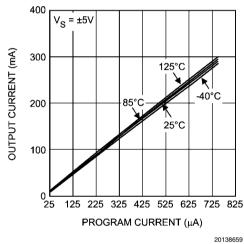

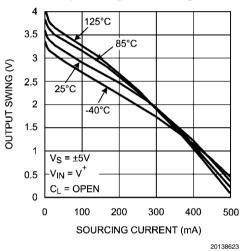

Output Short Circuit Current—Sourcing vs. Program Current 400  $V_S = \pm 5V$  $125^{\circ}C$

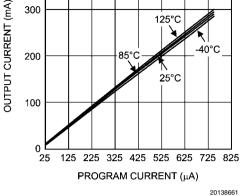

Positive Output Swing vs. Sourcing Current

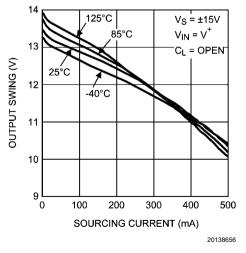

Positive Output Swing vs. Sourcing Current

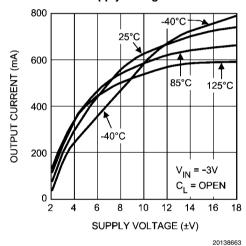

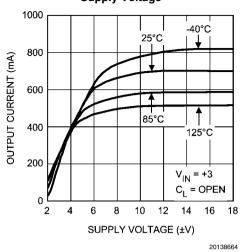

Output Short Circuit Current—Sinking vs. Supply Voltage

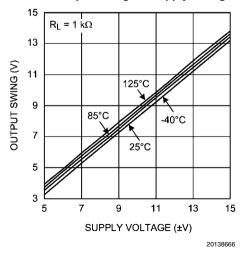

Positive Output Swing vs. Supply Voltage

Output Short Circuit Current—Sourcing vs. Supply Voltage

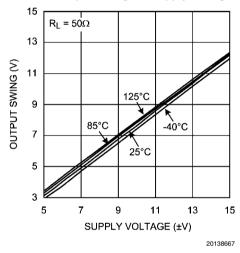

Positive Output Swing vs. Supply Voltage

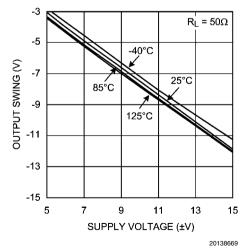

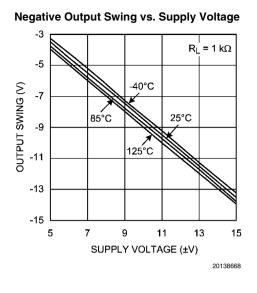

Negative Output Swing vs. Supply Voltage

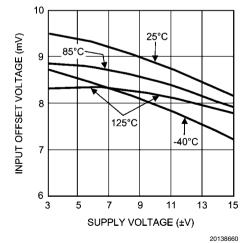

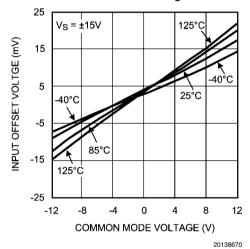

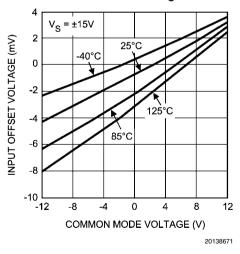

Input Offset Voltage of Amplifier vs. Common Mode Voltage

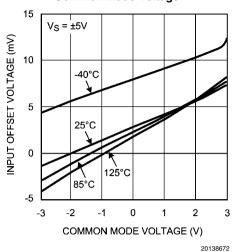

Input Offset Voltage of V/I Section vs. Common Mode Voltage

Input Offset Voltage of Amplifier vs. Common Mode Voltage

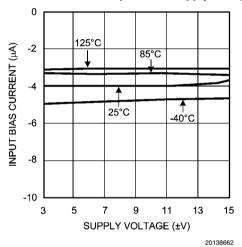

Input Bias Current of Amplifier vs. Supply Voltage

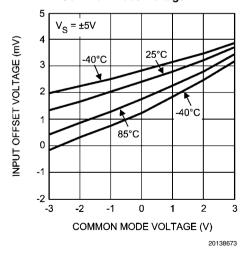

Input Offset Voltage of V/I Section vs. Common Mode Voltage

# **Application Hints**

#### BUFFERS

Buffers are often called voltage followers because they have largely unity voltage gain, thus the name has generally come to mean a device that supplies current gain but no voltage gain. Buffers serve in applications requiring isolation of source and load, i.e., high input impedance, low output impedance (high output current drive). In addition, they offer gain flatness and wide bandwidth.

Most operational amplifiers, that meet the other given requirements in a particular application, can be configured as buffers, though they are generally more complex and are, by and large, not optimized for unity gain operation. The commercial buffer is a cost effective substitute for an op amp. Buffers serve several useful functions, either in tandem with op amps or in standalone applications. As mentioned, their primary function is to isolate a high impedance source from a low impedance load, since a high Z source can't supply the needed current to the load. For example, in the case where the signal source to an analog to digital converter is a sensor, it is recommended that the sensor be isolated from the A/D converter. The use of a buffer ensures a low output impedance and delivery of a stable output to the converter. In A/D converter applications buffers need to drive varying and complex reactive loads.

Buffers come in two flavors: Open Loop and Closed Loop. While sacrificing the precision of some DC characteristics, and generally displaying poorer gain linearity, open loop buffers offer lower cost and increased bandwidth, along with less phase shift and propagation delay than do closed loop buffers. The LMH6321 is of the open loop variety.

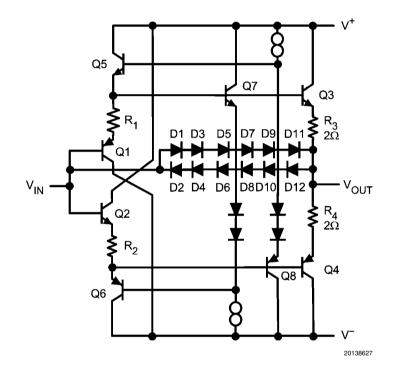

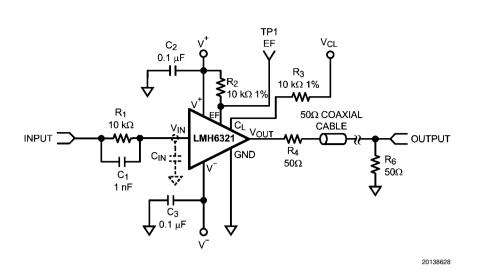

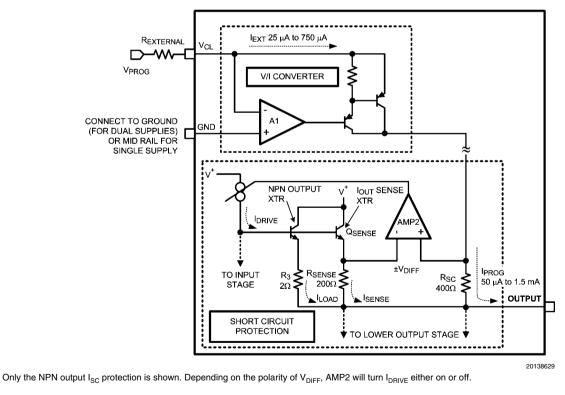

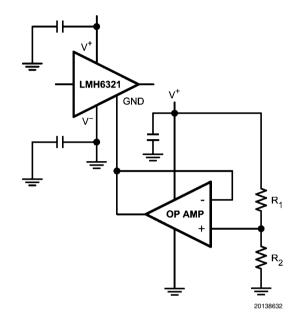

*Figure 1* shows a simplified diagram of the LMH6321 topology, revealing the open loop complementary follower design approach. *Figure 2* shows the LMH6321 in a typical application, in this case, a  $50\Omega$  coaxial cable driver.

**FIGURE 1. Simplified Schematic**

#### SUPPLY BYPASSING

The method of supply bypassing is not critical for frequency stability of the buffer, and, for light loads, capacitor values in the neighborhood of 1 nF to 10 nF are adequate. However, under fast slewing and large loads, large transient currents are demanded of the power supplies, and when combined with any significant wiring inductance, these currents can produce voltage transients. For example, the LMH6321 can slew

typically at 1000 V/µs. Therefore, under a 50 $\Omega$  load condition the load can demand current at a rate, di/dt, of 20 A/µs. This current flowing in an inductance of 50 nH (approximately 1.5" of 22 gage wire) will produce a 1V transient. Thus, it is recommended that solid tantalum capacitors of 5 µF to 10 µF, in parallel with a ceramic 0.1 µF capacitor be added as close as possible to the device supply pins.

FIGURE 2. 50 $\Omega$  Coaxial Cable Driver with Dual Supplies

For values of capacitors in the 10  $\mu F$  to 100  $\mu F$  range, ceramics are usually larger and more costly than tantalums but give superior AC performance for bypassing high frequency noise because of their very low ESR (typically less than 10  $M\Omega$ ) and low ESL.

#### LOAD IMPEDANCE

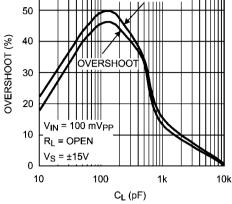

The LMH6321 is stable under any capacitive load when driven by a 50 $\Omega$  source. As shown by the Overshoot vs. Capacitive Load graph in the Typical Performance Characteristics, worst case overshoot is for a purely capacitive load of about 1 nF. Shunting the load capacitance with a resistor will reduce the overshoot.

#### SOURCE INDUCTANCE

Like any high frequency buffer, the LMH6321 can oscillate with high values of source inductance. The worst case condition occurs with no input resistor, and a purely capacitive load of 50 pF, where up to 100 nH of source inductance can be tolerated. With a 50 $\Omega$  load, this goes up to 200 nH. However, a 100 $\Omega$  resistor placed in series with the buffer input will ensure stability with a source inductances up to 400 nH with any load.

#### **OVERVOLTAGE PROTECTION**

(Refer to the simplified schematic in Figure 1).

If the input-to-output differential voltage were allowed to exceed the Absolute Maximum Rating of 5V, an internal diode clamp would turn on and divert the current around the compound emitter followers of Q1/Q3 (D1 – D11 for positive input), or around Q2/Q4 (D2 – D12 for negative inputs). Without this clamp, the input transistors Q1 – Q4 would zener, thereby damaging the buffer.

To limit the current through this clamp, a series resistor should be added to the buffer input (see R<sub>1</sub> in *Figure 2*). Although the allowed current in the clamp can be as high as 5 mA, which would suggest a 2 k $\Omega$  resistor from a 15V source, it is recommended that the current be limited to about 1 mA, hence the 10 k $\Omega$  shown.

The reason for this larger resistor is explained in the following: One way that the input/output voltage differential can exceed the Abs Max value is under a short circuit condition to ground while driving the input with up to ±15V. However, in the LMH6321 the maximum output current is set by the programmable Current Limit pin ( $C_L$ ). The value set by this pin is guaranteed to be accurate to 5 mA ±5%. If the input/output differential exceeds 5V while the output is trying to supply the maximum set current to a shorted condition or to a very low resistance load, a portion of that current will flow through the clamp diodes, thus creating an error in the total load current. If the input resistor is too low, the error current can exceed the 5 mA ±5% budget.

#### BANDWIDTH AND STABILITY

As can be seen in the schematic of *Figure 2*, a small capacitor is inserted in parallel with the series input resistors. The reason for this is to compensate for the natural band-limiting effect of the 1st order filter formed by this resistor and the input capacitance of the buffer. With a typical  $C_{IN}$  of 3.5 pF (*Figure 2*), a pole is created at

$$fp2 = 1/(2\pi R_1 C_{IN}) = 4.5 \text{ MHz}$$

(1)

This will band-limit the buffer and produce further phase lag. If used in an op amp-loop application with an amplifier that has the same order of magnitude of unity gain crossing as fp2, this additional phase lag will produce oscillation.

The solution is to add a small feed-forward capacitor (phase lead) around the input resistor, as shown in *Figure 2*. The value of this capacitor is not critical but should be such that the time constant formed by it and the input resistor that it is in parallel with ( $R_{IN}$ ) be at least five times the time constant of  $R_{IN}C_{IN}$ . Therefore,

$$C_{1} = (5R_{IN}/R_{1})(C_{IN})$$

(2)

from the Electrical Characteristics,  $R_{IN}$  is 250 k $\Omega$ .

In the case of the example in *Figure 2*,  $R_{IN}C_{IN}$  produces a time-constant of 870 ns, so  $C_1$  should be chosen to be a minimum of 4.4 µs, or 438 pF. The value of  $C_1$  (1000 pF) shown in *Figure 2* gives 10 µs.

#### OUTPUT CURRENT AND SHORT CIRCUIT PROTECTION

The LMH6321 is designed to deliver a maximum continuous output current of 300 mA. However, the maximum available current, set by internal circuitry, is about 700 mA at room temperature. The output current is programmable up to 300 mA by a single external resistor and voltage source.

The LMH6321 is not designed to safely output 700 mA continuously and should not be used this way. However, the available maximum continuous current will likely be limited by the particular application and by the package type chosen, which together set the thermal conditions for the buffer (see Thermal Management section) and could require less than 300 mA.

The programming of both the sourcing and sinking currents into the load is accomplished with a single resistor. *Figure 3* shows a simplified diagram of the V to I converter and  $I_{SC}$  protection circuitry that, together, perform this task.

Referring to *Figure 3*, the two simplified functional blocks, labeled V/I Converter and Short Circuit Protection, comprise the circuitry of the Current Limit Control.

The V/I converter consists of error amplifier A1 driving two PNP transistors in a Darlington configuration. The two input connections to this amplifier are V<sub>CL</sub> (inverting input) and GND (non-inverting input). If GND is connected to zero volts, then the high open loop gain of A1, as well as the feedback through the Darlington, will force C<sub>L</sub>, and thus one end R<sub>EXT</sub> to be at zero volts also. Therefore, a voltage applied to the other end of R<sub>EXT</sub> will force a current

#### $I_{EXT} = V_{PROG}/R_{EXT}$ (3)

into this pin. Via this pin, IOUT is programmable from 10 mA to 300 mA by setting I<sub>EXT</sub> from 25 µA to 750 µA by means of a fixed  $R_{EXT}$  of 10  $k\Omega$  and making  $V_{CL}$  variable from 0.25V to 7.5V. Thus, an input voltage V<sub>CL</sub> is converted to a current I<sub>EXT</sub>. This current is the output from the V/I converter. It is gained up by a factor of two and sent to the Short Circuit Protection block as  $I_{PROG}$ .  $I_{PROG}$  sets a voltage drop across  $R_{SC}$ which is applied to the non-inverting input of error amp A2. The other input is across R<sub>SENSE</sub>. The current through R<sub>SENSE</sub>, and hence the voltage drop across it, is proportional to the load current, via the current sense transistor Q<sub>SENSE</sub>. The output of A2 controls the drive (IDRIVE) to the base of the NPN output transistor, Q3 which is, proportional to the amount and polarity of the voltage differential (VDIFF) between AMP2 inputs, that is, how much the voltage across R<sub>SENSE</sub> is greater than or less than the voltage across R<sub>SC</sub>. This loop gains I<sub>EXT</sub> up by another 200, thus

$$I_{SC} = 2 \times 200 (I_{FXT}) = 400 I_{FXT}$$

(4)

Therefore, combining Equations (3) and (4), and solving for  $\mathsf{R}_{\mathsf{EXT}}$  , we get

$$R_{EXT} = 400 V_{PROG} / I_{SC}$$

(5)

If the  $V_{CL}$  pin is left open, the output short circuit current will default to about 700 mA. At elevated temperatures this current will decrease.

FIGURE 3. Simplified Diagram of Current Limit Control

#### THERMAL MANAGEMENT

#### Heatsinking

For some applications, a heat sink may be required with the LMH6321. This depends on the maximum power dissipation and maximum ambient temperature of the application. To accomplish heat sinking, the tabs on TO-263 and PSOP package may be soldered to the copper plane of a PCB for heatsinking (note that these tabs are electrically connected to the most negative point in the circuit, i. e., V<sup>-</sup>).

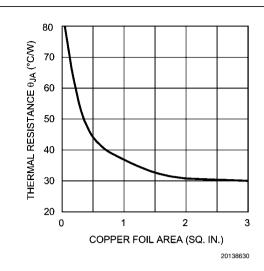

Heat escapes from the device in all directions, mainly through the mechanisms of convection to the air above it and conduction to the circuit board below it and then from the board to the air. Natural convection depends on the amount of surface area that is in contact with the air. If a conductive plate serving as a heatsink is thick enough to ensure perfect thermal conduction (heat spreading) into the far recesses of the plate, the temperature rise would be simply inversely proportional to the total exposed area. PCB copper planes are, in that sense, an aid to convection, the difference being that they are not thick enough to ensure perfect conduction. Therefore, eventually we will reach a point of diminishing returns (as seen in Figure 5). Very large increases in the copper area will produce smaller and smaller improvement in thermal resistance. This occurs, roughly, for a 1 inch square of 1 oz copper board. Some improvement continues until about 3 square inches, especially for 2 oz boards and better, but beyond that, external heatsinks are required. Ultimately, a reasonable practical value attainable for the junction to ambient thermal resistance is about 30 °C/W under zero air flow.

A copper plane of appropriate size may be placed directly beneath the tab or on the other side of the board. If the conductive plane is placed on the back side of the PCB, it is recommended that thermal vias be used per JEDEC Standard JESD51-5.

#### **Determining Copper Area**

One can determine the required copper area by following a few basic guidelines:

- 1. Determine the value of the circuit's power dissipation,  ${\rm P}_{\rm D}$

- 2. Specify a maximum operating ambient temperature,  $T_A$  (MAX). Note that when specifying this parameter, it must be kept in mind that, because of internal temperature rise due to power dissipation, the die temperature,  $T_J$ , will be higher than  $T_A$  by an amount that is dependent on the thermal resistance from junction to ambient,  $\theta_{JA}$ . Therefore,  $T_A$  must be specified such that  $T_J$  does not exceed the absolute maximum die temperature of 150° C.

- Specify a maximum allowable junction temperature, T<sub>J</sub> (MAX)<sup>1</sup>, which is the temperature of the chip at maximum operating current. Although no strict rules exist, typically one should design for a maximum continuous junction temperature of 100°C to 130°C, but no higher than 150° C which is the absolute maximum rating for the part.

- 4. Calculate the value of junction to ambient thermal resistance,  $\theta_{JA}$

- 5. Choose a copper area that will guarantee the specified  $T_{J(MAX)}$  for the calculated  $\theta_{JA}$ .  $\theta_{JA}$  as a function of copper area in square inches is shown in *Figure 4*.

The maximum value of thermal resistance, junction to ambient  $\theta_{JA}$ , is defined as:

$$\theta_{JA} = (T_{J(MAX)} - T_{A(MAX)}) / P_{D(MAX)}$$

(6)

where:

$T_{J(MAX)}$  = the maximum recommended junction temperature  $T_{A(MAX)}$  = the maximum ambient temperature in the user's environment

$P_{D(MAX)}$  = the maximum recommended power dissipation

**Note:** The allowable thermal resistance is determined by the maximum allowable heat rise ,  $T_{RISE} = T_{J(MAX)} \cdot T_{A(MAX)} = (\theta_{JA}) (P_{D(MAX)})$ . Thus, if ambient temperature extremes force  $T_{RISE}$  to exceed the design maximum, the part must be de-rated by either decreasing  $P_D$  to a safe level, reducing  $\theta_{JA}$ , further, or, if available, using a larger copper area.

#### Procedure

First determine the maximum power dissipated by the buffer, P<sub>D(MAX)</sub>. For the simple case of the buffer driving a resistive load, and assuming equal supplies, P<sub>D(MAX)</sub> is given by

$$P_{D(MAX)} = I_{S} (2V^{+}) + V^{+2}/4R_{L}$$

(7)

where: I<sub>S</sub> = quiescent supply current

2. Determine the maximum allowable die temperature rise,

$$T_{R(MAX)} = T_{J(MAX)} - T_{A(MAX)} = P_{D(MAX)} \theta_{JA}$$

(8)

3. Using the calculated value of  $T_{R(MAX)}$  and  $P_{D(MAX)}$  the required value for junction to ambient thermal resistance can be found:

$$\theta_{JA} = T_{R(MAX)} / P_{D(MAX)}$$

(9)

4. Finally, using this value for  $\theta_{JA}$  choose the minimum value of copper area from *Figure 4*.

#### Example

Assume the following conditions:

V+ = V- = 15V, R\_L = 50\Omega, I\_S = 15 mA  $T_{J(MAX)}$  = 125°C,  $T_A$   $_{(MAX)}$  = 85°C.

1. From (7)

$$P_{D(MAX)} = I_{S} (2V^{+}) + V^{+2}/4R_{L} = (15 mA)(30V) + 225V^{2}/200Ω = 1.58W$$

From (8)

$$T_{R(MAX)} = 125^{\circ}C - 85^{\circ}C = 40^{\circ}C$$

3. From (9)

$\theta_{JA} = 40^{\circ}C/1.58W = 25.3^{\circ}C/W$

Examining the plot of Copper Area vs.  $\theta_{JA}$ , we see that we cannot attain this low of a thermal resistance for one layer of 1 oz copper. It will be necessary to derate the part by decreasing either the ambient temperature or the power dissipation. Other solutions are to use two layers of 1 oz foil, or use 2 oz copper (see Table 1), or to provide forced air flow. One should allow about an extra 15% heat sinking capability for safety margin.

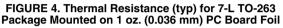

FIGURE 5. Derating Curve for TO-263 package. No Air Flow

TABLE 1.  $\theta_{JA}$  vs. Copper Area and P<sub>D</sub> for TO-263. 1.0 oz cu Board. No Air Flow. Ambient Temperature = 24°C

| Copper Area                        | θJA @ 1.0W<br>(°C/W) | θJA @ 2.0W<br>(°C/W) |  |  |  |

|------------------------------------|----------------------|----------------------|--|--|--|

| 1 Layer = 1"x2" cu<br>Bottom       | 62.4                 | 54.7                 |  |  |  |

| 2 Layer = 1"x2" cu<br>Top & Bottom | 36.4                 | 32.1                 |  |  |  |

| 2 Layer = 2"x2" cu<br>Top & Bottom | 23.5                 | 22.0                 |  |  |  |

| 2 Layer = 2"x4" cu<br>Top & Bottom | 19.8                 | 17.2                 |  |  |  |

As seen in the previous example, buffer dissipation in DC circuit applications is easily computed. However, in AC circuits, signal wave shapes and the nature of the load (reactive, nonreactive) determine dissipation. Peak dissipation can be several times the average with reactive loads. It is particularly important to determine dissipation when driving large load capacitance.

A selection of thermal data for the PSOP package is shown in Table 2. The table summarized  $\theta_{JA}$  for both 0.5 watts and 0.75 watts. Note that the thermal resistance, for both the TO-263 and the PSOP package is lower for the higher power dissipation levels. This phenomenon is a result of the principle of Newtons Law of Cooling. Restated in term of heatsink cooling, this principle says that the rate of cooling and hence the thermal conduction, is proportional to the temperature difference between the junction and the outside environment (ambient). This difference increases with increasing power levels, thereby producing higher die temperatures with more rapid cooling.

| Copper Area/Vias                                                      | θJA @ 0.5W<br>(°C/W) | θJA @ 0.75W<br>(°C/W) |

|-----------------------------------------------------------------------|----------------------|-----------------------|

| 1 Layer = 0.05 sq. in.<br>(Bottom) + 3 Via Pads                       | 141.4                | 138.2                 |

| 1 Layer = 0.1 sq. in.<br>(Bottom) + 3 Via Pads                        | 134.4                | 131.2                 |

| 1 Layer = 0.25 sq. in.<br>(Bottom) + 3 Via Pads                       | 115.4                | 113.9                 |

| 1 Layer = 0.5 sq. in.<br>(Bottom) + 3 Via Pads                        | 105.4                | 104.7                 |

| 1 Layer = 1.0 sq. in.<br>(Bottom) + 3 Via Pads                        | 100.5                | 100.2                 |

| 2 Layer = 0.5 sq. in.<br>(Top)/ 0.5 sq. in.<br>(Bottom) + 33 Via Pads | 93.7                 | 92.5                  |

| 2 Layer = 1.0 sq. in.<br>(Top)/ 1.0 sq. in.<br>(Bottom) + 53 Via Pads | 82.7                 | 82.2                  |

#### TABLE 2. $\theta_{JA}$ vs. Copper Area and P<sub>D</sub> for PSOP. 1.0 oz cu Board. No Airflow. Ambient Temperature = 22°C

#### ERROR FLAG OPERATION

The LMH6321 provides an open collector output at the EF pin that produces a low voltage when the Thermal Shutdown Protection is engaged, due to a fault condition. Under normal operation, the Error Flag pin is pulled up to V+ by an external resistor. When a fault occurs, the EF pin drops to a low voltage and then returns to V+ when the fault disappears. This voltage change can be used as a diagnostic signal to alert a microprocessor of a system fault condition. If the function is not used, the EF pin can be either tied to ground or left open. If this function is used, a 10 k $\Omega$ , or larger, pull-up resistor (R<sub>2</sub> in *Figure 2*) is recommended. The larger the resistor the lower the voltage will be at this pin under thermal shutdown. Table 3 shows some typical values of V<sub>EF</sub> for 10 k $\Omega$  and 100 k $\Omega$ .

TABLE 3. V<sub>EF</sub> vs. R<sub>2</sub> *Figure 2*

| R <sub>2</sub> | @ V+ = 5V | @V+ = 15V |

|----------------|-----------|-----------|

| 10 kΩ          | 0.24V     | 0.55V     |

| 100 KΩ         | 0.036V    | 0.072V    |

#### SINGLE SUPPLY OPERATION

If dual supplies are used, then the GND pin can be connected to a hard ground (0V) (as shown in *Figure 2*). However, if only a single supply is used, this pin must be set to a voltage of one  $V_{BE}$  (~0.7V) or greater, or more commonly, mid rail, by a stiff, low impedance source. This precludes applying a resistive voltage divider to the GND pin for this purpose. *Figure 6* shows one way that this can be done.

#### FIGURE 6. Using an Op Amp to Bias the GND Pin to ½ V + for Single Supply Operation

In *Figure 6*, the op amp circuit pre-biases the GND pin of the buffer for single supply operation.

The GND pin can be driven by an op amp configured as a constant voltage source, with the output voltage set by the resistor voltage divider,  $R_1$  and  $R_2$ . It is recommended that These resistors be chosen so as to set the GND pin to V+/2, for maximum common mode range.

#### SLEW RATE

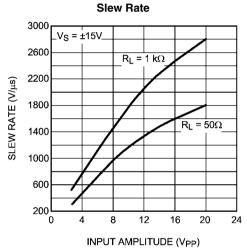

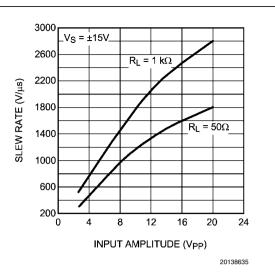

Slew rate is the rate of change of output voltage for largesignal step input changes. For resistive load, slew rate is limited by internal circuit capacitance and operating current (in general, the higher the operating current for a given internal capacitance, the faster is the slew rate). *Figure 7* shows the slew capabilities of the LMH6321 under large signal input conditions, using a resistive load.

FIGURE 7. Slew Rate vs. Peak-to-Peak Input Voltage

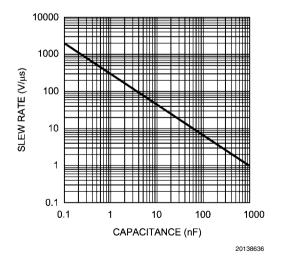

However, when driving capacitive loads, the slew rate may be limited by the available peak output current according to the following expression.

$$dv/dt = I_{PK}/C_{L}$$

(10)

and rapidly changing output voltages will require large output load currents. For example if the part is required to slew at 1000 V/µs with a load capacitance of 1 nF the current demand from the LMH6321 would be 1A. Therefore, fast slew rate is incompatible with large C<sub>L</sub>. Also, since C<sub>L</sub> is in parallel with the load, the peak current available to the load decreases as C<sub>L</sub> increases.

*Figure 8* illustrates the effect of the load capacitance on slew rate. Slew rate tests are specified for resistive loads and/or very small capacitive loads, otherwise the slew rate test would be a measure of the available output current. For the highest slew rate, it is obvious that stray load capacitance should be minimized. Peak output current should be kept below 500 mA. This translates to a maximum stray capacitance of 500 pF for a slew rate of 1000 V/µs.

FIGURE 8. Slew Rate vs. Load Capacitance

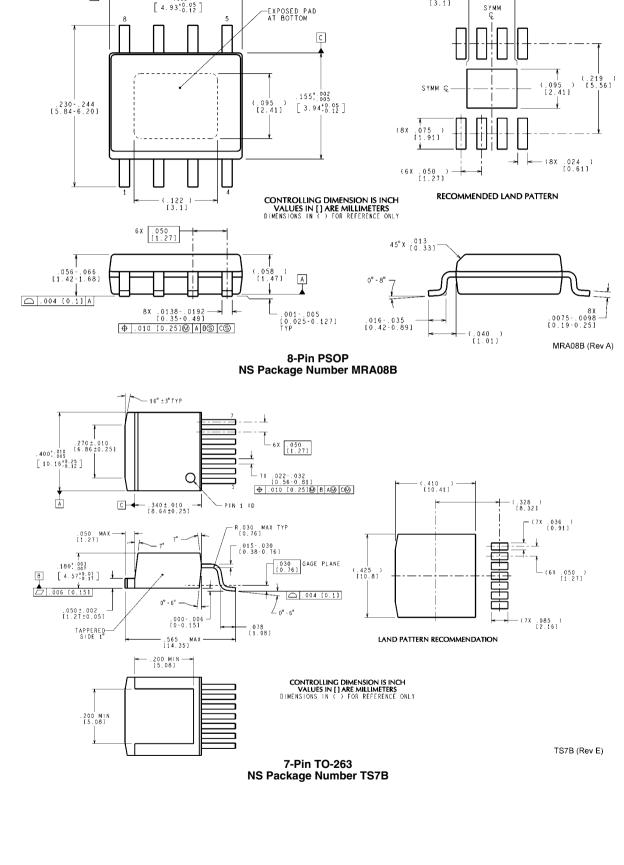

# Physical Dimensions inches (millimeters) unless otherwise noted

# Notes

LMH6321

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560