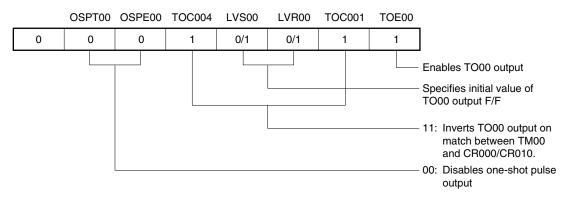

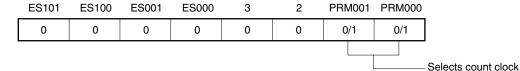

# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

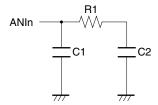

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

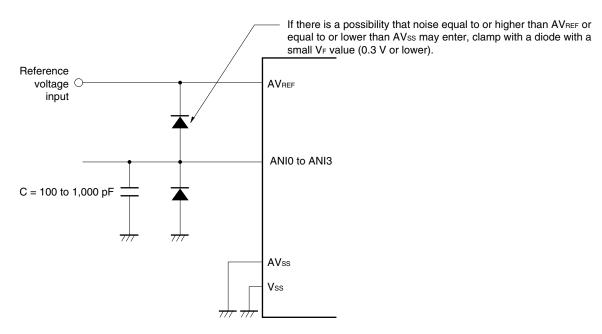

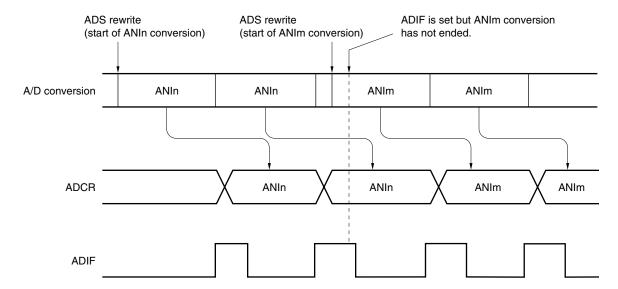

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

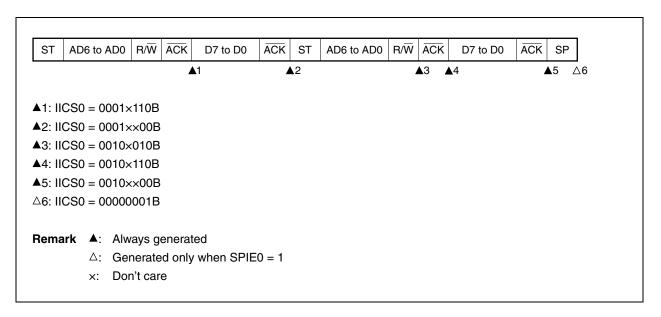

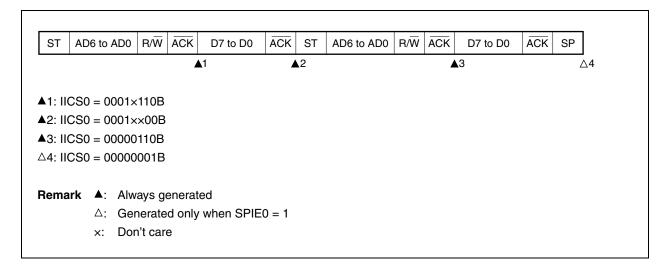

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

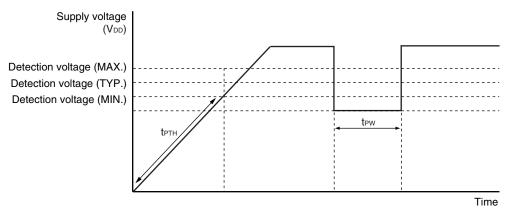

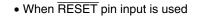

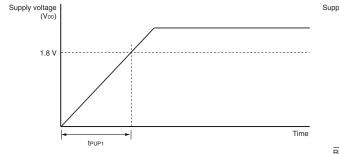

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **User's Manual**

# $\mu$ PD78F8024, 78F8025

**8-Bit Single-Chip Microcontrollers**

$\mu$ PD78F8024  $\mu$ PD78F8025

Document No. U18976EJ3V0UD00 (3rd edition) Date Published December 2008 NS CP(N)

# [MEMO]

#### NOTES FOR CMOS DEVICES —

#### 1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

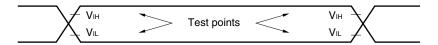

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

# **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

# **6** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

**EEPROM** is a trademark of NEC Electronics Corporation. Windows is a registered trademark or trademark of Microsoft Corporation in the United States and/or other countries. SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

- The information in this document is current as of December, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

#### INTRODUCTION

<R> Readers

This manual is intended for user engineers who wish to understand the functions of the  $\mu$ PD78F8024 and 78F8025, and design and develop application systems and programs for these devices.

**Purpose**

This manual is intended to give users an understanding of the functions described in the **Organization** below.

<R> Organization

The  $\mu$ PD78F8024 and 78F8025 manual is separated into two parts: this manual and the instructions edition (common to 78K0 microcontrollers).

μPD78F8024, 78F8025 User's Manual (This Manual) 78K/0 Series

User's Manual

Instructions

- Pin functions

- Internal block functions

- Interrupts

- Other on-chip peripheral functions

- · Electrical specifications

- CPU functions

- Instruction set

- Explanation of each instruction

How to Read This Manual

It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, and microcontrollers.

- To gain a general understanding of functions:

- → Read this manual in the order of the **CONTENTS**. The mark "<R>" shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what." field.

- How to interpret the register format:

- → For a bit number enclosed in angle brackets, the bit name is defined as a reserved word in the RA78K0, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0.

- To check the details of a register when you know the register name:

- → See APPENDIX C REGISTER INDEX.

- To know details of the 78K0 microcontrollers instructions:

- ightarrow Refer to the separate document 78K/0 Series Instructions User's Manual (U12326E).

Conventions

Data significance: Higher digits on the left and lower digits on the right

Active low representations:

Note:

Footnote for item marked with Note in the text Information requiring particular attention

**Remark**: Supplementary information

Numerical representations: Binary ····××× or ××××B

# **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# **Documents Related to Devices**

| Document Name                                                        | Document No. |

|----------------------------------------------------------------------|--------------|

| μPD78F8024, 78F8025 User's Manual                                    | This manual  |

| 78K/0 Series Instructions User's Manual                              | U12326E      |

| 78K0/Kx2 Flash Memory Programming (Programmer) Application Note      | U17739E      |

| 78K0 Microcontrollers Self Programming Library Type01 User's Manual  | U18274E      |

| 78K0 Microcontrollers EEPROM™ Emulation Library Type01 User's Manual | U18275E      |

# **Documents Related to Flash Memory Programming (User's Manuals)**

| Document Name                                             | Document No. |

|-----------------------------------------------------------|--------------|

| PG-FP5 Flash Memory Programmer                            | U18865E      |

| PG-FP4 Flash Memory Programmer                            | U15260E      |

| QB-MINI2 On-Chip Debug Emulator with Programming Function | U18371E      |

# **Documents Related to Development Tools (Hardware) (User's Manuals)**

| Document Name                      | Document No. |

|------------------------------------|--------------|

| QB-78K0KX2 In-Circuit Emulator     | U17341E      |

| QB-78F8024-EA-01T Exchange adapter | U19135X      |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

#### **Documents Related to Development Tools (Software)**

| Document Name                                                                               |                                       | Document No.     |

|---------------------------------------------------------------------------------------------|---------------------------------------|------------------|

| RA78K0 Ver.3.80 Assembler Package                                                           | Operation                             | U17199E          |

| User's Manual <sup>Note 1</sup>                                                             | Language                              | U17198E          |

|                                                                                             | Structured Assembly Language          | U17197E          |

| 78K0 Assembler Package RA78K0 Ver.4.01 Operating Precautions (Notification Document) Note 1 |                                       | ZUD-CD-07-0181-E |

| CC78K0 Ver.3.70 C Compiler                                                                  | Operation                             | U17201E          |

| User's Manual <sup>Note 2</sup>                                                             | Language                              | U17200E          |

| 78K0 C Compiler CC78K0 Ver. 4.00 Operating Precautions (Notification Document) Note 2       |                                       | ZUD-CD-07-0103-E |

| SM+ System Simulator                                                                        | Operation                             | U18601E          |

| User's Manual                                                                               | User Open Interface                   | U18212E          |

| ID78K0-QB Ver.2.94 Integrated Debugger User's Manual                                        | Operation                             | U18330E          |

| ID78K0-QB Ver.3.00 Integrated Debugger User's Manual                                        | Operation                             | U18492E          |

| PM plus Ver.5.20 User's Manual Note 3                                                       | PM plus Ver.5.20 User's Manual Note 3 |                  |

| PM+ Ver.6.30 User's Manual Note 4                                                           |                                       | U18416E          |

- **Notes 1.** This document is installed into the PC together with the tool when installing RA78K0 Ver. 4.01. For descriptions not included in "78K0 Assembler Package RA78K0 Ver. 4.01 Operating Precautions", refer to the user's manual of RA78K0 Ver. 3.80.

- 2. This document is installed into the PC together with the tool when installing CC78K0 Ver. 4.00. For descriptions not included in "78K0 C Compiler CC78K0 Ver. 4.00 Operating Precautions", refer to the user's manual of CC78K0 Ver. 3.70.

- 3. PM+ Ver. 5.20 is the integrated development environment included with RA78K0 Ver. 3.80.

- **4.** PM+ Ver. 6.30 is the integrated development environment included with RA78K0 Ver. 4.01. Software tool (assembler, C compiler, debugger, and simulator) products of different versions can be managed.

#### **Other Documents**

| Document Name                                                                      | Document No. |

|------------------------------------------------------------------------------------|--------------|

| SEMICONDUCTOR SELECTION GUIDE - Products and Packages -                            | X13769X      |

| Semiconductor Device Mount Manual                                                  | Note         |

| Quality Grades on NEC Semiconductor Devices                                        | C11531E      |

| NEC Semiconductor Device Reliability/Quality Control System                        | C10983E      |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

Note See the "Semiconductor Device Mount Manual" website (http://www.necel.com/pkg/en/mount/index.html).

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

# **CONTENTS**

| CHAPTER 1 OUTLINE                                                          | 16 |

|----------------------------------------------------------------------------|----|

| 1.1 Features                                                               | 16 |

| 1.2 Applications                                                           | 17 |

| 1.3 Ordering Information                                                   | 17 |

| 1.4 Pin Configuration (Top View)                                           | 18 |

| 1.5 Configuration                                                          | 20 |

| 1.6 Block Diagram                                                          | 21 |

| 1.7 Outline of Functions                                                   | 22 |

| CHAPTER 2 PIN FUNCTIONS                                                    | 24 |

| 2.1 Pin Function List                                                      | 24 |

| 2.1.1 CPU Part                                                             | 24 |

| 2.1.2 Constant Current Driver Part with Selectable Buck or Boost Converter | 27 |

| 2.2 Description of Pin Functions (CPU Part)                                | 28 |

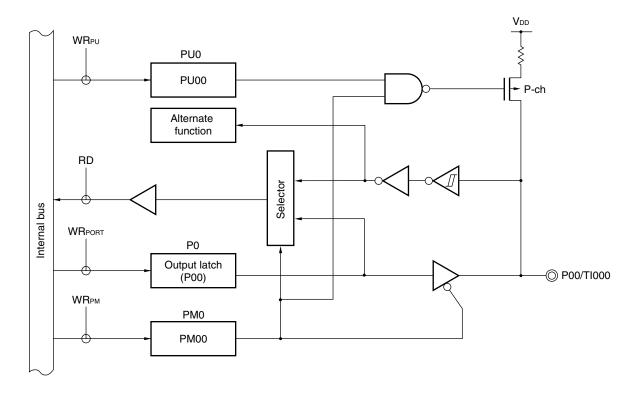

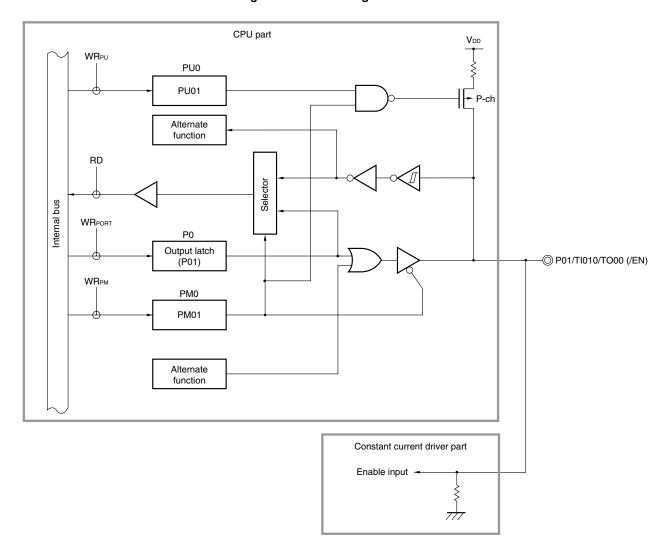

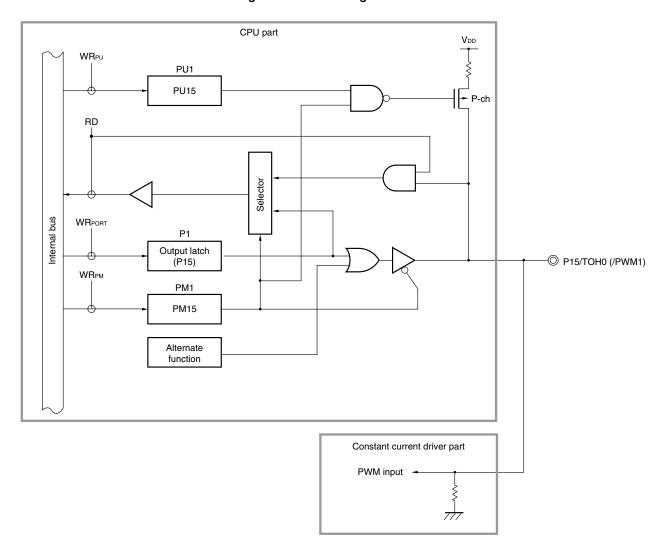

| 2.2.1 P00 and P01 (port 0)                                                 | 28 |

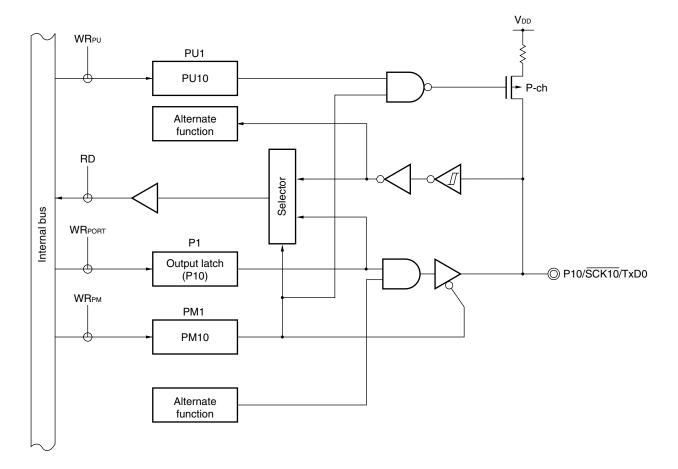

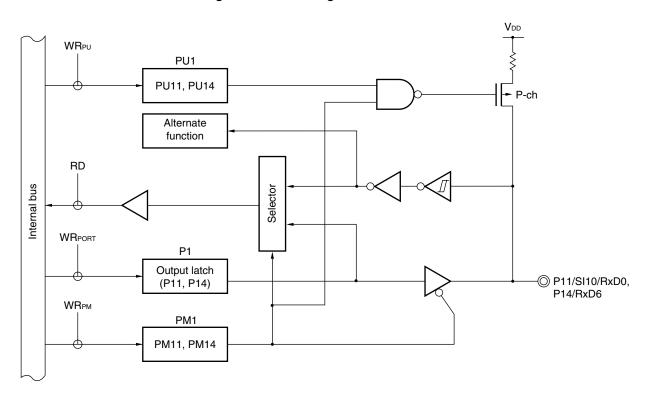

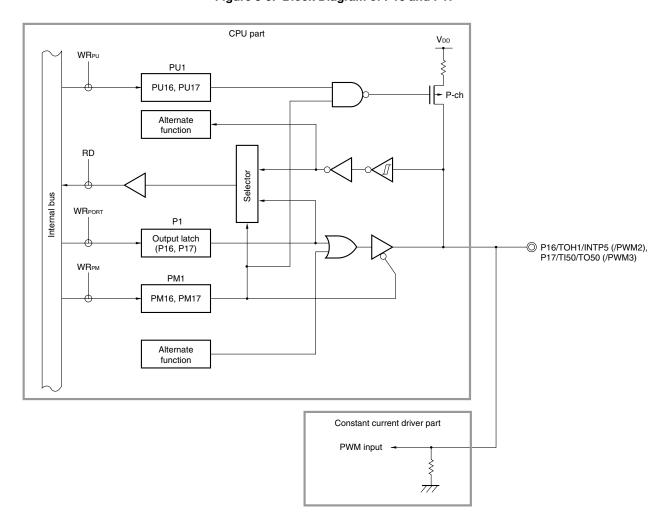

| 2.2.2 P10 to P17 (port 1)                                                  | 28 |

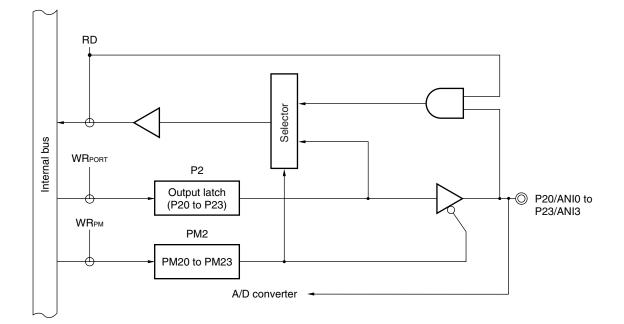

| 2.2.3 P20 to P23 (port 2)                                                  | 29 |

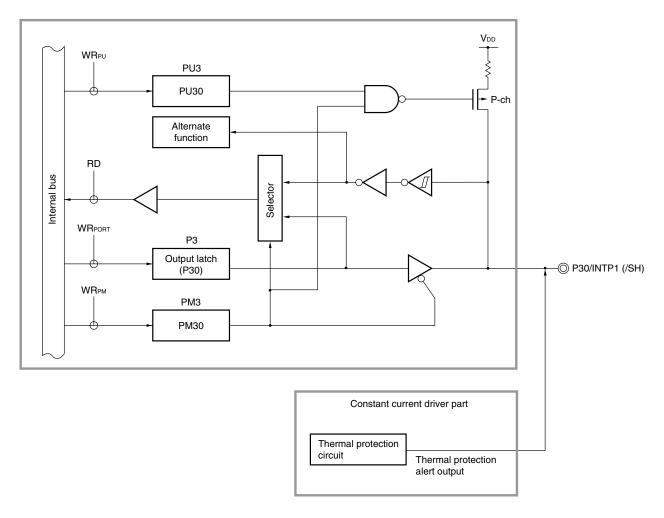

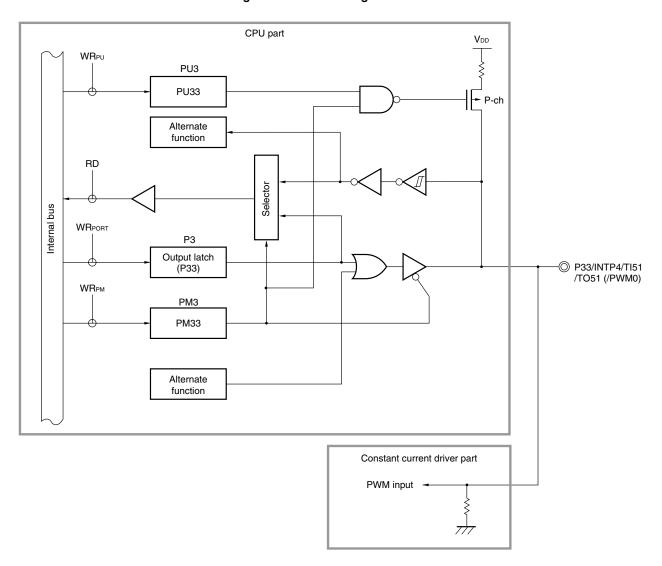

| 2.2.4 P30 to P33 (port 3)                                                  | 30 |

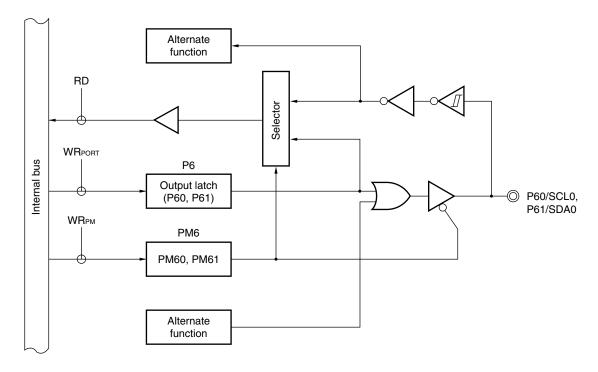

| 2.2.5 P60 and P61 (port 6)                                                 | 30 |

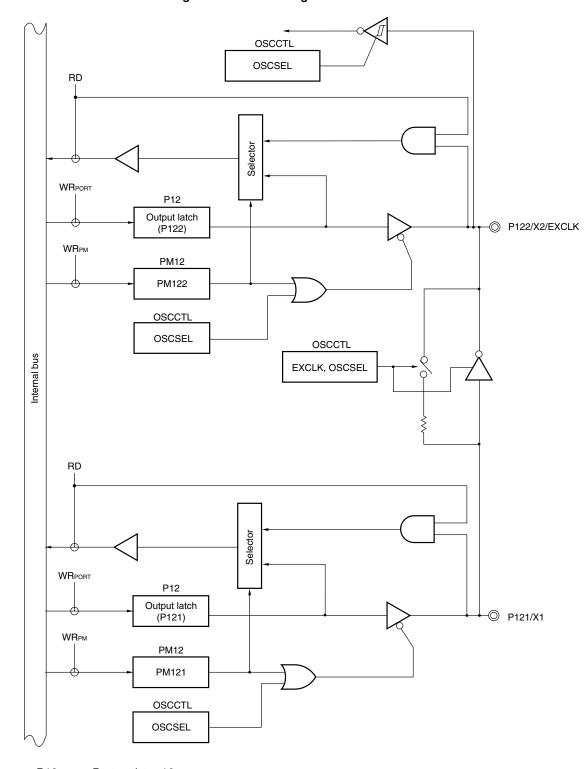

| 2.2.6 P120 to P122 (port 12)                                               | 31 |

| 2.2.7 AVREF                                                                | 31 |

| 2.2.8 AVss                                                                 | 31 |

| 2.2.9 RESET                                                                | 31 |

| 2.2.10 REGC                                                                | 32 |

| 2.2.11 VDD                                                                 | 32 |

| 2.2.12 Vss                                                                 | 32 |

| 2.2.13 FLMD0                                                               | 32 |

| 2.3 Description of Pin Functions (Constant Current Driver Part)            | 33 |

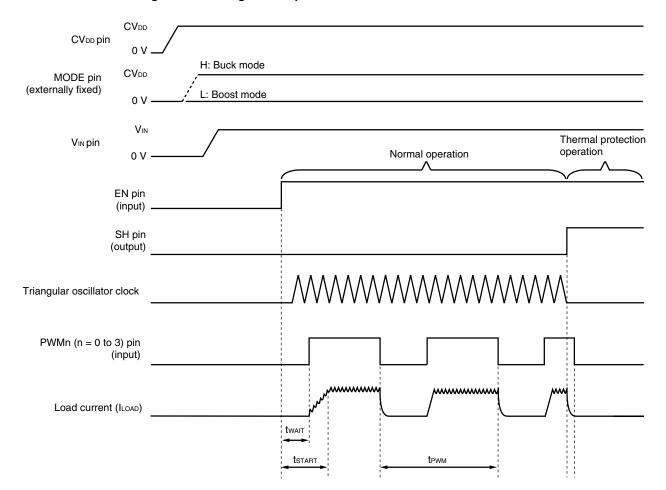

| 2.3.1 EN (internal pin)                                                    | 33 |

| 2.3.2 PWM0 to PWM3 (internal pins)                                         | 33 |

| 2.3.3 SH (internal pin)                                                    | 33 |

| 2.3.4 DRV0 to DRV3                                                         | 33 |

| 2.3.5 MODE                                                                 | 33 |

| 2.3.6 SENSA0 to SENSA3                                                     | 33 |

| 2.3.7 SENSB0 to SENSB3                                                     | 33 |

| 2.3.8 CCA0 to CCA3, CCB0 to CCB3                                           | 33 |

| 2.3.9 CT                                                                   | 33 |

| 2.3.10 RT                                                                  | 33 |

| 2.3.11 CVDD0 to CVDD2                                                      | 34 |

| 2.3.12 Vin                                                                 | 34 |

| 2.3.13 AGND                                                                | 34 |

| 2.3.14 PGND0 to PGND3, PGND11                                              | 34 |

| 2.3.15 IC0                                                                 | 34 |

| 2.4 Pin I/O Circuits and Recommended Connection of Unused Pins             | 35 |

| CHAPTE | R 3 CONSTANT CURRENT DRIVER WITH SELECTABLE BUCK OR BOOST CONVERT             | ER 39 |

|--------|-------------------------------------------------------------------------------|-------|

| 3.1 I  | Function of Constant Current Driver with Selectable Buck or Boost Converter   | 39    |

|        | Boost Mode                                                                    |       |

|        | Buck Mode                                                                     |       |

| 3.4 (  | Operation Mode Setting Procedure                                              | 42    |

| CHAPTE | R 4 CPU ARCHITECTURE                                                          | 44    |

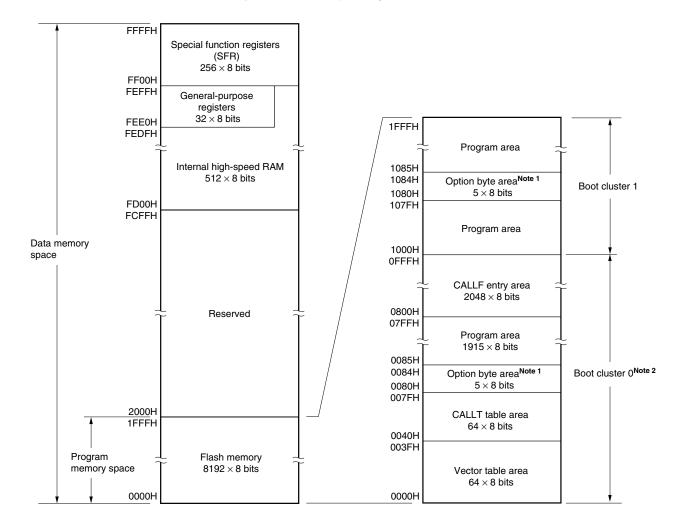

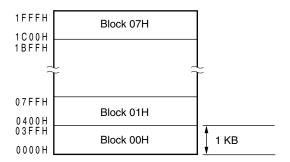

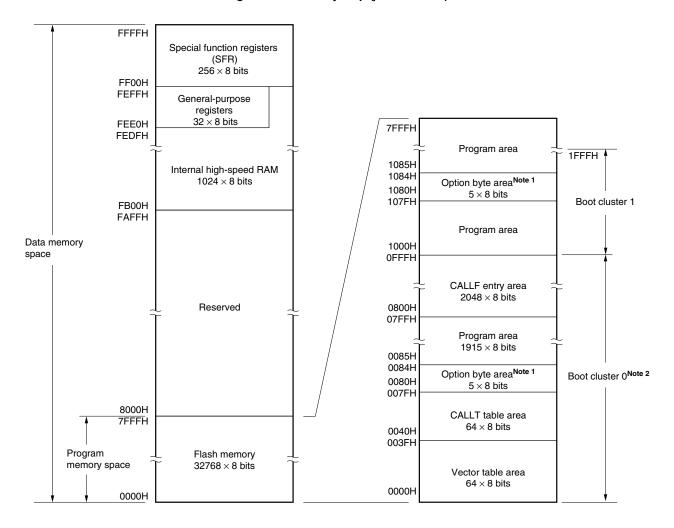

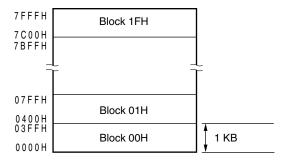

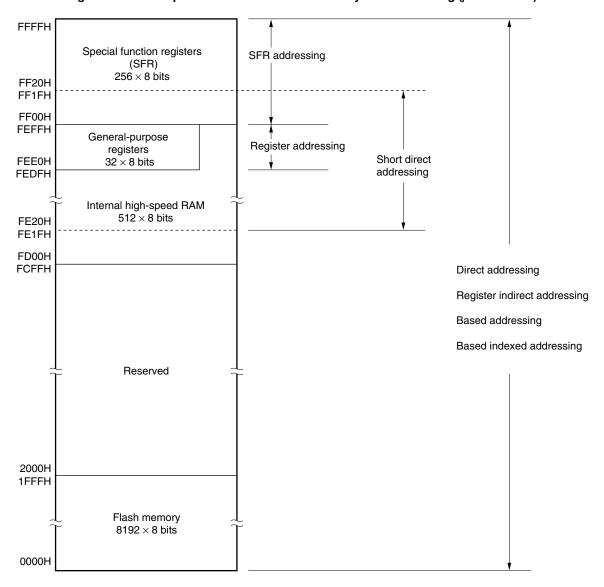

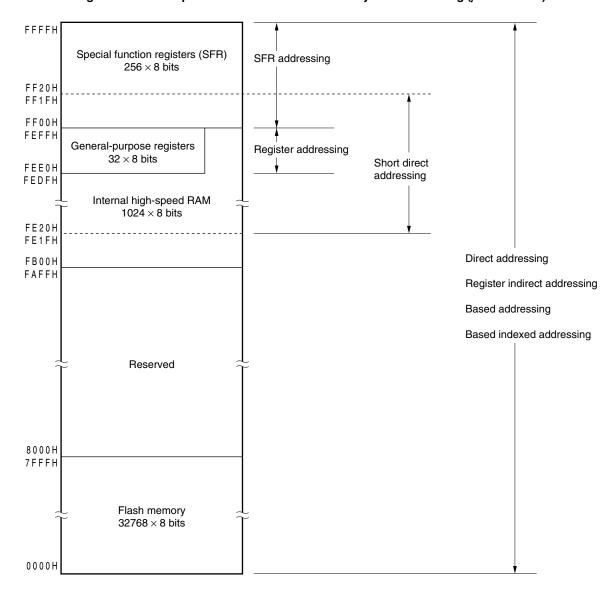

| 4.1 I  | Memory Space                                                                  | 44    |

|        | 4.1.1 Internal program memory space                                           | 47    |

|        | 4.1.2 Internal data memory space                                              | 48    |

|        | 4.1.3 Special function register (SFR) area                                    | 48    |

|        | 4.1.4 Data memory addressing                                                  |       |

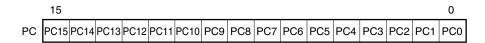

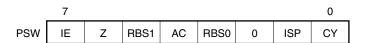

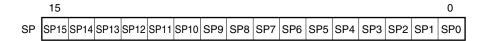

| 4.2    | Processor Registers                                                           |       |

|        | 4.2.1 Control registers                                                       |       |

|        | 4.2.2 General-purpose registers                                               |       |

|        | 4.2.3 Special function registers (SFRs)                                       |       |

| 4.3 I  | nstruction Address Addressing                                                 |       |

|        | 4.3.1 Relative addressing.                                                    |       |

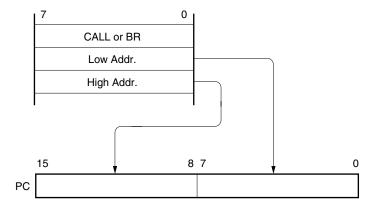

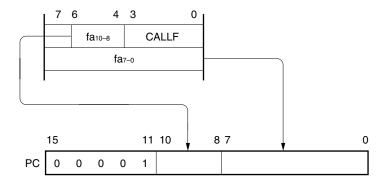

|        | 4.3.2 Immediate addressing                                                    |       |

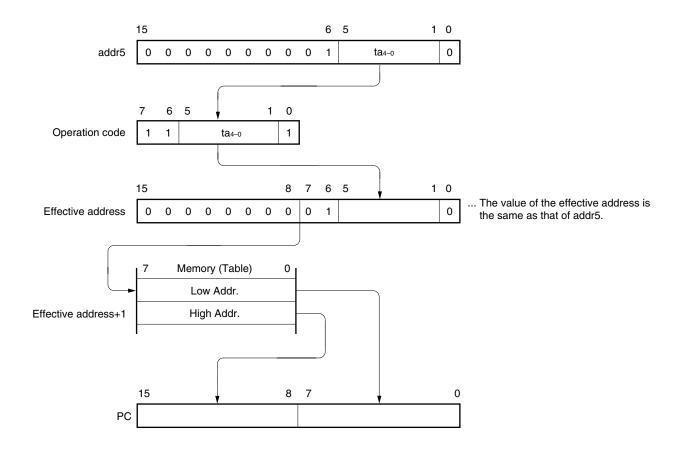

|        | 4.3.3 Table indirect addressing                                               |       |

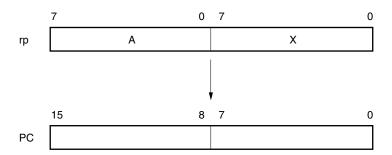

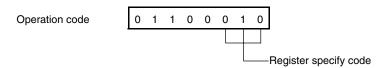

| 444    | 4.3.4 Register addressing                                                     |       |

| 4.4 (  | Operand Address Addressing                                                    |       |

|        | 4.4.1 Implied addressing                                                      |       |

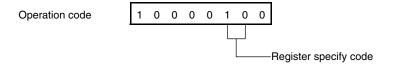

|        | 4.4.2 Register addressing                                                     |       |

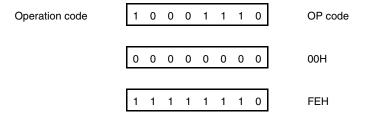

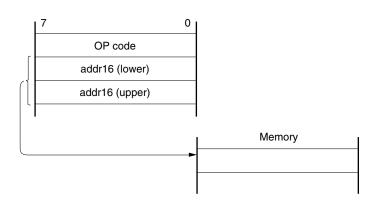

|        | 4.4.3 Direct addressing                                                       |       |

|        | 4.4.4 Short direct addressing                                                 |       |

|        | 4.4.5 Special function register (SFR) addressing                              |       |

|        | 4.4.6 Register indirect addressing                                            |       |

|        | 4.4.7 Based addressing                                                        |       |

|        | 4.4.8 Based indexed addressing                                                |       |

|        | 4.4.9 Stack addressing                                                        | 12    |

| CHAPTE | R 5 PORT FUNCTIONS                                                            | 73    |

|        | Port Functions                                                                |       |

| 5.2    | Port Configuration                                                            | 75    |

|        | 5.2.1 Port 0                                                                  |       |

|        | 5.2.2 Port 1                                                                  | 78    |

|        | 5.2.3 Port 2                                                                  |       |

|        | 5.2.4 Port 3                                                                  | 85    |

|        | 5.2.5 Port 6                                                                  |       |

|        | 5.2.6 Port 12                                                                 |       |

|        | Registers Controlling Port Function                                           |       |

| 5.4 F  | Port Function Operations                                                      |       |

|        | 5.4.1 Writing to I/O port                                                     |       |

|        | 5.4.2 Reading from I/O port                                                   |       |

|        | 5.4.3 Operations on I/O port                                                  |       |

|        | Settings of Port Mode Register and Output Latch When Using Alternate Function |       |

| 5.6 (  | Cautions on 1-Bit Manipulation Instruction for Port Register n (Pn)           | 99    |

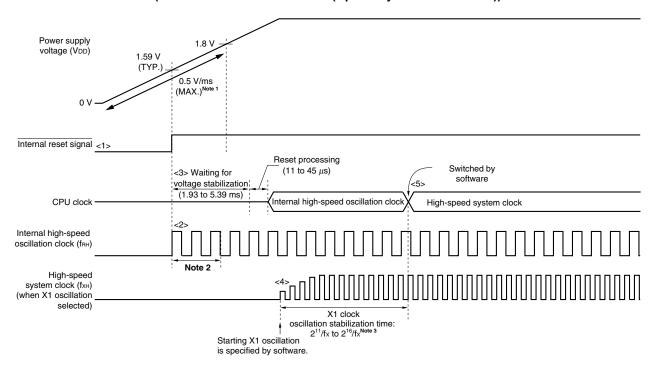

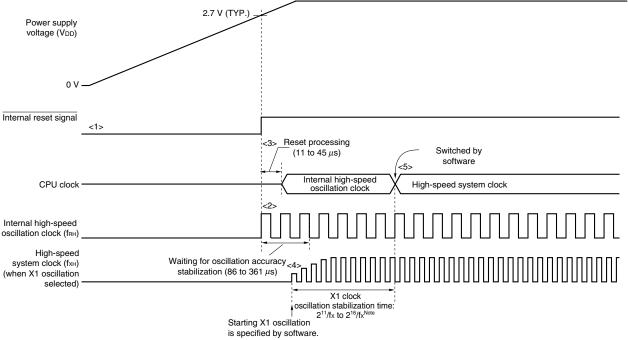

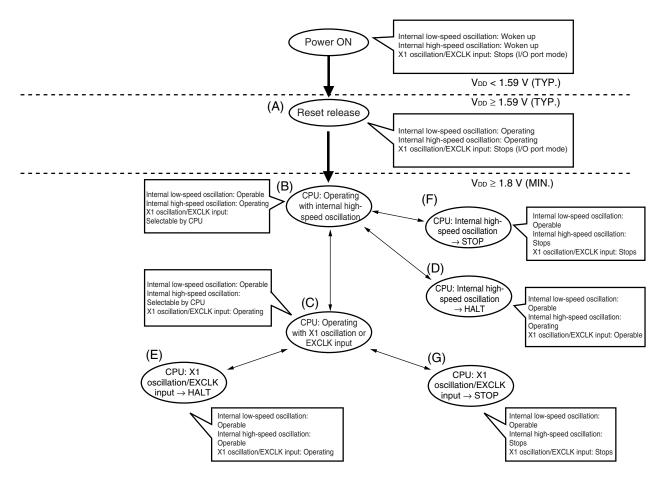

| СНАРТ | ER 6 CLOCK GENERATOR                                                              | 100 |

|-------|-----------------------------------------------------------------------------------|-----|

| 6.1   | Functions of Clock Generator                                                      | 100 |

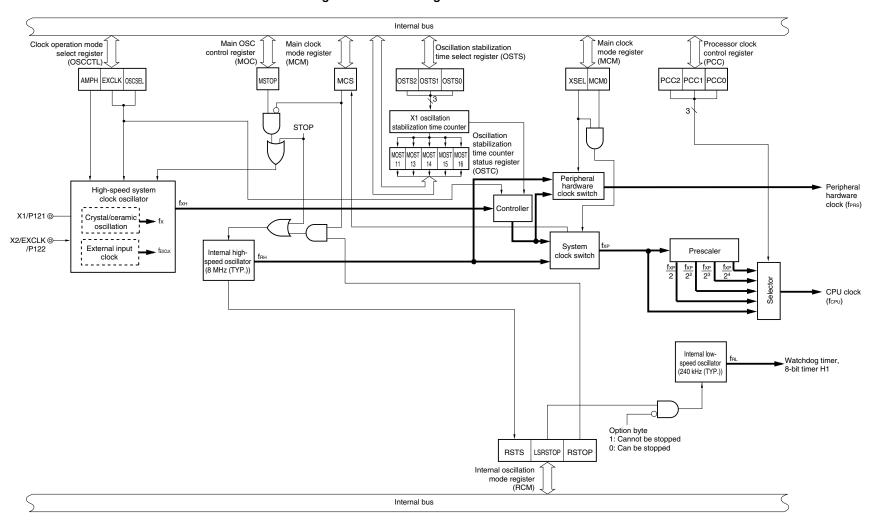

| 6.2   | Configuration of Clock Generator                                                  | 101 |

| 6.3   | Registers Controlling Clock Generator                                             | 103 |

| 6.4   | System Clock Oscillator                                                           | 111 |

|       | 6.4.1 X1 oscillator                                                               |     |

|       | 6.4.2 Internal high-speed oscillator                                              |     |

|       | 6.4.3 Internal low-speed oscillator                                               |     |

|       | 6.4.4 Prescaler                                                                   |     |

|       | Clock Generator Operation                                                         |     |

| 6.6   | Controlling Clock                                                                 |     |

|       | 6.6.1 Example of controlling high-speed system clock                              |     |

|       | 6.6.3 Example of controlling internal low-speed oscillation clock                 |     |

|       | 6.6.4 Clocks supplied to CPU and peripheral hardware                              |     |

|       | 6.6.5 CPU clock status transition diagram                                         |     |

|       | 6.6.6 Condition before changing CPU clock and processing after changing CPU clock |     |

|       | 6.6.7 Time required for switchover of main system clock                           |     |

|       | 6.6.8 Conditions before clock oscillation is stopped                              |     |

|       | 6.6.9 Peripheral hardware and source clocks                                       |     |

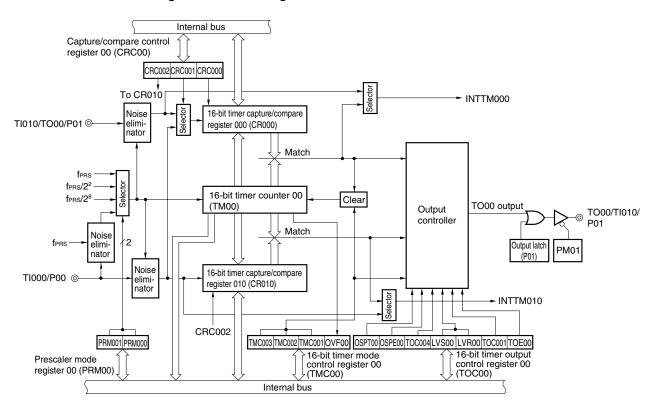

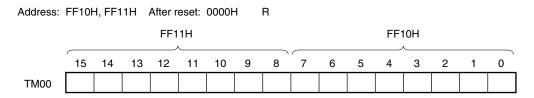

| СНАРТ | ER 7 16-BIT TIMER/EVENT COUNTER 00                                                | 130 |

| 7.1   | Functions of 16-bit Timer/Event Counter 00                                        | 130 |

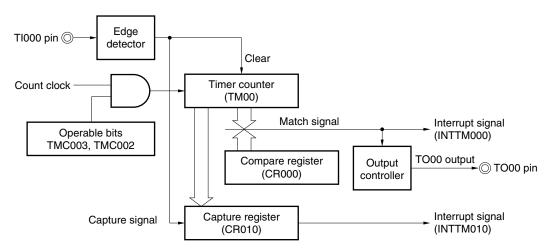

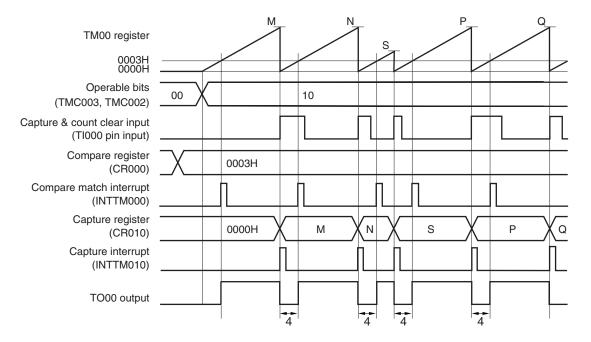

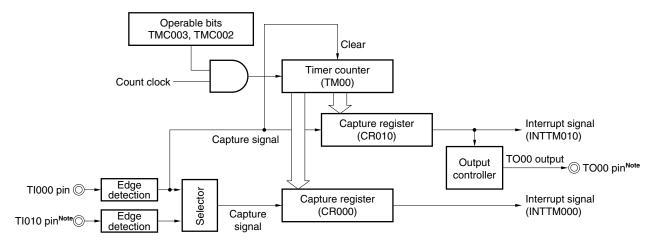

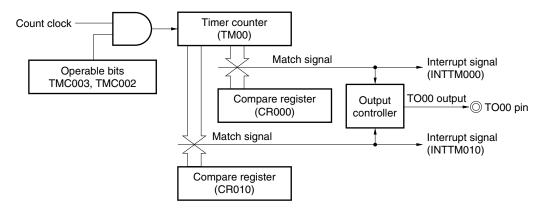

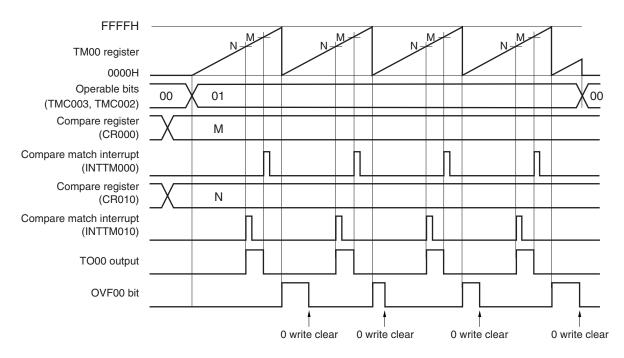

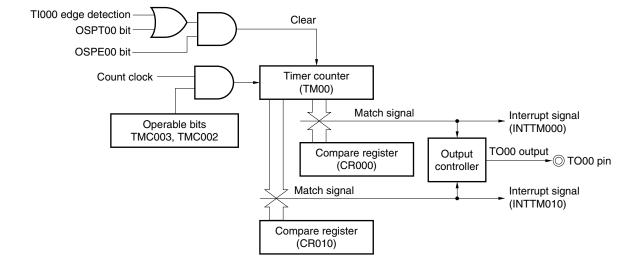

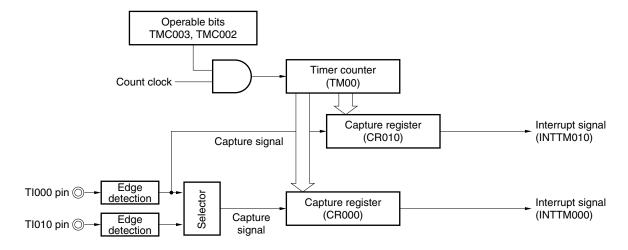

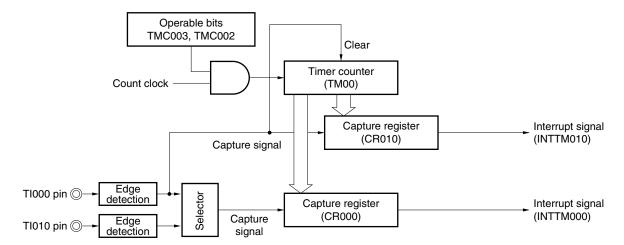

|       | Configuration of 16-bit Timer/Event Counter 00                                    |     |

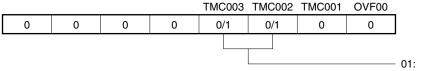

|       | Registers Controlling 16-bit Timer/Event Counter 00                               |     |

| 7.4   | Operation of 16-bit Timer/Event Counter 00                                        | 144 |

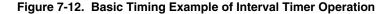

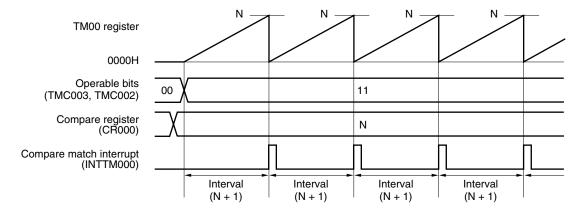

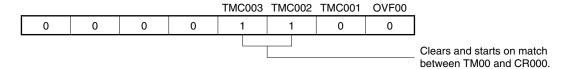

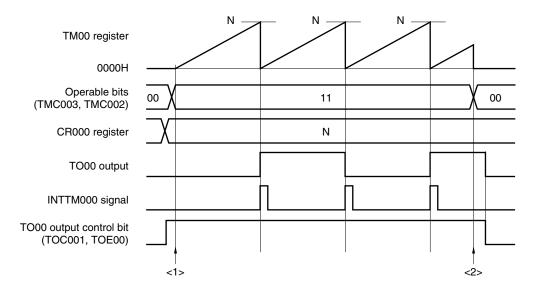

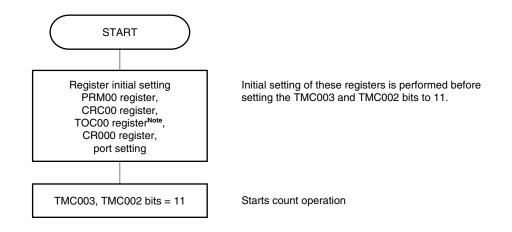

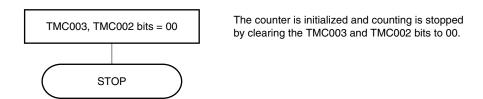

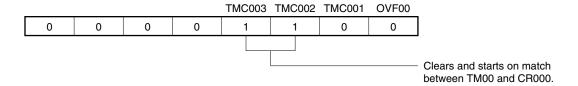

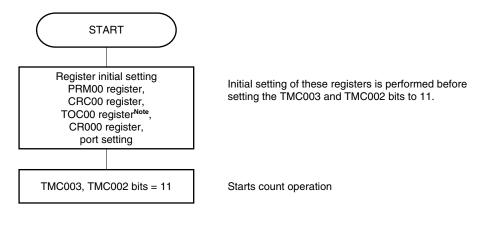

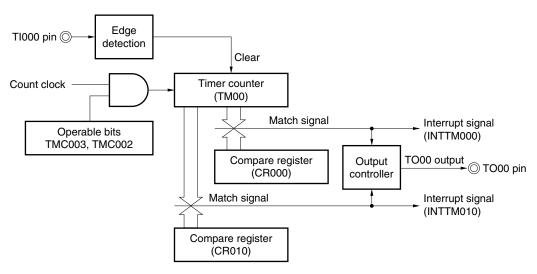

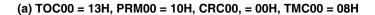

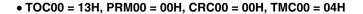

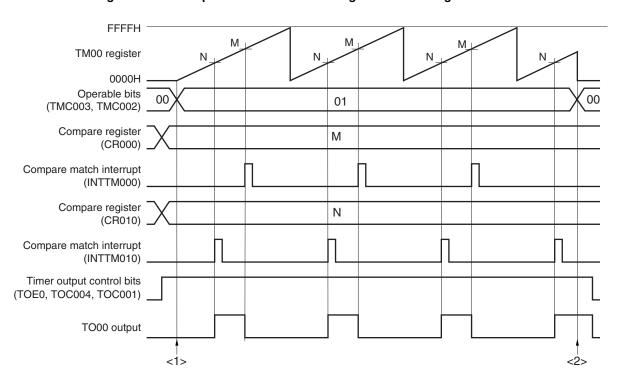

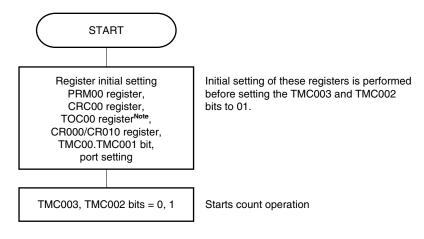

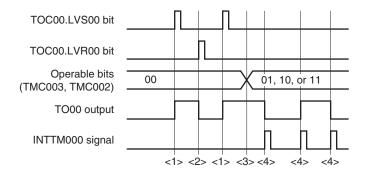

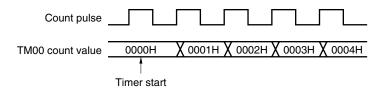

|       | 7.4.1 Interval timer operation                                                    | 144 |

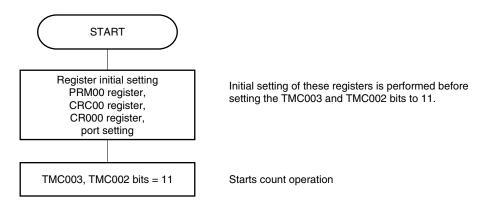

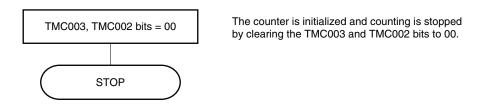

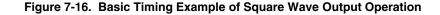

|       | 7.4.2 Square wave output operation                                                | 147 |

|       | 7.4.3 External event counter operation                                            |     |

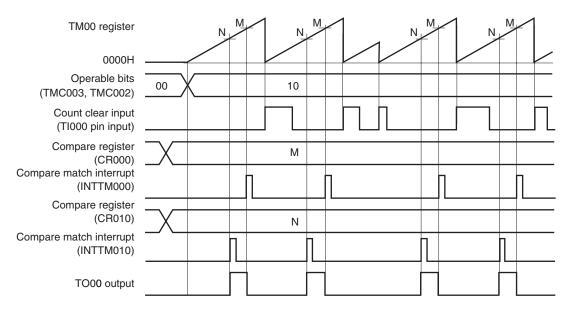

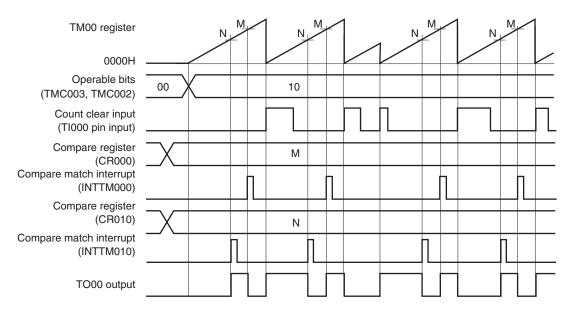

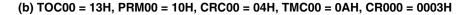

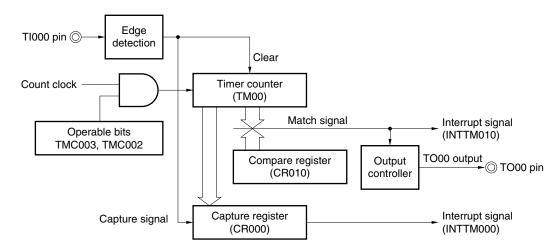

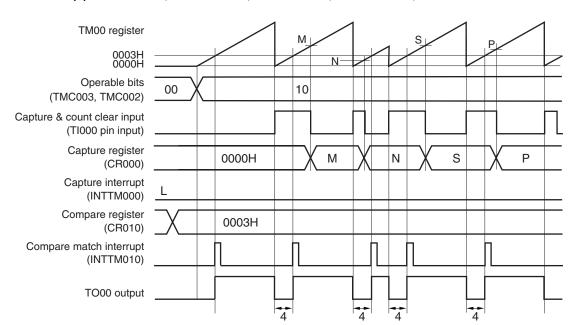

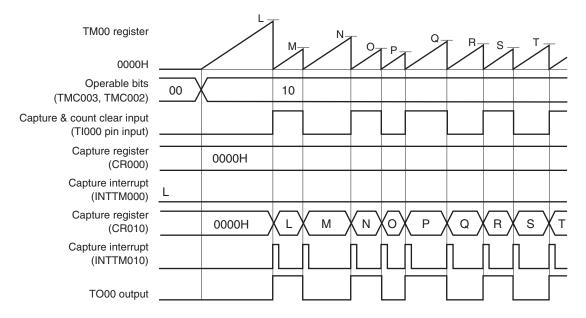

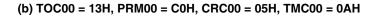

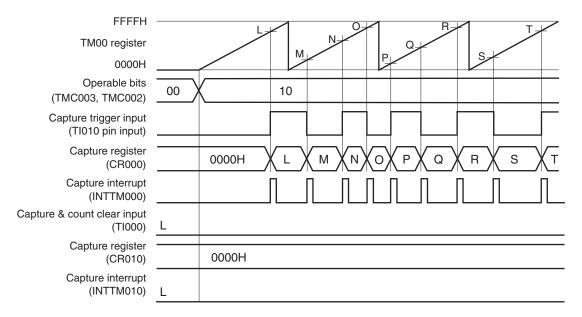

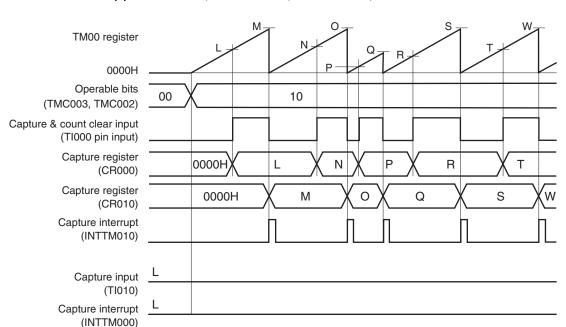

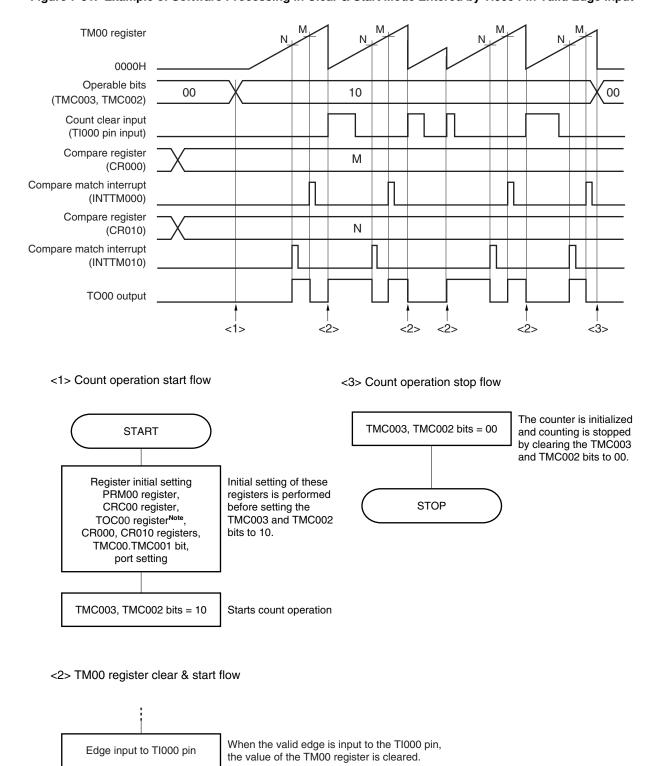

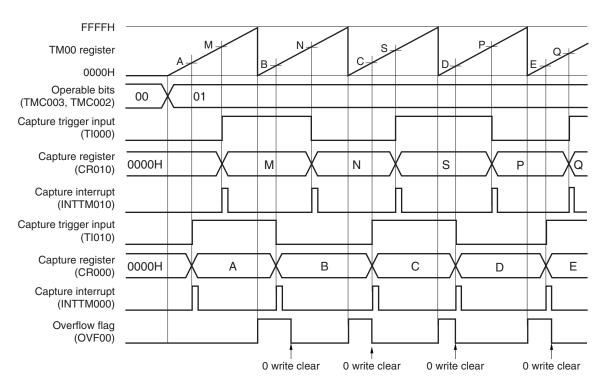

|       | 7.4.4 Operation in clear & start mode entered by Tl000 pin valid edge input       |     |

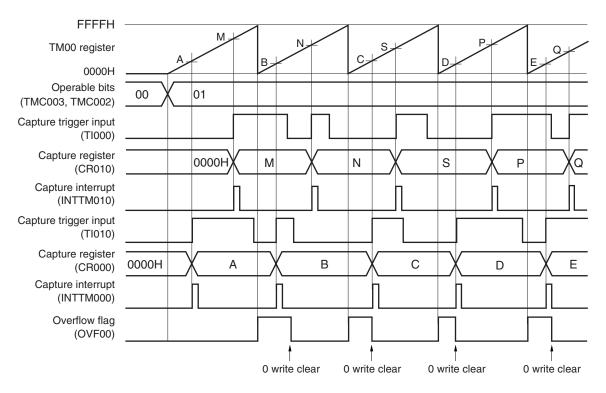

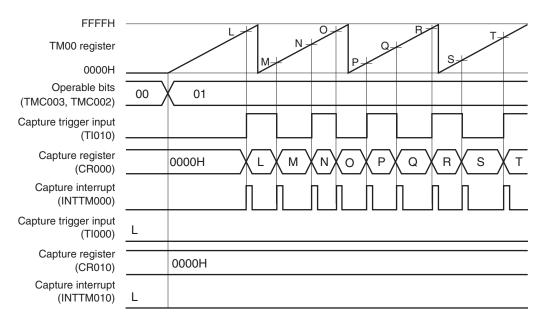

|       | 7.4.5 Free-running timer operation                                                |     |

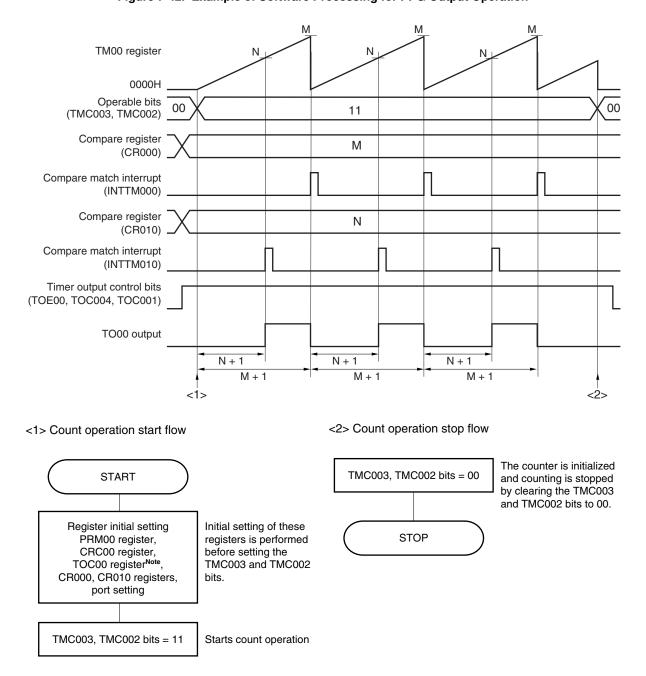

|       | 7.4.6 PPG output operation                                                        |     |

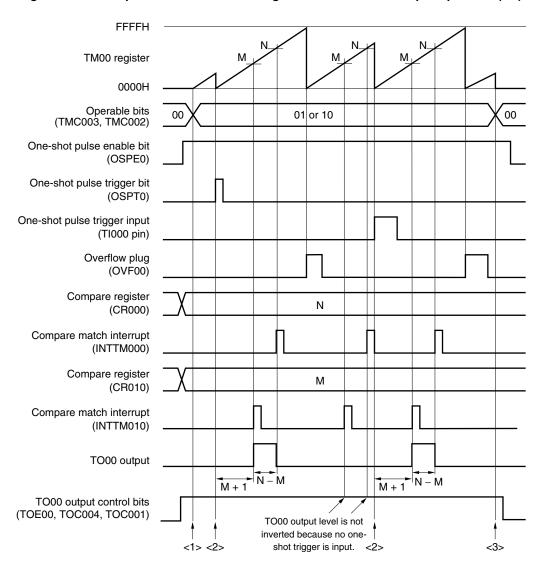

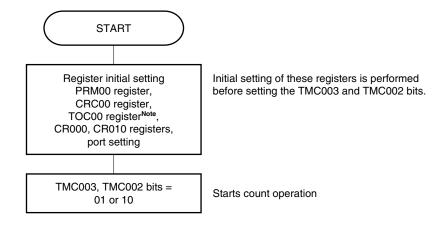

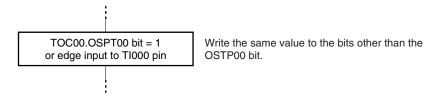

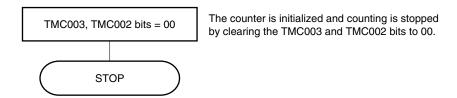

|       | 7.4.7 One-shot pulse output operation                                             |     |

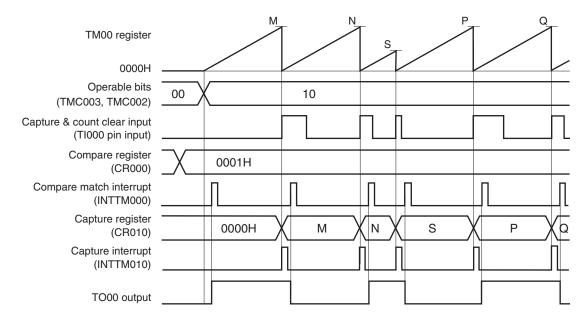

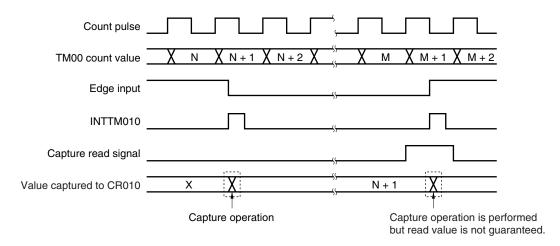

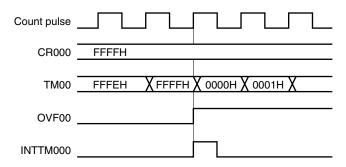

| 7.5   | 7.4.8 Pulse width measurement operation                                           |     |

| 7.5   | 7.5.1 Rewriting CR010 during TM00 operation                                       |     |

|       | 7.5.1 Rewnling CR010 during TM00 operation                                        |     |

| 7.6   | Cautions for 16-bit Timer/Event Counter 00                                        |     |

| CHAPT | ER 8 8-BIT TIMER/EVENT COUNTERS 50 AND 51                                         | 198 |

| 8.1   | Functions of 8-bit Timer/Event Counters 50 and 51                                 | 198 |

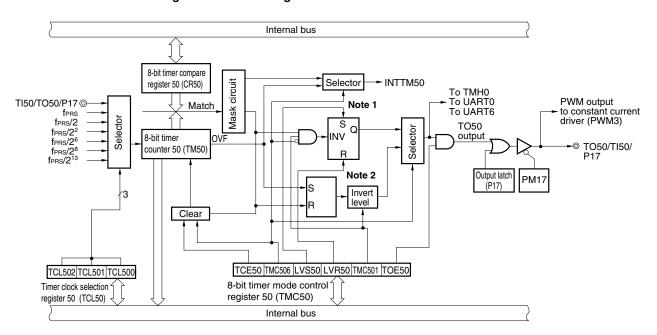

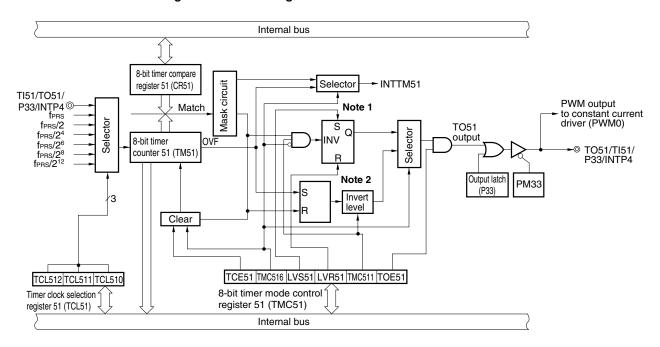

|       | Configuration of 8-bit Timer/Event Counters 50 and 51                             |     |

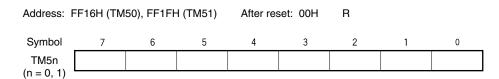

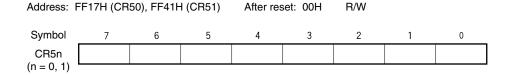

|       | Registers Controlling 8-bit Timer/Event Counters 50 and 51                        |     |

|       | Operations of 8-bit Timer/Event Counters 50 and 51                                |     |

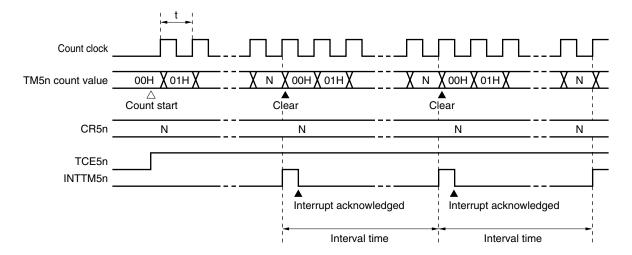

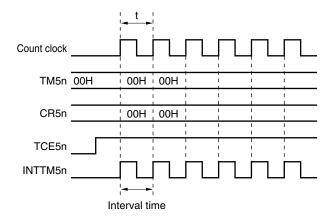

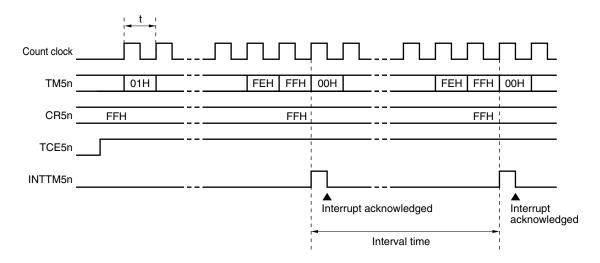

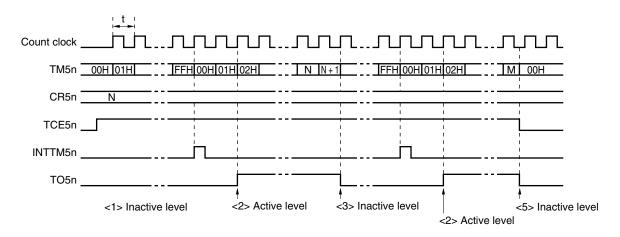

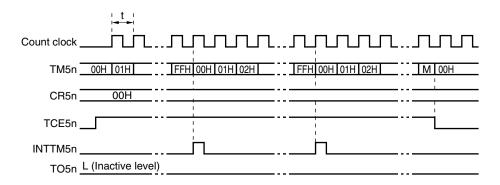

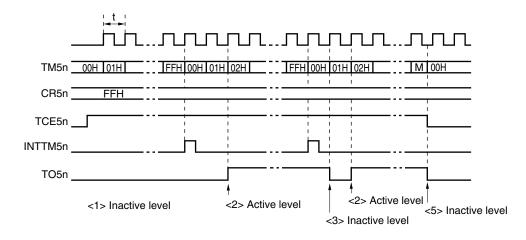

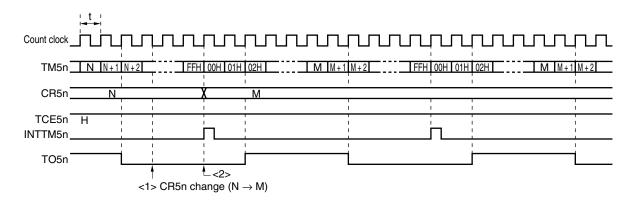

|       | 8.4.1 Operation as interval timer                                                 | 207 |

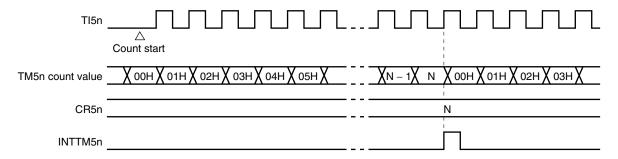

|       | 8.4.2 Operation as external event counter                                         | 209 |

|       | 8.4.3 Square-wave output operation                                                | 210 |

|       | 8.4.4 PWM output operation                                                        | 211 |

| 8.5 Cautions for 8-bit Timer/Event Counters 50 and 51   | 215 |

|---------------------------------------------------------|-----|

| CHAPTER 9 8-BIT TIMERS H0 AND H1                        | 216 |

| 9.1 Functions of 8-bit Timers H0 and H1                 | 216 |

| 9.2 Configuration of 8-bit Timers H0 and H1             | 216 |

| 9.3 Registers Controlling 8-bit Timers H0 and H1        | 220 |

| 9.4 Operation of 8-bit Timers H0 and H1                 | 226 |

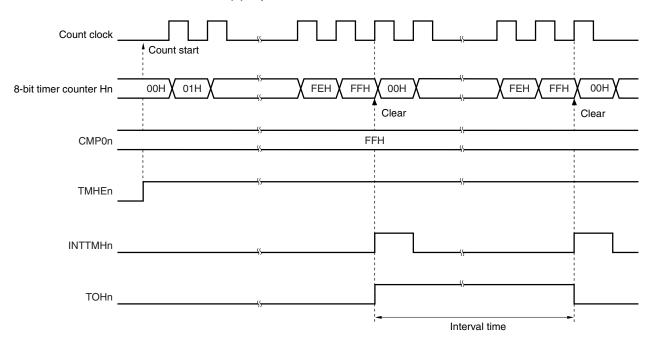

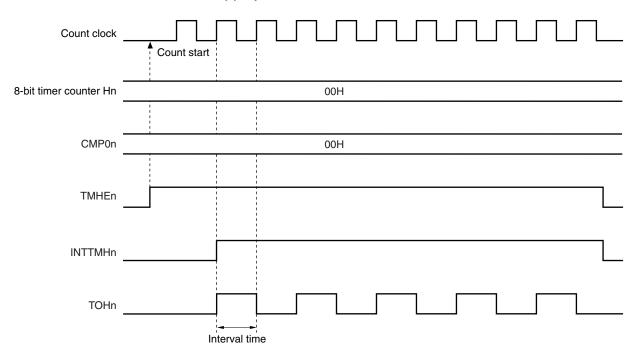

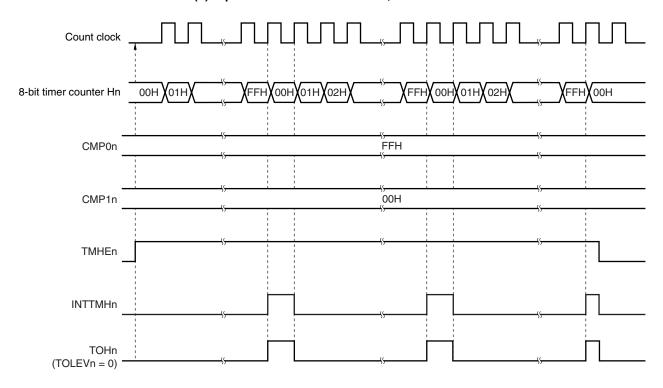

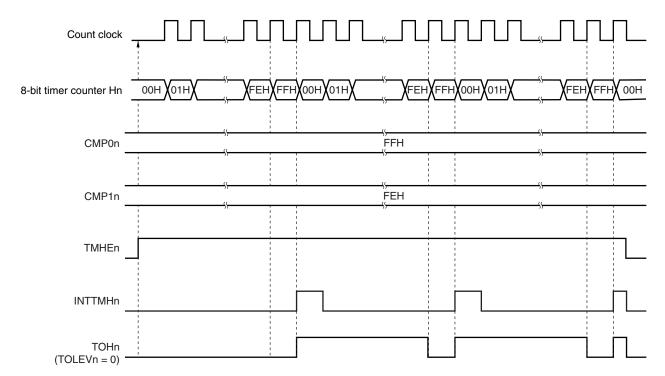

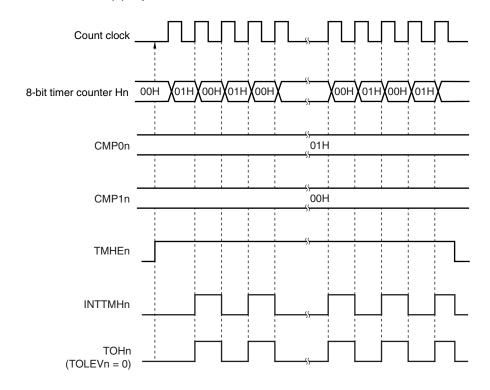

| 9.4.1 Operation as interval timer/square-wave output    | 226 |

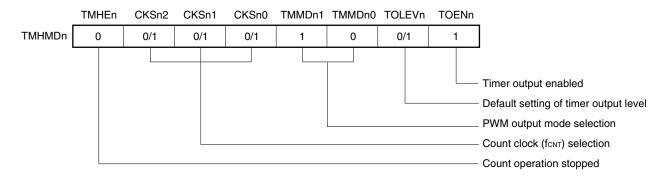

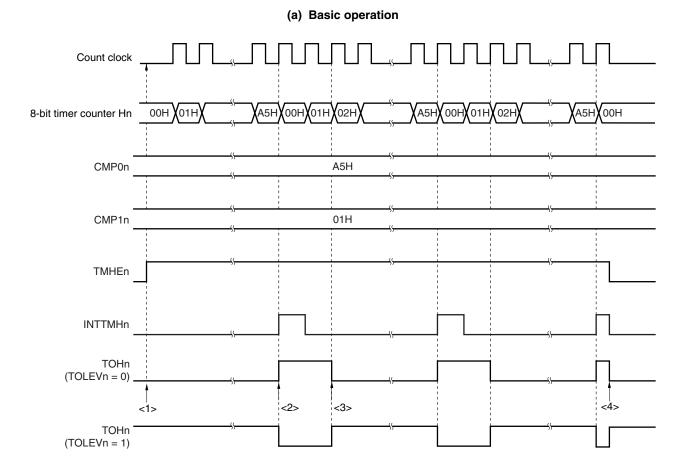

| 9.4.2 Operation as PWM output                           | 229 |

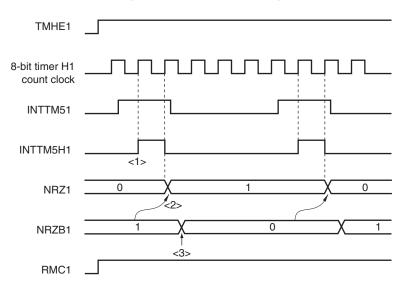

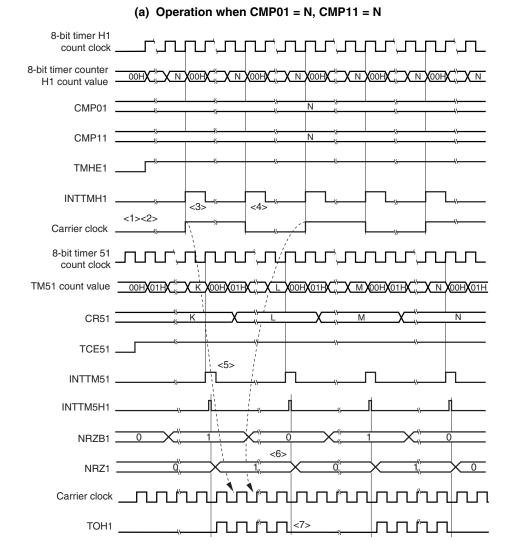

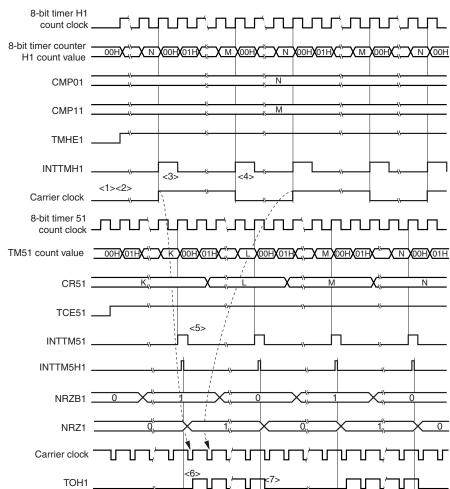

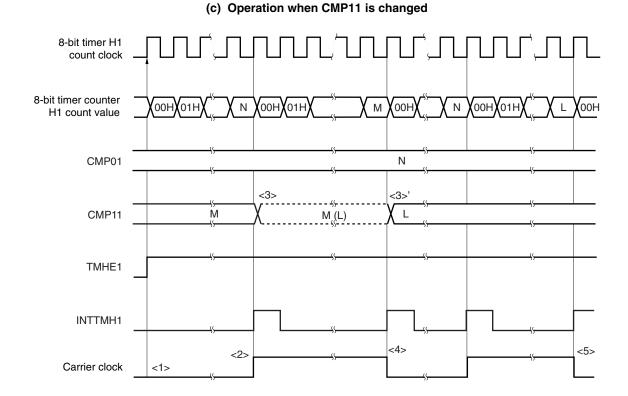

| 9.4.3 Carrier generator operation (8-bit timer H1 only) | 235 |

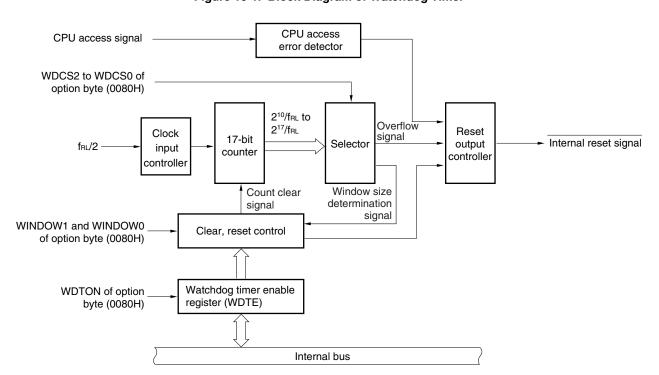

| CHAPTER 10 WATCHDOG TIMER                               | 242 |

| 10.1 Functions of Watchdog Timer                        |     |

| 10.2 Configuration of Watchdog Timer                    | 242 |

| 10.3 Register Controlling Watchdog Timer                | 244 |

| 10.4 Operation of Watchdog Timer                        | 245 |

| 10.4.1 Controlling operation of watchdog timer          | 245 |

| 10.4.2 Setting overflow time of watchdog timer          | 246 |

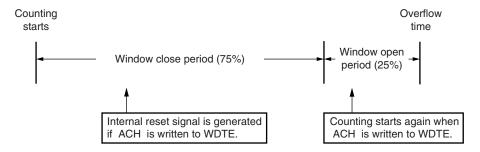

| 10.4.3 Setting window open period of watchdog timer     | 247 |

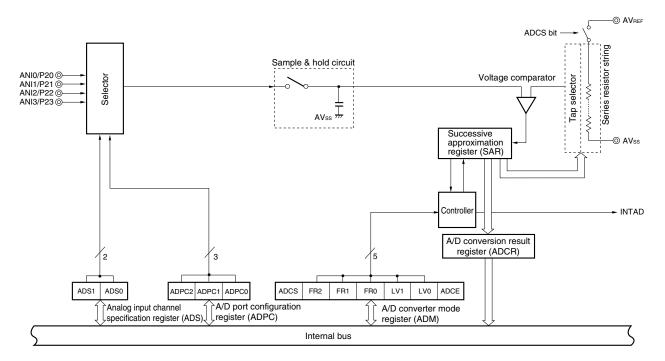

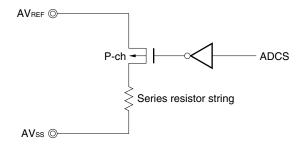

| CHAPTER 11 A/D CONVERTER                                | 249 |

| 11.1 Function of A/D Converter                          | 249 |

| 11.2 Configuration of A/D Converter                     |     |

| 11.3 Registers Used in A/D Converter                    | 252 |

| 11.4 A/D Converter Operations                           | 261 |

| 11.4.1 Basic operations of A/D converter                | 261 |

| 11.4.2 Input voltage and conversion results             | 263 |

| 11.4.3 A/D converter operation mode                     | 264 |

| 11.5 How to Read A/D Converter Characteristics Table    | 266 |

| 11.6 Cautions for A/D Converter                         | 268 |

| CHAPTER 12 SERIAL INTERFACE UARTO                       | 272 |

| 12.1 Functions of Serial Interface UART0                | 272 |

| 12.2 Configuration of Serial Interface UART0            | 273 |

| 12.3 Registers Controlling Serial Interface UART0       | 276 |

| 12.4 Operation of Serial Interface UART0                | 281 |

| 12.4.1 Operation stop mode                              | 281 |

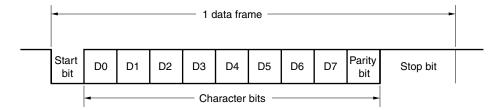

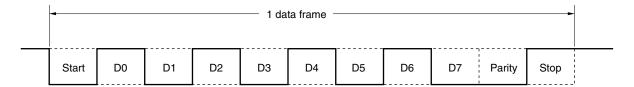

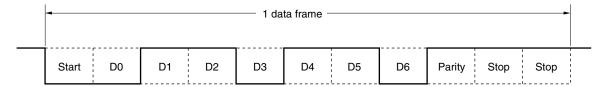

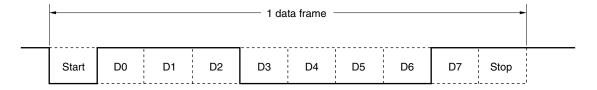

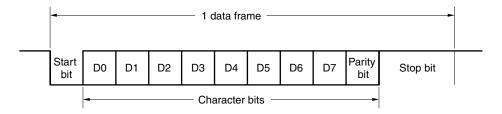

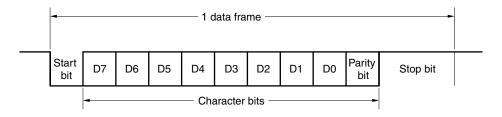

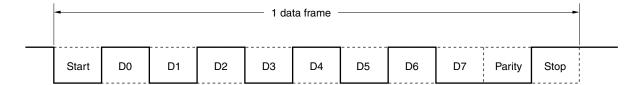

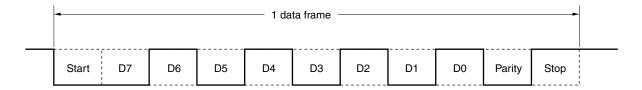

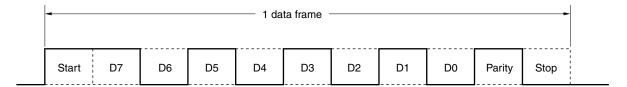

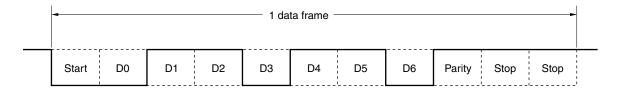

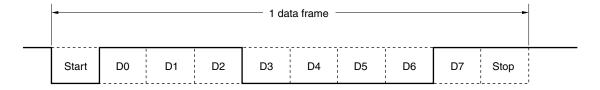

| 12.4.2 Asynchronous serial interface (UART) mode        | 282 |

| 12.4.3 Dedicated baud rate generator                    |     |

| 12.4.4 Calculation of baud rate                         | 289 |

| CHAPTER 13 SERIAL INTERFACE UART6                       |     |

| 13.1 Functions of Serial Interface UART6                |     |

| 13.2 Configuration of Serial Interface UART6            |     |

| 13.3 Registers Controlling Serial Interface UART6       |     |

| 13.4 Operation of Serial Interface UART6                |     |

| 13.4.1 Operation stop mode                              |     |

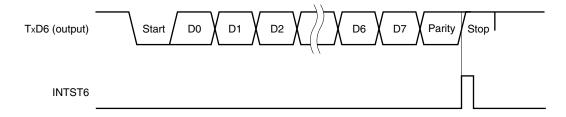

| 13.4.2 Asynchronous serial interface (UART) mode        | 310 |

| 13.4.3 Dedicated baud rate generator                                      | 323 |

|---------------------------------------------------------------------------|-----|

| 13.4.4 Calculation of baud rate                                           | 325 |

| CHAPTER 14 SERIAL INTERFACE CSI10                                         | 330 |

| 14.1 Functions of Serial Interface CSI10                                  | 330 |

| 14.2 Configuration of Serial Interface CSI10                              | 331 |

| 14.3 Registers Controlling Serial Interface CSI10                         |     |

| 14.4 Operation of Serial Interface CSI10                                  | 337 |

| 14.4.1 Operation stop mode                                                | 337 |

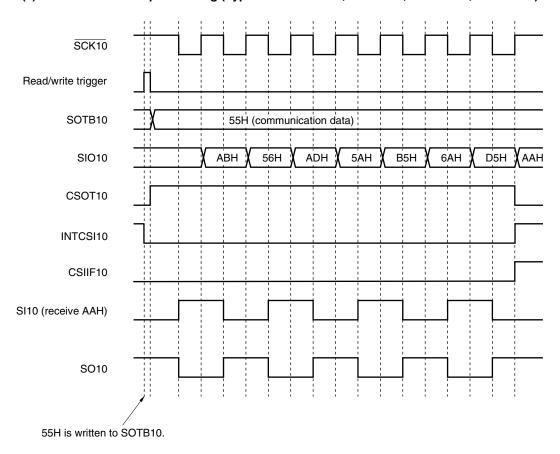

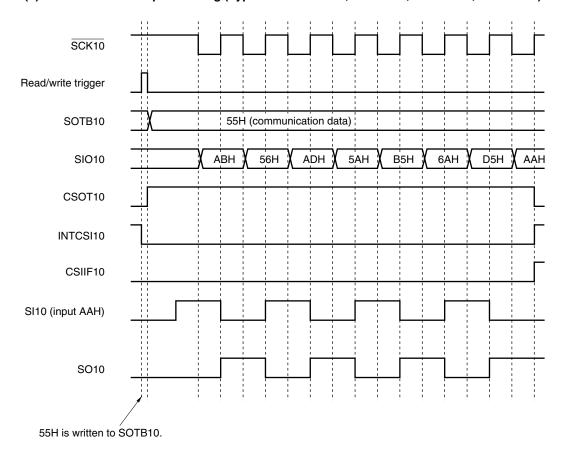

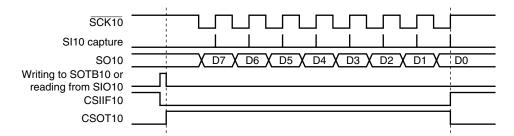

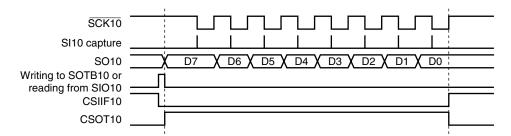

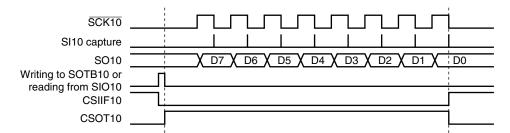

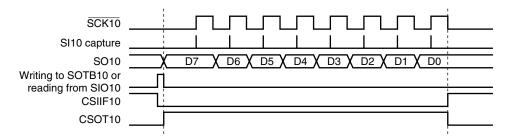

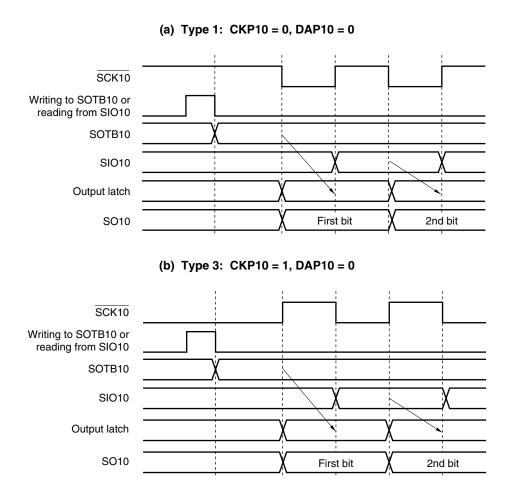

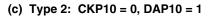

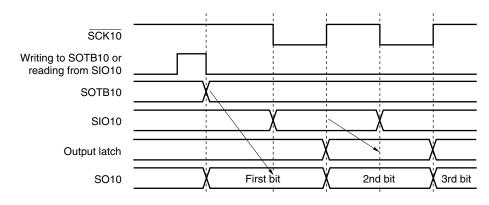

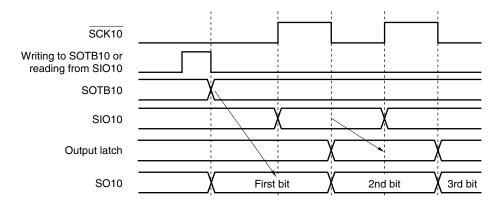

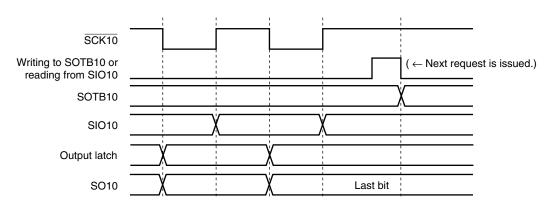

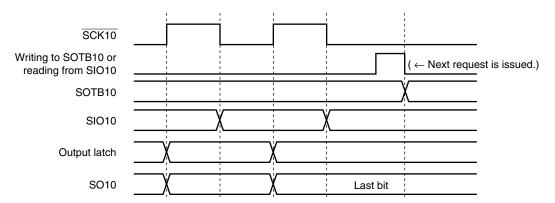

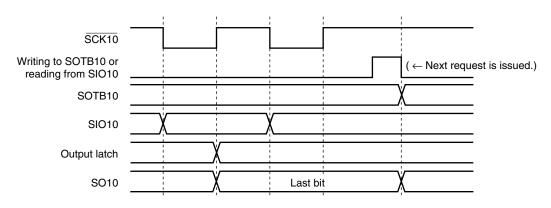

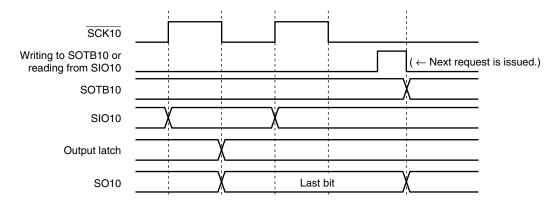

| 14.4.2 3-wire serial I/O mode                                             | 337 |

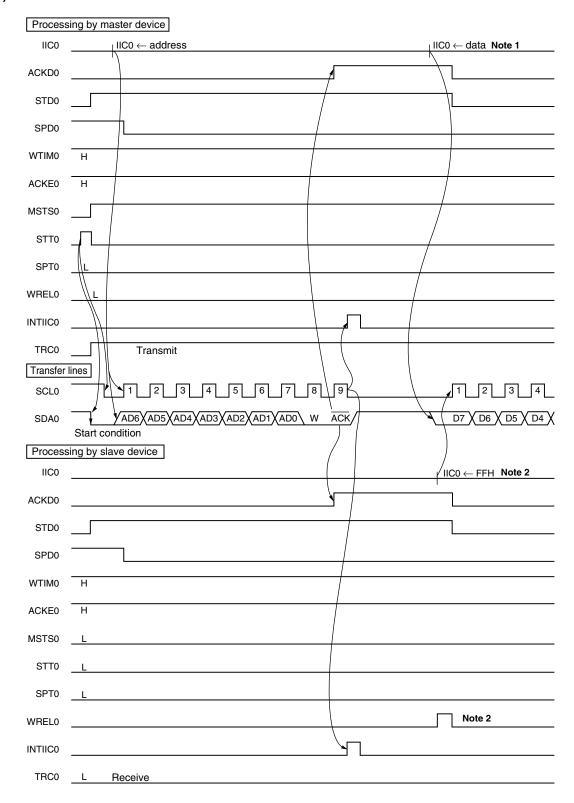

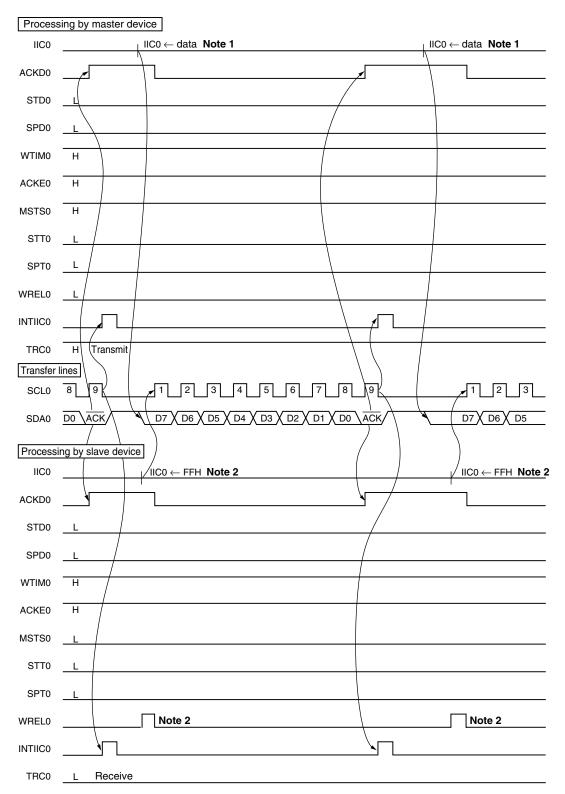

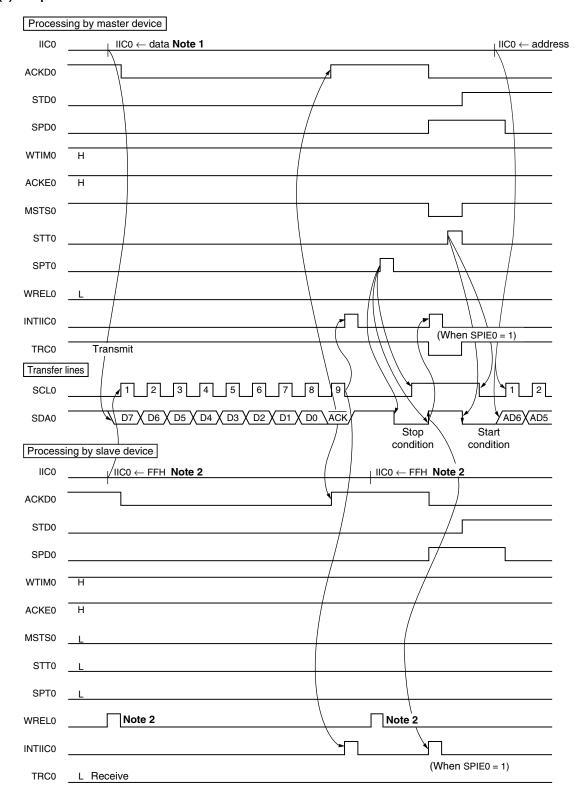

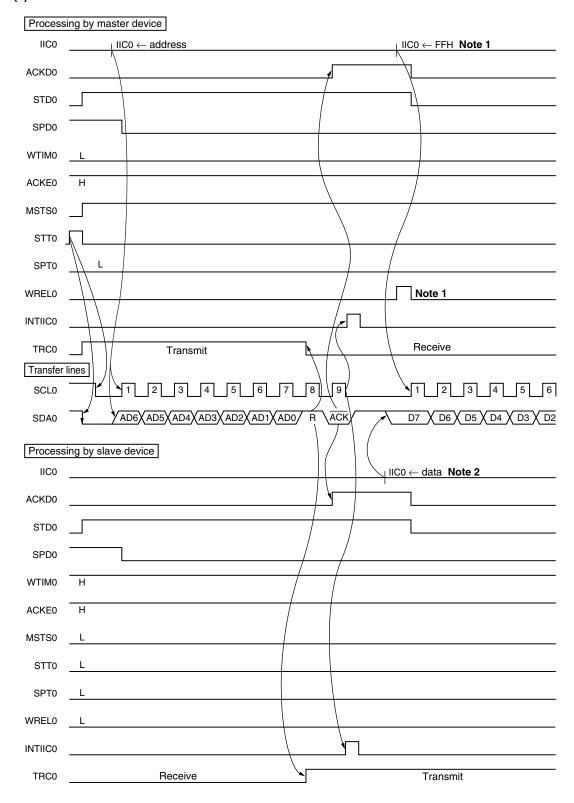

| CHAPTER 15 SERIAL INTERFACE IICO                                          | 348 |

| 15.1 Functions of Serial Interface IIC0                                   |     |

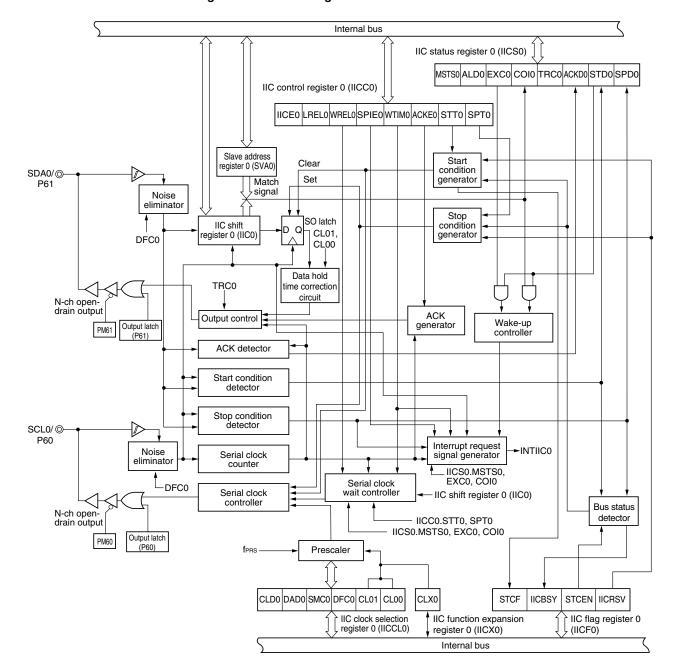

| 15.2 Configuration of Serial Interface IIC0                               |     |

| 15.3 Registers to Control Serial Interface IIC0                           | 354 |

| 15.4 I <sup>2</sup> C Bus Mode Functions                                  |     |

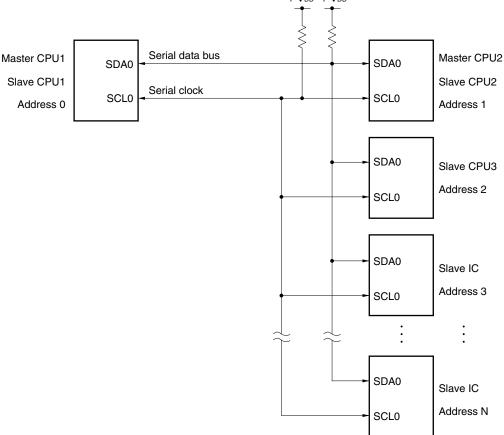

| 15.4.1 Pin configuration                                                  |     |

| 15.5 I <sup>2</sup> C Bus Definitions and Control Methods                 |     |

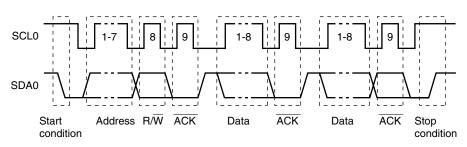

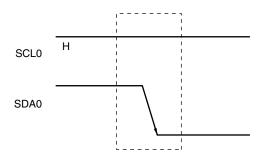

| 15.5.1 Start conditions                                                   | 368 |

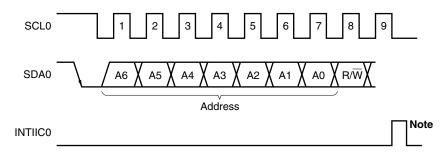

| 15.5.2 Addresses                                                          |     |

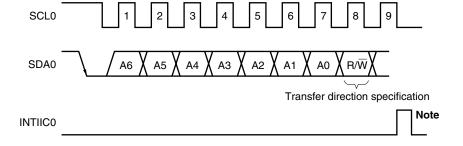

| 15.5.3 Transfer direction specification                                   |     |

| 15.5.4 Acknowledge (ACK)                                                  |     |

| 15.5.5 Stop condition                                                     |     |

| 15.5.6 Wait                                                               |     |

| 15.5.7 Canceling wait                                                     |     |

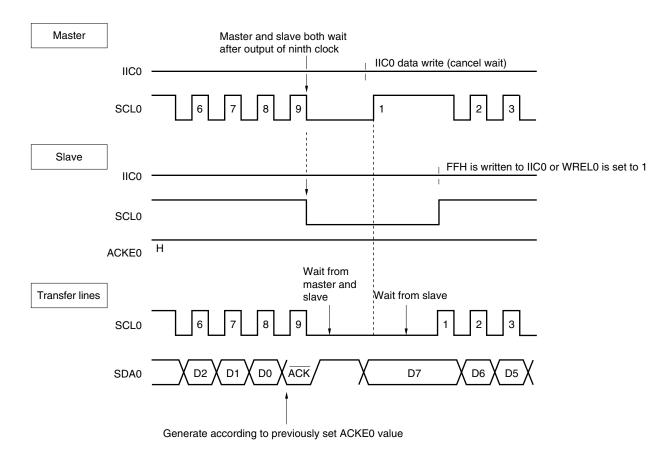

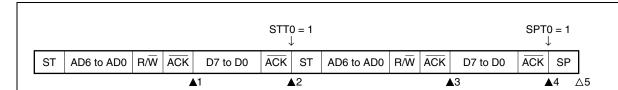

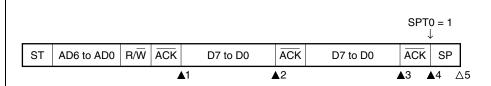

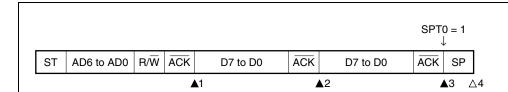

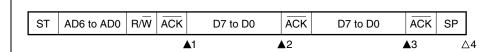

| 15.5.8 Interrupt request (INTIIC0) generation timing and wait control     |     |

| 15.5.9 Address match detection method                                     |     |

| 15.5.10 Error detection                                                   |     |

| 15.5.11 Extension code                                                    |     |

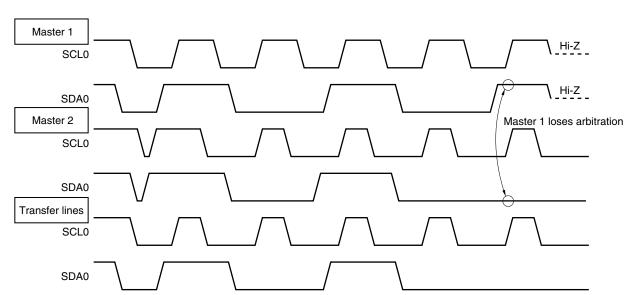

| 15.5.12 Arbitration                                                       |     |

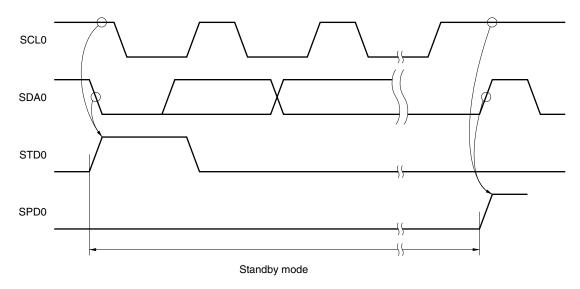

| 15.5.13 Wakeup function                                                   |     |

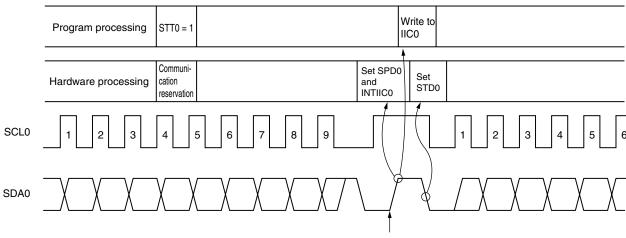

| 15.5.14 Communication reservation                                         |     |

| 15.5.15 Other cautions                                                    |     |

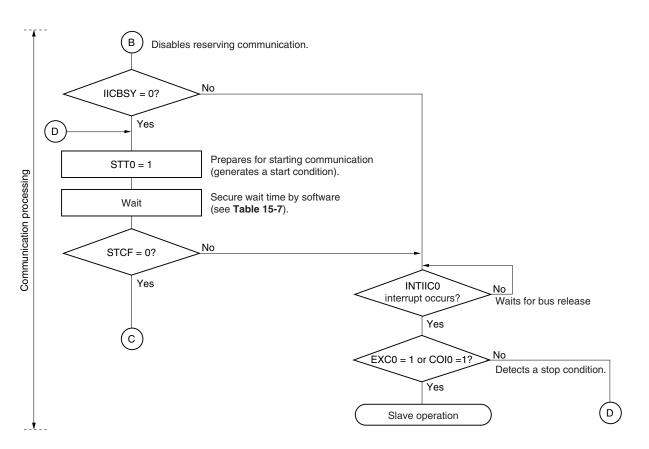

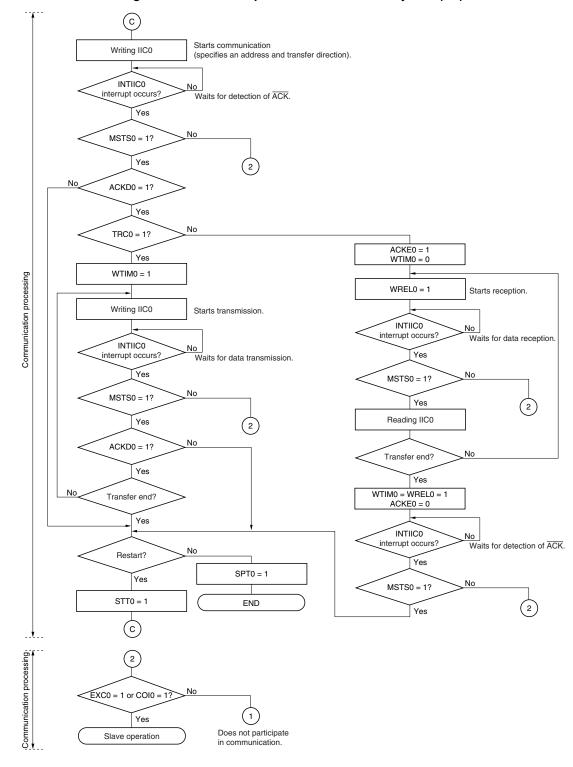

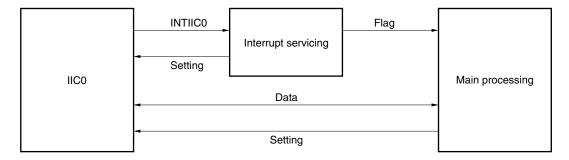

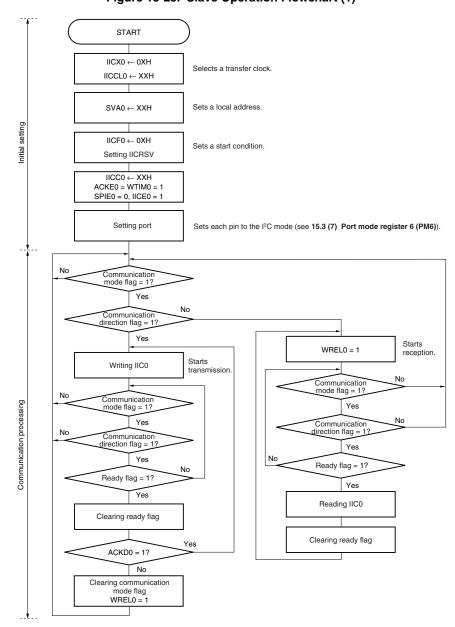

| 15.5.16 Communication operations                                          |     |

| 15.5.17 Timing of I <sup>2</sup> C interrupt request (INTIIC0) occurrence |     |

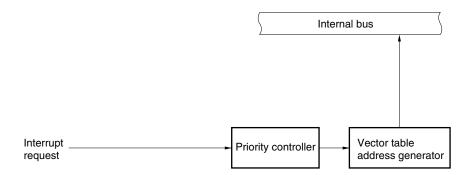

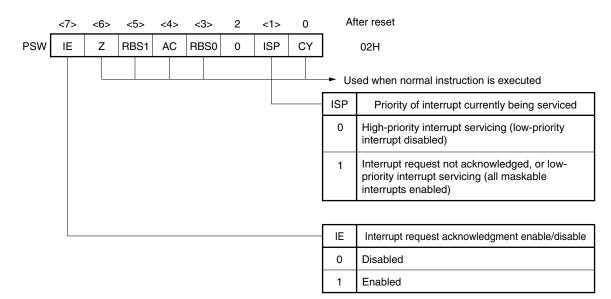

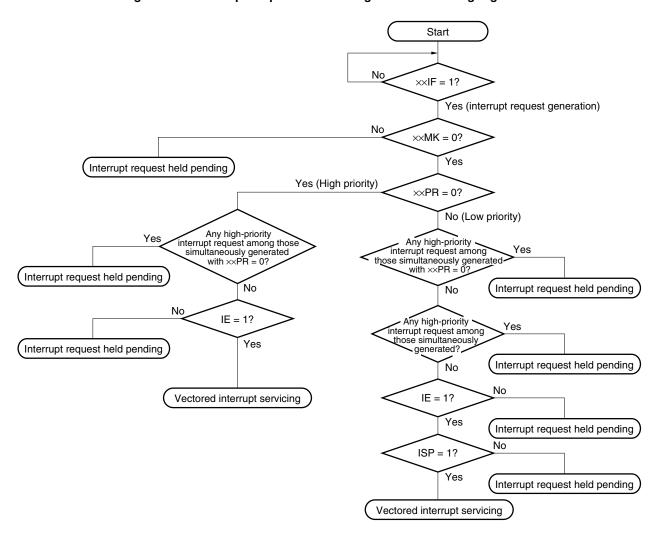

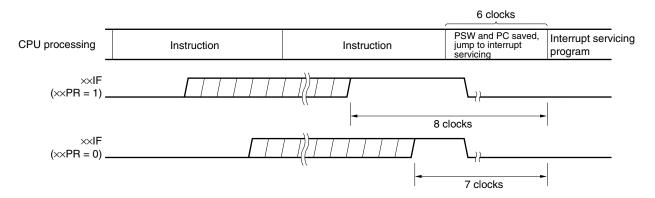

| CHAPTER 16 INTERRUPT FUNCTIONS                                            | 419 |

| 16.1 Interrupt Function Types                                             |     |

| 16.2 Interrupt Sources and Configuration                                  |     |

| 16.3 Registers Controlling Interrupt Functions                            |     |

| 16.4 Interrupt Servicing Operations                                       |     |

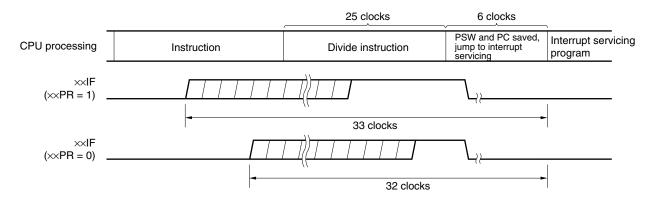

| 16.4.1 Maskable interrupt acknowledgement                                 |     |

| 16.4.2 Software interrupt request acknowledgement                         |     |

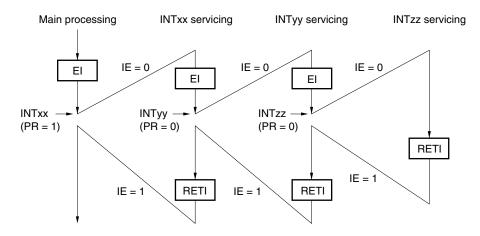

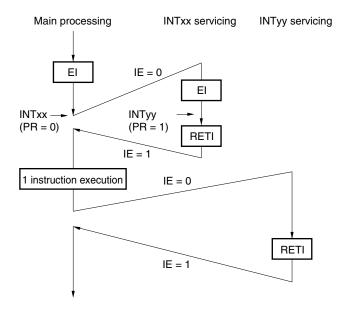

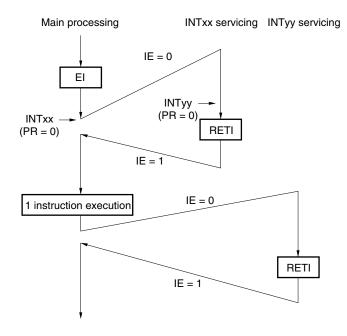

| 16.4.3 Multiple interrupt servicing                                       |     |

| 16.4.4 Interrupt request hold                                             |     |

| CHAPTER 17 STANDBY FUNCTION                                                            | 437 |

|----------------------------------------------------------------------------------------|-----|

| 17.1 Standby Function and Configuration                                                | 437 |

| 17.1.1 Standby function                                                                | 437 |

| 17.1.2 Registers controlling standby function                                          | 437 |

| 17.2 Standby Function Operation                                                        | 440 |

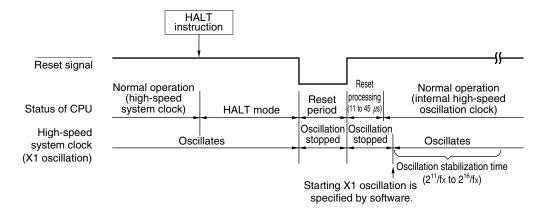

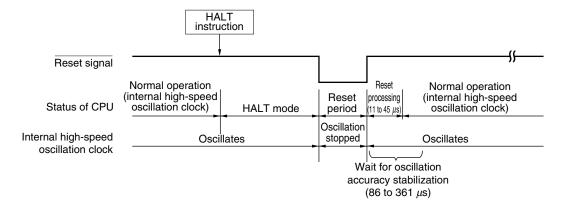

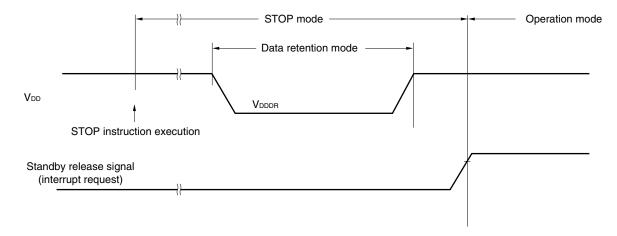

| 17.2.1 HALT mode                                                                       | 440 |

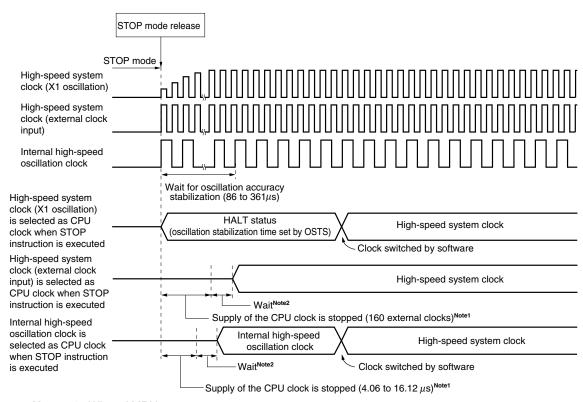

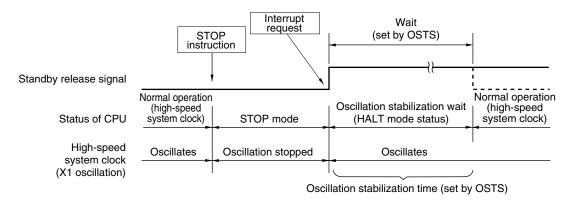

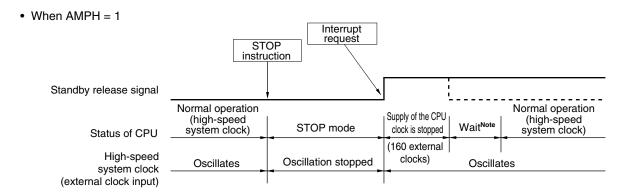

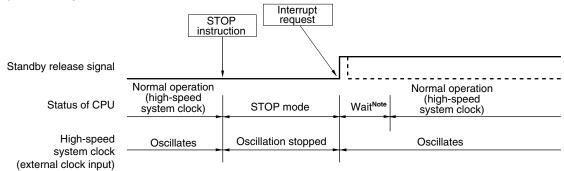

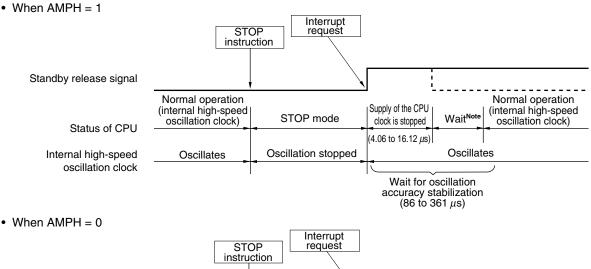

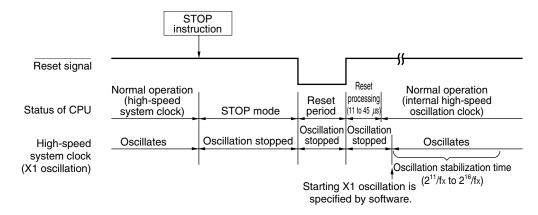

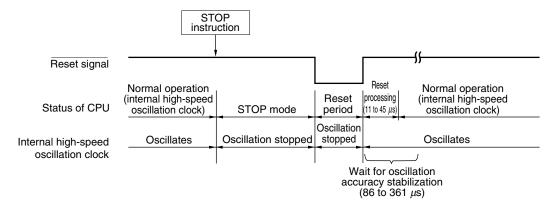

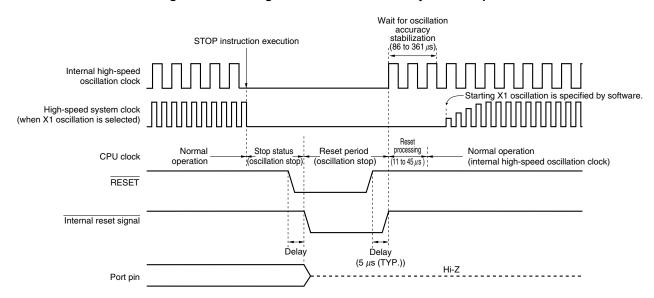

| 17.2.2 STOP mode                                                                       | 444 |

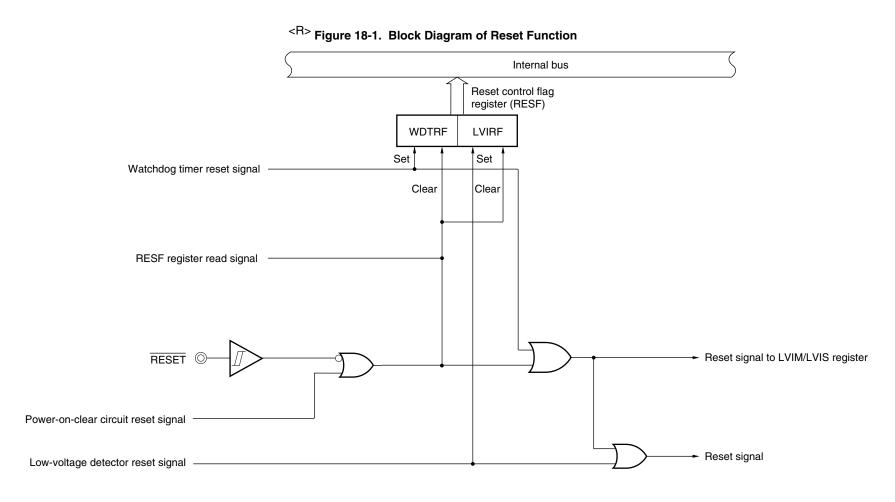

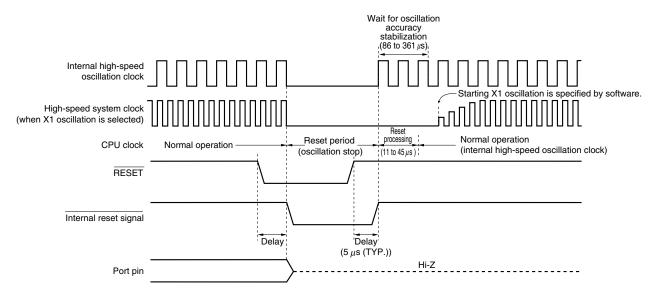

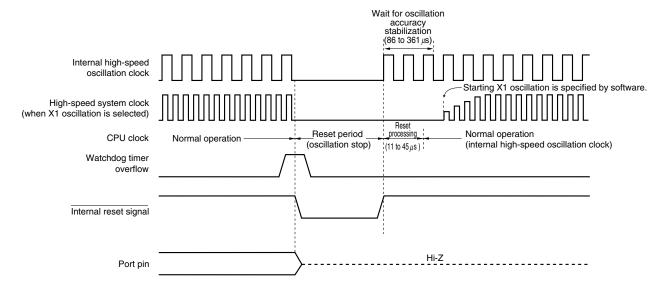

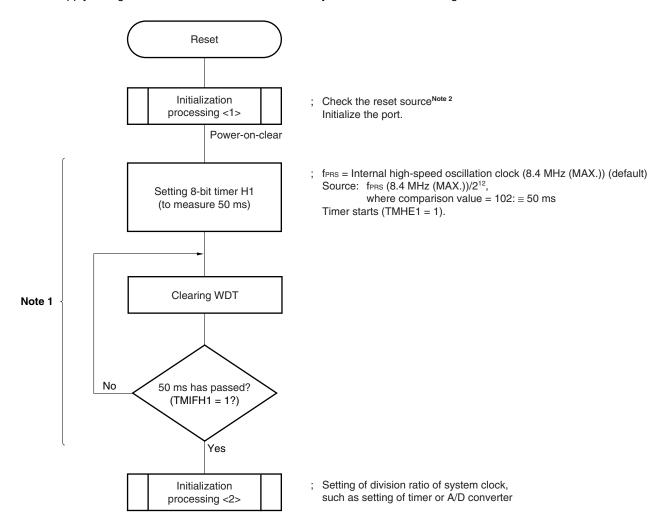

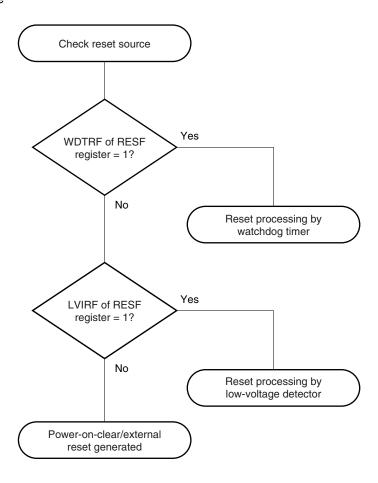

| CHAPTER 18 RESET FUNCTION                                                              | 450 |

| 18.1 Register for Confirming Reset Source                                              | 458 |

| CHAPTER 19 POWER-ON-CLEAR CIRCUIT                                                      | 459 |

| 19.1 Functions of Power-on-Clear Circuit                                               | 459 |

| 19.2 Configuration of Power-on-Clear Circuit                                           | 460 |

| 19.3 Operation of Power-on-Clear Circuit                                               | 460 |

| 19.4 Cautions for Power-on-Clear Circuit                                               | 463 |

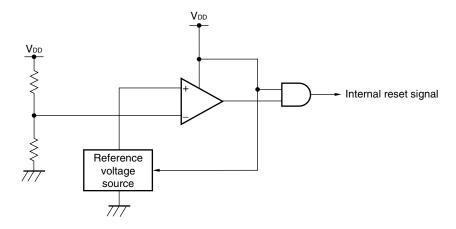

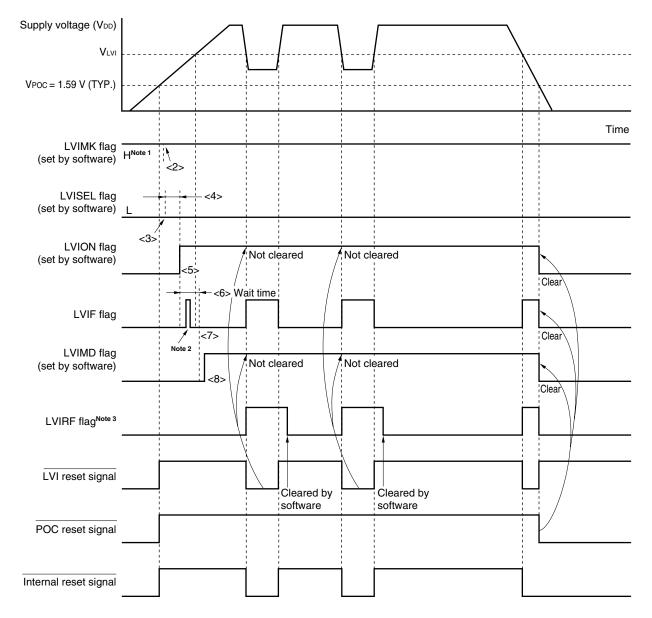

| CHAPTER 20 LOW-VOLTAGE DETECTOR                                                        | 465 |

| 20.1 Functions of Low-Voltage Detector                                                 | 465 |

| 20.2 Configuration of Low-Voltage Detector                                             |     |

| 20.3 Registers Controlling Low-Voltage Detector                                        |     |

| 20.4 Operation of Low-Voltage Detector                                                 |     |

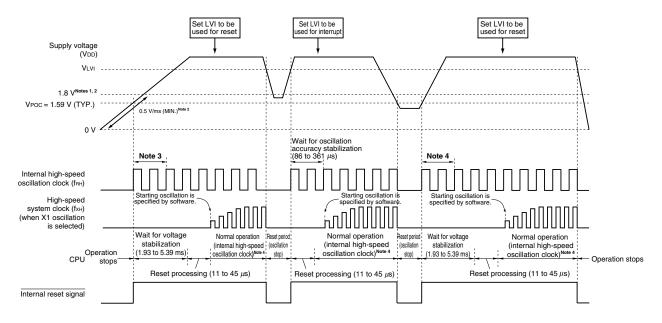

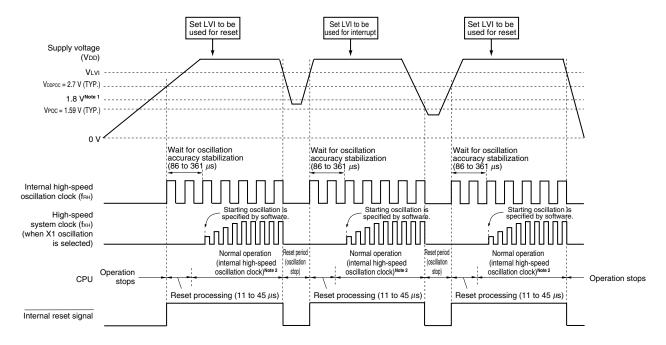

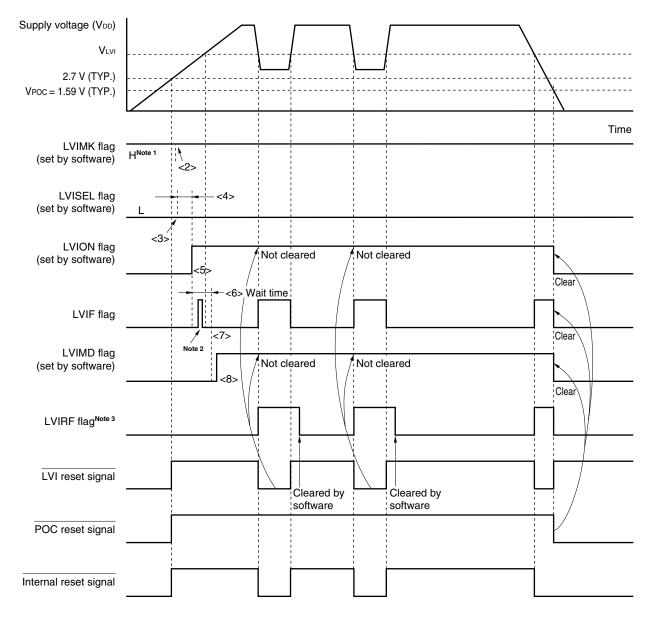

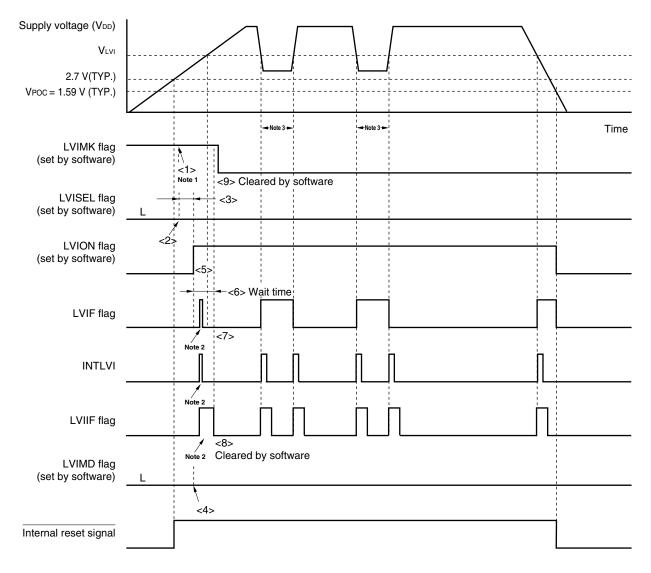

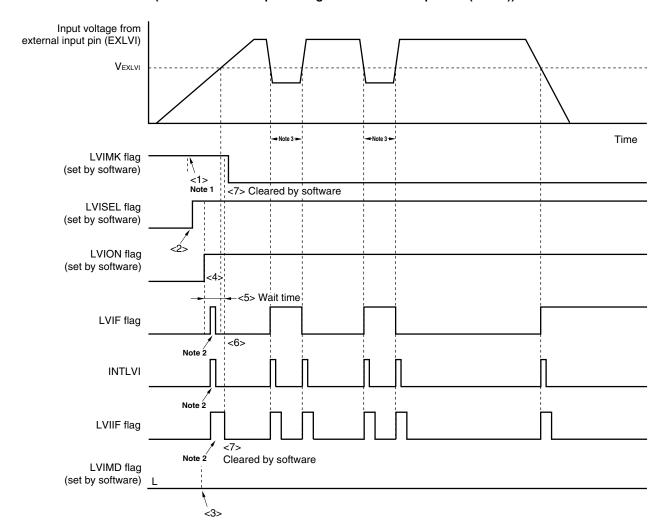

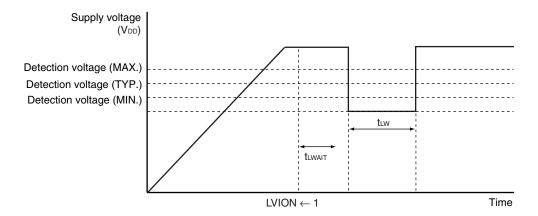

| 20.4.1 When used as reset                                                              | 470 |

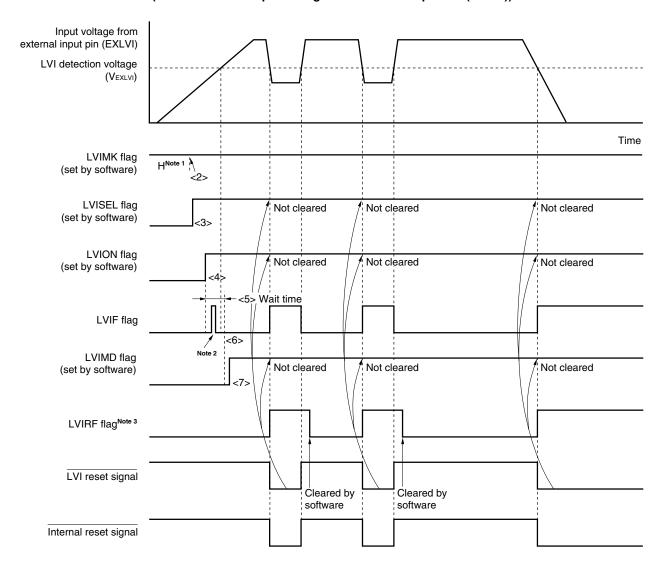

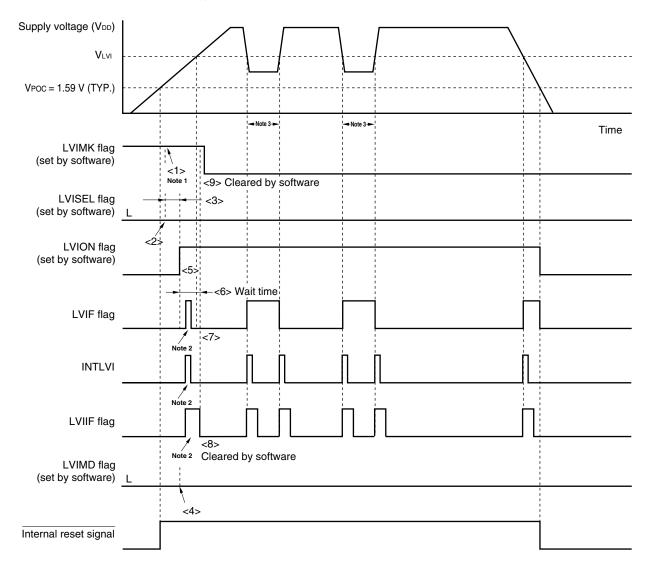

| 20.4.2 When used as interrupt                                                          | 475 |

| 20.5 Cautions for Low-Voltage Detector                                                 | 480 |

| 20.5.1 When the supply voltage fluctuates in the vicinity of the LVI detection voltage | 480 |

| 20.5.2 Cautions when using LVI as reset signal                                         | 481 |

| CHAPTER 21 OPTION BYTE                                                                 | 482 |

| 21.1 Functions of Option Bytes                                                         | 482 |

| 21.2 Format of Option Byte                                                             |     |

| CHAPTER 22 FLASH MEMORY                                                                |     |

| 22.1 Internal Memory Size Switching Register                                           |     |

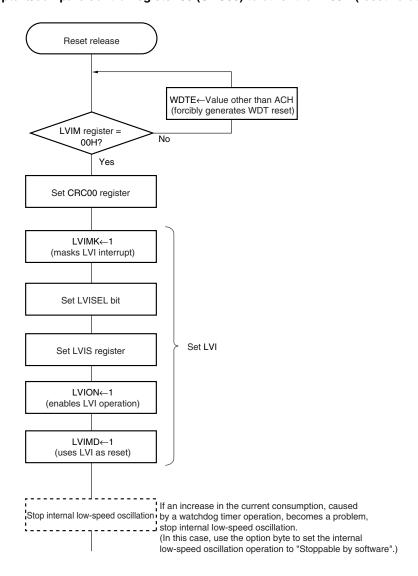

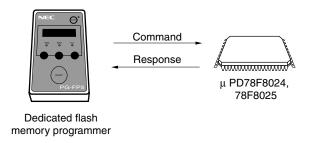

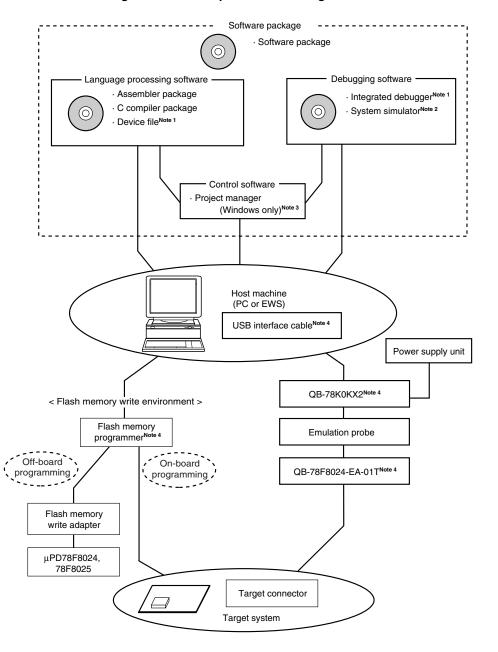

| 22.2 Writing with Flash Memory Programmer                                              |     |

| 22.3 Programming Environment                                                           |     |

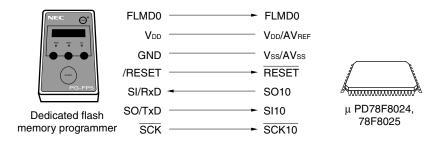

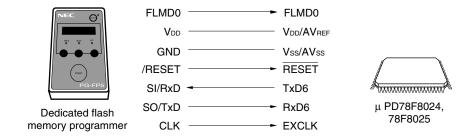

| 22.4 Communication Mode                                                                |     |

| 22.5 Handling of Pins on Board                                                         |     |

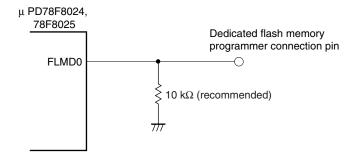

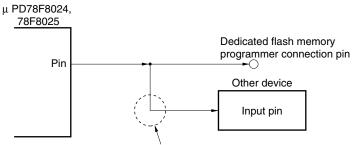

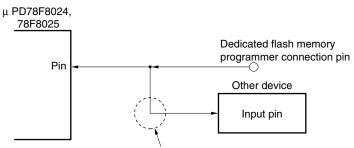

| 22.5.1 FLMD0 pin                                                                       |     |

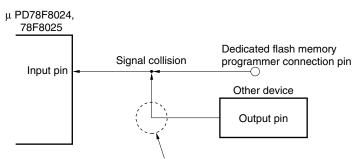

| 22.5.2 Serial interface pins                                                           |     |

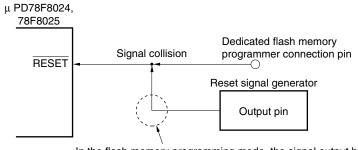

| 22.5.3 RESET pin                                                                       |     |

| 22.5.4 Port pins                                                                       |     |

| 22.5.5 REGC pin                                                                        |     |

| 22.5.6 Other signal pins                                                               |     |

| 22.5.7 Power supply                                                                    |     |

| 22.6 Programming Method                                                                |     |

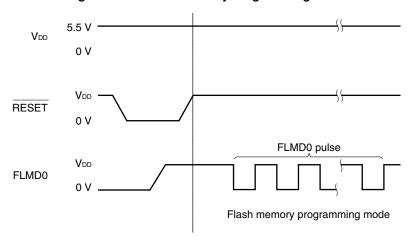

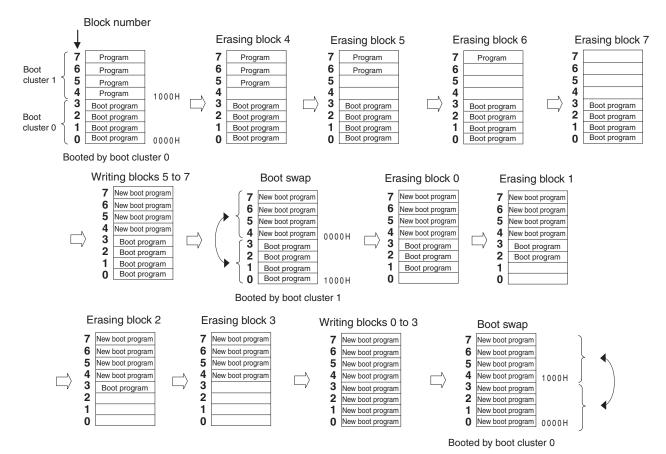

| 22.6.1 Controlling flash memory                                                        | 492 |

| 492               |

|-------------------|

| 493               |

| 494               |

| 495               |

| 497               |

| 504               |

| 506               |

| 506               |

| 506               |

| 507               |

| 507               |

| 508               |

| 516               |

| 519               |

| 519               |

| 540               |

| 543               |

| 543               |

| 544               |

| 545               |

|                   |

| 545               |

| 546               |

| 547               |

| 549               |

| 549               |

| 550               |

| 550               |

| 550               |

| 551               |

| 552               |

| 553               |

|                   |

| 554               |

|                   |

| 554<br>554<br>557 |

| 554               |

| 554<br>557        |

|                   |

#### **CHAPTER 1 OUTLINE**

#### 1.1 Features

- O On-chip constant current driver with selectable buck or boost converter

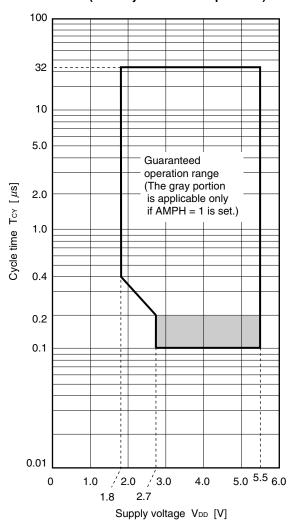

- O Minimum instruction execution time can be changed from high speed (0.1  $\mu$ s: @ 20 MHz operation with high-speed system clock) to low speed (1.6  $\mu$ s: @ 20 MHz operation with high-speed system clock)

- O General-purpose register: 8 bits × 32 registers (8 bits × 8 registers × 4 banks)

- O ROM, RAM capacities

| Iter        | 3 ,          |                         | Data Memory                 |  |

|-------------|--------------|-------------------------|-----------------------------|--|

| Part Number | (ROM)        |                         | (Internal High-Speed RAM)   |  |

| μPD78F8024  | Flash memory | 8 KB <sup>Note 1</sup>  | 512 bytes <sup>Note 1</sup> |  |

| μPD78F8025  |              | 32 KB <sup>Note 1</sup> | 1 KB Note 1                 |  |

<R>

- O On-chip single-power-supply flash memory

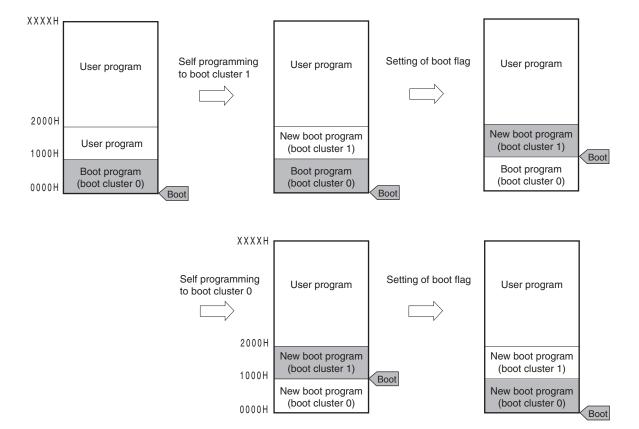

- O Self-programming (with boot swap function)

- On-chip power-on-clear (POC) circuit and low-voltage detector (LVI)

- O On-chip watchdog timer (operable with the on-chip internal low-speed oscillation clock)

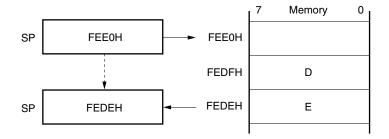

- O I/O ports: 23 (N-ch open drain: 2)

- O Timer: 6 channels

16-bit timer/event counter:

8-bit timer/event counter:

8-bit timer:

2 channels

8-bit timer:

2 channels

Watchdog timer:

1 channel

O Serial interface: 3 channels

UART (LIN (Local Interconnect Network)-bus supported): 1 channel

CSI/UART<sup>Note 2</sup>: 1 channel

I<sup>2</sup>C: 1 channel

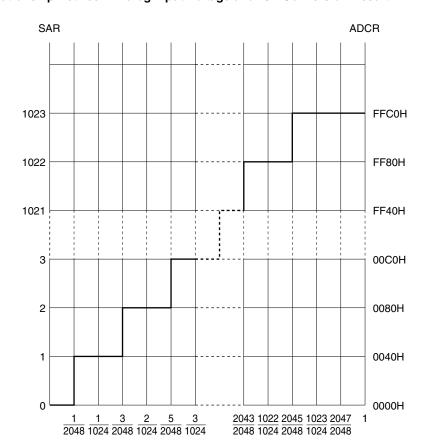

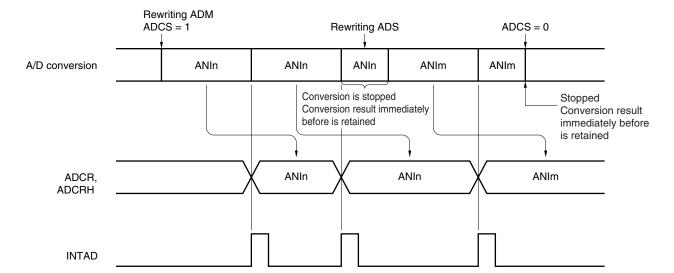

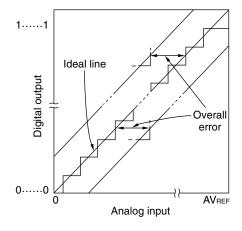

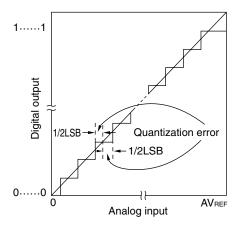

- O 10-bit resolution A/D converter (AVREF = 2.3 to 5.5 V): 4 channels

- O Power supply voltage: VDD = 1.8 to 5.5 V Note 3

- O Operating ambient temperature:  $T_A = -40 \text{ to } +85^{\circ}\text{C}$

- **Notes 1.** Set the internal flash memory and internal high-speed RAM capacities to be used by the internal memory size switching register (IMS) after release of reset.

- 2. Select either of the functions of these alternate-function pins.

- 3. When using the constant current driver:  $V_{DD} = CV_{DD} = 4.5$  to 5.5 V When not using the constant current driver:  $V_{DD} = 1.8$  to 5.5 V

# 1.2 Applications

- O Heater

- O Motor

- O LCD backlight

- O Lighting

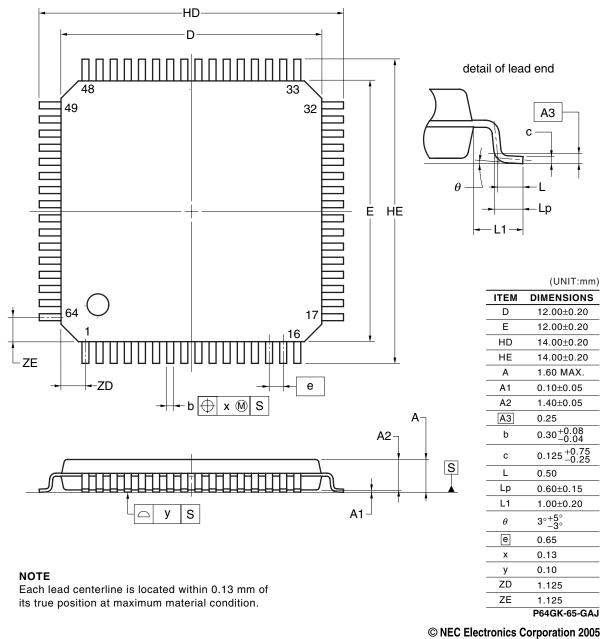

# 1.3 Ordering Information

• Flash memory version (lead-free product)

| Part Number              | Package                     |  |

|--------------------------|-----------------------------|--|

| $\mu$ PD78F8024GK-GAJ-AX | 64-pin plastic LQFP (12x12) |  |

| $\mu$ PD78F8025GK-GAJ-AX | 64-pin plastic LQFP (12x12) |  |

<R>

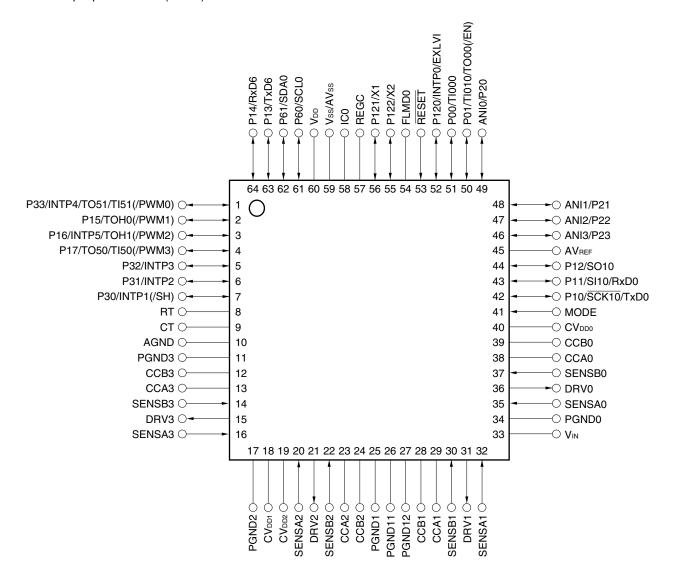

# 1.4 Pin Configuration (Top View)

• 64-pin plastic LQFP (12x12)

- Cautions 1. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F: recommended).

- 2. ANIO/P20 to ANI3/P23 pins are set in the analog input mode after release of reset.

- 3. Connect the IC0 (Internally Connected) pin directly to Vss.

#### Pin Identification

CPU Part

FLMD0:

RESET: ANI0 to ANI3: Analog input Reset

AVREE: Analog reference voltage RxD0, RxD6: Receive data

SCK10: AVss: Analog ground Serial clock input/output EXCLK: External clock input SCL0: Serial clock input/output SDA0: (main system clock) Serial data input/output

> External potential input SI10: Serial data input

EXLVI: for low-voltage detector SO10: Serial data output

Flash programming mode TI000, TI010,

INTP0 to INTP5: External interrupt input TI50, TI51: Timer input

P00, P01: Port 0 TO00,

P10 to P17: Port 1 TO50, TO51,

P20 to P23: Port 2 TOH0, TOH1: Timer output P30 to P33: TxD0, TxD6: Port 3 Transmit data P60, P61: Port 6 V<sub>DD</sub>: Power supply P120 to P122: Port 12 Vss: Ground

REGC: X1, X2: Regulator capacitance Crystal oscillator (main system clock)

• Constant Current Driver Part with Selectable Buck or Boost Converter

AGND: Analog ground

CCA0 to CCA3, CCB0 to CCB3: Capacitor for phase correction CT: Capacitor for triangular oscillator

CVDD0 to CVDD2: Power supply for constant current driver with selectable buck or boost converter

DRV0 to DRV3: Gate drive output for N-ch MOSFET

(EN): Enable signal for operation with pull-down (200 k $\Omega$  (TYP.) )

IC0: Internally connected

Buck mode or Boost mode select input with pull-down (200 k $\Omega$  (TYP.) ) MODE:

PGND0 to PGND3, PGND11,

PGND12: Ground

(PWM0 to PWM3): PWM pulse input for dimming control with pull-down (200 k $\Omega$  (TYP.) )

RT: Resistor for triangular oscillator

SENSA0 to SENSA3: Current sense for each channel at buck Mode / Voltage monitor for overvoltage

protection at boost mode

SENSB0 to SENSB3: Current sense for each channel at boost mode

(SH): Thermal protection alert VIN: High voltage power supply

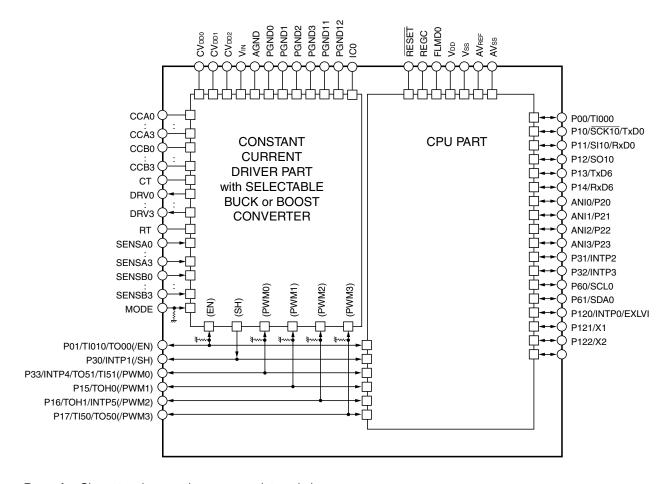

# 1.5 Configuration

$\mu$ PD78F8024 and 78F8025 are the SIP (System in a Package) product configured by the CPU part and the constant current driver part with selectable buck or boost converter.

Remark Characters in parentheses are an internal pin.

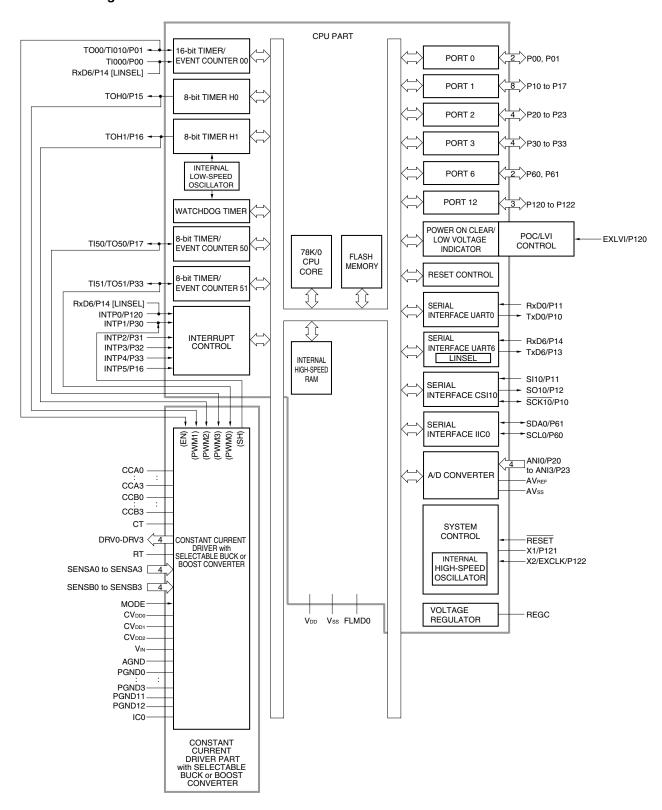

# 1.6 Block Diagram

Remark Characters in parentheses are an internal pin.

# 1.7 Outline of Functions

(1/2)

|                                                                        | Ite                                                   | m                                      | <i>µ</i> PD78F8024                                                                                                                                                                         | μPD78F8025                     |  |

|------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| Internal<br>memory                                                     | Flash m                                               | emory<br>gramming supported)           | 8 KB <sup>Note 1</sup> 32 KB <sup>Note 1</sup>                                                                                                                                             |                                |  |

|                                                                        | High-spe                                              | eed RAM                                | 512 bytes <sup>Note 1</sup>                                                                                                                                                                | 1 KB <sup>Note 1</sup>         |  |

| Memory sp                                                              | Memory space                                          |                                        | 64 KB                                                                                                                                                                                      |                                |  |

| Main                                                                   | Main High-speed system                                |                                        | X1 (crystal/ceramic) oscillation, external m                                                                                                                                               | ain system clock input (EXCLK) |  |

| system clock when not using the constant current driver when using the |                                                       |                                        | 1 to 20 MHz: V <sub>DD</sub> = 2.7 to 5.5 V,<br>1 to 5 MHz: V <sub>DD</sub> = 1.8 to 5.5 V<br>1 to 20 MHz: V <sub>DD</sub> = CV <sub>DD</sub> = 4.5 to 5.5 V                               |                                |  |

|                                                                        |                                                       | constant current<br>driver             |                                                                                                                                                                                            |                                |  |

|                                                                        | Internal                                              | high-speed oscillation                 | Internal oscillation                                                                                                                                                                       |                                |  |

|                                                                        | clock When not using the constant current driver      |                                        | 8 MHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                               |                                |  |

|                                                                        |                                                       | When using the constant current driver | 8 MHz (TYP.): V <sub>DD</sub> = CV <sub>DD</sub> = 4.5 to 5.5 V                                                                                                                            |                                |  |

| Internal lov                                                           | v-speed osc                                           | illation clock                         | Internal oscillation                                                                                                                                                                       |                                |  |

| (for TMH1,<br>WDT)                                                     | (for TMH1, When not using the constant current driver |                                        | 240 kHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                             |                                |  |

|                                                                        | When us                                               | sing the constant<br>driver            | 240 kHz (TYP.): V <sub>DD</sub> = CV <sub>DD</sub> = 4.5 to 5.5 V                                                                                                                          |                                |  |

| General-pu                                                             | ırpose regis                                          | ters                                   | 8 bits × 32 registers (8 bits × 8 registers ×                                                                                                                                              | 4 banks)                       |  |

| Minimum ir                                                             | nstruction ex                                         | xecution time                          | 0.1 $\mu$ s (high-speed system clock: @ fxH = 20 MHz operation)                                                                                                                            |                                |  |

|                                                                        |                                                       |                                        | 0.25 μs (internal high-speed oscillation clock: @ f <sub>RH</sub> = 8 MHz (TYP.) operation)                                                                                                |                                |  |

| Instruction                                                            | Instruction set                                       |                                        | <ul> <li>8-bit operation, 16-bit operation</li> <li>Multiply/divide (8 bits × 8 bits, 16 bits ÷ 8</li> <li>Bit manipulate (set, reset, test, and Bool</li> <li>BCD adjust, etc.</li> </ul> |                                |  |

| I/O ports                                                              |                                                       |                                        | Total: 23 CMOS I/O: 21 N-ch open-drain I/O (6 V tolerance): 2                                                                                                                              |                                |  |

| Timers                                                                 |                                                       |                                        | <ul> <li>16-bit timer/event counter: 1 channel</li> <li>8-bit timer/event counter: 2 channels</li> <li>8-bit timer: 2 channels</li> <li>Watchdog timer: 1 channel</li> </ul>               |                                |  |

|                                                                        | Timer o                                               | utputs                                 | 5 (PWM output: 4, PPG output: 1)                                                                                                                                                           |                                |  |

| A/D converter                                                          |                                                       |                                        | 10-bit resolution × 4 channels (AV <sub>REF</sub> = 2.3 to 5.5 V)                                                                                                                          |                                |  |

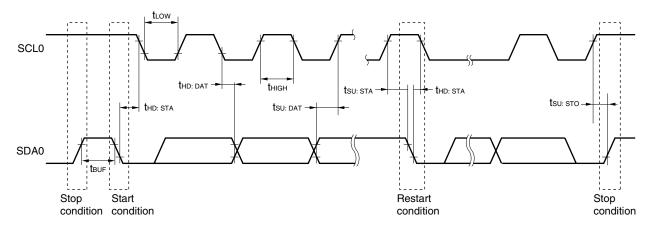

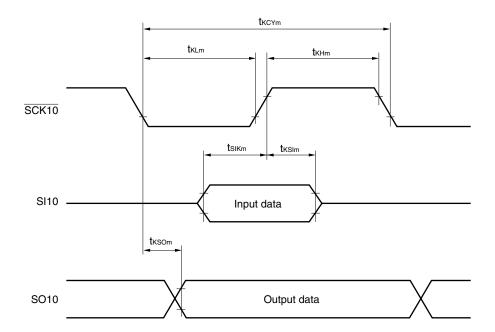

| Serial interface                                                       |                                                       |                                        | <ul> <li>UART supporting LIN-bus: 1 channel</li> <li>3-wire serial I/O/UART<sup>Note 2</sup>: 1 channel</li> <li>I<sup>2</sup>C bus: 1 channel</li> </ul>                                  |                                |  |

**Notes 1.** Set the internal flash memory and internal high-speed RAM capacities to be used by the internal memory size switching register (IMS) after release of reset.

2. Select either of the functions of these alternate-function pins.

(2/2)

|                                                                 | Item                                       | μPD78F8024                                                                                                                                                                    | μPD78F8025 |

|-----------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Constant current driver with selectable buck or boost converter |                                            | Boost mode: 4 channels     Buck mode: 4 channels                                                                                                                              |            |

| Vectored interrupt                                              | Internal                                   | 14                                                                                                                                                                            |            |

| sources                                                         | External                                   | 6                                                                                                                                                                             |            |

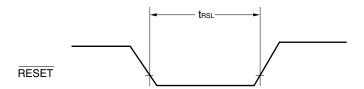

| Reset                                                           |                                            | <ul> <li>Reset using RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by power-on-clear</li> <li>Internal reset by low-voltage detector</li> </ul> | or         |

| Power supply voltage                                            | When not using the constant current driver | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                |            |

|                                                                 | When using the constant current driver     | V <sub>DD</sub> = CV <sub>DD</sub> = 4.5 to 5.5 V                                                                                                                             |            |

| Operating ambient                                               | temperature                                | T <sub>A</sub> = -40 to +85°C                                                                                                                                                 |            |

| Package                                                         |                                            | 64-pin plastic LQFP (12×12)                                                                                                                                                   |            |

An outline of the timer is shown below.

|           |                         | 16-Bit Timer/<br>Event Counter<br>00 | 8-Bit Timer/Event Counters 8-Bit Timers H0 and H1 50 and 51 |           | 8-Bit Timers H0 and H1 |                          | Watchdog<br>Timer |

|-----------|-------------------------|--------------------------------------|-------------------------------------------------------------|-----------|------------------------|--------------------------|-------------------|

|           |                         | TM00                                 | TM50                                                        | TM51      | TMH0                   | TMH1                     |                   |

| Function  | Interval timer          | 1 channel                            | 1 channel                                                   | 1 channel | 1 channel              | 1 channel                | -                 |

|           | External event counter  | 1 channel                            | 1 channel                                                   | 1 channel | -                      | -                        | -                 |

|           | PPG output              | 1 output                             | Ī                                                           | -         | ı                      | -                        | _                 |

|           | PWM output              | _                                    | 1 output                                                    | 1 output  | 1 output               | 1 output                 | -                 |

|           | Pulse width measurement | 2 inputs                             | -                                                           | -         | -                      | -                        | -                 |

|           | Square-wave output      | 1 output                             | 1 output                                                    | 1 output  | 1 output               | 1 output                 | -                 |

|           | Carrier generator       | -                                    | Î                                                           | ı         | 1                      | 1 output <sup>Nore</sup> | -                 |

|           | Watchdog timer          | -                                    | _                                                           | -         | _                      | -                        | 1 channel         |

| Interrupt | source                  | 2                                    | 1                                                           | 1         | 1                      | 1                        | -                 |

**Note** TM51 and TMH1 can be used in combination as a carrier generator mode.

# **CHAPTER 2 PIN FUNCTIONS**

# 2.1 Pin Function List

# 2.1.1 CPU Part

# (1) Port functions

| Function Name | I/O | Function                                                                                                                                 | After Reset                                                       | Alternate Function         |       |

|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|-------|

| P00           | I/O | Port 0.                                                                                                                                  | Input port                                                        | TI000                      |       |

| P01           |     | 2-bit I/O port. Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be specified by a software setting. |                                                                   | TI010/TO00 (/EN)           |       |

| P10           | I/O | Port 1.                                                                                                                                  | Input port                                                        | SCK10/TxD0                 |       |

| P11           |     | 8-bit I/O port.                                                                                                                          |                                                                   | SI10/RxD0                  |       |

| P12           |     | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specified by a software                         |                                                                   | SO10                       |       |

| P13           |     | setting.                                                                                                                                 |                                                                   | TxD6                       |       |

| P14           |     |                                                                                                                                          |                                                                   | RxD6                       |       |

| P15           |     |                                                                                                                                          |                                                                   | TOH0 (/PWM1)               |       |

| P16           |     |                                                                                                                                          |                                                                   | TOH1/INTP5<br>(/PWM2)      |       |

| P17           |     |                                                                                                                                          |                                                                   | TI50/TO50<br>(/PWM3)       |       |

| P20 to P23    | I/O | Port 2. 4-bit I/O port. Input/output can be specified in 1-bit units.                                                                    | Analog input                                                      | ANI0 to ANI3               |       |

| P30           | I/O | Port 3.                                                                                                                                  | Input port                                                        | INTP1 (/SH)                |       |

| P31           |     |                                                                                                                                          | 4-bit I/O port. Input/output can be specified in 1-bit units.     |                            | INTP2 |

| P32           |     |                                                                                                                                          | Use of an on-chip pull-up resistor can be specified by a software |                            | INTP3 |

| P33           |     | setting.                                                                                                                                 |                                                                   | INTP4/TI51/TO51<br>(/PWM0) |       |

| P60           | I/O | Port 6.                                                                                                                                  | Input port                                                        | SCL0                       |       |

| P61           |     | 2-bit I/O port. Output is N-ch open-drain output (6 V tolerance). Input/output can be specified in 1-bit units.                          |                                                                   | SDA0                       |       |

| P120          | I/O | 3-bit I/O port.                                                                                                                          | Input port                                                        | INTP0/EXLVI                |       |

| P121          | 1   |                                                                                                                                          |                                                                   | X1                         |       |

| P122          |     | Input/output can be specified in 1-bit units.  Only for P120, use of an on-chip pull-up resistor can be specified by a software setting. |                                                                   | X2/EXCLK                   |       |

# (2) Non-port functions (1/2)

| Function Name | I/O    | Function                                                                                                                                                | After Reset  | Alternate Function        |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|

| ANI0 to ANI3  | Input  | A/D converter analog input                                                                                                                              | Analog input | P20 to P23                |

| EXLVI         | Input  | Potential input for external low-voltage detection                                                                                                      | Input port   | P120/INTP0                |

| FLMD0         | -      | Flash memory programming mode setting                                                                                                                   | -            | -                         |

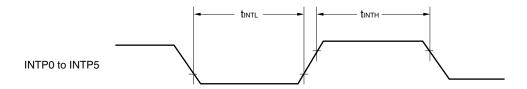

| INTP0         | Input  | External interrupt request input for which the valid edge (rising                                                                                       | Input port   | P120/EXLVI                |

| INTP1         |        | edge, falling edge, or both rising and falling edges) can be                                                                                            |              | P30 (/SH)                 |

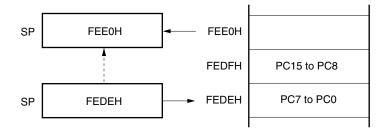

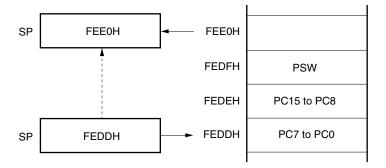

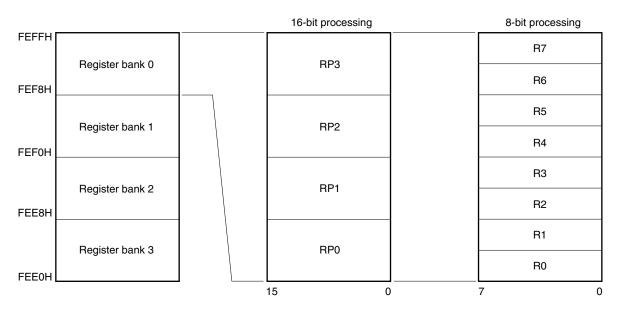

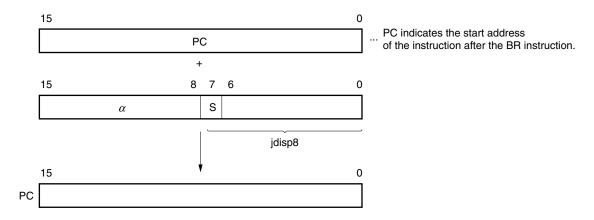

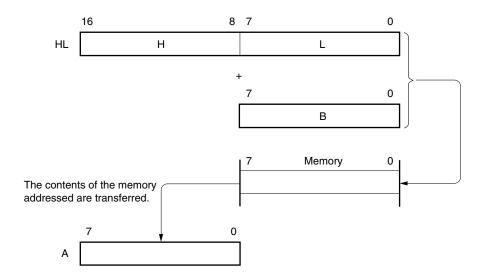

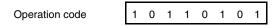

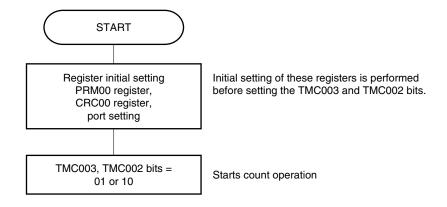

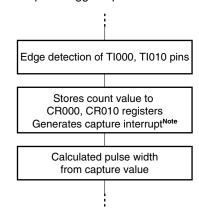

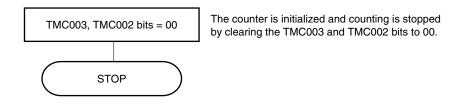

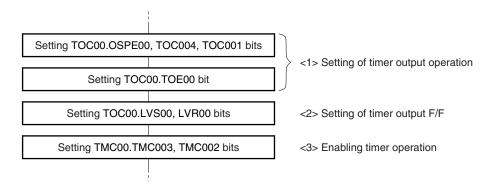

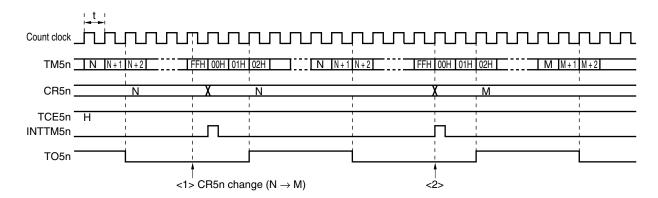

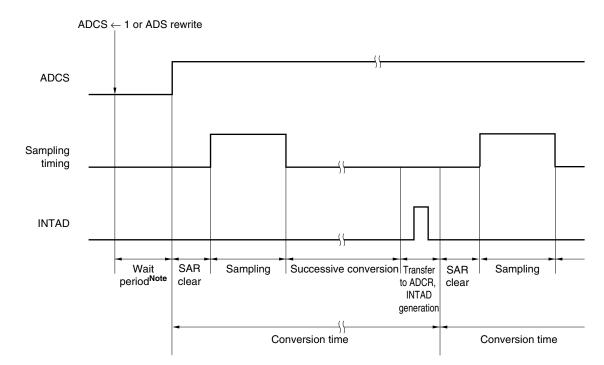

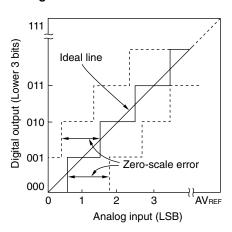

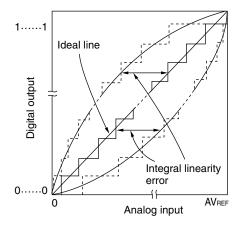

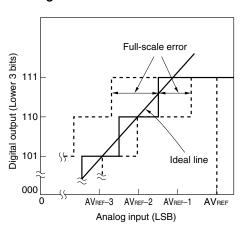

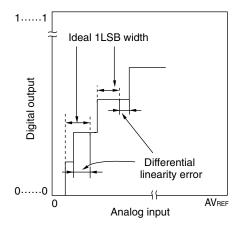

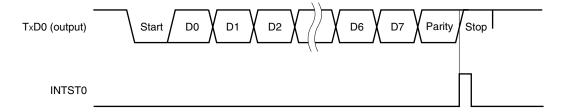

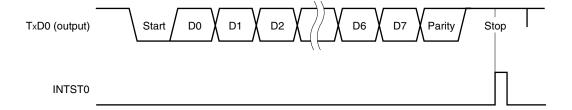

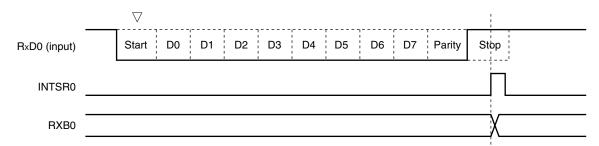

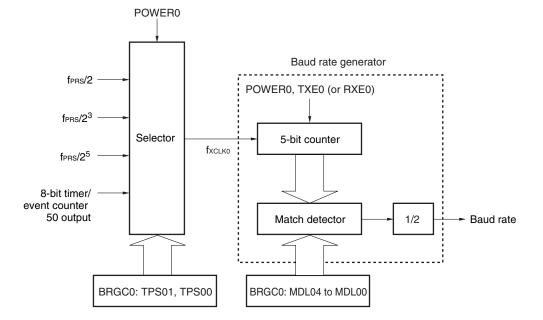

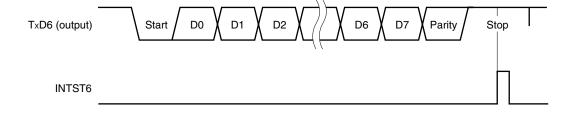

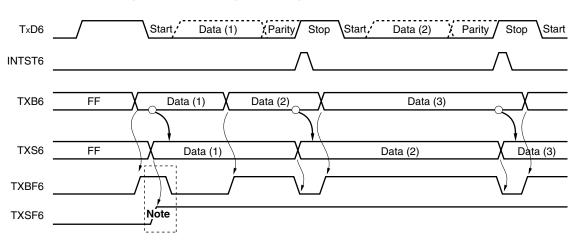

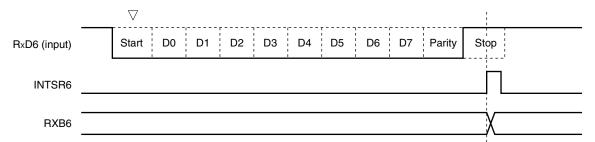

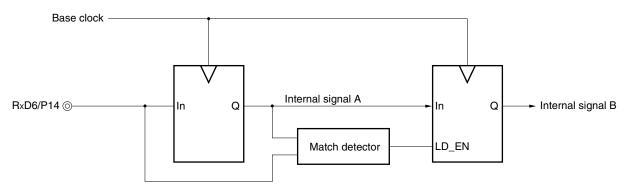

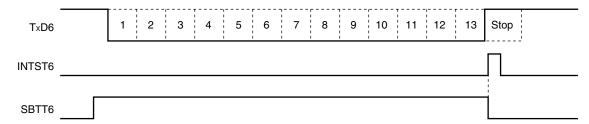

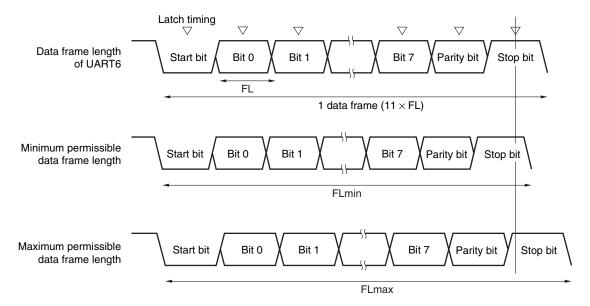

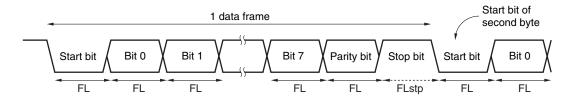

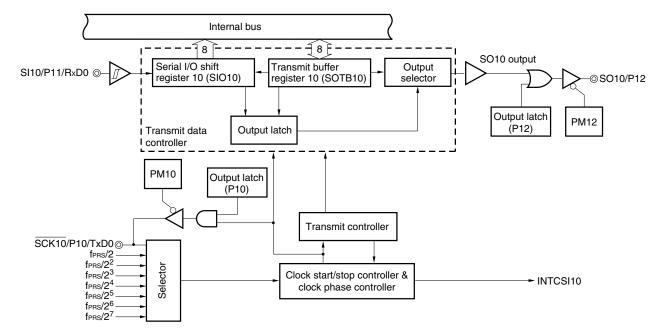

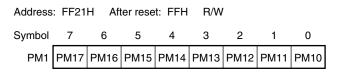

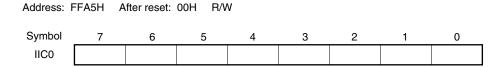

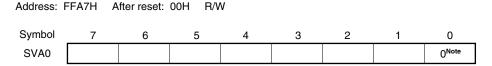

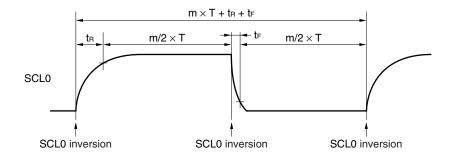

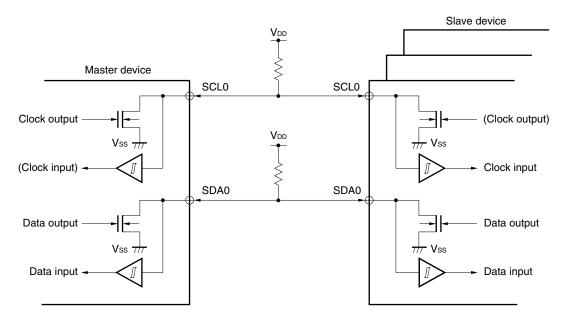

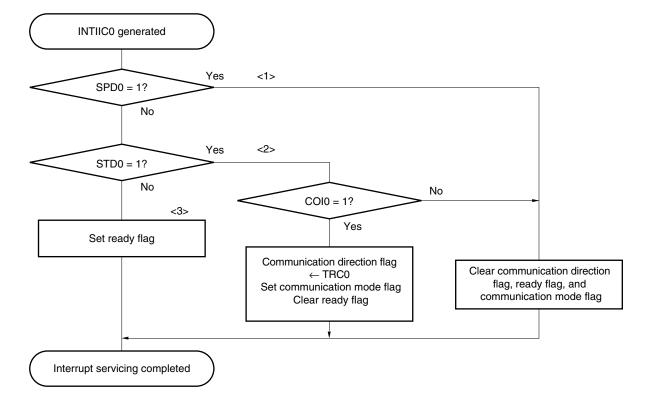

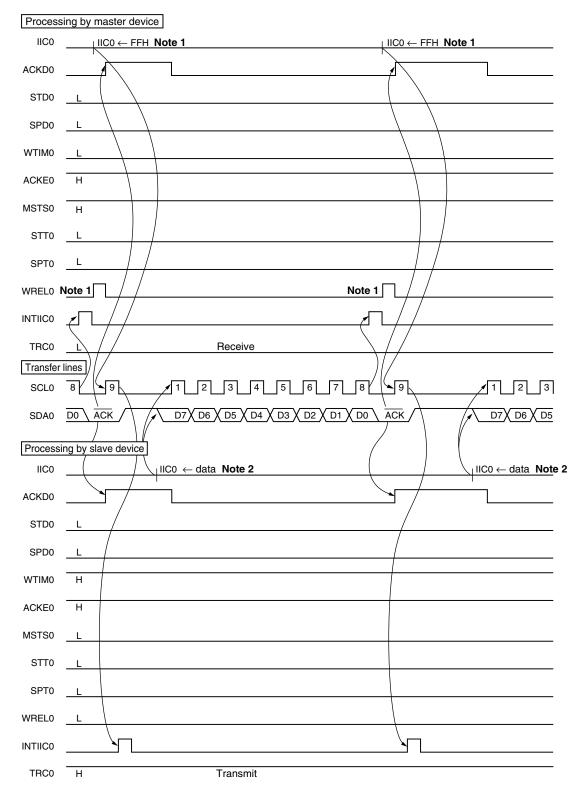

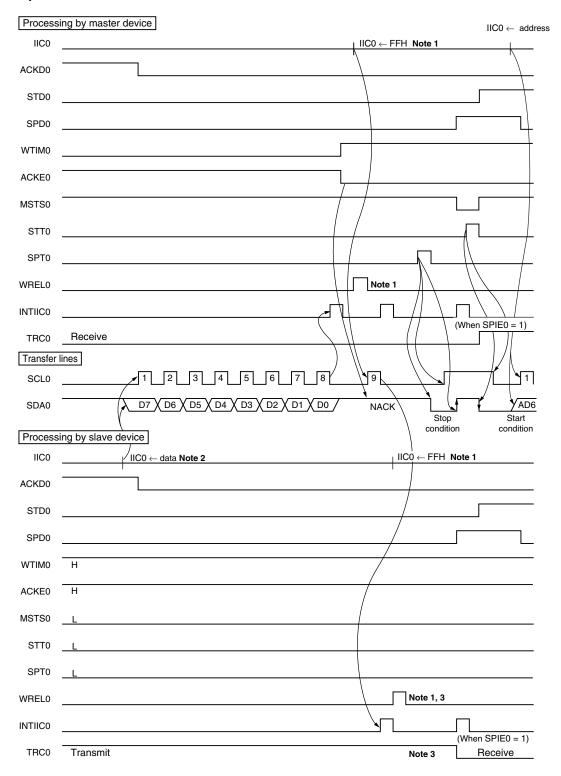

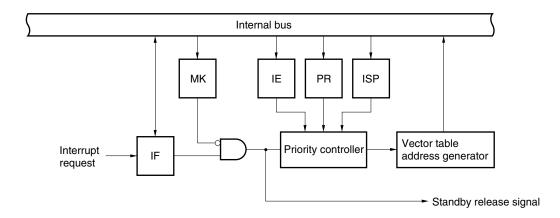

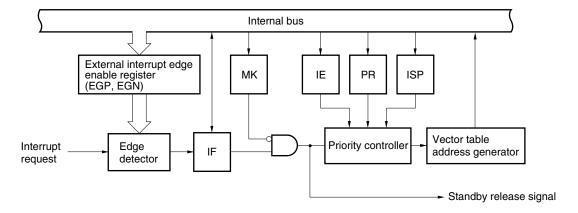

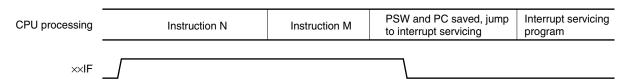

| INTP2         |        | specified                                                                                                                                               |              | P31                       |