The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7751 Group, SH7751R Group

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family / SH7750 Series

Page ii of liv

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics

does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages

incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by von.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(2012.4)

## **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

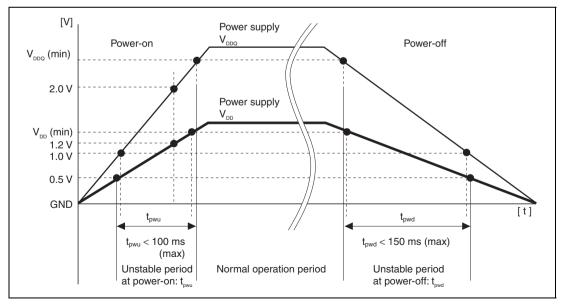

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

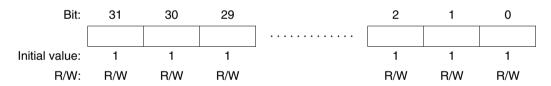

### 5. Reading from/Writing to Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

## **Preface**

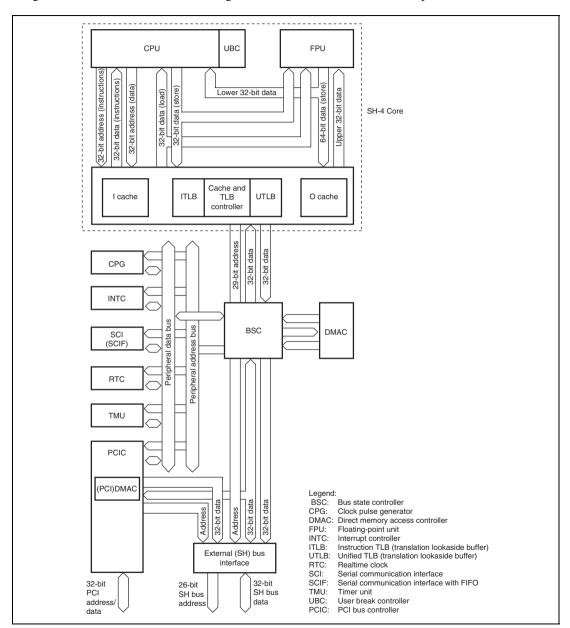

The SH-4 (SH7751 Group (SH7751, SH7751R)) microprocessor incorporates the 32-bit SH-4 CPU and is also equipped with peripheral functions necessary for configuring a user system.

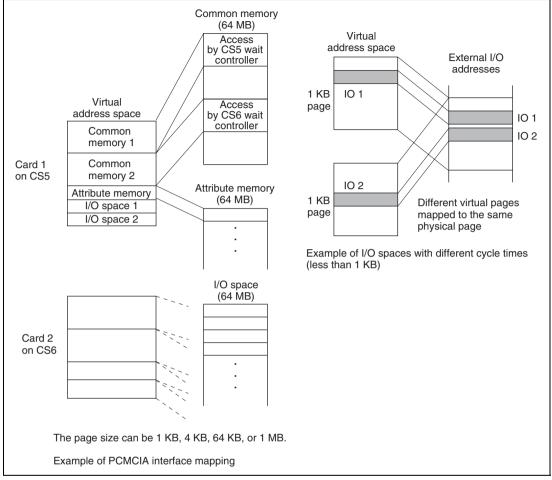

The SH7751 Group is built in with a variety of peripheral functions such as cache memory, memory management unit (MMU), interrupt controller, floating-point unit (FPU), timers, two serial communication interfaces (SCI, SCIF), real-time clock (RTC), user break controller (UBC), bus state controller (BSC) and PCI controller (PCIC). This series can be used in a wide range of multimedia equipment. The bus controller is compatible with ROM, SRAM, DRAM, synchronous DRAM and PCMCIA.

**Target Readers:** This manual is designed for use by people who design application systems using the SH7751 or SH7751R.

To use this manual, basic knowledge of electric circuits, logic circuits and microcomputers is required.

This hardware manual contains revisions related to the addition of R-mask functionality. Be sure to check the text for the updated content.

**Purpose:** This manual provides the information of the hardware functions and electrical characteristics of the SH7751 and SH7751R.

The SH-4 Software Manual contains detailed information of executable instructions. Please read the Software Manual together with this manual.

#### How to Use the Book:

- To understand general functions

- $\rightarrow$  Read the manual from the beginning.

The manual explains the CPU, system control functions, peripheral functions and electrical characteristics in that order.

- To understanding CPU functions

- $\rightarrow$  Refer to the separate SH-4 Software Manual.

Explanatory Note: Bit sequence: upper bit at left, and lower bit at right

**List of Related Documents:** The latest documents are available on our Web site. Please make sure that you have the latest version.

(http://www.renesas.com/)

### • User manuals for SH7751 and SH7751R

| Name of Document                            | Document No.    |

|---------------------------------------------|-----------------|

| SH7751 Group, SH7751R Group Hardware Manual | This manual     |

| SH-4 Software Manual                        | REJ09B0318-0600 |

## • User manuals for development tools

| Name of Document                                                           | Document No.     |

|----------------------------------------------------------------------------|------------------|

| SuperH™ C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10B0047-0100H |

| SuperH™ RISC engine Simulator/Debugger User's Manual                       | REJ10B0210-0300  |

| High-performance Embedded Workshop User's Manual                           | REJ10J1554-0100  |

## Main Revisions for This Edition

| Item                                                               | Page        | Revision (S                                                                                                                                                                          | ee Manua               | al for D                            | etails)                    |                                          |                                       |

|--------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------|----------------------------|------------------------------------------|---------------------------------------|

| All                                                                | _           | Added ONP                                                                                                                                                                            | AC-BGA p               | oroduct                             | ts (HD64                   | 17750SBA200                              | V)                                    |

| 1.1 SH7751/SH7751R<br>Group Features<br>Table 1.1                  | 2           | Table amen                                                                                                                                                                           | Features               | Electronics                         | original Supe              | erH architecture                         |                                       |

| SH7751/SH7751R Group<br>Features                                   | 8           | Item Product lineup                                                                                                                                                                  | Features               | \/-lk                               | Operating                  | Madal Na                                 | Deelees                               |

|                                                                    |             |                                                                                                                                                                                      | Abbreviation<br>SH7751 | 1.8 V                               | 167 MHz                    | Model No.  HD6417751BP167  HD6417751F167 | Package<br>256-pin BGA<br>256-pin QFP |

|                                                                    |             |                                                                                                                                                                                      | SH7751R                | 1.5 V                               | 240 MHz                    | HD6417751RBP240<br>HD6417751RBA240H      | 256-pin BGA                           |

|                                                                    |             |                                                                                                                                                                                      |                        |                                     |                            | HD6417751RF240<br>HD6417751RBG240        | 256-pin QFP<br>292-pin BGA            |

| Register 0 (PCICONF0)                                              |             | Note: * The vendor ID H'1054 specifies Hitachi<br>the SH7751 and SH7751R are now pro<br>Renesas Electronics Corp. For informa<br>these products, contact Renesas Electrope.<br>Corp. |                        | Rare now produ<br>. For information | ucts of<br>on on           |                                          |                                       |

| 22.12.5 Notes on Parity<br>Error Detection during<br>Master Access | 980,<br>981 | Newly added                                                                                                                                                                          | t                      |                                     |                            |                                          |                                       |

| 23.1 Absolute Maximum                                              | 983         | Table amen                                                                                                                                                                           | ded and n              | ote ad                              | ded                        |                                          |                                       |

| Ratings                                                            |             | Item                                                                                                                                                                                 |                        |                                     | ymbol                      | Value                                    | Unit                                  |

| Table 23.1 Absolute Maximum Ratings                                |             | I/O, RTC, CPG pow                                                                                                                                                                    | er supply voltag       | ٧                                   | DD-RTC' DD-CPG             | -0.3 to 4.2<br>-0.3 to 4.6* <sup>1</sup> | V                                     |

| ŭ                                                                  |             | Internal power supp                                                                                                                                                                  | ly voltage             |                                     | $V_{DD}$ , $V_{DD-PLL1/2}$ | -0.3 to 2.5<br>-0.3 to 2.1* <sup>1</sup> | V                                     |

|                                                                    |             | Input voltage                                                                                                                                                                        |                        | \<br>                               |                            | -0.3 to V <sub>DDQ</sub> +0.3            | V                                     |

|                                                                    |             | Operating temperat                                                                                                                                                                   |                        |                                     | opr                        | -20 to 75, -40 to 85*                    | °C                                    |

|                                                                    |             | Notes: 1. H                                                                                                                                                                          |                        | 1R only                             |                            | -55 to 125                               |                                       |

| Item                                                                                                                                                                                                                                                                                    | Page         | Revision (See Manual for Details)                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23.2 DC Characteristics  Table 23.2 DC  Characteristics (HD6417751RBP240 (V), HD6417751RBG240 (V), HD6417751RBA240HV)  T <sub>a</sub> = -20 to +75°C* <sup>3</sup>                                                                                                                      | 982,<br>983  | Table title amended and note added Notes: 3. $T_a = -40$ to 85°C for the HD6417751RBA240HV.                                                                                                   |

| Table 23.4 DC Characteristics (HD6417751RBP200 (V), HD6417751RBG200 (V), HD6417751RBA240HV*³) $T_a = -20 \text{ to } +75^{\circ}\text{C*}^4$                                                                                                                                            | 988,.<br>989 | Table title amended and note added  Notes: 3. This is the case when the device in use is an HD6417751RBA240HV running at 200 MHz.  4. T <sub>a</sub> = -40 to 85°C for the HD6417751RBA240HV. |

| 23.3 AC Characteristics<br>Table 23.9 Clock Timing<br>(HD6417751RBP240 (V),<br>HD6417751RBG240 (V),<br>HD6417751RBA240HV)                                                                                                                                                               | 996          | Table title amended                                                                                                                                                                           |

| Table 23.11 Clock<br>Timing<br>(HD6417751RBP200 (V),<br>HD6417751RBG200 (V),<br>HD6417751RBA240HV*)                                                                                                                                                                                     | 997          | Table title amended and note added  Note: * This is the case when the device in use is an HD6417751RBA240HV running at 200 MHz.                                                               |

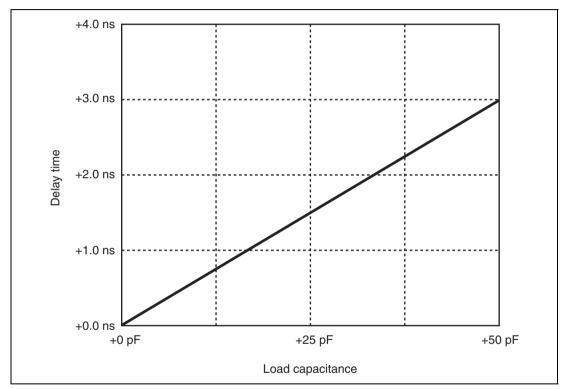

| 23.3.1 Clock and Control Signal Timing Table 23.14 Clock and Control Signal Timing (HD6417751RBP240 (V), HD6417751RBG240 (V), HD6417751RBA240HV) $V_{DDQ} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.5 \text{ V}, T_a = -20 \text{ to } 75^{\circ}\text{C}^{*^2}, C_L = 30 \text{ pF}$ | 998,<br>999  | Table title and table amended and note added    tem                                                                                                                                           |

| Item                                                                                                                                                                                                                         | Page          | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23.3.1 Clock and Control<br>Signal Timing                                                                                                                                                                                    | 1002,<br>1003 | Table title and table amended and note added    Symbol Min Max Unit Figure   Symbol Min Max Unit Figure |

| Table 23.16 Clock and Control Signal Timing (HD6417751RBP200 (V), HD6417751RBA240HV*²) $V_{DDO} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.5 \text{ V}, T_a = -20 \text{ to } 75^{\circ}\text{C}^{*3}, C_L = 30 \text{ pF}$ |               | Standby return oscillation settling time 1***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 23.3.2 Control Signal Timing Table 23.19 Control Signal Timing                                                                                                                                                               | 1012          | Table amended and note added    HD6417751   HD6417751   RBP240 (V)   HD6417751   RBG240 (V)   HD6417751   RBG200 (V)   HD6417751   RBG240HV   RB240HV   RB240HV   RF240 (V)    |

|                                                                                                                                                                                                                              |               | <ul> <li>Notes: 1. V<sub>DDQ</sub> = 3.0 to 3.6 V, V<sub>DD</sub> = 1.5 V, T<sub>a</sub> = −20 to 75°C*³, C<sub>L</sub> = 30 pF, PLL2 on</li> <li>2. This is the case when the device in use is an HD6417751RBA240HV running at 200 MHz.</li> <li>3. T<sub>a</sub> = −40 to 85°C for the HD6417751RBA240HV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.3.3 Bus Timing Table 23.21 Bus Timing (1)                                                                                                                                                                                 | 1016,<br>1017 | Table amended and note added $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Item                                                                                                                                                                                                                                                                                                       | Page               | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23.3.4 Peripheral<br>Module Signal Timing<br>Table 23.23 Peripheral<br>Module Signal Timing (1)                                                                                                                                                                                                            | 1067<br>to<br>1069 | Table amended and note added $\frac{\text{HD6417751}}{\text{RBP240 (V)}} + \frac{\text{HD6417751}}{\text{RBP240 (V)}} + \frac{\text{HD6417751}}{\text{RBP240 (V)}} + \frac{\text{HD6417751}}{\text{RBG200 (V)}} + \frac{\text{HD6417751}}{\text{HD6417751}} + \frac{\text{HD6417751}}{\text{RBG200 (V)}} + \frac{\text{HD6417751}}{\text{RBA240HV}} + \frac{\text{HD6417751}}{\text{RBA240HV}} + \frac{\text{HD6417751}}{\text{RBA240HV}} + \frac{\text{HD6417751}}{\text{RF240 (V)}} + \frac{\text{HD6417751}}{\text{RF200 (V)}}$ |

| Table 23.25 PCIC Signal<br>Timing (in<br>PCIREQ/PCIGNT Non-<br>Port Mode) (1)<br>HD6417751RBP240 (V),<br>HD6417751RBP200 (V),                                                                                                                                                                              | 1076               | Table title amended and note added  Notes: 1. HD6417751RF240 (V), HD6417751RF200 (V)  2. T <sub>a</sub> = -40 to 85°C for the HD6417751RBA240HV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HD6417751RBF200 (V),<br>HD6417751RBG200 (V),<br>HD6417751RBA240HV,<br>HD6417751RF240 (V),<br>HD6417751RF200 (V):<br>V <sub>DD0</sub> = 3.0 to 3.6 V, V <sub>DD</sub> =<br>1.5 V, Ta = -20 to 75°C* <sup>2</sup> ,<br>C <sub>L</sub> = 30 pF                                                                |                    | Asterisk "*" in table changed to "*1" $"3.0 \ (3.5*)" \rightarrow "3.0 \ (3.5*)"$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 23.27 PCIC Signal<br>Timing (With<br>PCIREQ/PCIGNT Port<br>Settings in Non-Host<br>Mode) (1)                                                                                                                                                                                                         | 1079               | Table title amended and note added Note: $*$ T <sub>a</sub> = -40 to 85°C for the HD6417751RBA240HV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HD6417751RBP240 (V),<br>HD6417751RBP200 (V),<br>HD6417751RBG240 (V),<br>HD6417751RBG200 (V),<br>HD6417751RBA240HV,<br>HD6417751RF240 (V),<br>HD6417751RF200 (V):<br>$V_{DDQ} = 3.0 \text{ to } 3.6 \text{ V}, V_{DD} = 1.5 \text{ V}, T_a = -20 \text{ to } 75^{\circ}\text{C*},$<br>$C_L = 30 \text{ pF}$ |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Item                                                                                       | Page | Revision (See Manual for Details)                                                                                                                                                     |  |  |

|--------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

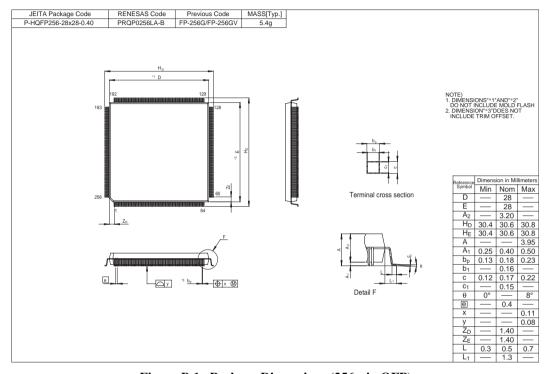

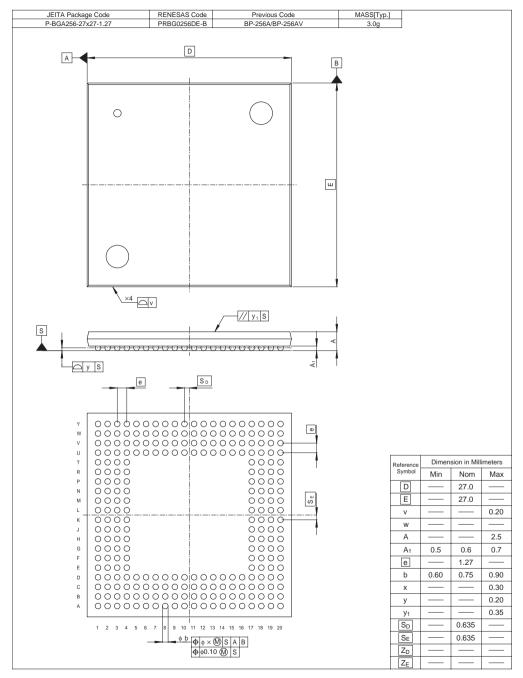

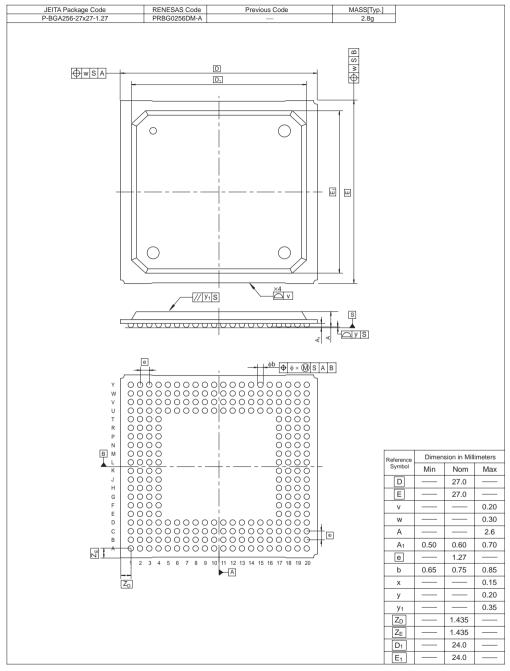

| Appendix B Package<br>Dimensions                                                           | 1092 | Figure title amended                                                                                                                                                                  |  |  |

| Figure B.2 Package<br>Dimensions (256-pin<br>BGA: Devices Other than<br>HD6417751RBA240HV) |      |                                                                                                                                                                                       |  |  |

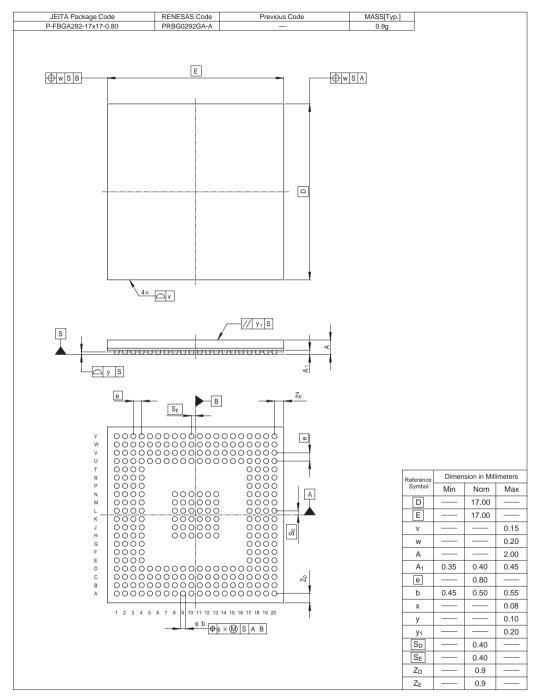

| Figure B.4 Package<br>Dimensions                                                           | 1094 | Figure newly added                                                                                                                                                                    |  |  |

| (256-Pin BGA:<br>HD6417750RBA240HV)                                                        |      |                                                                                                                                                                                       |  |  |

| D.2 Handling of Unused                                                                     | 1105 | Table amended                                                                                                                                                                         |  |  |

| Pins                                                                                       |      | Pin Name I/O Handling                                                                                                                                                                 |  |  |

| Table D.4 Handling of<br>Pins When PCI Is Not<br>Used                                      |      | AD31–AD0 I/O Pull up to 3.3 V*                                                                                                                                                        |  |  |

| Appendix H Product                                                                         | 1125 | Table note amended                                                                                                                                                                    |  |  |

| Lineup                                                                                     |      | Notes: 1. Contact a Renesas sales office regarding                                                                                                                                    |  |  |

| Table H.1<br>SH7751/SH7751R<br>Product Lineup                                              |      | product versions with specifications for a wider temperature range (-40 to +85°C). The wide temperature range (-40 to +85°C) is the standard specification for the HD6417751RBA240HV. |  |  |

## Contents

| Sect | tion 1 Overview                                                   | 1  |

|------|-------------------------------------------------------------------|----|

| 1.1  | SH7751/SH7751R Group Features                                     | 1  |

| 1.2  | Block Diagram                                                     | 9  |

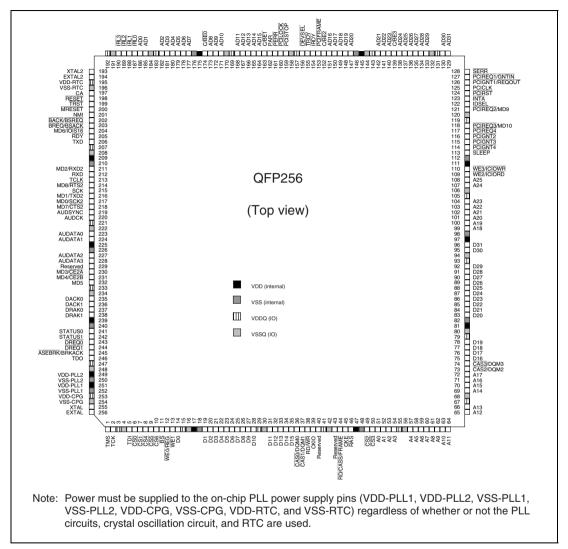

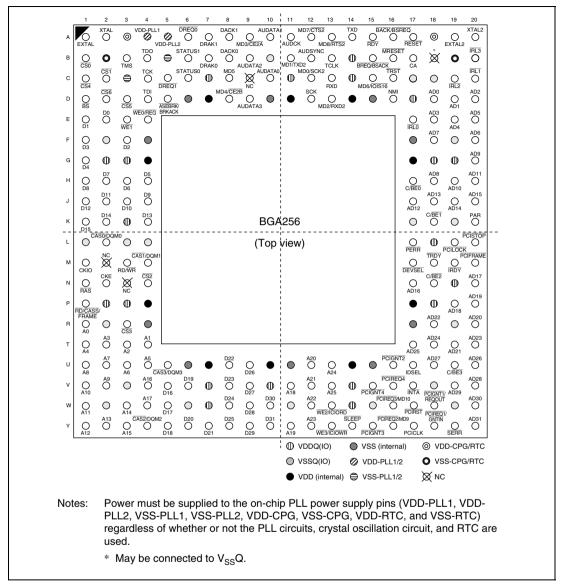

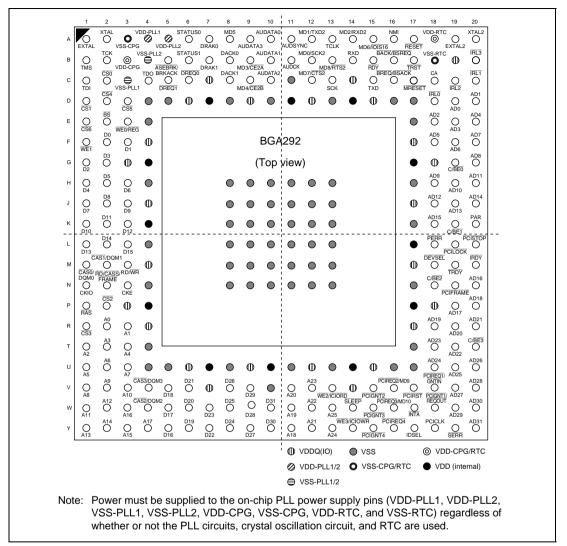

| 1.3  | Pin Arrangement                                                   | 10 |

| 1.4  | Pin Functions                                                     | 13 |

|      | 1.4.1 Pin Functions (256-Pin QFP)                                 | 13 |

|      | 1.4.2 Pin Functions (256-Pin BGA)                                 | 24 |

|      | 1.4.3 Pin Functions (292-Pin BGA)                                 | 35 |

| Sect | tion 2 Programming Model                                          | 47 |

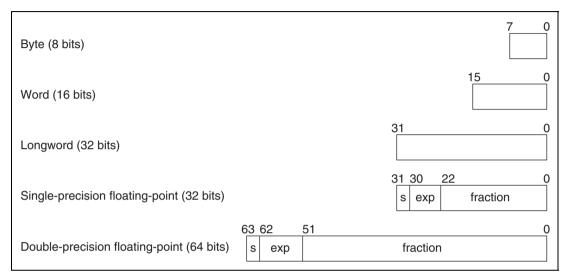

| 2.1  | Data Formats                                                      | 47 |

| 2.2  | Register Configuration                                            | 48 |

|      | 2.2.1 Privileged Mode and Banks                                   | 48 |

|      | 2.2.2 General Registers                                           | 51 |

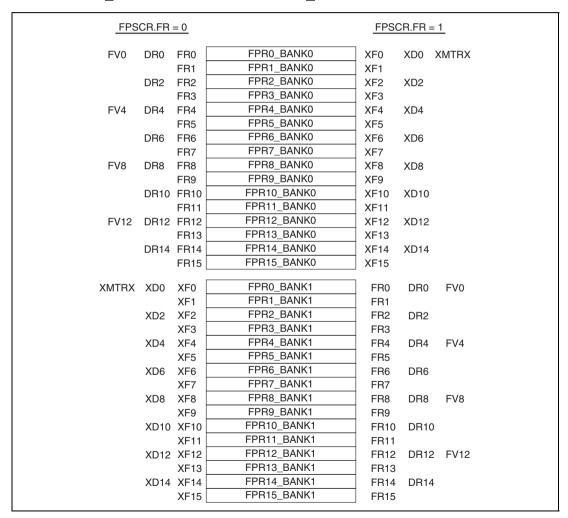

|      | 2.2.3 Floating-Point Registers                                    | 53 |

|      | 2.2.4 Control Registers                                           | 55 |

|      | 2.2.5 System Registers                                            | 56 |

| 2.3  | Memory-Mapped Registers                                           | 58 |

| 2.4  | Data Format in Registers                                          | 59 |

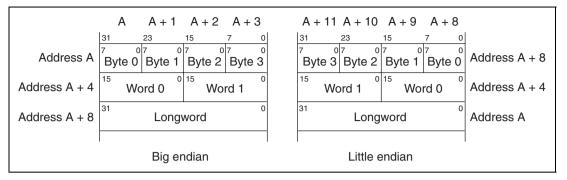

| 2.5  | Data Formats in Memory                                            | 59 |

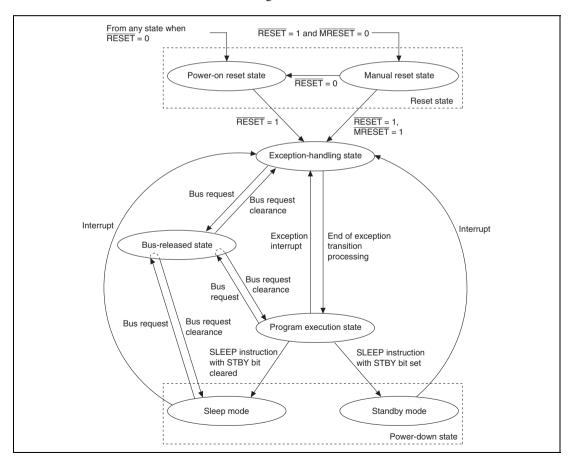

| 2.6  | Processor States                                                  | 60 |

| 2.7  | Processor Modes                                                   | 62 |

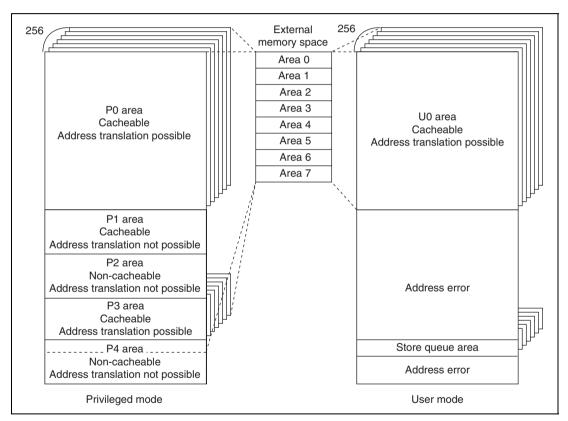

| Sect | tion 3 Memory Management Unit (MMU)                               | 63 |

| 3.1  | Overview                                                          |    |

|      | 3.1.1 Features                                                    | 63 |

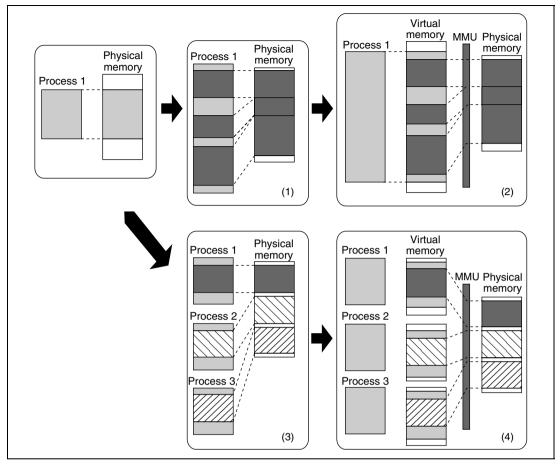

|      | 3.1.2 Role of the MMU                                             | 63 |

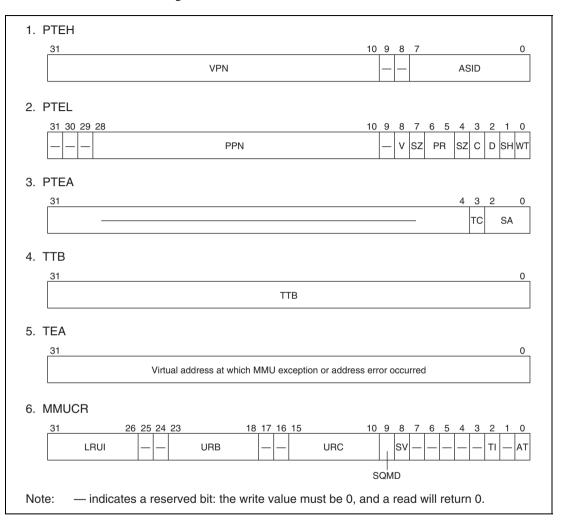

|      | 3.1.3 Register Configuration                                      | 66 |

|      | 3.1.4 Caution                                                     | 66 |

| 3.2  | Register Descriptions                                             | 67 |

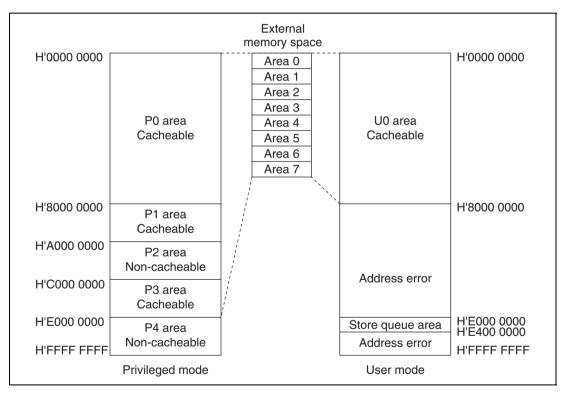

| 3.3  | Address Space                                                     | 71 |

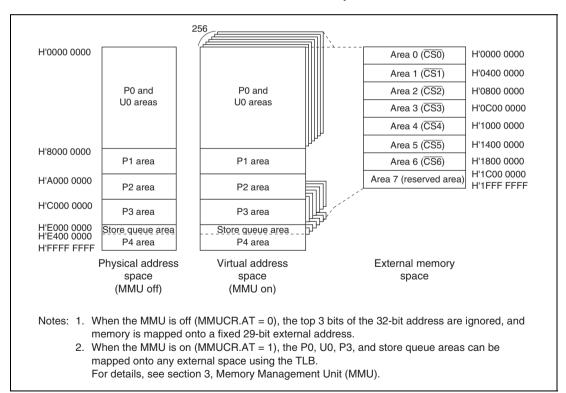

|      | 3.3.1 Physical Address Space                                      | 71 |

|      | 3.3.2 External Memory Space                                       | 74 |

|      | 3.3.3 Virtual Address Space                                       | 75 |

|      | 3.3.4 On-Chip RAM Space                                           | 76 |

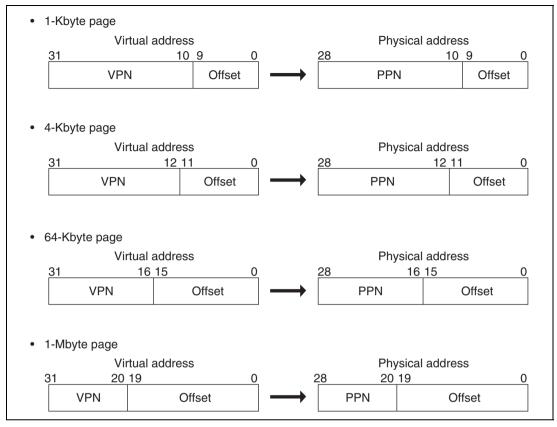

|      | 3.3.5 Address Translation                                         | 76 |

|      | 3.3.6 Single Virtual Memory Mode and Multiple Virtual Memory Mode | 77 |

|      | 3.3.7                           | Address Space Identifier (ASID)                | 77  |  |  |  |

|------|---------------------------------|------------------------------------------------|-----|--|--|--|

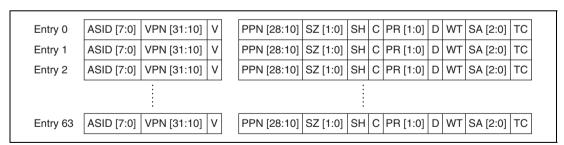

| 3.4  | TLB I                           | Functions                                      |     |  |  |  |

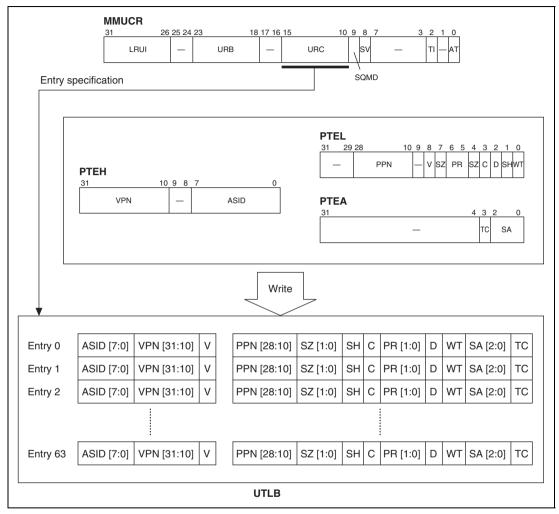

|      | 3.4.1                           | Unified TLB (UTLB) Configuration               | 78  |  |  |  |

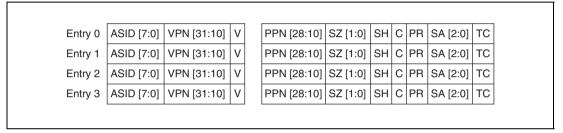

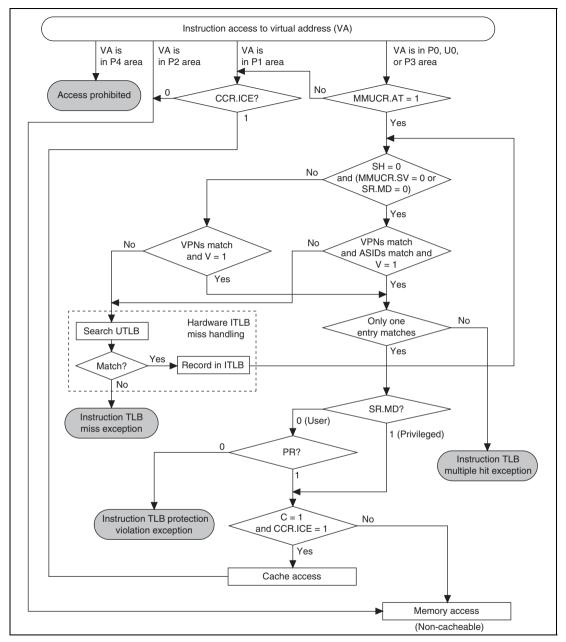

|      | 3.4.2                           | Instruction TLB (ITLB) Configuration           | 82  |  |  |  |

|      | 3.4.3                           | Address Translation Method                     |     |  |  |  |

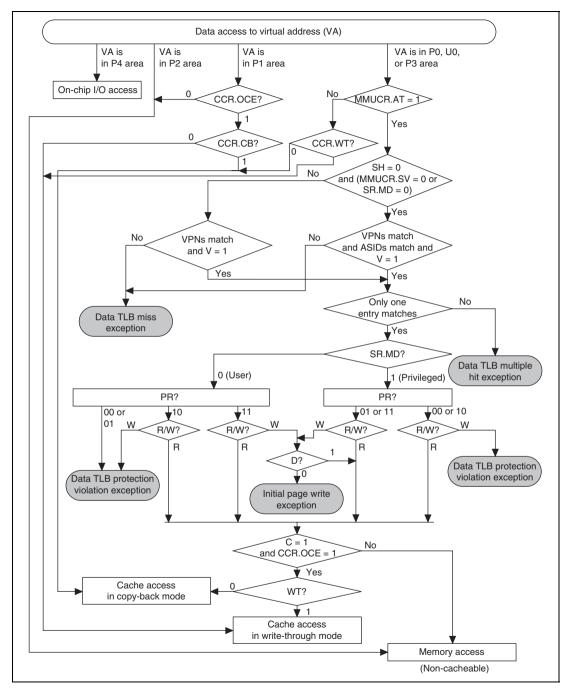

| 3.5  | MMU                             | Functions                                      | 85  |  |  |  |

|      | 3.5.1                           | MMU Hardware Management                        | 85  |  |  |  |

|      | 3.5.2                           | MMU Software Management                        | 85  |  |  |  |

|      | 3.5.3                           | MMU Instruction (LDTLB)                        | 85  |  |  |  |

|      | 3.5.4                           | Hardware ITLB Miss Handling                    | 86  |  |  |  |

|      | 3.5.5                           | Avoiding Synonym Problems                      | 87  |  |  |  |

| 3.6  | MMU                             | Exceptions                                     | 88  |  |  |  |

|      | 3.6.1                           | Instruction TLB Multiple Hit Exception         | 88  |  |  |  |

|      | 3.6.2                           | Instruction TLB Miss Exception                 | 88  |  |  |  |

|      | 3.6.3                           | Instruction TLB Protection Violation Exception | 89  |  |  |  |

|      | 3.6.4                           | Data TLB Multiple Hit Exception                | 90  |  |  |  |

|      | 3.6.5                           | Data TLB Miss Exception                        | 91  |  |  |  |

|      | 3.6.6                           | Data TLB Protection Violation Exception        | 92  |  |  |  |

|      | 3.6.7                           | Initial Page Write Exception                   | 93  |  |  |  |

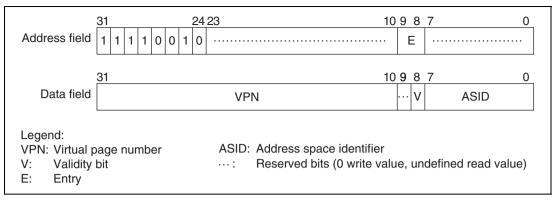

| 3.7  | Memory-Mapped TLB Configuration |                                                |     |  |  |  |

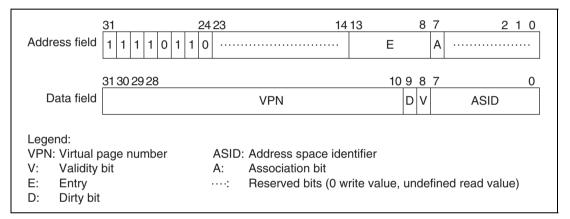

|      | 3.7.1                           | ITLB Address Array                             | 94  |  |  |  |

|      | 3.7.2                           | ITLB Data Array 1                              | 95  |  |  |  |

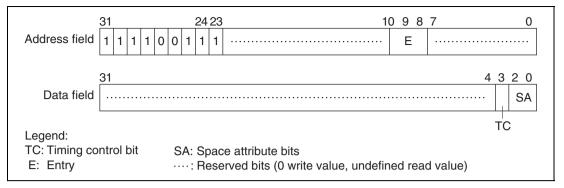

|      | 3.7.3                           | ITLB Data Array 2                              | 96  |  |  |  |

|      | 3.7.4                           | UTLB Address Array                             | 97  |  |  |  |

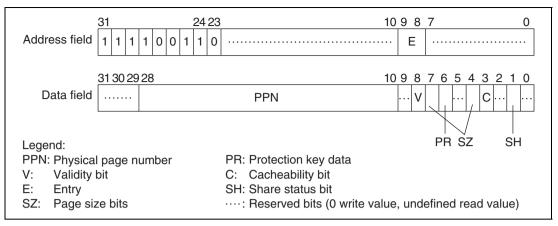

|      | 3.7.5                           | UTLB Data Array 1                              | 98  |  |  |  |

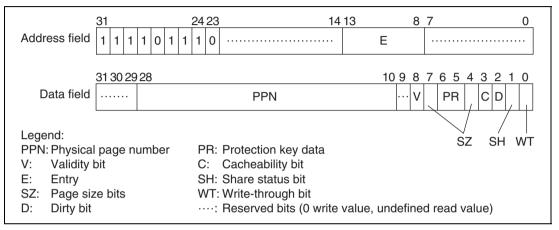

|      | 3.7.6                           | UTLB Data Array 2                              | 99  |  |  |  |

| 3.8  | Usage                           | Notes                                          | 100 |  |  |  |

| Sect | tion 4                          | Caches                                         | 101 |  |  |  |

| 4.1  | Overv                           | iew                                            | 101 |  |  |  |

|      | 4.1.1                           | Features                                       | 101 |  |  |  |

|      | 4.1.2                           | Register Configuration                         |     |  |  |  |

| 4.2  | Regist                          | ter Descriptions                               |     |  |  |  |

| 4.3  | _                               | nd Cache (OC)                                  |     |  |  |  |

|      | 4.3.1                           | Configuration                                  |     |  |  |  |

|      | 4.3.2                           | Read Operation                                 |     |  |  |  |

|      | 4.3.3                           | Write Operation                                |     |  |  |  |

|      | 4.3.4                           | Write-Back Buffer                              |     |  |  |  |

|      | 4.3.5                           | Write-Through Buffer                           |     |  |  |  |

|      | 4.3.6                           | RAM Mode                                       |     |  |  |  |

|      |                                 |                                                |     |  |  |  |

|     | 4.3.7    | OC Index Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113 |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | 4.3.8    | Coherency between Cache and External Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113 |

|     | 4.3.9    | Prefetch Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 113 |

|     | 4.3.10   | Notes on Using OC RAM Mode (SH7751R Only) when in Cache Enhanced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|     |          | Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 114 |