# M28F008 8 MBIT (1 MBIT x 8) FLASH MEMORY

- High-Density Symmetrically Blocked Architecture

- Sixteen 64 Kbyte Blocks

- Extended Cycling Capability

- 10K Block Erase Cycles Minimum

- 160K Block Erase Cycles per Chip

- Automated Byte Write and Block Erase

- Command User Interface

- Status Register

- System Performance Enhancements

- RY/BY Status Output

- Erase Suspend Capability

- **SRAM-Compatible Write Interface**

- Very High-Performance Read

100 ns Maximum Access Time

- Hardware Data Protection Feature

Erase/Write Lockout during Power

Transitions

- Industry Standard Packaging

- 40-Lead Sidebrazed DIP

- 42-Lead Flatpack

- ETOX™ Nonvolatile Flash Technology

12V Byte Write/Block Erase

- Independent Software Vendor Support

Microsoft\* Flash File System (FFS)

The M28F008 8-Mbit FlashFile Memory is the highest density nonvolatile read/write solution for solid state storage. The M28F008's extended cycling, symmetrically blocked architecture, fast access time, write automation and low power consumption provide a more reliable, lower power, lighter weight and higher performance alternative to traditional rotating disk technology. The M28F008 brings new capabilities to portable computing. Application and operating system software stored in resident flash memory arrays provide instant-on, rapid execute-in-place and protection from obsolescence through in-system software updates. Resident software also extends system battery life and increases reliability by reducing disk drive accesses.

For high-density data acquisition applications, the M28F008 offers a more cost-effective and reliable alternative to SRAM and battery. Traditional high density embedded applications, such as telecommunications, can take advantage of the M28F008's nonvolatility, blocking and minimal system code requirements for flexible firmware and modular software designs.

The M28F008 is offered in 40-lead sidebrazed DIP and 42-lead Flatpack packages. This device uses an integrated Command User Interface and state machine for simplified block erasure and byte write. The M28F008 memory map consists of 16 separately erasable 64 Kbyte blocks.

The M28F008 employs advanced CMOS circuitry for systems requiring low power consumption and noise immunity. Its 100 ns access time provides superior performance when compared with magnetic storage media. A deep powerdown mode lowers power consumption to 500  $\,\mu$ W maximum thru V<sub>CC</sub>. The RP power control input also provides absolute data protection during system powerup/down.

For complete Rochester ordering guide, please refer to page 2

Please contact factory for specific package availability and

Military/Aerospace specifications/availability.

Rochester Electronics guarantees performance of its semiconductor products to the original OEM specifications. "Typical" values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing. Rochester Electronics reserves the right to make changes without further notice to any specification herein.

# M28F008

## **Rochester Ordering Guide**

\*Most products can also be offered as RoHS compliant, designated by a –G suffix. Please contact factory for more information.

| Rochester Part Number | Intel Part Number | Package        | Temperature    |

|-----------------------|-------------------|----------------|----------------|

| MC28F008-10/B         | MC28F008-10       | CDIP-40        | -55° to +125°C |

| MC28F008-12/B         | MC28F008-12       | CDIP-40        | -55° to +125°C |

| MF28F008-10/B         | MF28F008-10       | FP-42, Ceramic | -55° to +125°C |

| MF28F008-12/B         | MF28F008-12       | FP-42, Ceramic | -55° to +125°C |

#### PRODUCT OVERVIEW

The M28F008 is a high-performance 8 Mbit (8,388,608 bit) memory organized as 1 Mbyte (1,048,576 bytes) of 8 bits each. Sixteen 64 Kbyte (65,536 byte) blocks are included on the M28F008. A memory map is shown in Figure 4 of this specification. A block erase operation erases one of the sixteen blocks of memory in typically 1.6 seconds, independent of the remaining blocks. Each block can be independently erased and written 10,000 cycles. Erase Suspend mode allows system software to suspend block erase to read data or execute code from any other block of the M28F008.

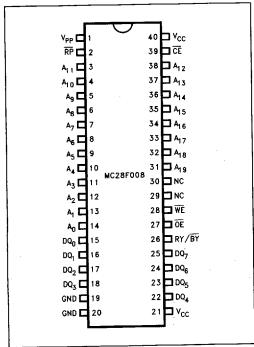

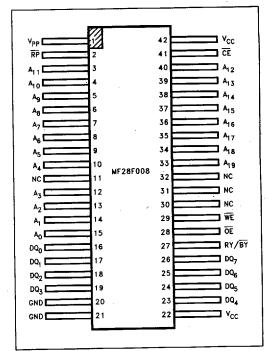

The M28F008 is available in **40-lead sidebrazed DIP** and **42-lead Flatpack** packages. Pinouts are shown in Figures 2a and 2b of this specification.

The **Command User Interface** serves as the interface between the microprocessor or microcontroller and the internal operation of the M28F008.

Byte Write and Block Erase Automation allow byte write and block erase operations to be executed using a two-write command sequence to the Command User Interface. The internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for byte write and block erase operations, including verifications, thereby unburdening the microprocessor or microcontroller. Writing of memory data is performed in byte increments typically within 9  $\mu$ s, an 80% improvement over current flash memory products. Ipp byte write and block erase currents are 30 mA maximum. Vpp byte write and block erase voltage is 11.4V to 12.6V.

The Status Register indicates the status of the WSM and when the WSM successfully completes the desired byte write or block erase operation.

The RY/BY output gives an additional indicator of WSM activity, providing capability for both hardware signal of status (versus software polling) and status masking (interrupt masking for background erase, for example). Status polling using RY/BY minimizes both CPU overhead and system power consumption. When low, RY/BY indicates that the WSM is performing a block erase or byte write operation. RY/BY high indicates that the WSM is ready for new commands, block erase is suspended or the device is in deep powerdown mode.

Maximum access time is 100 ns ( $t_{ACC}$ ) over the military temperature range ( $-55^{\circ}$ C to  $+125^{\circ}$ C) and over V<sub>CC</sub> supply voltage range 4.5V to 5.5V. I<sub>CC</sub> active current (CMOS Read) is 35 mA maximum at 8 MHz

When the  $\overline{CE}$  and  $\overline{RP}$  pins are at  $V_{CC}$ , the  $I_{CC}$  CMOS Standby mode is enabled.

A **Deep Powerdown** mode is enabled when the  $\overline{RP}$  pin is at GND, minimizing power consumption and providing write protection. **I**<sub>CC</sub> current in deep powerdown is 100  $\mu$ A maximum. Reset time of 400 ns is required from  $\overline{RP}$  switching high until outputs are valid to read attempts. Equivalently, the device has a wake time of 1  $\mu$ s from  $\overline{RP}$  high until writes to the Command User Interface are recognized by the M28F008. With  $\overline{RP}$  at GND, the WSM is reset and the Status Register is cleared.

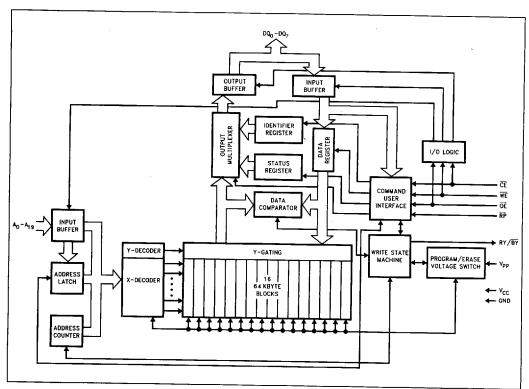

Figure 1. Block Diagram

**Table 1. Pin Description**

| Symbol                           | Туре         | Name and Function                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>19</sub>  | INPUT        | ADDRESS INPUTS for memory addresses. Addresses are internally latched during a write cycle.                                                                                                                                                                                                                                                                                                    |

| DQ <sub>0</sub> -DQ <sub>7</sub> | INPUT/OUTPUT | DATA INPUT/OUTPUTS: Inputs data and commands during Command User Interface write cycles; outputs data during memory array, Status Register and Identifier read cycles. The data pins are active high and float to tri-state off when the chip is deselected or the outputs are disabled. Data is internally latched during a write cycle.                                                      |

| CE                               | INPUT        | CHIP ENABLE: Activates the device's control logic, input buffers, decoders, and sense amplifiers. $\overline{CE}$ is active low; $\overline{CE}$ high deselects the memory device and reduces power consumption to standby levels.                                                                                                                                                             |

| RP                               | INPUT        | RESET/DEEP POWERDOWN: Puts the device in deep powerdown mode. $\overline{RP}$ is active low; $\overline{RP}$ high gates normal operation. $\overline{RP}$ also locks out block erase or byte write operations when active low, providing data protection during power transitions. $\overline{RP}$ active resets internal automation. Exit from Deep Powerdown sets device to read-array mode. |

| ŌĒ                               | INPUT        | OUTPUT ENABLE: Gates the device's outputs through the data buffers during a read cycle. OE is active low.                                                                                                                                                                                                                                                                                      |

| WE                               | INPUT        | WRITE ENABLE: Controls writes to the Command User Interface and array blocks. WE is active low. Addresses and data are latched on the rising edge of the WE pulse.                                                                                                                                                                                                                             |

Table 1. Pin Description (Continued)

| Symbol          | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RY/BY           | OUTPUT | READY/BUSY: Indicates the status of the internal Write State Machine. When low, it indicates that the WSM is performing a block erase or byte write operation: RY/BY high indicates that the WSM is ready for new commands, block erase is suspended or the device is in deep powerdown mode. RY/BY is always active and does NOT float to tri-state off when the chip is deselected or data outputs are disabled. |

| V <sub>PP</sub> |        | BLOCK ERASE/BYTE WRITE POWER SUPPLY for erasing blocks of the array or writing bytes of each block.  NOTE:  With V <sub>PP</sub> < V <sub>PPLMAX</sub> , memory contents cannot be altered.                                                                                                                                                                                                                        |

| V <sub>CC</sub> |        | DEVICE POWER SUPPLY (5V ± 10%)                                                                                                                                                                                                                                                                                                                                                                                     |

| GND             |        | GROUND                                                                                                                                                                                                                                                                                                                                                                                                             |

Figure 2a. DIP Pinout

Figure 2b. Flatpack Pinout

### **ABSOLUTE MAXIMUM RATINGS\***

Operating Temperature . . . . . . . - 55°C to + 125°C Temperature Under Bias . . . . . . -55°C to +125°C Storage Temperature .....-65°C to +125°C Voltage on Any Pin (except V<sub>CC</sub> and V<sub>PP</sub>) with Respect to GND ..... -2.0V to +7.0V(1) V<sub>PP</sub> Program Voltage with Respect to GND during Block Erase/Byte Write ... -2.0V to +14.0V(1, 2) V<sub>CC</sub> Supply Voltage with Respect to GND  $\dots$  -2.0V to +7.0V(1)

NOTICE: This data sheet contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel Sales office that you have the latest data sheet before finalizing a design.

WARNING: Stressing the device beyond the "Absolute MAXIMUM Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and ex-tended exposure beyond the "Operating Conditions" may affect device reliability.

- 1. Minimum DC voltage is -0.5V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <20 ns. Maximum DC voltage on input/output pins is V<sub>CC</sub> + 0.5V which, during transitions, may overshoot to V<sub>CC</sub> + 2.0V for periods <20 ns.

- Maximum DC voltage on V<sub>PP</sub> may overshoot to +14.0V for periods <20 ns.</li>

- 3. Output shorted for no more than one second. No more than one output shorted at a time.

#### OPERATING CONDITIONS

| Symbol | Parameter                            | Min  | Max   | Unit |

|--------|--------------------------------------|------|-------|------|

| To     | Operating Temperature                | -55  | + 125 | *C   |

| Vcc    | V <sub>CC</sub> Supply Voltage (10%) | 4.50 | 5.50  | V    |

#### DC CHARACTERISTICS

| Symbol          | Parameter                              | Notes |     | 008 and<br>3F008 | Unit | Test Conditions                                                                                                          |  |

|-----------------|----------------------------------------|-------|-----|------------------|------|--------------------------------------------------------------------------------------------------------------------------|--|

| OyiiiDO:        | ,                                      |       | Min | Max              |      |                                                                                                                          |  |

| t <sub>Ll</sub> | Input Load Current                     | 1     |     | ±1.0             | μΑ   | $V_{CC} = V_{CC} Max$<br>$V_{IN} = V_{CC} or GND$                                                                        |  |

| LO              | Output Load Current                    | 1     |     | ±10              | μА   | $V_{CC} = V_{CC} Max$<br>$V_{OUT} = V_{CC} or GND$                                                                       |  |

| Iccs            | V <sub>CC</sub> Standby Current        | 1, 3  |     | 2.0              | ·mA  | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE = RP = V <sub>IH</sub>                                                       |  |

|                 |                                        |       |     | 150              | μА   | $V_{CC} = V_{CC} Max$ $\overline{CE} = \overline{RP} = V_{CC} \pm 0.2V$                                                  |  |

| ICCD            | V <sub>CC</sub> Deep Powerdown Current | 1     |     | 100              | μА   | $\overline{RP} = GND \pm 0.2V$ $I_{OUT} (RY/\overline{BY}) = 0 \text{ mA}$                                               |  |

| ICCR            | V <sub>CC</sub> Read Current           | 1     |     | 35               | mA   | $V_{CC} = V_{CC} \text{ Max}, \overline{CE} = \text{GND}$<br>$F = 8 \text{ MHz}, I_{OUT} = 0 \text{ mA},$<br>CMOS inputs |  |

|                 |                                        |       |     | 50               | mA   | $V_{CC} = V_{CC} \text{ Max, } \overline{CE} = V_{IL},$ $F = 8 \text{ MHz, } I_{OUT} = 0 \text{ mA,}$ TTL inputs         |  |

## **DC CHARACTERISTICS (Continued)**

| Symbol           | Parameter                                     | Notes |      | F008 and<br>28F008   | Unit | Test Conditions                                                   |  |

|------------------|-----------------------------------------------|-------|------|----------------------|------|-------------------------------------------------------------------|--|

|                  |                                               | _     | Min  | Max                  |      |                                                                   |  |

| lccw             | V <sub>CC</sub> Byte Write Current            | 1     |      | 30                   | mA   | Byte Write In Progress                                            |  |

| ICCE             | V <sub>CC</sub> Block Erase Current           | 1     |      | 30                   | mA   | Block Erase In Progress                                           |  |

| ICCES            | V <sub>CC</sub> Erase Suspend Current         | 1, 2  |      | 10                   | mA   | Block Erase Suspended  CE = V <sub>IH</sub>                       |  |

| I <sub>PPS</sub> | V <sub>PP</sub> Standby Current               | 1     |      | ±15                  | μΑ   | V <sub>PP</sub> ≤ V <sub>CC</sub>                                 |  |

|                  |                                               |       |      | 200                  | μΑ   | V <sub>PP</sub> > V <sub>CC</sub>                                 |  |

| I <sub>PPD</sub> | V <sub>PP</sub> Deep PowerDown Current        | 1     |      | 20                   | μА   | $\overline{RP} = GND \pm 0.2V$                                    |  |

| IPPW             | V <sub>PP</sub> Write Current                 | 1     |      | 30                   | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Byte Write in Progress      |  |

| IPPE             | V <sub>PP</sub> Block Erase Current           | 1     |      | 30                   | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Block Erase in Progress     |  |

| PPES             | V <sub>PP</sub> Erase Suspend Current         | 1     |      | 200                  | μΑ   | V <sub>PP</sub> = V <sub>PPH</sub><br>Block Erase Suspended       |  |

| VIL              | Input Low Voltage                             |       | -0.5 | 0.8                  | ٧    |                                                                   |  |

| V <sub>IH</sub>  | Input High Voltage                            |       | 2.0  | V <sub>CC</sub> +0.5 | ٧    |                                                                   |  |

| V <sub>OL</sub>  | Output Low Voltage                            | 3     |      | 0.45                 | ٧    | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OL</sub> = 5.8 mA |  |

| V <sub>OH</sub>  | Output High Voltage                           | 3     | 2.4  |                      | ٧    | $V_{CC} = V_{CC}$ Min $I_{OH} = -2.5$ mA                          |  |

| V <sub>PPL</sub> | V <sub>PP</sub> during Normal Operations      | 4     | 0.0  | 6.5                  | V    |                                                                   |  |

| V <sub>PPH</sub> | V <sub>PP</sub> during Erase/Write Operations |       | 11.4 | 12.6                 | ٧    |                                                                   |  |

| V <sub>LKO</sub> | V <sub>CC</sub> Erase/Write Lock Voltage      |       | 1.8  |                      | ٧    |                                                                   |  |

# CAPACITANCE(5) TA = 25°C, f = 1 MHz

| Symbol           | Parameter          | Тур | Max | Unit | Condition             |

|------------------|--------------------|-----|-----|------|-----------------------|

| C <sub>IN</sub>  | Input Capacitance  | 6   | 8   | pF   | $V_{IN} = 0V$         |

| C <sub>OUT</sub> | Output Capacitance | 8   | 12  | рF   | V <sub>OUT</sub> = 0V |

### NOTES:

<sup>1.</sup> All currents are in RMS unless otherwise noted.

2. I<sub>CCES</sub> is specified with the device deselected. If the M28F008 is read while in Erase Suspend Mode, current draw is the sum of I<sub>CCES</sub> and I<sub>CCR</sub>.

3. Includes RY/BY.

<sup>4.</sup> Block Erases/Byte Writes are inhibited when V<sub>PP</sub> = V<sub>PPL</sub> and not guaranteed in the range between V<sub>PPH</sub> and V<sub>PPL</sub>.

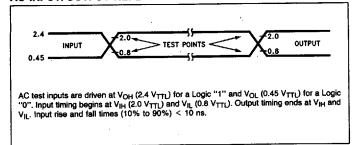

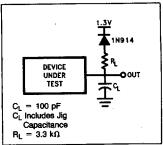

## AC INPUT/OUTPUT REFERENCE WAVEFORM

## **AC TESTING LOAD CIRCUIT**

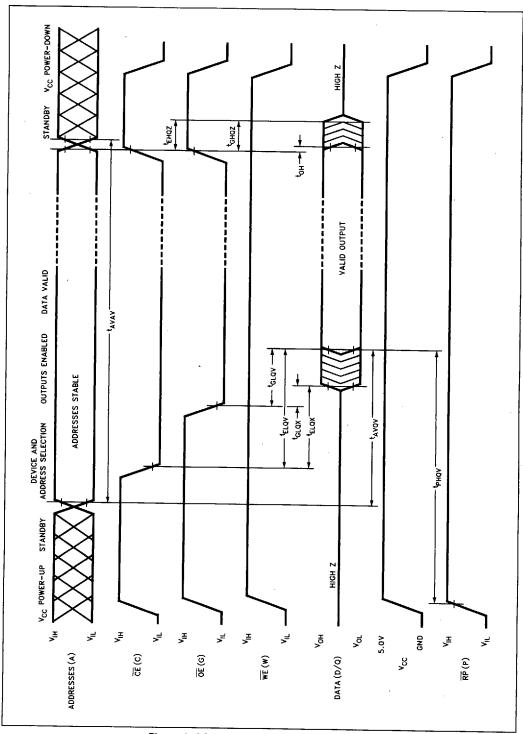

AC CHARACTERISTICS—Read-Only Operations(1, 4)

|                   |                 |                                                                       |       | M28F0 | 08-10 <sup>(4)</sup> | M28F0 | 08-12(4) | Unit  |

|-------------------|-----------------|-----------------------------------------------------------------------|-------|-------|----------------------|-------|----------|-------|

| Sym               | bol             | Parameter                                                             | Notes | Min   | Max                  | Min   | Max      | Offic |

| tavav             | t <sub>RC</sub> | Read Cycle Time                                                       |       | 100   |                      | 120   |          | ns    |

| tavov             | tACC            | Address to Output Display                                             |       |       | 100                  |       | 120      | ns    |

| tELQV             | tCE             | CE to Output Delay                                                    | 2     |       | 100                  |       | 120      | ns    |

| tPHQV             | tpwH            | RP High to Output Delay                                               |       |       | 400                  |       | 400      | ns    |

| tGLQV             | toE             | OE to Output Delay                                                    | 2     |       | 60                   |       | 60       | ns    |

| tELQX             | tLZ             | CE to Output Low Z                                                    | 3     | 0     |                      | 0     |          | ns    |

| t <sub>EHQZ</sub> | t <sub>HZ</sub> | ČE High to Output High Z                                              | 3     |       | 55                   |       | 55       | ns    |

| tGLQX             | toLZ            | OE to Output Low Z                                                    | 3     | 0     |                      | 0     |          | ns    |

| tGHQZ             | t <sub>DF</sub> | OE High to Output High Z                                              | 3     |       | 30                   |       | 30       | ns    |

|                   | tон             | Output Hold from<br>Addresses, CE or OE<br>Change, Whichever is First | 3     | 0     |                      | 0     |          | ns    |

#### NOTES:

NOIES:

See AC Input/Output Reference Waveform for timing measurements.

OE may be delayed up to t<sub>CE</sub>-t<sub>OE</sub> after the falling edge of CE without Impact on t<sub>CE</sub>.

Sampled, not 100% tested.

See AC Input/Output Reference Waveforms and AC Testing Load Circuits for testing characteristics.

Figure 8. AC Waveform for Read Operations

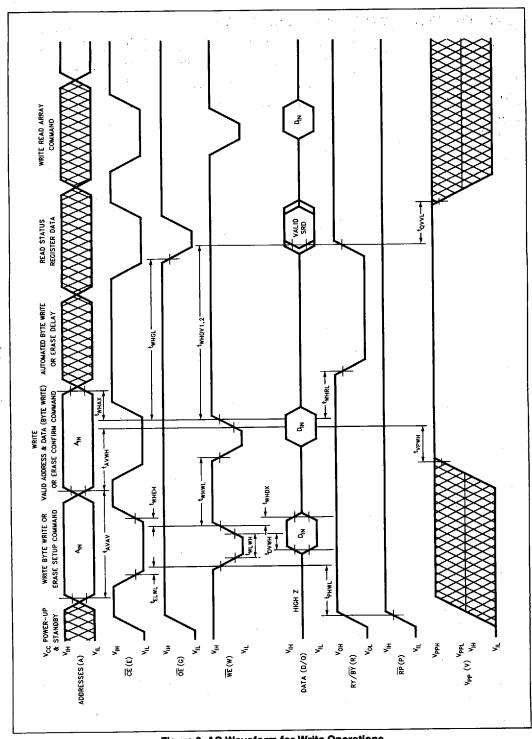

# AC CHARACTERISTICS—Write Operations(1,7)

|                    | · ·              |                                                    |       | M28F0 | 08-10 <sup>(7)</sup> | M28F0 | Unit |       |

|--------------------|------------------|----------------------------------------------------|-------|-------|----------------------|-------|------|-------|

| Symt               | ool              | Parameter                                          | Notes | Min   | Max                  | Min   | Max  | Oilit |

| tavav              | twc              | Write Cycle Time                                   |       | 100   |                      | 120   |      | ns    |

| t <sub>PHWL</sub>  | t <sub>PS</sub>  | RP High Recovery to WE Going Low                   | 2     | 1     |                      | 1     |      | μs    |

| t <sub>ELWL</sub>  | tcs              | CE Setup to WE Going Low                           |       | 10    |                      | 10    |      | ns    |

| twLwH              | twp              | WE Pulse Width                                     |       | 40    |                      | 40    |      | ns    |

| <b>t</b> ∨PWH      | typs             | V <sub>PP</sub> Setup to WE Going<br>High          | 2     | 100   |                      | 100   |      | ns    |

| t <sub>AVWH</sub>  | tas              | Address Setup to WE Going High                     | 3     | 40    |                      | 40    |      | ns    |

| t <sub>DVWH</sub>  | t <sub>DS</sub>  | Data Setup to WE Going<br>High                     | 4     | 40    |                      | 40    |      | ns    |

| twhox              | t <sub>DH</sub>  | Data Hold from WE High                             |       | 5     |                      | 5     |      | ns    |

| twhax              | t <sub>AH</sub>  | Address Hold from WE High                          |       | 5     |                      | 5     |      | ns    |

| twhen              | t <sub>CH</sub>  | CE Hold from WE High                               |       | 10    |                      | 10    |      | ns    |

| twhwL              | twpH             | WE Pulse Width High                                |       | 30    |                      | 30    |      | ns    |

| twhal              |                  | WE High to RY/BY Going Low                         |       |       | 100                  |       | 100  | ns    |

| twHQV1             |                  | Duration of Byte Write<br>Operation                | 5, 6  | 6     |                      | 6     |      | μs    |

| t <sub>WHQV2</sub> |                  | Duration of Block Erase<br>Operation               | 5, 6  | 0.3   |                      | 0.3   |      | sec   |

| twHGL              | ,                | Write Recovery before<br>Read                      |       | 0     |                      | 0     |      | μs    |

| <sup>t</sup> QVVL  | t <sub>VPH</sub> | V <sub>PP</sub> Hold from Valid SRD,<br>RY/BY High | 2, 6  | 0     |                      | 0     |      | ns    |

#### NOTES:

- 1. Read timing characteristics during erase and byte write operations are the same as during read-only operations. Refer to AC Characteristics for Read-Only Operations.

- 2. Sampled, not 100% tested.

- Sampied, not 100% tested.

Refer to Table 3 for valid A<sub>IN</sub> for byte write or block erasure.

Refer to Table 3 for valid D<sub>IN</sub> for byte write or block erasure.

The on-chip Write State Machine incorporates all byte write and block erase system functions and overhead of standard Intel flash memory, including byte program and verify (byte write) and block precondition, precondition verify, erase and erase verify (block erase).

Byte write and block erase durations are measured to completion (SR 7 = 1 RV/RV = Vo.). Ver should be held at

- erase verily (DIOCK erase).

6. Byte write and block erase durations are measured to completion (SR.7 = 1, RY/ $\overline{BY}$  = V<sub>OH</sub>). V<sub>PP</sub> should be held at V<sub>PPH</sub> until determination of byte write/block erase success (SR.3/4/5 = 0)

7. See AC Input/Output Reference Waveforms and AC Testing Load Circuits for testing characteristics.

# M28F008

### **BLOCK ERASE AND BYTE WRITE PERFORMANCE**

| Parameter        | Notes |     | M28F008- | 10  | ı   |         |     |      |

|------------------|-------|-----|----------|-----|-----|---------|-----|------|

|                  | NOIES | Min | Тур      | Max | Min | Тур Мах | Max | Unit |

| Block Erase Time | 1, 2  |     | 1.6      | 10  |     | 1.6     | 10  | sec  |

| Block Write Time | 1, 2  |     | 0.6      | 2.1 |     | 0.6     | 2.1 | sec  |

NOTES: 1. 25°C, 12.0 Vpp. 2. Excludes System-Level Overhead.

Figure 9. AC Waveform for Write Operations

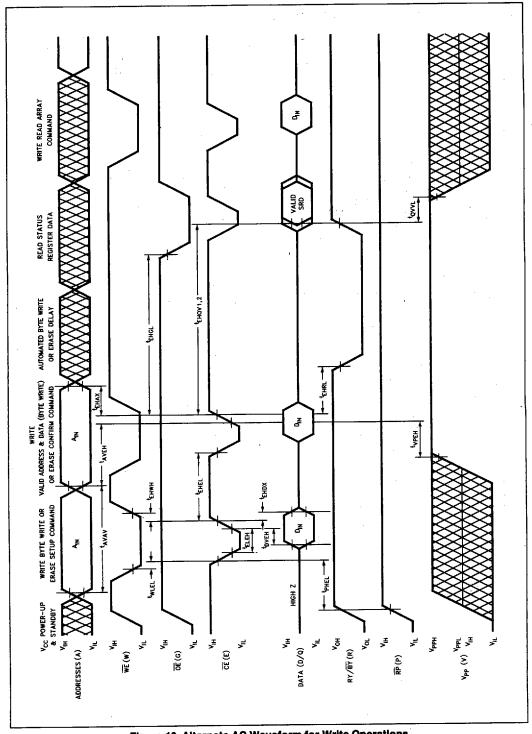

## **ALTERNATIVE CE-CONTROLLED WRITES(1)**

| Sym                | hal              | Parameter                                          | Natas | M28F0 | 08-10(6) | M28F0 | 08-12(6) | Maria |

|--------------------|------------------|----------------------------------------------------|-------|-------|----------|-------|----------|-------|

| Sym                | JOI              | Parameter                                          | Notes | Min   | Max      | Min   | Max      | Unit  |

| t <sub>AVAV</sub>  | twc              | Write Cycle Time                                   |       | 100   |          | 120   |          | ns    |

| t <sub>PHEL</sub>  | t <sub>PS</sub>  | RP High Recovery to CE<br>Going Low                | 2     | 1     |          | 1     |          | μs    |

| twlel              | tws              | WE Setup to CE Going Low                           |       | 0     |          | 0     | ,        | ns    |

| <sup>t</sup> ELEH  | t <sub>CP</sub>  | CE Pulse Width                                     |       | 50    |          | 50    |          | ns    |

| t <sub>VPEH</sub>  | t <sub>VPS</sub> | V <sub>PP</sub> Setup to CE Going High             | 2     | 100   |          | 100   |          | ns    |

| <sup>t</sup> AVEH  | tas              | Address Setup to CE Going High                     | 3     | 40    |          | 40    |          | ns    |

| t <sub>DVEH</sub>  | t <sub>DS</sub>  | Data Setup to CE Going High                        | 4     | 40    |          | 40    |          | ns    |

| t <sub>EHDX</sub>  | t <sub>DH</sub>  | Data Hold from CE High                             |       | 5     |          | 5     |          | ns    |

| t <sub>EHAX</sub>  | t <sub>AH</sub>  | Address Hold from CE High                          |       | 5     |          | 5     |          | ns    |

| <sup>t</sup> EHWH  | twH              | WE Hold from CE High                               |       | 0     |          | 0     |          | ns    |

| t <sub>EHEL</sub>  | t <sub>EPH</sub> | CE Pulse Width High                                |       | 25    |          | 25    |          | ns    |

| <sup>t</sup> EHRL  |                  | CE High to RY/BY Going<br>Low                      |       |       | 100      |       | 100      | ns    |

| t <sub>EHQV1</sub> |                  | Duration of Byte Write<br>Operation                | 5     | 6     |          | 6     |          | μs    |

| t <sub>EHQV2</sub> |                  | Duration of Block Erase<br>Operation               | 5     | 0.3   |          | 0.3   |          | sec   |

| t <sub>EHGL</sub>  |                  | Write Recovery before Read                         |       | 0     |          | 0     |          | μs    |

| <sup>t</sup> QVVL  | t∨PH             | V <sub>PP</sub> Hold from Valid SRD,<br>RY/BY High | 2, 5  | 0     |          | 0     |          | ns    |

<sup>1.</sup> Chip-Enable Controlled Writes: Write operations are driven by the valid combination of  $\overline{CE}$  and  $\overline{WE}$ . In systems where  $\overline{CE}$  defines the write pulsewidth (within a longer  $\overline{WE}$  timing waveform), all setup, hold and inactive  $\overline{WE}$  times should be measured relative to the  $\overline{CE}$  waveform.

2. Sampled, not 100% tested.

Sampled, not 100% tested.

Refer to Table 3 for valid A<sub>IN</sub> for byte write or block erasure.

Refer to Table 3 for valid D<sub>IN</sub> for byte write or block erasure.

Byte write and block erase durations are measured to completion (SR.7 = 1, RY/BY = V<sub>OH</sub>). V<sub>PP</sub> should be held at V<sub>PPH</sub> until determination of byte write/block erase success (SR.3/4/5 = 0)

See AC Input/Output Reference Waveforms and AC Testing Load Circuits for testing characteristics.

Figure 10. Alternate AC Waveform for Write Operations

Rochester Electronics guarantees performance of its semiconductor products to the original OEM specifications. "Typical" values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing. Rochester Electronics reserves the right to make changes without further notice to any specification herein.