# LM96511 LM96511 Ultrasound Receive Analog Front End (AFE)

# **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

> Literature Number: SNAS476H May 2010-Revised May 2013

SNAS476H-MAY 2010-REVISED MAY 2013

# Contents

| 1 | INTRO | DUCTIO  | ON       |                                        | . <u>6</u> |

|---|-------|---------|----------|----------------------------------------|------------|

|   | 1.1   | FEATUR  | ≀ES      |                                        | . <u>6</u> |

|   | 1.2   | APPLICA | ATIONS   |                                        | . <u>6</u> |

|   | 1.3   |         |          |                                        | _          |

| 2 | DEVIC |         |          | Ν                                      |            |

|   | 2.1   |         |          | IONS                                   |            |

|   | 2.2   | •       |          | 1 Block Diagram                        | _          |

|   | 2.3   |         |          | ۱                                      |            |

|   | 2.4   |         |          | ms                                     |            |

| 3 | ELEC  |         |          | ICATIONS                               |            |

|   | 3.1   |         |          | n Ratings                              |            |

|   | 3.2   | •       | 0 0      |                                        |            |

|   | 3.3   |         |          | aracteristics (B-Mode)                 |            |

|   | 3.4   |         |          | rical Characteristics                  |            |

|   | 3.5   |         |          | aracteristics                          |            |

|   | 3.6   |         |          | haracteristics                         | -          |

|   | 3.7   |         |          | aracteristics                          |            |

|   | 3.8   |         |          | Output Characteristics                 |            |

| 4 |       |         |          | S                                      |            |

|   | 4.1   |         |          | 1S                                     |            |

| 5 |       |         |          | NCE CHARACTERISTICS                    |            |

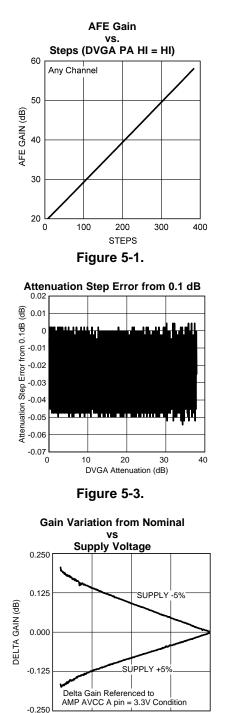

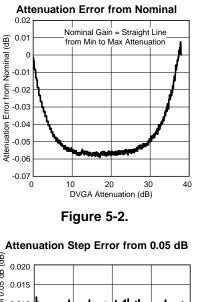

|   | 5.1   |         |          | erformance Characteristics             |            |

| _ | 5.2   |         |          |                                        |            |

| 6 |       |         |          |                                        |            |

|   | 6.1   |         |          | ITUDE RANGE                            |            |

|   | 6.2   |         |          | CONFIGURATION                          |            |

|   | 6.3   |         |          | E INPUT IMPEDANCE & LNA GAIN SELECTION |            |

|   | 6.4   |         |          | RIM                                    | _          |

|   | 6.5   |         |          |                                        |            |

|   | 6.6   | DVGA O  |          | N                                      |            |

|   |       | 6.6.1   |          | alf Step Mode                          | _          |

|   |       |         |          | K Pin                                  |            |

|   |       |         |          | A RST Pin                              |            |

|   |       |         |          | P Pin:                                 |            |

|   |       | 6.6.5   |          | celerated Gain Adjustment:             |            |

|   | 6.7   |         |          | C                                      |            |

|   | 6.8   |         |          | ERFACE                                 |            |

|   | 6.9   |         |          | ELTA (ΣΔ) ADC CORE                     |            |

|   | 6.10  |         |          | DAD RECOVERY                           |            |

|   | 6.11  |         |          | ODE                                    |            |

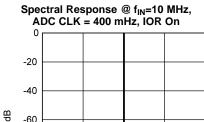

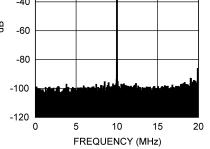

|   |       |         |          | Use of IOR On Mode                     |            |

|   |       |         |          | d Use of IOR On Mode                   |            |

|   | 6.12  |         |          | ECISION LC PLL ADVANTAGES              |            |

|   | 6.13  |         |          | TION FILTER AND EQUALIZER              |            |

|   | 6.14  |         |          | SYNCHRONIZATION ACROSS MULTIPLE CHIPS  |            |

|   | 6.15  |         |          | ECTION                                 |            |

|   | 6.16  |         |          | NSIDERATIONS                           |            |

|   |       | 6.16.1  |          | riving Voltage, ADC IO DVDD            |            |

|   |       |         |          | Output Modes and Output Common Mode    |            |

|   |       |         |          | Termination                            |            |

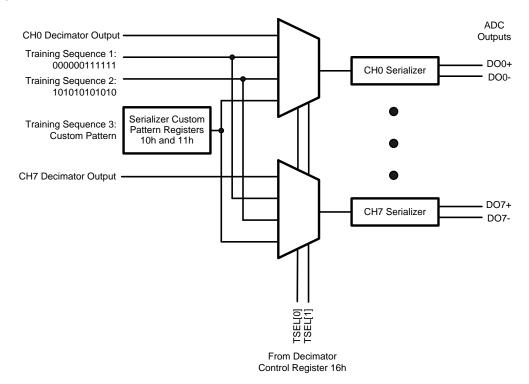

|   |       |         | 6.16.1.3 | LVDS Output Training Sequences         | <u>48</u>  |

### SNAS476H-MAY 2010-REVISED MAY 2013

| 6.17               | The Voltage Reference                                   | <u>48</u> |

|--------------------|---------------------------------------------------------|-----------|

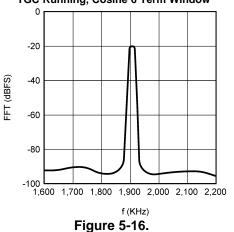

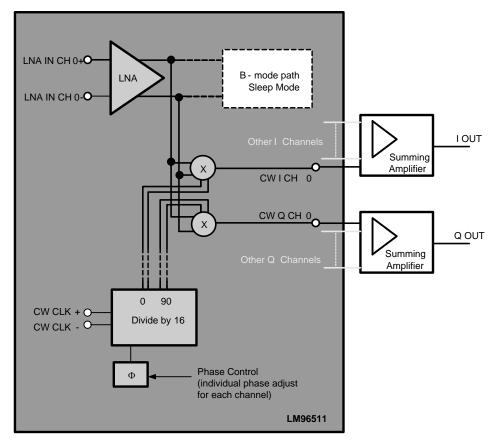

| 6.18               | CW Doppler Section Theory of Operation                  | 49        |

|                    | 6.18.1 CW DOPPLER NOISE ANALYSIS                        |           |

|                    | 6.18.2 CW DOPPLER 16x LO SOURCE IMPLEMENTATION          | 53        |

| 6.19               | LM96511 Power Management                                | 54        |

|                    | 6.19.1 POWER-UP SEQUENCING                              | 55        |

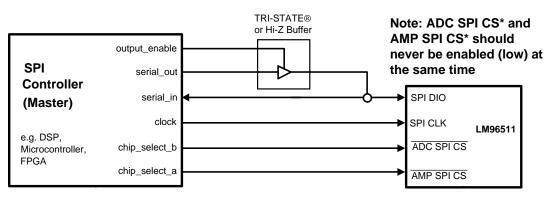

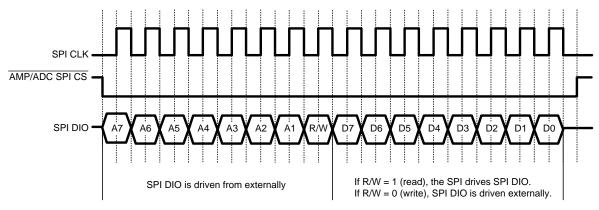

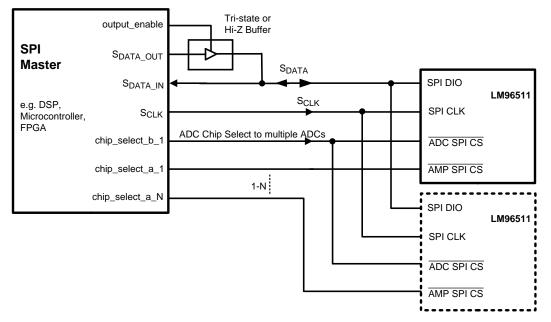

| 6.20               | SPI™ Interface                                          | 56        |

|                    | 6.20.1 THE SERIAL PERIPHERAL INTERFACE                  | 56        |

|                    | 6.20.2 ACCESS TO THE SERIAL PERIPHERAL INTERFACE        | 56        |

|                    | 6.20.3 CONNECTING MULTIPLE LM96511 DEVICES TOGETHER     | 57        |

|                    | 6.20.4 SERIAL PERIPHERAL INTERFACE READ AND WRITE SPEED |           |

| 6.21               | SPI™ Register Map                                       | 58        |

| 6.22               | SPI™ Register Map Notes                                 | 61        |

| <b>Revision Hi</b> | istory                                                  |           |

# List of Figures

| 2-1  | Simplified LM96511 Block Diagram                                              | <u>8</u>  |

|------|-------------------------------------------------------------------------------|-----------|

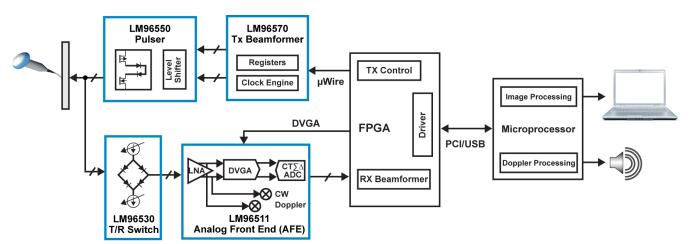

| 2-2  | 8-Channel Transmit/Receive Chipset                                            | <u>9</u>  |

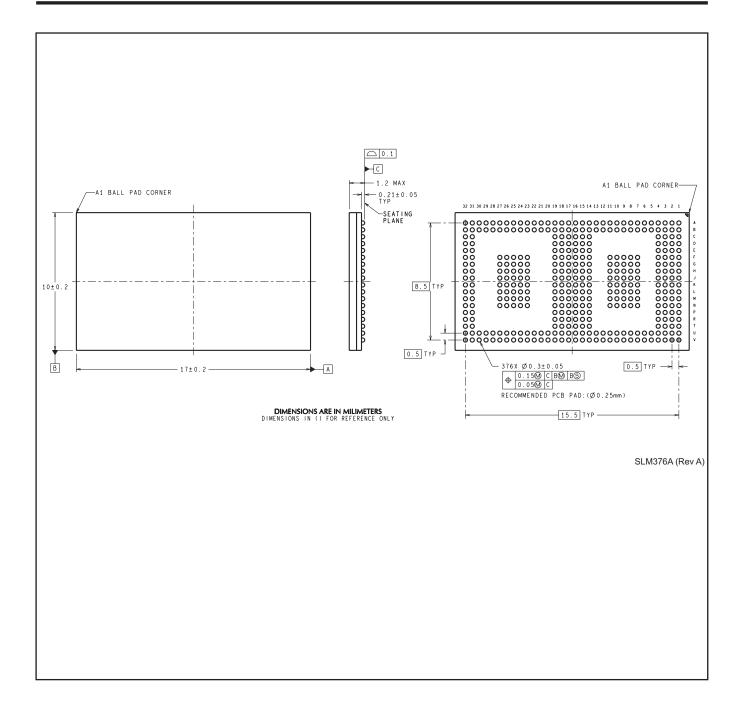

| 2-3  | 376–Pin NFBGA Package (18 Rows by 32 Columns)<br>See Package Number NZJ0376A  | <u>10</u> |

| 2-4  | 376–Pin NFBGA Package (18 Rows by 32 Columns)<br>See Package Number NZJ0376A  | 10        |

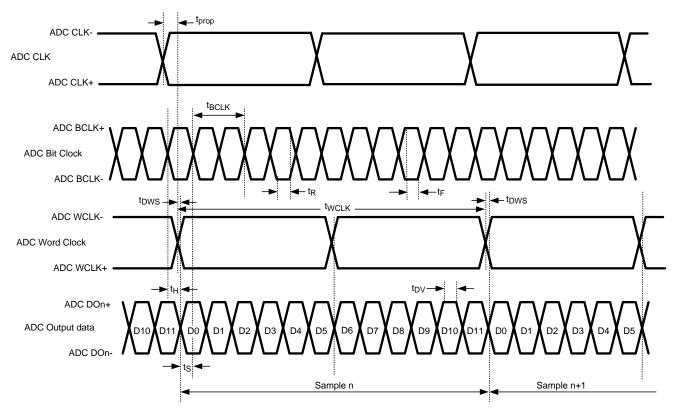

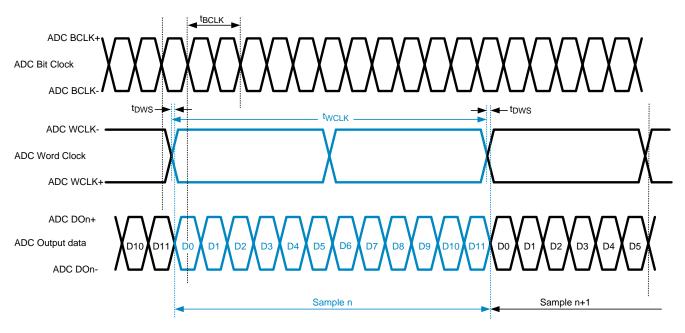

| 4-1  | B-Mode ADC Data Output Timing                                                 |           |

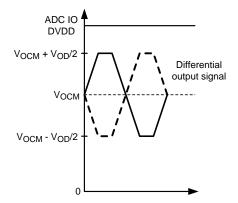

| 4-2  | B-Mode ADC Data Output Level Definitions                                      |           |

| 4-3  | CW CLK Level Definitions                                                      | 25        |

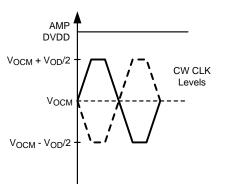

| 4-4  | SPI™ Write Timing                                                             |           |

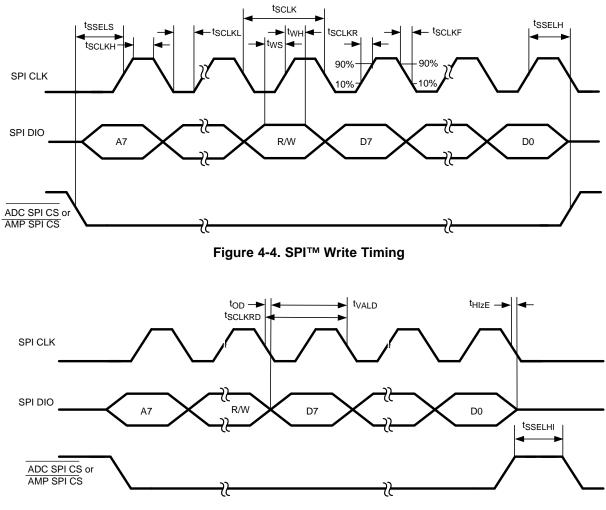

| 4-5  | SPI™ Read Timing                                                              | 26        |

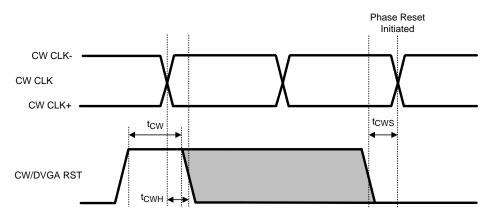

| 4-6  | CW/DVGA RST Timing (CW Doppler Mode)                                          | 26        |

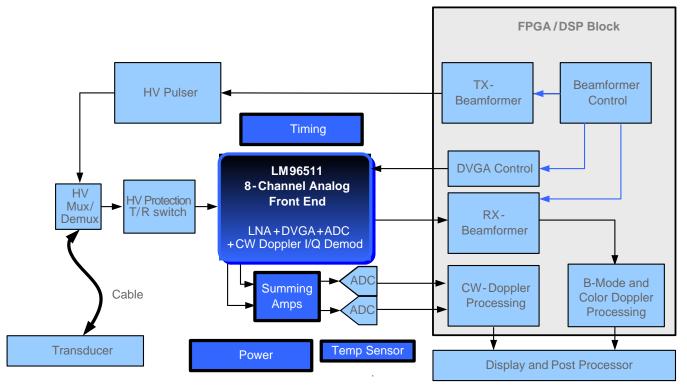

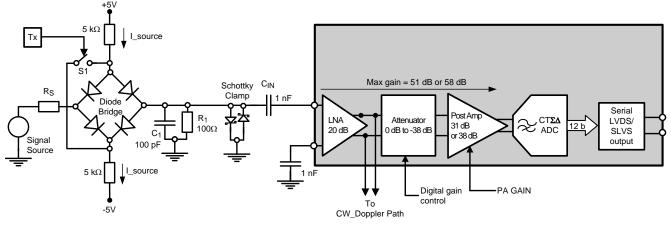

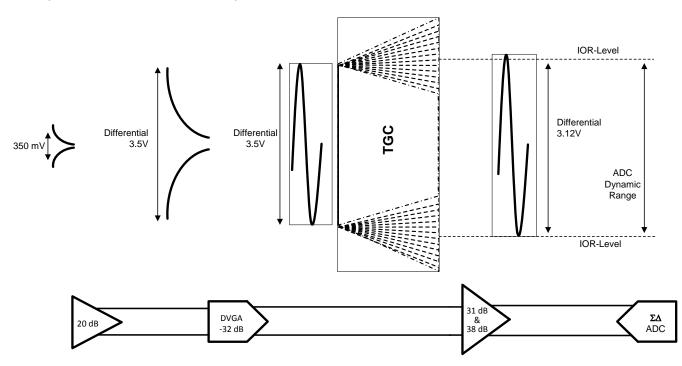

| 6-1  | Ultra-Sound System Block Diagram                                              | 32        |

| 6-2  | Signal Path (B-Mode) Single Channel<br>Including Input Clamp and Diode Bridge | 33        |

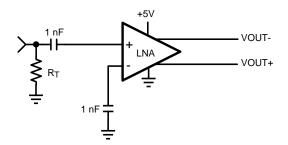

| 6-3  | Standard Input Termination                                                    |           |

| 6-4  | Active Termination Schematic                                                  |           |

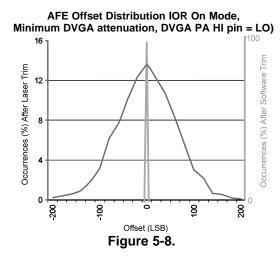

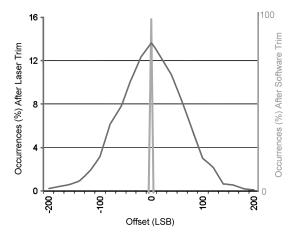

| 6-5  | Offset Distribution Histogram including Soft-Trim Improvement                 |           |

| 6-6  | LM96511 in Typical TGC Operation at 5MHz                                      |           |

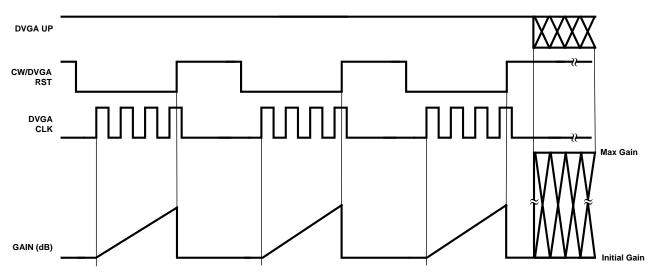

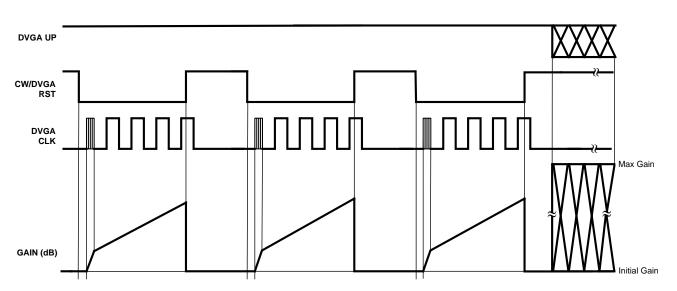

| 6-7  | Periodic TGC Ramp: Example 1 (Half-Step Disable bit = 1)                      |           |

| 6-8  | DVGA UP bit Change (Half-Step Disable bit = 1)                                |           |

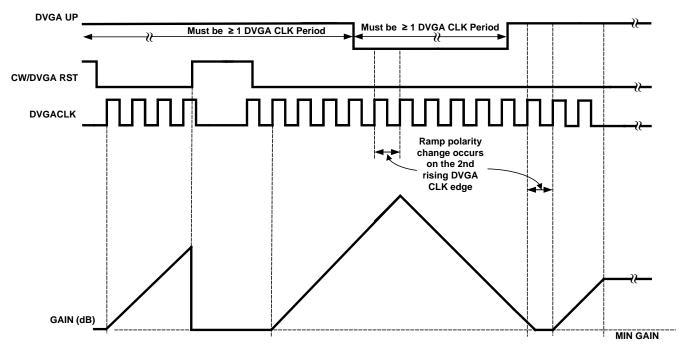

| 6-9  | Periodic TGC Ramp: Example 2 (Half Step Disable bit = 1)                      |           |

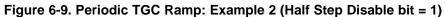

| 6-10 | Basic Gain Adjustment (Half Step Disable Bit = 1)                             |           |

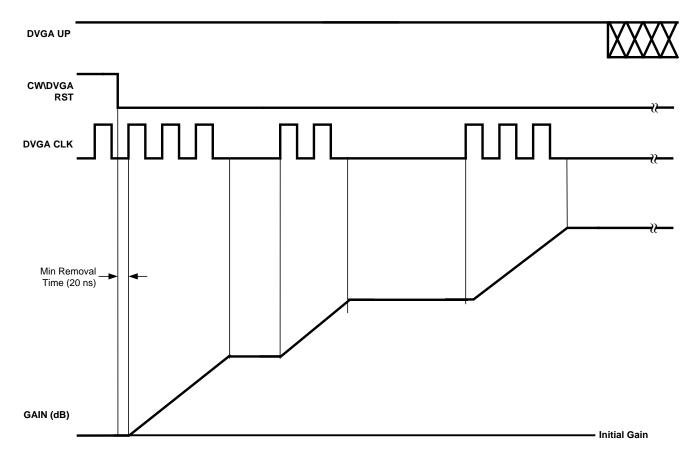

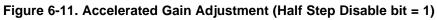

| 6-11 | Accelerated Gain Adjustment (Half Step Disable bit = 1)                       |           |

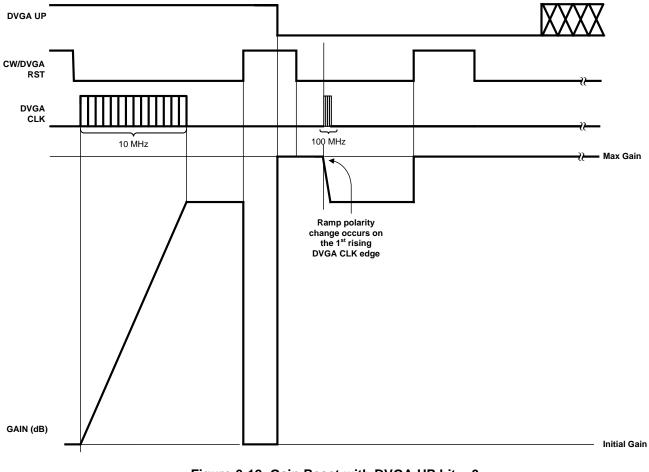

| 6-12 | Gain Reset with DVGA UP bit = 0                                               | 40        |

| 6-13 | DVGA Gain control "Micro Illustration" of the Gain Stair Case                 | 40        |

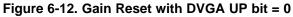

| 6-14 | LM96511 ADC Block Diagram                                                     | 42        |

| 6-15 | ADC WCLK                                                                      | <u>43</u> |

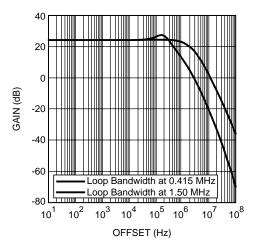

| 6-16 | PLL Phase Noise Transfer Function: ADC CLK = 40 MHz                           | <u>45</u> |

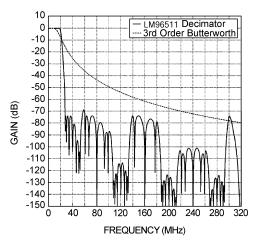

| 6-17 | Digital Filter Transfer Function                                              | 46        |

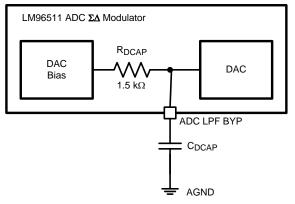

| 6-18 | DAC LPF Capacitor                                                             | <u>47</u> |

| 6-19 | LVDS Training Sequence                                                        | <u>48</u> |

| 6-20 | Reference Sharing                                                             | <u>49</u> |

| 6-21 | Signal Path (CW Doppler) Single Channel                                       | <u>50</u> |

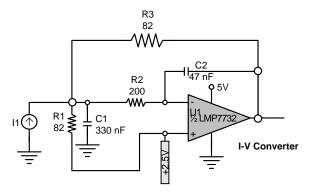

| 6-22 | I-V with Integrated 2–Pole LFP                                                | <u>50</u> |

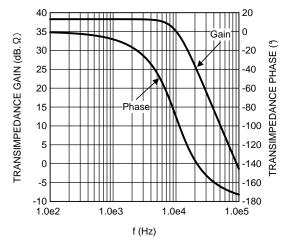

| 6-23 | CW Doppler LPF Gain/Phase Characteristics                                     | <u>51</u> |

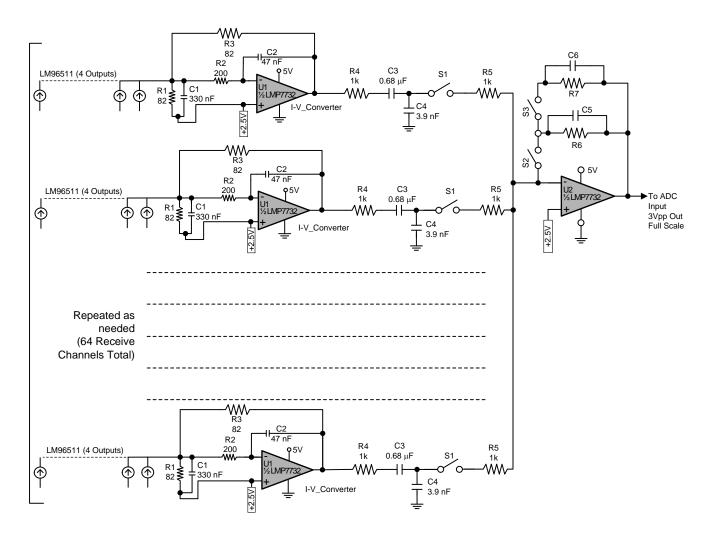

| 6-24 | CW Doppler Output (I or Q) Implementation (64 Receive Channels)               | <u>53</u> |

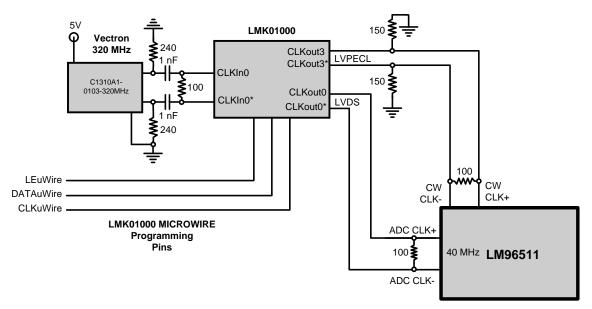

| 6-25 | CW Doppler Low-Phase Noise Clock Source Design                                | <u>54</u> |

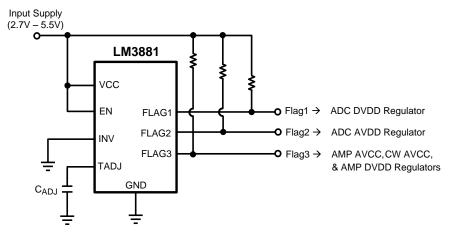

| 6-26 | LM3881 Power Sequencer Can be Used for Proper LM96511 Power-Up                | <u>56</u> |

| 6-27 | SPI™ Bus Master Slave Connection                                              | <u>56</u> |

| 6-28 | SPI™ Compatible Read/Write Timing Diagram                                     | <u>57</u> |

| 6-29 | SPI™ Compatible Interconnect for Multiple LM96511's (Open Drain Mode)         | 58        |

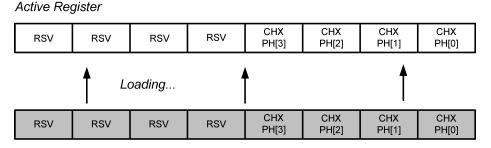

| 6-30 | CW Doppler Shadow Register Representation                                     | <u>67</u> |

|      |                                                                               |           |

#### www.ti.com

# List of Tables

| 2-1 | Pin Descriptions                                 | <u>11</u> |

|-----|--------------------------------------------------|-----------|

| 6-1 | ADC Output Mode Summary                          | <u>47</u> |

| 6-2 | LM96511 Power Consumption for Various Conditions | 54        |

| 6-3 | Recommended Operating Conditions                 | 56        |

| 6-4 | DVGA Initial Attenuation Truth Table             | 68        |

| 6-5 | DVGA Notation                                    | 68        |

| 6-6 | Offset Trim "Write" Truth Table                  | 69        |

| 6-7 | Offset Trim "Write" and "Read" Example           | 69        |

|     |                                                  |           |

www.ti.com

# LM96511 Ultrasound Receive Analog Front End (AFE)

Check for Samples: LM96511

Embedded ADC Digital Filter

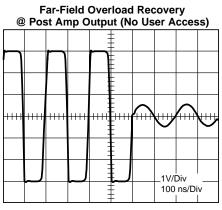

ADC Instant Overload Recovery

• Embedded ADC "Clock-Cleaning" PLL

• 11 mm x 17 mm RoHS NFBGA Package

# 1 INTRODUCTION

# 1.1 FEATURES

- 8-Channel LNA, DVGA, and 12-bit Continuous Time  $\Sigma\Delta$  ADC

- Programmable Active Termination LNA

- 8-channel, Integrated CW Doppler Beamforer

- Low-Power Consumption

# 1.2 APPLICATIONS

- Ultrasound Imaging

- Communications

- Portable Instrumentation

- Sonar

# 1.3 DESCRIPTION

The LM96511 is an 8-channel integrated analog front end (AFE) module for multi-channel applications, particularly medical ultrasound. Each of the 8 signal paths consists of a low noise amplifier (LNA), a digitally programmable variable gain amplifier (DVGA) and a 12-bit, 40 Mega Samples Per Second (MSPS) analog-to-digital converter (ADC) with Instant Overload Recovery (IOR). The architecture of the DVGA is a digitally-controlled linear-in-dB step attenuator driving a fixed-gain post-amplifier (PA). The ADC uses a Continuous-Time-Sigma-Delta (CT $\Sigma\Delta$ ) architecture with digital decimation filtering to maximize dynamic performance and provide an alias free input bandwidth to ADC CLK / 2. The ADC digital outputs are serialized and provided on differential LVDS outputs. The ADC includes an on-chip clock cleaner PLL.

In addition, for baseband CW Doppler Beamformer applications, an 8-channel demodulator with 16 discrete phase rotation angles is included.

Selective power reduction is included to minimize consumption of idle sections during interleaved imaging modes.

An SPI<sup>™</sup> compatible serial interface allows dynamic digital programming and control. Texas Instruments offers a full development package for sale which includes acquisition analysis hardware and software with user friendly GUI for device programming and control.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# 2 DEVICE INFORMATION

# 2.1 KEY SPECIFICATIONS

|                                          | VALUE              | UNIT     |

|------------------------------------------|--------------------|----------|

| (Full path unless noted)                 |                    | <u>.</u> |

| B-Mode:                                  |                    |          |

| Total Input Voltage Noise (RTI)          | 0.9 nV/vHz         |          |

| Max AFE Gain                             | 58                 | dB       |

| Single-Ended Input Swing                 | 500mVpp            |          |

| Programmable Maximum DVGA Attenuation    | 38, 36, 34, 32     | dB       |

| Programmable Post Amp Gain               | 31 or 38           | dB       |

| Attenuator Step Resolution               | 0.05 or 0.1        | dB       |

| ADC Resolution                           | 12                 | bits     |

| Conversion Rate (ADC CLK)                | 40                 | MSPS     |

| ADC Digital Filter stop band attenuation | 72                 | dB       |

| ADC Digital Filter Passband Ripple       | ± 0.01             | dB       |

| ADC Instant Overload Recovery            | 1 ADC Clock Period |          |

| Power Consumption (per channel)          | 110 mW             |          |

| CW Doppler Mode:                         |                    |          |

| Phase Rotation Resolution                | 22.5 degrees       |          |

| Phase Noise (Per Channel, Offset = 5KHz) | -144 dBc/Hz        |          |

| Dynamic Range                            | -161 dB/Hz         |          |

| Amplitude Quadrature Error (I to Q)      | ± 0.04             | dB       |

| Phase Quadrature Error (I to Q)          | ± 0.10°            |          |

| Power Consumption (Per Channel)          | 208 mW             |          |

| Common Specifications:                   |                    |          |

| LNA Input Voltage Noise                  | 0.82 nV/vHz        |          |

| Operating temp. Range                    | 0 to +70°C         |          |

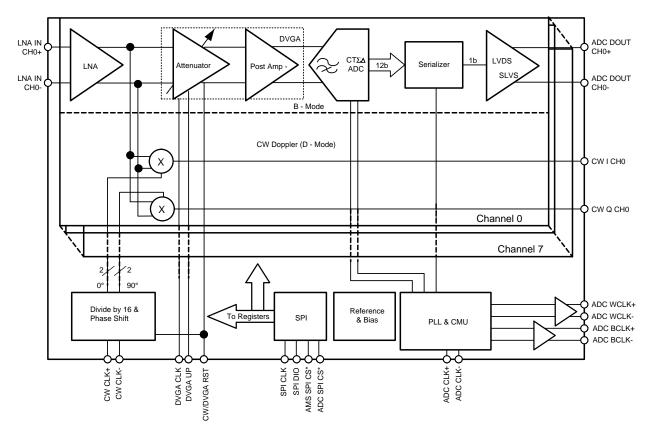

# 2.2 Simplified LM96511 Block Diagram

Figure 2-1. Simplified LM96511 Block Diagram

# 2.3 Typical Application

# 2.4 Connection Diagrams

|   | 1                | 2               | 3          | 4               | 5                | 6                | 7               | 8               | 9               | 10              | 11              | 12      | 13         | 14             | 15              | 16              |   |

|---|------------------|-----------------|------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|------------|----------------|-----------------|-----------------|---|

| A | LNA PD           | DVGA PD         | AMP RST    | AMP SPI CS      | ADC SPI CS       | DVGA INIT<br>MSB | AMP DVDD        | AMP DGND        | AGND            | AMP AVCC A      | CW I CH7        | AGND    | AGND       | CW DGND        | CW DGND         | AGND            | A |

| в | DVGA PA HI       | CW AVCC         | SPI CLK    | SPI DIO         | DVGA INIT<br>LSB | AMP IO<br>DVDD   | AMP DVDD        | AMP AVCC A      | DVGA BYP<br>CH7 | CW AVCC         | CW Q CH7        | CW DGND | CW DGND    | CW AVCC        | CW AVCC         | CWICH6          | в |

| С | NC               | CW AVCC         | AGND       | NC              |                  |                  |                 |                 |                 |                 |                 |         |            | CW AVCC        | DVGA BYP<br>CH6 | AMP AVCC A      | С |

| D | LNA IN CH7-      | LNA IN CH7+     | AGND       | LNA OUT<br>CH7- |                  |                  |                 |                 |                 |                 |                 |         |            | AMP AVCC A     | AMP AVCC A      | DVGA BYP<br>CH5 | D |

| Е | LNA IN CH6+      | CW AVCC         | NC         | AMP AVCC A      |                  |                  |                 |                 |                 |                 |                 |         |            | AMP AVCC A     | CWICH5          | CW AVCC         | E |

| F | LNA OUT<br>CH6-  | LNA IN CH6-     | AGND       | CW AVCC         |                  |                  | AMP THRM<br>GND |         |            | CW Q CH5       | CW DGND         | CW DGND         | F |

| G | LNA IN CH5+      | NC              | AMP AVCC A | CW AVCC         |                  |                  | AMP THRM<br>GND |         |            | CW Q CH4       | CW AVCC         | CWICH4          | G |

| н | LNA OUT<br>CH5 - | LNA IN CH5-     | AGND       | CW AVCC         |                  |                  | AMP THRM<br>GND |         |            | AMP DGND       | CW AVCC         | AMP DVDD        | н |

| J | LNA IN CH4+      | NC              | AMP AVCC A | CW AVCC         |                  |                  | AMP THRM<br>GND |         |            | CW CLK+        | CW CLK-         | AMP AVCC A      | J |

| ĸ | LNA OUT<br>CH4-  | LNA IN CH4-     | AGND       | CW AVCC         |                  |                  | AMP THRM<br>GND |         |            | DVGA CLK       | CW/DVGA<br>RST  | AMP<br>CW/DVGA  | к |

| L | LNA IN CH3+      | NC              | AMP AVCC A | CW AVCC         |                  |                  | AMP THRM<br>GND |         |            | AMP IO<br>DVDD | DVGA BYP<br>CH3 | AMP AVCC A      | L |

| М | LNA OUT<br>CH3-  | LNA IN CH3-     | AGND       | AMP AVCC A      |                  |                  | AMP THRM<br>GND |         |            | CW AVCC        | CW AVCC         | CW I CH3        | м |

| Ν | LNA IN CH2+      | CW AVCC         | NC         | AMP AVCC A      |                  |                  | AMP THRM<br>GND |         |            | CW Q CH3       | CW DGND         | CW DGND         | N |

| Ρ | LNA OUT<br>CH2-  | LNA IN CH2-     | AGND       | CW AVCC         |                  |                  |                 |                 |                 |                 |                 |         |            | AGND           | CWICH2          | CW AVCC         | Р |

| R | LNA IN CH1+      | NC              | AMP AVCC A | AGND            |                  |                  |                 |                 |                 |                 |                 |         |            | AMP AVCC A     | AMP AVCC A      | DVGA BYP<br>CH2 | R |

| т | LNA OUT<br>CH1-  | LNA IN CH1-     | CW AVCC    | AMP AVCC A      |                  |                  |                 |                 |                 |                 |                 |         |            | AMP AVCC A     | AMP AVCC A      | CW AVCC         | т |

| U | LNA IN CHO+      | NC              | AGND       | AMP AVCC A      | AMP DGND         | AGND             | AMP AVCC A      | AMP AVCC A      | CW AVCC         | CVV Q CHO       | CW DGND         | AGND    | AMP AVCC A | AMP DVDD       | AMP DVDD        | CW AVCC         | U |

| ۷ | LNA IN CHO-      | LNA OUT<br>CHD- | AGND       | AMP AVCC A      | AMP DVDD         | AMP AVCC A       | NC              | DVGA BYP<br>CH0 | CW AVCC         | CWICHD          | AGND            | AGND    | AMP AVCC A | CW I CH1       | AGND            | CW DGND         | ۷ |

|   | 1                | 2               | 3          | 4               | 5                | 6                | 7               | 8               | 9               | 10              | 11              | 12      | 13         | 14             | 15              | 16              |   |

**Top View**

Figure 2-3. 376–Pin NFBGA Package (18 Rows by 32 Columns) See Package Number NZJ0376A

www.ti.com

| Top View |  |

|----------|--|

|----------|--|

|   | 17              | 18       | 19       | 20   | 21              | 22       | 23              | 24              | 25              | 26              | 27              | 28             | 29             | 30             | 31               | 32               |   |

|---|-----------------|----------|----------|------|-----------------|----------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|------------------|------------------|---|

| A | CW Q CH6        | NC       | ADC AVDD | NC   | NC              | ADC CLK- | AGND            | AGND            | AGND            | ADC DVDD        | ADC IO<br>DGND  | ADC IO<br>DGND | ADC WCLK-      | ADC WCLK+      | ADC BCLK-        | ADC BCLK+        | A |

| в | AGND            | NC       | AGND     | AGND | AGND            | ADC CLK+ | AGND            | AGND            | ADC DVDD        | ADC DVDD        | ADC 10<br>DGND  | ADC IO<br>DGND | AGND           | ADC IO<br>DVDD | AGND             | ADC DOUT<br>CH7- | в |

| с | AMP AVCC A      | ADC AVDD | AGND     |      |                 |          |                 |                 |                 |                 |                 |                |                |                | AGND             | ADC DOUT<br>CH7+ | c |

| D | AMP AVCC A      | AGND     | AGND     |      |                 |          |                 |                 |                 |                 |                 |                |                |                | ADC IO<br>DGND   | ADC DOUT<br>CH6- | D |

| E | CW AVCC         | NC       | NC       |      |                 |          |                 |                 |                 |                 |                 |                |                |                | ADC IO<br>DGND   | ADC DOUT<br>CH6+ | E |

| F | AGND            | ADC AVDD | AGND     |      |                 |          | ADC THRM<br>GND |                |                |                | AGND             | ADC DOUT<br>CH5- | F |

| 3 | AGND            | AGND     | AGND     |      |                 |          | ADC THRM<br>GND |                |                |                | ADC IO<br>DVDD   | ADC DOUT<br>CH5+ | G |

| H | AMP DVDD        | NC       | NC       |      |                 |          | ADC THRM<br>GND |                |                |                | ADC IO<br>DVDD   | ADC DOUT<br>CH4- | н |

| J | DVGA BYP<br>CH4 | ADC AVDD | AGND     |      |                 |          | ADC THRM<br>GND |                |                |                | AGND             | ADC DOUT<br>CH4+ | J |

| K | AMP AVCC A      | NC       | AGND     |      |                 |          | ADC THRM<br>GND |                |                |                | AGND             | ADC DOUT<br>CH3- | к |

| L | DVGA UP         | AGND     | NC       |      |                 |          | ADC THRM<br>GND |                |                |                | AGND             | ADC DOUT<br>CH3+ | L |

| N | AGND            | AGND     | ADC AVDD |      |                 |          | ADC THRM<br>GND |                |                |                | ADC IO<br>DGND   | AGND             | м |

| N | AGND            | AGND     | NC       |      |                 |          | ADC THRM<br>GND |                |                |                | ADC IO<br>DGND   | ADC DOUT<br>CH2- | N |

| P | CW Q CH2        | AGND     | NC       |      |                 |          |                 |                 |                 |                 |                 |                |                |                | AGND             | ADC DOUT<br>CH2+ | P |

| R | CW AVCC         | AGND     | ADC AVDD |      |                 |          |                 |                 |                 |                 |                 |                |                |                | AGND             | NC               | R |

| т | DVGA BYP<br>CH1 | AGND     | AGND     |      |                 |          |                 |                 |                 |                 |                 |                |                |                | NC               | ADC DOUT<br>CH1- | т |

| U | AMP DGND        | NC       | ADC AVDD | NC   | AGND            | AGND     | ADC RREF        | ADC AVDD        | ADC RST         | ADC AVDD        | ADC DVDD        | ADC AVDD       | ADC IO<br>DGND | AGND           | ADC IO<br>DVDD   | ADC DOUT<br>CH1+ | U |

| V | CW Q CH1        | NC       | AGND     | NC   | ADC VREF<br>GND | ADC VREF | ADC LPF<br>BYP  | AGND            | AGND            | ADC<br>CW/DVGA  | ADC AVDD        | ADC DVDD       | ADC AVDD       | ADC IO<br>DGND | ADC DOUT<br>CHD+ | ADC DOUT<br>CHD- | v |

|   | 17              | 18       | 19       | 20   | 21              | 22       | 23              | 24              | 25              | 26              | 27              | 28             | 29             | 30             | 31               | 32               |   |

Figure 2-4. 376–Pin NFBGA Package (18 Rows by 32 Columns) See Package Number NZJ0376A

# Table 2-1. Pin Descriptions

| Ball Id.<br>(Row_Column) | Pin Name           | Function | Description                                                                    |  |  |  |  |

|--------------------------|--------------------|----------|--------------------------------------------------------------------------------|--|--|--|--|

|                          |                    | Amplif   | ier Signals                                                                    |  |  |  |  |

| U1                       | LNA IN CH0+        |          |                                                                                |  |  |  |  |

| R1                       | LNA IN CH1+        |          |                                                                                |  |  |  |  |

| N1                       | LNA IN CH2+        |          |                                                                                |  |  |  |  |

| L1                       | LNA IN CH3+        |          | I NA Neg Investing Input                                                       |  |  |  |  |

| J1                       | LNA IN CH4+        |          | LNA Non-Inverting Input                                                        |  |  |  |  |

| G1                       | LNA IN CH5+        |          |                                                                                |  |  |  |  |

| E1                       | LNA IN CH6+        |          |                                                                                |  |  |  |  |

| D2                       | LNA IN CH7+        | Innut    |                                                                                |  |  |  |  |

| V1                       | LNA IN CH0-        | Input    | LNA Inverting Input                                                            |  |  |  |  |

| T2                       | LNA IN CH1-        |          |                                                                                |  |  |  |  |

| P2                       | LNA IN CH2-        |          |                                                                                |  |  |  |  |

| M2                       | LNA IN CH3-        |          |                                                                                |  |  |  |  |

| K2                       | LNA IN CH4-        |          |                                                                                |  |  |  |  |

| H2                       | LNA IN CH5-        |          |                                                                                |  |  |  |  |

| F2                       | LNA IN CH6-        |          |                                                                                |  |  |  |  |

| D1                       | LNA IN CH7-        |          |                                                                                |  |  |  |  |

| V2                       | LNA OUT CH0-       |          |                                                                                |  |  |  |  |

| T1                       | LNA OUT CH1-       |          |                                                                                |  |  |  |  |

| P1                       | LNA OUT CH2-       | - Output |                                                                                |  |  |  |  |

| M1                       | LNA OUT CH3-       |          | LNA Inverting Output                                                           |  |  |  |  |

| K1                       | LNA OUT CH4-       |          |                                                                                |  |  |  |  |

| H1                       | LNA OUT CH5 -      |          |                                                                                |  |  |  |  |

| F1                       | LNA OUT CH6-       |          |                                                                                |  |  |  |  |

| D4                       | LNA OUT CH7-       |          |                                                                                |  |  |  |  |

| V8                       | DVGA BYP CH0       |          |                                                                                |  |  |  |  |

| T17                      | DVGA BYP CH1       |          |                                                                                |  |  |  |  |

| R16                      | DVGA BYP CH2       |          |                                                                                |  |  |  |  |

| L15                      | DVGA BYP CH3       | Bypace   | Decoupling Capacitor to Analog Ground                                          |  |  |  |  |

| J17                      | DVGA BYP CH4       | Bypass   |                                                                                |  |  |  |  |

| D16                      | DVGA BYP CH5       |          |                                                                                |  |  |  |  |

| C15                      | DVGA BYP CH6       |          |                                                                                |  |  |  |  |

| В9                       | DVGA BYP CH7       |          |                                                                                |  |  |  |  |

| J14<br>J15               | CW CLK+<br>CW CLK- | Input    | CW DOPPLER Differential Input Clock +<br>CW DOPPLER Differential Input Clock - |  |  |  |  |

| V10                      | CW I CH0           |          |                                                                                |  |  |  |  |

| V14                      | CW I CH1           | Output   |                                                                                |  |  |  |  |

| P15                      | CW I CH2           |          |                                                                                |  |  |  |  |

| M16                      | CW I CH3           |          |                                                                                |  |  |  |  |

| G16                      | CW I CH4           | Output   | CW DOPPLER In-Phase output current                                             |  |  |  |  |

| E15                      | CW I CH5           |          |                                                                                |  |  |  |  |

| B16                      | CW I CH6           |          |                                                                                |  |  |  |  |

| A11                      | CW I CH7           |          |                                                                                |  |  |  |  |

Texas Instruments

www.ti.com

# Table 2-1. Pin Descriptions (continued)

| Dall 14                  |                      | 2 1.1 11 003 | criptions (continued)                                                                                                                              |  |  |  |  |  |

|--------------------------|----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Ball Id.<br>(Row_Column) | Pin Name             | Function     | Description                                                                                                                                        |  |  |  |  |  |

| U10                      | CW Q CH0             |              |                                                                                                                                                    |  |  |  |  |  |

| V17                      | CW Q CH1             |              |                                                                                                                                                    |  |  |  |  |  |

| P17                      | CW Q CH2             |              |                                                                                                                                                    |  |  |  |  |  |

| N14                      | CW Q CH3             | Output       | CW DOPPLER Quadrature-Phase output current                                                                                                         |  |  |  |  |  |

| G14                      | CW Q CH4             | Output       | W DOI'T LEIN Quadrature-I hase output current                                                                                                      |  |  |  |  |  |

| F14                      | CW Q CH5             |              |                                                                                                                                                    |  |  |  |  |  |

| A17                      | CW Q CH6             |              |                                                                                                                                                    |  |  |  |  |  |

| B11                      | CW Q CH7             |              |                                                                                                                                                    |  |  |  |  |  |

|                          |                      | Amplifi      | er Controls                                                                                                                                        |  |  |  |  |  |

| K14                      | DVGA CLK             |              | DVGA GAIN Clock                                                                                                                                    |  |  |  |  |  |

| L17                      | DVGA UP              |              | 1 = Increment DVGA gain<br>0 = Decrement DVGA gain                                                                                                 |  |  |  |  |  |

| A6                       | DVGA INIT MSB        |              | DVGA Initial Gain Control. Sets the initial DVGA gain. See Section 6.                                                                              |  |  |  |  |  |

| B5                       | DVGA INIT LSB        |              |                                                                                                                                                    |  |  |  |  |  |

| K15                      | CW/DVGA RST          | Input        | 1 = CW DOPPLER Phase and DVGA Gain Reset                                                                                                           |  |  |  |  |  |

| K16                      | AMP CW/DVGA          |              | 0 = B-mode<br>1 = CW DOPPLER mode                                                                                                                  |  |  |  |  |  |

| A1                       | LNA PD               |              | 1 = LNA Power-down                                                                                                                                 |  |  |  |  |  |

| A2                       | DVGA PD              |              | 1 = DVGA Power-down                                                                                                                                |  |  |  |  |  |

| A3                       | AMP RST              |              | 1 = Reset all Amplifier SPI™ Registers                                                                                                             |  |  |  |  |  |

| B1                       | DVGA PA HI           |              | Post Amplifier Gain:<br>1= 38 dB<br>0= 31 dB                                                                                                       |  |  |  |  |  |

|                          | +                    | ADC          | Signals                                                                                                                                            |  |  |  |  |  |

| B22<br>A22               | ADC CLK+<br>ADC CLK- | Input        | Differential Input Clock. The input clock must lie in the range of 40 to 40.5 MHz. It is used by the PLL to generate the internal sampling clocks. |  |  |  |  |  |

| V31                      | ADC DOUT CH0+        |              |                                                                                                                                                    |  |  |  |  |  |

| U32                      | ADC DOUT CH1+        |              |                                                                                                                                                    |  |  |  |  |  |

| P32                      | ADC DOUT CH2+        |              |                                                                                                                                                    |  |  |  |  |  |

| L32                      | ADC DOUT CH3+        |              |                                                                                                                                                    |  |  |  |  |  |

| J32                      | ADC DOUT CH4+        |              |                                                                                                                                                    |  |  |  |  |  |

| G32                      | ADC DOUT CH5+        |              |                                                                                                                                                    |  |  |  |  |  |

| E32                      | ADC DOUT CH6+        |              | Differential Serial Outputs for channels 0 to 7. Each pair of outputs                                                                              |  |  |  |  |  |

| C32                      | ADC DOUT CH7+        | 0.1.1.1      | provides the serial output for the specific channel. The default output is LVDS format, but programming the appropriate control registers,         |  |  |  |  |  |

| V32                      | ADC DOUT CH0-        | Output       | the output format can be changed to SLVS .                                                                                                         |  |  |  |  |  |

| T32                      | ADC DOUT CH1-        |              | By programming TX_term (bit 4) in the LVDS Control register, it is possible to internally terminate these outputs with 100Ω resistors.             |  |  |  |  |  |

| N32                      | ADC DOUT CH2-        |              |                                                                                                                                                    |  |  |  |  |  |

| K32                      | ADC DOUT CH3-        |              |                                                                                                                                                    |  |  |  |  |  |

| H32                      | ADC DOUT CH4-        |              |                                                                                                                                                    |  |  |  |  |  |

| F32                      | ADC DOUT CH5-        |              |                                                                                                                                                    |  |  |  |  |  |

| D32                      | ADC DOUT CH6-        |              |                                                                                                                                                    |  |  |  |  |  |

| B32                      | ADC DOUT CH7-        |              |                                                                                                                                                    |  |  |  |  |  |

SNAS476H-MAY 2010-REVISED MAY 2013

| Ball Id.<br>(Row_Column)                                                                                                                                 | Pin Name               | Function     | Description                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A30<br>A29                                                                                                                                               | ADC WCLK+<br>ADC WCLK- | Output       | Word Clock. Differential output frame clock used to indicate the bit boundary of each data sample. Information on timing can be seen in Electrical Characteristics. By programming TX_term (bit 4) in the LVDS Control register, it is possible to internally terminate these outputs with 100 $\Omega$ resistors. |

| A32<br>A31                                                                                                                                               | ADC BCLK+<br>ADC BCLK- | - Output     | Bit clock. Differential output clock used for sampling the serial outputs. Information on timing can be seen in Electrical Characteristics. By programming TX_term (bit 4) in the LVDS Control register, it is possible to internally terminate these outputs with $100\Omega$ resistors.                          |

|                                                                                                                                                          |                        | ADC          | Controls                                                                                                                                                                                                                                                                                                           |

| U25                                                                                                                                                      | ADC RST                | Input        | This pin is an active low reset for the entire ADC, both analog and digital components. The pin must be held low for 500 ns then returned to high in order to ensure that the chip is reset correctly.                                                                                                             |

| V26                                                                                                                                                      | ADC CW/DVGA            |              | 0 = B-mode<br>1 = CW DOPPLER mode, PLL and References are still active to<br>minimize recovery time.                                                                                                                                                                                                               |

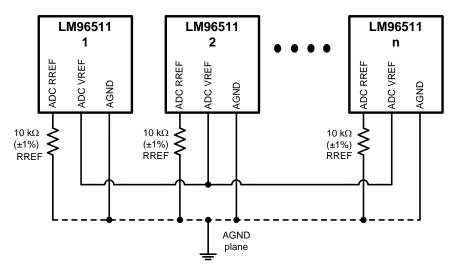

| V22                                                                                                                                                      | ADC VREF               | Input        | ADC Optional External Reference Voltage; Improves channel-to-<br>channel and converter-to-converter matching.                                                                                                                                                                                                      |

| V21                                                                                                                                                      | ADC VREF GND           |              | If Internal Reference is used, connect to AGND.                                                                                                                                                                                                                                                                    |

| U23                                                                                                                                                      | ADC RREF               | Output       | External 10k $\pm$ 1% resistor to ADC Analog GND. Used to set internal bias currents. Required regardless of the type of reference used.                                                                                                                                                                           |

| V23                                                                                                                                                      | ADC LPF BYP            | Bypass       | Capacitor required by the Modulator DAC's LP Filter. Must be at least 100 nF to ADC Analog GND. Can be increased to 10 $\mu$ F to minimize close-in phase noise.                                                                                                                                                   |

|                                                                                                                                                          |                        | SPI™ Comp    | atible Interface                                                                                                                                                                                                                                                                                                   |

| B3                                                                                                                                                       | SPI™ CLK               | Input        | SPI™ clock                                                                                                                                                                                                                                                                                                         |

| B4                                                                                                                                                       | SPI™ DIO               | Input/Output | SPI™ Data Input/Output                                                                                                                                                                                                                                                                                             |

| A5                                                                                                                                                       | ADC SPI™ CS            | lanut        | 0 = ADC SPI <sup>™</sup> Chip Select                                                                                                                                                                                                                                                                               |

| A4                                                                                                                                                       | AMP SPI™ CS            | - Input      | 0 = Amplifier SPI™ Chip Select.                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                          |                        | Power a      | nd Ground                                                                                                                                                                                                                                                                                                          |

| A10, B8, C16, C17,<br>D14, D15, D17, E4,<br>E14, G3, J3, J16,<br>K17, L3, L16, M4, N4,<br>R3, R14, R15, T4,<br>T14, T15, U4, U7, U8,<br>U13, V4, V6, V13 | AMP AVCC A             |              | Amplifier Analog Power<br>Nominally +3.3V.                                                                                                                                                                                                                                                                         |

| B10, B14, B15, C14,<br>E16, E17, H15, G15,<br>M14, M15, P16, R17,<br>T16, U9, U16, V9, B2,<br>C2, E2, F4, G4, H4,<br>J4, K4, L4, N2, P4, T3              | CW AVCC                | Power        | CW DOPPLER Analog Power<br>Nominally +5.0V.                                                                                                                                                                                                                                                                        |

| V5, A7, B7, H16, H17,<br>U14, U15                                                                                                                        | AMP DVDD               |              | DVGA Digital Power. Nominally +3.3V.                                                                                                                                                                                                                                                                               |

| B6, L14                                                                                                                                                  | AMP IO DVDD            |              | Amplifier IO Digital Power. Connect to ADC IO DVDD. Nominally +1.2V.                                                                                                                                                                                                                                               |

| B30, G31, H31, U31                                                                                                                                       | ADC IO DVDD            | 1            | ADC IO Digital Power. Nominally +1.2V.                                                                                                                                                                                                                                                                             |

| A19, C18, F18, J18,<br>M19, R19, U19, U24,<br>U26, U28, V27, V29                                                                                         | ADC AVDD               |              | ADC Analog Power. Nominally +1.2V.                                                                                                                                                                                                                                                                                 |

| A26, B25, B26, U27,<br>V28                                                                                                                               | ADC DVDD               |              | ADC Digital Power. Nominally +1.2V .                                                                                                                                                                                                                                                                               |

# LM96511

Ball Id.

(Row\_Column)

SNAS476H-MAY 2010-REVISED MAY 2013

Pin Name

| A9, A12, A13, A16,<br>A23, A24, A25, B17,<br>B19, B20, B21, B23,<br>B24, B29, B31, C3,<br>C19, C31, D3, D18,<br>D19, F3, F17, F19,<br>F31, G17, G18, G19,<br>H3, J19, J31, K3,<br>K19, K31, L18, L31,<br>M3, M17, M18, M32,<br>N17, N18, P3, P14,<br>P18, P31, R4, R18,<br>R31, T18, T19, U3,<br>U6, U12, U21, U22,<br>U30, V3, V11, V12,<br>V15, V19, V24, V25 | AGND                      |                      | Analog Ground                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|------------------------------------------------------|

| F7, F8, F9, F10, F11,<br>G7, G8, G9, G10,<br>G11, H7, H8, H9,<br>H10, H11, J7, J8, J9,<br>J10, J11, K7, K8, K9,<br>K10, K11, L7, L8, L9,<br>L10, L11, M7, M8,<br>M9, M10, M11, N7,<br>N8, N9, N10, N11                                                                                                                                                          | AMP THRM GND              | Ground               |                                                      |

| F23, F24, F25, F26,<br>F27, G23, G24, G25,<br>G26, G27, H23, H24,<br>H25, H26, H27, J23,<br>J24, J25, J26, J27,<br>K23, K24, K25, K26,<br>K27, L23, L24, L25,<br>L26, L27. M23, M24,<br>M25, M26, M27, N23,<br>N24, N25, N26, N27                                                                                                                               | ADC THRM GND              |                      | Thermal Ground (Connect to AGND)                     |

| A14, A15, B12, B13,<br>F15, F16, N15, N16,<br>U11, V16                                                                                                                                                                                                                                                                                                          | CW DGND                   |                      |                                                      |

| A8, H14, U5, U17                                                                                                                                                                                                                                                                                                                                                | AMP DGND                  |                      | Digital Ground                                       |

| A27, A28, B27, B28,<br>D31, E31, M31, N31,<br>U29, V30                                                                                                                                                                                                                                                                                                          | ADC IO DGND               |                      |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 |                           | No Co                | onnect                                               |

| Important: "NC" pins sh                                                                                                                                                                                                                                                                                                                                         | ould be left unconnected. | Any connection to th | ese pins could affect performance and functionality. |

| A18, A20, A21, B18,<br>C1, E3, E18, E19,<br>G2, H18, H19, J2,<br>K18, L2, L19, N3,<br>N19, P19, R2, U2,<br>U18, U20, V18, V20,<br>R32, T31, V7, C4                                                                                                                                                                                                              | NC                        |                      | Do Not Connect                                       |

# Table 2-1. Pin Descriptions (continued)

Description

Function

www.ti.com

# 3 ELECTRICAL SPECIFICATIONS

# 3.1 Absolute Maximum Ratings <sup>(1)(2)</sup>

| Supply Voltage (CW AVCC)                                                         | -0.3V and +6V    |

|----------------------------------------------------------------------------------|------------------|

| Supply Voltage (AMP AVCC A, AMP DVDD)                                            | -0.3V and +3.63V |

| Supply Voltage (ADC AVDD, ADC DVDD)                                              | -0.3V and +1.44V |

| IO Supply Voltage (AMP IO DVDD, ADC IO DVDD)                                     | -0.3V and +2.0V  |

| Voltage at Analog Inputs                                                         | -0.3V and +2.0V  |

| Voltage at SPI™ Compatible inputs (SPI™ CLK, SPI™ DIO, AMP SPI™ CS, ADC SPI™ CS) | -0.3V and +2.0V  |

| Input Current at any pin other than a Supply Voltage and LNA Inputs              | 25 mA            |

| LNA Inputs                                                                       | 2.6 Vpp & ±10 mA |

(1) Absolute maximum ratings are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the device should be operated at these limits. Operating Ratings indicate conditions for which the device is specified to be functional, but do not specify specific performance limits. Specifications and test conditions are specified in the Electrical Characteristics sections below. Operations of the device beyond the Operating Ratings is not recommended as it may degrade the lifetime of the device. All voltages are measured with respect to GND = AGND = DNGD = 0V, unless otherwise specified.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

# 3.2 Operating Ratings <sup>(1)</sup>

| Operation Temperature Range                                           |                     | 0°C to + 70°C    |

|-----------------------------------------------------------------------|---------------------|------------------|

| Supply Voltage (CW AVCC)                                              |                     | +4.75V to +5.25V |

| Supply Voltage (AMP AVCC A, AMP DVD                                   | D)                  | +3.13V to 3.47V  |

| Supply Voltage (ADC AVDD, ADC DVDD)                                   |                     | +1.14V to +1.26V |

| IO Supply Voltage (AMP IO DVDD, ADC io DVD)                           |                     | +1.14V to +1.89V |

| SPI™ Compatible Inputs (SPI™ CLK, SPI™ DIO, AMP SPI™ CS, ADC SPI™ CS) |                     | +1.14V to +1.89V |

| ADC CLK Input Frequency                                               |                     | 40 MHz           |

| ADC CLK Duty Cycle                                                    |                     | 30 to 70%        |

| DVGA CLK Frequency                                                    |                     | < 100 MHz        |

| Ground Difference  AGND - DGND                                        |                     | 50 mV            |

| ESD Tolerance <sup>(2)</sup> :                                        | Human Body Model    | 1500V            |

|                                                                       | Machine Model       | 100V             |

|                                                                       | Charge Device Model | 750∨             |

(1) Absolute maximum ratings are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the device should be operated at these limits. Operating Ratings indicate conditions for which the device is specified to be functional, but do not specify specific performance limits. Specifications and test conditions are specified in the Electrical Characteristics sections below. Operations of the device beyond the Operating Ratings is not recommended as it may degrade the lifetime of the device. All voltages are measured with respect to GND = AGND = DNGD = 0V, unless otherwise specified.

(2) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

3.3

www.ti.com

SNAS476H-MAY 2010-REVISED MAY 2013

# AFE Electrical Characteristics (B-Mode)

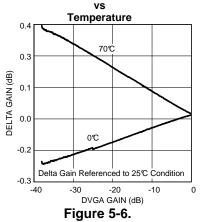

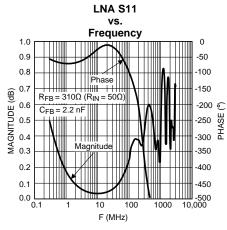

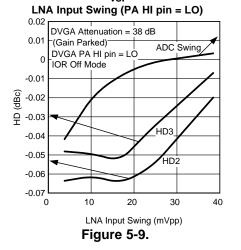

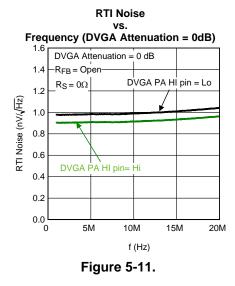

Unless otherwise noted, specified limits apply for AMP AVCC A = **3.3V**, CW AVCC = **5V**, AMP IO DVDD = ADC IO DVDD = **1.2V**, ADC AVDD = ADC DVDD = **1.2V**, Full Scale ADC Output with RF Input at 5 MHz, DVGA PA HI = LO; AMP CW/DVGA pin = ADC CW/DVGA pin = LO,  $F_{CLK}$  = 40 MSPS; Clock duty cycle stabilization enabled; IOR On Mode. All 8 channels powered. **Boldface limits** apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ ; All other limits apply for  $T_A = +25^{\circ}$ C.

| Parameter                                                                | Conditions                                                                                 | Min | Тур                 | Max   | Units            |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|---------------------|-------|------------------|

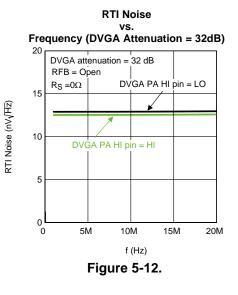

| Total Input (RTI) Voltage Noise                                          | See , No Active Feedback, Input AC shorted to ground                                       |     | 0.9                 |       | nV/√Hz           |

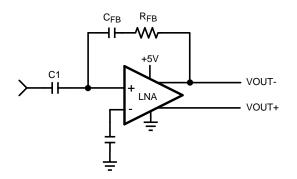

| Noise Figure                                                             | Equivalent 50 $\Omega$ termination using Active Feedback (R <sub>FB</sub> = 301 $\Omega$ ) |     | 3.7                 |       | dB               |

| Single-Ended LNA Input Swing                                             | 1 dB SNR Loss (TGC in Operation). (1) (2)                                                  |     | 380                 |       | mV <sub>PP</sub> |

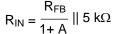

| Externally Programmable Input Resistance<br>Range (overall)              |                                                                                            | 50  |                     | 2k    | Ω                |

| Offset Related Full Scale Amplitude Loss                                 | Max DVGA Gain. 1δ <sup>(3)</sup>                                                           |     | -0.23               |       | - dB             |

| Oliset Related Full Scale Amplitude Loss                                 | Max DVGA Gain, IOR Off Mode. 1 $\delta$ , <sup>(3)</sup>                                   |     | -0.15               |       | uБ               |

| Offset Tempco                                                            |                                                                                            |     | -0.22               |       | LSB/ °C          |

| Overland Recovery                                                        | Max DVGA Gain, Error < ±1%                                                                 |     | 1/f <sub>CLK</sub>  |       | seconds          |

| Overload Recovery                                                        | Max DVGA Gain, Error < ±1%                                                                 |     | 1/f <sub>CLK</sub>  |       | seconds          |

| Ch-Ch Gain Match                                                         | Worst case across DVGA Gain Range                                                          |     | ± 0.06              | ±0.2  | dB               |

| Ch-Ch Phase Match                                                        | Worst case across DVGA Gain Range                                                          |     | ±0.35               | ±0.75 | °C               |

| Ch-Ch Group Delay Match                                                  |                                                                                            |     | ±0.20               | ±0.80 | ns               |

|                                                                          | Min DVGA Gain. <sup>(4)</sup>                                                              |     | -61                 |       |                  |

| Ch-Ch Crosstalk                                                          | Min DVGA Gain. <sup>(4)</sup>                                                              |     | -62                 |       | dBc              |

|                                                                          | Min DVGA Gain. <sup>(4)</sup>                                                              |     | -62                 |       |                  |

| Bandwidth                                                                | -3 dB, Small Signal                                                                        |     | f <sub>CLK</sub> /2 |       | MHz              |

|                                                                          | Mid DVGA gain, -6dB FS, DVGA PA HI<br>pin= LO                                              | 60  | 63                  |       |                  |

| SNR                                                                      | Mid DVGA gain, -1dB FS, DVGA PA HI<br>pin= LO                                              |     | 62                  |       | dBFS             |

| SNR                                                                      | Mid DVGA gain, -6dB FS, DVGA PA HI<br>pin= HI                                              |     | 57                  |       | UDF3             |

|                                                                          | Mid DVGA gain, -1dB FS, DVGA PA HI<br>pin= HI                                              |     | 56                  |       |                  |

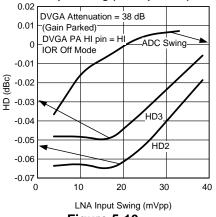

| HD2                                                                      | f <sub>in</sub> = 5 MHz, -6dBFS, Mid DVGA Gain                                             |     | -72                 | -60   | dBFS             |

|                                                                          | $f_{in} = 5 \text{ MHz}, -1 \text{dBFS}, \text{Mid DVGA Gain}$                             |     | -68                 |       | ubr 3            |

| HD3                                                                      | f <sub>in</sub> = 5 MHz, -6dBFS, Mid DVGA Gain                                             |     | -52                 |       | dBFS             |

| HD3                                                                      | f <sub>in</sub> = 5 MHz, -1dBFS, Mid DVGA Gain                                             |     | -43                 |       | UDF 3            |

| DVGA Clock Feedthrough                                                   | DVGA CLK frequency = 7.5MHz                                                                |     | -95                 |       | dBFS             |

| Spurious Noise near $f_{in}$ , $f_{in} \pm (3/8 \text{ x } f_{in})$      | f <sub>in</sub> = 2 to 20 MHz                                                              |     | -84                 |       | dBFS             |

| Spurious Noise near $2f_{in}$ , 2 x $f_{in} \pm (3/4 \text{ x } f_{in})$ |                                                                                            |     | -83                 |       | dBFS             |

| SFDR                                                                     | $f_{in}$ = 5 MHz, -6 dBFS, Mid DVGA Gain                                                   |     | 88                  |       | dBFS             |

|                                                                          | $f_{in}$ = 5 MHz, -1 dBFS, Mid DVGA Gain                                                   |     | 82                  |       |                  |

|                                                                          | Active Mode, IO DVDD = 1.2V                                                                |     | 880                 | 910   |                  |

| Power Consumption                                                        | Active Mode, IO DVDD = 1.8V                                                                |     | 905                 |       | mW               |

|                                                                          | Power Down                                                                                 |     | 50                  |       |                  |

(1) The LNA non-inverting input is always driven single-ended. The inverting input is always AC grounded. See Section 6 for typical connection diagrams in Figure 6-2.

- (2) Please take note of the LNA Input Amplitude Range information described in the Section 6.1

- (3) Maximum expected full scale amplitude loss due to DC offset (minimum DVGA attenuation):

= 20 x log

$$\left(\frac{2^{12} - |Offset (LSB)|}{2^{12}}\right)$$

For Further information, refer to Section 6.4.

(4) One channel with active input and the worst of the other 7 channels measured.

### AFE Electrical Characteristics (B-Mode) (continued)

Unless otherwise noted, specified limits apply for AMP AVCC A = **3.3V**, CW AVCC = **5V**, AMP IO DVDD = ADC IO DVDD = **1.2V**, ADC AVDD = ADC DVDD = **1.2V**, Full Scale ADC Output with RF Input at 5 MHz, DVGA PA HI = LO; AMP CW/DVGA pin = ADC CW/DVGA pin = LO,  $F_{CLK}$  = 40 MSPS; Clock duty cycle stabilization enabled; IOR On Mode. All 8 channels powered. **Boldface limits** apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ ; All other limits apply for  $T_A = +25^{\circ}$ C.

| Parameter            | Conditions                                                                                                         | Min | Тур                              | Max | Units |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|-------|--|

| Power Supply Current | AMP AVCC = 3.3V                                                                                                    |     | 155                              |     | mA    |  |

|                      | AMP DVDD = 3.3V                                                                                                    |     | 1.6                              |     |       |  |

|                      | CW AVCC = 5.0V                                                                                                     |     | 3.2                              |     | -     |  |

| Power Supply Current | ADC AVDD = 1.2V                                                                                                    |     | 147                              |     | mA    |  |

|                      | ADC DVDD = 1.2V                                                                                                    |     | 3.2       147       104       35 |     |       |  |

|                      | IO DVDD = 1.2V                                                                                                     |     | 35                               |     |       |  |

| Wake-up Time         | From Stand-By (From CW DOPPLER to B<br>Mode when AMP CW/DVGA pin is<br>switched from HI to LO). See <sup>(5)</sup> |     | 15                               | 20  | μs    |  |

(5) "Wake up" time defined as the time it takes the output (or its digital representation) to reach within 10% of expected.

www.ti.com

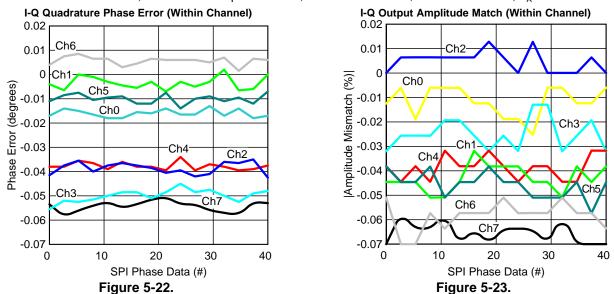

#### 3.4 CW Doppler Electrical Characteristics

Unless otherwise noted, specified limits apply for AMP AVCC A = 3.3V, CW AVCC = 5V, AMP IO DVDD = ADC IO DVDD = 1.2V, ADC AVDD = ADC DVDD = 1.2V; Full Scale ADC Output with RF Input at 5 MHz; CW CLK = 80 MHz (LVPECL levels), AMP CW/DVGA pin = ADC CW/DVGA = HI. Boldface limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ ; All other limits apply for  $T_A = +25^{\circ}$ C.

| Parameter                         | Conditions                                                             | Min  | Тур        | Max  | Units            |

|-----------------------------------|------------------------------------------------------------------------|------|------------|------|------------------|

| Phase Noise                       | $f_{OFFSET}$ = 5kHz with LNA Input = 240 mV_{PP} @ 5 MHz. See $^{(1)}$ |      | -144       |      | dBc/Hz           |

| Dynamic Range (DNR)               | IP1dB referred to RTI Noise                                            |      | -161       |      | dB/Hz            |

| RTI Noise                         |                                                                        |      | 1.2        |      | nV/√Hz           |

| Single-Ended LNA Input Swing      | 1dB Compression (CW Doppler Mode). (IP1dB). ${}^{(2)}$ &               |      | 500        |      | mV <sub>PP</sub> |

| Phase Rotation Resolution         | 16 dynamically selectable angles                                       |      | 22.5       |      | degrees          |

| Phase Temperature Coefficient     | I or Q. See <sup>(4)</sup>                                             |      | ±20        |      | milli°C          |

| Phase Quadrature Accuracy         | I to Q. ±6δ. See <sup>(4) (5)</sup>                                    |      | ± 0.10     |      | °C               |

| Phase Match                       | I to I or Q to Q. See $^{(6)}$ $^{(5)}$                                |      | ±0.35      |      | °C               |

| Amplitude Match                   | I to Q. See <sup>(6)</sup> & <sup>(5)</sup>                            |      | ±0.04      |      | dB               |