SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

- Support for 6-Bit as Well as 8-Bit Video Inputs, With On-Chip Dithering

- FlatLink<sup>™</sup> Input Interface for Low EMI and Power

- mini-LVDS Intra-Panel Interface Towards **Column Drivers**

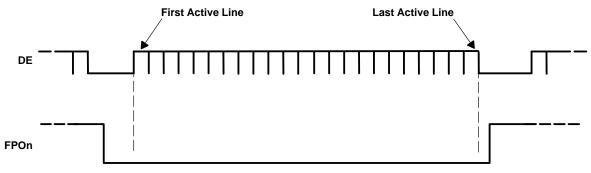

- **DE-Only Mode of Operation**

- **Tolerates Spread Spectrum Clock at the** Input, With SSC Pass-Thru to the Outputs

- Support for SSC at the Outputs by Using **External SSC Generation**

- **Flexible Control Outputs With User-Programmable Timings**

- Support for 2-Level and 3-Level Gate • Drivers

- Optional Serial EEPROM for Fine Tuning **Timing During Development**

- Four Default Timing Sets Provided On-Chip

- Fail-Safe Circuit Detects Off-Spec **Conditions and Generates Timing Signals** Internally

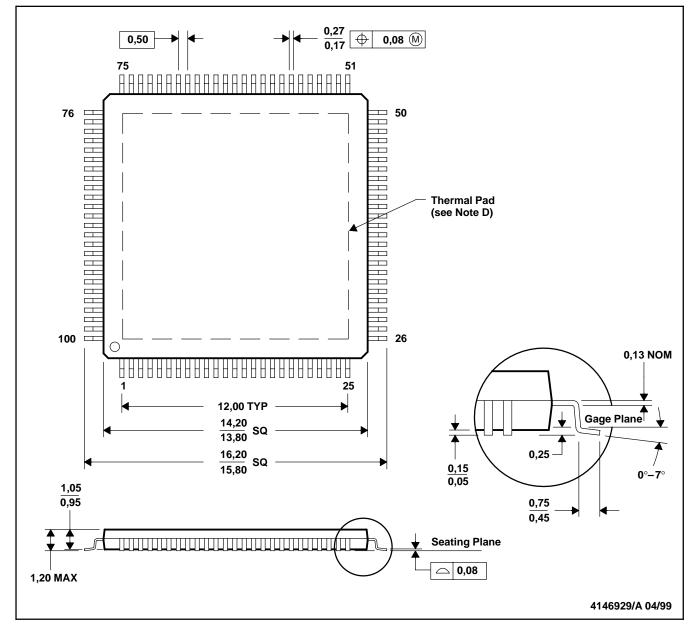

- **PowerPAD<sup>™</sup> TQFP Package**

- Operating Voltage Range: 2.7 V to 3.6 V

#### description

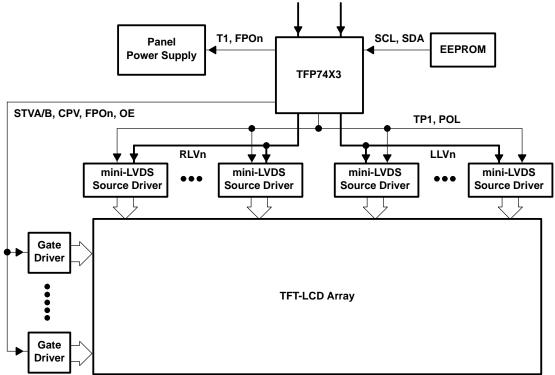

The TFP74X3 is a family of programmable timing controllers for TFT LCD panels supporting resolutions from XGA up to QXGA. The timing controllers reside on the panel and provide the interface between graphics controllers and the TFT-LCD system, routing video data and generating timing signals for the panel.

The host interface is FlatLink, which is a proven, low-power, and low-EMI serial interface. mini-LVDS, an advanced serial intra-panel interface, is used between the TFP74X3 and the column drivers, resulting in improved EMI performance and lower power consumption.

Control outputs with user-programmable timings are available to control source and gate drivers. Additional control outputs are available to sequence the panel power supplies. The TFP74X3 can be configured from an optional external serial EEPROM.

| DEVICE  | RESOLUTIONS SUPPORTED | PACKAGE      |  |  |  |  |  |

|---------|-----------------------|--------------|--|--|--|--|--|

| TFP7423 | XGA                   | 100-pin TQFP |  |  |  |  |  |

| TFP7433 | SXGA, SXGA+           | 100-pin TQFP |  |  |  |  |  |

| TFP7443 | UXGA                  | 100-pin TQFP |  |  |  |  |  |

| TFP7453 | QXGA                  | 100-pin TQFP |  |  |  |  |  |

#### PACKAGE INFORMATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

FlatLink and PowerPAD are trademarks of Texas Instruments

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### TFP7423, TFP7433, TFP7443, TFP7453 TFT LCD PANEL TIMING CONTROLLER WITH mini-LVDS AND FlatLink<sup>TM</sup> SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

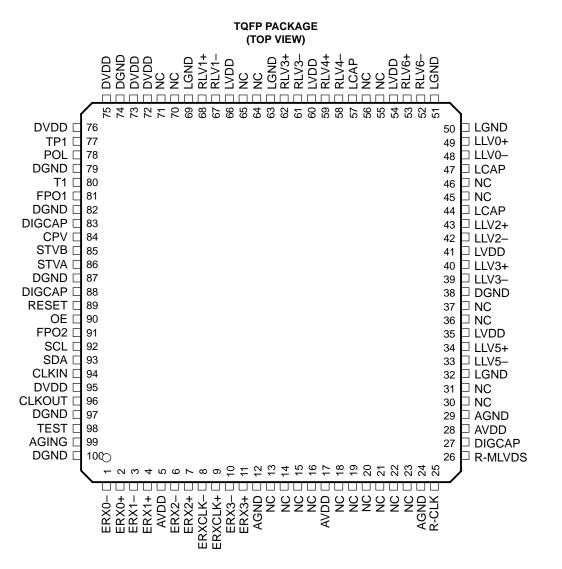

#### pin assignment for TFP7423

#### TFP7423, TFP7433, TFP7443, TFP7453 TFT LCD PANEL TIMING CONTROLLER WITH mini-LVDS AND FlatLink<sup>TM</sup> SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

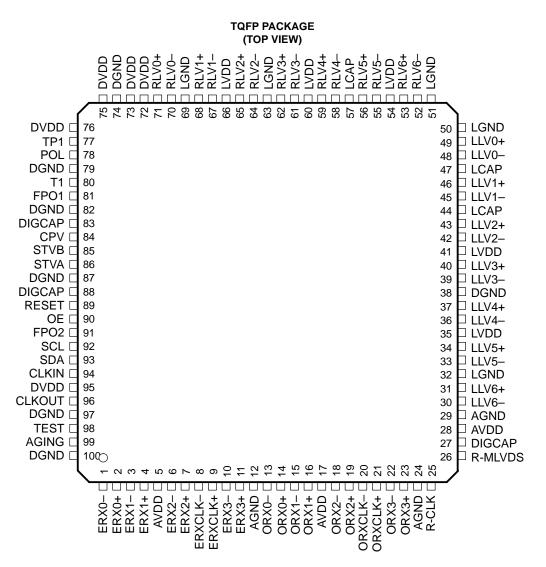

#### pin assignment for TFP7433, TPF7443, and TFP7453

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

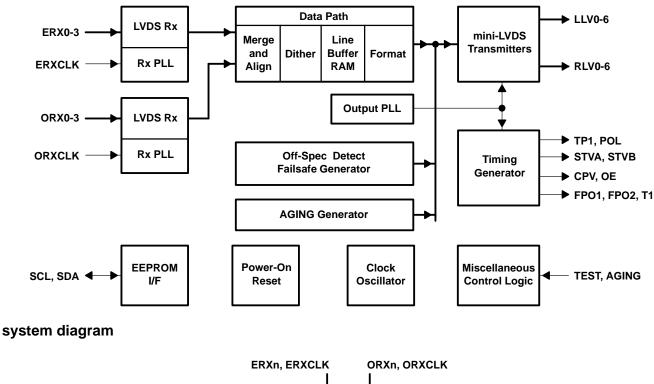

#### block diagram

# TFP7423, TFP7433, TFP7443, TFP7453 TFT LCD PANEL TIMING CONTROLLER WITH mini-LVDS AND FlatLink<sup>TM</sup> SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

## **Terminal Functions**

# FlatLink inputs<sup>†</sup>

|            | TERMINAL                                 |                          |                     |                                                                                                                                              |  |  |  |  |

|------------|------------------------------------------|--------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME       | N                                        | 0.                       | TYPE                | DESCRIPTION                                                                                                                                  |  |  |  |  |

| NAME       | TFP7423 TFP74x3                          |                          |                     |                                                                                                                                              |  |  |  |  |

| ERX0±ERX3± | 1, 2, 3, 4, 6,<br>7, 10, 11<br>7, 10, 11 |                          | Differential inputs | Even pixel FlatLink (LVDS) data inputs. This is the port used in single-port mode. In dual-port mode, the first pixel is input to this port. |  |  |  |  |

| ERXCLK±    | 8, 9                                     | 8,9 8,9                  |                     | Clock pair for even-pixel port                                                                                                               |  |  |  |  |

| ORX0±ORX3± |                                          | 13-16, 18,<br>19, 22, 23 | Differential inputs | Odd pixel FlatLink (LVDS) data inputs. This port is unused in single-port mode.                                                              |  |  |  |  |

| ORXCLK±    |                                          | 21, 20                   | Differential input  | Clock pair for odd-pixel port                                                                                                                |  |  |  |  |

| NC         | 13-16, 18-23                             |                          |                     | Not connected                                                                                                                                |  |  |  |  |

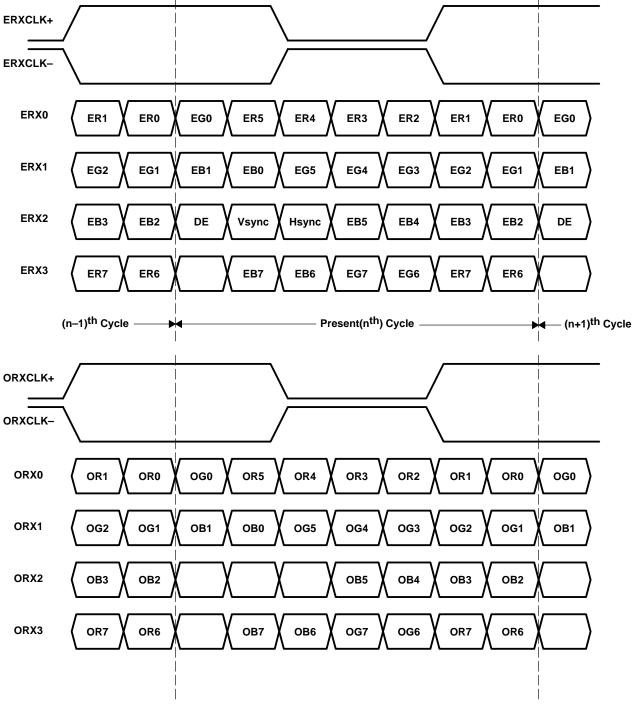

<sup>†</sup> All the FlatLink signals have to be terminated with external resistors. See Figure 1 for the data format on the FlatLink ports.

#### mini-LVDS outputs

|            | TERMINAL                                             |                                                                 |              |                                                                                                                                                                                                                                                      |  |  |  |

|------------|------------------------------------------------------|-----------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|            | N                                                    | 0.                                                              | TYPE         | DESCRIPTION                                                                                                                                                                                                                                          |  |  |  |

| NAME       | TFP7423                                              | TFP74x3                                                         |              |                                                                                                                                                                                                                                                      |  |  |  |

| LLV0±LLV6± | 49, 48, 43, 42,<br>40, 39, 34, 33                    | 49, 48, 46, 45,<br>43, 42, 40, 39,<br>37, 36, 34, 33,<br>31, 30 | Differential | mini-LVDS outputs. mini-LVDS clock pairs are assigned out of these pins depending on the mode/resolution. Drive levels for data pins are set by a resistor on R-MLVDS. Drive levels for clock pins are set proportional to the data pin drive levels |  |  |  |

| RLV0±RLV6± | 68, 67, 62, 61,<br>59, 58, 53, 52                    | 71, 70, 68, 67,<br>65, 64, 62, 61,<br>59, 58, 56, 55,<br>53, 52 | outputs      | by a register. Pre-emphasis levels are programmable by registers.                                                                                                                                                                                    |  |  |  |

| NC         | 30, 31, 36, 37,<br>45, 46, 55, 56,<br>64, 65. 70, 71 |                                                                 |              | Not connected                                                                                                                                                                                                                                        |  |  |  |

#### source driver control signals

| TEI  | RMINAL  |         |           |                                                                                                                  |  |  |  |  |

|------|---------|---------|-----------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|      | NO.     |         | TYPE      | DESCRIPTION                                                                                                      |  |  |  |  |

| NAME | TFP7423 | TFP74x3 |           |                                                                                                                  |  |  |  |  |

| POL  | 78      | 78      | Output    | Polarity control. Output with reference to TIP1. Programmable for dot-inversion or 2-line inversion by register. |  |  |  |  |

| TP1  | 77      | 77      | CMOS 4 mA | Rising edge generated after all the line data is fed out on mini-LVDS pairs. Width programmable by register.     |  |  |  |  |

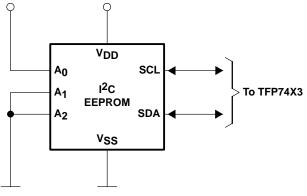

#### **EEPROM** interface

| ті       | ERMINAL |         |                   |                                                                                                                                                                               |  |  |  |

|----------|---------|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | N       | 0.      | TYPE              | DESCRIPTION                                                                                                                                                                   |  |  |  |

| NAME     | TFP7423 | TFP74x3 |                   |                                                                                                                                                                               |  |  |  |

| SCL, SDA | 92, 93  | 92, 93  | Open-drain<br>I/O | $\rm I^2C$ interface pins for connecting to external EEPROM. If an EEPROM is not present, then these pins are used as inputs to select from one of four built-in timing sets. |  |  |  |

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

# **Terminal Functions (Continued)**

#### power pins

|        | TERMINAL                       |                                |      |                                                                                                                                       |  |  |  |  |

|--------|--------------------------------|--------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | N                              | 0.                             | TYPE | DESCRIPTION                                                                                                                           |  |  |  |  |

| NAME   | TFP7423                        | TFP74x3                        |      |                                                                                                                                       |  |  |  |  |

| AGND   | 12, 24, 29                     | 12, 24, 29                     |      | Analog ground                                                                                                                         |  |  |  |  |

| AVDD   | 5, 17, 28                      | 5, 17, 28                      |      | Power supply for the analog circuitry (PLLs).                                                                                         |  |  |  |  |

| DGND   | 38, 74, 79, 82,<br>87, 97, 100 | 38, 74, 79, 82,<br>87, 97, 100 |      | Digital ground                                                                                                                        |  |  |  |  |

| DIGCAP | 27, 83, 88                     | 27, 83, 88                     |      | External capacitor for on-chip 1.8-V regulator for the digital logic. Each DIGCAP pin requires their own capacitor to DGND.           |  |  |  |  |

| DVDD   | 72, 73, 75, 76, 95             | 72, 73, 75, 76, 95             |      | Power supply for the digital circuitry.                                                                                               |  |  |  |  |

| LCAP   | 44, 47, 57                     | 44, 47, 57                     |      | External capacitor for on-chip 1.8-V regulator for the mini-LVDS transmitters.<br>Each LCAP pin requires their own capacitor to LGND. |  |  |  |  |

| LGND   | 32, 50, 51, 63, 69             | 32, 50, 51, 63, 69             |      | Ground connection for the mini-LVDS outputs.                                                                                          |  |  |  |  |

| LVDD   | 35, 41, 54, 60, 66             | 35, 41, 54, 60, 66             |      | Power supply for the mini-LVDS outputs.                                                                                               |  |  |  |  |

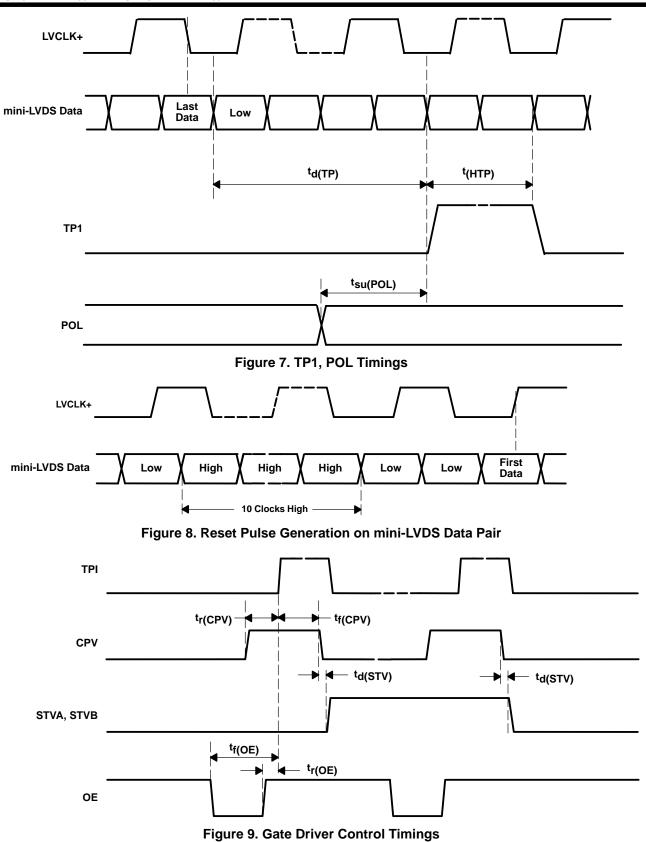

#### gate driver control signals

| ٦    | TERMINAL |         |                     |                                                                                                                                                                         |

|------|----------|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | N        | 0.      | TYPE                | DESCRIPTION                                                                                                                                                             |

| NAME | TFP7423  | TFP74x3 |                     |                                                                                                                                                                         |

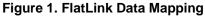

| CPV  | 84       | 84      | Output<br>CMOS 4 mA | Shift clock for gate driver. Rising and falling edges programmable around TP1 rising edge by registers. CPV starting time (after power-on) is programmable by register. |

| FPO1 | 81       | 81      | Output              | Fully programmable general-purpose output. Can be used for OE2, frame pulse, or                                                                                         |

| FPO2 | 91       | 91      | CMOS 4 mA           | dc-dc control. Programmable using registers.                                                                                                                            |

| OE   | 90       | 90      | Output<br>CMOS 4 mA | Output enable for gate driver. Rising and falling edges programmable around TP1 rising edge by registers. Polarity of OE after power on is programmable.                |

| STVA | 86       | 86      | Output              | Gate strobe. Pulse width, duration, and position with respect to the first line is                                                                                      |

| STVB | 85       | 85      | CMOS 4 mA           | programmable using registers.                                                                                                                                           |

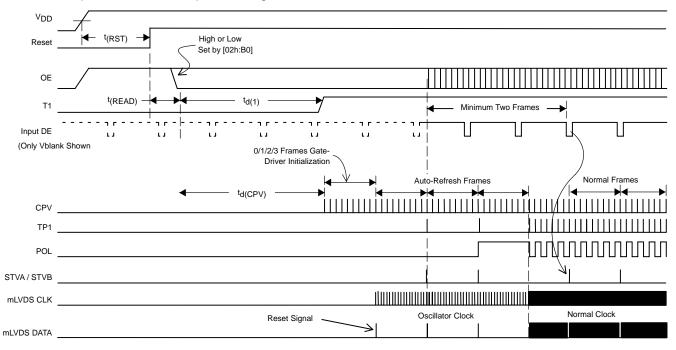

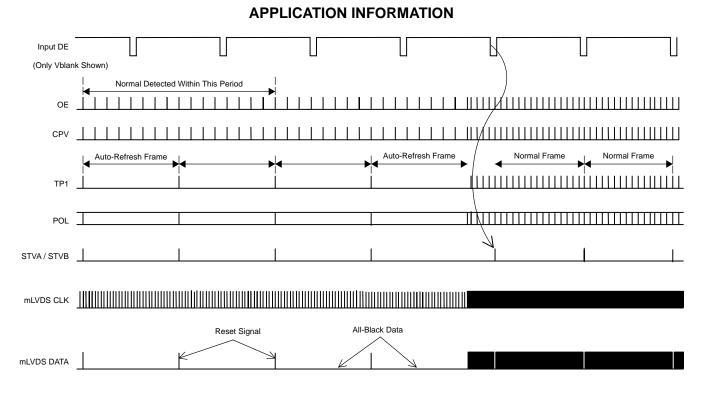

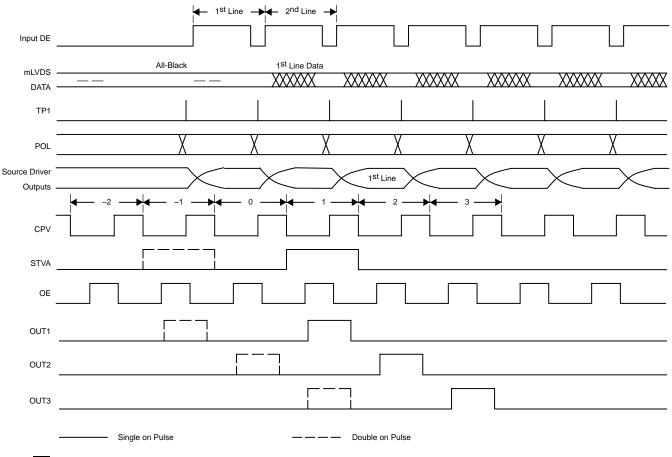

Figure 2 is an example of typical waveforms that can be generated on the gate driver control outputs. For details on programming the timings of these signals, see the *EEPROM register assignment and definition* section.

# TFP7423, TFP7433, TFP7443, TFP7453 TFT LCD PANEL TIMING CONTROLLER WITH mini-LVDS AND FlatLink<sup>TM</sup> SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

# **Terminal Functions (Continued)**

#### miscellaneous

| Т        | ERMINAL         |      |                          |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------|-----------------|------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME NO. |                 | TYPE | DESCRIPTION              |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| NAME     | TFP7423 TFP74x3 |      |                          |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

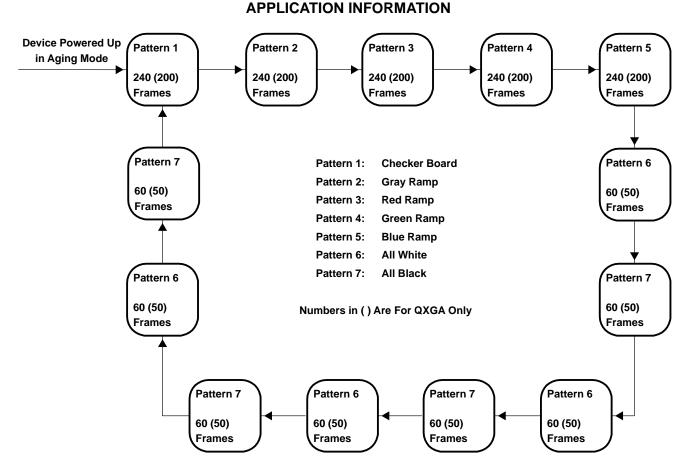

| AGING    | 99              | 99   | Input                    | In AGING mode, built-in video patterns are fed out on the mini-LVDS outputs.<br>L = Auto-graying patterns are output<br>H = Normal operation<br>Internally pulled up<br>AGING mode requires external clock to be fed in at the FlatLink ports.<br>Note: The status of AGING is sensed only at power on. |  |  |  |  |

| CLKIN    | 94              | 94   | Input                    | Dot-clock fed in after spreading.<br>If external SSC is not being done, then CLKOUT can be connected to CLKIN<br>internally by register programming. In that case, CLKOUT buffer is powered<br>down.                                                                                                    |  |  |  |  |

| CLKOUT   | 96              | 96   | Output<br>CMOS 8 mA      | Recovered dot-clock brought out, to feed to external SSC chip.                                                                                                                                                                                                                                          |  |  |  |  |

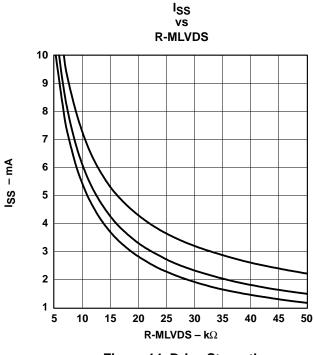

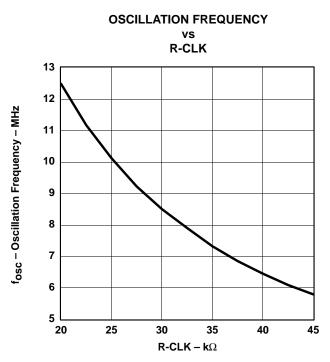

| R-CLK    | 25              | 25   | Analog output            | External resistor to GND sets internal clock oscillator frequency.<br>The frequency can be set between 6 MHz and 12 MHz.                                                                                                                                                                                |  |  |  |  |

| R-MLVDS  | 26              | 26   | Analog output            | External resistor to GND sets drive level (steady state) on mini-LVDS data pairs. The drive level can be set up to 8 mA.                                                                                                                                                                                |  |  |  |  |

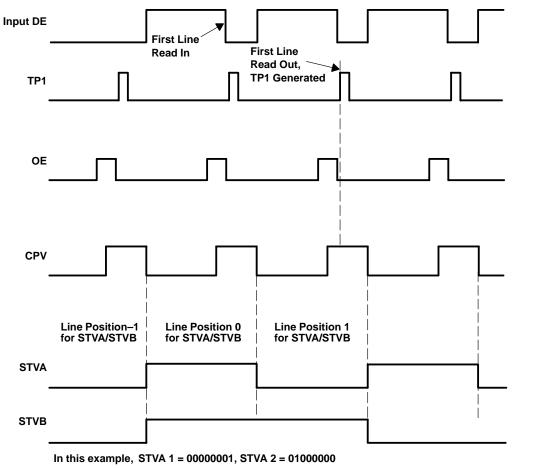

| RESET    | 89              | 89   | Schmitt trigger<br>input | Used for power-on reset with external resistor and capacitor.                                                                                                                                                                                                                                           |  |  |  |  |

| TEST     | 98              | 98   | Input                    | Controls whether the TFP74X3 is in normal operation mode. H = test mode, L = normal operation.                                                                                                                                                                                                          |  |  |  |  |

| T1       | 80              | 80   | Output<br>CMOS 4 mA      | Can be used to control panel dc-dc converter. Starting time after power on is programmable with register.                                                                                                                                                                                               |  |  |  |  |

#### detailed description

#### LVDS receiver

The FlatLink receiver has two input ports. ERX0– through ERX3– and ERX0+ through ERX3+ are for the even (0, 2, 4...) pixels, ORX0– through ORX3– and ORX0+ through ORX3+ are for the odd (1, 3, 5...) pixels. In the single input port mode, ERX0– through ERX3– and ERX0+ through ERX3+ must be used. Both 18-bit color and 24-bit color are supported.

The FlatLink inputs are SSC tolerant and input SSC is passed on to the outputs to enable a low-EMI total solution.

#### NOTE:

The TFP7423 has only one input port.

#### data path

In the data path, video data from the two input ports are aligned and merged to form a single data stream. On-chip dithering is available to convert 24-bit color to 18-bit color. The dithering can be turned on or off by the user through the use of suitable register programming. The formatting section adds control bits to the mini-LVDS data stream and distributes data to different mini-LVDS outputs depending on resolution and mounting options. For normally-black panels, the video data can be inverted by register programming.

#### mini-LVDS transmitter

There are 14 pairs of mini-LVDS outputs, arranged as seven pairs for the left half-bus (LLV0– through LLV6– and LLV0+ through LLV6+) and seven pairs for the right half-bus (RLV0– through RLV6– and RLV0+ through RLV6+). Data and clock pairs are assigned out of these pins depending on the mode/resolution. Drive levels for data pairs are set by a resistor on R-MLVDS. The drive levels on the clock pairs can be set proportional to the data-pair drive levels by register programming. Pre-emphasis with register-programmable levels may be used on the mini-LVDS signals.

#### timing generator

The timing generator produces signals for controlling the gate drivers, source drivers, and the panel power supply. The timing signals can be programmed by configuring the internal registers from an external EEPROM. Two versatile general-purpose outputs, FPO1 and FPO2, are also available.

#### fail-safe circuit and clock oscillator

The TFP74X3 detects if the input signal is out of specification. In such a case, the fail-safe circuit generates timing signals and feeds black data to the panel. This prevents any damage to the panel. The fail-safe circuit works off an internal clock. The frequency of the internal oscillator is set by a single external resistor.

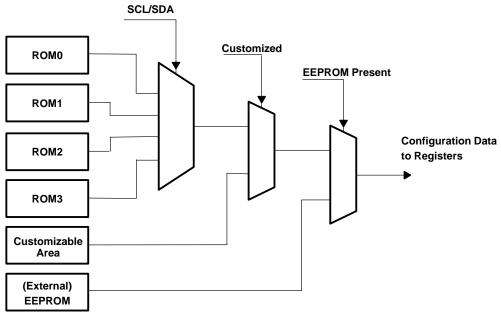

#### **EEPROM** interface

This block controls the reading of an external I<sup>2</sup>C EEPROM. If an EEPROM is not connected, the TFP74X3 configures itself from one of four internal ROMs, depending on how the SCL and SDA pins are connected (pulled high/pulled low). In case an external EEPROM is connected, but the read operation is not successful, the TFP74X3 remains in the reset condition.

#### miscellaneous control logic

This block configures the internal registers from the EEPROM (if present) and sets up the internal control depending on the contents of the EEPROM, the status of SCL, SDA, TEST, and AGING.

#### power-on reset

A laser-trimmed band-gap voltage sets accurate thresholds for the power-on reset. An external resistor and capacitor set the reset duration. Internal circuitry in this block also detects glitches in the power supply and initiates a reset sequence if a glitch in the power supply reduces voltage below safe levels, preventing damage to the panel.

SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

STVB 1 = 00000001, STVB 2 = 10000000

Figure 2. Timing of Normal Operation

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage | DVDD, AVDD, LVDD                    | –0.5 V to 4 V         |

|----------------|-------------------------------------|-----------------------|

| Input voltage: | FlatLink pins                       | –0.5 V to 2.6 V       |

|                | mini-LVDS outputs                   | –0.1 V to 2.6 V       |

|                | DIGCAP                              | 1.8 V to 2.6 V        |

|                |                                     | –0.5 V to VDD + 0.5 V |

| Storage tempe  | erature range, T <sub>stg</sub>     | 65°C to 150°C<br>     |

| Lead temperat  | ure 1,5 mm from case for 10 seconds |                       |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to the GND terminals unless otherwise noted.

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

#### recommended operating conditions

|                                                                                     |                     | MIN                     | TYP | MAX                   | UNIT             |

|-------------------------------------------------------------------------------------|---------------------|-------------------------|-----|-----------------------|------------------|

| Supply voltage, V <sub>DD</sub>                                                     | DVDD, AVDD, LVDD    | 2.7                     | 3.3 | 3.6                   | V                |

| High-level input voltage, VIH                                                       | Digital inputs, SDA | 0.7V <sub>DD</sub>      |     |                       | V                |

| Low-level input voltage, VIL                                                        | Digital inputs, SDA |                         |     | 0.3V <sub>DD</sub>    | V                |

| Differential input voltage,  VID                                                    | FlatLink inputs     | 50                      |     | 600                   | mV               |

| Common-mode input voltage, VIC                                                      | FlatLink inputs     | <u>0.6 +  VID </u><br>2 | 1.2 | <u>2 –  VID </u><br>2 | V                |

| mini-LVDS drive level (steady state), ISS                                           | LLV0-7, RLV0-7      |                         |     | 8                     | mA               |

| Internal clock frequency, fOSC                                                      |                     | 6                       | 10  | 12                    | MHz              |

| Input clock frequency, f <sub>(Clk)</sub>                                           | ERXCLK, ORXCLK      | 40                      |     | 112                   | MHz              |

| Modulating frequency of input clock during SSC, fMOD                                | ERXCLK, ORXCLK      |                         |     | 200                   | kHz              |

| Maximum deviation of input clock frequency during SSC, $f_{\mbox{\scriptsize DEV}}$ | ERXCLK, ORXCLK      |                         |     | ±2%                   |                  |

| Reset duration, t(RST)                                                              |                     |                         | 10  |                       | ms               |

| TP1 width, T <sub>H</sub> TP                                                        |                     | 1                       |     |                       | <sup>t</sup> (R) |

| Pullup resistors, RP                                                                | SCL, SDA            |                         | 4.7 |                       | kΩ               |

| Ambient temperature, T <sub>A</sub>                                                 |                     | 0                       |     | 70                    | °C               |

NOTE: For values of t(R) and t(M), see the mini-LVDS outputs and the gate and source driver control outputs sections.

#### electrical characteristics over recommended operating conditions (unless otherwise specified)

#### TP1, POL, CPV, OE, FPO1, FPO2, STVA, STVB, T1, SCL

|     | PARAMETER                 | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----|---------------------------|------------------------|-----|-----|-----|------|

| VOH | High-level output voltage | I <sub>OH</sub> = 4 mA | 2.3 |     |     | V    |

| VOL | Low-level output voltage  | I <sub>OL</sub> = 4 mA |     |     | 0.4 | V    |

#### CLKOUT

|     | PARAMETER                 | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----|---------------------------|------------------------|-----|-----|-----|------|

| VOH | High-level output voltage | IOH = 8 mA             | 2.3 |     |     | V    |

| VOL | Low-level output voltage  | I <sub>OL</sub> = 8 mA |     |     | 0.4 | V    |

#### CLKIN, TEST

|     | PARAMETER     | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|-----|---------------|-----------------------------------|-----|-----|-----|------|

| IIN | Input current | $V_{IN} = 0 V \text{ to } V_{DD}$ |     |     | 10  | μA   |

#### AGING

|                 | PARAMETER     | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|-----------------|---------------|-----------------------|-----|-----|-----|------|

| ۱ <sub>IL</sub> | Input current | V <sub>IL</sub> = 0 V |     |     | 800 | μΑ   |

#### **RESET (see Figure 3)**

|                   | PARAMETER               | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|-------------------|-------------------------|-----------------------------------|-----|-----|-----|------|

| IIN               | Input current           | $V_{IN} = 0 V \text{ to } V_{DD}$ |     |     | 1   | μA   |

| V <sub>(TH)</sub> | Reset threshold voltage |                                   | 2.3 | 2.4 | 2.5 | V    |

| V <sub>hys</sub>  | Hysteresis voltage      |                                   |     | 50  |     | mV   |

SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

#### electrical characteristics over recommended operating conditions (unless otherwise specified) (continued)

Figure 3. Power-On Reset and Glitch Detect

#### FlatLink ports

|           | PARAMETER                              | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|-----------|----------------------------------------|-------------------------|-----|-----|-----|------|

| VIT+      | Positive-going input threshold voltage | V <sub>IC</sub> = 1.2 V |     |     | 50  | mV   |

| $V_{IT-}$ | Negative-going input threshold voltage | V <sub>IC</sub> = 1.2 V | -50 |     |     | mV   |

| IIN       | Input current                          |                         |     |     | 10  | μA   |

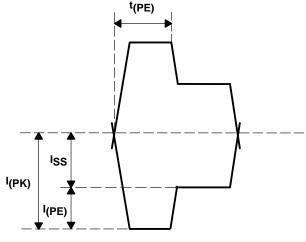

#### mini-LVDS outputs (see Figure 4)

|                     | PARAMETER                        | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|----------------------------------|-----------------|-----|-----|-----|------|

| VOCM                | Common-mode output voltage       |                 | 1.1 | 1.2 | 1.3 | V    |

| ISS                 | Drive level (steady state)       |                 |     |     | 8   | mA   |

| l(PK)               | Peak drive level                 |                 | 1   |     | 1.6 | ISS  |

| R <sub>(TERM)</sub> | mini-LVDS termination resistance |                 | 50  |     | 150 | Ω    |

NOTE:  $I(PK) \times R(TERM)$  should not exceed 800 mV

Figure 4. mini-LVDS Outputs

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

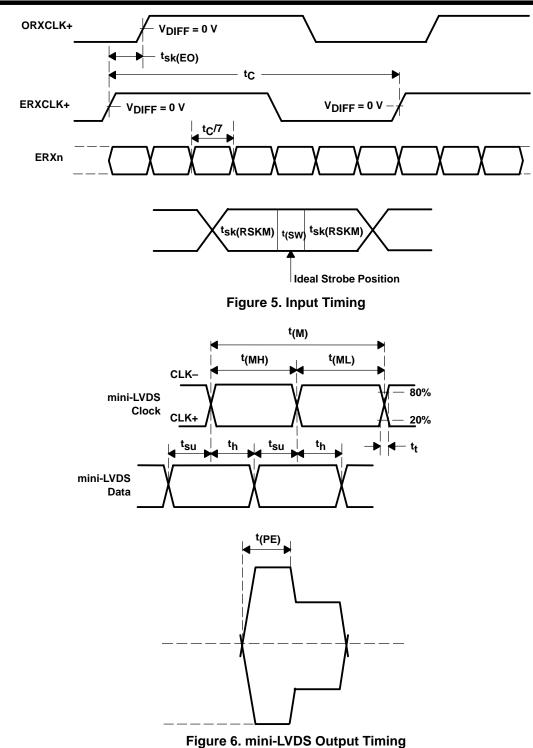

# ac electrical characteristics over recommended operating conditions (unless otherwise specified) FlatLink inputs (see Figure 5)

|                       | PARAMETER               | TEST CONDITIONS             | MIN  | TYP | MAX | UNIT |

|-----------------------|-------------------------|-----------------------------|------|-----|-----|------|

| <sup>t</sup> (SW)     | Sampling window         |                             |      |     | 650 | ps   |

| <sup>t</sup> sk(RSKM) | Receiver skew margin    | f <sub>(CLK)</sub> = 82 MHz | 540  |     |     | ps   |

| <sup>t</sup> sk(EO)   | Skew - even to odd port |                             | -3/7 |     | 3/7 | tC   |

#### mini-LVDS outputs (see Figure 6)

|                   | PARAMETER             | TEST CONDITIONS | MIN TYP            | MAX | UNIT |

|-------------------|-----------------------|-----------------|--------------------|-----|------|

| <sup>t</sup> (MH) | Clock high time       |                 | t(M)/2             |     |      |

| <sup>t</sup> (ML) | Clock low time        |                 | t(M)/2             |     |      |

| t <sub>su</sub>   | Data setup time       |                 | <sup>t</sup> (M)/4 |     |      |

| t <sub>h</sub>    | Data hold time        |                 | <sup>t</sup> (M)/4 |     |      |

| <sup>t</sup> (PE) | pre-emphasis duration |                 | t(M)/4             |     |      |

| tt                | Transition time       |                 |                    | 500 | ps   |

#### source driver control outputs (TP1, POL) (see Figure 7)

|                       | PARAMETER                        | TEST CONDITIONS | MIN | TYP  | MAX | UNIT             |

|-----------------------|----------------------------------|-----------------|-----|------|-----|------------------|

| <sup>t</sup> d(TP)    | Last mini-LVDS data to TP1 delay |                 |     | 11.5 |     | <sup>t</sup> (M) |

| <sup>t</sup> (HTP)    | TP1 high time                    |                 | 1   |      | 63  | <sup>t</sup> (R) |

| t <sub>su</sub> (POL) | POL setup time to TP1            |                 |     | 1    |     | <sup>t</sup> (M) |

#### gate driver control outputs (CPV, STVA, STVB, OE) (see Figure 9)

|                     | PARAMETER           | TEST CONDITIONS | MIN  | TYP | MAX | UNIT             |

|---------------------|---------------------|-----------------|------|-----|-----|------------------|

| <sup>t</sup> r(CPV) | TP1 to CPV rising   |                 | -127 |     | 127 | <sup>t</sup> (R) |

| tf(CPV)             | TP1 to CPV falling  |                 | -127 |     | 127 | <sup>t</sup> (R) |

| <sup>t</sup> r(OE)  | TP1 to OE rising    |                 | -127 |     | 127 | <sup>t</sup> (R) |

| tf(OE)              | TP1 to OE falling   |                 | -127 |     | 127 | <sup>t</sup> (R) |

| <sup>t</sup> d(STV) | CPV to STVA/B delay |                 |      | 0   |     |                  |

#### T1, CPV, OE at power-on (see Figure 10)

|                     | PARAMETER                 | TEST CONDITIONS           | MIN | TYP    | MAX | UNIT |

|---------------------|---------------------------|---------------------------|-----|--------|-----|------|

| <sup>t</sup> (RST)  | Reset duration            |                           |     | 0.55RC |     |      |

| <sup>t</sup> (READ) | EEPROM read duration      | f <sub>OSC</sub> = 10 MHz | 5.2 |        |     | ms   |

| <sup>t</sup> d(T1)  | T1 activation delay time  | f <sub>OSC</sub> = 10 MHz | 0   |        | 155 | ms   |

| <sup>t</sup> d(CPV) | CPV activation delay time | f <sub>OSC</sub> = 10 MHz | 0   |        | 155 | ms   |

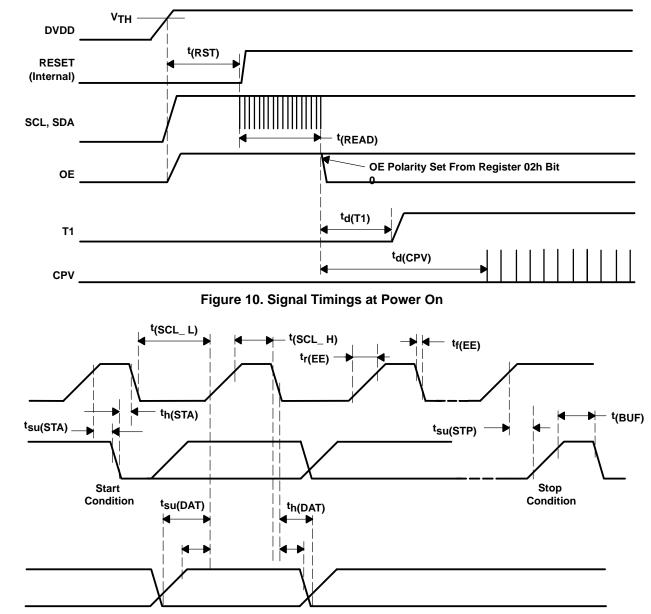

#### **EEPROM** interface (see Figure 11)

|                       | PARAMETER                  | TEST CONDITIONS                              | MIN | TYP  | MAX  | UNIT |

|-----------------------|----------------------------|----------------------------------------------|-----|------|------|------|

| f(SCL)                | SCL clock frequency        |                                              |     | 46.5 |      | kHz  |

| <sup>t</sup> (SCL_H)  | Clock high time            |                                              | 4.0 |      |      | μs   |

| t(SCL_L)              | Clock low time             |                                              | 4.7 |      |      | μs   |

| t <sub>r(EE)</sub>    | SCL, SDA rise time         |                                              |     |      | 1000 | ns   |

| <sup>t</sup> f(EE)    | SCL, SDA fall time         |                                              |     |      | 300  | ns   |

| t <sub>su(STA)</sub>  | Start condition setup time | $f_{OSC}$ = 7.5 MHz, Rp = 4.7 kΩ, CL = 50 pF | 4.7 |      |      | μs   |

| <sup>t</sup> h(STA)   | Start condition hold time  |                                              | 4.0 |      |      | μs   |

| t <sub>su</sub> (STP) | Stop condition setup time  |                                              | 4.0 |      |      | μs   |

| <sup>t</sup> su(DAT)  | Data setup time            |                                              | 250 |      |      | ns   |

| <sup>t</sup> h(DAT)   | Data hold time             |                                              | 300 |      |      | ns   |

| <sup>t</sup> (BUF)    | Bus free time              |                                              | 4.7 |      |      | μs   |

# TFP7423, TFP7433, TFP7443, TFP7453 TFT LCD PANEL TIMING CONTROLLER WITH mini-LVDS AND FlatLink<sup>TM</sup> SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

#### **EEPROM** interface (continued)

|                      | PARAMETER                  | TEST CONDITIONS                                                            | MIN | TYP | MAX  | UNIT |

|----------------------|----------------------------|----------------------------------------------------------------------------|-----|-----|------|------|

| f(SCL)               | SCL clock frequency        |                                                                            |     | 62  |      | kHz  |

| t(SCL_H)             | Clock high time            |                                                                            | 4.0 |     |      | μs   |

| t(SCL_L)             | Clock low time             |                                                                            | 4.7 |     |      | μs   |

| <sup>t</sup> r(EE)   | SCL, SDA rise time         |                                                                            |     |     | 1000 | ns   |

| <sup>t</sup> f(EE)   | SCL, SDA fall time         |                                                                            |     |     | 300  | ns   |

| <sup>t</sup> su(STA) | Start condition setup time | $f_{osc} = 10 \text{ MHz}, R_P = 4.7 \text{ k}\Omega, C_L = 50 \text{ pF}$ | 3.5 |     |      | μs   |

| <sup>t</sup> h(STA)  | Start condition hold time  |                                                                            | 3.7 |     |      | μs   |

| <sup>t</sup> su(STP) | Stop condition setup time  |                                                                            | 4.0 |     |      | μs   |

| <sup>t</sup> su(DAT) | Data setup time            |                                                                            | 250 |     |      | ns   |

| <sup>t</sup> h(DAT)  | Data hold time             |                                                                            | 300 |     |      | ns   |

| <sup>t</sup> (BUF)   | Bus free time              |                                                                            | 4.7 |     |      | μs   |

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

Figure 11. EEPROM Interface Timings

#### off-spec conditions

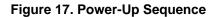

During normal display operation, the fail-safe circuitry in the TFP74X3 constantly checks for a valid input signal as well as input clock. If either the clock fails or if the signal becomes abnormal, the TFP74X3 enters auto-refresh mode and generates control signals for the source and gate drivers, at the same time feeding all black data on the mini-LVDS data pairs.

Any input signal not complying with the conditions listed in Table 1 and Table 2 forces the TFP74X3 into the auto-refresh mode.

|          | TOTAL NUMBER OF<br>CLOCKS/LINE |      | TOTAL NUMBER OF<br>LINES/FRAME |      | TOTAL NUMBER OF<br>LINES/VBLANK |     |

|----------|--------------------------------|------|--------------------------------|------|---------------------------------|-----|

|          | MIN                            | MAX  | MIN                            | MAX  | MIN                             | MAX |

| XGA      | 1088                           | 2048 | 512                            | 1536 | 4                               |     |

| SXGA     | 1344                           | 2048 | 512                            | 1536 | 4                               |     |

| SXGA+    | 1464                           | 4096 | 1024                           | 2046 | 4                               |     |

| UXGA     | 1664                           | 4096 | 1024                           | 2046 | 4                               |     |

| UXGA-FPT | 1664                           | 4096 | 1024                           | 2046 | 4                               |     |

| QXGA     | 2128                           | 4096 | 1024                           | 2046 | 6                               |     |

#### Table 1. Specifications of Valid Input Signal in DE-Only Mode

|          | TOTAL CLOC | TOTAL CLOCKS/LINE |      | TOTAL Hs/FRAME |     | s/VB-bp | TOTAL Hs in VB |     |

|----------|------------|-------------------|------|----------------|-----|---------|----------------|-----|

|          | MIN        | MAX               | MIN  | MAX            | MIN | MAX     | MIN            | MAX |

| XGA      | 1088       | 2048              | 512  | 1536           | 4   | 126     |                |     |

| SXGA     | 1344       | 2048              | 512  | 1536           | 4   | 126     |                |     |

| SXGA+    | 1464       | 4096              | 1024 | 2046           | 4   | 126     |                |     |

| UXGA     | 1664       | 4096              | 1024 | 2046           | 5   | 126     |                |     |

| UXGA-FPT | 1664       | 4096              | 1024 | 2046           |     |         | 4              | 126 |

1024

2046

126

6

2128

QXGA

4096

#### Table 2. Specifications of Valid Input Signal in H-Sync, V-Sync Mode

# **EEPROM** register assignment and definition

| ADDRESS (Hex) | NAME                     | FUNCTION                                            |

|---------------|--------------------------|-----------------------------------------------------|

| 00            | Auto detect              | If 10101010, EEPROM present. Else default mode      |

| 01            | Format control 1         | Sets resolutions, modes, etc.                       |

| 02            | Format control 2         | Sets 6/8-bit mode, dithering, OE polarity, etc.     |

| 03            | Drive levels             | Sets pre-emphasis and mini-LVDS clock drive levels  |

| 04            | T1 timing                | Defines timing on T1 pin                            |

| 05            | CPV start                | CPV start timer value                               |

| 06            | TP1 width                | Programs TP1 width                                  |

| 07            | CPV rising edge          | Sets CPV timing with respect to TP1                 |

| 08            | CPV falling edge         | Sets CPV timing with respect to TP1                 |

| 09            | OE timing 1              | Sets OE timing with respect to TP1                  |

| 0A            | OE timing 2              | Sets OE timing with respect to TP1                  |

| 0B            | STVA control 1           | Sets STVA width and position in terms of line count |

| 0C            | STVA control 2           | Sets STVA width and position in terms of line count |

| 0D            | STVB control 1           | Sets STVB width and position in terms of line count |

| 0E            | STVB control 2           | Sets STVB width and position in terms of line count |

| 0F            | Off-spec checks          | Enables/disables various off-spec checks            |

| 10            | FPO1 control             | Sets FPO1 mode                                      |

| 11            | FPO1 start               | Sets FPO1 first transition                          |

| 12            | FPO1 stop                | Sets FPO1 second transition                         |

| 13            | FPO2 control             | Sets FPO2 mode                                      |

| 14            | FPO2 start               | Sets FPO2 first transition                          |

| 15            | FPO2 stop                | Sets FPO2 second transition                         |

| 16            | Auto-refresh TP1         | Sets TP1 width during auto-refresh                  |

| 17            | Auto-refresh CPV low     | Sets duration of CPV low during auto-refresh        |

| 18            | Auto-refresh CPV high    | Sets duration of CPV high during auto-refresh       |

| 19            | Auto-refresh OE timing 1 | Sets OE timing with respect to CPV in auto-refresh  |

| 1A            | Auto-refresh OE timing 2 | Sets OE timing with respect to CPV in auto-refresh  |

| 1B            | Reserved                 |                                                     |

| 1C            | Reserved                 |                                                     |

| 1D            | Reserved                 |                                                     |

| 1E            | Reserved                 |                                                     |

| 1F            | Check-sum                | Check-sum of EEPROM contents from 00h to 1Eh        |

# Table 3. EEPROM Register Assignment and Definition

# TFP7423, TFP7433, TFP7443, TFP7453 TFT LCD PANEL TIMING CONTROLLER WITH mini-LVDS AND FlatLink<sup>TM</sup> SLDS140B – APRIL 2001 – REVISED SEPTEMBER 2002

#### **Table 4. Format Control 1**

| [2–0]                   | 000 = XGA<br>001 = SXGA<br>010 = SXGA+<br>011 = UXGA<br>100 = UXGA FPT<br>110 = QXGA |                                                                         |          |         |  |

|-------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------|---------|--|

| [3]                     | 0 = single input port, 1 =                                                           | 0 = single input port, 1 = dual input ports                             |          |         |  |

| [4]                     | Should be 0                                                                          | Should be 0                                                             |          |         |  |

| [5]                     | Video signal inversion.<br>0 = signal not inverted, 1                                | Video signal inversion.<br>0 = signal not inverted, 1 = signal inverted |          |         |  |

| [6]                     | 2-line POL control. 0 = D                                                            | 2-line POL control. 0 = Dot inversion, 1 = 2-line inversion             |          |         |  |

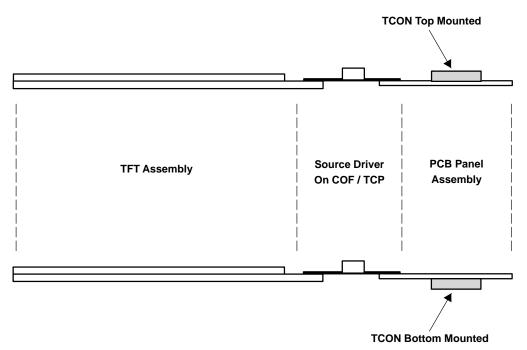

| [7]                     | TCON position. 0 = top r                                                             | TCON position. 0 = top mount, 1 = bottom mount (see Figure 23)          |          |         |  |

| Built-in Default Values | ROM0                                                                                 |                                                                         |          |         |  |

|                         | 10101110                                                                             | 10001010                                                                | 10001011 | 1000000 |  |

#### Table 5. Format Control 2

| [0]                     | OE polarity after EEPRC                                                                                                                                              | OE polarity after EEPROM read                                                                                                                                                                                                                    |         |          |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|--|

| [2–1]                   | Gate driver initialization at power on<br>00 = 0 frame initialization<br>01 = 1 frame initialization<br>10 = 2 frames initialization<br>11 = 3 frames initialization |                                                                                                                                                                                                                                                  |         |          |  |

| [3]                     | 0 = H-sync is used to ge                                                                                                                                             | Determines the method of the timing signal generation in Vblank<br>0 = H-sync is used to generate signals (should be used if the input has a spread spectrum)<br>1 = Signals are generated internally, using the stored value of the line length |         |          |  |

| [4]                     | 0 = 6-bit input, 1 = 8-bit i                                                                                                                                         | 0 = 6-bit input, 1 = 8-bit input                                                                                                                                                                                                                 |         |          |  |

| [5]                     | 0 = 6-bit output, $1 = 8$ -bit                                                                                                                                       | 0 = 6-bit output, 1 = 8-bit output                                                                                                                                                                                                               |         |          |  |

| [6]                     |                                                                                                                                                                      | 0 = Disable dithering, 1 = enable dithering<br>If dithering is disabled and input is 8 bits and output is 6 bits, then truncate.                                                                                                                 |         |          |  |

| [7]                     | 0 = Short CLKIN to CLKOUT, 1 = CLKIN and CLKOUT not connected                                                                                                        |                                                                                                                                                                                                                                                  |         |          |  |

| Built-in Default Values | ROM0                                                                                                                                                                 | ROM1                                                                                                                                                                                                                                             | ROM2    | ROM3     |  |

|                         | 00000001                                                                                                                                                             | 0000001                                                                                                                                                                                                                                          | 0000001 | 00000011 |  |

#### Table 6. Drive Levels

| [2–0] | Sets clock drive levels in terms of data drive levels.<br>From 1x to 4x in steps of 0.5x<br>000Clock drive level = 1 times data drive level<br>001Clock drive level = 1.5 times data drive level<br><br>110Clock drive level = 4 times data drive level<br>111Reserved |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]   | Determines the minimum operating frequency of the input PLL.<br>0 = Minimum frequency is 4 x f <sub>OSC</sub><br>1 = Minimum frequency is 2.8 x f <sub>OSC</sub><br>(Recommended value = 1)                                                                            |

| [5-4] | Sets data pre-emphasis drive levels in terms of data steady-state level.<br>00No pre-emphasis<br>0120% pre-emphasis<br>1040% pre-emphasis<br>1160% pre-emphasis                                                                                                        |

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

#### Table 6. Drive Levels (Continued)

| [7–6]                   | 00No pre-emphasis<br>0120% pre-emphasis<br>1040% pre-emphasis | Sets clock pre-emphasis drive levels in terms of clock steady-state level.<br>00No pre-emphasis<br>0120% pre-emphasis<br>1040% pre-emphasis<br>1160% pre-emphasis |         |         |  |  |

|-------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|--|--|

| Built-in Default Values | ROM0 ROM1 ROM2 ROM3                                           |                                                                                                                                                                   |         |         |  |  |

|                         | 0000000                                                       | 0000000                                                                                                                                                           | 0000000 | 0000000 |  |  |

#### Table 7. T1 Timing

| [4–0]                   | Sets timing of transition from 0 ms to 155 ms in 5-ms increments |         |         |          |

|-------------------------|------------------------------------------------------------------|---------|---------|----------|

| [7–5]                   | Reserved                                                         |         |         |          |

| Built-in Default Values | ROM0                                                             | ROM1    | ROM2    | ROM3     |

|                         | 0000001                                                          | 0000001 | 0000001 | 00001010 |

#### Table 8. CPV Start

| [4–0]                   | Sets start timing of CPV pulses from 0 ms to 155 ms in 5-ms increments |          |          |          |

|-------------------------|------------------------------------------------------------------------|----------|----------|----------|

| [7–5]                   | Reserved                                                               |          |          |          |

| Built-in Default Values | ROM0                                                                   | ROM1     | ROM2     | ROM3     |

|                         | 00000010                                                               | 00000011 | 00000011 | 00001111 |

#### Table 9. TP1 Width

| [5–0]                   | Controls TP1 width from 1 t(R) to 63 t(R) |          |          |          |

|-------------------------|-------------------------------------------|----------|----------|----------|

| [7–6]                   | Reserved                                  |          |          |          |

| Built-in Default Values | ROM0                                      | ROM1     | ROM2     | ROM3     |

|                         | 00000101                                  | 00001000 | 00001100 | 00010011 |

#### Table 10. CPV Rising Edge

| [6–0]                   | Sets CPV rising edge with reference to TP1 rising edge from 0 $t_{(R)}$ to 127 $t_{(R)}$ . |          |          |          |

|-------------------------|--------------------------------------------------------------------------------------------|----------|----------|----------|

| [7]                     | 0 = transition after TP1 edge, 1 = transition before TP1 edge                              |          |          |          |

| Built-in Default Values | ROM0                                                                                       | ROM1     | ROM2     | ROM3     |

|                         | 10100101                                                                                   | 00000000 | 10111000 | 00010011 |

#### Table 11. CPV Falling Edge

| [6–0]                   | Sets CPV falling edge with reference to TP1 rising edge from 0 $t_{(R)}$ to 127 $t_{(R)}$ |          |          |          |

|-------------------------|-------------------------------------------------------------------------------------------|----------|----------|----------|

| [7]                     | 0 = transition after TP1 edge, 1 = transition before TP1 edge                             |          |          |          |

| Built-in Default Values | ROM0                                                                                      | ROM1     | ROM2     | ROM3     |

|                         | 00101111                                                                                  | 00101000 | 00111101 | 10111001 |

#### Table 12. OE Timing 1

| If OE power-on polarity is high (bit 0 of register $02h = 1$ ), then this register defines the OE falling edge timing.<br>If OE power-on polarity is low (bit 0 of register $02h = 0$ ), then this register defines the OE rising edge timing. |                                                                                                      |                                                               |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|

| [6-0]                                                                                                                                                                                                                                          | [6–0] Sets OE edge with reference to TP1 rising edge from 0 t <sub>(R)</sub> to 127 t <sub>(R)</sub> |                                                               |  |  |  |  |

| [7]                                                                                                                                                                                                                                            | 0 = transition after TP1                                                                             | 0 = transition after TP1 edge, 1 = transition before TP1 edge |  |  |  |  |

| Built-in Default Values                                                                                                                                                                                                                        | ROM0                                                                                                 | ROM0 ROM1 ROM2 ROM3                                           |  |  |  |  |

|                                                                                                                                                                                                                                                | 00000101 00001000 0000000 00010111                                                                   |                                                               |  |  |  |  |

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

#### Table 13. OE Timing 2

| If OE power-on polarity is high (bit 0 of register $02h = 1$ ), then this register defines the OE rising edge timing.<br>If OE power-on polarity is low (bit 0 of register $02h = 0$ ), then this register defines the OE falling edge timing. |                                                               |          |          |          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|----------|----------|--|

| [6–0] Sets OE edge with reference to TP1 rising edge from 0 t <sub>(R)</sub> to 127 t <sub>(R)</sub>                                                                                                                                           |                                                               |          |          |          |  |

| [7]                                                                                                                                                                                                                                            | 0 = transition after TP1 edge, 1 = transition before TP1 edge |          |          |          |  |

| Built-in Default Values                                                                                                                                                                                                                        | ROM0 ROM1 ROM2 ROM3                                           |          |          |          |  |

|                                                                                                                                                                                                                                                | 10110100                                                      | 10101000 | 10111101 | 00000110 |  |

NOTE: If OE timing 1 and OE timing 2 are programmed to the same value, the OE remains at the value set by register bit 02[0].

#### Table 14. STVA Control 1 and Control 2

| Together, STVA control 1 and STVA control 2 determine the generation of the STVA pulses. The range is from –7 to 8. A 1 in the bit position enables the generation of a pulse in the corresponding line. |                                              |          |         |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|---------|---------|

| STVA 1 [7–0] Bit 7 = line number –7, Bit 0 = line number 0                                                                                                                                               |                                              |          |         |         |

| STVA 2 [7–0]                                                                                                                                                                                             | Bit 7 = line number 1, Bit 0 = line number 8 |          |         |         |

| Built-in Default Values                                                                                                                                                                                  | ROM0                                         | ROM1     | ROM2    | ROM3    |

| 1                                                                                                                                                                                                        | 00000111 00000111 00000011 00000001          |          |         |         |

| 2                                                                                                                                                                                                        | 00000000                                     | 00000000 | 0000000 | 0000000 |

#### Table 15. STVB Control 1 and Control 2

| Together, STVB control 1 and STVB control 2 determine the generation of the STVB pulses. The range is from –7 to 8. A 1 in the bit position enables the generation of a pulse in the corresponding line. |                                              |                     |          |          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------|----------|----------|--|

| STVB 1 [7–0] Bit 7 = line number –7, Bit 0 = line number 0                                                                                                                                               |                                              |                     |          |          |  |

| STVB 2 [7–0]                                                                                                                                                                                             | Bit 7 = line number 1, Bit 0 = line number 8 |                     |          |          |  |

| Built-in Default Value                                                                                                                                                                                   | ROM0                                         | ROM0 ROM1 ROM2 ROM3 |          |          |  |

| 1                                                                                                                                                                                                        | 0000001                                      | 00000011            | 00000011 | 00000000 |  |

| 2                                                                                                                                                                                                        | 0000000                                      | 1000000             | 1000000  | 1000000  |  |

#### Table 16. Off-Spec Check

| [2]<br>[3] | H-sync / frame<br>H-sync / VB back porch |                         | 0 = ignore V-sync frequency, 1 = check<br>0 = ignore # H-sync in VB back-porch, 1 = check |                                           |                       |          |

|------------|------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|----------|

| [4]        | H-sync / Vblank                          |                         |                                                                                           | 0 = ignore # H-sync in Vblank , 1 = check |                       |          |

| [5]        | Clocks / line (DE only)                  | Clocks / line (DE only) |                                                                                           | 0 = ignore clocks / line, 1 = check       |                       |          |

| [6]        | Lines / frame (DE only)                  |                         |                                                                                           | 0 = ignore lines / frame, 1 = check       |                       |          |

| [7]        | Lines / Vblank (DE only)                 | unly)                   |                                                                                           | 0 = ignore line                           | s / Vblank, 1 = check |          |

| Buil       | Built-in Default Values ROM0             |                         | R                                                                                         | OM1                                       | ROM2                  | ROM3     |

|            |                                          | 00010111                | 00                                                                                        | 001111                                    | 00000111              | 11100001 |

#### Table 17. FPO1 Control

| [7]                     | Pulse polarity                                                  | Pulse polarity               |                          |           |  |

|-------------------------|-----------------------------------------------------------------|------------------------------|--------------------------|-----------|--|

| [6–5]                   | 00 = Pulse is dc<br>01 = Pulse per frame<br>10 = Pulse per line |                              |                          |           |  |

| [4–0]                   | Starting time of pulse ac                                       | tivation after power on, fro | om 0 ms to 155 ms in 5-m | ns steps. |  |

| Built-in Default Values | ROM0                                                            | ROM0 ROM1 ROM2 ROM3          |                          |           |  |

|                         | 00000010                                                        | 00000010                     | 00000010                 | 11000000  |  |

SLDS140B - APRIL 2001 - REVISED SEPTEMBER 2002

#### Table 18. FPO1 Start

| [7–0]                   | Ignored in dc mode.<br>In the once per frame mode, starting position of pulse = $[7-0] = -127$ to 127 with reference to the first line. ([7] = 1 indicates before first line)<br>In the once per line mode, similar to OE start programming. |         |         |          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|----------|

| Built-in Default Values | ROM0 ROM1 ROM2 ROM3                                                                                                                                                                                                                          |         |         |          |

|                         | 00000000                                                                                                                                                                                                                                     | 0000000 | 0000000 | 00010111 |

#### Table 19. FPO1 Stop

| [7–0]                   | Ignored in dc mode<br>In the once per frame mode, stop position of pulse = $[7-0] = -127$ to 127 with reference to the last line.<br>([7] = 1 indicates before last line)<br>In the once per line mode, similar to OE stop programming. |          |         |          |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------|

| Built-in Default Values | ROM0 ROM1 ROM2 ROM3                                                                                                                                                                                                                     |          |         |          |

|                         | 00000000                                                                                                                                                                                                                                | 00000000 | 0000000 | 10000011 |

#### Table 20. FPO2 Control

| [7]                     | Pulse polarity                                                  | Pulse polarity               |                          |           |  |

|-------------------------|-----------------------------------------------------------------|------------------------------|--------------------------|-----------|--|

| [6–5]                   | 00 = Pulse is dc<br>01 = Pulse per frame<br>10 = Pulse per line |                              |                          |           |  |

| [4–0]                   | Starting time of pulse ac                                       | tivation after power-on, fro | om 0 ms to 155 ms in 5-m | ns steps. |  |

| Built-in Default Values | ROM0                                                            | ROM0 ROM1 ROM2 ROM3          |                          |           |  |

|                         | 00000011                                                        | 00000011                     | 00000011                 | 11000000  |  |

#### Table 21. FPO2 Start

| [7–0]                   | line. ([7] = 1 indicates be | Ignored in dc mode<br>In the once per frame mode, starting position of pulse $= [7-0] = -127$ to 127 with reference to the first<br>line. ([7] = 1 indicates before first line)<br>In the once per line mode, similar to OE start programming. |          |          |  |

|-------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--|

| Built-in Default Values | ROM0                        | ROM0 ROM1 ROM2 ROM3                                                                                                                                                                                                                            |          |          |  |

|                         | 00000000                    | 00000000                                                                                                                                                                                                                                       | 00000000 | 00010111 |  |

#### Table 22. FPO2 Stop

| [7–0]                   | ([7] = 1 indicates before | Ignored in dc mode<br>In the once per frame mode, stop position of pulse = $[7-0] = -127$ to 127 with reference to the last line.<br>([7] = 1 indicates before last line)<br>In the once per line mode, similar to OE stop programming. |          |          |  |

|-------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--|

| Built-in Default Values | ROM0                      | ROM0 ROM1 ROM2 ROM3                                                                                                                                                                                                                     |          |          |  |

|                         | 00000000                  | 0000000                                                                                                                                                                                                                                 | 00000000 | 10000011 |  |

#### Table 23. Auto-Refresh TPI Width