# **Three Output Controller** with Single SVID Interface for Desktop and Notebook **CPU Applications**

The NCP81212 (2 + 2 + 1) phase) three-output buck solution is optimized for Intel's IMVP8 CPUs.

The two multi-phase rail control systems are based on Dual-Edge pulse-width modulation (PWM) combined with DCR current sensing providing an ultra fast initial response to dynamic load events and reduced system cost.

The single-phase rail makes use of ON Semiconductor's patented high performance RPM operation. RPM control maximizes transient response while allowing for smooth transitions between discontinuous-frequency-scaling operation and continuous-mode full-power operation. The NCP81212 has an ultra-low offset current monitor amplifier with programmable offset compensation for high-accuracy current monitoring.

### Multi-Phase Rail Features

- Dual Edge Modulation for Fastest Initial Response to Transient

- High Performance Operational Error Amplifier

- Digital Soft Start Ramp

- Dynamic Reference Injection (Patent #US7057381)

- Accurate Total Summing Current Amplifier (Patent #US6683441)

- Dual High Impedance Differential Voltage and Total Current Sense **Amplifiers**

- Phase-to-Phase Dynamic Current Balancing

- True Differential Current Balancing Sense Amplifiers for Each Phase

- Adaptive Voltage Positioning (AVP)

- Switching Frequency Range of 300 kHz 1.2 MHz

- Vin range 4.5 V to 25 V

- Startup into Pre-Charged Loads While Avoiding False OVP

- UltraSonic Operation

## Single-Phase Rail Features

- Enhanced RPM Control System

- Ultra Low Offset IOUT Monitor

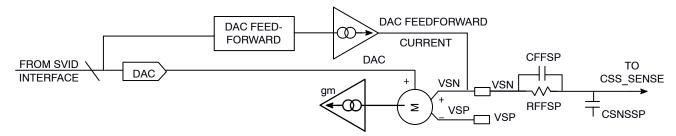

- Dynamic VID Feed–Forward

- Programmable Droop Gain

- Zero Droop Capable

- Thermal Monitor

- UltraSonic Operation

- Adjustable Vboot

- Digitally Controlled Operating Frequency

## ON Semiconductor®

#### www.onsemi.com

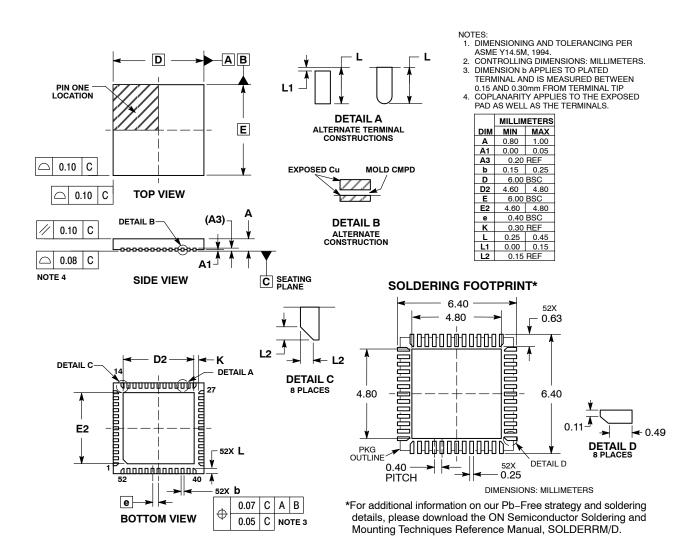

QFN52 6 × 6, 0.4P CASE 485BE

#### MARKING DIAGRAM

= Wafer Fab

= Assembly Site

WL = Lot ID

YY = Year

WW = Work Week

= Pb-Free Designator

### **ORDERING INFORMATION**

| Device        | Package | Shipping†          |  |  |

|---------------|---------|--------------------|--|--|

| NCP81212MNTXG | 52 QFN  | 2500 / Tape & Reel |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

## **Applications**

- Desktop & Notebook Processors

- Gaming

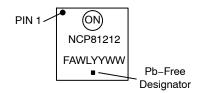

Figure 1.

**Pinout**

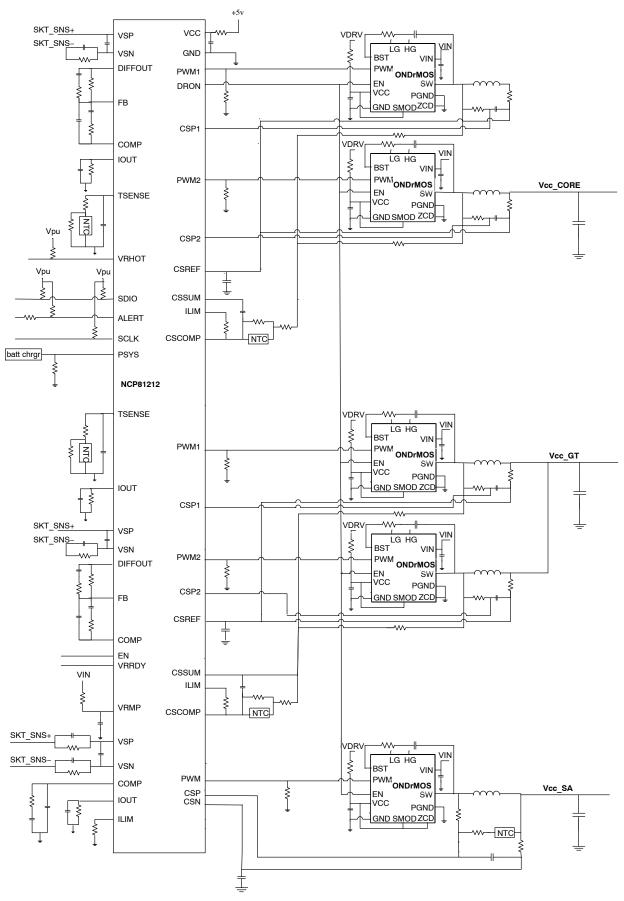

Figure 2. Pinout Diagram

# **Pin Function Description**

**Table 1. QFN52 PIN LIST DESCRIPTION**

| Pin | Name                         | Description                                                                                                |

|-----|------------------------------|------------------------------------------------------------------------------------------------------------|

| 1   | VSP_2PH_A                    | Differential output voltage sense positive for multi-phase rail "A"                                        |

| 2   | VSN_2PH_A                    | Differential output voltage sense negative for multi-phase rail "A"                                        |

| 3   | IMON_2PH_A                   | A resistor to ground programs IOUT gain for multi-phase rail "A"                                           |

| 4   | DIFFOUT_2PH_A                | Output of multi-phase rail "A" differential remote sense amplifier                                         |

| 5   | FB_2PH_A                     | Error amplifier voltage feedback for multi-phase rail "A"                                                  |

| 6   | COMP_2PH_A                   | Error amplifier output and PWM comparator inverting input for multi-phase rail "A"                         |

| 7   | ILIM_2PH_A                   | A resistor to CSCOMP_2PH_A programs the over-current threshold for multi-phase rail "A"                    |

| 8   | CSCOMP_2PH_A                 | Total-current-sense amplifier output for multi-phase rail "A"                                              |

| 9   | CSSUM_2PH_A                  | Inverting input of total-current-sense amplifier for multi-phase rail "A"                                  |

| 10  | CSREF_2PH_A                  | Total-current-sense amplifier reference voltage input for multi-phase rail "A"                             |

| 11  | CSP1_2PH_A                   | Current-balance amplifier positive input for Phase 1 of multi-phase rail "A"                               |

| 12  | CSP2_2PH_A                   | Current-balance amplifier positive input for Phase 2 of multi-phase rail "A"                               |

| 13  | NC                           | No connect                                                                                                 |

| 14  | TTSENSE_2PH_A                | Temperature sense input for multi-phase rail "A"                                                           |

| 15  | VRMP                         | Vin feed-forward input. Controls a current used to generate the ramps of the modulators                    |

| 16  | VCC                          | Power for the internal control circuits. A decoupling capacitor is connected from this pin to ground       |

| 17  | DRON                         | External FET driver enable for discrete driver or DrMOS                                                    |

| 18  | PWM1_2PH_A/                  | Phase 1 PWM output of multi-phase rail "A" /                                                               |

|     | ICCMAX_2PH_A                 | A resistor to ground programs ICCMAX for multi-phase rail "A"                                              |

| 19  | PWM2_2PH_A/                  | Phase 2 PWM output of multi-phase rail "A" /                                                               |

|     | ADDR                         | A resistor to ground configures SVID addresses for all 3 rails (ADDR)                                      |

| 20  | VBOOT                        | A resistor to ground configures boot voltage for all 3 rails (VBOOT)                                       |

| 21  | ROSC_2PH                     | A resistor to ground configures Fsw for both "A" and "B" multi-phase rails (ROSC_2PH)                      |

| 22  | PWM2_2PH_B/<br>ROSC_1PH      | Phase 2 PWM output of multi-phase rail "B" /                                                               |

|     |                              | A resistor to ground configures Fsw for 1ph rail (ROSC_1ph)                                                |

| 23  | PWM1_2PH_B /<br>ICCMAX_2PH_B | Phase 1 PWM output of multi-phase rail "B" / A resistor to ground programs ICCMAX for multi-phase rail "B" |

| 24  | TTSENSE 1PH/                 | Temperature sense input for the single-phase rail /                                                        |

| 24  | PSYS                         | System input power monitor. A resistor to ground scales this signal                                        |

| 25  | TTSENSE_2PH_B                | Temperature sense input for multi-phase rail "B"                                                           |

| 26  | NC                           | No Connect                                                                                                 |

| 27  | CSP2 2PH B                   | Current-balance amplifier positive input for Phase 2 of multi-phase rail "B"                               |

| 28  | CSP1_2PH_B                   | Current-balance amplifier positive input for Phase 1 of multi-phase rail "B"                               |

| 29  | CSREF_2PH_B                  | Total-current-sense amplifier reference voltage input for multi-phase rail "B"                             |

| 30  | CSSUM_2PH_B                  | Inverting input of total-current-sense amplifier for multi-phase rail "B"                                  |

| 31  | CSCOMP_2PH_B                 | Total-current-sense amplifier output for multi-phase rail "B"                                              |

| 32  | ILIM_2PH_B                   | A resistor to CSCOMP 2PH B programs the over-current threshold for multi-phase rail "B                     |

| 33  | COMP_2PH_B                   | Error amplifier output and PWM comparator inverting input for multi-phase rail "B"                         |

| 34  | FB_2PH_B                     | Error amplifier voltage feedback for multi-phase rail "B"                                                  |

| 35  | DIFFOUT_2PH_B                | Output of multi-phase rail "B" differential remote sense amplifier                                         |

| 36  | IMON_2PH_B                   | A resistor to ground programs IOUT gain for multi-phase rail "B"                                           |

| 37  | VSN_2PH_B                    | Differential output voltage sense negative for multi-phase rail "B"                                        |

| 38  | VSN_2F11_B<br>VSP_2PH_B      | Differential output voltage sense negative for multi-phase rail "B"                                        |

| 39  | VR HOT#                      | Thermal logic output for over–temperature condition on TTSENSE pins                                        |

| 40  | SDIO                         | Serial VID data interface                                                                                  |

| 41  | ALERT#                       | Serial VID data interface  Serial VID ALERT#                                                               |

Table 1. QFN52 PIN LIST DESCRIPTION (continued)

| Pin | Name                    | Description                                                                                          |

|-----|-------------------------|------------------------------------------------------------------------------------------------------|

| 42  | SCLK                    | Serial VID clock                                                                                     |

| 43  | EN                      | Enable input. High enables all three rails                                                           |

| 44  | PWM_1PH /<br>ICCMAX_1PH | PWM output of the single-phase rail / A resistor to ground programs ICCMAX for the single-phase rail |

| 45  | VR_RDY                  | VR_RDY indicates all three rails are ready to accept SVID commands                                   |

| 46  | IMON_1PH                | A resistor to ground programs IOUT gain for the single-phase rail                                    |

| 47  | CSP_1PH                 | Differential current sense positive for the single-phase rail                                        |

| 48  | CSN_1ph                 | Differential current sense negative for the single-phase rail                                        |

| 49  | ILIM_1ph                | A resistor to ground programs ILIM gain for the single-phase rail                                    |

| 50  | COMP_1ph                | Compensation for single-phase rail                                                                   |

| 51  | VSN_1ph                 | Differential output voltage sense negative for single-phase rail                                     |

| 52  | VSP_1ph                 | Differential output voltage sense positive for single-phase rail                                     |

| 53  | Tab                     | GND                                                                                                  |

#### **Electrical Information**

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Pin Symbol     | Pin Symbol V <sub>MAX</sub> |              | I <sub>SOURCE</sub> | I <sub>SINK</sub> |

|----------------|-----------------------------|--------------|---------------------|-------------------|

| COMPX          | VCC + 0.3 V                 | -0.3 V       | 2 mA                | 2 mA              |

| CSCOMPX        | VCC + 0.3 V                 | -0.3 V       | 2 mA                | 2 mA              |

| VSN            | GND + 300 mV                | GND – 300 mV | 1 mA                | 1 mA              |

| VRDY           | VCC + 0.3 V                 | -0.3 V       | N/A                 | 2 mA              |

| VCC            | 6.5 V                       | -0.3 V       | N/A                 | N/A               |

| VRMP           | +25 V                       | -0.3 V       |                     |                   |

| All Other Pins | VCC + 0.3 V                 | -0.3 V       |                     |                   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **Thermal Information**

**Table 3. THERMAL INFORMATION**

| Description                                     | Symbol           | Тур          | Unit |

|-------------------------------------------------|------------------|--------------|------|

| Thermal Characteristic,<br>QFN Package (Note 2) | R <sub>JA</sub>  | 68           | °C/W |

| Operating Junction Temperature Range (Note 3)   | TJ               | -10 to 125   | °C   |

| Operating Ambient Temperature Range             |                  | -10 to 100   | °C   |

| Maximum Storage Temperature Range               | T <sub>STG</sub> | - 40 to +150 | °C   |

| Moisture Sensitivity Level QFN Package          | MSL              | 1            |      |

The maximum package power dissipation must be observed

JESD 51–5 (1S2P Direct–Attach Method) with 0 LFM

JESD 51–7 (1S2P Direct–Attach Method) with 0 LFM

<sup>1.</sup> All signals referenced to GND unless noted otherwise.

# Table 4. ELECTRICAL CHARACTERISTICS

(Unless otherwise stated:  $-10^{\circ}C < T_A < 100^{\circ}C; 4.75 \text{ V} < VCC < 5.25 \text{ V}; CVCC = 0.1 \mu F)$

| Parameter                                 | Test Conditions                                                                                                                                                                   | MIN  | TYP  | MAX  | Units |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| ERROR AMPLIFIER                           |                                                                                                                                                                                   |      |      |      | _     |

| Input Bias Current                        |                                                                                                                                                                                   | -900 |      | 900  | nA    |

| Open Loop DC Gain                         | CL = 20 pF to GND,<br>RL = 10 K $\Omega$ to GND                                                                                                                                   |      | 80   |      | dB    |

| Open Loop Unity Gain Bandwidth            | CL = 20 pF to GND,<br>RL = 10 KΩ to GND                                                                                                                                           |      | 20   |      | MHz   |

| Slew Rate                                 | $\Delta Vin = 100 \text{ mV}, \text{ G} = -10 \text{ V/V},$ $\Delta Vout = 0.75 \text{ V} - 1.52 \text{ V},$ $CL = 20 \text{ pF to GND},$ $DC \text{ Load} = 10 \text{ k to GND}$ |      | 5    |      | V/µs  |

| Maximum Output Voltage                    | I <sub>SOURCE</sub> = 2.0 mA                                                                                                                                                      | 3.5  | -    | -    | V     |

| Minimum Output Voltage                    | I <sub>SINK</sub> = 2.0 mA                                                                                                                                                        | _    | _    | 1    | V     |

| DIFFERENTIAL SUMMING AMPLIFIER            | <u>,                                      </u>                                                                                                                                    |      | •    |      |       |

| Input Bias Current                        |                                                                                                                                                                                   | -25  | -    | 25   | nA    |

| VSP Input Voltage Range                   |                                                                                                                                                                                   | -0.3 | -    | 3.0  | V     |

| VSN Input Voltage Range                   |                                                                                                                                                                                   | -0.3 | _    | 0.3  | V     |

| -3dB Bandwidth                            | CL = 20 pF to GND,<br>RL = 10 K $\Omega$ to GND                                                                                                                                   |      | 22.5 |      | MHz   |

| Closed Loop DC gain<br>VS to DIFF         | VS+ to VS- = 0.5 to 1.3 V                                                                                                                                                         |      | 1.0  |      | V/V   |

| Maximum Output Voltage                    | I <sub>SOURCE</sub> = 2 mA                                                                                                                                                        | 3.5  | -    | -    | V     |

| Minimum Output Voltage                    | I <sub>SINK</sub> = 2 mA                                                                                                                                                          | _    | _    | 0.8  | V     |

| CURRENT SUMMING AMPLIFIER                 |                                                                                                                                                                                   |      |      | ı    | I     |

| Offset Voltage (Vos)                      |                                                                                                                                                                                   | -300 |      | 300  | μV    |

| Input Bias Current                        | CSSUM = CSREF = 1V                                                                                                                                                                | -7.5 |      | 7.5  | μΑ    |

| Open Loop Gain                            |                                                                                                                                                                                   |      | 80   |      | dB    |

| Current Sense Unity Gain Bandwidth        | $C_L$ = 20 pF to GND,<br>$R_L$ = 10 K $\Omega$ to GND                                                                                                                             |      | 15   |      | MHz   |

| Maximum CSCOMP (A) Output Voltage         | Isource = 2 mA                                                                                                                                                                    | 3.5  | _    | -    | V     |

| Minimum CSCOMP(A) Output Voltage          | Isink = 500 μA                                                                                                                                                                    | -    | -    | 0.15 | V     |

| CURRENT BALANCE AMPLIFIER                 | -                                                                                                                                                                                 |      |      |      | !     |

| Input Bias Current                        | CSPX - CSPX + 1 = 1.2 V                                                                                                                                                           | -50  | -    | 50   | nA    |

| Common Mode Input Voltage Range           | CSPx = CSREF                                                                                                                                                                      | 0    | -    | 2.3  | V     |

| Differential Mode Input Voltage Range     | CSNx = 1.2 V                                                                                                                                                                      | -100 | -    | 100  | mV    |

| Closed loop Input Offset Voltage Matching | CSPx = 1.2 V,<br>Measured from the average                                                                                                                                        | -1.5 | -    | 1.5  | mV    |

| Current Sense Amplifier Gain              | 0 V < CSPx < 0.1 V,                                                                                                                                                               | 5.7  | 6.0  | 6.3  | V/V   |

| Multiphase Current Sense Gain Matching    | CSREF = CSP = 10 mV to<br>30 mV                                                                                                                                                   | -3   |      | 3    | %     |

| -3 dB Bandwidth                           |                                                                                                                                                                                   |      | 8    |      | MHz   |

| BIAS SUPPLY                               | •                                                                                                                                                                                 |      |      | •    |       |

| Supply Voltage Range                      |                                                                                                                                                                                   | 4.75 |      | 5.25 | V     |

| VCC Quiescent Current                     | PS0                                                                                                                                                                               |      | 33   | 45   | mA    |

| VCC Quiescent Current                     | PS3                                                                                                                                                                               |      | 20   |      | mA    |

| VCC Quiescent Current                     | PS4 at 25°C                                                                                                                                                                       |      | 400  |      | μΑ    |

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^{\circ}C < T_A < 100^{\circ}C; 4.75 \text{ V} < VCC < 5.25 \text{ V}; CVCC = 0.1 \mu F)$

| Parameter                         | Test Conditions                                                                      | MIN  | TYP            | MAX  | Units |

|-----------------------------------|--------------------------------------------------------------------------------------|------|----------------|------|-------|

| BIAS SUPPLY                       |                                                                                      |      |                |      |       |

| VCC Quiescent Current             | Enable low                                                                           |      |                | 60   | μА    |

| UVLO Threshold                    | VCC rising                                                                           |      |                | 4.5  | V     |

|                                   | VCC falling                                                                          | 4    |                |      | V     |

| VCC UVLO Hysteresis               |                                                                                      |      | 250            |      | mV    |

| VRMP                              |                                                                                      |      |                |      |       |

| Supply Range                      |                                                                                      | 4.5  |                | 20   | V     |

| UVLO Threshold                    | VRamp rising                                                                         |      |                | 4.25 | V     |

|                                   | VRamp falling                                                                        | 3    |                |      | V     |

| UVLO Hysteresis                   | , ,                                                                                  |      | 675            |      | mV    |

| DAC SLEW RATE                     |                                                                                      |      |                |      |       |

| Slew Rate Fast                    |                                                                                      |      | >10            |      | mV/μs |

| Soft Start Slew Rate              |                                                                                      |      | 1/2 SR<br>Fast |      | mV/μs |

| Slew Rate Slow                    |                                                                                      |      | 1/2 SR<br>Fast |      | mV/μs |

| ENABLE INPUT                      |                                                                                      |      | 1              |      | 1     |

| Enable High Input Leakage Current | Enable = 0                                                                           | -1   |                | 1    | μА    |

| Upper Threshold                   | V <sub>UPPER</sub>                                                                   | 0.8  |                |      | V     |

| Lower Threshold                   | V <sub>LOWER</sub>                                                                   |      |                | 0.3  | V     |

| Enable Delay Time                 | Measure time from Enable transitioning HI , VBOOT is not 0 V                         |      |                | 2.5  | ms    |

| DRON                              |                                                                                      |      |                |      | I     |

| Output High Voltage               | Sourcing 500 μA                                                                      | 3.0  | _              | _    | V     |

| Output Low Voltage                | Sinking 500 μA                                                                       | _    | _              | 0.1  | V     |

| Pull Up Resistances               |                                                                                      |      | 2.0            |      | kΩ    |

| Rise/Fall Time                    | CL (PCB) = 20pF,<br>ΔVo = 10% to 90%                                                 | _    | 160            |      | ns    |

| Internal Pull Down Resistance     | VCC = 0 V                                                                            |      | 70             |      | kΩ    |

| OVERCURRENT PROTECTION            |                                                                                      |      |                |      | ı     |

| Ilim Threshold Current            | PS0                                                                                  | 9    | 10             | 11   | μА    |

| (delayed OCP shutdown)            | PS1, PS2, PS3<br>(N = PS0 phase count)                                               |      | 10/N           |      | μA    |

| Ilim Threshold Current            | PS0                                                                                  | 13.5 | 15             | 16.5 | μА    |

| (immediate OCP shutdown)          | PS1, PS2, PS3<br>(N = PS0 phase count)                                               |      | 15/N           |      | μА    |

| Shutdown Delay                    | Immediate                                                                            |      | 300            |      | ns    |

| a.a 20.ay                         | Delayed                                                                              |      | 50             |      | μs    |

| ILIM Output Voltage Offset        | Ilim sourcing 10 μA                                                                  | -2   |                | 2    | mV    |

|                                   | Measured relative to CSRef                                                           |      |                |      |       |

| IOUT_4PH /IOUT_2PH OUTPUT         |                                                                                      |      |                |      |       |

| Output Offset Current             | V <sub>Ilim</sub> = 5 V                                                              |      |                | 0.25 | μΑ    |

| Output current max                | Ilimit sink current 20 μA                                                            |      | 200            |      | μΑ    |

| Current Gain                      | (lout current)/(llimit Current) Rlim = 20 K, Riout = 5 K DAC = 0.8 V, 1.25 V, 1.52 V | 9.5  | 10             | 10.5 | A/A   |

**OSCILLATOR**

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^{\circ}C < T_A < 100^{\circ}C$ ; 4.75 V < VCC < 5.25 V; CVCC = 0.1 $\mu$ F)

| Parameter                                | Test Conditions                             | MIN       | TYP  | MAX      | Units    |

|------------------------------------------|---------------------------------------------|-----------|------|----------|----------|

| OSCILLATOR                               |                                             |           | •    | •        | •        |

| Switching Frequency Range                |                                             | 300       | -    | 1200     | kHz      |

| Switching Frequency Accuracy             | 300KHz < Fsw < 1MHz                         | -10       | -    | 10       | %        |

| PSYS                                     |                                             |           | •    |          | •        |

| Input Current                            | $R_{psys} = 20 \text{ k}\Omega$             |           |      | 100      | μΑ       |

| ADC resolution                           | 8 bit                                       |           | 7.81 |          | mV/LSB   |

| Register update rate                     |                                             |           |      | 500      | μs       |

| Disable Threshold                        |                                             |           |      | 4.5      | V        |

| OUTPUT OVER VOLTAGE & UNDER VOLTAGE      | PROTECTION (OVP & UVP)                      |           | *    | •        | •        |

| Over Voltage Threshold During Soft-Start |                                             | 1.9       | 2.0  | 2.1      | V        |

| Over Voltage Threshold Above DAC         | VSP rising                                  | 370       | 400  | 430      | mV       |

| Over Voltage Delay                       | VSP rising to PWMx low                      |           | 25   |          | ns       |

| Under Voltage Threshold Below DAC-DROOP  | VSP falling                                 | 225       | 300  | 370      | mV       |

| Under-voltage Hysteresis                 | VSP rising                                  |           | 25   |          | mV       |

| Under-Voltage Delay                      |                                             |           | 5    |          | μs       |

| SVID DAC                                 |                                             |           | •    | •        | •        |

| System Voltage Accuracy                  | .75 V ≤ DAC < 1.52 V                        | -0.5      |      | 0.5      | %        |

|                                          | 0.5V < DAC < .745 V<br>0.25 V DAC < 0.495 V | −8<br>−10 |      | 8<br>10  | mV<br>mV |

| MODULATORS (PWM COMPARATORS) FOR A I     |                                             | 10        |      | 10       | 111.4    |

| Minimum Pulse Width                      | Fsw = 350 KHz                               |           | 40   |          | ns       |

| 0% Duty Cycle                            | COMP voltage when the                       |           | 1.3  | _        | V        |

| 0/8 Buty Cycle                           | PWM outputs remain LO                       |           | 1.0  |          | V        |

| 100% Duty Cycle                          | COMP voltage when the PWM outputs remain HI | -         | 2.5  | -        | V        |

| DWW DI A 1 F                             | VRMP=12.0 V                                 |           |      |          | 0        |

| PWM Phase Angle Error                    | Between adjacent phases                     |           | ±5   |          |          |

| TSENSE                                   | 1                                           |           | 100  | 1        |          |

| VRHOT Assert Threshold                   |                                             |           | 468  |          | mV       |

| VRHOT Rising Threshold                   |                                             |           | 488  |          | mV       |

| Alert Assertion Threshold                |                                             |           | 488  |          | mV       |

| Alert Rising Threshold                   |                                             | 445       | 510  | 105      | mV       |

| TSENSE Bias Current                      |                                             | 115       | 120  | 125      | μА       |

| VRHOT                                    |                                             |           | 1    |          | 1 ,,     |

| Output Low Saturation Voltage            | I <sub>VR_HOT</sub> = -4 mA                 |           |      | 0.3      | V        |

| Output Leakage Current                   | High Impedance State                        | -1        | _    | 1        | μА       |

| ADC                                      |                                             |           |      |          |          |

| Voltage Range                            |                                             | 0         |      | 2        | V        |

| Total Unadjusted Error (TUE)             |                                             | -1        | +    | 1        | %        |

| Differential Nonlinearity (DNL)          | 8-bit                                       |           |      | 1        | LSB      |

| Power Supply Sensitivity                 | - DIE                                       |           | +/-1 | <u> </u> | %        |

| Conversion Time                          |                                             |           | 7.4  |          | μs       |

| Round Robin                              |                                             |           | 206  |          | μs       |

| VRDY OUTPUT                              |                                             |           | 200  |          | μο       |

| Output Low Saturation Voltage            | I <sub>VR RDY</sub> = 4 mA,                 | _         | _    | 0.3      | V        |

| Output Low Outuration voitage            | VH_HDY - + IIIA,                            |           |      | 0.0      | , v      |

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^{\circ}C < T_A < 100^{\circ}C; 4.75 \ V < VCC < 5.25 \ V; CVCC = 0.1 \mu F)$

| Parameter                        | Test Conditions                                                       | MIN         | TYP  | MAX  | Units |

|----------------------------------|-----------------------------------------------------------------------|-------------|------|------|-------|

| VRDY OUTPUT                      |                                                                       |             |      |      |       |

| Rise Time                        | External pull-up of 1 KΩ to                                           | -           | -    | 150  | ns    |

|                                  | 3.3 V<br>C <sub>TOT</sub> = 45 pF,                                    |             |      |      |       |

|                                  | ΔVo = 10% to 90%                                                      |             |      |      |       |

| Fall Time                        | External pull–up of 1 K $\Omega$ to 3.3 V                             | -           | -    | 150  | ns    |

|                                  | $C_{TOT} = 45 \text{ pF},$<br>$\Delta Vo = 90\% \text{ to } 10\%$     |             |      |      |       |

| Output Leakage Current When High | VR_RDY= 5.0 V                                                         | -1          | _    | 1    | μΑ    |

| VR_RDY Delay (rising)            | En rising to VR_RDY rising (TA)                                       | -           | -    | 2.5  | ms    |

| VR_RDY Delay (falling)           | Due to OCP or OVP                                                     | -           | 0.3  | -    | μs    |

|                                  | En falling to VR_RDY falling (TD + TE)                                | -           | -    | 1.5  | μs    |

| PWM OUTPUTS                      |                                                                       | -           |      | -    |       |

| Output High Voltage              | Sourcing 500 μA                                                       | VCC - 0.2 V | -    | -    | V     |

| Output Mid Voltage               | No Load                                                               | 1.9         | 2.0  | 2.1  | V     |

| Output Low Voltage               | Sinking 500 μA                                                        | -           | _    | 0.7  | V     |

| Rise and Fall Time               | CL (PCB) = 50pF,<br>ΔVo =10% to 90% of VCC                            | -           | 5    |      | ns    |

| Tri-State Output Leakage         | Gx = 2.0 V, x = 1-2,<br>EN = Low                                      | -1          | -    | 1    | μА    |

| PHASE DETECTION                  |                                                                       |             |      |      |       |

| CSPX Phase Disable Voltage       |                                                                       | 4.75        |      |      | V     |

| SCLK, SDIO, ALERT#               |                                                                       |             |      |      |       |

| $V_{IL}$                         | Input Low Voltage                                                     |             |      | .45  | V     |

| VIH                              | Input High Voltage                                                    | .65         |      |      | V     |

| VOH                              | Output High Voltage                                                   |             | 1.05 |      | V     |

| VOL                              | SDIO, ALERT#                                                          |             |      | 0.3  | V     |

| Leakage Current                  |                                                                       | -1          |      | 1    | μΑ    |

| Pin Capacitance                  | @25°C only                                                            |             | 9    |      | pF    |

| VR clock to data delay (Tco)     |                                                                       |             |      | 12   | ns    |

| Setup time (Tsu)                 |                                                                       | 7           |      |      | ns    |

| Hold time (Thld)                 |                                                                       | 14          |      |      | ns    |

| ERROR AMPLIFIER                  |                                                                       |             |      |      |       |

| Input Bias Current               |                                                                       | -25         | -    | 25   | nA    |

| VSP Input Voltage Range          |                                                                       | -0.3        | -    | 3.0  | V     |

| VSN Input Voltage Range          |                                                                       | -0.3        | -    | 0.3  | V     |

| gm                               |                                                                       | 1.34        | 1.6  | 1.85 | mS    |

| Output Offset Current            |                                                                       | -15         |      | 15   | μΑ    |

| Open loop Gain                   | Load= 1nF in series with 1 $k\Omega$ in parallel with 10 pF to ground | 70          | 73   |      | dB    |

| Source Current                   | Input Differential -200 mV                                            |             | 280  |      | μΑ    |

| Sink Current                     | Input Differential 200 mV                                             |             | 280  |      | μΑ    |

| −3 dB Bandwidth                  | Load= 1nF in series with 1 kΩ in parallel with 10 pF to ground        |             | 20   |      | MHz   |

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^{\circ}C < T_A < 100^{\circ}C; 4.75 \ V < VCC < 5.25 \ V; CVCC = 0.1 \mu F)$

| Parameter                                | Test Conditions                                | MIN   | TYP  | MAX   | Units |

|------------------------------------------|------------------------------------------------|-------|------|-------|-------|

| IOUT                                     |                                                |       | •    | •     |       |

| gm                                       |                                                | 0.97  | 1    | 1.03  | mS    |

| Output Offset Current                    | CSP = CSN                                      | -250  |      | 250   | nA    |

| DROOP                                    |                                                |       |      |       |       |

| gm                                       |                                                | 0.96  | 1    | 1.04  | mS    |

| Output Offset Current                    | CSP = CSN                                      | -1.5  |      | 1.5   | μΑ    |

| OVERCURRENT PROTECTION                   |                                                |       |      |       |       |

| ILIMIT Threshold                         |                                                | 1.275 | 1.3  | 1.325 | V     |

| ILIMIT Delay                             |                                                |       | 200  |       | ns    |

| ILIMIT Gain                              | I <sub>ILIMIT</sub> /(CSP-CSN)<br>CSP-CSN=20mV | 0.925 | 1    | 1.075 | mS    |

| OUTPUT OVER VOLTAGE & UNDER VOLTAGE      | PROTECTION (OVP & UVP)                         |       |      |       |       |

| Over Voltage Threshold During Soft-Start |                                                |       | 2.0  |       | V     |

| Over Voltage Threshold Above DAC         | VSP - VSN - VID setting                        | 370   |      | 430   | mV    |

| Over Voltage Delay                       | VSP rising to PWMx low                         |       | 25   |       | ns    |

| Over Voltage VR_RDY Delay                | VSP rising to VR_RDY low                       |       | 350  |       | ns    |

| Under Voltage Threshold                  | VSP - VSN falling                              | 215   | 300  | 385   | mV    |

| Under-voltage Hysteresis                 | VSP - VSN falling/rising                       |       | 25   |       | mV    |

| Under-voltage Blanking Delay             | VSP-VSN falling to VR_RDY falling              |       | 5    |       | μs    |

| CSP-CSN ZCD COMPARATOR                   | <u>.</u>                                       |       |      |       |       |

| Offset Accuracy                          |                                                |       | ±1.5 |       | mV    |

Table 5. IMVP8 VID CODES

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage | Hex |

|------|------|------|------|------|------|------|------|---------|-----|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | Off     | 00  |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.25    | 01  |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.255   | 02  |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.26    | 03  |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.265   | 04  |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.27    | 05  |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.275   | 06  |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.28    | 07  |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.285   | 08  |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.29    | 09  |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.295   | 0A  |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.3     | 0B  |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.305   | 0C  |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.31    | 0D  |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.315   | 0E  |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.32    | 0F  |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.325   | 10  |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.33    | 11  |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.335   | 12  |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.34    | 13  |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.345   | 14  |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.35    | 15  |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.355   | 16  |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.36    | 17  |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.365   | 18  |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.37    | 19  |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.375   | 1A  |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.38    | 1B  |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.385   | 1C  |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.39    | 1D  |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.395   | 1E  |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.4     | 1F  |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.405   | 20  |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0.41    | 21  |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.415   | 22  |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.42    | 23  |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.425   | 24  |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.43    | 25  |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.435   | 26  |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.44    | 27  |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.445   | 28  |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.45    | 29  |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0.455   | 2A  |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0.46    | 2B  |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0.465   | 2C  |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0.47    | 2D  |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0.475   | 2E  |

Table 5. IMVP8 VID CODES (continued)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage | Hex |

|------|------|------|------|------|------|------|------|---------|-----|

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0.48    | 2F  |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0.485   | 30  |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0.49    | 31  |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0.495   | 32  |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0.5     | 33  |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0.505   | 34  |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0.51    | 35  |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0.515   | 36  |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0.52    | 37  |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0.525   | 38  |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0.53    | 39  |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0.535   | 3A  |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0.54    | 3B  |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0.545   | 3C  |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0.55    | 3D  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0.555   | 3E  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0.56    | 3F  |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0.565   | 40  |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0.57    | 41  |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0.575   | 42  |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0.58    | 43  |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0.585   | 44  |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0.59    | 45  |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0.595   | 46  |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0.6     | 47  |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0.605   | 48  |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0.61    | 49  |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0.615   | 4A  |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0.62    | 4B  |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0.625   | 4C  |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0.63    | 4D  |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0.635   | 4E  |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0.64    | 4F  |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0.645   | 50  |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0.65    | 51  |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0.655   | 52  |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0.66    | 53  |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0.665   | 54  |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0.67    | 55  |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0.675   | 56  |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0.68    | 57  |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0.685   | 58  |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0.69    | 59  |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0.695   | 5A  |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0.7     | 5B  |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0.705   | 5C  |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0.71    | 5D  |

Table 5. IMVP8 VID CODES (continued)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage | Hex |

|------|------|------|------|------|------|------|------|---------|-----|

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0.715   | 5E  |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0.72    | 5F  |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0.725   | 60  |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0.73    | 61  |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0.735   | 62  |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.74    | 63  |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.745   | 64  |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.75    | 65  |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.755   | 66  |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.76    | 67  |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.765   | 68  |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.77    | 69  |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.775   | 6A  |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.78    | 6B  |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.785   | 6C  |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.79    | 6D  |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.795   | 6E  |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.8     | 6F  |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.805   | 70  |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.81    | 71  |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.815   | 72  |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.82    | 73  |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.825   | 74  |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.83    | 75  |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.835   | 76  |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.84    | 77  |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.845   | 78  |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.85    | 79  |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.855   | 7A  |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.86    | 7B  |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.865   | 7C  |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.87    | 7D  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.875   | 7E  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.88    | 7F  |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0.885   | 80  |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.89    | 81  |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.895   | 82  |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.9     | 83  |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.905   | 84  |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.91    | 85  |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.915   | 86  |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.92    | 87  |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.925   | 88  |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.93    | 89  |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.935   | 8A  |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.94    | 8B  |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.945   | 8C  |

| ı    | U    | U    | U    | I    |      | U    | U    | 0.945   | 80  |

Table 5. IMVP8 VID CODES (continued)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage | Hex |

|------|------|------|------|------|------|------|------|---------|-----|

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.95    | 8D  |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.955   | 8E  |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.96    | 8F  |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.965   | 90  |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.97    | 91  |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.975   | 92  |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.98    | 93  |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.985   | 94  |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.99    | 95  |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.995   | 96  |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1       | 97  |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1.005   | 98  |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1.01    | 99  |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1.015   | 9A  |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1.02    | 9B  |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1.285   | D0  |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1.29    | D1  |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1.295   | D2  |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1.3     | D3  |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1.305   | D4  |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1.31    | D5  |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1.315   | D6  |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1.32    | D7  |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1.325   | D8  |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1.33    | D9  |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1.335   | DA  |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1.34    | DB  |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1.345   | DC  |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1.35    | DD  |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1.355   | DE  |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1.36    | DF  |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1.365   | E0  |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1.37    | E1  |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1.375   | E2  |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 1.38    | E3  |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 1.385   | E4  |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 1.39    | E5  |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 1.395   | E6  |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 1.4     | E7  |

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 1.405   | E8  |

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1.405   | E9  |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 1.415   | EA  |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 1.415   | EB  |

| 1    |      | 1    | 0    |      | 1    | 0    | 0    |         |     |

|      | 1    |      |      | 1    |      |      |      | 1.425   | EC  |

| 1    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 1.43    | ED  |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 1.435   | EE  |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1.44    | EF  |

Table 5. IMVP8 VID CODES (continued)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage | Hex |

|------|------|------|------|------|------|------|------|---------|-----|

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1.445   | F0  |

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 1.45    | F1  |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 1.455   | F2  |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 1.46    | F3  |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 1.465   | F4  |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 1.47    | F5  |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 1.475   | F6  |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1.48    | F7  |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 1.485   | F8  |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1.49    | F9  |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1.495   | FA  |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1.5     | FB  |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1.505   | FC  |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1.51    | FD  |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1.515   | FE  |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1.52    | FF  |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.025   | 9C  |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1.03    | 9D  |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1.035   | 9E  |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1.04    | 9F  |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1.045   | A0  |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1.05    | A1  |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1.055   | A2  |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1.06    | A3  |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1.065   | A4  |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1.07    | A5  |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1.075   | A6  |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1.08    | A7  |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1.085   | A8  |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1.09    | A9  |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1.095   | AA  |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1.1     | AB  |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1.105   | AC  |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1.11    | AD  |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1.115   | AE  |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1.12    | AF  |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1.125   | B0  |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1.13    | B1  |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1.135   | B2  |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1.14    | В3  |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1.145   | B4  |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1.15    | B5  |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1.155   | B6  |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1.16    | B7  |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1.165   | B8  |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1.17    | B9  |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1.175   | BA  |

Table 5. IMVP8 VID CODES (continued)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage | Hex |

|------|------|------|------|------|------|------|------|---------|-----|

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1.18    | BB  |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1.185   | ВС  |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1.19    | BD  |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1.195   | BE  |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1.2     | BF  |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1.205   | C0  |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1.21    | C1  |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1.215   | C2  |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1.22    | СЗ  |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1.225   | C4  |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1.23    | C5  |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1.235   | C6  |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1.24    | C7  |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1.245   | C8  |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1.25    | C9  |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1.255   | CA  |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1.26    | СВ  |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1.265   | CC  |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1.27    | CD  |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1.275   | CE  |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1.28    | CF  |

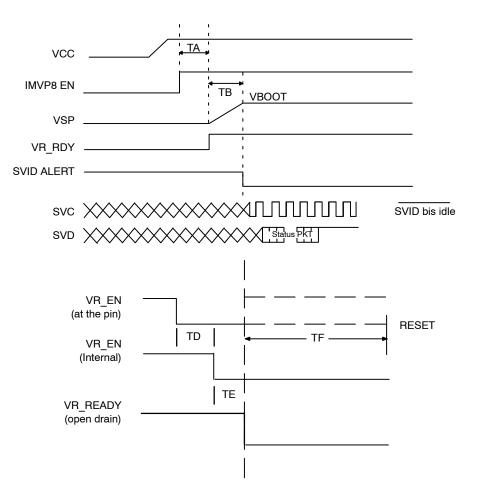

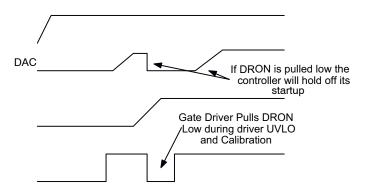

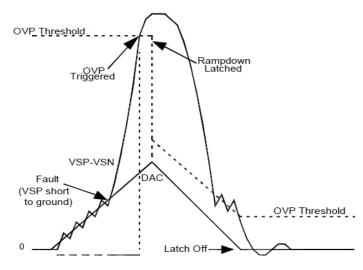

Figure 3. Startup Timing

Table 6.

|    | MIN  | TYP | MAX        |

|----|------|-----|------------|

| TA |      |     | 2.5 ms     |

| ТВ |      |     | VID / Slow |

| TD | 0 us |     | 1 us       |

| TE |      |     | 500 ns     |

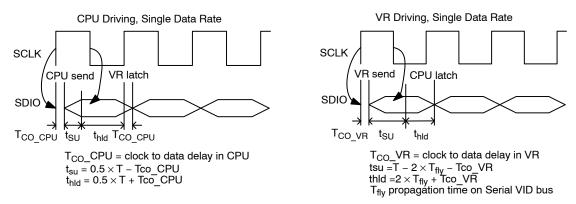

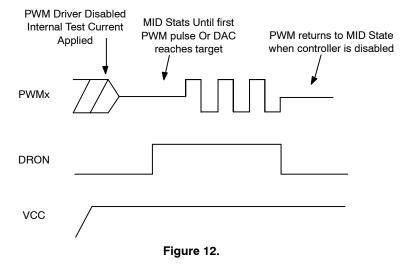

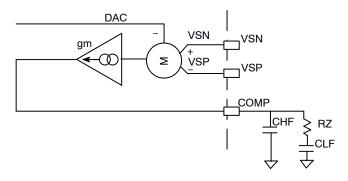

Figure 4. SVID Timing Diagram

## **GENERAL**

The NCP81212 is a three rail 2 + 2 + 1 phase PWM controller with a single serial SVID control interface.

## **Serial VID**

The NCP81212 supports the Intel serial VID interface. It communicates with the microprocessor through three wires

(SCLK, SDIO, ALERT#). The table of supported registers for Domains 00h, 01h, and 02/03h is shown below. The SVID register set for Domain 0Dh is smaller and contains the following registers: 00h, 01h, 02h, 05h, 10h, 11h, and 1Bh.

Table 7.

| Index | Name                       | Description                                                                                                                                                                                                                                                                                     | Access | Default<br>00h/01h/02h | PSYS 0Dh |

|-------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|----------|

| 00h   | Vendor ID                  | Uniquely identifies the VR vendor. The vendor ID assigned by Intel to ON Semiconductor is 0x1A                                                                                                                                                                                                  | R      | 1Ah                    | 1Ah      |

| 01h   | Product ID                 | Uniquely identifies the VR product. The VR vendor assigns this number.  2Ch = NCP81212                                                                                                                                                                                                          | R      | 2Ch                    | 2Ch      |

| 02h   | Product<br>Revision        | Uniquely identifies the revision or stepping of the VR control IC. The VR vendor assigns this data.                                                                                                                                                                                             | R      |                        |          |

| 03h   | Product<br>date code<br>ID |                                                                                                                                                                                                                                                                                                 | R      |                        |          |

| 05h   | Protocol ID                | Identifies the SVID Protocol the controller supports. 05h = IMVP8                                                                                                                                                                                                                               | R      | 05h                    | 05h      |

| 06h   | Capability                 | Informs the Master of the controller's Capabilities  Bit0 = Iout ADC (15h) = 1  Bit1 = Vout ADC (16h) = 0  Bit2 = Pout ADC (18h) = 0  Bit3 = I input ADC (19h) = 0  Bit4 = V input ADC (1Ah) = 1  Bit5 = P input ADC (1Bh) = 0  Bit6 = Temperature ADC (17h) = 1  Bit7 = 1 if (15h) is Iout = 1 | R      | D1h                    | N/A      |

| 10h   | Status_1                   | Data register read after the ALERT# signal is asserted. Conveying the status of the VR.                                                                                                                                                                                                         | R      | 00h                    | 00h      |

| 11h   | Status_2                   | Data register showing optional status_2 data.                                                                                                                                                                                                                                                   | R      | 00h                    | 00h      |

| 12h   | Temp zone                  | Data register showing temperature zones the system is operating in                                                                                                                                                                                                                              | R      | 00h                    | N/A      |

| 15h   | I_out                      | 8 bit binary word ADC of current. This register reads<br>0xFF when the output current is at Icc_Max                                                                                                                                                                                             | R      |                        | N/A      |

| 17h   | VR_Temp                    | 8 bit binary word ADC of voltage. Binary format in deg C, IE 100C=64h. A value of 00h indicates this function is not supported                                                                                                                                                                  | R      |                        | N/A      |

| 1Bh   | Input<br>Power             | Required for Input Power Domain Address 0Dh                                                                                                                                                                                                                                                     | R      | N/A                    |          |

| 1Ch   | Status2_la<br>st read      | When the status 2 register is read its contents are copied into this register. The format is the same as the Status 2 Register                                                                                                                                                                  | R      | 00h                    | N/A      |

| 21h   | Icc_Max                    | Data register containing the lcc_Max the platform supports. The value is measured on the ICCMAX pin on power up and placed in this register. From that point on the register is read only                                                                                                       | R      | 00h                    | N/A      |

| 22h   | Temp_Max                   | Data register containing the max temperature the plat-<br>form supports and the level VR_hot asserts. This value<br>defaults to 100°C and programmable over the SVID In-<br>terface                                                                                                             | R/W    | 64h                    | N/A      |

| 24h   | SR_fast                    | Slew Rate for SetVID_fast commands. Binary format in mV/us                                                                                                                                                                                                                                      | R      | 1Eh                    | N/A      |

| 25h   | SR_slow                    | Slew Rate for SetVID_slow commands. Determined by SR_Slow selector register (2Ah)                                                                                                                                                                                                               | R      | 0Fh                    | N/A      |

Table 7. (continued)

| Index | Name                                          | Description                                                                                                                                                                                                                                                                                  | Access | Default<br>00h/01h/02h | PSYS 0Dh |

|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|----------|

| 26h   | Vboot                                         | Vboot is resistor programmed at startup. The controller will ramp to Vboot and hold at Vboot until it receives a new SetVID command to move to a different voltage.                                                                                                                          | R      | 00h                    | N/A      |

| 2Ah   | SR_Slow<br>selector                           | Fast_SR/2: default Fast_SR/4 Fast_SR/8 Fast_SR/16                                                                                                                                                                                                                                            | R/W    | 01h                    | N/A      |

| 2Bh   | PS4 exit<br>latency                           | Reflects the latency of exiting PS4 state. The exit latency is defined as the time duration, in µs, from the ACK of the SETVID Slow/Fast command to the output voltage beginning to ramp                                                                                                     | R      | 8Ch                    | N/A      |

| 2Ch   | PS3 exit<br>latency                           | Reflects the latency of exiting PS3 state. The exit latency is defined as the time duration, in µs, from the ACK of the SETVID/SetPS command until the controller is capable of supplying max current of the command PS state                                                                | R      | 55h                    | N/A      |

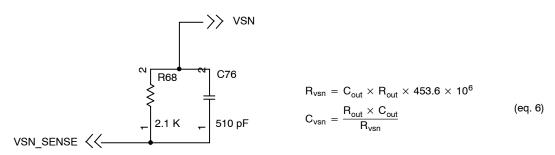

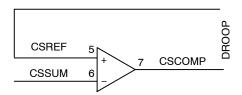

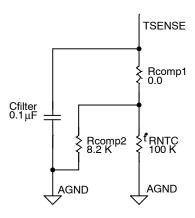

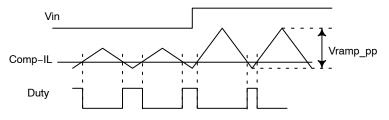

| 2Dh   | EN to<br>Ready for<br>SVID<br>command<br>(TA) | Reflects the latency from enable assertion to the VR controller being ready to accept SVID commands                                                                                                                                                                                          | R      | CAh                    | N/A      |