# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

- Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

- Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

- Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these

materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

Hitachi Single-Chip Microcomputer

H8/3217 Series

H8/3217, H8/3216

H8/3214, H8/3212

H8/3202

Hardware Manual

## **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from

accidents or any other reasons during operation of the user's unit according to this

document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## **Preface**

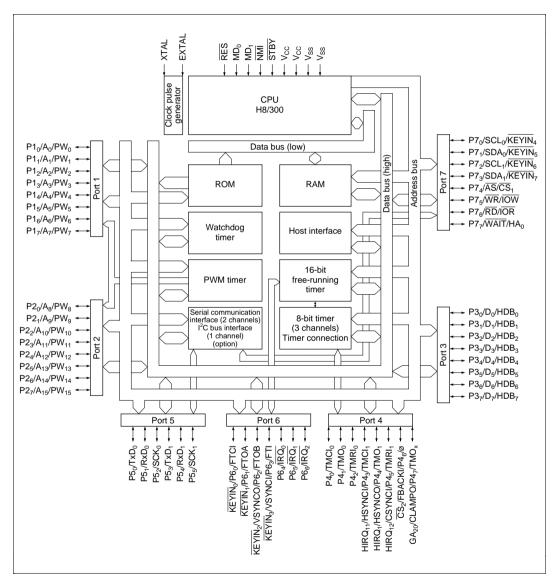

The H8/3217 Series is a family of high-performance single-chip microcomputers ideally suited for embedded control of industrial equipment. The chips are built around an H8/300 CPU core: a high-speed processor. On-chip supporting modules provide ROM, RAM, four types of timers, I/O ports, a serial communication interface, I<sup>2</sup>C bus interface, and host interface for easy implementation of compact, high-speed control systems.

The H8/3217 Series offers a selection of on-chip memory.

H8/3217: 60-kbyte ROM; 2-kbyte RAM H8/3216: 48-kbyte ROM; 2-kbyte RAM H8/3214: 32-kbyte ROM; 1-kbyte RAM H8/3212: 16-kbyte ROM; 512-byte RAM

The H8/3217 and H8/3214 chips are available with electrically programmable ROM. Manufacturers can use the electrically programmable ZTAT<sup>TM</sup> (Zero Turn-Around Time\*) version to get production off to a fast start and make software changes quickly.

This manual describes the H8/3217 Series hardware. Refer to the *H8/300 Series Programming Manual* for a detailed description of the instruction set.

Note: \* ZTAT is a trademark of Hitachi, Ltd.

# Contents

| Sect | ion 1  | Overview                               | 1  |

|------|--------|----------------------------------------|----|

| 1.1  | Overv  | riew                                   | 1  |

| 1.2  | Block  | Diagram                                | 6  |

| 1.3  | Pin A  | ssignments and Functions               | 7  |

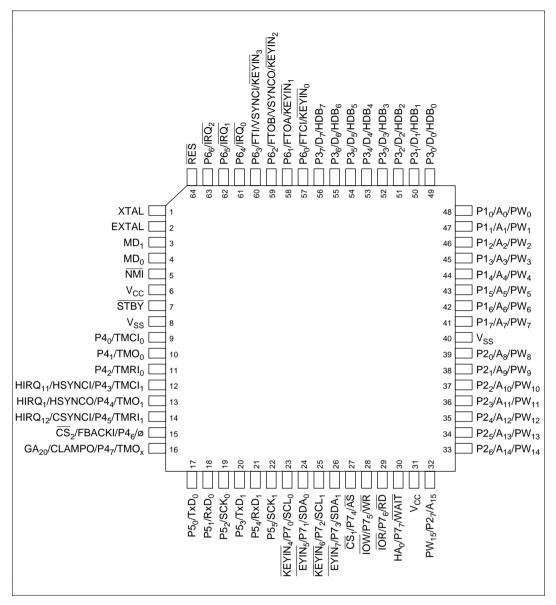

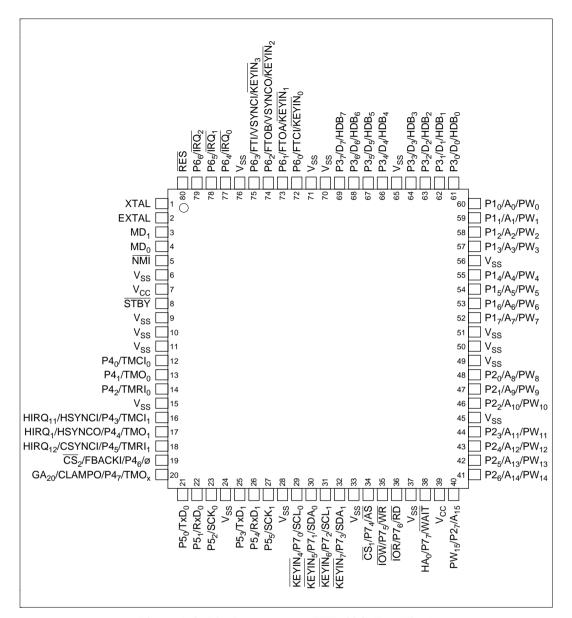

|      | 1.3.1  | Pin Arrangement                        | 7  |

|      | 1.3.2  | Pin Functions                          | 10 |

| Sect | ion 2  | CPU                                    | 25 |

| 2.1  | Overv  | view                                   | 25 |

|      | 2.1.1  | Features                               | 25 |

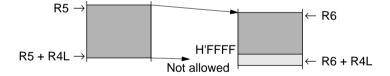

|      | 2.1.2  | Address Space                          | 26 |

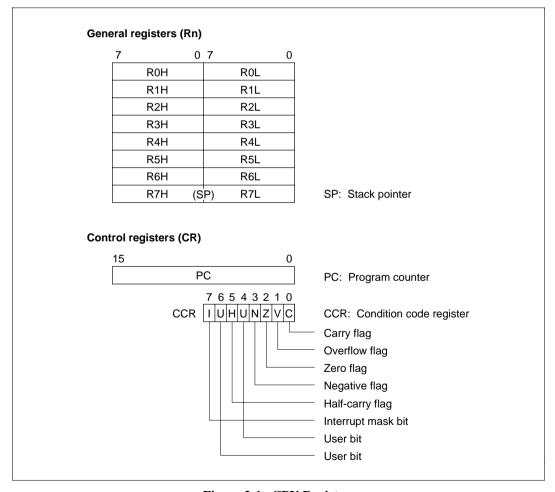

|      | 2.1.3  | Register Configuration                 | 26 |

| 2.2  | Regis  | ter Descriptions                       | 27 |

|      | 2.2.1  | General Registers                      | 27 |

|      | 2.2.2  | Control Registers                      | 27 |

|      | 2.2.3  | Initial Register Values                | 28 |

| 2.3  | Data l | Formats                                | 29 |

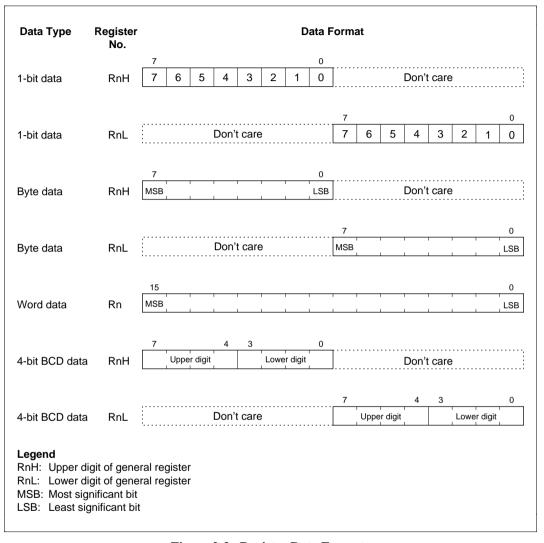

|      | 2.3.1  | Data Formats in General Registers      | 30 |

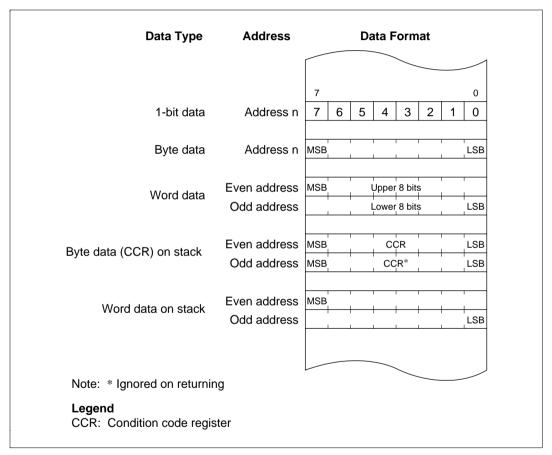

|      | 2.3.2  | Memory Data Formats                    | 31 |

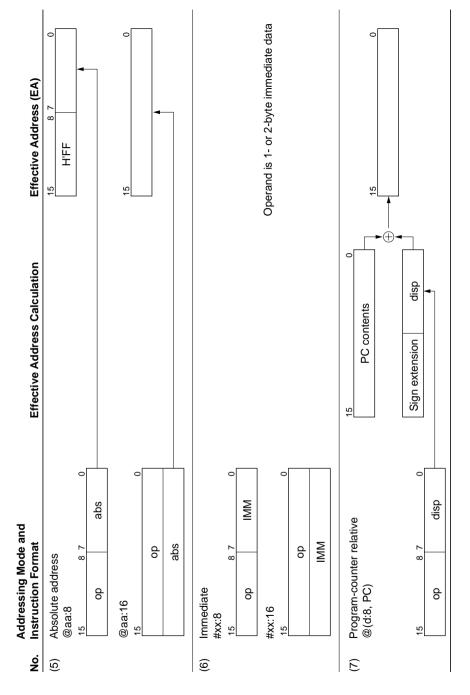

| 2.4  | Addre  | essing Modes                           | 32 |

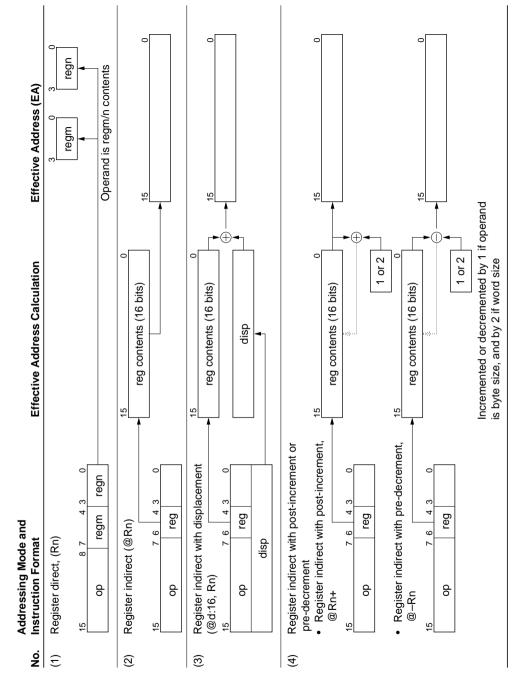

|      | 2.4.1  | Addressing Modes                       | 32 |

|      | 2.4.2  | Effective Address Calculation          | 33 |

| 2.5  | Instru | ction Set                              | 37 |

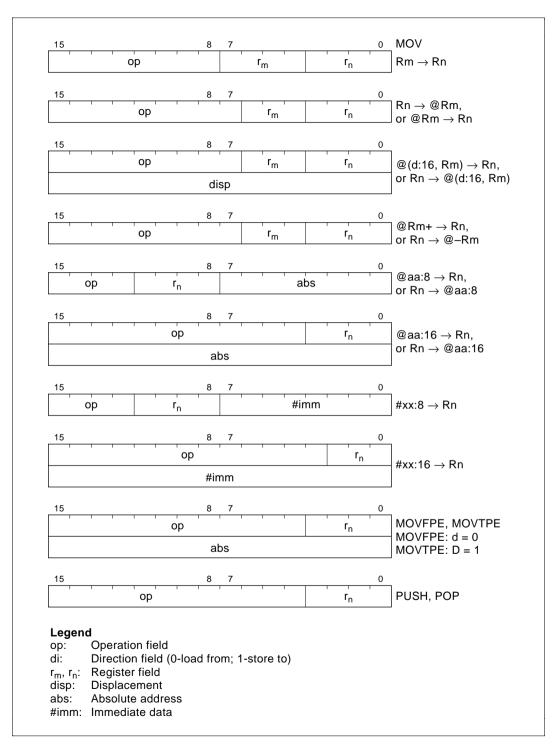

|      | 2.5.1  | Data Transfer Instructions             | 39 |

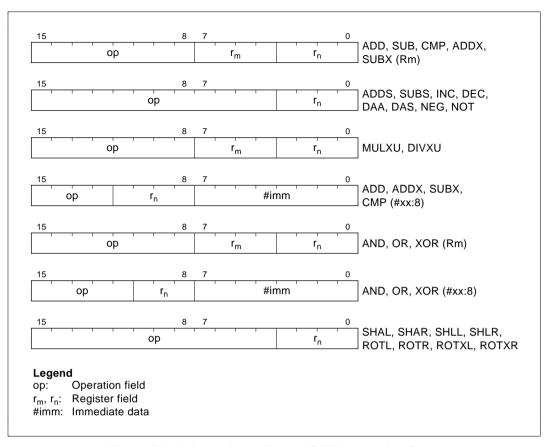

|      | 2.5.2  | Arithmetic Operations                  | 41 |

|      | 2.5.3  | Logic Operations                       | 42 |

|      | 2.5.4  | Shift Operations                       | 42 |

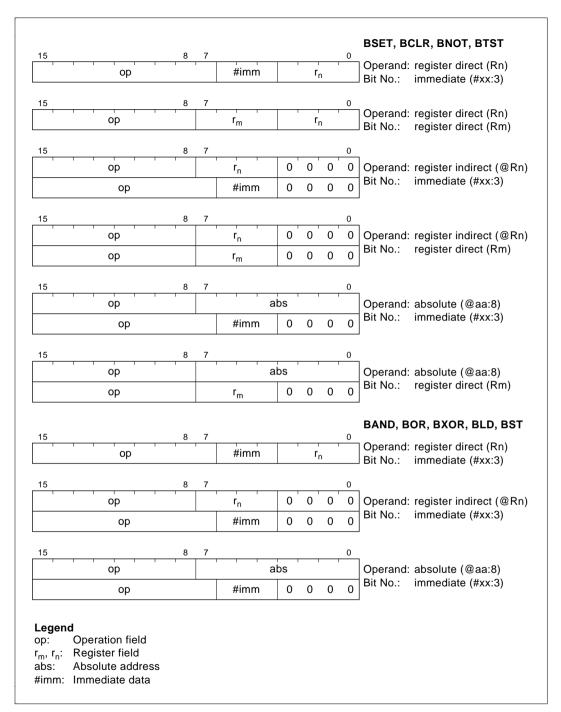

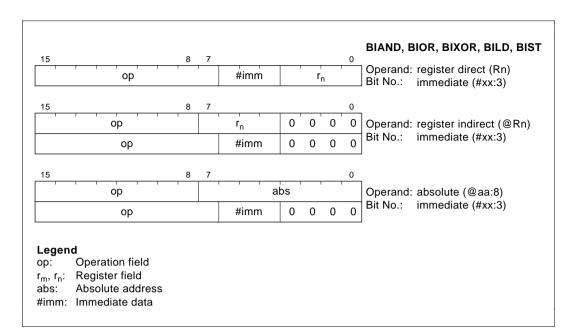

|      | 2.5.5  | Bit Manipulations                      | 44 |

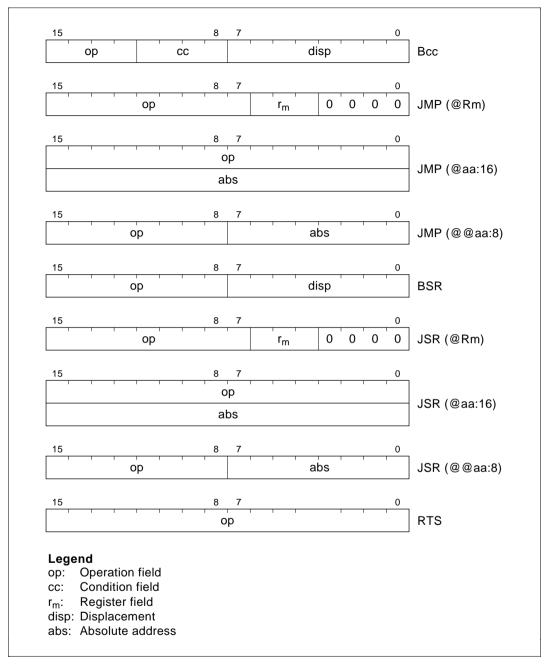

|      | 2.5.6  | Branching Instructions                 | 49 |

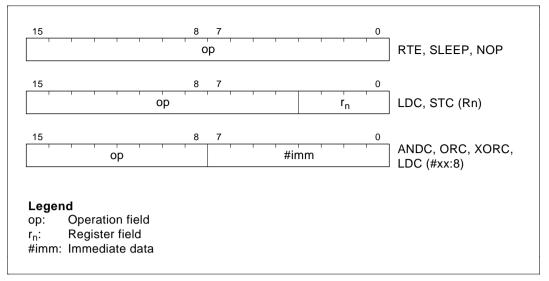

|      | 2.5.7  | System Control Instructions            | 51 |

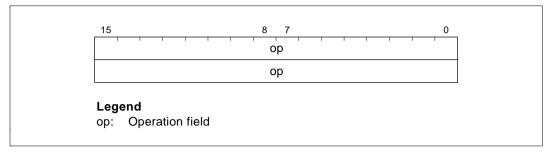

|      | 2.5.8  | Block Data Transfer Instruction        | 52 |

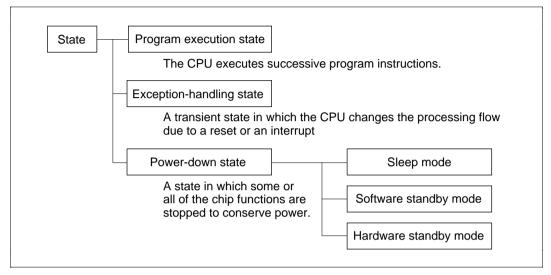

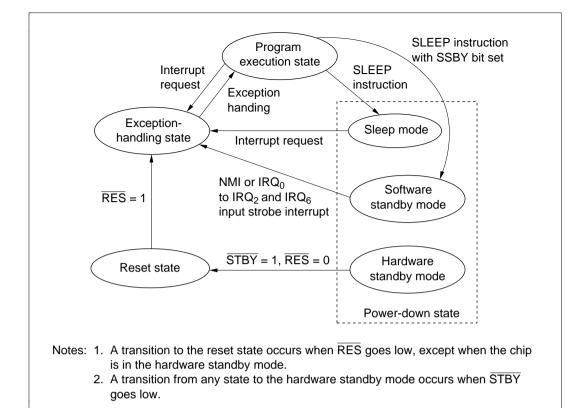

| 2.6  | CPU :  | States                                 | 54 |

|      | 2.6.1  | Program Execution State                | 55 |

|      | 2.6.2  | Exception-Handling State               | 55 |

|      | 2.6.3  | Power-Down State                       | 56 |

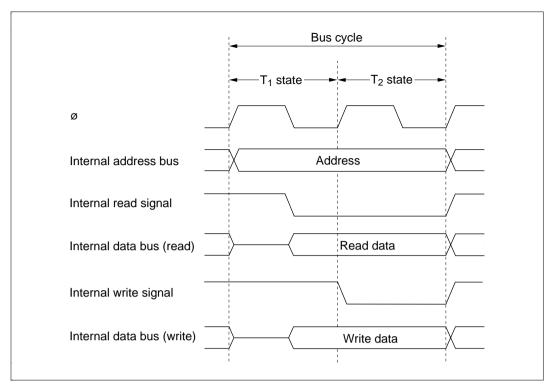

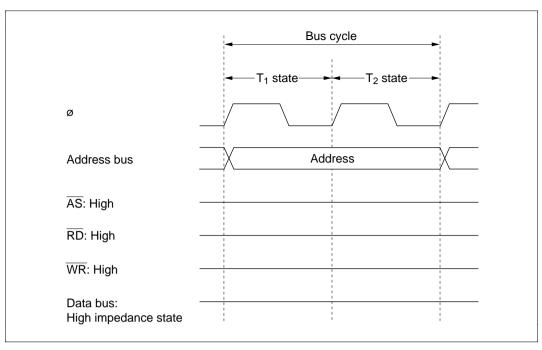

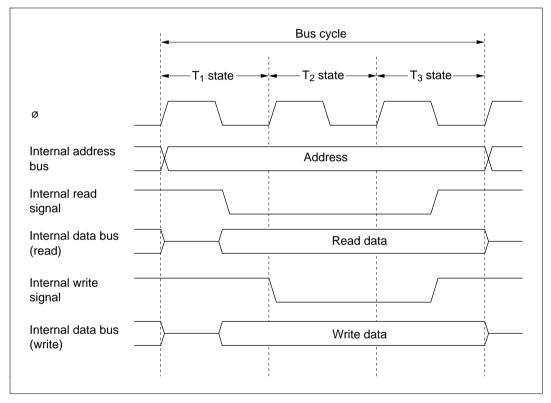

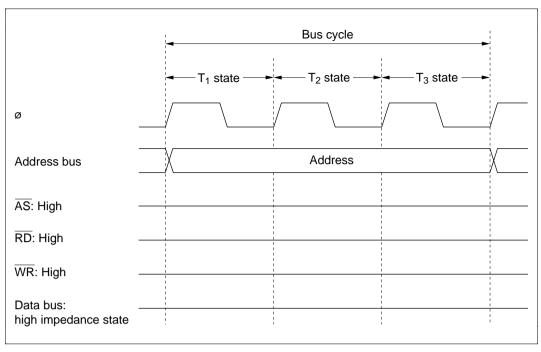

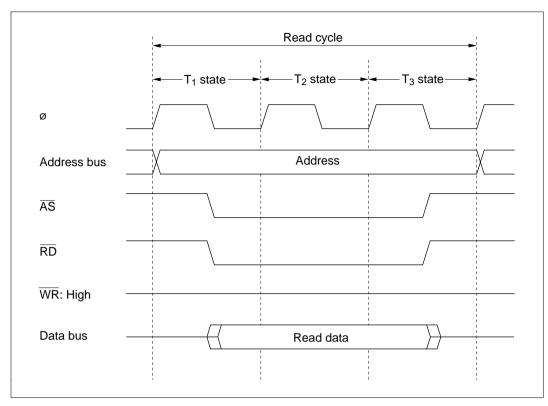

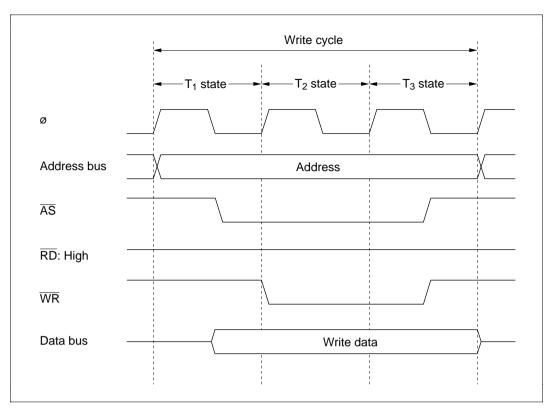

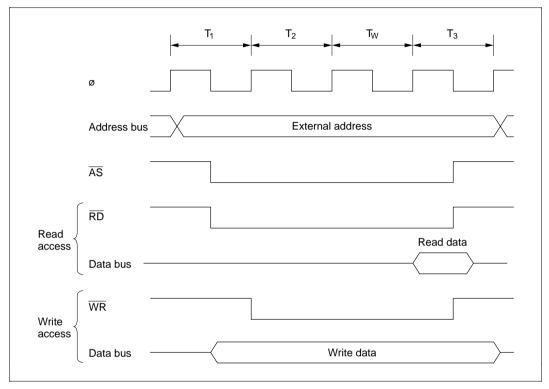

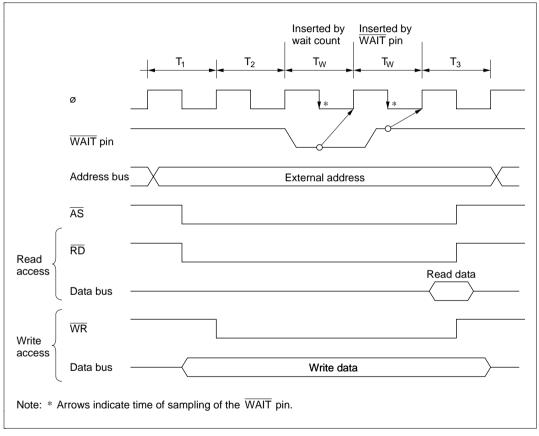

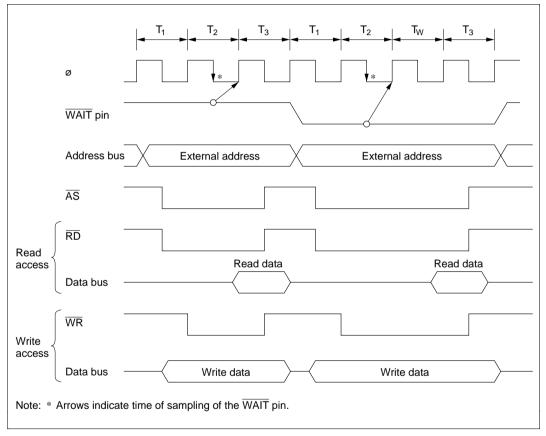

| 2.7  | Acces  | ss Timing and Bus Cycle                | 56 |

|      | 2.7.1  | Access to On-Chip Memory (RAM and ROM) |    |

|      | 2.7.2  |                                        |    |

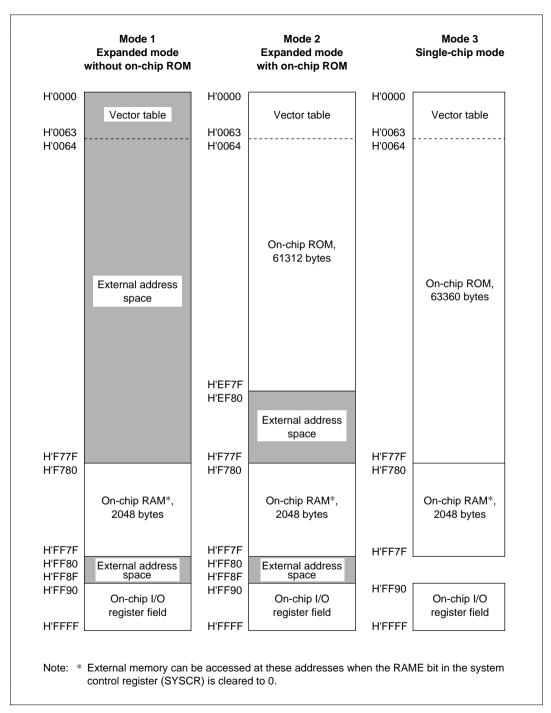

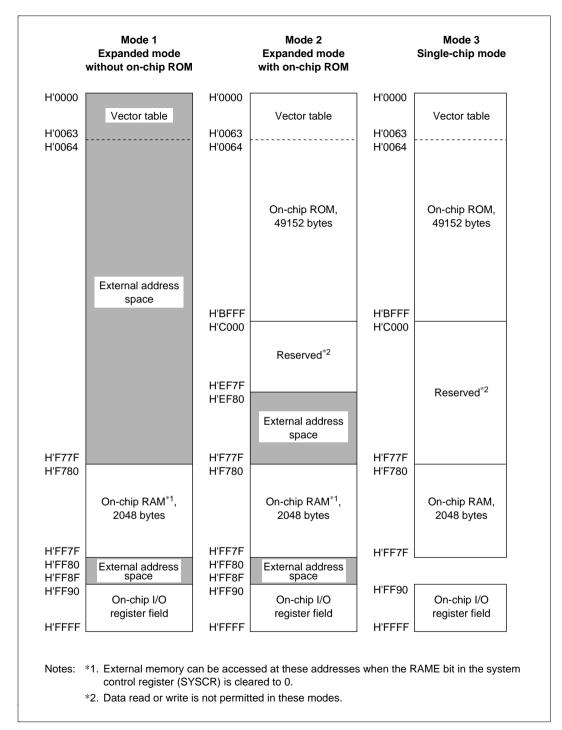

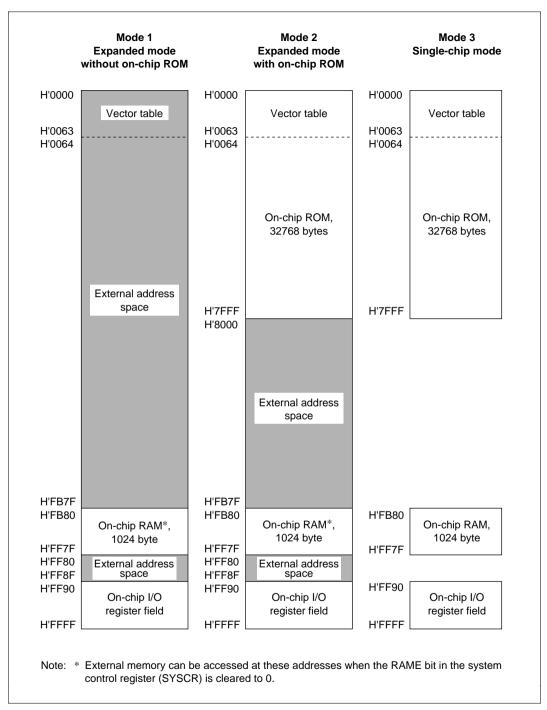

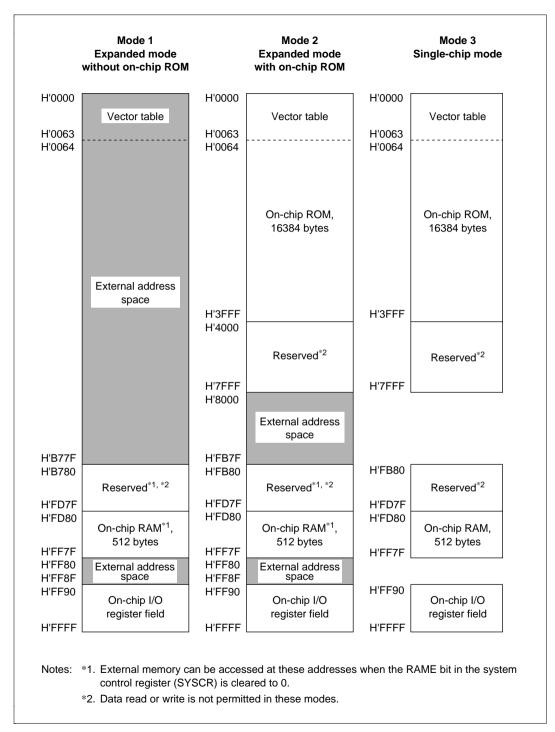

| Sect       | ion 3 MCU Operating Modes and Address Space | 63  |  |

|------------|---------------------------------------------|-----|--|

| 3.1        | Overview                                    | 63  |  |

|            | 3.1.1 Operating Modes                       | 63  |  |

|            | 3.1.2 Mode and System Control Registers     | 63  |  |

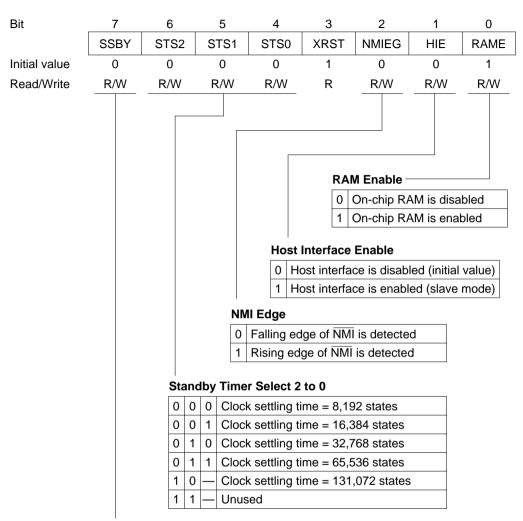

| 3.2        | System Control Register (SYSCR)             | 64  |  |

| 3.3        | Mode Control Register (MDCR)                |     |  |

| 3.4        | Mode Descriptions                           | 66  |  |

| 3.5        | Address Space Maps for Each Operating Mode  | 67  |  |

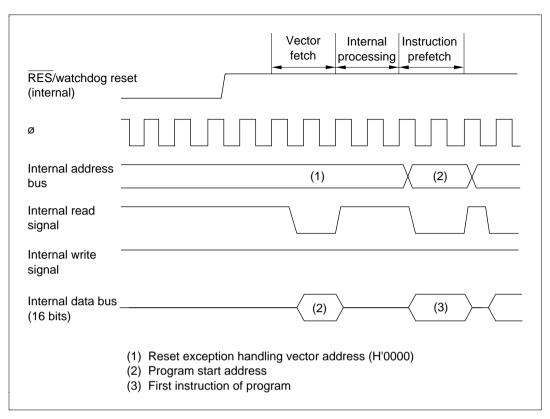

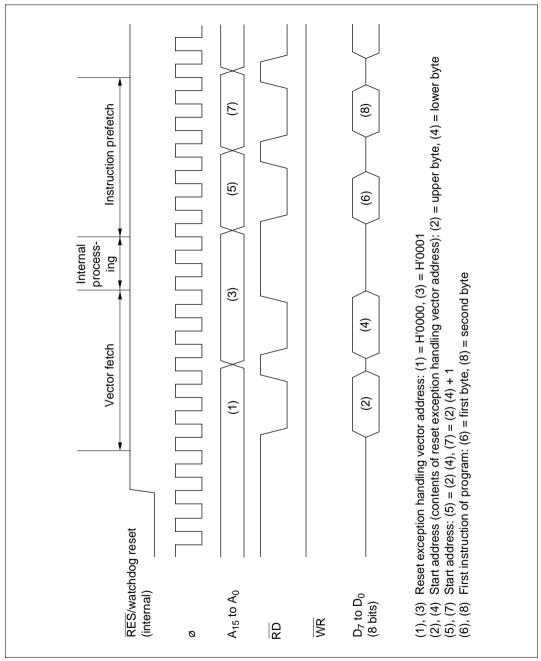

| Sect       | ion 4 Exception Handling                    | 73  |  |

| 4.1        | Overview                                    | 73  |  |

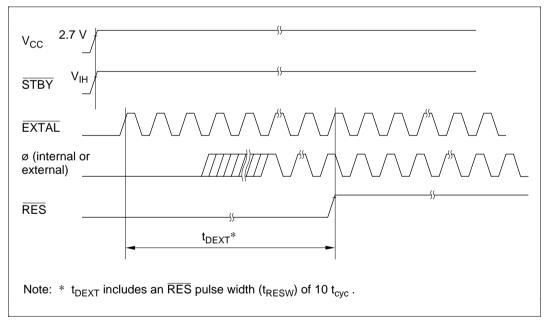

| 4.2        | Reset                                       | 73  |  |

|            | 4.2.1 Overview                              | 73  |  |

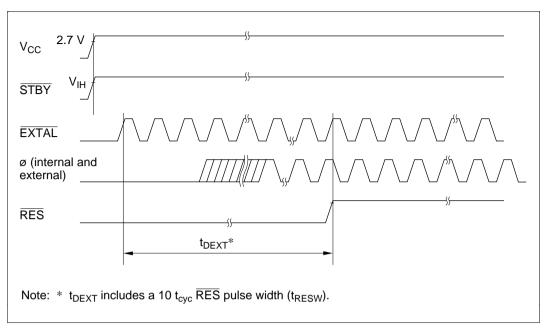

|            | 4.2.2 Reset Sequence                        | 74  |  |

|            | 4.2.3 Disabling of Interrupts after Reset   | 77  |  |

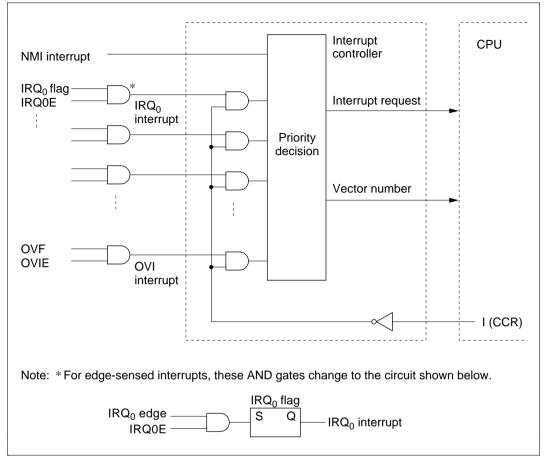

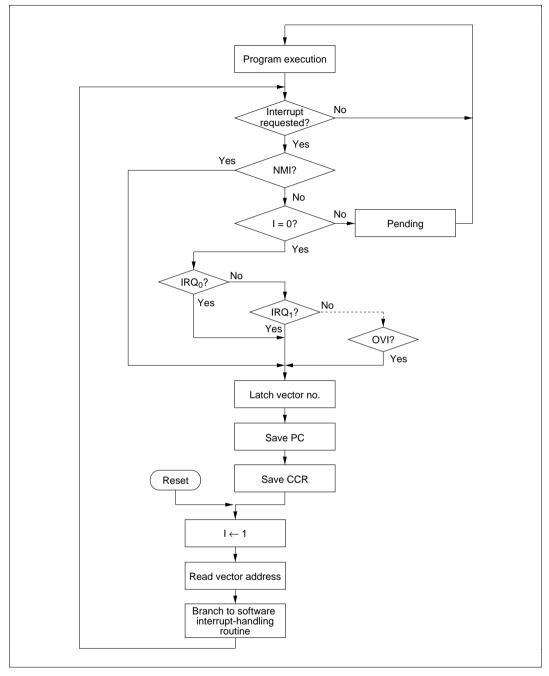

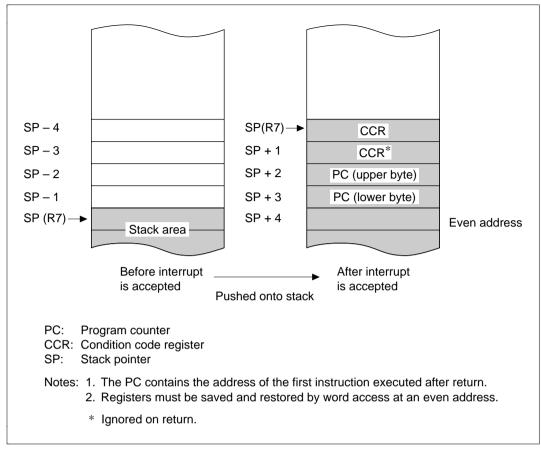

| 4.3        | Interrupts                                  | 77  |  |

| 1.0        | 4.3.1 Overview                              | 77  |  |

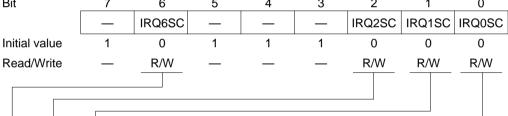

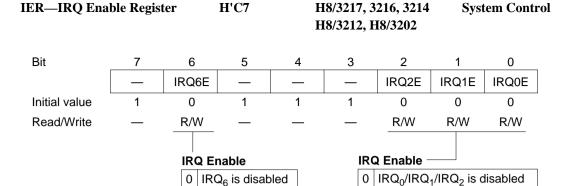

|            | 4.3.2 Interrupt-Related Registers           | 79  |  |

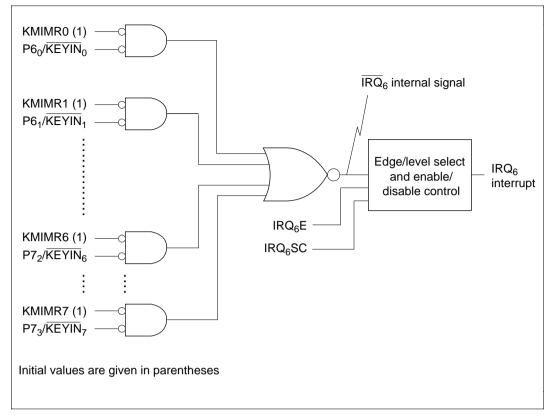

|            | 4.3.3 External Interrupts                   | 82  |  |

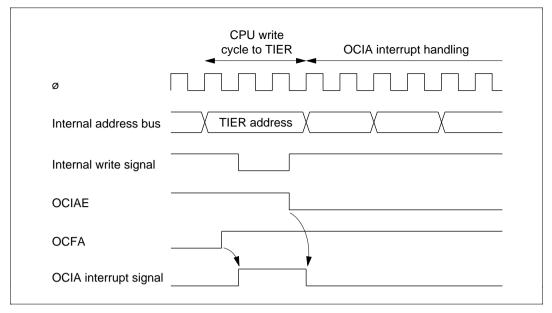

|            | 4.3.4 Internal Interrupts                   | 83  |  |

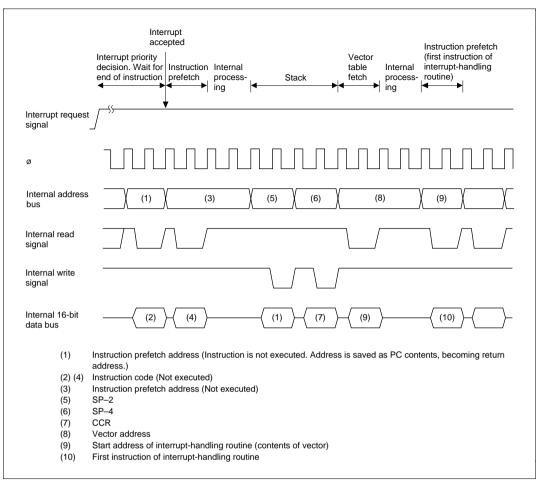

|            | 4.3.5 Interrupt Handling                    | 83  |  |

|            | 4.3.6 Interrupt Response Time               | 89  |  |

|            | 4.3.7 Precaution                            | 89  |  |

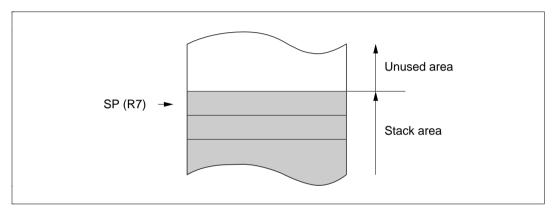

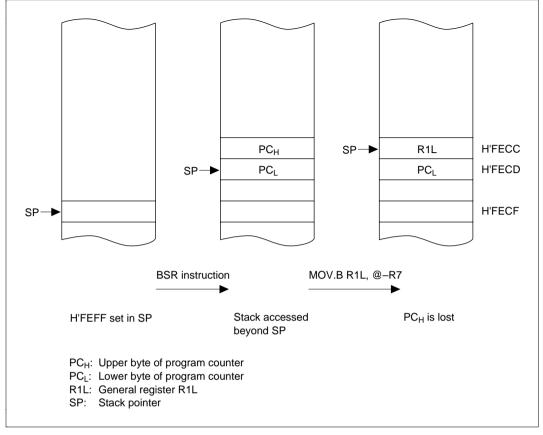

| 4.4        | Note on Stack Handling.                     | 90  |  |

| 4.5        | Notes on the Use of Key-Sense Interrupts    | 91  |  |

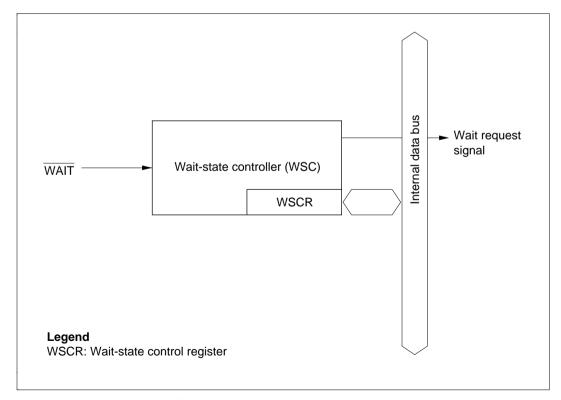

| Sact       | ion 5 Wait-State Controller                 | 93  |  |

| 5.1        |                                             | 93  |  |

| 5.1        | Overview                                    | 93  |  |

|            | 5.1.1 Features                              |     |  |

|            | 5.1.2 Block Diagram                         | 93  |  |

|            | 5.1.3 Input/Output Pins                     | 94  |  |

| <i>5</i> 2 | 5.1.4 Register Configuration                | 94  |  |

| 5.2        | Register Description (NGCP)                 | 94  |  |

| <b>5</b> 0 | 5.2.1 Wait-State Control Register (WSCR)    | 94  |  |

| 5.3        | Wait Modes                                  | 96  |  |

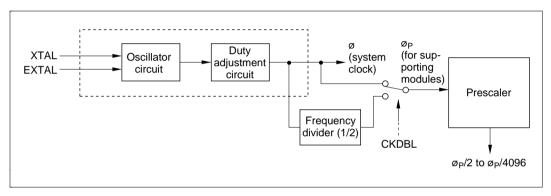

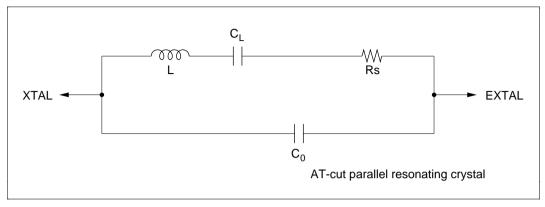

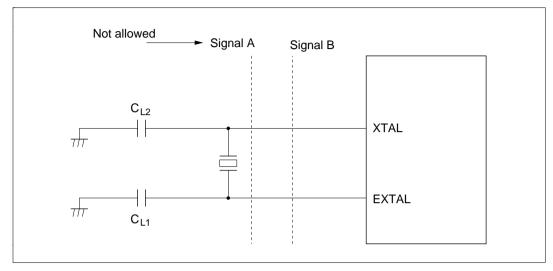

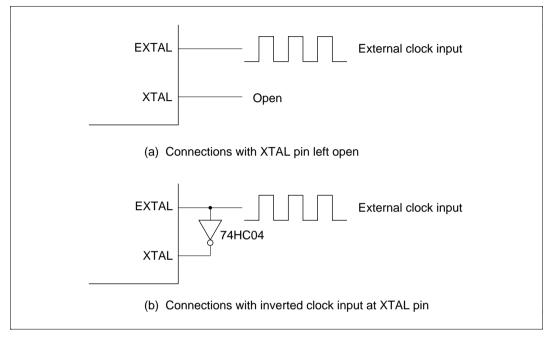

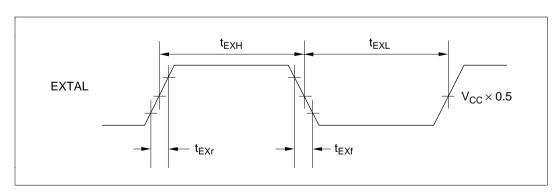

|            | ion 6 Clock Pulse Generator                 | 99  |  |

| 6.1        | Overview                                    | 99  |  |

|            | 6.1.1 Block Diagram                         | 99  |  |

|            |                                             | 100 |  |

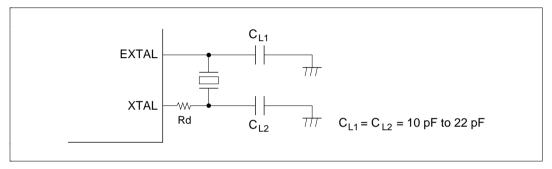

| 6.2        | Oscillator Circuit                          | 101 |  |

| 6.3        | Duty Adjustment Circuit                     | 107 |  |

| 6.4        | Prescaler                                   | 107 |  |

| Secti | on 7   | I/O Ports                                               | 109 |

|-------|--------|---------------------------------------------------------|-----|

| 7.1   | Overv  | ew                                                      | 109 |

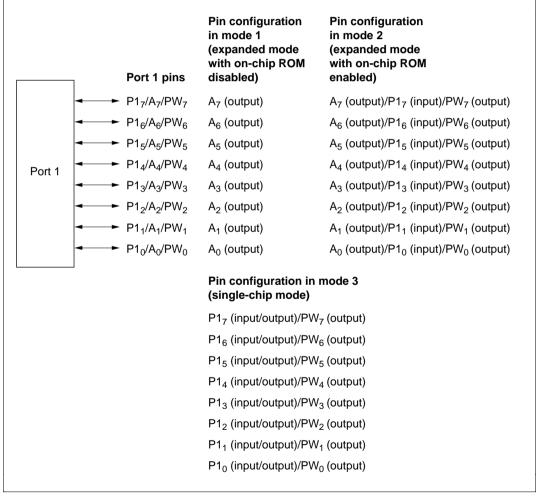

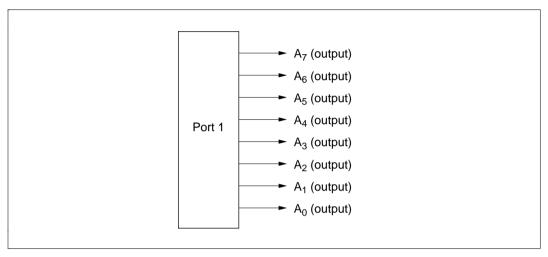

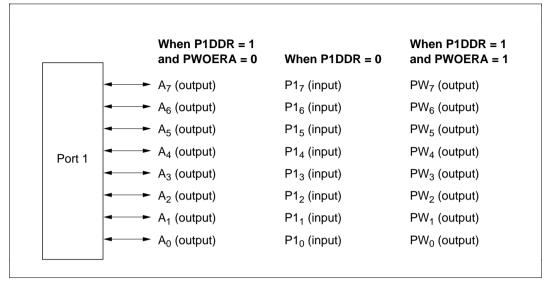

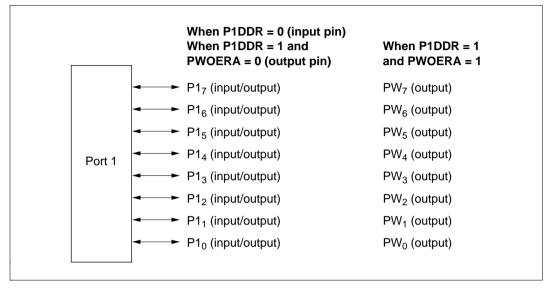

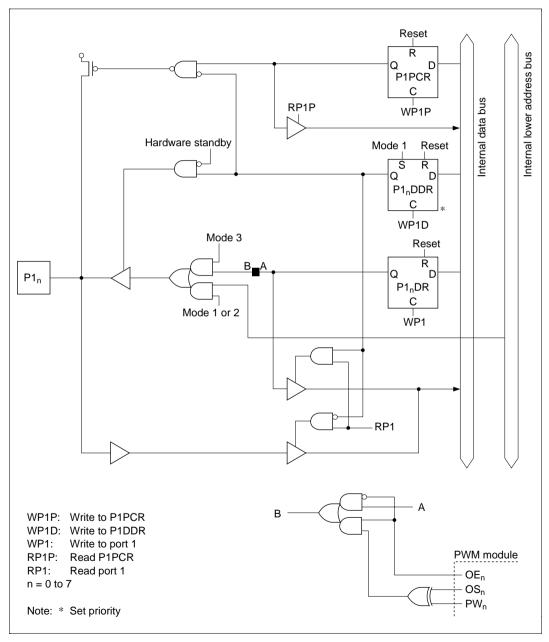

| 7.2   | Port 1 |                                                         | 116 |

|       | 7.2.1  | Overview                                                | 116 |

|       | 7.2.2  | Register Configuration and Descriptions                 | 117 |

|       | 7.2.3  | Pin Functions in Each Mode                              | 119 |

|       | 7.2.4  | MOS Input Pull-Ups                                      | 122 |

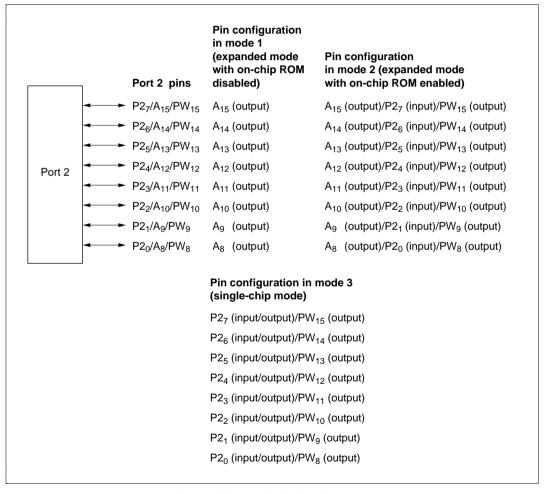

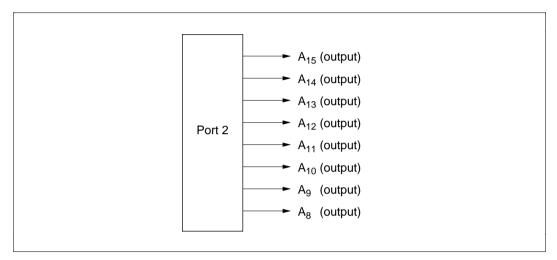

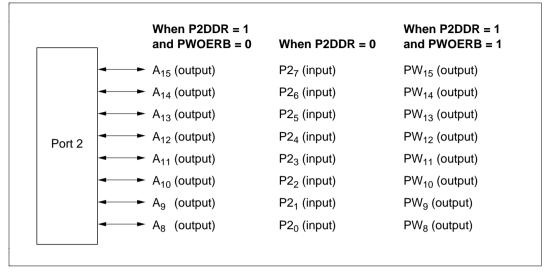

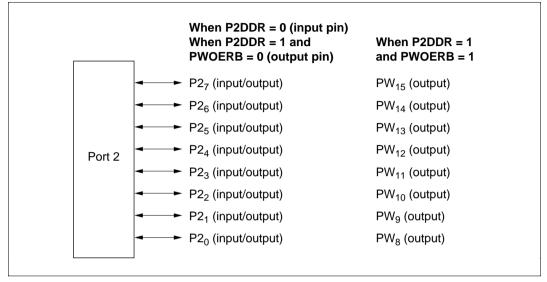

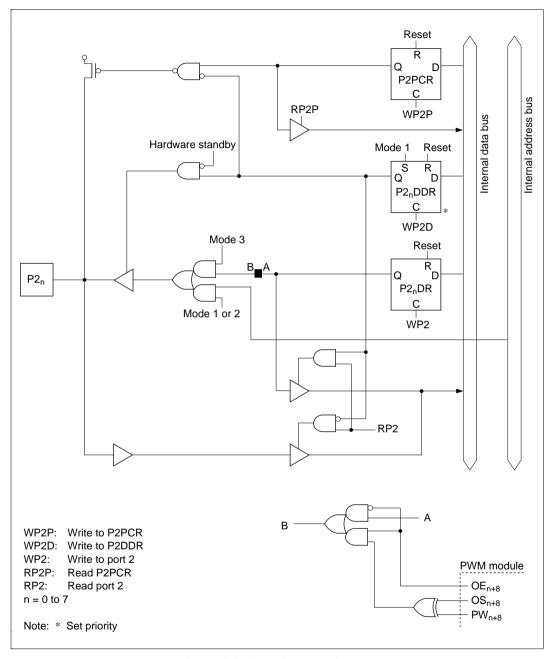

| 7.3   | Port 2 |                                                         | 123 |

|       | 7.3.1  | Overview                                                | 123 |

|       | 7.3.2  | Register Configuration and Descriptions                 | 124 |

|       | 7.3.3  | Pin Functions in Each Mode                              | 126 |

|       | 7.3.4  | MOS Input Pull-Ups                                      | 129 |

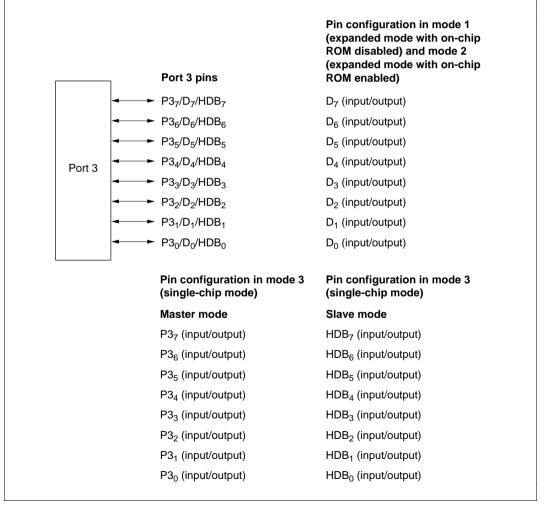

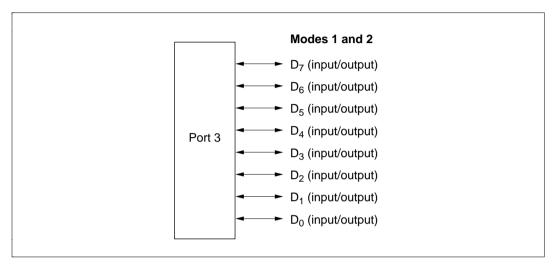

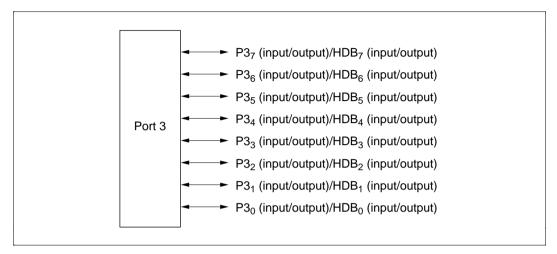

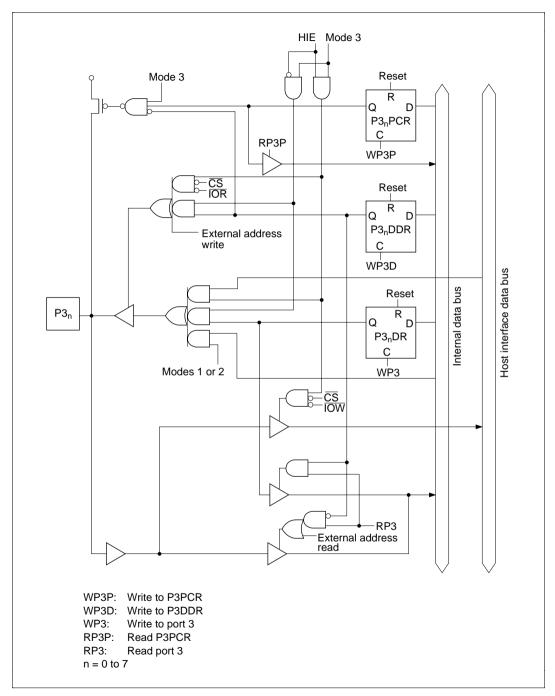

| 7.4   | Port 3 |                                                         | 130 |

|       | 7.4.1  | Overview                                                | 130 |

|       | 7.4.2  | Register Configuration and Descriptions                 | 131 |

|       | 7.4.3  | Pin Functions in Each Mode                              | 133 |

|       | 7.4.4  | Input Pull-Up Transistors                               | 134 |

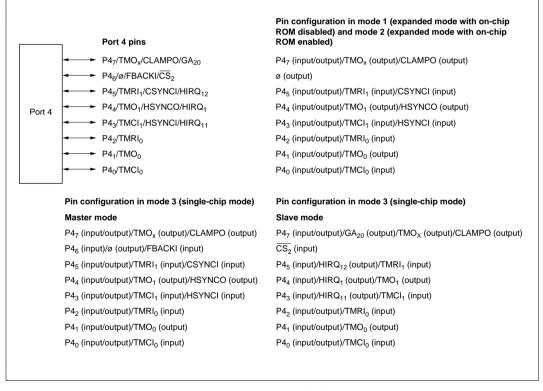

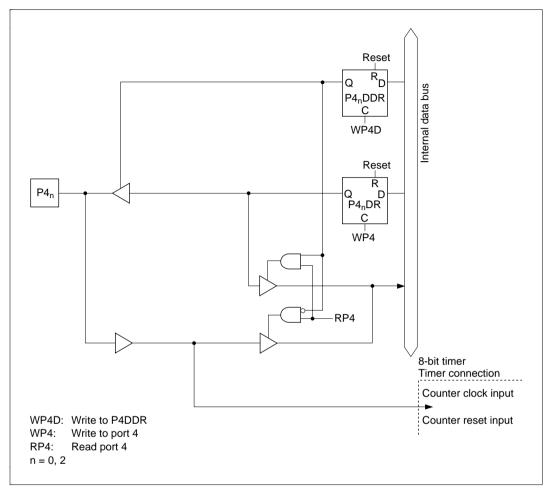

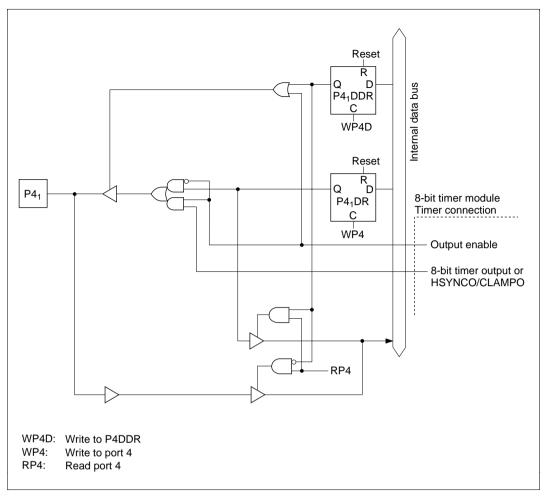

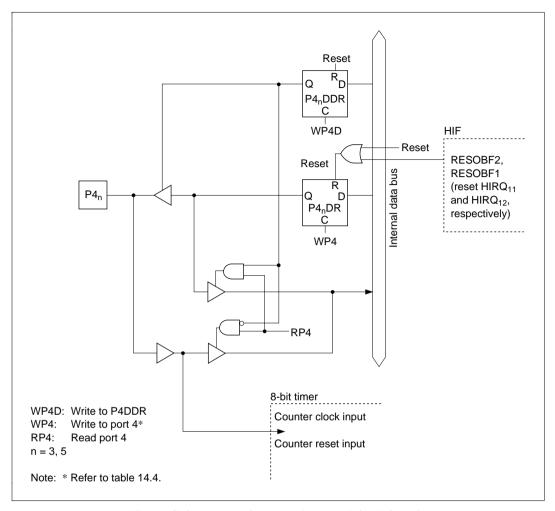

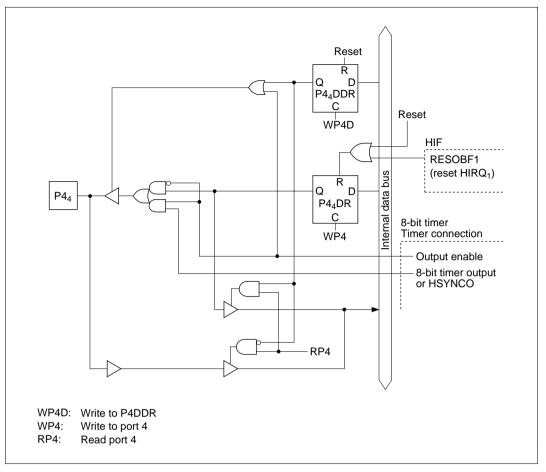

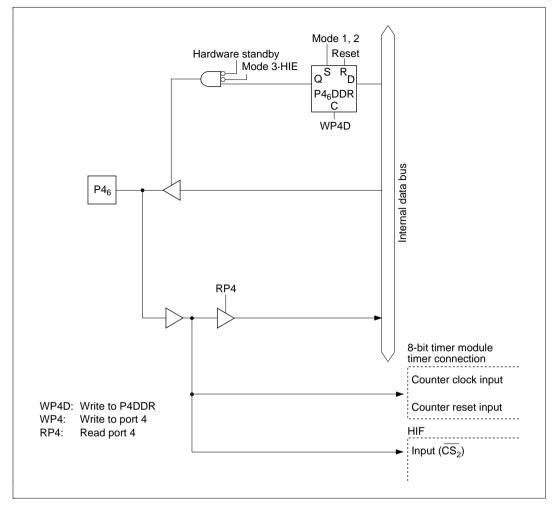

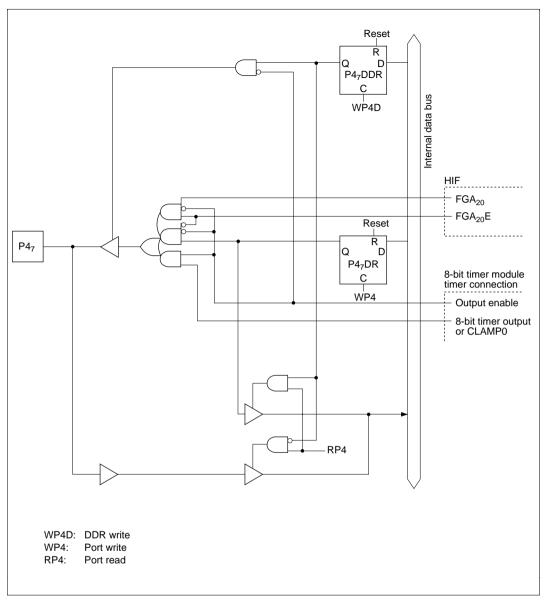

| 7.5   | Port 4 |                                                         | 135 |

|       | 7.5.1  | Overview                                                | 135 |

|       | 7.5.2  | Register Configuration and Descriptions                 | 136 |

|       | 7.5.3  | Pin Functions                                           | 138 |

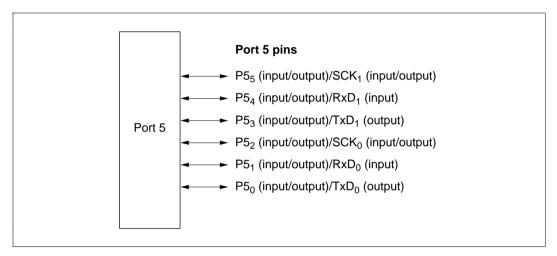

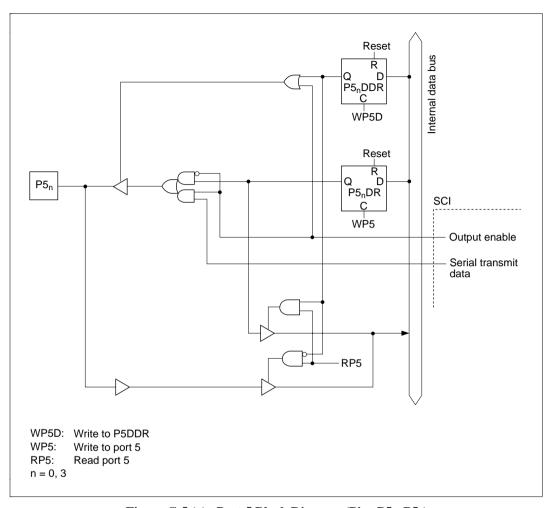

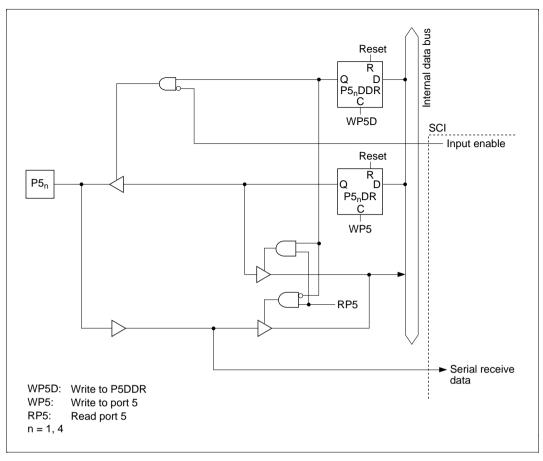

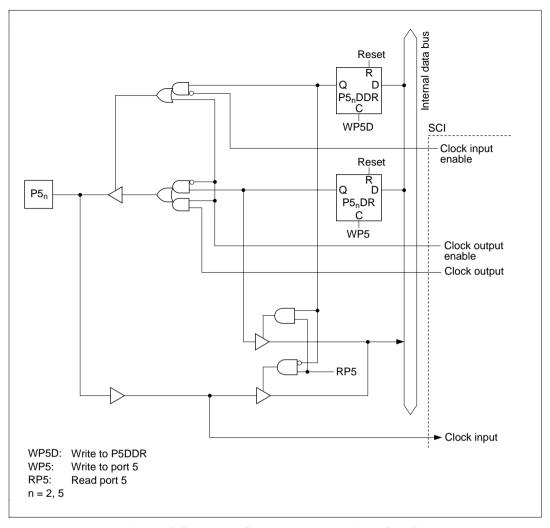

| 7.6   | Port 5 |                                                         | 141 |

|       | 7.6.1  | Overview                                                | 141 |

|       | 7.6.2  | Register Configuration and Descriptions                 | 141 |

|       | 7.6.3  | Pin Functions                                           | 143 |

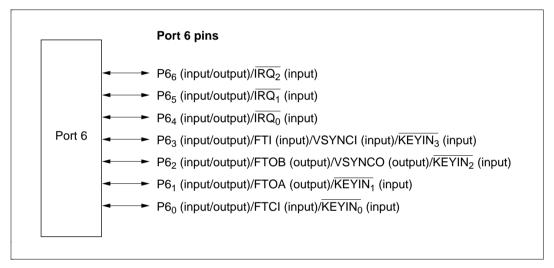

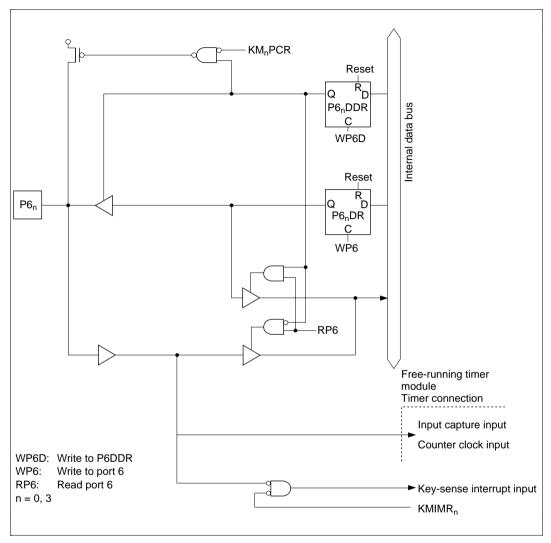

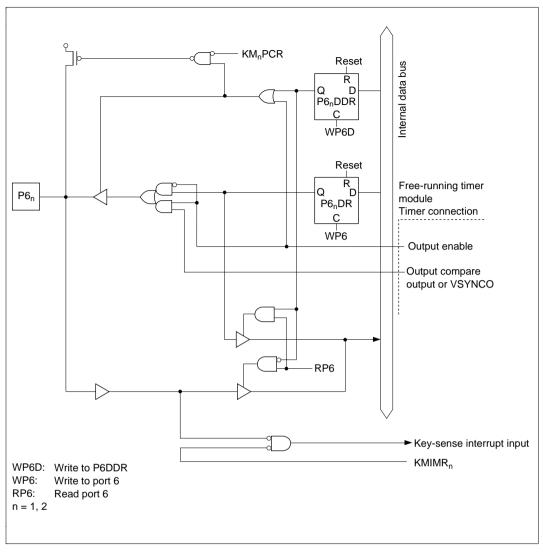

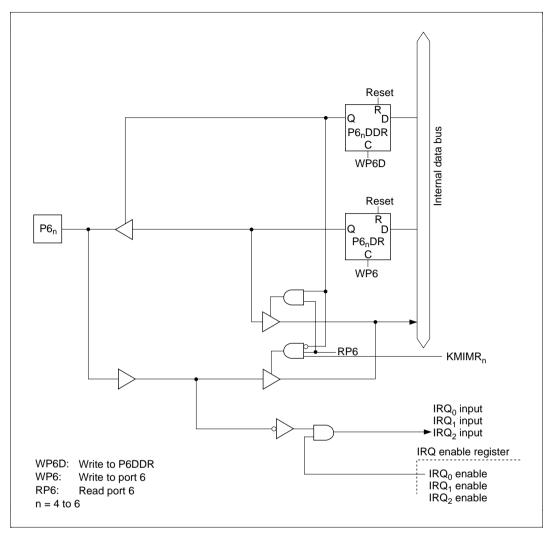

| 7.7   | Port 6 |                                                         | 145 |

|       | 7.7.1  | Overview                                                | 145 |

|       | 7.7.2  | Register Configuration and Descriptions                 | 146 |

|       | 7.7.3  | Pin Functions                                           | 148 |

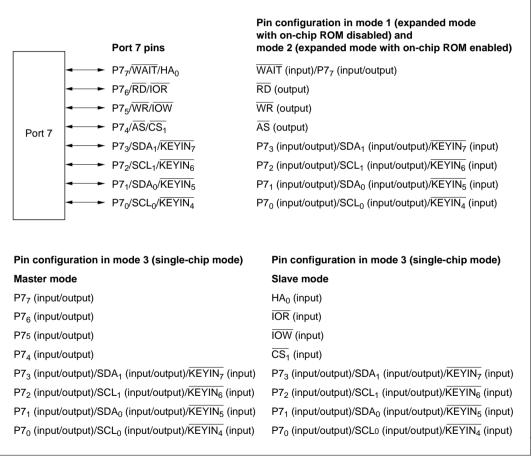

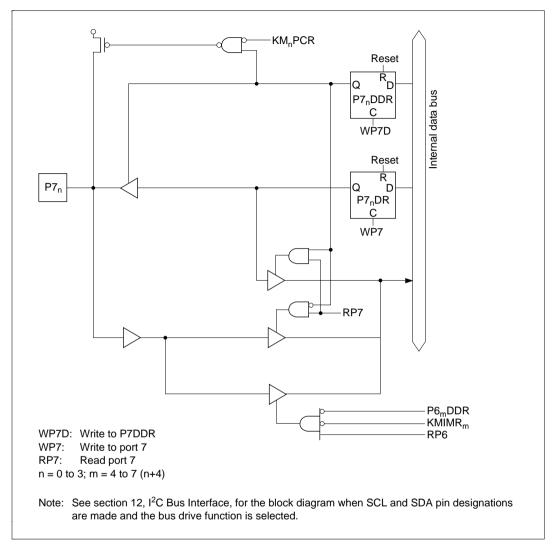

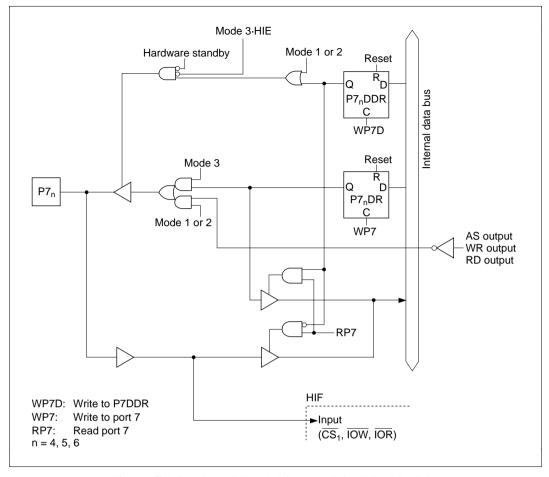

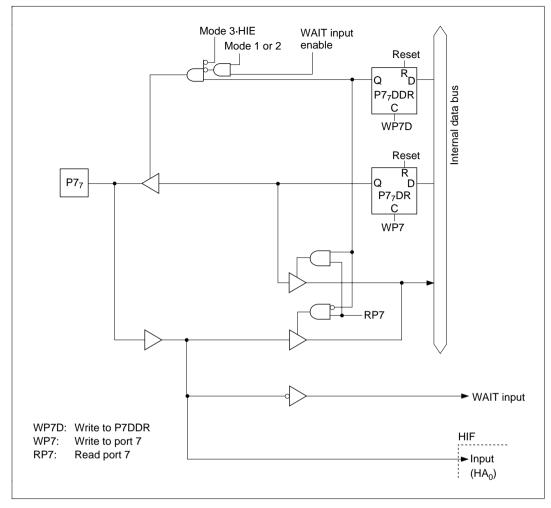

| 7.8   | Port 7 |                                                         | 150 |

|       | 7.8.1  | Overview                                                | 150 |

|       | 7.8.2  | Register Configuration and Descriptions                 | 151 |

|       | 7.8.3  | Pin Functions                                           | 153 |

|       |        |                                                         |     |

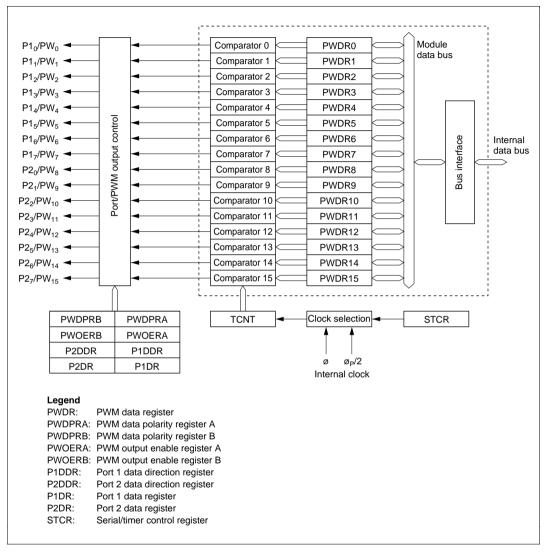

| Secti | on 8   | PWM Timers                                              | 157 |

| 8.1   | Overv  | ew                                                      | 157 |

|       | 8.1.1  | Features                                                | 157 |

|       | 8.1.2  | Block Diagram                                           | 158 |

|       | 8.1.3  | Input and Output Pins                                   | 159 |

|       | 8.1.4  | Register Configuration                                  | 160 |

| 8.2   |        | er Descriptions                                         | 161 |

|       | 8.2.1  | PWM Data Registers (PWDR0 to PWDR15)                    | 161 |

|       | 8.2.2  | PWM Data Polarity Registers A and B (PWDPRA and PWDPRB) | 161 |

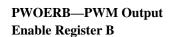

|      | 8.2.3   | PWM Output Enable Registers A and B (PWOERA and PWOERB)            | 162 |

|------|---------|--------------------------------------------------------------------|-----|

|      | 8.2.4   | Port 1 Data Direction Register (P1DDR)                             |     |

|      | 8.2.5   | Port 2 Data Direction Register (P2DDR)                             |     |

|      | 8.2.6   | Port 1 Data Register (P1DR)                                        |     |

|      | 8.2.7   | Port 2 Data Register (P2DR)                                        |     |

|      | 8.2.8   | Serial/Timer Control Register (STCR)                               |     |

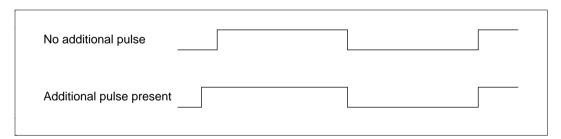

| 8.3  | Operati | on                                                                 |     |

|      | 8.3.1   | Correspondence between PWM Data Register Contents and              |     |

|      |         | Output Waveform                                                    | 166 |

|      |         |                                                                    |     |

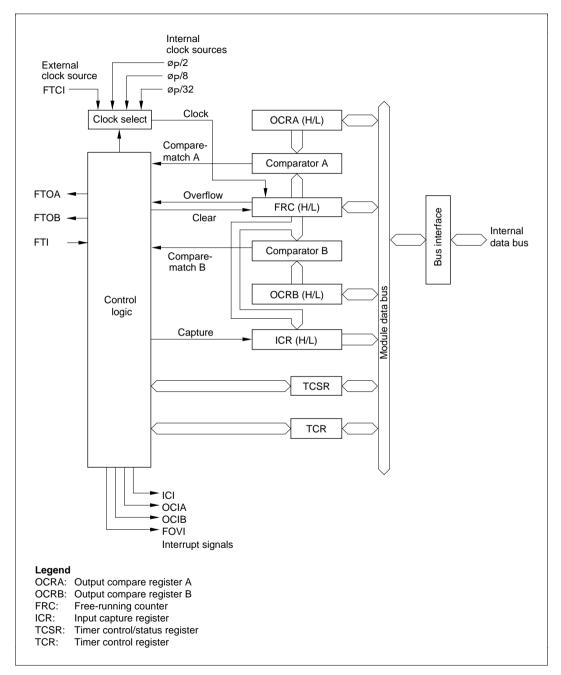

| Sect | ion 9   | 16-Bit Free-Running Timer                                          | 169 |

| 9.1  | Overvi  | ew                                                                 | 169 |

|      | 9.1.1   | Features                                                           | 169 |

|      | 9.1.2   | Block Diagram                                                      | 170 |

|      | 9.1.3   | Input and Output Pins                                              | 171 |

|      | 9.1.4   | Register Configuration                                             | 171 |

| 9.2  | Registe | r Descriptions                                                     | 172 |

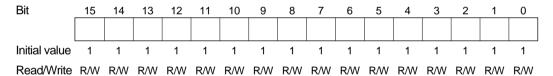

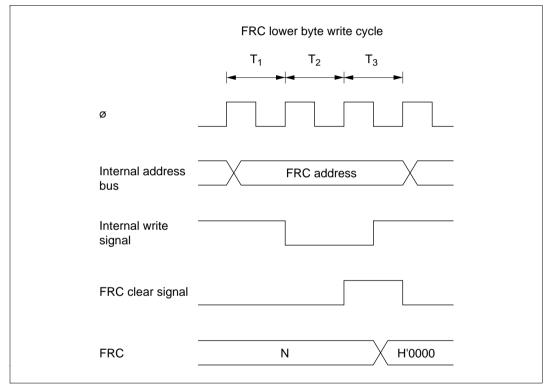

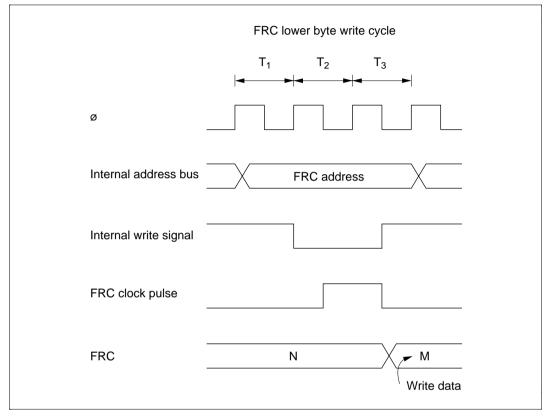

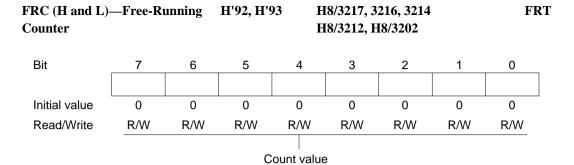

|      | 9.2.1   | Free-Running Counter (FRC)—H'FF92                                  | 172 |

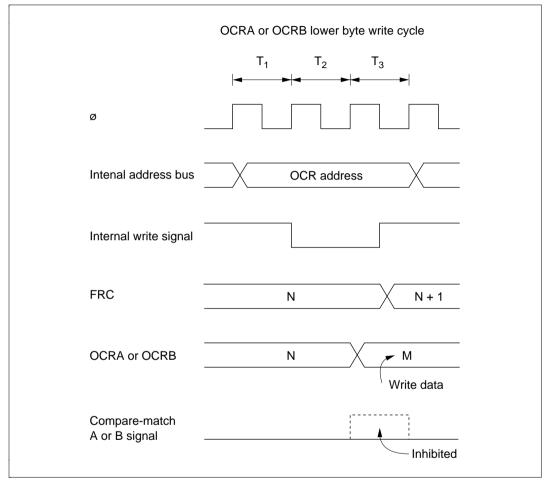

|      | 9.2.2   | Output Compare Registers A and B (OCRA and OCRB)—H'FF94 and H'FF96 | 172 |

|      | 9.2.3   | Input Capture Register (ICR)—H'FF98                                |     |

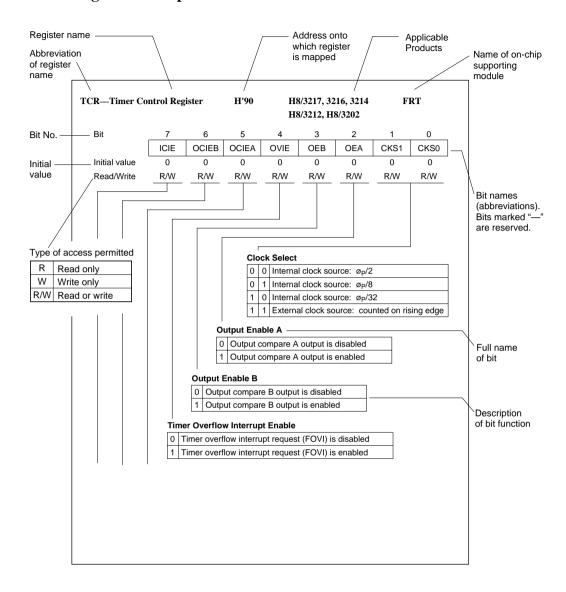

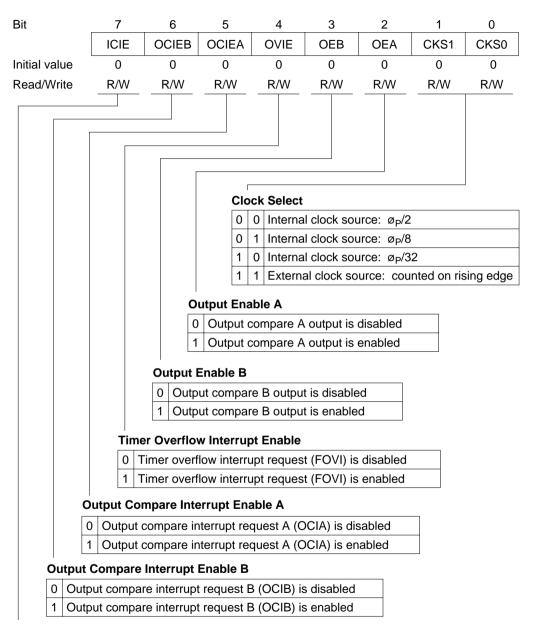

|      | 9.2.3   | Timer Control Register (TCR)—H'FF90                                |     |

|      | 9.2.4   |                                                                    |     |

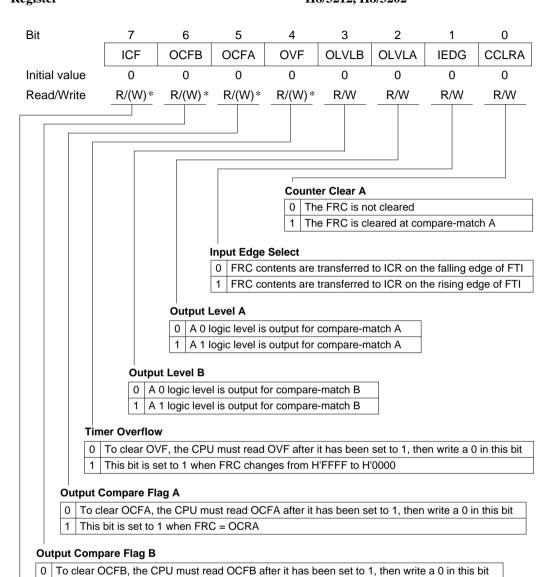

| 0.2  |         | Timer Control/Status Register (TCSR)—H'FF91                        |     |

| 9.3  |         | terface                                                            |     |

| 9.4  |         | on                                                                 |     |

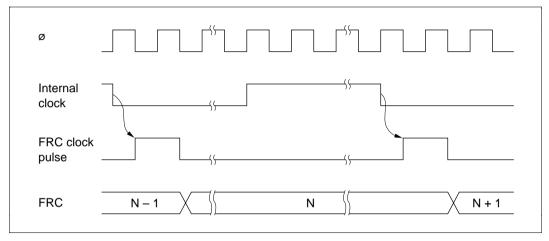

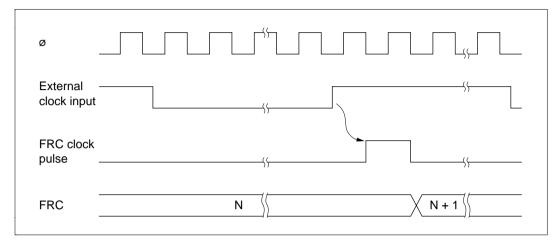

|      | 9.4.1   | FRC Incrementation Timing                                          |     |

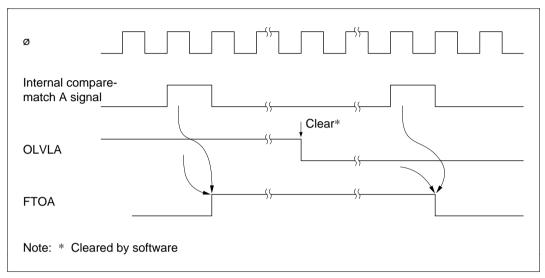

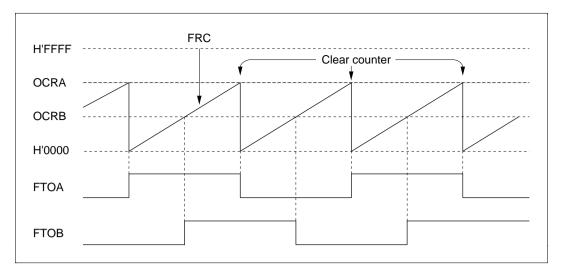

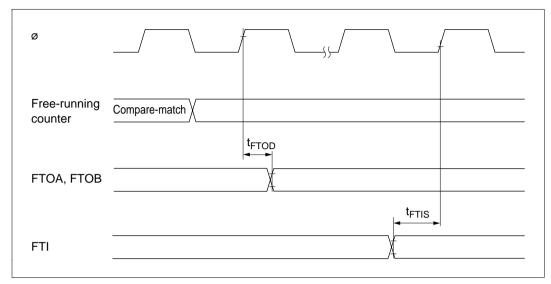

|      | 9.4.2   | Output Compare Timing                                              |     |

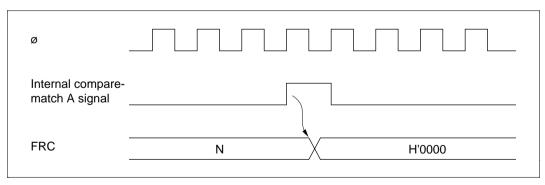

|      | 9.4.3   | FRC Clear Timing                                                   |     |

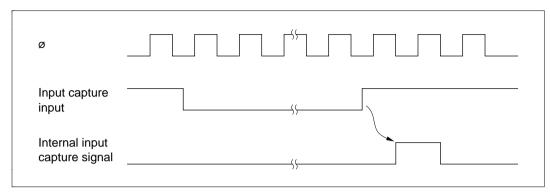

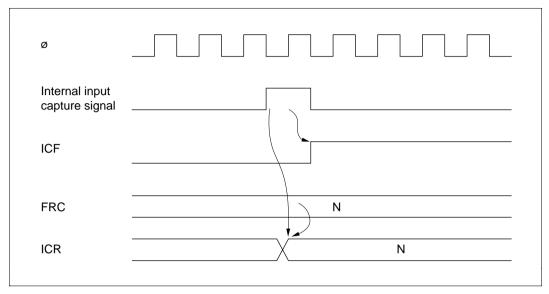

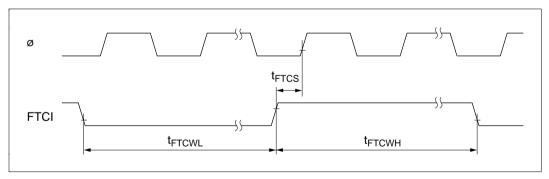

|      | 9.4.4   | Input Capture Timing.                                              |     |

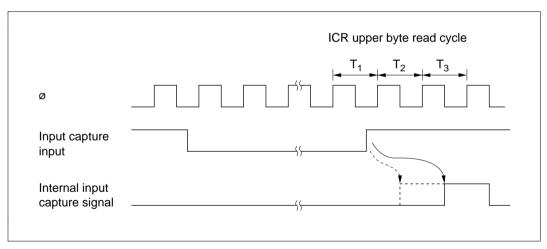

|      | 9.4.5   | Timing of Input Capture Flag (ICF) Setting                         |     |

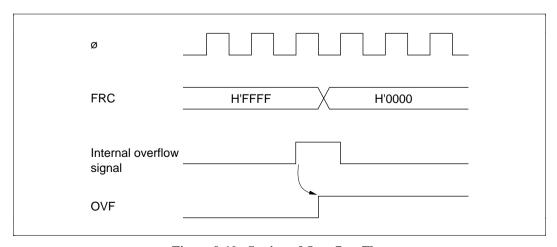

|      | 9.4.6   | Setting of FRC Overflow Flag (OVF)                                 |     |

| 9.5  | -       | ots                                                                |     |

| 9.6  | -       | Application                                                        |     |

| 9.7  | Applica | ation Notes                                                        | 188 |

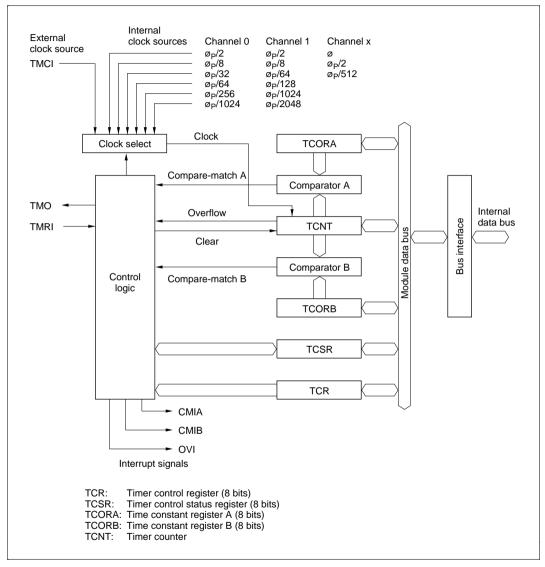

| Sect | ion 10  | 8-Bit Timers                                                       | 193 |

| 10.1 | Overvi  | ew                                                                 | 193 |

|      | 10.1.1  | Features                                                           | 193 |

|      | 10.1.2  | Block Diagram                                                      | 194 |

|      | 10.1.3  | Input and Output Pins.                                             | 195 |

|      | 10.1.4  | Register Configuration                                             | 196 |

|      |         |                                                                    |     |

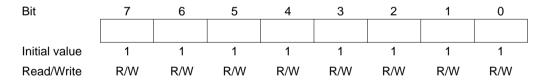

| 10.2  | 0.2 Register Descriptions |                                                              | 197 |

|-------|---------------------------|--------------------------------------------------------------|-----|

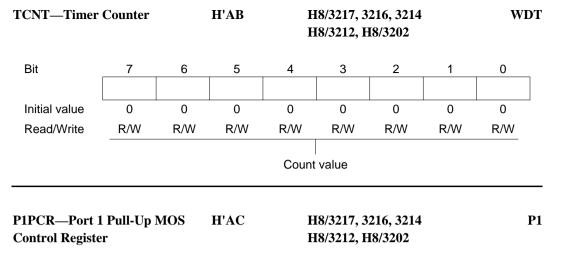

|       | 10.2.1                    | Timer Counter (TCNT)—H'FFCC (TMR0), H'FFD4 (TMR1),           |     |

|       |                           | H'FF9E (TMRX)                                                | 197 |

|       | 10.2.2                    | Time Constant Registers A and B (TCORA and TCORB)—H'FFCA and |     |

|       |                           | H'FFCB (TMR0), H'FFD2 and H'FFD3 (TMR1), H'FF9C and          |     |

|       |                           | H'FF9D (TMRX)                                                | 197 |

|       | 10.2.3                    | Timer Control Register (TCR)—H'FFC8 (TMR0), H'FFD0 (TMR1),   |     |

|       |                           | H'FF9A (TMRX)                                                | 198 |

|       | 10.2.4                    | Timer Control/Status Register (TCSR)—H'FFC9 (TMR0),          |     |

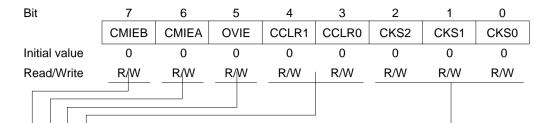

|       |                           | H'FFD1 (TMR1), H'FF9B (TMRX)                                 | 202 |

|       | 10.2.5                    | Serial/Timer Control Register (STCR)                         | 205 |

| 10.3  |                           | on                                                           |     |

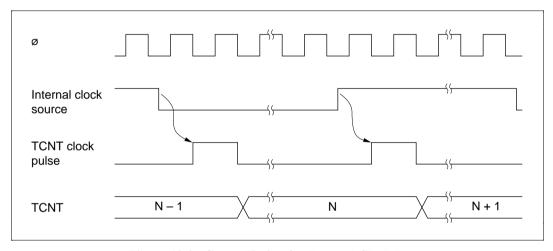

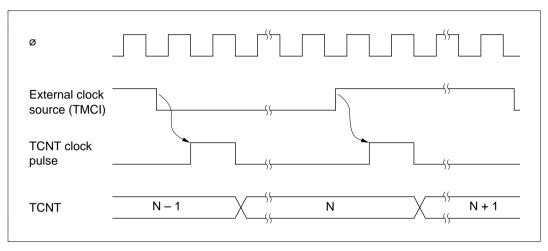

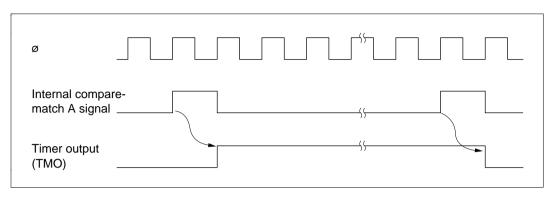

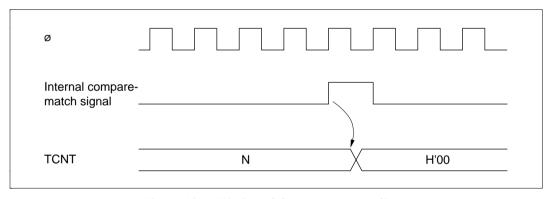

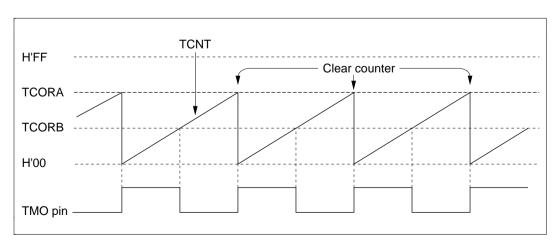

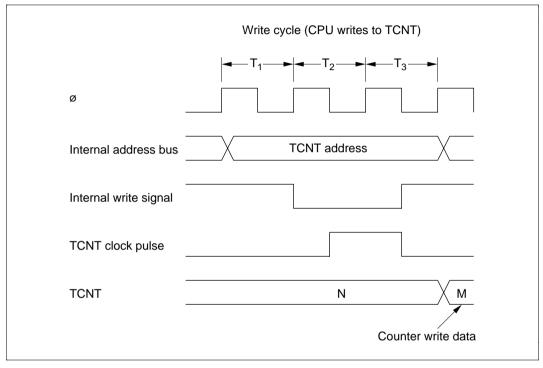

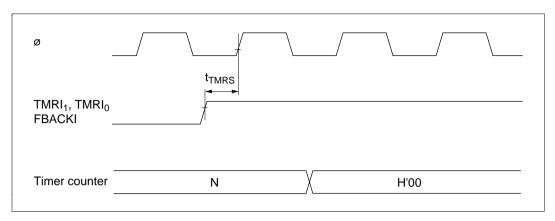

|       | 10.3.1                    | TCNT Incrementation Timing                                   | 206 |

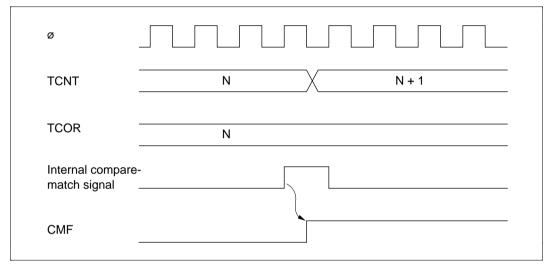

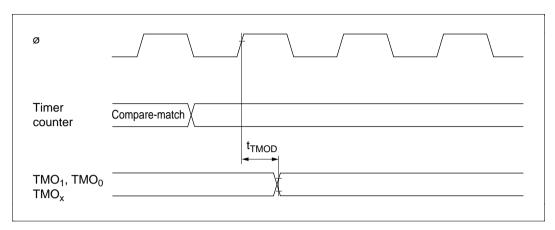

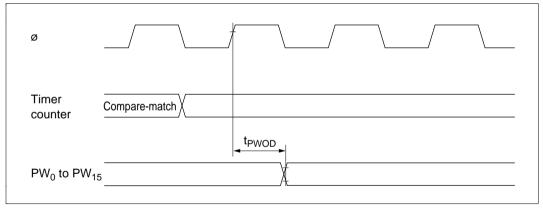

|       |                           | Compare Match Timing                                         |     |

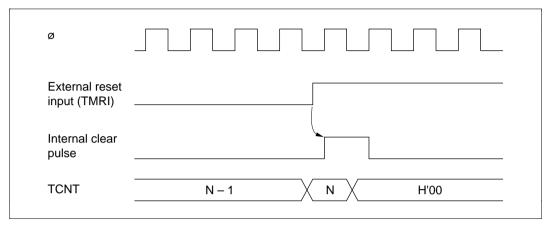

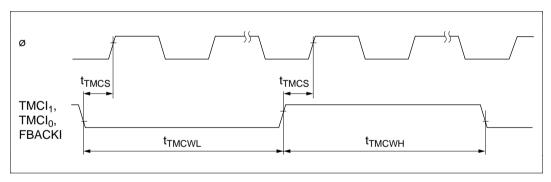

|       |                           | External Reset of TCNT                                       |     |

|       |                           | Setting of TCSR Overflow Flag                                |     |

| 10.4  |                           | ots                                                          |     |

| 10.5  | _                         | Application                                                  |     |

| 10.6  | -                         | ation Notes                                                  |     |

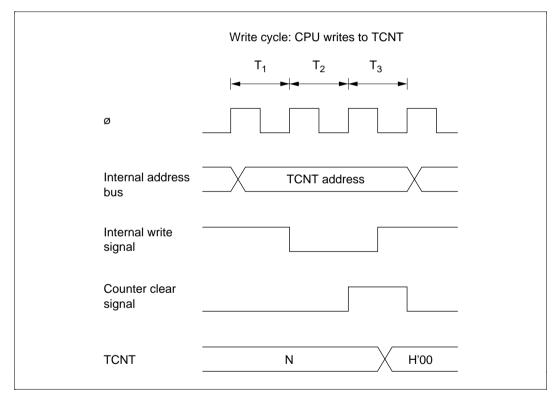

|       |                           | Contention between TCNT Write and Clear                      |     |

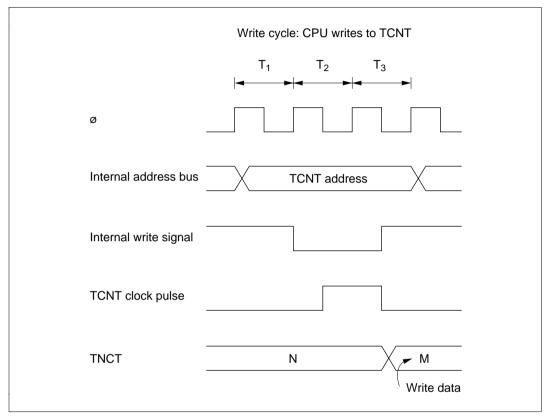

|       |                           | Contention between TCNT Write and Increment                  |     |

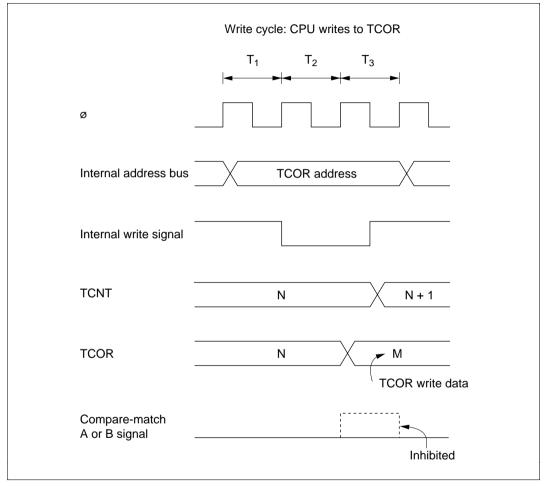

|       |                           | Contention between TCOR Write and Compare-Match              |     |

|       |                           | Contention between Compare-Match A and Compare-Match B       |     |

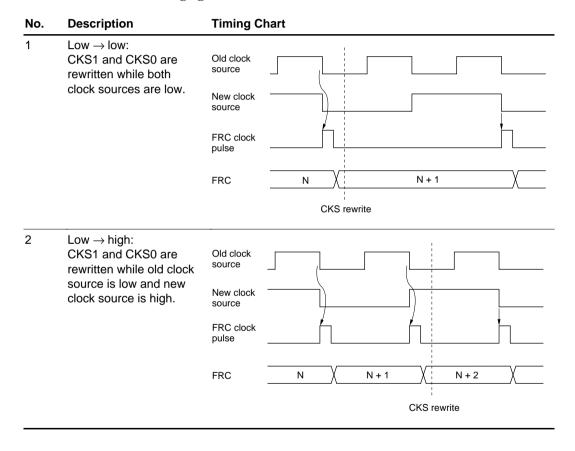

|       |                           | Incrementation Caused by Changing of Internal Clock Source   |     |

|       |                           | , , ,                                                        |     |

| Secti | on 11                     | Timer Connection                                             | 219 |

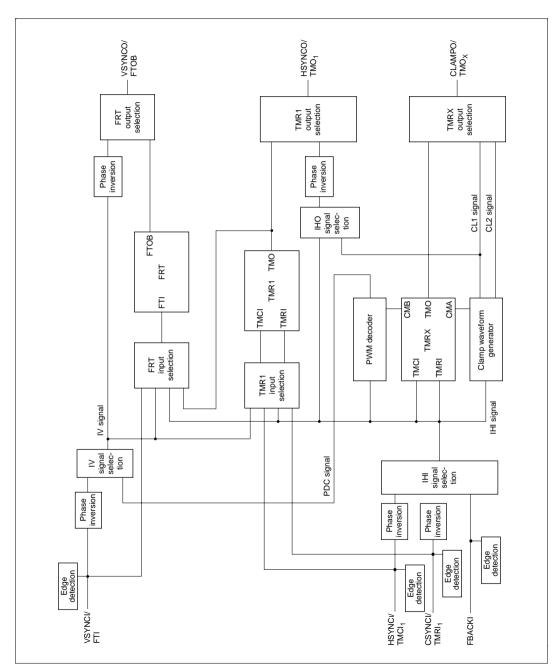

| 11.1  | Overvie                   | ew                                                           | 219 |

|       | 11.1.1                    | Features                                                     | 219 |

|       | 11.1.2                    | Block Diagram                                                | 220 |

|       | 11.1.3                    | Input and Output Pins.                                       | 221 |

|       | 11.1.4                    | Register Configuration                                       | 222 |

| 11.2  |                           | r Descriptions                                               |     |

|       | 11.2.1                    | Timer Connection Register (TCONR)                            | 222 |

|       |                           | Serial/Timer Control Register (STCR)                         |     |

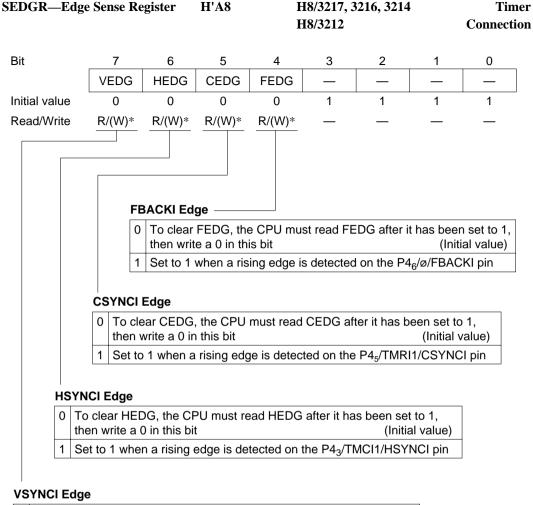

|       |                           | Edge Sense Register (SEDGR)                                  |     |

| 11.3  |                           | on                                                           |     |

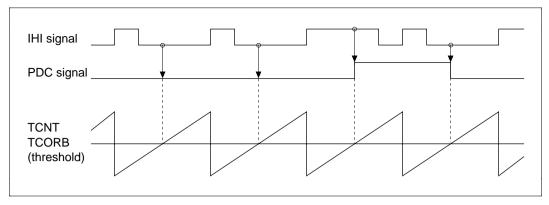

|       | _                         | PWM Decoding                                                 |     |

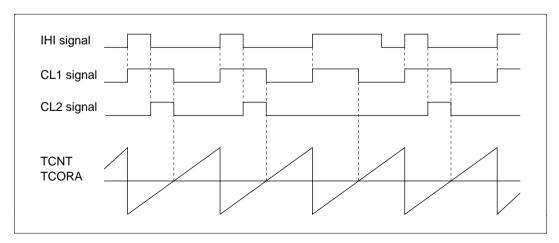

|       |                           | Clamp Waveform Generation                                    |     |

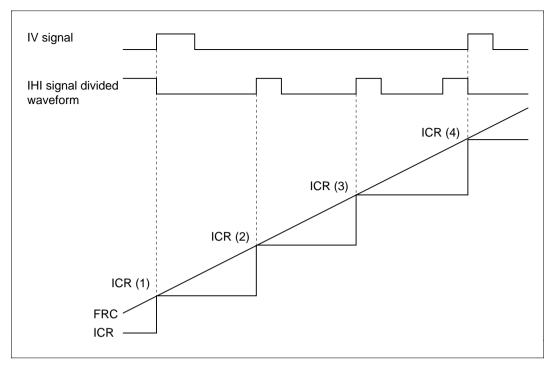

|       | 11.3.3                    | Measurement of 8-Bit Timer Divided Waveform Period           | 229 |

|       |                           |                                                              |     |

| Secti | on 12                     | Watchdog Timer                                               | 231 |

| 12.1  |                           | ew                                                           |     |

|       | 12.1.1                    | Features                                                     | 231 |

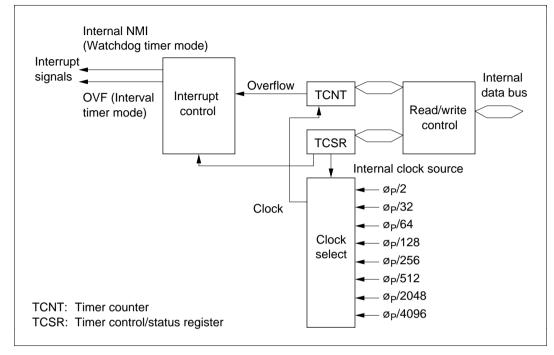

| 12.1.2   | Block Diagram                                                                                                                                                                                                                                                                        | 232                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 12.1.3   | Register Configuration                                                                                                                                                                                                                                                               | 232                                                                            |

| Registe  | •                                                                                                                                                                                                                                                                                    |                                                                                |

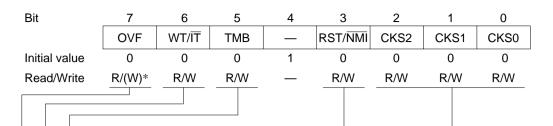

| 12.2.1   |                                                                                                                                                                                                                                                                                      |                                                                                |

| 12.2.2   |                                                                                                                                                                                                                                                                                      |                                                                                |

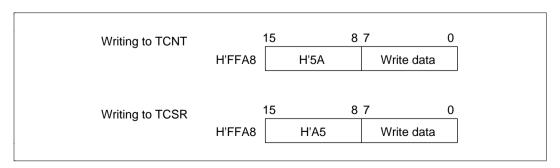

| 12.2.3   | Register Access                                                                                                                                                                                                                                                                      | 235                                                                            |

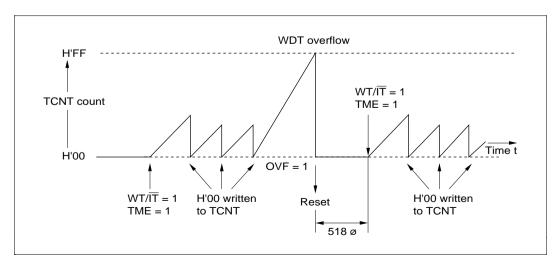

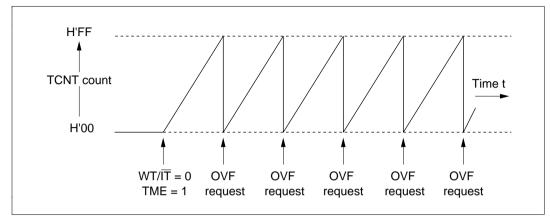

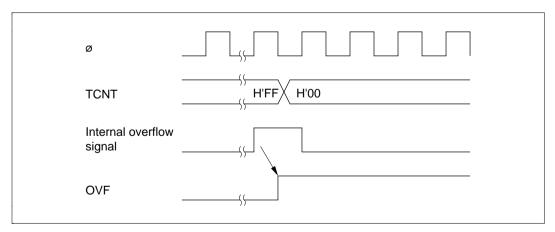

| Operati  | on                                                                                                                                                                                                                                                                                   | 236                                                                            |

|          | <u> </u>                                                                                                                                                                                                                                                                             |                                                                                |

| 12.3.2   |                                                                                                                                                                                                                                                                                      |                                                                                |

| 12.3.3   | 6                                                                                                                                                                                                                                                                                    |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

| 12.4.1   | Contention between TCNT Write and Increment                                                                                                                                                                                                                                          | 238                                                                            |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

| 12.4.3   | Recovery from Software Standby Mode                                                                                                                                                                                                                                                  | 238                                                                            |

| . 10     |                                                                                                                                                                                                                                                                                      |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

|          | _                                                                                                                                                                                                                                                                                    |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

|          | · ·                                                                                                                                                                                                                                                                                  |                                                                                |

| _        |                                                                                                                                                                                                                                                                                      |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

| 13.2.4   |                                                                                                                                                                                                                                                                                      |                                                                                |

| 13.2.5   |                                                                                                                                                                                                                                                                                      |                                                                                |

| 13.2.6   |                                                                                                                                                                                                                                                                                      |                                                                                |

| 13.2.7   |                                                                                                                                                                                                                                                                                      |                                                                                |

| 13.2.8   |                                                                                                                                                                                                                                                                                      |                                                                                |

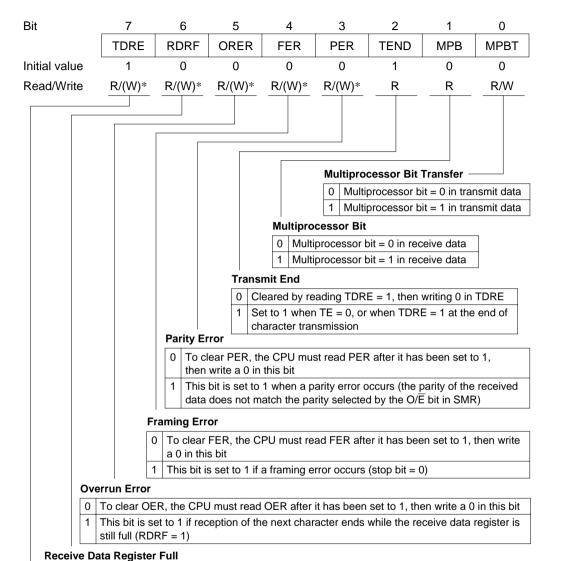

| 13.2.9   | Serial Communication Mode Register (SCMR)                                                                                                                                                                                                                                            | 259                                                                            |

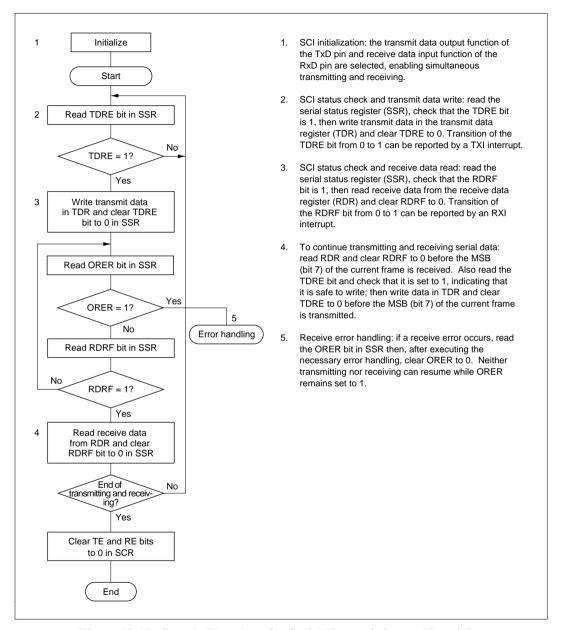

| Operati  | on                                                                                                                                                                                                                                                                                   | 260                                                                            |

|          |                                                                                                                                                                                                                                                                                      |                                                                                |

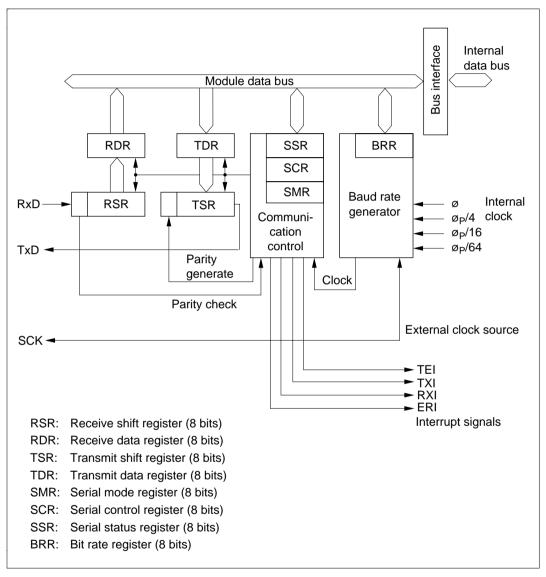

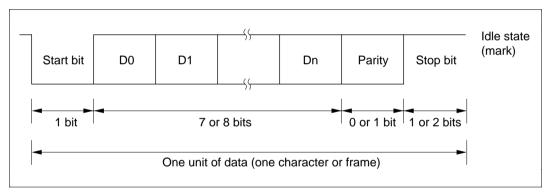

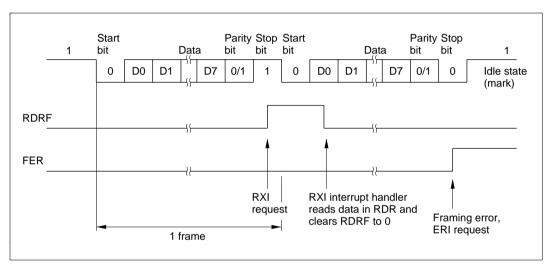

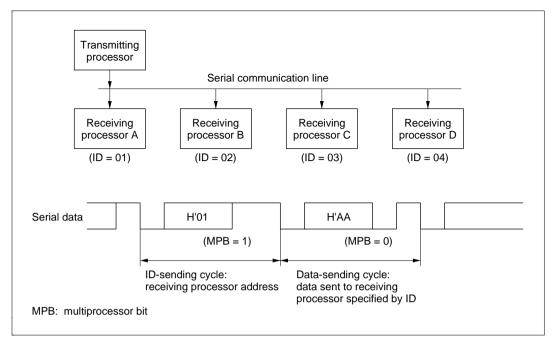

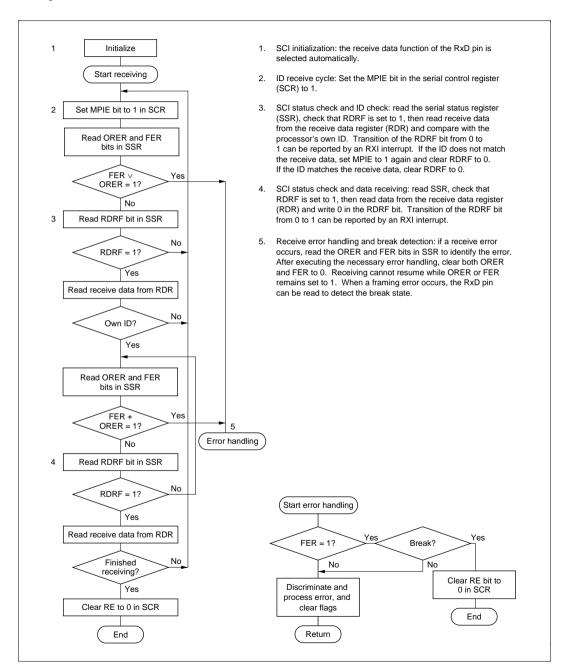

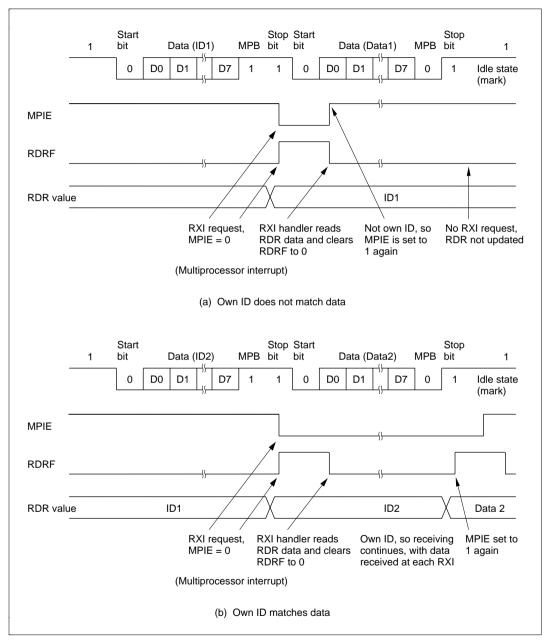

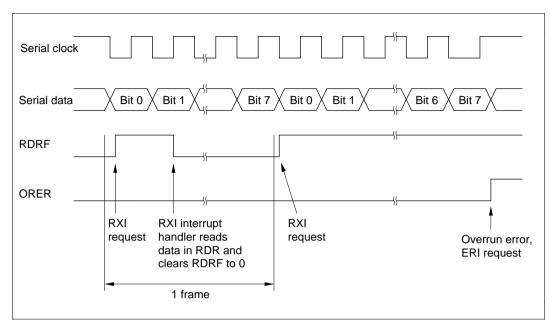

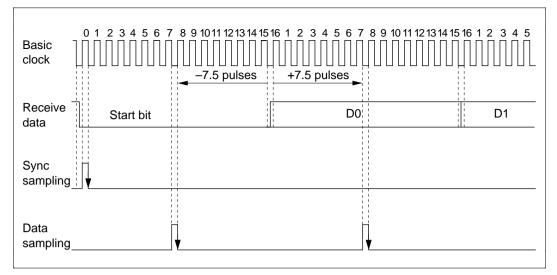

| 13.3.2   | Asynchronous Mode                                                                                                                                                                                                                                                                    | 262                                                                            |

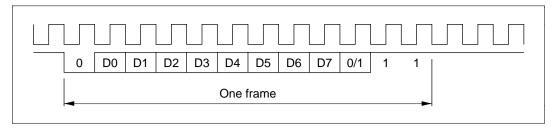

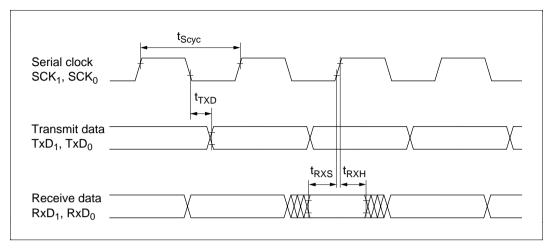

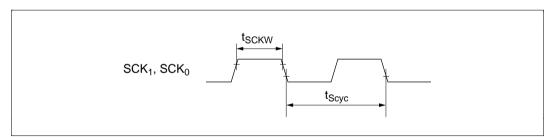

| 13.3.3   | Synchronous Mode                                                                                                                                                                                                                                                                     | 276                                                                            |

| Interrup | ots                                                                                                                                                                                                                                                                                  | 284                                                                            |

| Applica  | ation Notes                                                                                                                                                                                                                                                                          | 284                                                                            |

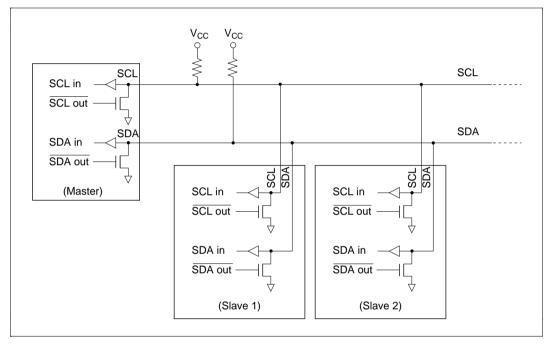

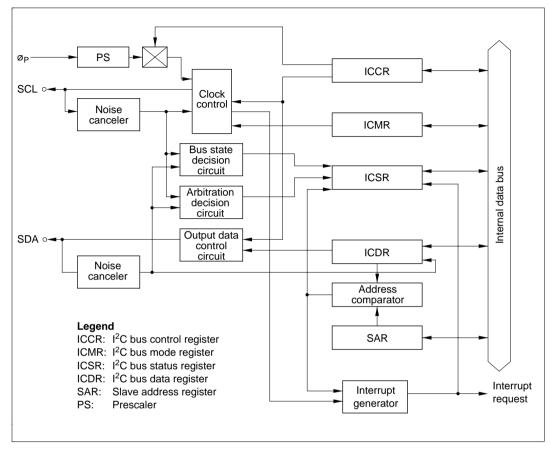

| on 11    | I/C Due Interface [Ontion]                                                                                                                                                                                                                                                           | 207                                                                            |

|          | •                                                                                                                                                                                                                                                                                    | 287                                                                            |

|          |                                                                                                                                                                                                                                                                                      | 287                                                                            |

|          |                                                                                                                                                                                                                                                                                      | 287                                                                            |

|          | _                                                                                                                                                                                                                                                                                    |                                                                                |

| 14.1.3   | Input/Output Pins                                                                                                                                                                                                                                                                    | 290                                                                            |

|          | 12.1.3 Registe 12.2.1 12.2.2 12.2.3 Operati 12.3.1 12.3.2 12.3.3 Applica 12.4.1 12.4.2 12.4.3 Overvio 13.1.1 13.1.2 13.1.3 13.1.4 Registe 13.2.1 13.2.2 13.2.3 13.2.4 13.2.5 13.2.6 13.2.7 13.2.8 13.2.9 Operati 13.3.1 13.3.2 13.3.3 Interrup Applica fron 14 Overvio 14.1.1 14.1.2 | 12.2.2 Timer Control/Status Register (TCSR).  12.2.3 Register Access Operation |

| 14.1.4                                                                                                                            | Register Configuration                                                                                                                                                                                                                                                                  | 290                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registe                                                                                                                           | er Descriptions                                                                                                                                                                                                                                                                         | 291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14.2.1                                                                                                                            | I <sup>2</sup> C Bus Data Register (ICDR)                                                                                                                                                                                                                                               | 291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

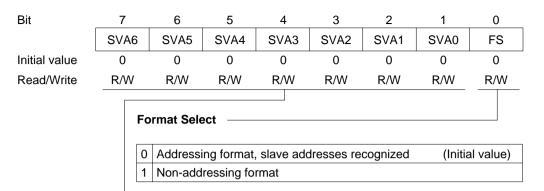

| 14.2.2                                                                                                                            | Slave Address Register (SAR)                                                                                                                                                                                                                                                            | 291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14.2.3                                                                                                                            | I <sup>2</sup> C Bus Mode Register (ICMR)                                                                                                                                                                                                                                               | 292                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

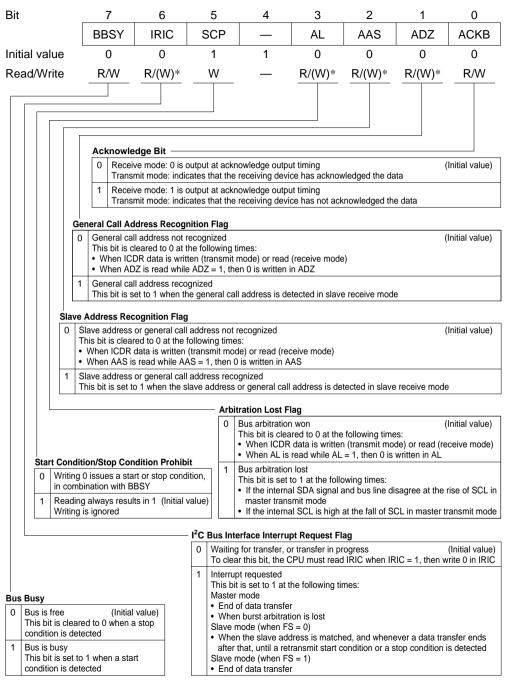

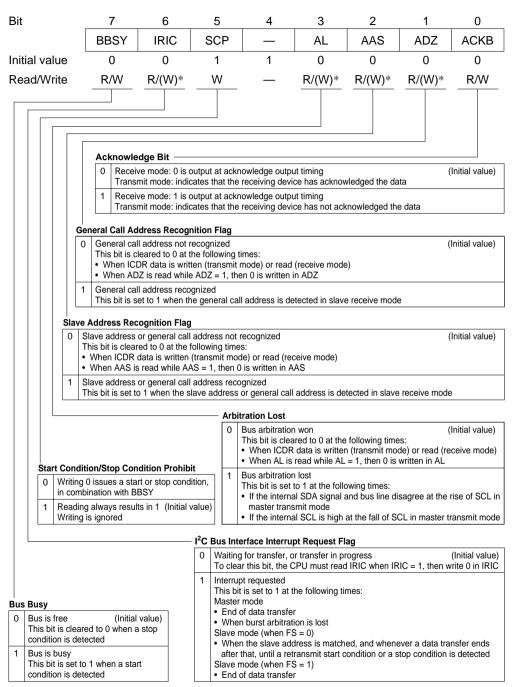

| 14.2.4                                                                                                                            | I <sup>2</sup> C Bus Control Register (ICCR)                                                                                                                                                                                                                                            | 294                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14.2.5                                                                                                                            | I <sup>2</sup> C Bus Status Register (ICSR)                                                                                                                                                                                                                                             | 297                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14.2.6                                                                                                                            | Serial/Timer Control Register (STCR)                                                                                                                                                                                                                                                    | 301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

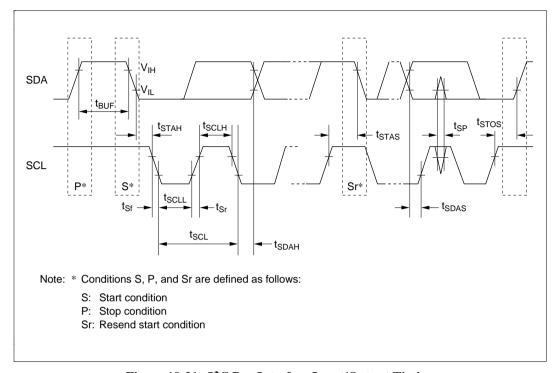

| Operati                                                                                                                           | ion                                                                                                                                                                                                                                                                                     | 302                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

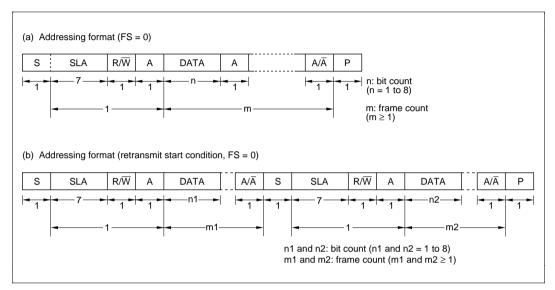

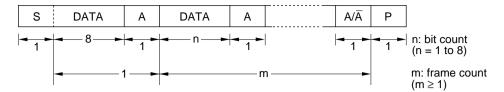

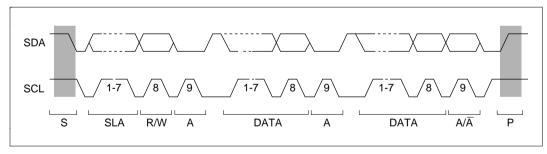

| 14.3.1                                                                                                                            | I <sup>2</sup> C Bus Data Format                                                                                                                                                                                                                                                        | 302                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

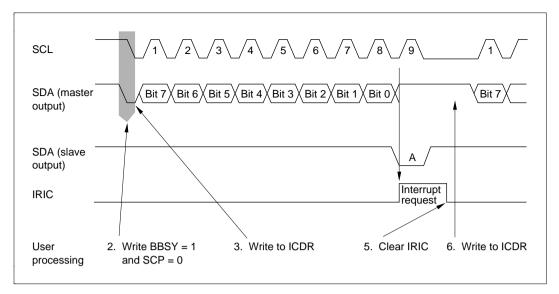

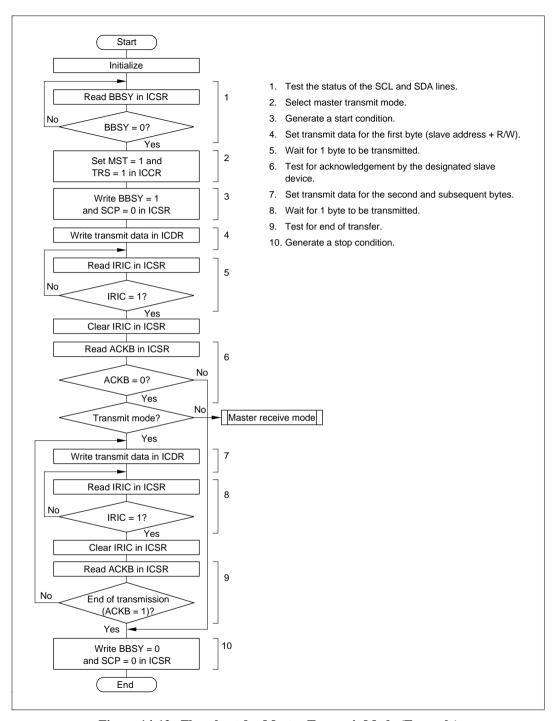

| 14.3.2                                                                                                                            | Master Transmit Operation                                                                                                                                                                                                                                                               | 304                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

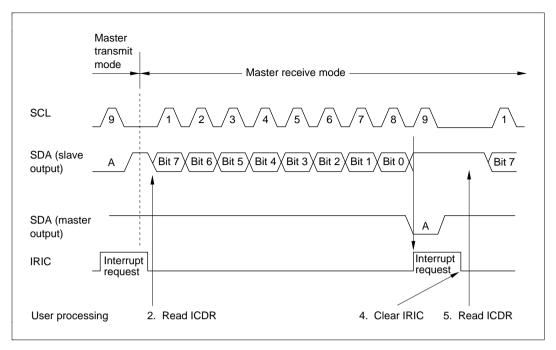

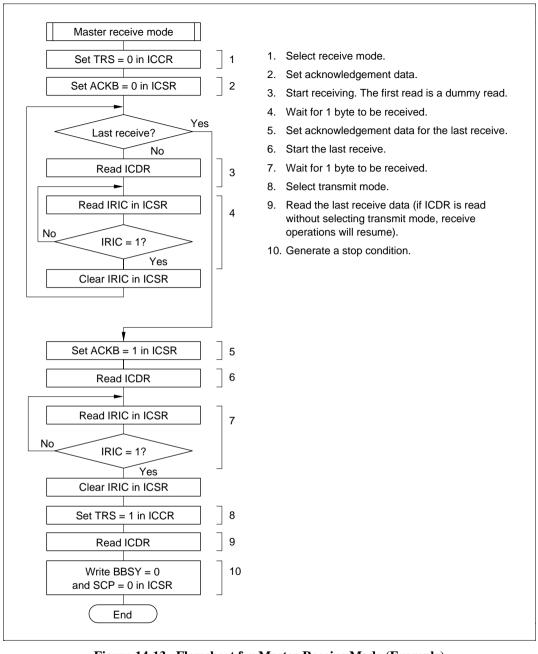

| 14.3.3                                                                                                                            | Master Receive Operation                                                                                                                                                                                                                                                                | 306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

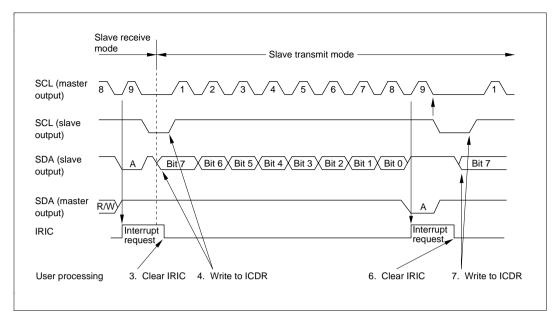

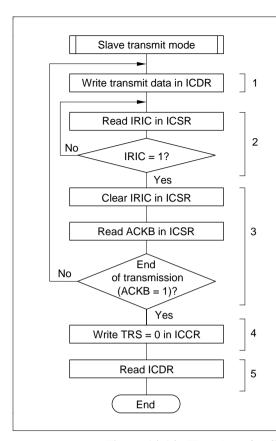

| 14.3.4                                                                                                                            | Slave Transmit Operation                                                                                                                                                                                                                                                                | 308                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

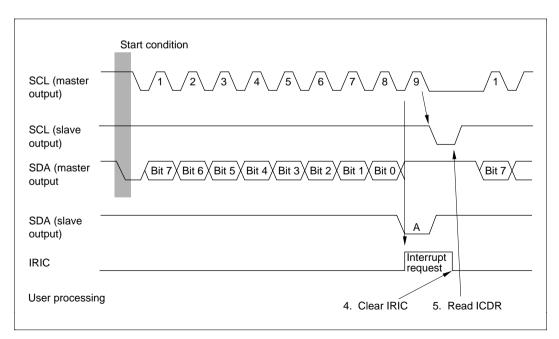

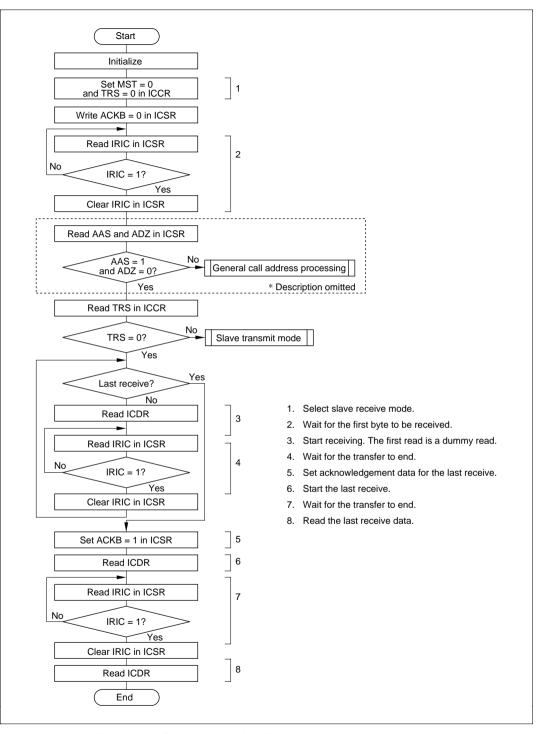

| 14.3.5                                                                                                                            | Slave Receive Operation                                                                                                                                                                                                                                                                 | 310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

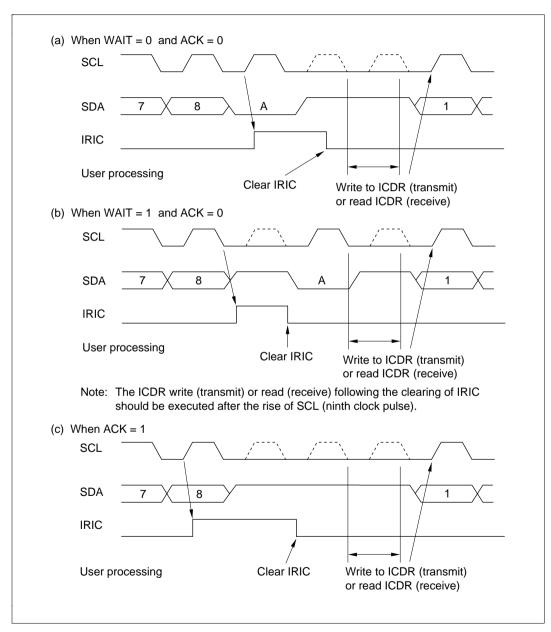

| 14.3.6                                                                                                                            | IRIC Set Timing and SCL Control                                                                                                                                                                                                                                                         | 311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

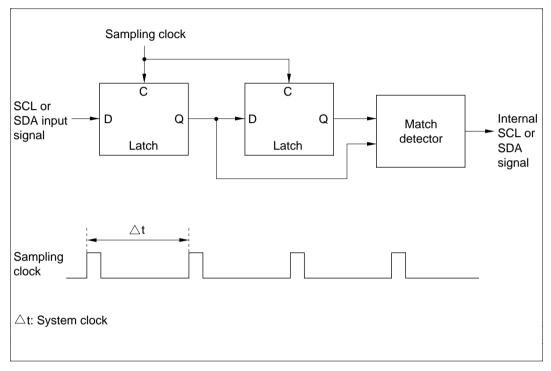

| 14.3.7                                                                                                                            | Noise Canceler                                                                                                                                                                                                                                                                          | 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14.3.8                                                                                                                            | Sample Flowcharts                                                                                                                                                                                                                                                                       | 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Applica                                                                                                                           | ation Notes                                                                                                                                                                                                                                                                             | 317                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ion 15                                                                                                                            | Host Interface                                                                                                                                                                                                                                                                          | 319                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

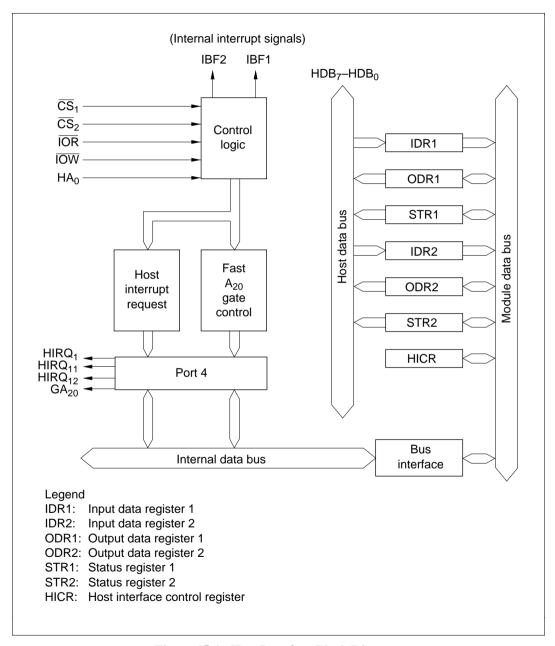

| Overvi                                                                                                                            | ew                                                                                                                                                                                                                                                                                      | 319                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15.1.1                                                                                                                            | Block Diagram                                                                                                                                                                                                                                                                           | 320                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15.1.2                                                                                                                            | Input and Output Pins                                                                                                                                                                                                                                                                   | 321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15.1.3                                                                                                                            | Register Configuration                                                                                                                                                                                                                                                                  | 322                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Registe                                                                                                                           | er Descriptions                                                                                                                                                                                                                                                                         | 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15.2.1                                                                                                                            | System Control Register (SYSCR)                                                                                                                                                                                                                                                         | 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15 2 2                                                                                                                            |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10.2.2                                                                                                                            | Host Interface Control Register (HICR)                                                                                                                                                                                                                                                  | 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                   | Host Interface Control Register (HICR)  Input Data Register 1 (IDR1)                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15.2.3                                                                                                                            |                                                                                                                                                                                                                                                                                         | 324                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15.2.3                                                                                                                            | Input Data Register 1 (IDR1) Output Data Register 1 (ODR1)                                                                                                                                                                                                                              | 324<br>325                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15.2.3<br>15.2.4                                                                                                                  | Input Data Register 1 (IDR1) Output Data Register 1 (ODR1)                                                                                                                                                                                                                              | 324<br>325<br>325                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

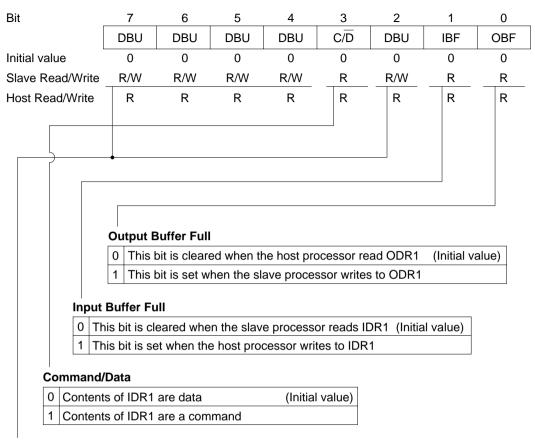

| 15.2.3<br>15.2.4<br>15.2.5<br>15.2.6                                                                                              | Input Data Register 1 (IDR1)  Output Data Register 1 (ODR1)  Status Register 1 (STR1)                                                                                                                                                                                                   | 324<br>325<br>325<br>326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15.2.3<br>15.2.4<br>15.2.5<br>15.2.6<br>15.2.7                                                                                    | Input Data Register 1 (IDR1) Output Data Register 1 (ODR1) Status Register 1 (STR1) Input Data Register 2 (IDR2)                                                                                                                                                                        | 324<br>325<br>325<br>326<br>327                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

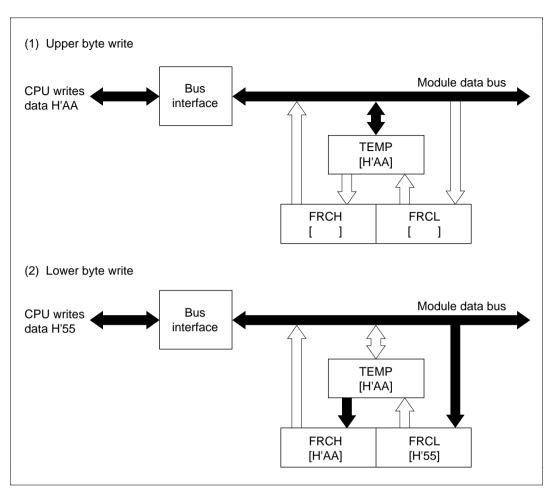

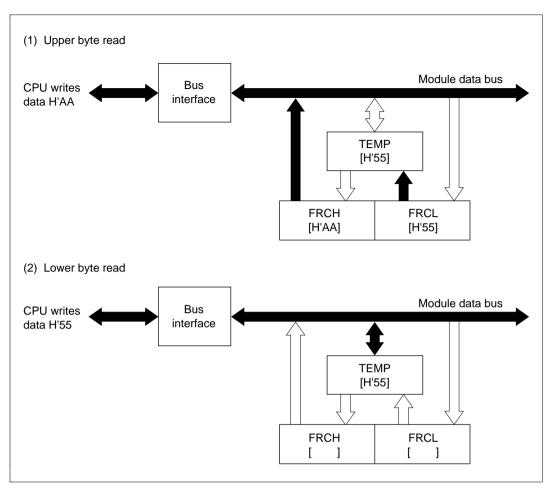

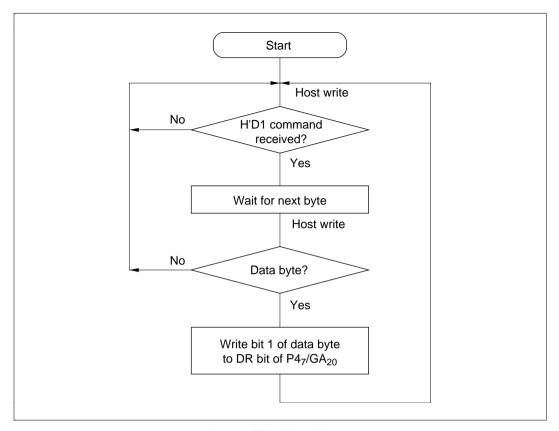

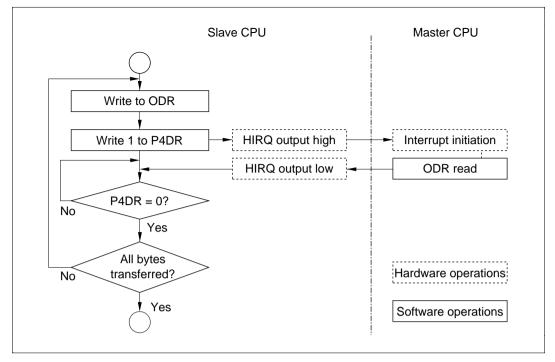

| 15.2.3<br>15.2.4<br>15.2.5<br>15.2.6<br>15.2.7<br>15.2.8<br>Operati                                                               | Input Data Register 1 (IDR1)  Output Data Register 1 (ODR1)  Status Register 1 (STR1)  Input Data Register 2 (IDR2)  Output Data Register 2 (ODR2)  Status Register 2 (STR2)  ion                                                                                                       | 324<br>325<br>325<br>326<br>327<br>327<br>329                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |