# Quad-SHARC® DSP Multiprocessor Family

## AD14160/AD14160L

### **GENERAL DESCRIPTION**

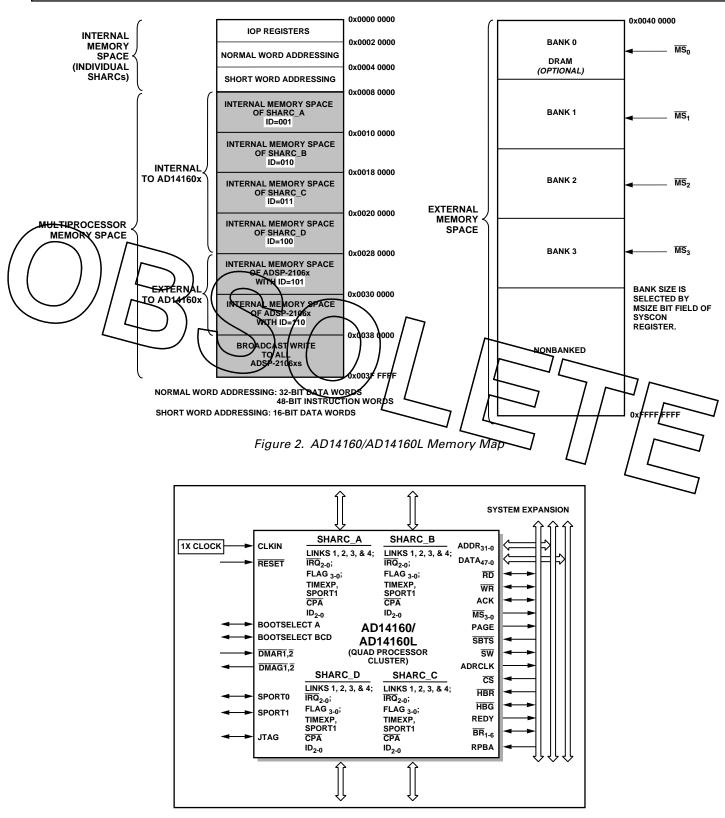

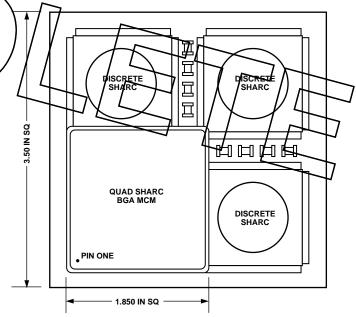

The AD14160/AD14160L Quad-SHARC Ceramic Ball Grid Array (CBGA) puts the power of the first generation AD14060 (CQFP) DSP multiprocessor into a very high density ball grid array package; now with additional link and serial I/O pinned out, beyond that from the CQFP package. The core of the multiprocessor is the ADSP-21060 DSP microcomputer. The AD14x60 modules have the highest performance—density and lowest cost— performance ratios of any in their class. They are ideal for applications requiring higher levels of performance and/or functionality per unit area.

The AD14160/AD14160L takes advantage of the built-in multiprocessing features of the ADSP-21060 to achieve 480 peak MFLOPS with a single chip type, in a single package. The onchip SRAM of the DSPs provides 16 Mbits of on-module shared SRAM. The complete shared bus (48 data, 32 address) is also brought off-module for interfacing with expansion memory or other peripherals.

SHARC is a registered trademark of Analog Devices, Inc.

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

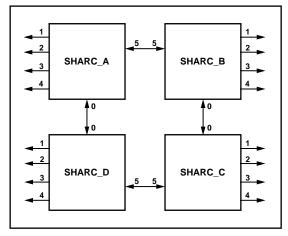

The ADSP-21060 link ports are interconnected to provide direct communication among the four SHARCs as well as high speed off-module access. Internally, links connect the SHARC in a ring. Externally, each SHARC has a total of 160 Mbytes/s link port bandwidth.

Multiprocessor performance is enhanced with embedded power and ground planes, matched impedance interconnect, and optimized signal routing lengths and separation. The fully tested and ready-to-insert multiprocessor also significantly reduces board space.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998

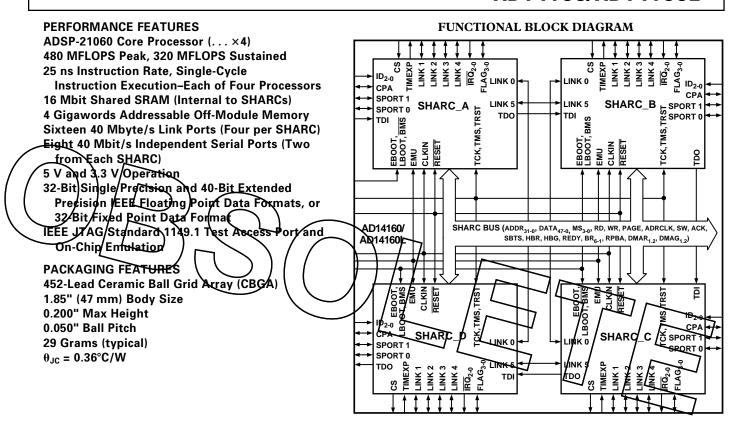

### DETAILED DESCRIPTION Architectural Features ADSP-21060 Core

The AD14160/AD14160L is based on the powerful ADSP-21060 (SHARC) DSP chip. The ADSP-21060 SHARC combines a high performance floating-point DSP core with integrated, on-chip system features including a 4 Mbit SRAM memory, host processor interface, DMA controller, serial ports, and both link port and parallel bus connectivity for glueless DSP multiprocessing, (see Figure 1). It is fabricated in a high speed, low power CMOS process, and has a 25 ns instruction cycle time. The arithmetic/ logic unit (ALU), multiplier and shifter all perform single-cycle instructions, and the three units are arranged in parallel, maximizing computational throughput.

The SHARG features an enhanced Harvard architecture in which the data memory (DM) bus transfers data, and the program memory (PM) bus transfers both instructions and data. There is also an on-chip instruction cache which selectively caches only those instructions whose fetches conflict with the RM bus data accesses. This combines with the separate program and data memory buses to enable three-bus operation for fetching an instruction and two operands all in a single cycle. The SHARC also contains a general purpose data register file which

is a 10-port, 32-register (16 primary, 16 secondary) file. Each SHARC's core also implements two data address generators (DAGs), implementing circular data buffers in hardware. The DAGs contain sufficient registers to allow the creation of up to 32 circular buffers. The 48-bit instruction word accommodates a variety of parallel operations, for concise programming. For example, the ADSP-21060 can conditionally execute a multiply, an add, a subtract, and a branch, all in a single instruction.

The SHARCs contain 4 Mbits of on-chip SRAM each, organized as two blocks of 2 Mbits, which can be configured for different combinations of code and data storage. The memory can be configured as a maximum of 128K words of 32-bit data, 256K words of 16-bit data, 80K words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to 4 megabits. A 16-bit floating-point storage format is supported which effectively doubles the amount of data that may be stored on chip. Conversion between the 32-bit floating point and 16-bit floating point formats is done in a single instruction. Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor or DMA controller. The dual-ported memory and separate on-chip buses allow two data transfers from the core and one from I/O, all in a

Figure 1. ADSP-21060 Processor Block Diagram (Core of the AD14160/AD14160L)

-2- REV. A

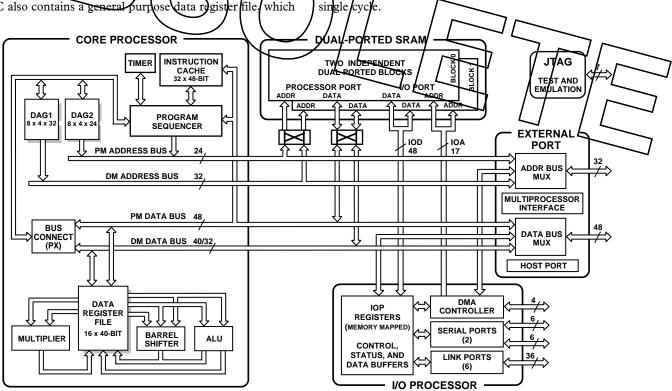

Figure 3. Complete Shared Memory Multiprocessing System

REV. A \_3\_

#### **Shared Memory Multiprocessing**

The AD14160/AD14160L takes advantage of the powerful multiprocessing features built into the SHARC. The SHARCs are connected to maximize the performance of this cluster-of-four architecture, and still allow for off-module expansion. The AD14160/AD14160L in itself is a complete shared memory multiprocessing system, as shown in Figure 3. The unified address space of the SHARCs allows direct interprocessor accesses of each SHARCs' internal memory. In other words, each SHARC can directly access the internal memory and IOP registers of each of the other SHARCs by simply reading or writing to the appropriate address in multi-processor memory space (see Figure 2)—this is called a *direct read or direct write*.

Bus arbitration is accomplished with the on-SHARC arbitration logic Each SHARC has a unique ID, and drives the Bus-Request (PR) line corresponding to its ID, while monitoring all others.  $\overline{BR1}$ - $\overline{BR4}$  are used within the AD14160/AD14160L, while  $\overline{BR5}$  and  $\overline{BR6}$  can be used for expansion. All bus requests ( $\overline{BR1}$ - $\overline{BR6}$ ) are included in the module I/O.

Two different priority schemes, fixed and rotsting, are available to resolve competing bus requests. The RPBA pin selects which scheme is used: when RPBA is high, rotating priority bus arbitration is selected, and when RPBA is low, fixed priority is selected.

Table I. Rotating Priority Arbitration Example

| Hardware Processor IDs |      |      |      |     |     |      |                              |

|------------------------|------|------|------|-----|-----|------|------------------------------|

| Cycle                  | ID1  | ID2  | ID3  | ID4 | ID5 | ID6  |                              |

| 1                      | M    | 1    | 2 BR | 3   | 4   | 5    | Initial Priority Assignments |

| 2                      | 4    | 5 BR | M-BR | 1   | 2   | 3    |                              |

| 3                      | 4    | 5 BR | M    | 1   | 2   | 3    |                              |

| 4                      | 5 BR | M    | 1    | 2   | 3   | 4 BR |                              |

| 5                      | 1 BR | 2    | 3    | 4   | 5   | M    | Final Priority Assignments   |

NOTES

1-5 = Assigned Priority.

M = Bus Mastership (in that cycle).

BR = Requesting Bus Mastership with BRx.

Bus mastership is passed from one SHARC to another during a bus transition cycle. A bus transition cycle only occurs when the current bus master deasserts its BR line and one of the slave SHARCs asserts its BR line. The bus master can therefore retain bus mastership by keeping its BR line asserted. When the bus master deasserts its BR line, and no other BR line is asserted, then the master will not lose any bus cycles. When more than one SHARC asserts its BR line, the SHARC with the highest priority request becomes bus master on the following cycle. Each SHARC observes all of the BR lines, and therefore tracks when a bus transition cycle has occurred, and which processor has become the new bus master. Master processor changeover incurs only one cycle of overhead. An example bus transition sequence is shown in Table I.

Bus locking is possible, allowing indivisible read-modify-write sequences for semaphores. In either the fixed or rotating priority scheme, it is also possible to limit the number of cycles the master can control the bus. The AD14160/AD14160L also provides the option of using the Core Priority Access (CPA) mode of the SHARC. Using the CPA signal allows external bus accesses by the core processor of a slave SHARC to take priority over ongoing DMA transfers. Also, each SHARC can broadcast write to all other SHARCs simultaneously, allowing the implementation of reflective semaphores.

The bus master can communicate with slave SHARCs by writing messages to their internal IOP registers. The MSRG0– MSRG7 registers are general-purpose registers that can be used for convenient message passing, semaphores and resource sharing between the SHARCs. For message passing, the master communicates with a slave by writing and/or reading any of the eight message registers on the slave. For vector interrupts, the master can issue a vector interrupt to a slave by writing the address of an interrupt service routine to the slave's VIRPT register. This causes an immediate high priority interrupt on the slave which, when serviced, will cause it to branch to the specified service routine.

### Off-Module Memory and Peripherals Interface

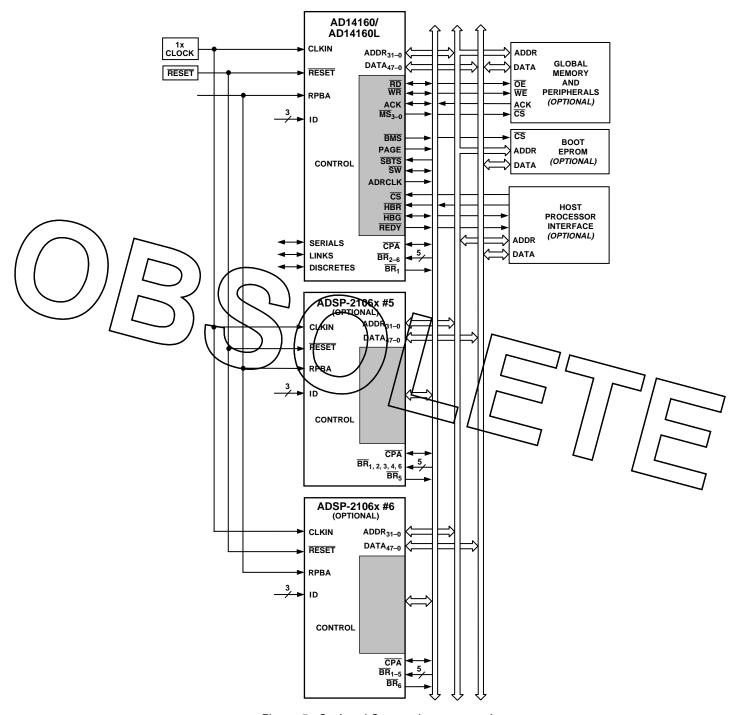

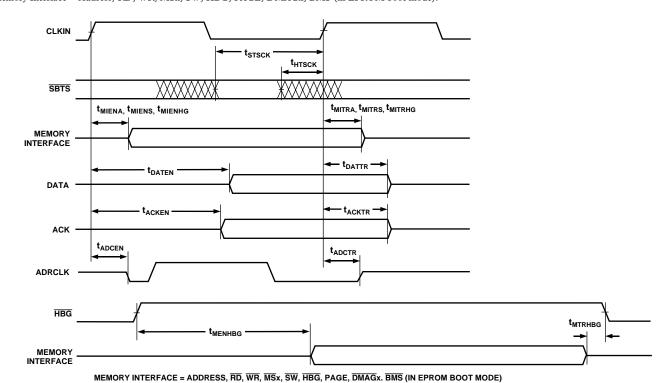

The AD14160/AD14160L's external port provides the interface to off-module memory and peripherals (see Figure 5). This port consists of the complete external port bus of the SHARC, bused together in common among the four SHARCs.

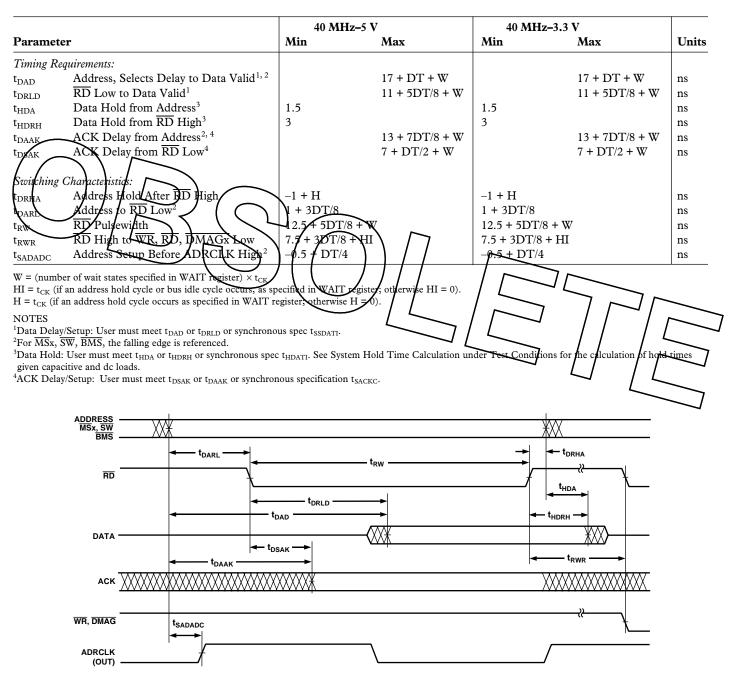

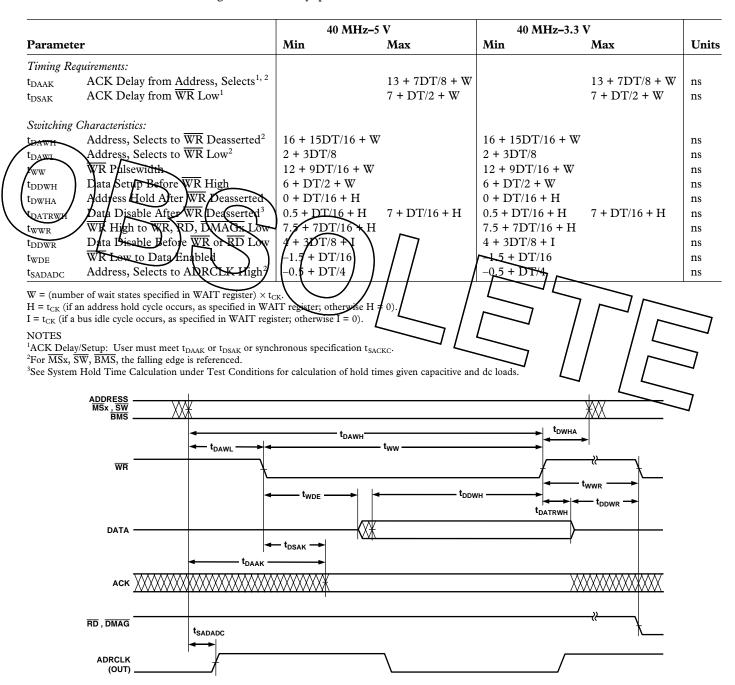

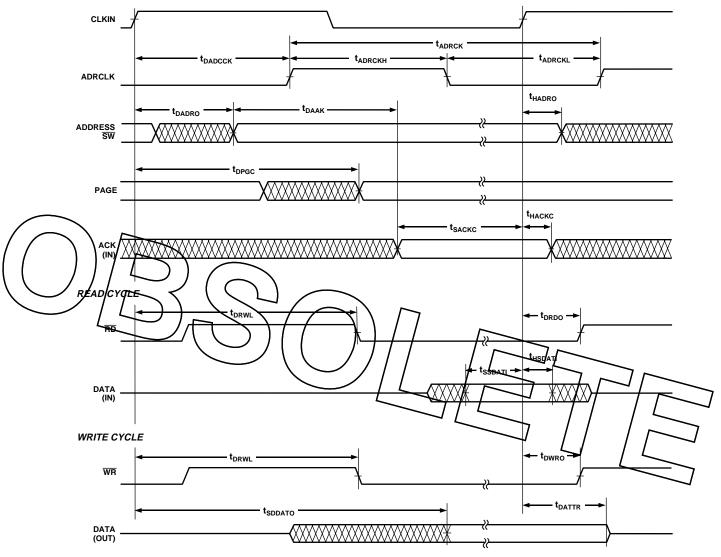

The 4-gigaword off-module address space is included in the AD14160/AD14160L's unified address space. Addressing of external memory devices is facilitated by each SHARC internally decoding the high order address lines to generate memory bank select signals. Separate control lines are also generated for simplified addressing of page-mode DRAM. The AD14160/AD14160L also supports programmable memory wait states and external memory acknowledge controls to allow interfacing to DRAM and peripherals with variable access, hold and disable time requirements.

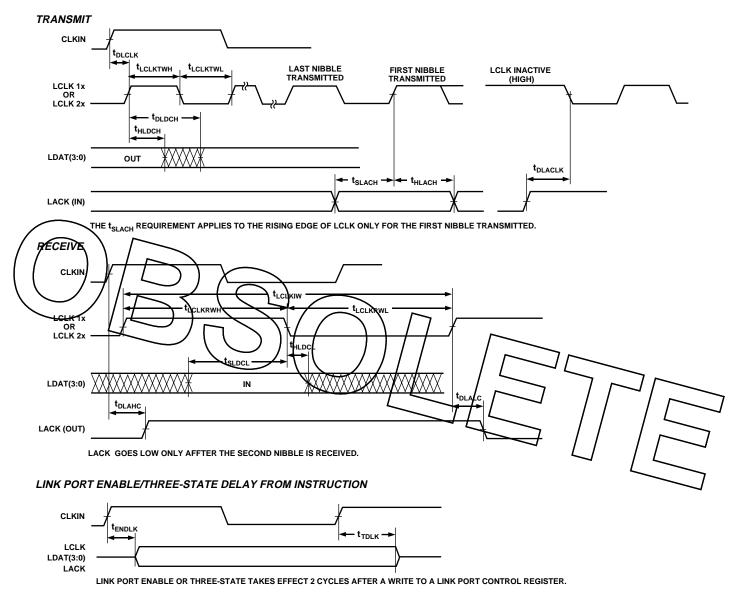

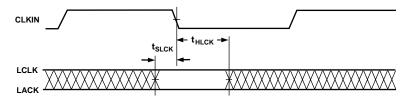

Link Port I/O

Each individual SHARC features six 4-bit link ports that facilitate SHARC-to-SHARC communication and external I/O interfacing. Each link port can be configured for either 1x or 2x operation, allowing each to transfer either 4 or 8 bits per cycle. The link ports can operate independently and simultaneously, with a maximum bandwidth of 40 MBytes/s each, or a total of 240 MBytes/s per SHARC.

The AD14160/AD14160L provides additional link port I/O beyond that of the AD14060. Internally, two links from each SHARC form a ring connection among the four. The remaining four link ports from each SHARC are brought out independently from each SHARC. A maximum of 640 MBytes/s link port bandwidth is then available off of the AD14160/AD14160L. The link port connections are detailed in Figure 4.

Figure 4. Link Port Connections

Figure 5. Optional System Interconnections

REV. A -5-

Link port 4, the boot link port, is brought off independently from each SHARC. Individual booting is then allowed, or chained link port booting is possible as described under "Link Port Booting."

Link port data is packed into 32-bit or 48-bit words, and can be directly read by the SHARC core processor or DMA-transferred to on-SHARC memory.

Each link port has its own double-buffered input and output registers. Clock/acknowledge handshaking controls link port transfers. Transfers are programmable as either transmit or receive.

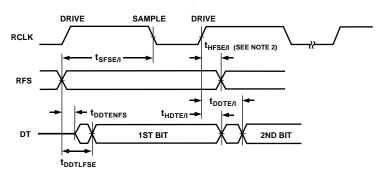

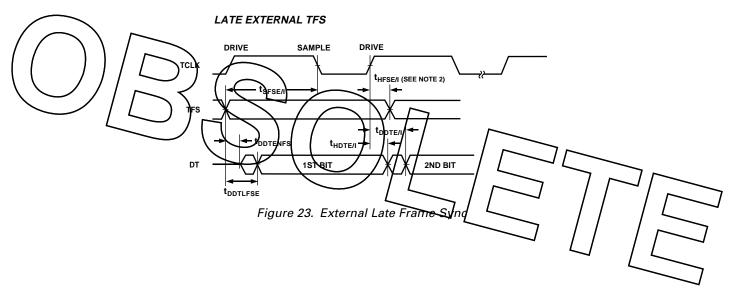

#### **Serial Ports**

The SHARC serial ports provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. Each SHARC has two serial ports. All eight of the AD14160/AD14160L serial ports are brought off-module.

The serial ports can operate at the full clock rate of the module, providing each with a maximum data rate of 40 Mbit/s. Independent transmit and receive functions provide more flexible communications. Serial port data can be automatically transferred to and from on-SHARC memory via DMA, and each of the serial ports offers time division multiplexed (TDM) multichannel mode.

The serial ports can operate with little-endian or big-endian transmission formats, with word lengths selectable from 3 bits to 32 bits. They offer selectable synchronization and transmit modes as well as optional  $\mu$ -law or A-law companding. Serial port clocks and frame syncs can be internally or externally generated.

### **Program Booting**

The AD14160/AD14160L supports automatic downloading of programs following power-up or a software reset. The SHARC offers four options for program booting: 1) from an 8-bit EPROM; 2) from a host processor; 3) through the link ports; and 4) no-boot. In no-boot mode, the SHARC starts executing instructions from address 0x0040 0004 in external memory. The boot mode is selected by the state of the following signals: BMS, EBOOT, and LBOOT.

On the AD14160/AD14160L, SHARC\_A's boot mode is separately controlled, while SHARCs B, C, and D are controlled as a group. With this flexibility, the AD14160/AD14160L can be configured to boot in any of the following methods.

#### Multiprocessor Host Booting

To boot multiple ADSP-21060 processors from a host, each ADSP-21060 must have its EBOOT, LBOOT and BMS pins configured for host booting: EBOOT = 0, LBOOT = 0, and BMS = 1. After system power-up, each ADSP-21060 will be in the idle state and the  $\overline{BRx}$  bus request lines will be deasserted. The host must assert the  $\overline{HBR}$  input and boot each ADSP-21060 by asserting its CS pin and downloading instructions.

### Multiprocessor EPROM Booting

There are two methods of booting the multiprocessor system from an EPROM.

SHARC\_A Is Booted, Which Then Boots the Others. The EBOOT pin on the SHARC\_A must be set high for EPROM booting. All other ADSP-21060s should be configured for host booting (EBOOT = 0, LBOOT = 0, and BMS = 1), which leaves them in the idle state at start-up and allows SHARC\_A

to become bus master and boot itself. Only the BMS pin of SHARC\_A is connected to the chip select of the EPROM. When SHARC\_A has finished booting, it can boot the remaining ADSP-21060s by writing to their external port DMA buffer 0 (EPB0) via multiprocessor memory space.

All ADSP-21060s Boot in Turn From a Single EPROM. The BMS signals from each ADSP-21060 may be wire-ORed together to drive the chip select pin of the EPROM. Each ADSP-21060 can boot in turn, according to its priority. When the last one has finished booting, it must inform the others (which may be in the idle state) that program execution can begin.

#### Multiprocessor Link Port Booting

Booting can also be accomplished from a single source through the link ports. Link Buffer 4 must always be used for booting. To simultaneously boot all of the ADSP-21060s, a parallel common connection is available through Link Port 4 on each of the processors. Or, using the daisy chain connection that exists between the processors' link ports, each ADSP-21060 can boot the next one in turn. In this case, the Link Assignment Register (LAR) must be programmed to configure the internal link ports with Link Buffer 4.

Multiprocessor Booting From External Memory

If external memory contains a program after reset, then

SHARC A should be set up for no boot mode, it will begin executing from address 0x0040 0004 in external memory. When

booting has completed the other ADSP-21000s may be booted

by SHARC A if they are set up for host booting, or they can

begin executing out of external memory if they are set up for no

boot mode. Multiprocessor bus arbitration will allow this booting

to occur in an orderly manner.

#### **Host Processor Interface**

The AD14160/AD14160L's host interface allows for easy connection to standard microprocessor buses, both 16-bit and 32-bit, with little additional hardware required. Asynchronous transfers at speeds up to the full clock rate of the module are supported. The host interface is accessed through the AD14160/AD14160L external port and is memory-mapped into the unified address space. Four channels of DMA are available for the host interface; code and data transfers are accomplished with low software overhead.

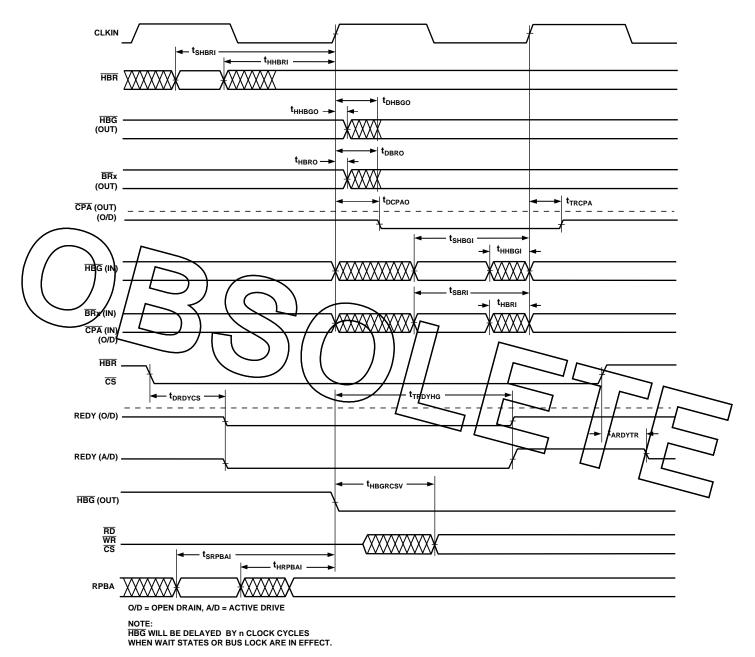

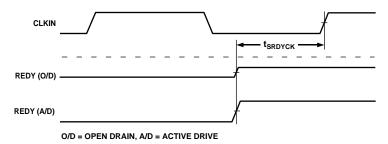

The host processor requests the AD14160/AD14160L's external bus with the host bus request (HBR), host bus grant (HBG), and ready (REDY) signals. The host can directly read and write the internal memory of the SHARCs, and can access the DMA channel setup and mailbox registers. Vector interrupt support is provided for efficient execution of host commands.

### Direct Memory Access (DMA) Controller

The SHARCs on-chip DMA control logic allows zero-overhead data transfers without processor intervention. The DMA controller operates independently and invisibly to each SHARCs processor core, allowing DMA operations to occur while the core is simultaneously executing its program instructions.

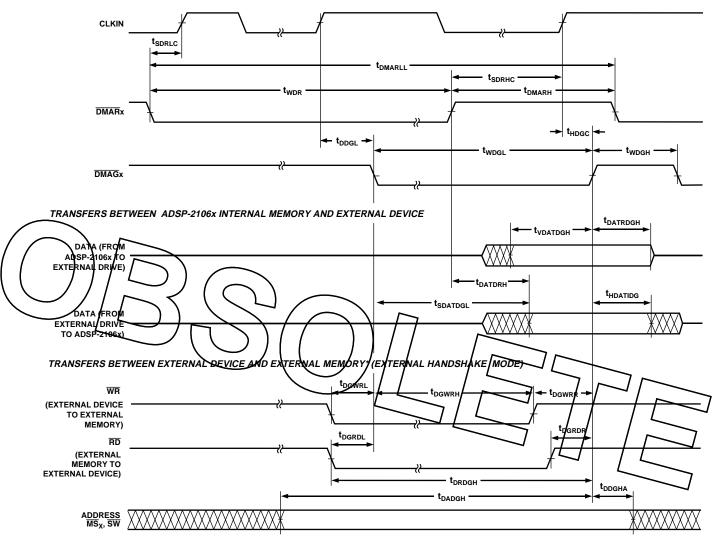

DMA transfers can occur between SHARC internal memory and either external memory, external peripherals, or a host processor. DMA transfers can also occur between the SHARC's internal memory and its serial ports or link ports. DMA transfers between external memory and external peripheral devices are another option. External bus packing to 16-, 32- or 48-bit words is performed during DMA transfers.

-6- REV. A

Ten channels of DMA are available on the SHARCs—two via the link ports, four via the serial ports, and four via the processor's external port (for either host processor, other SHARCs, memory, or I/O transfers). Four additional link port DMA channels are shared with serial port 1 and the external port. Programs can be downloaded to the SHARCs using DMA transfers. Asynchronous off-module peripherals can control two DMA channels using DMA Request/Grant lines (DMAR1-2, DMAG1-2). Other DMA features include interrupt generation upon completion of DMA transfers and DMA chaining for automatic linked DMA transfers.

#### **Development Tools**

The AD14160/AD14160L is supported with a complete set of software and hardware development tools, including an EZ-LAB® In-Circuit Emulator, and development software.

Analog Devices' ADSP 21000 Family Development Software includes an easy to use Assembler based on an algebraic syntax, an Assembly Library/Librarian) a Linker, an Instruction-Level Simulator, an ANSI C optimizing Compiler, the CBug<sup>TM</sup> C Source-Level Debugger, and a C Runting Library including DSP and mathematical functions. The Optimizing Compiler includes Numerical C extensions based on the work of the ANSI Numerical C Extensions Group Numerical C provides extensions to the C language for array selection, vector math operations, complex data types, circular pointers and variably dimensioned arrays. The ADSP-21000 Family Development Software is available for both the PC and Sun platforms.

The SHARC EZ-KIT combines the ADSP-21000 Family Development Software for the PC and the EZ-LAB Development Board in one package.

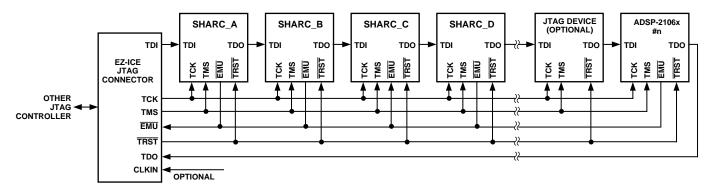

The ADSP-2106x EZ-ICE® Emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-2106x processor to monitor and control the target board processor during emulation. The

EZ-ICE provides full-speed emulation, allowing inspection and modification of memory, registers and processor stacks.

Nonintrusive in-circuit emulation is assured by the use of the processor's JTAG interface—the emulator does not affect target system loading or timing.

Further details and ordering information are available in the *ADSP-21000 Family Hardware & Software Development Tools* data sheet (ADDS-2100xx-TOOLS). This data sheet can be requested from any Analog Devices sales office or distributor, or from the Literature Center.

In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the SHARC processor family. Hardware tools include SHARC PC plug-in cards, multiprocessor SHARC VME boards, and daughter card modules with multiple SHARCs and additional memory. These modules are based on the SHARCPAC™ module specification. Third party software tools include an Ada compiler, DSP libraries, operating systems and block diagram design tools.

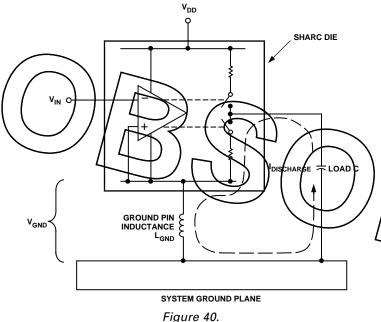

### Other Package Details

The AD14160/AD14160L contains 14 on-module 0.1 microfarad bypass capacitors. It is recommended that in the target system at least four additional capacitors, of 0.018 microfarad value, be placed around the module—one near each of the four comers.

The top surface, Ild, of the AD14160/AD14160L is electrically connected to GND.

#### **Additional Information**

This data sheet provides a general overview of the AD14160/AD14160L architecture and functionality. For detailed information on the ADSP-2106x SHARC and the ADSP-21000 Family core architecture and instruction set, refer to the ADSP-2106x SHARC *User's Manual.*

EZ-ICE and EZ-LAB are registered trademarks of Analog Devices, Inc. CBug and SHARCPAC are trademarks of Analog Devices, Inc.

REV. A \_7\_

### PIN FUNCTION DESCRIPTIONS

AD14160/AD14160L pin definitions are listed below. Inputs identified as synchronous (S) must meet timing requirements with respect to CLKIN (or with respect to TCK for TMS, TDI). Inputs identified as asynchronous (A) can be asserted asynchronously to CLKIN (or to TCK for TRST).

Unused inputs should be tied or pulled to  $V_{DD}$  or GND, except for ADDR<sub>31-0</sub>, DATA<sub>47-0</sub>, FLAG<sub>2-0</sub>,  $\overline{SW}$ , and inputs that have internal pull-up or pull-down resistors (CPA, ACK, DTx, DRx,

TCLKx, RCLKx, LxDAT<sub>3-0</sub>, LxCLK, LxACK, TMS and TDI)—these pins can be left floating. These pins have a logic-level hold circuit that prevents the input from floating internally.

A = Asynchronous O = Output (A/D) = Active Drive

G = Ground P = Power Supply (O/D) = Open Drain

I = Input S = Synchronous

T = Three-State (when  $\overline{SBTS}$  is asserted, or when the AD14160/AD14160L is a bus slave)

| Pin                                 | Type  | Function                                                                                                                                                                                                                                                   |

|-------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ADDR_{31-0}$                       | I/O/T | <b>External Bus Address.</b> (Common to all SHARCs) The AD14160/AD14160L outputs addresses for external memory and peripherals on these pins. In a multiprocessor system, the bus master outputs ad-                                                       |

| _                                   |       | dresses for read/writes on the internal memory or IOP registers of slave ADSP-2106xs. The AD14160/                                                                                                                                                         |

|                                     | \ \   | AD14160L inputs addresses when a host processor or multiprocessing bus master is reading or writing the internal memory or IOP registers of internal ADSP-21060s.                                                                                          |

| DATA <sub>47-0</sub>                |       | External Bus Data. (Common to all SHARCs) The AD14160/AD14160L inputs and outputs data and                                                                                                                                                                 |

| [ [ ]                               |       | instructions on these pigs. 32-bit single-precision floating-point data and 32-bit fixed-point data is trans-                                                                                                                                              |

| $\setminus \bigcup$                 |       | ferred over bits 47-19 of the bus 40-bit extended-precision floating-point data is transferred over bits 47-                                                                                                                                               |

|                                     | [ [ [ | 8 of the bus. 16-bit short word data is transferred over bits 31-16 of the bus. In PROM boot mode, 8-bit data is transferred over bits 23-16. Pull up resistors on unused DATA pins are not necessary.                                                     |

| $\overline{\text{MS}}_{3\text{-}0}$ | O/T   | Memory Select Lines (Common to all SHAKCs) These lines are asserted (low) as chip selects for the                                                                                                                                                          |

|                                     |       | corresponding banks of external memory. Memory bank size must be defined in the individual ADSP-                                                                                                                                                           |

|                                     |       | 21060's system control registers (SY8COX). The $\overline{MS}_{3-0}$ lines are decoded memory address lines that change at the same time as the other address lines. When no external memory access is occurring the $\overline{MS}_{3-0}$                 |

|                                     |       | lines are inactive; they are active, however, when a conditional memory access instruction is executed, whether                                                                                                                                            |

|                                     |       | or not the condition is true. $\overline{\text{MS}}_0$ can be used with the PAGE signal to implement a bank of DRAM memory                                                                                                                                 |

|                                     |       | (Bank 0). In a multiprocessing system, the $\overline{\text{MS}}_{3-0}$ lines are output by the bus master.                                                                                                                                                |

| $\overline{\text{RD}}$              | I/O/T | Memory Read Strobe. (Common to all SHARCs) This pin is asserted (low) when the AD 14160/                                                                                                                                                                   |

|                                     |       | AD14160L reads from external devices or when the internal memory of internal ADSP-210 exs is being                                                                                                                                                         |

|                                     |       | accessed. External devices (including other ADSP-2106xs) must assert RD to read from the AD14160/                                                                                                                                                          |

|                                     |       | AD14160L's internal memory. In a multiprocessing system, $\overline{RD}$ is output by the bus master and is input by all other ADSP-2106xs.                                                                                                                |

| $\overline{ m WR}$                  | I/O/T | <b>Memory Write Strobe.</b> (Common to all SHARCs) This pin is asserted (low) when the AD14160/                                                                                                                                                            |

|                                     |       | AD14160L writes to external devices or when the internal memory of internal ADSP-2106xs is being                                                                                                                                                           |

|                                     |       | accessed. External devices (including other ADSP-2106xs) must assert $\overline{WR}$ to write to the AD14160/                                                                                                                                              |

|                                     |       | AD14160L's internal memory. In a multiprocessing system $\overline{WR}$ is output by the bus master and is input by all other ADSP-2106xs.                                                                                                                 |

| PAGE                                | O/T   | DRAM Page Boundary. (Common to all SHARCs) The AD14160/AD14160L asserts this pin to signal                                                                                                                                                                 |

|                                     |       | that an external DRAM page boundary has been crossed. DRAM page size must be defined in the indi-                                                                                                                                                          |

|                                     |       | vidual ADSP-21060's memory control register (WAIT). DRAM can only be implemented in external memory Bank 0; the PAGE signal can only be activated for Bank 0 accesses. In a multiprocessing system,                                                        |

|                                     |       | PAGE is output by the bus master.                                                                                                                                                                                                                          |

| ADRCLK                              | O/T   | Clock Output Reference. (Common to all SHARCs) In a multiprocessing system, ADRCLK is output                                                                                                                                                               |

|                                     |       | by the bus master.                                                                                                                                                                                                                                         |

| $\overline{\text{SW}}$              | I/O/T | Synchronous Write Select. (Common to all SHARCs) This signal is used to interface the AD14160/                                                                                                                                                             |

|                                     |       | AD14160L to synchronous memory devices (including other ADSP-2106xs). The AD14160/AD14160L                                                                                                                                                                 |

|                                     |       | asserts $\overline{SW}$ (low) to provide an early indication of an impending write cycle, which can be aborted if $\overline{WR}$ is not later asserted (e.g., in a conditional write instruction). In a multiprocessing system, $\overline{SW}$ is output |

|                                     |       | by the bus master and is input by all other ADSP-2106xs to determine if the multiprocessor memory                                                                                                                                                          |

|                                     |       | access is a read or write. $\overline{SW}$ is asserted at the same time as the address output. A host processor using                                                                                                                                      |

|                                     |       | synchronous writes must assert this pin when writing to the AD14160/AD14160L.                                                                                                                                                                              |

| ACK                                 | I/O/S | Memory Acknowledge. (Common to all SHARCs) External devices can deassert ACK (low) to add                                                                                                                                                                  |

|                                     |       | wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other pe-                                                                                                                                                     |

|                                     |       | ripherals to hold off completion of an external memory access. The AD14160/AD14160L deasserts ACK, as an output, to add wait states to a synchronous access of its internal memory. In a multiprocessing                                                   |

|                                     |       | system, a slave ADSP-2106x deasserts the bus master's ACK input to add wait state(s) to an access of its                                                                                                                                                   |

|                                     |       | internal memory. The bus master has a keeper latch on its ACK pin that maintains the input at the level                                                                                                                                                    |

|                                     |       | it was last driven to.                                                                                                                                                                                                                                     |

|                                     |       |                                                                                                                                                                                                                                                            |

-8- REV. A

| Pin                                   | Type  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBTS                                  | I/S   | Suspend Bus Three-State. (Common to all SHARCs) External devices can assert \$\overline{\text{SBTS}}\$ (low) to place the external bus address, data, selects, and strobes in a high impedance state for the following cycle If the AD14160/AD14160L attempts to access external memory while \$\overline{\text{SBTS}}\$ is asserted, the processor will halt and the memory access will not be completed until \$\overline{\text{SBTS}}\$ is deasserted. \$\overline{\text{SBTS}}\$ should only be used to recover from host processor/AD14160/AD14160L deadlock, or used with a DRAM controller. |

| HBR                                   | I/A   | Host Bus Request. (Common to all SHARCs) Must be asserted by a host processor to request control of the AD14160/AD14160L's external bus. When $\overline{HBR}$ is asserted in a multiprocessing system, the ADSP-2106x that is bus master will relinquish the bus and assert $\overline{HBG}$ . To relinquish the bus, the ADSP-2106x places the address, data, select, and strobe lines in a high impedance state. $\overline{HBR}$ has priority over all ADSP-2106x bus requests ( $\overline{BR}_{6-1}$ ) in a multiprocessing system.                                                          |

| HBG                                   | I/O   | Host Bus Grant. (Common to all SHARCs) Acknowledges an $\overline{HBR}$ bus request, indicating that the host processor may take control of the external bus. $\overline{HBG}$ is asserted (held low) by the AD14160/AD14160L until $\overline{HBR}$ is released. In a multiprocessing system, $\overline{HBG}$ is output by the ADSP-2106x bus master and is monitored by all others.                                                                                                                                                                                                             |

| CSA )                                 | I/A/  | Chip Select. Asserted by host processor to select SHARC_A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $\overline{\text{CSB}}$               | / I/A | Chip Select. Asserted by host processor to select SHARC_B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| cse /                                 | I/A   | Chip Select Ascerted by host processor to select SHARC_C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CSD                                   | t/A   | Chip Select. Asserted by Most processor to select SHARC_D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| REDY (O/D)                            | 0     | Host Bus Acknowledge. (Common to all SHARCs) The AD14160/AD14160L deasserts REDY (low) to add wait states to an asynchronous access of its internal memory or IOP registers by a host. Open drain output (O/D) by default; can be programmed in ADREDY bit of SYSCON register of individual ADSP-21060s to be active drive (A/D). REDY will only be output if the CS and HBR inputs are asserted.                                                                                                                                                                                                  |

| $\overline{\mathrm{BR}}_{6\text{-}1}$ | I/O/S | Multiprocessing Bus Requests. (Common to all SHARQs) Used by multiprocessing ADSP-2106xs to arbitrate for bus mastership. An ADSP-2106x only drives its own $\overline{BR}x$ line (corresponding to the value of its ID2-0 inputs) and monitors all others. In a multiprocessor system with less than six ADSP-2106x3, the unused $\overline{BR}x$ pins should be pulled high; $\overline{BR}_{4-1}$ must not be pulled high or low because they are outputs.                                                                                                                                      |

| IDy2-0                                | I     | Multiprocessing ID. (Individual ID2–0 from $y = SHARC_A$ , SHARC_B, SHARC_C, SHARC_D.) Determines which multiprocessing bus request $(\overline{BR1}-\overline{BR6})$ is used by individual ADSP-2106x's. ID = 001 corresponds to $\overline{BR1}$ , ID = 010 corresponds to $\overline{BR2}$ , etc. ID = 000 is reserved for single processor systems. These lines are a system configuration selection, which should be hardwired or only changed at reset.                                                                                                                                      |

| RPBA                                  | I/S   | <b>Rotating Priority Bus Arbitration Select.</b> (Common to all SHARCs) When RPBA is high, rotating priority for multiprocessor bus arbitration is selected. When RPBA is low, fixed priority is selected. This signal is a system configuration selection that must be set to the same value on every ADSP-2106x. If the value of RPBA is changed during system operation, it must be changed in the same CLKIN cycle on every ADSP-2106x.                                                                                                                                                        |

| CPAy (O/D)                            | I/O   | Core Priority Access. (y = SHARC_A, B, C, D) Asserting its CPA pin allows the core processor of an ADSP-2106x bus slave to interrupt background DMA transfers and gain access to the external bus. CPA is an open drain output that is connected to all ADSP-2106x in the system if this function is required. The CPA pin of each internal ADSP-21060 is brought out individually. The CPA pin has an internal 5 k $\Omega$ pull-up resistor. If core access priority is not required in a system, the CPA pin should be left unconnected.                                                        |

| DTy0                                  | O/T   | <b>Data Transmit</b> (Serial Port 0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D). DT pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DRy0                                  | I     | <b>Data Receive</b> (Serial Port 0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D). DR pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TCLKy0                                | I/O   | Transmit Clock (Serial Port 0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D). TCLK pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RCLKy0                                | I/O   | <b>Receive Clock</b> (Serial Port 0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D). RCLK pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TFSy0                                 | I/O   | Transmit Frame Sync (Serial Port 0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RFSy0                                 | I/O   | Receive Frame Sync (Serial Port 0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

REV. A \_9\_

| Pin       | Type               | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTy1      | O/T                | <b>Data Transmit</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) DT pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                     |

| DRy1      | I                  | <b>Data Receive</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) DR pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                              |

| TCLKy1    | I/O                | <b>Transmit Clock</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) TCLK pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                  |

| RCLKy1    | I/O                | <b>Receive Clock</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) RCLK pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                   |

| TFSy1     | I/O                | Transmit Frame Sync (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D)                                                                                                                                                                                                                                                                                                                                    |

| RFSy1     | I/O                | Receive Frame Sync (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D)                                                                                                                                                                                                                                                                                                                                     |

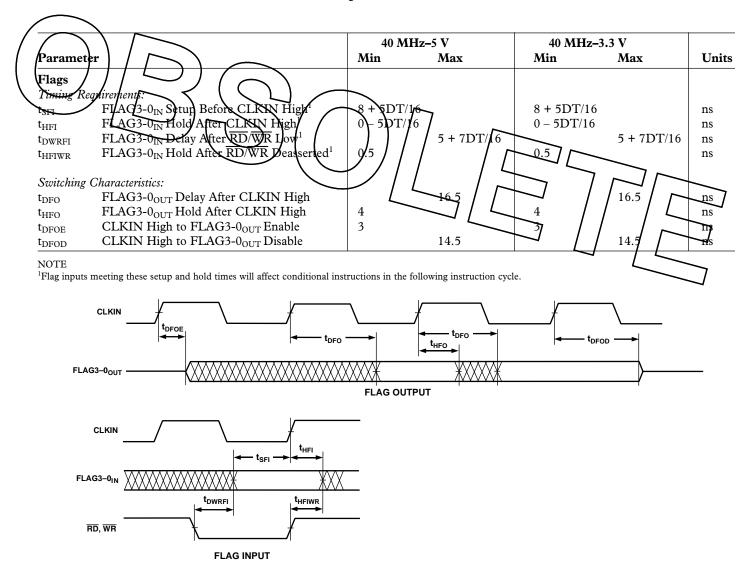

| FLAGy3-0  | I/O/A              | Flag Pins. (Individual FLAG3-0 from y = SHARC_A, SHARC_B, SHARC_C, SHARC_D) Each is configured via control bits as either an input or output. As an input, it can be tested as a condition. As an output, it can be used to signal external peripherals.                                                                                                                                                                  |

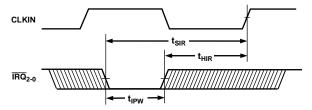

| RQy2-0    | )/A/ [             | Interrupt Request Lines. (Individual IRQ2-0 from y = SHARC_A, SHARC_B, SHARC_C, SHARC_D)  May be either edge-triggered or level-sensitive.                                                                                                                                                                                                                                                                                |

| DMARI     | / I/k /            | DMA Request L(DMA Chaparel 7). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                              |

| DMAR2     | I/A                | DMA Request 2 (DMA Channel 8). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                              |

| DMAG1     | O/T                | DMA Grant (DMA Channel 7). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                                  |

| DMAG2     | O/T                | DMA Grant 2 (DMA Channel 8). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                                |

| LyxCLK    | I/O                | Link Port Clock (y = SHARC_A, B, C, D; x = Link Ports 1/2, 3, 4). Each LyxCLK pin has a 50 kΩ internal pull-down resistor which is enabled or disabled by the LPDRD bit of the LCOM register, of the ADSP-20160.                                                                                                                                                                                                          |

| LyxDAT3-0 | I/O                | <b>Link Port Data</b> (y = SHARC_A, B, C, D; x = Link Ports 1, 2, 3, 4) Each LyxDAT pin has a 50 k $\Omega$ internal pull-down resistor which is enabled or disabled by the LFDRD bit of the LCOM register, of the ADSP-21060.                                                                                                                                                                                            |

| LyxACK    | I/O                | <b>Link Port Acknowledge</b> (y = SHARC_A, B, C, D; x = Link Ports 1, 2, 3, 4) <sup>1</sup> . Each LyxACK pin has a 50 k $\Omega$ internal pull-down resistor which is enabled or disabled by the LPDRD bit of the LCOM register, of the ADSP-21060.                                                                                                                                                                      |

| ЕВООТА    | I                  | <b>EPROM Boot Select.</b> (SHARC_A) When EBOOTA is high, <u>SHARC_A</u> is configured for booting from an 8-bit EPROM. When EBOOTA is low, the LBOOTA and <u>BMSA</u> inputs determine booting mode for SHARC_A. See the following table. This signal is a system configuration selection which should be hardwired.                                                                                                      |

| LBOOTA    | I                  | <b>Link Boot.</b> When LBOOTA is high, SHARC_A is configured for link port booting. When LBOOTA is low, SHARC_A is configured for host processor booting or no booting. See the following table. This signal is a system configuration selection which should be hardwired.                                                                                                                                               |

| BMSA      | I/O/T <sup>2</sup> | <b>Boot Memory Select.</b> <i>Output:</i> Used as chip select for boot EPROM devices (when EBOOTA = 1, LBOOTA = 0). In a multiprocessor system, BMS is output by the bus master. <i>Input:</i> When low, indicates that no booting will occur and that SHARC_A will begin executing instructions from external memory. See the following table. This input is a system configuration selection which should be hardwired. |

| EBOOTBCD  | I                  | <b>EPROM Boot Select.</b> (Common to SHARC_B, SHARC_C, SHARC_D) When EBOOTBCD is high, SHARC_B, C, D are configured for booting from an 8-bit EPROM. When EBOOTBCD is low, the LBOOTBCD and BMSBCD inputs determine booting mode for SHARC_B, C and D. See the following table. This signal is a system configuration selection which should be hardwired.                                                                |

| LBOOTBCD  | I                  | <b>LINK Boot.</b> (Common to SHARC_B, SHARC_C, SHARC_D) When LBOOTBCD is high, SHARC_B, C, D are configured for link port booting. When LBOOTBCD is low, SHARC_B, C, D are configured for host processor booting or no booting. See the following table. This signal is a system configuration selection which should be hardwired.                                                                                       |

-10- REV. A

| Pin               | Type               | Function                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| BMSBCD            | I/O/T <sup>2</sup> | <b>Boot Memory Select.</b> <i>Output:</i> Used as chip select for boot EPROM devices (when EBOOTBCD = 1, LBOOTBCD = 0). In a multiprocessor system, BMS is output by the bus master. <i>Input:</i> When low, indicates that no booting will occur and that SHARC_B, C, D will begin executing instructions from external memory. See table below. This input is a system configuration selection which should be hardwired. |  |  |  |  |  |  |

|                   |                    | EBOOT LBOOT BMS Booting Mode                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                   |                    | 1 0 Output EPROM (Connect BMS to EPROM chip select) 0 0 1 (Input) Host Processor 0 1 1 (Input) Link Port 0 0 0 (Input) No Booting. Processor executes from external memory. 0 1 0 (Input) Reserved 1 x (Input) Reserved                                                                                                                                                                                                     |  |  |  |  |  |  |

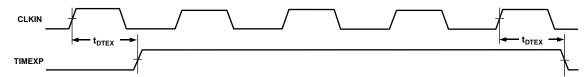

| TIMEXPy           | 1                  | <b>Timer Expired.</b> (Individual TIMEXP from y = SHARC_A, SHARC_B, SHARC_C, SHARC_D) Asserted for four cycles when the timer is enabled and TCOUNT decrements to zero.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| CLKIN             | I L                | Clock In (Cosmon to all SHARCs) External clock input to the AD14160/AD14160L. The instruction cycle rate is equal to CLKIN. CLKIN may not be halted, changed, or operated below the minimum specified requency.  Module Reset. (Common to all SHARCs) Resets the AD14160/AD14160L to a known state. This input plus be asserted (low) at power-up.                                                                          |  |  |  |  |  |  |

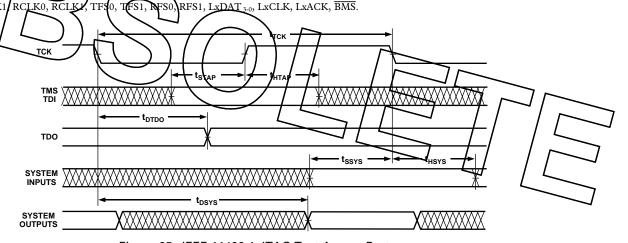

| TCK               | I                  | Test Clock (JTAG). (Common to all SHARCs) Provides an asynchronous clock for JTAG boundary scan.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| TMS               | I/S                | Test Mode Select (JTAG). (Common to all SHARCs) Used to control the test state machine. TMS has a 20 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| TDI               | I/S                | Test Data Input (JTAG). Provides serial data for the boundary scan logic chain starting at SHARC_A.  TDI has a 20 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| TDO               | О                  | Test Data Output (JTAG). Serial scan output of the boundary scan chain path, from SHARC_D.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| TRST              | I/A                | <b>Test Reset (JTAG).</b> (Common to all SHARCs) Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held low for proper operation of the AD14160/AD14160L. TRST has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                             |  |  |  |  |  |  |

| EMU (O/D)         | О                  | <b>Emulation Status.</b> (Common to all SHARCs) Must be connected to the ADSP-2106x EZ-ICE target board connector <i>only</i> .                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| $V_{\mathrm{DD}}$ | P                  | <b>Power Supply.</b> Nominally +5.0 V dc for 5 V devices or +3.3 V dc for 3.3 V devices (50 pins).                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| GND               | G                  | Power Supply Return. (64 pins).                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

REV. A -11-

NOTES  $^1LINK$  PORTS 0 and 5 are connected internally as described earlier in Link Port I/O.  $^2Three\mbox{-statable}$  only in EPROM boot mode (when  $\overline{BMS}$  is an output).

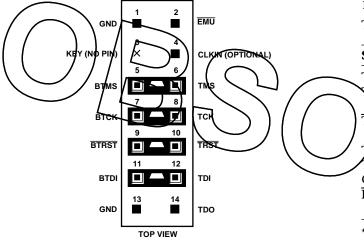

### TARGET BOARD CONNECTOR FOR EZ-ICE PROBE

The ADSP-2106x EZ-ICE Emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-2106x to monitor and control the target board processor during emulation. The EZ-ICE probe requires that the AD14160/AD14160L's CLKIN (optional), TMS, TCK, TRST, TDI, TDO, EMU and GND signals be made accessible on the target system via a 14-pin connector (a pin strip header) such as that shown in Figure 6. The EZ-ICE probe plugs directly onto this connector for chip-on-board emulation. You must add this connector to your target board design if you intend to use the ADSP-2106x EZ-ICE. The length of the traces between the connector and the AD14160/AD14160L's JTAG pins should be as short as possible.

Figure 6. Target Board Connector for ADSP-2106x EZ-ICE Emulator (Jumpers in Place)

The 14-pin, 2-row pin strip header is keyed at the Pin 3 location; Pin 3 must be removed from the header. The pins must be 0.025 inch square and at least 0.20 inch in length. Pin spacing should be  $0.1 \times 0.1$  inches. Pin strip headers are available from vendors such as 3M, McKenzie and Samtec.

The BTMS, BTCK,  $\overline{BTRST}$  and BTDI signals are provided so that the test access port can also be used for board-level testing. When the connector is not being used for emulation, place jumpers between the Bxxx pins and the xxx pins as shown in Figure 6. If you are not going to use the test access port for board testing, tie  $\overline{BTRST}$  to GND and tie or pull up BTCK to  $\overline{V_{DD}}$ . The  $\overline{TRST}$  pin must be asserted after power-up (through  $\overline{BTRST}$  on the connector) or held low for proper operation of the AD14160/AD14160L. None of the Bxxx pins (Pins 5, 7, 9, 11) are connected on the EZ-ICE probe.

The JTAG signals are terminated on the EZ-ICE probe as follows:

| Signal     | Termination                                                  |

|------------|--------------------------------------------------------------|

| TMS        | Driven through 22 Ω Resistor (16 mA/3.2 mA Driver)           |

| ACK ~      | Driven at 10 MHz through 22 Ω Resistor (16 mA/               |

| ١ ١ /      | B.2 mA Driver)                                               |

| TRST       | Driven by Open Drain Driver* (Pulled Up by On-Chip           |

| / / / .    | 20 kΩ Resistor                                               |

| 7/DI/ /    | Driven by 16 mA/3.2 mA Driver                                |

| /TD/D /    | One TTI Load, No Termination                                 |

| CL/KIN-    | One TTL Load, No Termination (Optional Signal)               |

| EMU        | 4.7 kD Pull Up Resistor, One TTL Load Open-Drain             |

|            | Output from ADSP 2106x)                                      |

| *TRST is c | driven low until the EZ-ICE probe is turned on by the EZ-ICE |

|            | after the invocation command).                               |

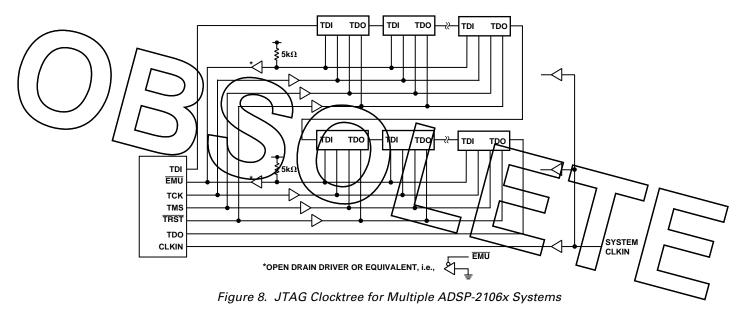

Figure 7 shows JTAG scan path connections for the multi-processor system.

Figure 7. JTAG Scan Path Connections for the AD14160/AD14160L

–12– REV. A

Connecting CLKIN to Pin 4 of the EZ-ICE header is optional. The emulator only uses CLKIN when directed to perform operations such as starting, stopping and single-stepping multiple ADSP-2106xs in a synchronous manner. If you do not need these operations to occur synchronously on the multiple processors, simply tie Pin 4 of the EZ-ICE header to ground.

If synchronous multiprocessor operations are needed and CLKIN is connected, clock skew between the AD14160/ AD14160L and the CLKIN pin on the EZ-ICE header must be minimal. If the skew is too large, synchronous operations may be off by one cycle between processors. For synchronous multiprocessor operation TCK, TMS, CLKIN and  $\overline{\rm EMU}$  should be

treated as critical signals in terms of skew, and should be laid out as short as possible on your board. If TCK, TMS and CLKIN are driving a large number of ADSP-2106xs (more than eight) in your system, then treat them as a "clock tree" using multiple drivers to minimize skew. (See Figure 8 JTAG Clock Tree and Clock Distribution in the "High Frequency Design Considerations" section of the ADSP-2106x User's Manual).

If synchronous multiprocessor operations are not needed (i.e., CLKIN is not connected), just use appropriate parallel termination on TCK and TMS. TDI, TDO, EMU and TRST are not critical signals in terms of skew.

REV. A -13-

## AD14160/AD14160L—SPECIFICATIONS

## RECOMMENDED OPERATING CONDITIONS

|                     |                            | B Grade |      |      | K G  |      |       |

|---------------------|----------------------------|---------|------|------|------|------|-------|

| Paramete            | r                          |         | Min  | Max  | Min  | Max  | Units |

| $\overline{V_{DD}}$ | Supply Voltage (5 V)       |         | 4.75 | 5.25 | 4.75 | 5.25 | V     |

| DD                  | Supply Voltage (3.3 V)     |         | 3.15 | 3.6  | 3.15 | 3.6  | V     |

| $T_{CASE}$          | Case Operating Temperature |         | -40  | +100 | 0    | +85  | °C    |

## **ELECTRICAL CHARACTERISTICS (5 V, 3.3 V SUPPLY)**

| Parame              | ter                                             | Case<br>Temp | Test<br>Level | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Min | 5 V<br>Typ | Max                   |               | 3.3 V<br>Typ | Max                   | Units |

|---------------------|-------------------------------------------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----------------------|---------------|--------------|-----------------------|-------|

| V <sub>IH1</sub>    | High Level Input Voltage <sup>1</sup>           | Full         | I             | @ V <sub>DD</sub> = max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0 |            | V <sub>DD</sub> + 0.5 | 2.0           |              | V <sub>DD</sub> + 0.5 |       |