# **Rochester Electronics Manufactured Components**

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# BCD DECADE/MODULO 16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS

The SN54/74LS168 and SN54/74LS169 are fully synchronous 4-stage up/down counters featuring a preset capability for programmable operation, carry lookahead for easy cascading and a U/D input to control the direction of counting. The SN54/74LS168 counts in a BCD decade (8, 4, 2, 1) sequence, while the SN54/74LS169 operates in a Modulo 16 binary sequence. All state changes, whether in counting or parallel loading, are initiated by the LOW-to-HIGH transition of the clock.

- Low Power Dissipation 100 mW Typical

- High-Speed Count Frequency 30 MHz Typical

- Fully Synchronous Operation

- Full Carry Lookahead for Easy Cascading

- Single Up/Down Control Input

- Positive Edge-Trigger Operation

- Input Clamp Diodes Limit High-Speed Termination Effects

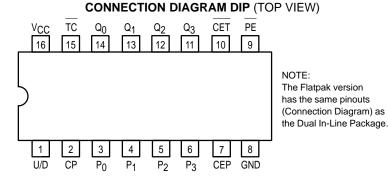

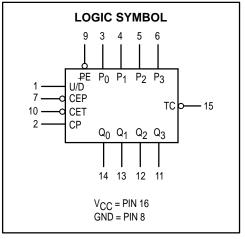

**PIN NAMES** LOADING (Note a) HIGH LOW CEP Count Enable Parallel (Active LOW) Input 0.5 U.L. 0.25 U.L. CET Count Enable Trickle (Active LOW) Input 0.5 U.L. 1.0 U.L. CP Clock Pulse (Active positive going edge) Input 0.5 U.L. 0.25 U.L. Parallel Enable (Active LOW) Input 0.5 U.L. PE 0.25 U.L. U/D Up-Down Count Control Input 0.5 U.L. 0.25 U.L.  $P_0 - P_3$ Parallel Data Inputs 0.5 U.L. 0.25 U.L.  $Q_0 - Q_3$ Flip-Flop Outputs 10 U.L. 5 (2.5) U.L. TC Terminal Count (Active LOW) Output 10 U.L. 5 (2.5) U.L. NOTES:

a. 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

# SN54/74LS168 SN54/74LS169

### BCD DECADE/MODULO 16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS

#### LOW POWER SCHOTTKY

### FAST AND LS TTL DATA

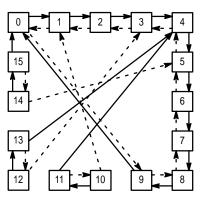

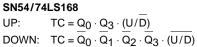

### STATE DIAGRAMS

Count Up Count Down

- ->

SN54/74LS168 UP/DOWN DECADE COUNTER SN54/74LS169

#### SN54/74LS169

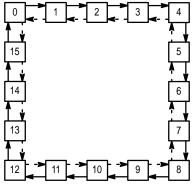

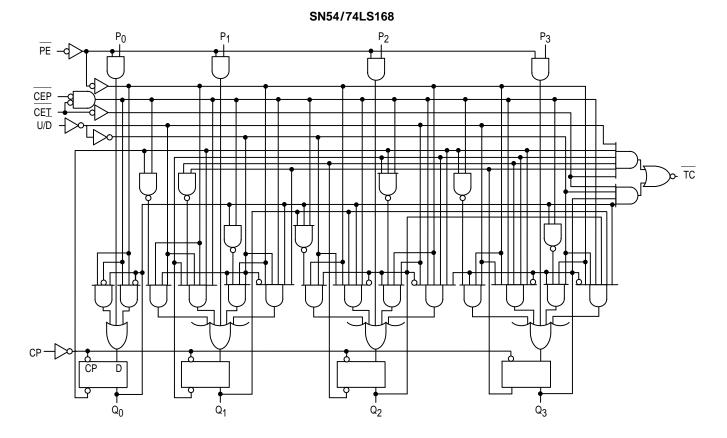

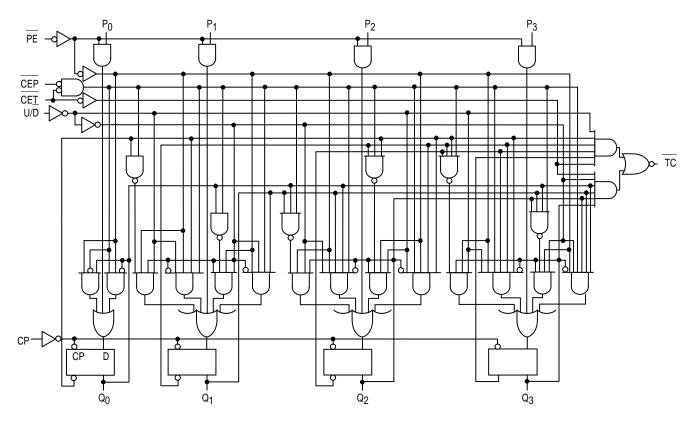

LOGIC DIAGRAMS

LOGIC DIAGRAMS (continued)

### **GUARANTEED OPERATING RANGES**

| Symbol         | Parameter                           |          | Min         | Тур        | Max         | Unit |

|----------------|-------------------------------------|----------|-------------|------------|-------------|------|

| VCC            | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| т <sub>А</sub> | Operating Ambient Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| ЮН             | Output Current — High               | 54, 74   |             |            | -0.4        | mA   |

| IOL            | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

|                 |                                                 |        |     | Limits |              |      |                                                                                                  |                        |

|-----------------|-------------------------------------------------|--------|-----|--------|--------------|------|--------------------------------------------------------------------------------------------------|------------------------|

| Symbol          | Parameter                                       |        | Min | Тур    | Max          | Unit | Tes                                                                                              | t Conditions           |

| VIH             | Input HIGH Voltage                              |        | 2.0 |        |              | V    | Guaranteed Input HIGH Voltage for<br>All Inputs                                                  |                        |

|                 | Input LOW Voltage                               | 54     |     |        | 0.7          | v    | Guaranteed Input LOW Voltage for<br>All Inputs                                                   |                        |

| VIL             |                                                 | 74     |     |        | 0.8          |      |                                                                                                  |                        |

| VIK             | Input Clamp Diode Voltage                       |        |     | -0.65  | -1.5         | V    | $V_{CC} = MIN, I_{IN} = -18 \text{ mA}$                                                          |                        |

| V <sub>OH</sub> | Output HIGH Voltage                             | 54     | 2.5 | 3.5    |              | V    | $V_{CC} = MIN, I_{OH} = MAX, V_{IN} = V_{IH}$<br>or $V_{IL}$ per Truth Table                     |                        |

|                 |                                                 | 74     | 2.7 | 3.5    |              | V    |                                                                                                  |                        |

| V <sub>OL</sub> | Output LOW Voltage                              | 54, 74 |     | 0.25   | 0.4          | V    | $V_{OL} = 4.0 \text{ mA}$ $V_{CC} = V_{CC} \text{ MIN},$<br>$V_{IN} = V_{IL} \text{ or } V_{IH}$ | $V_{CC} = V_{CC} MIN,$ |

|                 |                                                 | 74     |     | 0.35   | 0.5          | V    | IOL = 8.0 mA                                                                                     | per Truth Table        |

| ин              | Input HIGH Current<br>Other Inputs<br>CET Input |        |     |        | 20<br>40     | μΑ   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7 V                                                   |                        |

|                 | <u>Othe</u> r Input<br>CET Input                |        |     |        | 0.1<br>0.2   | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0 V                                                   |                        |

| Ι <sub>ΙL</sub> | Input LOW Current<br>Other Input<br>CET Input   |        |     |        | -0.4<br>-0.8 | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                                           | = 0.4 V                |

| IOS             | Short Circuit Current (Note 1)                  |        | -20 |        | -100         | mA   | $V_{CC} = MAX$                                                                                   |                        |

| ICC             | Power Supply Current                            |        |     |        | 34           | mA   | V <sub>CC</sub> = MAX                                                                            |                        |

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Note 1: Not more than one output should be shorted at one time, nor for more than 1 second.

#### FUNCTIONAL DESCRIPTION

The SN54/74LS168 and SN54/74LS169 use edgetriggered D-type flip-flops that have no constraints on changing the control or data input signals in either state of the Clock. The only requirement is that the various inputs attain the desired state at least a set-up time before the rising edge of the clock and remain valid for the recommended hold time thereafter.

The parallel load operation takes precedence over the <u>other</u> operations, as indicated in the Mode Select Table. When PE is LOW, the data on the  $P_0-P_3$  inputs enters the flip-flops on the next <u>rising</u> edge of the Clock. In orde<u>r for</u> counting to occur, both CEP and CET must be LOW and PE must be HIGH. The U/D input then determines the direction of counting.

The Terminal Count (TC) output is normally HIGH and goes LOW, provided that CET is LOW, when a counter reaches zero in the COUNT DOWN mode or reaches <u>15</u> (9 for the SN54/74LS168) in the COUNT UP mode. The <u>TC</u> output state is not <u>a</u> function of the Count Enable Parallel (CEP) input level. The TC output of the SN54/74LS168 decade counter can also be LOW in the illegal states 11, 13 and 15, which can occur when power is turned on or via parallel loading. If illegal state occurs, the SN54/74LS168 will ret<u>urn</u> to the legitimate sequence within two counts. Since the TC signal is derived by decoding the flip-flop\_states, there exists the possibility of decoding spikes on TC. For this reason the use of TC as a clock signal is not recommended.

| PE | CEP | CET | U/D | Action on Rising Clock Edge |

|----|-----|-----|-----|-----------------------------|

| L  | X   | X   | X   | Load (Pn → Qn)              |

| H  | L   | L   | H   | Count Up (increment)        |

| H  | L   | L   | L   | Count Down (decrement)      |

| H  | H   | X   | X   | No Change (Hold)            |

| H  | X   | H   | X   | No Change (Hold)            |

#### MODE SELECT TABLE

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

### **AC CHARACTERISTICS** (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

|                                      |                                                  | Limits |          |          |      |                                                   |  |  |

|--------------------------------------|--------------------------------------------------|--------|----------|----------|------|---------------------------------------------------|--|--|

| Symbol                               | Parameter                                        | Min    | Тур      | Max      | Unit | Test Conditions                                   |  |  |

| fMAX                                 | Maximum Clock Frequency                          | 25     | 32       |          | MHz  |                                                   |  |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propaga <u>tion</u> Delay,<br>Clock to TC        |        | 23<br>23 | 35<br>35 | ns   |                                                   |  |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay,<br>Clock to any Q             |        | 13<br>15 | 20<br>23 | ns   | V <sub>CC</sub> = 5.0 V<br>C <sub>L</sub> = 15 pF |  |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | <u>Prop</u> ag <u>atio</u> n Delay,<br>CET to TC |        | 15<br>15 | 20<br>20 | ns   |                                                   |  |  |

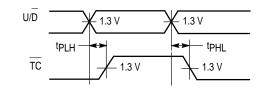

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propag <u>atio</u> n Delay,<br>U/D to TC         |        | 17<br>19 | 25<br>29 | ns   |                                                   |  |  |

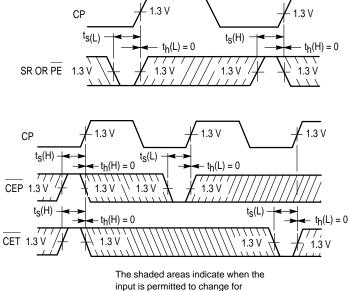

### AC SETUP REQUIREMENTS (T<sub>A</sub> = 25°C)

|                |                               | Limits |     |     |      |                         |

|----------------|-------------------------------|--------|-----|-----|------|-------------------------|

| Symbol         | Parameter                     | Min    | Тур | Max | Unit | Test Conditions         |

| tW             | Clock Pulse Width             | 25     |     |     | ns   |                         |

| ts             | Setup Time,<br>Data or Enable | 20     |     |     | ns   |                         |

| t <sub>s</sub> | <u>Se</u> tup Time<br>PE      | 25     |     |     | ns   | V <sub>CC</sub> = 5.0 V |

| t <sub>s</sub> | Se <u>tu</u> p Time<br>U/D    | 30     |     |     | ns   |                         |

| t <sub>h</sub> | Hold Time<br>Any Input        | 0      |     |     | ns   |                         |

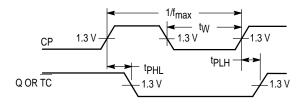

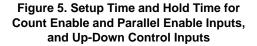

### AC WAVEFORMS

Figure 1. Clock to Output Delays, Count Frequency, and Clock Pulse Width

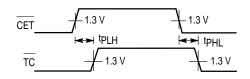

Figure 2. Count Enable Trickle Input To Terminal Count Output Delays

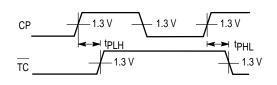

### Figure 3. Clock to Terminal Delays

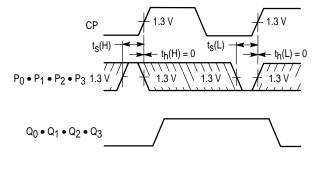

Figure 4. Setup Time (t<sub>S</sub>) and Hold (t<sub>h</sub>) for Parallel Data Inputs

predictable output performance.

Figure 6. Up-Down Input to Terminal Count Output Delays